(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7269347号

(P7269347)

(45)発行日 令和5年5月8日(2023.5.8)

(24)登録日 令和5年4月25日(2023.4.25)

(51)国際特許分類

|        |                 |        |      |   |

|--------|-----------------|--------|------|---|

| H 05 K | 3/46 (2006.01)  | H 05 K | 3/46 | Q |

| H 05 K | 1/09 (2006.01)  | H 05 K | 3/46 | G |

| H 05 K | 3/32 (2006.01)  | H 05 K | 3/46 | N |

| H 05 K | 1/18 (2006.01)  | H 05 K | 1/09 | A |

| H 01 L | 23/12 (2006.01) | H 05 K | 3/32 | B |

請求項の数 9 (全22頁) 最終頁に続く

(21)出願番号 特願2021-533390(P2021-533390)

(86)(22)出願日 令和1年8月22日(2019.8.22)

(65)公表番号 特表2021-534596(P2021-534596)

A)

(43)公表日 令和3年12月9日(2021.12.9)

(86)国際出願番号 PCT/US2019/047731

(87)国際公開番号 WO2020/041605

(87)国際公開日 令和2年2月27日(2020.2.27)

審査請求日 令和4年8月22日(2022.8.22)

(31)優先権主張番号 62/721,538

(32)優先日 平成30年8月22日(2018.8.22)

(33)優先権主張国・地域又は機関

米国(US)

早期審査対象出願

(73)特許権者 521075321

リキッド ワイヤ インコーポレイテッド

L I Q U I D W I R E I N C .

アメリカ合衆国 9 7 2 0 2 オレゴン州

, ポートランド, 1 7 1 0 エスイー

ブルックリン ストリート

(74)代理人 100137095

弁理士 江部 武史

(74)代理人 100091627

弁理士 朝比 一夫

(72)発明者 ローナイ, マーク

アメリカ合衆国 9 7 0 0 8 オレゴン州

, ビーバートン, 8 2 4 0 エス ダブ

リュー ニンバス アベニュー

(72)発明者 リビエラ, トレバー スピゲル アント

最終頁に続く

(54)【発明の名称】 変形可能な導体を有する構造体

## (57)【特許請求の範囲】

## 【請求項1】

基板と、

前記基板によって支持され、変形可能な導電性材料から形成される複数の接点のパターンと、

前記基板によって支持され、前記複数の接点のパターンに対応するパターンで配置された複数の端子を有する電気部品と、を含み、

前記電気部品の前記複数の端子のうちの1つ以上は、対応する前記複数の接点のうちの1つ以上と接触して、前記電気部品と前記複数の接点との間に1つ以上の電気的接続部を形成し、

前記基板は、自己接着性表面を有し、

前記電気部品は、前記基板に固定されるように、前記基板の前記自己接着性表面に直接取り付けられていることを特徴とする回路アセンブリ。

## 【請求項2】

前記基板によって支持され、変形可能な導電性材料から形成された複数の導電性トレースのパターンをさらに含み、

前記複数の導電性トレースのパターンは、前記複数の接点のパターンと相互接続されている請求項1に記載の回路アセンブリ。

## 【請求項3】

前記電気部品および前記複数の接点を覆う封止材をさらに含む請求項1に記載の回路ア

センブリ。

**【請求項 4】**

前記複数の接点は、前記基板上に形成されている請求項 1 に記載の回路アセンブリ。

**【請求項 5】**

前記複数の接点は、前記基板の前記自己接着性表面上に形成されている請求項 1 に記載の回路アセンブリ。

**【請求項 6】**

前記複数の接点は、前記基板内の凹部に設けられている請求項 4 に記載の回路アセンブリ。

**【請求項 7】**

前記基板によって支持された絶縁材料層をさらに含み、

前記複数の接点は、前記絶縁材料層内の凹部に設けられている請求項 1 に記載の回路アセンブリ。

**【請求項 8】**

前記複数の接点は、前記絶縁材料層内のビアによって形成されている請求項 7 に記載の回路アセンブリ。

**【請求項 9】**

前記基板は、伸縮性材料を含む請求項 1 に記載の回路アセンブリ。

**【発明の詳細な説明】**

**【背景技術】**

20

**【0001】**

(関連出願の相互参照)

本出願は、2018年8月22日に出願された米国仮特許出願第62/721,538号からの優先権を主張し、これは参照により組み込まれる。

**【0002】**

(著作権)

本特許文書の開示の一部は、著作権の保護対象となる内容を含む。著作権者は、任意の者による本特許開示のファクシミリによる複製に対しては、特許商標庁の特許ファイルまたは記録にあることから、異議を有さないが、他の場合にはいかなる著作権も全て留保する。

30

**【0003】**

(技術分野)

本特許開示の発明原理は、一般に、変形可能な導電性材料 (deformable conductive materials) に関し、より具体的には、変形可能な導電性材料を伴う電気的接続部および/または層 (electrical connections and/or layers) を有する構造体、ならびにそのような構造体を形成する方法に関する。

**【発明の概要】**

**【0004】**

回路アセンブリは、基板と、該基板によって支持され、変形可能な導電性材料から形成される接点 (contact points) のパターンとを備え得る。また、アセンブリは、基板によって支持され、接点のパターンに対応するパターンで配置された端子を有する電気部品を備え得る。電気部品の1つ以上の端子は、対応する接点の1つ以上と接触して、電気部品と接点との間に1つ以上の電気的接続部を形成する。アセンブリは、基板によって支持され、変形可能な導電性材料から形成される導電性トレースのパターンをさらに備えてもよい。ここで、導電性トレースのパターンは、接点のパターンと相互接続される。アセンブリは、電気部品および接点を覆う封止材をさらに備え得る。接点は、基板上に形成されてもよい。接点は、基板の表面上に形成されてもよい。接点は、基板の凹部に設けられてもよい。アセンブリは、基板によって支持される絶縁材料層をさらに備えてもよく、接点が絶縁材料層の凹部に設けられてもよい。接点は、絶縁材料層におけるビアによって形成されてもよい。電気部品は、表面実装コンポーネントを備え得る。電気部品は、パッケージ

40

50

化された集積回路を備え得る。電気部品は、ペア集積回路ダイ (bare integrated circuit die) を備え得る。基板は、可撓性材料を含み得る。基板は、伸縮性材料を含み得る。基板の少なくとも一部は、接着性を有していてもよい。電気部品は、接着性によって基板に取り付けられてもよい。

#### 【 0 0 0 5 】

回路アセンブリは、基板と、基板によって支持される第1の絶縁材料層であって、その中に形成されるチャネル (channels) のパターンを有する第1の絶縁材料層と、チャネル内に配置された変形可能な導電性材料とを備え得る。アセンブリは、第1の絶縁材料層におけるチャネルに配置された変形可能な導電性材料を封入するように配置される第2の絶縁材料層をさらに備え得る。第2の絶縁材料層は、チャネルと相互接続された接点のパターンを備え得る。第2の絶縁材料層は、第1の絶縁材料層のチャネルのパターンと整列したビアのパターンを備え得る。アセンブリは、第2の絶縁材料層によって支持される第3の絶縁材料層であって、その中に形成されるチャネルのパターンを有する第3の絶縁材料層をさらに備え得る。第2の絶縁材料層は、第1の絶縁材料層のチャネルのパターンおよび第3の絶縁材料層のチャネルのパターンと整列したビアのパターンを備え得る。第3の絶縁材料層は、第3の絶縁材料層のチャネルと相互接続された接点のパターンを備え得る。第2の絶縁材料層は、第1の絶縁材料層のチャネルのパターンと整列したビアの第2のパターンを備えていてもよく、第3の絶縁材料層は、第2の絶縁材料層におけるビアの第2のパターンと整列したビアのパターンを備えていてもよく、第3の絶縁材料層の接点のパターンは、第3の絶縁材料層のビアのパターンのうちの1つ以上を備えていてもよい。アセンブリは、第3の絶縁材料層のチャネル内に配置された変形可能な導電性材料を封入するように配置された第4の絶縁材料層をさらに備え得る。第4の絶縁材料層は、第3の絶縁材料層のチャネルのパターンと整列したビアのパターンを備え得る。第2の絶縁材料層、第3の絶縁材料層および第4の絶縁材料層は、互いに、かつ第1の絶縁材料層のチャネルと整列したビアのパターンを備える。アセンブリは、第4の絶縁材料層によって支持される電気部品をさらに備えてよく、電気部品は端子のパターンを有し、第4の絶縁材料層を介する2つ以上のビアは、電気部品の端子のパターンに対応する接点のパターンを形成する。

#### 【 0 0 0 6 】

回路アセンブリは、基板と、基板に取り付けられ、変形可能な導電性材料を含む第1の通路パターンを有する第1の絶縁材料層とを備え得る。回路アセンブリは、第1の絶縁材料層に取り付けられ、変形可能な導電性材料を含む第2の通路パターンを有する第2の絶縁材料層をさらに備え得る。ここで、第2の通路パターンは、第1の通路パターンと少なくとも部分的に連通する。第1の通路パターンは1つ以上のトレースを備えていてもよく、第2の通路パターンは1つ以上のビアを備えていてもよい。回路アセンブリは、第2の絶縁材料層に取り付けられ、変形可能な導電性材料を含む第3の通路パターンを有する第3の絶縁材料層をさらに備え得る。ここで、第3の通路パターンは、少なくとも部分的に第2の通路パターンと連通する。第1の通路パターンは1つ以上のトレースを備えていてもよく、第2の通路パターンは1つ以上のビアを備えていてもよく、第3の通路パターンは1つ以上のトレースを備えていてもよい。回路アセンブリは、第3の絶縁材料層に取り付けられ、変形可能な導電性材料を含む第4の通路パターンを有する第4の絶縁材料層をさらに備え得る。ここで、第4の通路パターンは、少なくとも部分的に第3の通路パターンと連通する。第1の通路パターンは1つ以上のトレースを備えていてもよく、第2の通路パターンは1つ以上のビアを備えていてもよく、第3の通路パターンは1つ以上のトレースを備えていてもよく、第4の通路パターンは1つ以上のビアを備えていてもよい。

#### 【 0 0 0 7 】

方法は、1つ以上の通路 (passages) を有する第1の絶縁材料層を基板上に積層するステップと、第1の絶縁材料層における通路のうちの少なくとも1つに変形可能な導電性材料を堆積するステップと、第1の絶縁材料層上に第2の絶縁材料層を積層するステップとを含み得る。ここで、第2の絶縁材料層は、第1の絶縁材料層における少なくとも1つの

10

20

30

40

50

通路に変形可能な導電性材料を少なくとも部分的に封入する。第1の絶縁材料層における通路のうちの少なくとも1つは、第1の絶縁材料層の厚さ全体を貫通してもよい。第1の絶縁材料層における通路のうちの少なくとも1つに変形可能な導電性材料を堆積するステップは、少なくとも1つの通路に変形可能な導電性材料を過剰充填するステップと、第1の絶縁材料層の表面から過剰な変形可能な導電性材料を除去するステップとを含み得る。第1の絶縁材料層の表面から剥離層を除去するステップを含み得る。第2の絶縁材料層が1つ以上の通路を有する方法であって、当該方法は、第2の絶縁材料層における通路のうちの少なくとも1つに変形可能な導電性材料を堆積するステップと、第2の絶縁材料層上に第3の絶縁材料層を積層するステップとをさらに含み得る。ここで、第3の絶縁材料層は、第2の絶縁材料層における少なくとも1つの通路に変形可能な導電性材料を少なくとも部分的に封入する。第1の絶縁材料層における通路のうちの少なくとも1つは、第2の絶縁材料層における通路のうちの少なくとも1つと連通し得る。第2の絶縁材料層の通路のうちの少なくとも1つは、第2の絶縁材料層の厚さ全体を貫通してもよい。第3の絶縁材料層が1つ以上の通路を有する方法であって、当該方法は、第3の絶縁材料層における通路のうちの少なくとも1つに変形可能な導電性材料を堆積するステップと、第3の絶縁材料層上に第4の絶縁材料層を積層するステップとをさらに含み得る。ここで、第4の絶縁材料層は、第3の絶縁材料層における少なくとも1つの通路に変形可能な導電性材料を少なくとも部分的に封入する。

## 【0008】

方法は、基板上に少なくとも1つの接点を形成するステップであって、該接点が変形可能な導電性材料を有するステップと、電気部品を該基板上に支持するステップであって、該電気部品が少なくとも1つの端子を有するステップとを含み得る。ここで、該電気部品の少なくとも1つの端子は、該接点のうちの少なくとも1つと接触して、該電気部品と該接点との間に少なくとも1つの電気的接続部を形成する。少なくとも1つの端子はパターン状に配置された複数の端子を備えていてもよく、少なくとも1つの接点は変形可能な導電性材料を有し、かつ電気部品の端子のパターンに対応するパターンで配置された複数の接点を備えていてもよく、電気部品の複数の端子は複数の接点と接触して、電気部品と接点との複数の電気的接続部を形成してもよい。

## 【図面の簡単な説明】

## 【0009】

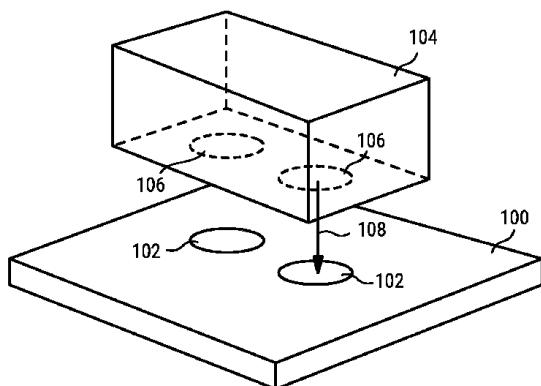

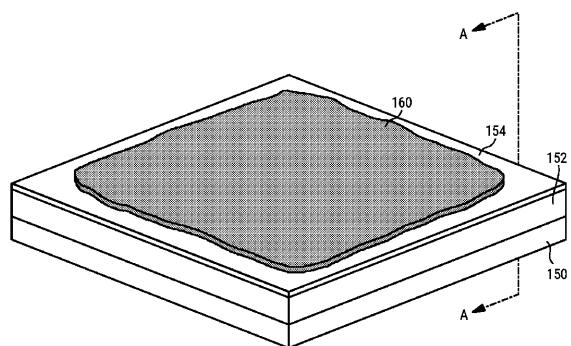

【図1】図1は、本特許開示のいくつかの発明原理による回路アセンブリの実施形態を示す分解図である。

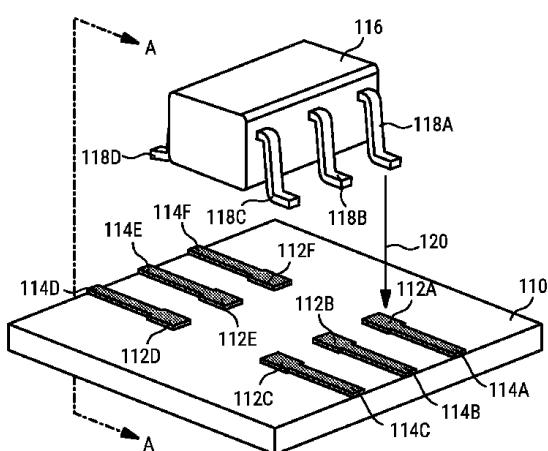

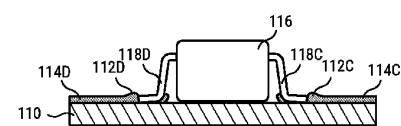

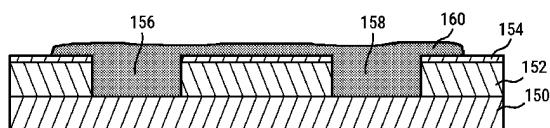

【図2】図2は、本特許開示のいくつかの発明原理による回路アセンブリの例示的実施形態の部分分解斜視図である。

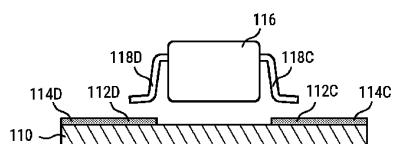

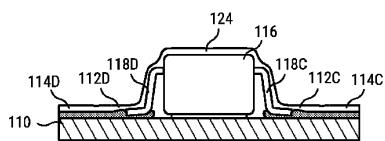

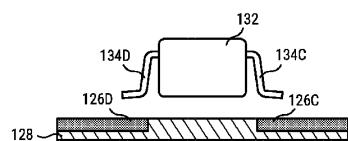

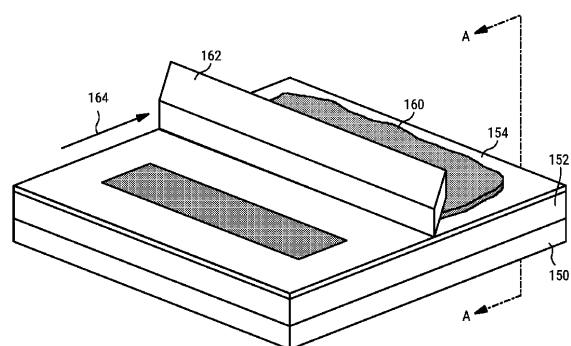

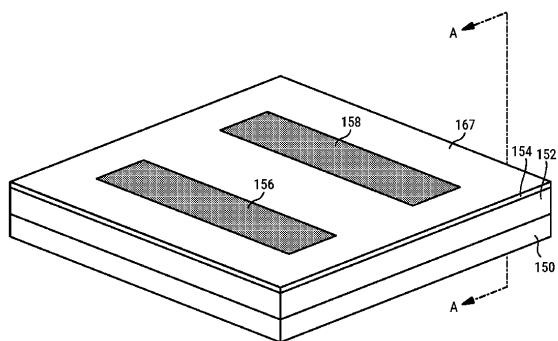

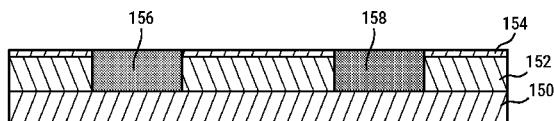

【図3】図3A～図3Eは図2のA-A線に沿った断面図であって、本特許開示のいくつかの発明原理による、いくつかの可能な例示的実装の詳細および代替実施形態を示す断面図である。

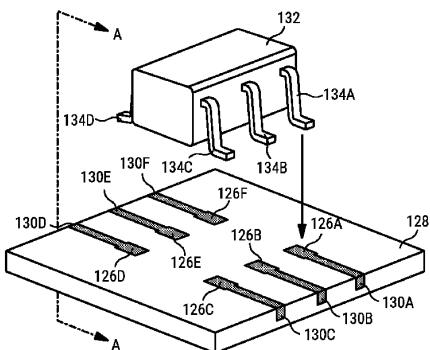

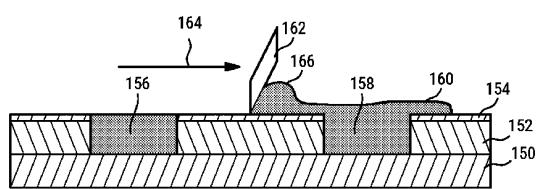

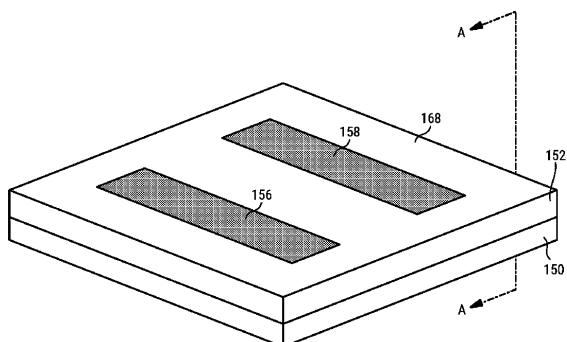

【図4】図4は、本特許開示のいくつかの発明原理による回路アセンブリの別の例示的実施形態の部分分解斜視図である。

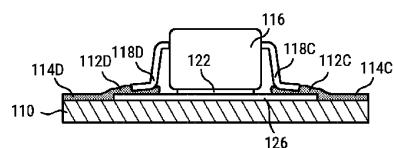

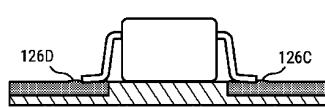

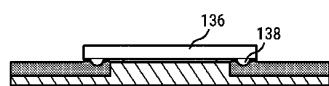

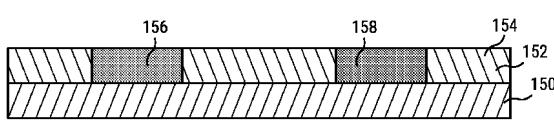

【図5】図5A～図5Cは、図4のA-A線に沿った断面図であって、本特許開示のいくつかの発明原理による、いくつかの可能な例示的実装の詳細および代替実施形態を示す断面図である。

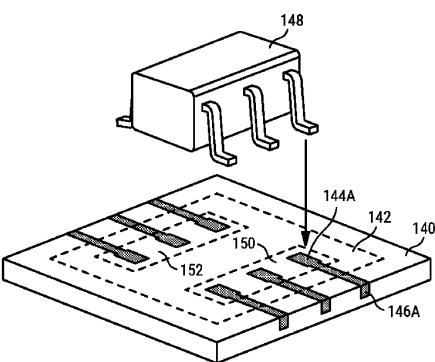

【図6】図6は、本特許開示のいくつかの発明原理による回路アセンブリの別の例示的実施形態の部分分解斜視図である。

【図7-15】図7Aおよび図7B～図15Aおよび図15Bは、本特許開示のいくつかの発明原理による、回路アセンブリの実施形態および回路アセンブリを製造する方法の実施形態を示す。

【図16】図16は、本特許開示のいくつかの発明原理による回路アセンブリの別の実施形態を示す断面図である。

10

20

30

40

50

【図17】図17は、本特許開示のいくつかの発明原理による回路アセンブリの別の実施形態を示す断面図である。

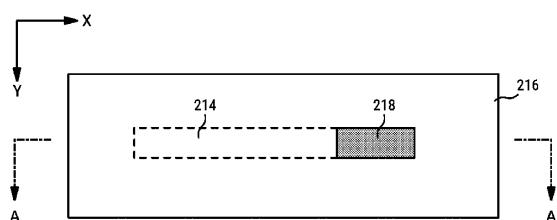

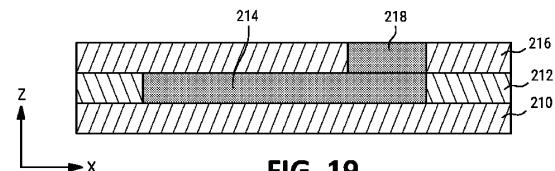

【図18-19】図18および図19は、それぞれ、本特許開示のいくつかの発明原理によるピア構造の平面図および断面図である。

【発明を実施するための形態】

【0010】

以下に記載される実施形態および例示的実装の詳細は、例示の目的のためにある。図面は必ずしも縮尺通りに示されていない。本発明の原理は、これらの実施形態および詳細に限定されない。

【0011】

本特許開示の発明原理のいくつかは、回路アセンブリにおけるコンポーネントと変形可能な導電性材料との間の電気的接続部に関する。

【0012】

図1は、本特許開示のいくつかの発明原理による回路アセンブリの実施形態を示す分解図である。図1の実施形態は、基板100を備え、基板100は、該基板によって支持され、変形可能な導電性材料から形成される接点102のパターンを有する。また、電気部品104は、基板100によって支持され、接点102のパターンに対応するパターンで配置された1つ以上の端子106を有する。端子106は、電気部品104の底部に配置されているので、破線(ファンтом図)で示されている。電気部品104の端子106のうちの1つ以上は、対応する接点102のうちの1つ以上と接触して、電気部品と接点との間に1つ以上の電気的接続部を形成し得る。1つ以上の端子106は、例えば、矢印108によって示されるように、電気部品104が、基板100に取り付けられる時、基板100に近づけられる時、あるいは基板100によって支持される時に、1つ以上の接点102と接触し得る。したがって、本発明の原理のいくつかは、はんだ付けまたは電気的接続部を生成するための他の任意の従来プロセス無しで、電気的接続部の生成を可能にする。

【0013】

接点102は、例えば、基板の表面上に直接形成されることにより、基板内の凹部に設けられることにより、基板上の別の材料層上に形成されることにより、または他の方法により、基板100によって支持され得る。電気部品104は、例えば、基板の表面に直接取り付けられることにより、基板によって支持される別のコンポーネントに取り付けされることにより、接点102のパターンによって支持されることにより、または他の方法により、基板100によって支持され得る。

【0014】

図1のアセンブリは、基板によって支持され、変形可能な導電性材料から形成される導電性トレースのパターンをさらに備え得る。導電性トレースのパターンは、接点のパターンと相互接続されてもよい。

【0015】

図1の実施形態は、多種多様な材料およびコンポーネントを用いて実施することができる。例えば、基板は、ポリジメチルシロキサン(PDMS)等の任意のシリコン系材料、熱可塑性ポリウレタン(TPU)、エチレンプロピレンジエンテルポリマー(EPDPM)、ネオプレン、ポリエチレンテレフタレート(PET)、ならびにエポキシおよびエポキシ系材料等を含む、プラスチック材料または天然もしくは合成ゴム、布、木材、皮革、紙、ガラス繊維および他の複合材料、ならびに他の絶縁材料および/またはそれらの組合せから製造され得る。

【0016】

変形可能な導電性材料は、液体、ペースト、ゲル、粉末を含む任意の形態で、または、軟質性、可撓性、伸縮性、屈曲性、弾性、流動性、粘弾性、またはニュートン特性および非ニュートン特性を含むその他の変形可能な特性を有する他の形態で、提供されてもよい。変形可能な導電性材料は、ガリウムインジウム合金(商標「Metal Gel」とも

10

20

30

40

50

いう)等の導電性ゲルを含む変形可能な導体(deformable conductors)を含むが、これらに限定されない任意の電気活性材料(electroactive materials)で実現することができる。そのいくつかの例は2017年2月27日に出願された国際特許出願PCT/US2017/019762に開示され、これは参照により組み込まれる。該出願は、2017年9月8日に国際公開番号WO2017/151523A1として公開され、これも参照により組み込まれる。他の適切な電気活性材料としては、金、ニッケル、銀、白金、銅等を含む任意の導電性金属、シリコン、ガリウム、ゲルマニウム、アンチモン、ヒ素、ホウ素、炭素、セレン、硫黄、テルル等に基づく半導体、ヒ化ガリウム、アンチモン化インジウム、および多くの金属の酸化物を含む半導体化合物、有機半導体、ならびにグラファイト等の導電性非金属物質が挙げられる。導電性ゲルの他の例には、グラファイトまたは炭素の他の同素体に基づくゲル、イオン性化合物、または他のゲルが含まれる。

10

#### 【0017】

電気部品は、集積回路、トランジスタ、ダイオード、LED、コンデンサ、抵抗器、インダクタ、スイッチ、端子、コネクタ、ディスプレイ、センサ、プリント回路基板、または他のデバイスを含むがこれらに限定されない、任意の電気、電子、電気機械、または他の電気部品であってもよい。電気部品は、ベアコンポーネントの形態であってもよく、または、様々なタイプのパッケージ内に部分的にもしくは完全に封入されてもよい。集積回路および他の半導体の場合には、以下でより詳細に説明するように、幅広いパッケージタイプを使用することができる。チップスケールデバイス(chip-scale device)等の基板上に実装されているがパッケージ内に完全には封入されていないダイまたはベアダイの形態の集積回路を使用することもできる。

20

#### 【0018】

接点のパターンは、1つ以上の電気部品上の端子の数および配置、ならびに電気的接続部の数および配置に応じて、接点の任意の数および配置を含む(单一の接点を含む)ことができる。

#### 【0019】

図2は、本特許開示のいくつかの発明原理による回路アセンブリの例示的実施形態の部分分解斜視図である。図2の実施形態は、リード118A～118Fの形態の端子を有する表面実装パッケージにおける集積回路(IGC)116を備える。変形可能な導電性材料から作られ、集積回路116上のリード118A～118F(総称して118ともいう)のフットプリントに適合するように配置された接点112A～112F(総称して112ともいう)のパターンを基板110は有する。この例では、IGCとプリント回路基板との間に電気的接続部を作るために従来から使用されるはんだパッドの形状で接点が形成される。変形可能な導電性材料から作られ得る導電性トレース114A～114F(総称して114ともいう)は、接点112A～112Fに接続され、この図において基板110の端部で終点となる。トレース114A～114Fは例えば、集積回路116を他のコンポーネント、回路、端子等に接続するために使用されてもよい。リード118A～118Fは、矢印120で示すように、集積回路116が基板上に配置される時、対応する接点112A～112Fと接触する。

30

#### 【0020】

図2の実施形態では、接点112およびトレース114が例えば、フレキソ印刷、プロック印刷、ジェット印刷、3D印刷、ステンシル(stenciling)、マスクスプレー(masked spraying)、押出、圧延もしくはブラッシングのスクリーン印刷、パターン堆積、または任意の他の適切な技術によって、基板110の上面に形成され、上方に突出する。

40

#### 【0021】

図3A～図3Eは、図2のA-A線に沿った断面図であって、いくつかの可能な例示的実装の詳細および代替実施形態を示す断面図である。

#### 【0022】

図3Aは、IGC116が、基板110上へ配置される前の状態を示す。

#### 【0023】

50

図3Bは、基板110上に配置され、リード118と接点112との間にオーミック接觸 (ohmic contacts) を形成するIC116を示す。IC116は、接着剤層122によって基板110に固定される。この例では、リード118は、接点112の変形可能な導電性材料の一部をずらしており、これは、リード118の形状に適合し、追加の表面積および向上した電気的接続部を提供し得る。

【0024】

図3Cは、図3Bの実施形態と同様であるが、集積回路116、リード118、接点112およびトレース114を覆う封止材124を有する実施形態を示す。また、封止材124は、集積回路116、リード118および基板110の間の空間を充填してもよい。封止材124に適した材料の例には、P D M S等のシリコン系材料、ウレタン、エポキシ、ポリエステル、ポリアミド、ワニス、ならびに、保護コーティングを提供し、および/またはアセンブリと一緒に保持するのを助けることができる任意の他の材料が含まれる。

【0025】

図3Dは、集積回路116が基板110に直接接觸する実施形態を示し、これは、例えば、封止材が集積回路116を基板110に保持するのに十分な強度を提供する場合や、本質的に接着性または粘着性の材料から製造された基板110を用いる場合に、使用され得る。この実施形態では、リード118が接点112内にさらに押し込まれてもよい。

【0026】

図3Eは、追加の材料層126が、基板110の上面に取り付けられ、接点112のパターンの下に配置される実施形態を示す。層126は、様々な機能を発揮することができる。例えば、基板が可撓性または伸縮性材料から製造される実装において、より剛性の高いまたはより伸縮性の低い材料から層126が製造され、集積回路116の端子118と接点112との間の接続不良を引き起こす可能性がある、集積回路または他の電気部品の直下の基板の領域の屈曲または伸張を防止してもよい。別の例として、層126は、集積回路116または他の電気部品のための放熱または熱放散機能 (heat sinking or heat dissipating function) を発揮することができる。あるいは、追加の層126が基板110の下、基板内、または任意の他の適切な位置に配置されてもよい。層126は、材料の連続シートとして形成されてもよく、または、例えば、接点112、トレース114、集積回路116、または他のコンポーネントの一部または全部に対する開口部を有するようにパターン化されてもよい。層126に使用することができる材料の例には、T P U、ガラス繊維、P E T、および他の比較的剛性のあるもしくは非伸縮性の材料等の形態が含まれる。

【0027】

図4は、本特許開示のいくつかの発明原理による回路アセンブリの別の例示的実施形態の部分分解斜視図である。図4の実施形態は、図2の実施形態と同様であるが、接点126A～126Fは、変形可能な導電性材料で部分的または完全に充填された基板128内の凹部によって形成される。また、図4の実施形態は、基板内の凹部に設けられたトレース130を備える。

【0028】

基板の凹部は、ドリル加工 (drilling)、ルーティング (routing)、エッティング、切断、または機械的光学 (例えば、レーザ)、化学的、電気的、超音波もしくは他の装置を用いて材料を除去する任意の他の方法あるいはそれらの組合せによって、材料のシートの部分を除去することによって形成され得る。代替的に、基板は、成形、鋳造、3D印刷、または他の形成プロセスによって、その中に凹部を有するように形成されてもよい。変形可能な導電性材料は、印刷、ステンシル、スプレー、圧延、ブラッシング、および材料を凹部に堆積するための任意の他の技術を含む、上述のプロセスのいずれかによって、凹部に堆積されてもよい。さらに、凹部は変形可能な導電性材料で過剰に充填されてもよく、次いで、以下でより詳細に記載されるように、基板の周囲表面と同一平面上になる、または基板の周囲表面よりわずかに上または下になるように、搔き取り (scraping)、圧延、ブラッシング等を含む任意の適切な技術が、過剰な材料を除去するために使用されてもよ

10

20

30

40

50

い。

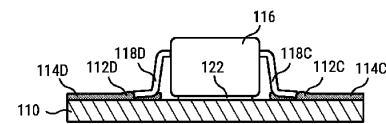

【0029】

図5A～図5Cは、図4のA-A線に沿った断面図であって、いくつかの可能な例示的実装の詳細および代替実施形態を示す断面図である。

【0030】

図5Aは、IC132が、基板128上へ配置される前の状態を示す。

【0031】

図5Bは、基板128上に配置され、リード134と接点126との間にオーミック接觸を形成するIC132を示す。この例では、IC132は、例えば自己接着性表面を有し得る基板110に直接取り付けられる。あるいは、IC132は、接着剤または任意の他の適切な技術を使用して基板に取り付けられてもよい。この例では、リード134は、接点126内の下方へ突出し、変形可能な導電性材料の一部をずらしており、これは、リード134の形状に適合し、追加の表面積および向上した電気的接続部を提供し得る。

【0032】

図2、図3A～図3E、図4および図5A～図5Bに示される集積回路は、SOT23-6(6つのリードの小型アウトライントランジスタ)パッケージ等の表面実装パッケージにパッケージされるが、本特許開示の発明原理に従って、任意の他の種類のICパッケージおよび電子部品を使用することができる。例えば、リードレスチップキャリアは、変形可能な導電性材料のパターンを乱すことなく、開示された接点のいずれかに良好な接觸領域を提供する平坦なリード面を備えた端子を有し得る。良好に動作し得るいくつかの他のタイプのパッケージには、ボールグリッドアレイ(BGA)やウエハレベルチップスケールパッケージング(WL-CSP)のようなはんだ構造が突出しているパッケージや、リード付きチップキャリアのようなリードがわずかに突出しているパッケージが含まれる。それらのはんだ構造またはリードは、接点にわずかに沈み込むことで、パターンを乱すほどの変形可能な導電性材料の位置ずれ無しで、信頼性の高いオーミック接続(ohmic connections)を作り出すことができる。

【0033】

図5Cは、はんだバンプ138を有するチップスケールパッケージ136が基板128に接着された実施形態を示す。

【0034】

図6は、接点144およびトレース146のパターンを形成した後であるが、集積回路148を取り付ける前における、追加の材料層142を基板140の表面に取り付けた実施形態を示す。層142は、例えば、図3Eの実施形態における層126と同様であってもよい。この実施形態では、層142が接点144のための開口部を備える。

【0035】

パッケージ化された集積回路および他のデバイスに加えて、ペア集積回路ダイおよび他のコンポーネントは、本特許開示の発明原理に従って使用され得る。例えば、ボンディングパッドまたは接点パッドを有するICダイは、ダイ上のボンディングパッドまたは接点パッドのパターンに対応する接点の同一平面パターンまたは突出パターンを有する基板に取り付けられてもよい。これは通常、変形可能な導電性材料を含む接点がボンディングパッドまたは接点パッドとのオーミック接続を形成するように、ダイを上下逆に(すなわち、ボンディングパッドまたは接点パッドが基板の上面を向くように)搭載することを必要とする。

【0036】

図4、図5A～図5Cおよび図6の実施形態では変形可能な導電性材料が一般に基板の表面と同一平面となるように示されているが、変形可能な導電性材料は代替的に、基板の表面から沈降するように(すなわち、下に凹むように)形成されてもよく、または基板の表面から隆起するように(すなわち、上に突出するように)形成されてもよい。例えば、凹部の一部または全部を材料で部分的にのみ充填することによって、または掻き取り、ブラッシング、ガウジング(gouging)、エッティング、蒸発等によって一部の材料を除去す

10

20

30

40

50

ることによって、表面から沈降するように材料が形成されてもよい。また、パターン堆積 (pattern depositing)、ステンシル、様々な形態の印刷等によって、表面から隆起するように材料が形成されてもよい。いくつかの実施形態では、凹部のパターンに一致するパターンを有する剥離層を使用することによって、表面から隆起するように材料が形成されてもよい。剥離層が基板上に配置され、凹部のパターンが過剰充填されてから、剥離層の上面と同一平面上で掻き取られてもよい。その後、剥離層を除去して、以下に説明する実施形態と同様の方法で突出材料を残すことができる。

#### 【0037】

図2、図3A～図3E、図4、図5A～図5Cおよび図6の実施形態では、接点およびトレースは一般に、基板の表面上に示されているか、または基板内の途中まで延在している。他の実施形態では、接点および／またはトレースの一部または全部は、基板の厚さ全体を介して延在してもよい。例えば、接点は、基板を介するビアとして実装されてもよく、そして、以下に記載される実施形態のうちの1つにおいて層として機能してもよい。

10

#### 【0038】

本特許開示のいくつかの追加の発明原理は、変形可能な導電性材料を含む通路を有する層を備える回路アセンブリに関する。電気的接続部に関する発明原理および通路を有する層に関する発明原理は、独立した有用性を有する独立した原理である。しかしながら、本特許開示のいくつかの追加の発明原理は、これらの別々の原理のいくつかを組み合わせて、相乗的な結果を提供することができる方法で、より多くの発明原理をもたらすことができる。

20

#### 【0039】

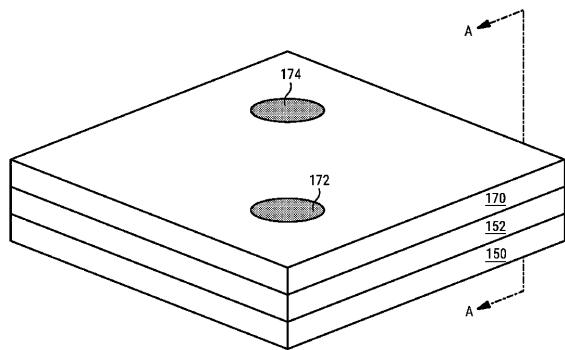

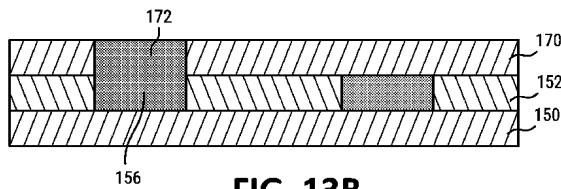

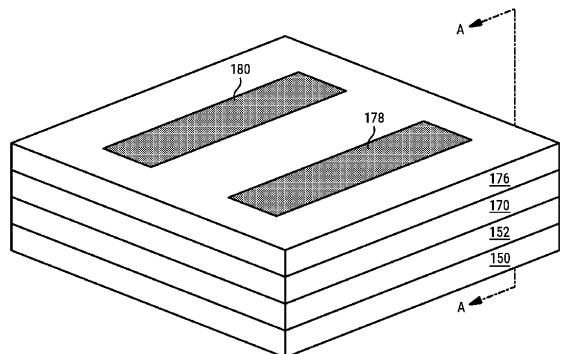

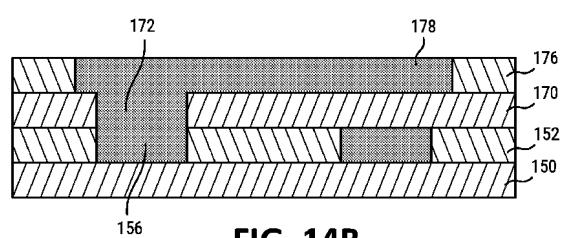

図7Aおよび図7B～図15Aおよび図15Bは、本特許開示のいくつかの発明原理による回路アセンブリの実施形態および回路アセンブリを製造する方法の実施形態を示す。図7B、図8B、図9B、図10B、図11B、図12B、図13B、図14Bおよび図15Bは、それぞれ図7A、図8A、図9A、図10A、図11A、図12A、図13A、図14Aおよび図15Aの斜視図におけるA-A線に沿った断面図である。

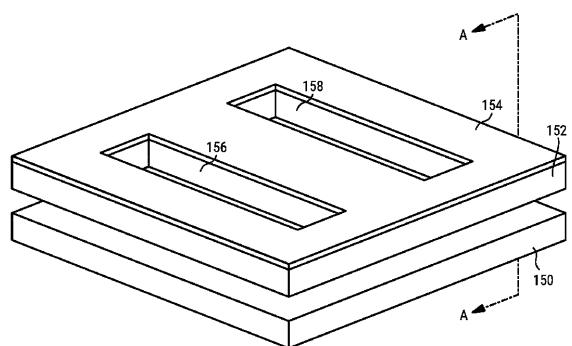

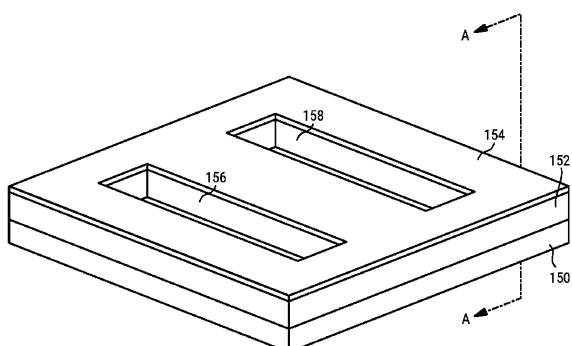

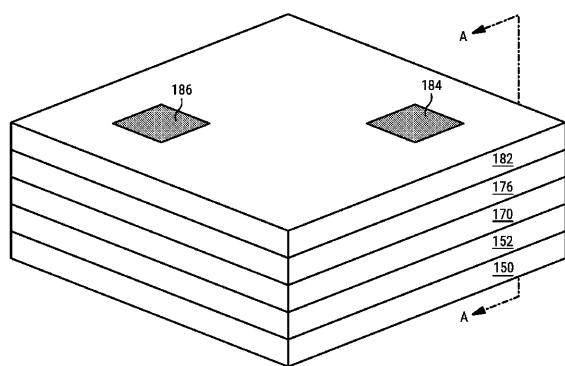

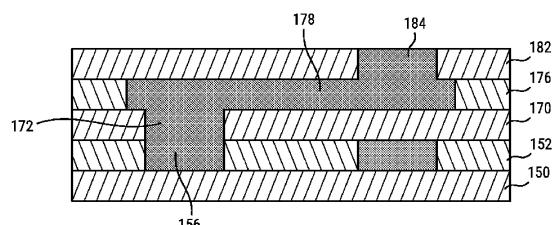

#### 【0040】

図7Aは、基板150、第1の絶縁材料層（第1の層）152および剥離層154の斜視図である。図7Bは、図7AのA-A線に沿った断面図である。基板150および第1の層152、ならびに、図8Aおよび図8B～図15Aおよび図15Bに示される絶縁層は、図1の実施形態に関して上述した絶縁材料から製造することができる。例えば、基板150および第1の層152は、伸縮性のあるTPUまたはエポキシ系材料から製造されてもよい。基板150は一般に、中断されていない材料シート（uninterrupted sheet of material）であってもよい。一方、第1の絶縁材料層152および剥離層154は、通路156および158のパターンを有し、この例では、それらの全体の厚さを介してチャネルが切断され、マスクまたはステンシルを作る。第1の層よりも薄くてもよい剥離層154は、第1の層152上に積層され、図1の実施形態に関して上述した絶縁材料のいずれかから製造されてもよい。例えば、剥離層154は、PETの薄層から製造することができる。剥離層154が最終的に除去される実施形態では、剥離層154は、金属化プラスチックまたは他の導電性材料ならびに、合金または純粋な形態の金属を含む導電性材料から製造されてもよい。

30

#### 【0041】

通路156および158は、レーザ切断、ドリル加工、ルーティング、ダイ切断、ウォータージェット切断等の任意の適切なサブトラクティブ技術（subtractive technique）を用いて、第1の絶縁材料層152および剥離層154に形成されてもよい。他の実施形態では、第1の層152および／または剥離層が3D印刷、パターン堆積等のアディティブ製造技術（additive manufacturing technique）によって形成されてもよい。

40

#### 【0042】

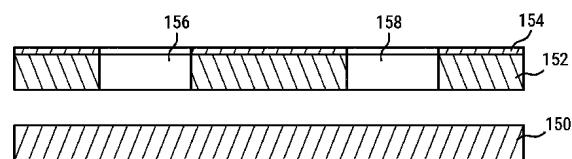

図8Aは、第1の層が基板上に積層された後の基板150および第1の絶縁材料層152の斜視図である。図8Bは、図8AのA-A線に沿った断面図である。基板150およ

50

び第1の絶縁材料層152は、一緒に結合、融合または硬化され、あるいは、任意の適切なプロセスおよび／または材料を用いる他の方法で互いに取り付けられてもよい。例えば、基板150および第1の層152は、TPUまたは他の熱可塑性樹脂から製造される場合、熱および圧力で一緒に結合されてもよい。別の例として、基板150および第1の層152は、いくつかのエポキシ系材料等の本質的に接着性を有する材料から製造される場合、これらの層を一緒にプレスすることによって一緒に結合されてもよい。さらに別の例では、基板150および第1の層152は、UV硬化性材料から製造され、積層後にUV光源にさらされてもよい。2つの層の積層および結合は、チャネル156および158の底部を閉鎖し得、その結果、それらが材料で充填される時、漏れがほとんどまたは全くない。

10

#### 【0043】

図9Aは、チャネル156および158が変形可能な導電性材料160で過剰充填された後の、基板150、第1の絶縁材料層152および剥離層154の斜視図である。

#### 【0044】

図9Aおよび図9Bを参照すると、チャネル156および158は、図1の実施形態に關して上述した変形可能な導電性材料のいずれかで実施され得る変形可能な導電性材料160で過剰充填されている。変形可能な導電性材料としては、例えば、導電性ゲルを用いることができる。材料は、押出、圧延、塗布(swabbing)、噴霧、印刷、ブラッシング、堆積等の任意の適切な技術を使用して過剰充填されてもよい。実施形態の一例では、変形可能な導電性材料をチャネル156および158中へ完全に入れるために、綿棒を使用して材料が過剰充填されてもよい。

20

#### 【0045】

図10Aおよび図10Bを参照すると、過剰な変形可能導電性材料160は、矢印164で示すように、ツール162で掻き取ることによって、剥離層154の表面から除去されてもよい。これにより、過剰な材料がツール162の前にマウンド166を形成し、これがチャネル156および158の充填不足領域を充填するのを助ける。過剰な材料は、廃棄されるか、または他のアセンブリと共に使用するためにリサイクルされてもよい。ツール162に使用され得るアイテムの例としては、直定規(straight-edge ruler)、スクイージー、へら、掻き取り刃(scaper blade)等が挙げられる。他の実施形態では、圧延、ブラッシング、エッティング等の代替技術を使用して、過剰な変形可能材料を除去することができる。実施形態の一例では、変形可能な導電性材料を予め装填したローラを使用して、単一のステップにおいて、材料を塗布することと、ローラの下から過剰な材料を押し込むことによって過剰な材料を除去することの両方を行うことができる。

30

#### 【0046】

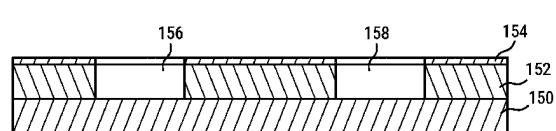

図11Aおよび図11Bを参照すると、変形可能な導電性材料は、全てまたは大部分の過剰材料が除去された状態で、剥離層154の上面167と略同一平面上に示されている。過剰材料を除去するために使用される技術によっては、依然として、剥離層154の上面に残る変形可能な導電性材料の薄いパッチが存在し得る。したがって、剥離層は、例えば、図12Aおよび図12Bに示されるように、第1の絶縁材料層152上にクリーンな上面168を残すように剥離して、除去されてもよい。

40

#### 【0047】

チャネル156および158内の変形可能な導電性材料160は、図12Aおよび図12Bにおいて、第1の絶縁材料層152の上面168と略同一平面上に示されている。これは、残っている変形可能な導電性材料が効果的に同一平面となるのに十分に薄い(例えば、数ミクロンもしくは数十ミクロン、または数千分の1インチの厚さである)剥離層を使用することによって達成され得る。いくつかの実施形態では、剥離層154の厚さは、図7Aおよび図7B～図11Aおよび図11Bにおいて誇張されてもよい。いくつかの実施形態では、少量の突出だけを回避する必要がある場合、剥離層154を除去する前に、掻き取り、ブラッシング等によって、少量の変形可能な導電性材料160をチャネル156および158から除去し、それによって、変形可能な導電性材料160を第1の絶縁材

50

料層 152 の上面 168 と同一平面にしておくことができる。

【0048】

いくつかの実施形態では、変形可能な導電性材料 160 を表面からわずかに隆起させることが有益であり得る。いくつかの実施形態では、剥離層 154 の厚さは、変形可能な導電性材料 160 を第 1 の絶縁材料層 152 の上面 168 の上に所定量だけ突出させることができると意図的に設定されてもよい。

【0049】

図 12A および図 12B に示される構造体は、製造された時に、または追加の層のためのベースとしての有用性がある。例えば、製造された時、接点パッドのパターンとして使用され、図 1 ~ 図 6 に関して上述したように、第 1 の層 152 上に取り付けられ、またはそれによって支持され得る電気部品の端子と係合することができる。そのような用途では、変形可能な導電性材料 160 は、例えば、電気部品の端子とより良好に係合するため、第 1 の絶縁材料層 152 の上面 168 の上方に突出することが有益である。導電性チャネル 156 および 158 のパターンは、接点および / またはトレースとして機能するために、異なる数、サイズ、形状等の導電性通路を含むように修正されてもよい。

10

【0050】

製造された時、図 12A および図 12B に示される実施形態、または修正された通路パターンを備える実施形態は、回路素子自体として使用されてもよい。例えば、変形可能な導電性材料 160 で充填されたチャネル 156 および 158 は、ストリップライン等の伝送ラインとして、または回路コンデンサにおいて機能することができる。そのような実装において、層 152 の上部を覆うように封止材層を形成して、変形可能な導電性材料 160 を封入し、保護してもよい。

20

【0051】

上述のように、図 12A および図 12B に示されるような構造体、または修正された通路パターンを有する構造体は、追加の層のためのベースとして使用され得る。例えば、図 13A および図 13B を参照すると、第 2 の絶縁材料層（第 2 の層）170 は、第 1 の層 152 の上部に積層される。第 2 の層 170 は通路パターンを有することができ、その少なくとも 1 つは、第 1 の層 152 内の 1 つ以上の通路と連通する。図 13A および図 13B の例では、パターンは、第 1 の層 152 内のチャネル 156 および 158 によってそれぞれ形成されたトレースと整列するスルービア 172 および 174 を備える。第 2 の層 170 の他の部分は、第 1 の層 152 におけるチャネル 156 および 158 の部分内に変形可能な導電性材料を封入する役割を果たすことができる。第 2 の層 170 ならびにビア 172 および 174 は、剥離層の使用を含む第 1 の層 152 について開示された材料および技術のいずれかを使用して形成され、取り付けられてもよい。簡潔性の観点から、第 2 の層 170 が形成され、取り付けられる中間ステップは図示されておらず、第 2 の層は、その最終形態で図 13A および図 13B に示されている。

30

【0052】

図 13B で示されるように、第 2 の層 170 におけるビア 172 は、第 1 の層 152 におけるチャネル 156 の一部と整列し、連通する。したがって、ビア 172 が変形可能な導電性材料で充填されると、チャネル 156 と連続的な導電性構造を形成する。

40

【0053】

第 2 の層 170 におけるビア 172 および 174 は、多くの機能を果たすことができる。例えば、それらは、1 つ以上の電気部品のための接点として機能することができ、それらは、回路素子自体として、例えば、伝送ラインまたはセンサとして機能することができる。また、それらは、第 1 の層 152 におけるチャネル 156 および 158 によって形成されるトレースを、第 2 の層の上の別の層内のトレース等と電気的に接続することができる。図 13A および図 13B に示されるビア 172 および 174 のパターンは単なる一例であり、そのパターンは、導電性通路の任意の数、形状、配置等を含むように修正されてもよい。

【0054】

50

図14Aおよび図14Bを参照すると、第3の絶縁材料層（第3の層）176が、第2の絶縁材料層170上に積層される。第3の層176は、通路パターンを有することができ、その少なくとも1つは、第2の層170における1つ以上の通路と連通する。図14Aおよび図14Bの例では、パターンは、第2の層170におけるビア172および174とそれぞれ整列するチャネル178および180を備える。第3の層176およびチャネル178および180は、剥離層の使用を含む第1の層152および第2の層170について開示された材料および技術のいずれかを使用して形成され、取り付けられてもよい。簡潔性の観点から、第3の層176が形成され、取り付けられる中間ステップは図示されておらず、第3の層は、その最終形態で図14Aおよび図14Bに示されている。

#### 【0055】

第1の層152および第2の層170における通路パターンと同様に、第3の層176におけるチャネル178および180のパターンは、多くの機能を果たし得る。例えば、それらは、1つ以上の電気部品のための接点として機能することができ、それらは、回路素子自体として、例えば、伝送ラインまたはセンサとして機能することができる。また、それらは、第2の層170におけるビア172および174等に電気的に接続されるトレースとして機能することができる。図14Aおよび図14Bに示されるチャネル178および180のパターンは単なる一例であり、そのパターンは、導電性通路の任意の数、形状、配置等を含むように修正されてもよい。

#### 【0056】

図15Aおよび図15Bを参照すると、第4の絶縁材料層（第4の層）182が、第3の絶縁材料層176上に積層される。第4の層182は通路パターンを有することができ、その少なくとも1つは、第3の層176における1つ以上の通路と連通する。図15Aおよび図15Bの例では、パターンは、第3の層176におけるチャネル178および180とそれぞれ整列するパッド184および186を備える。第4の層182の他の部分は、第3の層176におけるチャネル178および180の部分内に変形可能な導電性材料を封入する役割を果たすことができる。第4の層182ならびにパッド184および186は、剥離層の使用を含む第1の層152、第2の層170および第3の層176について開示された材料および技術のいずれかを使用して形成され、取り付けられてもよい。簡潔性の観点から、第4の層182が形成され、取り付けられる中間ステップは図示されておらず、第4の層は、その最終形態で図15Aおよび図15Bに示されている。

#### 【0057】

他の層における通路パターンと同様に、第4の層182におけるパッド184および186のパターンは、多くの機能を果たすことができる。例えば、それらは、1つ以上の電気部品のための接点として機能することができ、それらは、回路素子自体として、例えば、伝送ラインまたはセンサとして機能することができる。また、それらは、第3の層182におけるチャネル178および180を、第4の層182より上の追加の層における通路に電気的に接続するビアとして機能することができる。さらに、それらは、硬い外部端子と変形可能な導電性材料との間の「ハードおよびソフト」接続部（“hard-to-soft” connections）を作るための接点として機能することもできる。図15Aおよび図15Bに示されるパッド184および186のパターンは単なる一例であり、そのパターンは、導電性通路の任意の数、形状、配置等を含むように修正されてもよい。

#### 【0058】

図15Bに示されるように、第1の層152におけるチャネル156、第2の層170におけるビア172、第3の層176におけるチャネル178および第4の層182におけるパッド184を介する1つの連続的な導電経路がある。図7Aおよび図7B～図15Aおよび図15Bに示される実施形態における層および通路は、例示のみを目的としたものであり、任意のタイプの回路構成を作り出すように修正することができる。例えば、ビアおよびパッドの層、ならびにトレースを有する層の順序を変更することができる。いくつかの層は、トレースならびにビアおよびパッドの両方を含むことができる。

#### 【0059】

10

20

30

40

50

いくつかの例示的実施形態では、絶縁層のうちの1つ以上が、Lubrizol Es tane 58000シリーズ、例えば58238等のTPU、または伸縮性エポキシ系材料で形成され得る。伸縮性エポキシ系材料はまた、電気部品を層に結合するため、および層を互いに結合するための自己接着性表面 (self-adhesive surface) を提供し得る。接着性を有する材料の他の例には、ポリウレタン (PU) 接着剤 (例えば、Bemis またはFramis) 等の熱活性化接着剤 (thermally activated adhesives)、シリコン、アクリルまたは他の異なる化学的性質を有する熱硬化性接着剤、および任意の化学的性質の感圧接着剤等が含まれる。

#### 【0060】

そのような材料は、患者の身体に対してまたは近接して着用される医療用電子機器、衣服等に使用するのに十分な可撓性および/または伸縮性を有する回路アセンブリの実施形態をもたらし得る。いくつかの実施形態では、1つ以上の剥離層が絶縁材料層の表面上の所定箇所に残されてもよい。他の実施形態では、剥離層は完全に省略されてもよい。図7Aおよび図7B～図15Aおよび図15Bの実施形態に示される通路は、一般に、絶縁材料層を完全に貫通して延在するように示される。ただし、他の実施形態では、通路の一部または全部は、1つ以上の絶縁材料層を介し、その途中までのみに延在してもよい。

10

#### 【0061】

いくつかの実施形態では、電気部品は、積層体へ (例えば層の間に) 一体化されてもよい。例えば、積層体の1つ以上の内部層は、集積回路パッケージ等のデバイスの高さに適合するように切欠部 (cutout section) を有してもよい。他の実施形態では、抵抗器および/またはコンデンサならびにより小さなICパッケージおよびペアICダイ等のコンポーネントは、層が比較的軟らかくおよび/または柔軟である場合は特に、層の間に配置するため十分小さくてもよい。

20

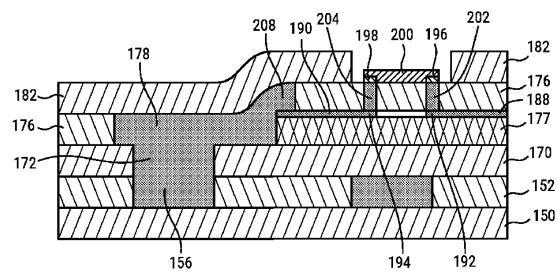

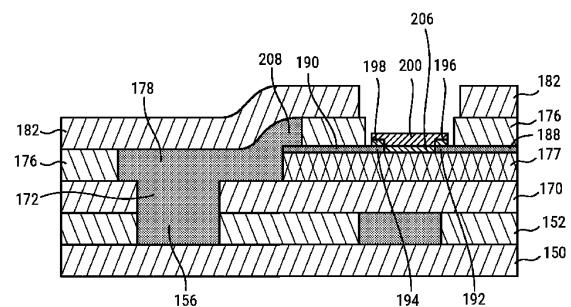

#### 【0062】

図16は、本特許開示のいくつかの発明原理による回路アセンブリの別の実施形態を示す断面図である。例示の目的で、図16の実施形態は、図15Bの層と同様の層を有するように示されているが、本発明原理はこれらの詳細に限定されない。図16の実施形態は、層、副層、または層の一部 (総称して「副層」という) 177を備え、その中または上に、導電性要素のパターンが形成されている。この例では、副層177が積層体の右側部分上の第2の層170と第3の層176との間に挿入される。第3の層176および第4の層182は、副層177に対応するための段差部を伴って形成される。他の実施形態では、副層は、層の一部、層全体を置き換えるてもよく、または別の層全体として追加されてもよい。副層177は、その他の層のいずれかより薄くても、厚くても、同じ厚さであってもよい。

30

#### 【0063】

層177上の導電性要素の一部または全部は、上記で開示された変形可能な導電性材料のいずれかから形成され得る。また、導電性要素のパターンは、変形可能な導電性要素と非変形可能な導電性要素との混合物を含んでもよい。副層177は、上記に開示した絶縁材料のいずれかから製造され、上記のように他の層に取り付けられる。素子のパターンは、トレース、ピア、パッド、伝送ラインおよびセンサを含む回路素子等を含んでもよい。要素のパターンは、上述の技術のいずれかによって副層177上に形成されてもよい。いくつかの実施形態では、リール・ツー・リール (R2R) プロセス等の印刷プロセスによって要素の一部または全部を形成することが有益である。これは、より微細な導電性要素の生成を可能にし、より小さな電気部品または相互接続部に対応し得、または一般的に異なる特性を有するコンポーネントまたは相互接続部に対応し得る。

40

#### 【0064】

図16の実施形態では、副層177は、電気部品200上の端子196および198とそれぞれ整列するパッド192および194に接続された2つのトレース188および190を備えるパターンを有する。第3の層176を介するピア202および204は、パッド192および194をそれぞれ端子196および198に接続する。この例における

50

電気部品 200 は、端子 196 および 198 がボンディングパッドまたは接点パッドとして形成されたペア集積回路ダイとして示されているが、任意の他のタイプの電気部品を使用することができる。この例では、ICダイ 200 は、第 3 の層 176 に接着剤で取り付けられるが、任意の他の方法で取り付けられてもよい。

#### 【0065】

副層 177 上に形成される導電性要素のパターンは、任意の他のトレース、ビア、パッド、コンポーネント等と相互接続されてもよい。図 16 の例では、副層 177 上のトレース 190 は、副層 177 の厚さに対応する層 176 の段差部に形成されたハイブリッドトレース / ビア 208 を介して、層 176 におけるトレース 178 に電気的に接続される。他の実施形態では副層 177 上の層 176 の部分は省略されてもよく、第 4 の層 182 は、層 176 の残りの部分および副層 177 によって形成される平面上に形成されてもよい。

10

#### 【0066】

図 17 は、本特許開示のいくつかの発明原理による回路アセンブリの別の実施形態を示す断面図である。図 17 の実施形態は図 16 の実施形態と同様であるが、ICダイ 200 の下にある第 3 の層 176 の全部分が省略され、ビア 202 および 204 も同様に省略されている。ICダイは、接着剤層 206 によって副層 177 の上面に取り付けられ、ボンディングまたは接点パッド 196 および 198 は、変形可能な導電性材料から形成されたパッド 192 および 194 にそれぞれ直接接触する。

#### 【0067】

図 18 は、本特許開示のいくつかの発明原理によるビア構造の平面図である。図 19 は、図 18 の A - A 線に沿った断面図である。図 18 および図 19 の実施形態は、上述の材料および製造技術のいずれかを利用することができ、基板 210 と、基板 210 上に積層された第 1 の絶縁材料層 212 および第 2 の絶縁材料層 216 とを備える。第 1 の層 212 はトレース 214 を備える。第 2 の層は、トレース 214 上に形成され、トレース 214 と連通するビア 218 を備える。図 18 に示されるように、ビア 218 は、(Y 軸と比較して) X 軸に延在する長さを有する。X 軸に沿って、図 18 のアセンブリは、歪み (strain)、剪断力、および / または伸張変形を受ける。X 軸に沿ってビアの長さを延ばすことは、アセンブリが X 軸に沿って伸ばされる時に互いにすれ違う傾向にあるビア 218 とトレース 214 との間のより強固な接続を提供することができる。

20

#### 【0068】

導電性要素を予想される延伸方向に延伸する技術は、図 18 および図 19 のビアの文脈に示されているが、他の任意の通路、相互接続部または構造体にも適用することができる。いくつかの実施形態では、ビア、トレース、および他の特徴の相対的なサイズおよび形状の他の様様は、延伸に対応するように調整されてもよい。例えば、いくつかの実施形態では、ビアがトレース幅の約半分の直径を有してもよい。

30

#### 【0069】

本特許開示の発明原理に従って構築された実施形態は、より安価なパッケージングされていない電子部品の使用を可能にし、また、はんだ付けステップを排除することができる。アセンブリのコストを低減し得る高機能回路アセンブリをもたらし得る。また、本特許開示の発明原理に従って構築された実施形態は、はんだの排除によってはんだ付けに関連する加熱を減少させることができ、また、熱放散に対する障壁となり得るデバイスパッケージングを排除することによって改善された冷却を提供するため、向上した信頼性を提供することができる。

40

#### 【0070】

本特許開示の発明原理は、本発明の概念から逸脱することなく、配置および詳細を変更することができるので、そのような変更および修正は以下の特許請求の範囲内にあると考えられる。第 1 および第 2 のような用語の使用は、異なるコンポーネントを区別するためのものであり、必ずしも 2 以上のコンポーネントの存在を意味するものではない。

50

【図面】

【図 1】

FIG. 1

【図 2】

FIG. 2

【図 3 A】

FIG. 3A

【図 3 B】

FIG. 3B

【図 3 C】

FIG. 3C

【図 3 D】

FIG. 3D

10

20

30

40

50

【図 3 E】

FIG. 3E

【図 4】

FIG. 4

10

【図 5 A】

FIG. 5A

【図 5 B】

FIG. 5B

20

【図 5 C】

FIG. 5C

【図 6】

FIG. 6

30

40

50

【図 7 A】

【図 7 B】

FIG. 7B

10

FIG. 7A

【図 8 A】

【図 8 B】

FIG. 8B

20

FIG. 8A

30

40

50

【図 9 A】

【図 9 B】

FIG. 9B

10

FIG. 9A

【図 10 A】

【図 10 B】

FIG. 10B

20

FIG. 10A

30

40

50

【図 1 1 A】

【図 1 1 B】

**FIG. 11B**

10

**FIG. 11A**

【図 1 2 A】

【図 1 2 B】

**FIG. 12B**

20

**FIG. 12A**

30

40

50

【図 13 A】

【図 13 B】

**FIG. 13B**

10

**FIG. 13A**

【図 14 A】

【図 14 B】

**FIG. 14B**

20

**FIG. 14A**

30

40

50

【図 15 A】

FIG. 15A

【図 15 B】

FIG. 15B

10

【図 16】

FIG. 16

【図 17】

FIG. 17

20

【図 18】

FIG. 18

【図 19】

FIG. 19

30

40

50

## フロントページの続き

## (51)国際特許分類

| F I     |       |

|---------|-------|

| H 0 5 K | 1/18  |

| H 0 1 L | 23/12 |

| H 0 1 L | 23/12 |

ニオ

アメリカ合衆国 97008 オレゴン州, ビーバートン, 8240 エス ダブリュー ニンバス

アベニュー

## (72)発明者 ホプキンス, マイケル アドベンチャー

アメリカ合衆国 97008 オレゴン州, ビーバートン, 8240 エス ダブリュー ニンバス

アベニュー

## (72)発明者 ゴッドシャルク, エドワード

アメリカ合衆国 97008 オレゴン州, ビーバートン, 8240 エス ダブリュー ニンバス

アベニュー

## (72)発明者 キンツェル, チャールズ

アメリカ合衆国 97008 オレゴン州, ビーバートン, 8240 エス ダブリュー ニンバス

アベニュー

審査官 小林 大介

## (56)参考文献 特開2000-183092 (JP, A)

特開2016-143763 (JP, A)

国際公開第2015/151433 (WO, A1)

特開2000-286555 (JP, A)

## (58)調査した分野 (Int.Cl., DB名)

H 0 5 K 3 / 4 6

H 0 5 K 1 / 0 9

H 0 5 K 3 / 3 2

H 0 5 K 1 / 1 8

H 0 1 L 2 3 / 1 2