(19) 日本国特許庁(JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-287866

(P2010-287866A)

(43) 公開日 平成22年12月24日(2010.12.24)

| (51) Int.Cl.  |               | F I              |        | テーマコード (参考)   |

|---------------|---------------|------------------|--------|---------------|

| <b>HO 1 L</b> | <b>21/822</b> | <b>(2006.01)</b> | HO 1 L | 27/04 H 5FO38 |

| <b>HO 1 L</b> | <b>27/04</b>  | <b>(2006.01)</b> | HO 1 L | 23/36 D 5F136 |

| <b>HO 1 L</b> | <b>23/36</b>  | <b>(2006.01)</b> | HO 1 L | 27/04 E       |

| <b>HO 1 L</b> | <b>23/12</b>  | <b>(2006.01)</b> | HO 1 L | 23/12 E       |

|               |               |                  | HO 1 L | 23/12 5O1F    |

審査請求 未請求 請求項の数 6 O.L. (全 12 頁)

|            |                                                                                                      |          |                               |

|------------|------------------------------------------------------------------------------------------------------|----------|-------------------------------|

| (21) 出願番号  | 特願2009-142806 (P2009-142806)                                                                         | (71) 出願人 | 302062931<br>ルネサスエレクトロニクス株式会社 |

| (22) 出願日   | 平成21年6月15日 (2009. 6. 15)                                                                             | (74) 代理人 | 100102864<br>弁理士 工藤 実         |

| (72) 発明者   | 小林 伸行<br>神奈川県川崎市中原区下沼部 1753番地<br>NECエレクトロニクス株式会社内                                                    |          |                               |

| F ターム (参考) | 5F038 BE07 BE09 BH16 BH19 CA02<br>CA03 CA08 CA10 CD02 CD04<br>CD12 EZ06 EZ20<br>5F136 BA30 BC01 DA13 |          |                               |

(54) 【発明の名称】 半導体装置

(57) 【要約】 (修正有)

【課題】アドレスドライバICとシステムGNDとの間の配線インピーダンスを低減して、アドレスドライバICにおける更なるGND電位の安定化を図ることが可能な半導体装置を提供する。

【解決手段】所定の電位に保持された放熱板250と、放熱板25に実装されるSOI(Silicon On Insulator)チップ200と、放熱板250とSOIチップ200との接触面に塗布される放熱グリス260とを備え、SOIチップ200は、回路素子領域を形成する第1シリコン(以下、Si)基板203と、放熱板250と面する第2Si基板201と、第1Si基板203と第2Si基板201との間に形成された絶縁膜202とを具備し、第1Si基板203と第2Si基板201とは電気的に接続されており、放熱グリス260は、導電性であり、第2Si基板201と放熱板250とを電気的に接続する。

【選択図】 図 6

**【特許請求の範囲】****【請求項 1】**

所定の電位に保持された放熱板と、

前記放熱板に実装される S O I ( Silicon On Insulator ) チップ

と、

前記放熱板と前記 S O I チップとの接触面に塗布される放熱グリスと

を備え、

前記 S O I チップは、

回路素子領域を形成する第 1 シリコン ( 以下、 Si ) 基板と、

前記放熱板と面する第 2 Si 基板と、

前記第 1 Si 基板と前記第 2 Si 基板との間に形成された絶縁膜と

を具備し、

前記第 1 Si 基板と前記第 2 Si 基板とは電気的に接続されており、

前記放熱グリスは、導電性であり、前記第 2 Si 基板と前記放熱板とを電気的に接続す

る

半導体装置。

**【請求項 2】**

請求項 1 に記載の半導体装置であって、

前記 S O I チップは、前記第 1 Si 基板から絶縁膜を貫通して前記第 2 Si 基板へ達す

るコンタクト孔を備え、

前記コンタクト孔は、前記回路素子領域に形成された接地電極と前記第 2 Si 基板とを

電気的に接続する

半導体装置。

**【請求項 3】**

請求項 1 または請求項 2 に記載の半導体装置であって、

前記 S O I チップは、 T C P ( Tape Carrier Package ) 、あるいは C O F ( Chip On Film ) により実装される

半導体装置。

**【請求項 4】**

請求項 3 に記載の半導体装置であって、

前記コンタクト孔は、さらに前記 T C P 、あるいは前記 C O F において、前記所定の電

位を供給するインナーリードと接続される

半導体装置。

**【請求項 5】**

請求項 1 から請求項 4 までのいずれかに記載の半導体装置であって、

前記所定の電位は、前記回路素子領域における G N D 電位である

半導体装置。

**【請求項 6】**

請求項 2 から請求項 5 いずれかに記載の半導体装置であって、

前記回路素子領域は、 P D P ( Plasma Display Panel ) アドレス

ドライバ回路を形成し、

前記 P D P アドレスドライバ回路は、高圧出力部と低圧路ロジック部とを備え、

前記コンタクト孔は、前記第 2 Si 基板と、前記高圧出力部の前記接地電極とを電気的

に接続する

半導体装置。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、 P D P ( Plasma Display Panel ) アドレスドライバ I

C を実装する半導体装置に関する。

10

20

30

40

50

## 【背景技術】

## 【0002】

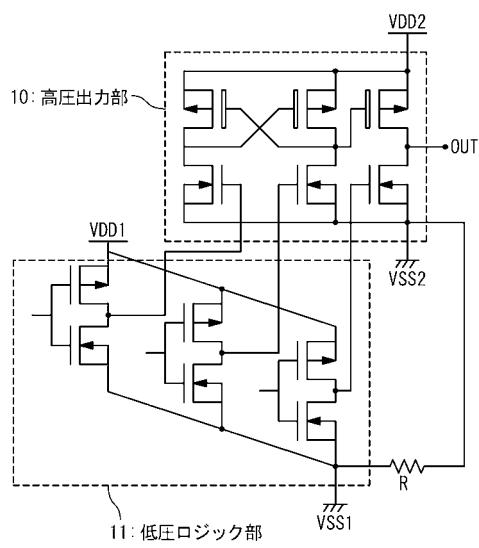

PDP (Plasma Display Panel) ドライバIC (Integrated Circuit) は、走査線を駆動するスキャンドライバICと、データ線を駆動するアドレスドライバICとが存在する。アドレスドライバICは、低圧ロジック部と高圧出力部とを備える。図1は、アドレスドライバICの出力セルの構成例を示す図である。アドレスドライバICは、一般に、高圧出力部10と低圧ロジック部11とが1つの出力セルとして1チップに集約されて搭載されている。

## 【0003】

低圧ロジック部11は、CMOS回路で構成される。低圧ロジック部11は、電源電位VDD1とGND電位VSS1と接続されている。低圧ロジック部は、前段の回路から画像データを入力して、駆動信号を生成して高圧出力部10へ出力する。高圧出力部10は、高耐圧NチャネルMOSFET (Metal Oxide Semiconductor Field Effect Transistor) (以下、HVNch) と高耐圧PチャネルMOSFET (以下、HVPch) で構成される。高圧出力部10は、電源電位VDD2とGND電位VSS2と接続されている。高圧出力部10は、低圧ロジック部11からの駆動信号に基づいて、PDPの駆動電圧を出力する。

10

## 【0004】

高圧出力部10と低圧ロジック部11とでは、使用する電源電位が異なる。低圧ロジック部11のVDD1は、3.3V～5.0Vと、一般に、数V程度である。一方、高圧出力部10のVDD2は、数十V～数百Vである。低圧ロジック部11のVSS1と高圧出力部10のVSS2とは、チップ内部において、抵抗Rを介して接続されている。

20

## 【0005】

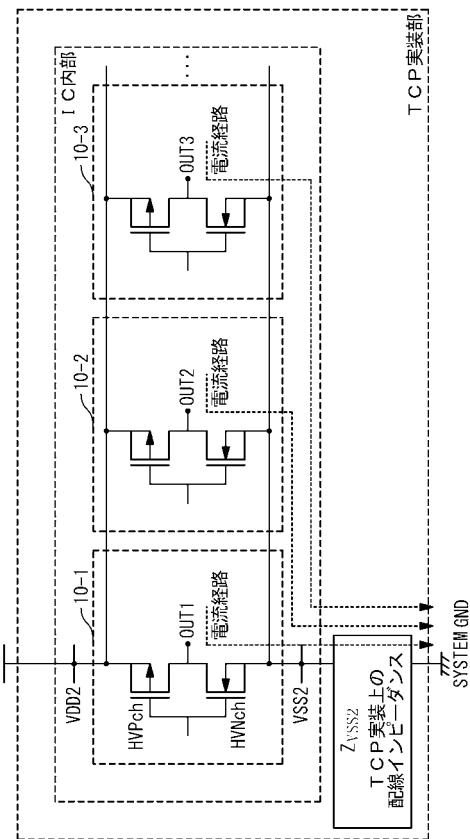

図2は、TCP (Tape Carrier Package) 実装されたアドレスドライバICの構成例を示す図である。アドレスドライバICは、1チップ上に複数の出力セルを備える。なお、図2は、複数の出力セルのうち高圧出力部10-1～3のみを記載している。実際には、アドレスドライバIC200は、これよりさらに多くの数の、例えば、192個の出力セルを、1チップ上に備える。各高圧出力部10-1～3は、VDD2端子を介してシステム電源と接続されてVDD2を入力しており、また、同様にVSS2端子を介してシステムGNDと接続されている。

30

## 【0006】

このように、アドレスドライバICの電源線には、多数の高圧出力部10が接続されているため、複数の高圧出力部10で同時にスイッチング動作が行われると、VSS2端子からシステムGND間に大きな電流が流れる。このとき、VSS2端子とシステムGNDとの間の配線上における、特性インピーダンスの不整合等に起因して、VSS2電位の持ち上がりやリンクギングが発生し、VSS2の電位に揺れが発生する。このような、VSS2電位の揺れは、高圧出力部10の論理誤動作を招く。また、VSS2電位の揺れは、VSS2と抵抗を介して接続されているVSS1電位にも影響を与え、低圧ロジック部11の誤動作を招く。

40

## 【0007】

このような課題は、PDPパネルの低電流化や、配線上のインピーダンス(以下、配線インピーダンス)の低減により、解決することができるが、PDPパネルの駆動電流は、PDPパネルの特性に起因するため変更が難しい。そのため、配線インピーダンスを低減する技術が検討されており、以下のような関連技術が開示されている。

## 【0008】

特許文献1は、フラットパネルディスプレイにおいて、駆動用ドライバICとして用いられる半導体装置を単層配線基板で実現でき、多ピン出力化に伴うフリップチップ内部の電源配線の長配線による高インピーダンス化や、フリップチップ内部の長辺方向における両端での電圧降下を抑制しながら、なおかつ大画面化に伴う駆動負荷の増大に対しても、放熱性と電源電位、システムGNDを強化することができる半導体装置を開示している。

50

## 【0009】

特許文献1の半導体装置は、素子電極が設けられた半導体素子と、素子電極に電気的に接続される基板電極が設けられた単層配線基板とを備え、半導体素子が単層配線基板に実装された半導体装置であって、コネクタ部と、1枚または複数枚の放熱板と、中継電極部と、1個または複数個の接続用部材とを備える。コネクタ部は、単層配線基板の端部に設けられ、半導体素子を駆動するための第1の電位および第2の電位を含む外部信号を受信する。放熱板は、第1の電位及び、または第2の電位の伝送に使用される導電性および熱伝導性を有する。中継電極部は、単層配線基板に1箇所または複数個所設けられる。接続用部材は、導電性を有し、放熱板と中継電極部との間に配置されて、放熱板と中継電極部とを電気的に接続する。単層配線基板は、コネクタ部により受信した第1の電位及び、または第2の電位が、放熱板、中継電極部、および接続用部材からなる経路を経由し、基板電極を介して半導体素子の素子電極へ伝送される構造を有する。

10

## 【0010】

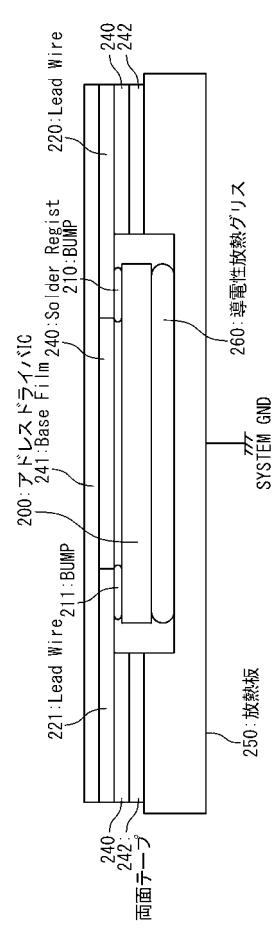

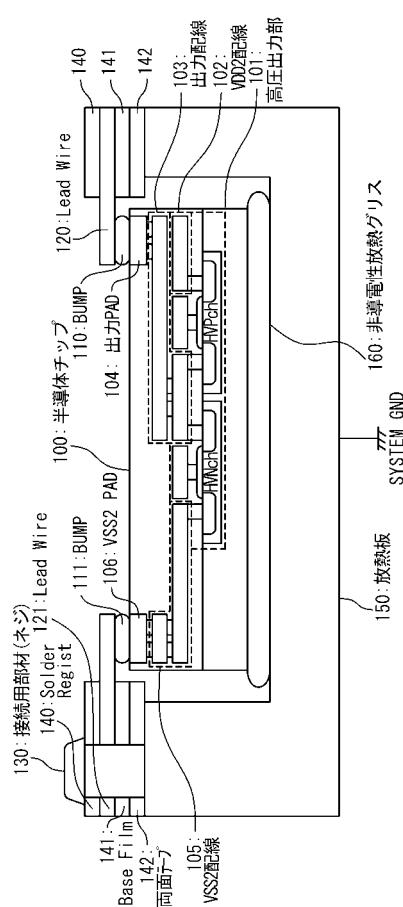

図3を用いて特許文献1の半導体装置を説明する。図3は、特許文献1の半導体装置の構成を示す断面図である。図3では、半導体チップ100がTCP実装された場合を例として説明する。図3を参照すると、放熱板150には、半導体チップ100を積載するための窪みが設けられている。半導体チップ100は、放熱板150上の窪みに設置される。放熱板150と半導体チップ100の接触面には絶縁層である非導電性の放熱グリス(以下、非導電性放熱グリス)160が塗布されており、半導体チップ100と放熱板150とを電気的に絶縁している。半導体チップ100は、高圧出力部101と低圧ロジック部とを備える。なお、図3では、低圧ロジック部の図示を省略している。高圧出力部101は、VDD2配線102とビアを介して接続されて、電源電位VDD2を入力する。また、高圧出力部101は、出力配線103と、出力パッド(出力PAD)104と、バンプ(BUMP)110とを介して、TCPのインナーリード(Lead Wire)120と電気的に接続されている。高圧出力部101は、インナーリード120を介して出力信号を出力する。

20

## 【0011】

また、高圧出力部101を構成する各トランジスタの端子は、VSS2配線105とビアを介して接続される。VSS2配線105は、VSS2パッド(VSS2PAD)106とビアを介して接続される。半導体チップ100の表面のVSS2パッド106上にはバンプ111が設けられている。バンプ111は、TCPのインナーリード121と接続される。インナーリード121は、放熱板150と両面テープ142により固定されたベースフィルム(Base Film)141上に構成されている。インナーリード121の表面は、ソルダレジスト(Solder Register)140によって覆われている。接続用部材(ネジ)130は、ソルダレジスト140と、インナーリード121と、ベースフィルム141と、両面テープ142とを貫通して、放熱板150と接続される。接続用部材130は、インナーリード121と放熱板150とを電気的に接続する。放熱板150は、システムGND(SYSTEM GND)と接続されており、所定の電位に保たれている。これによって、高圧出力部101は、VSS2配線105、VSS2パッド106、バンプ111、インナーリード121、接続用部材130、放熱板150を介する経路で所定の電位を供給される。

30

## 【0012】

特許文献1の半導体装置によれば、接続用部材130を介して、放熱板150とVSS2パッド106とを電気的に接続することで、半導体チップ100内の長配線化による高インピーダンス化を抑えることができる。これによって、駆動用ドライバICの、システムGNDを強化することができる。

40

## 【先行技術文献】

## 【特許文献】

## 【0013】

## 【特許文献1】特開2008-203376号公報

50

【特許文献 2】特開 2002-110950 号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

しかしながら、特許文献 1 の半導体装置は、半導体チップ 100 の VSS2 パッド 106 からシステム GND までの経路において、バンプ 106 、インナーリード 121 、接続用部材 130 、放熱板 150 を経由する必要がある。配線インピーダンスの抵抗成分は、配線長が長くなるほどに高くなるため、特許文献 1 の半導体装置では、PDP パネルの大型化等により駆動負荷がさらに増大すると、GND 電位を十分に安定させることができない。そのため、アドレスドライバ IC は、アドレスドライバ IC とシステム GND との間の配線インピーダンスを低減して、更なる GND 電位の安定化を図ることが求められる。

10

【課題を解決するための手段】

【0015】

以下に、(発明を実施するための形態)で使用される番号を用いて、課題を解決するための手段を説明する。これらの番号は、(特許請求の範囲)の記載と(発明を実施するための形態)との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、(特許請求の範囲)に記載されている発明の技術的範囲の解釈に用いてはならない。

【0016】

本発明の半導体装置は、所定の電位に保持された放熱板 (250) と、放熱板 (25) に実装される SOI (Silicon On Insulator) チップ (200) と、放熱板 (250) と SOI チップ (200) との接触面に塗布される放熱グリス (260) とを備え、SOI チップ (200) は、回路素子領域を形成する第 1 シリコン (以下、Si) 基板 (203) と、放熱板 (250) と面する第 2 Si 基板 (201) と、第 1 Si 基板 (203) と第 2 Si 基板 (201) との間に形成された絶縁膜 (202) とを具備し、第 1 Si 基板 (203) と第 2 Si 基板 (201) とは電気的に接続されており、放熱グリス (260) は、導電性であり、第 2 Si 基板 (201) と放熱板 (250) とを電気的に接続する半導体装置。

20

【発明の効果】

【0017】

本発明によれば、システム GND とアドレスドライバ IC 間の配線長を削減して、配線インピーダンスを低下させることができる。そのため、高圧出力部の動作に起因する VSS2 電位の揺れを抑えることができ、アドレスドライバ IC の GND 電位をより安定させることが可能である。

30

【図面の簡単な説明】

【0018】

【図 1】アドレスドライバ IC の出力セルの構成例を示す図である。

【図 2】TCP (Tape Carrier Package) 実装されたアドレスドライバ IC の構成例を示す図である。

40

【図 3】特許文献 1 の半導体装置の構成を示す断面図である。

【図 4】本発明における半導体装置の構成を示す平面図である。

【図 5】本発明における半導体装置の構成を示す断面図である。

【図 6】本発明における半導体装置の構成を示すより詳細な断面図である。

【図 7】本発明の半導体装置におけるインナーリードを介して VSS2 を供給する経路を省いた構成を示す断面図である。

【図 8】本発明の半導体装置におけるアドレスドライバ IC 200 を COF 実装した場合を示す断面図である。

【発明を実施するための形態】

【0019】

添付図面を参照して、本発明の実施形態による半導体装置を以下に説明する。

50

## 【0020】

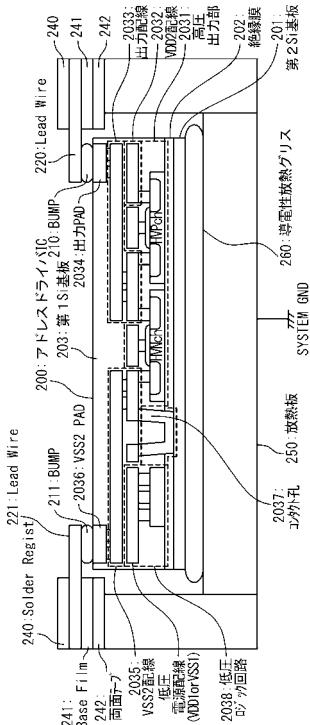

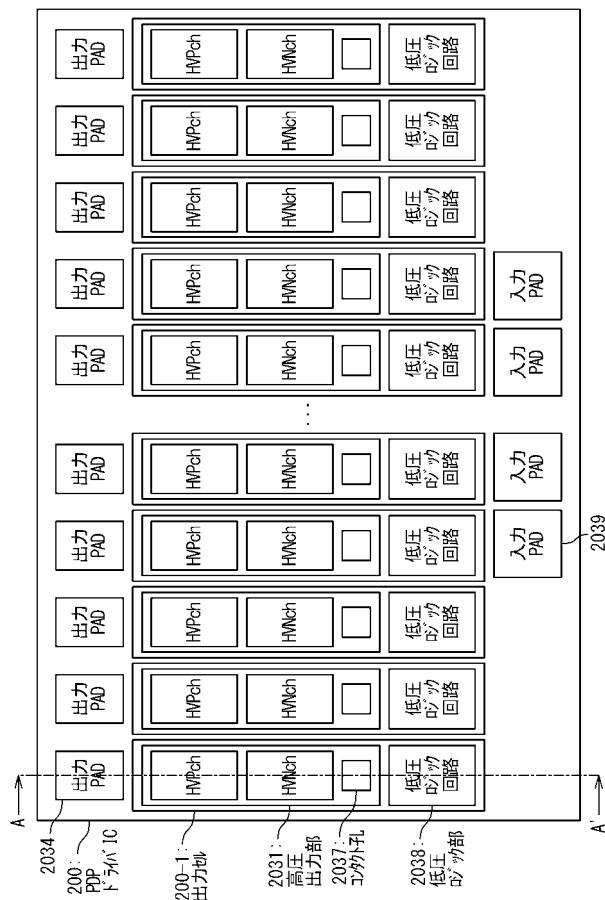

図4は、本実施形態における半導体装置の構成を示す平面図である。従来技術で説明を行ったように、アドレスドライバIC200は、複数の出力セル200-1を備える。各出力セル200-1は、高圧出力部2031と、低圧ロジック部2038とを備える。本実施形態の高圧出力部2031は、高耐圧PchMOSFET(Metal Oxide Semiconductor Field Effect Transistor)(以下、HVPch)と、高耐圧NchMOSFET(以下、HVNch)と、コンタクト孔2037とを備える。また、アドレスドライバIC200は、複数の出力セル200-1の各々に対応する出力PAD2034と、画像データの入力PAD2039とを備える。

10

## 【0021】

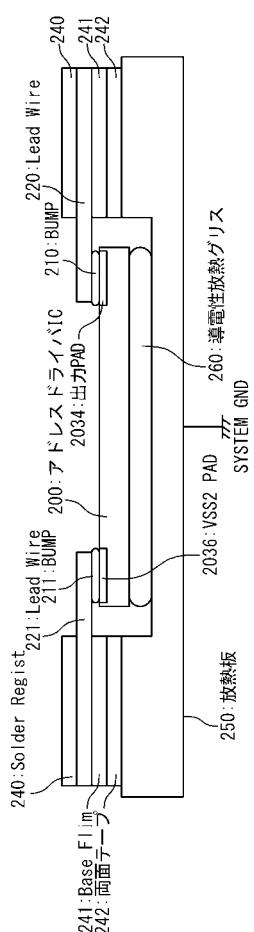

図5は、本実施形態における半導体装置の構成を示す断面図である。図5は、図4におけるA-A'に副った断面図である。図5において、アドレスドライバIC200は、TCP(Tape Carrier Package)実装されている。

## 【0022】

放熱板250には、アドレスドライバIC200を積載するための窪みが設けられている。アドレスドライバIC200は、放熱板250の窪みに積載される。放熱板250とアドレスドライバIC200との接触面には導電性の放熱グリス(以下、導電性放熱グリス)260が塗布されている。導電性放熱グリス260は、放熱板250とアドレスドライバIC200とが面する範囲に塗布される。

20

## 【0023】

導電性放熱グリス260は、例えば、導電性を有する金属粒子を均一に配合したシリコングリスである。なお、導電性放熱グリス260の成分は、これに限定しない。また、導電性放熱グリス260の電気特性は、特に限定はしない。本実施形態の半導体装置は、導電性放熱グリス260によって、アドレスドライバIC200と放熱板250とを電気的に接続する。導電性放熱グリス260は、従来の放熱特性を保ちつつ、アドレスドライバIC200と放熱板とを電気的に接続することができれば、その成分や電気特性は特に問わない。また、導電性放熱グリス260は、導電性を有すればグリスに限定せず、例えば時間が経過しても固化しないペースト状の導電体であっても構わない。固化するものとして、例えば、従来技術としてチップをパッケージに固定するために使用される銀ペーストはチップに機械的ストレスを与え、電気的な接続の信頼性が保てないため本発明の目的には適さない。

30

## 【0024】

アドレスドライバIC200は、出力パッド(出力PAD)2034と、VSS2パッド2036とを備える。出力パッド2034上には、バンプ(BUMP)210が形成される。バンプ210は、TCPのインナーリード(Lead Wire)220と接続される。また、VSS2パッド2036上には、バンプ211が形成される。バンプ211は、TCPのインナーリード221と接続される。

## 【0025】

インナーリード220、221は、放熱板250上へ両面テープ242により固定されたベースフィルム(Base Film)241上に構成されている。インナーリード220、221の表面は、ソルダレジスト(Solder Resist)240により覆われている。インナーリード220は、アドレスドライバICの出力でありPDPのデータ線と接続されている。また、インナーリード221は、GND電位VSS2と接続される。

40

## 【0026】

放熱板250は、システムGND(System GND)と接続されて所定の電位に保たれている。ここで、所定の電位とは、アドレスドライバIC200内で一定の基準電位として使用されるGND電位である。PDPパネルセットは、一般に、PDPパネルセットの金属シャーシをシステムGNDとして用いる。放熱板250は、金属シャーシと接

50

続することによって、GND電位を供給される。

【0027】

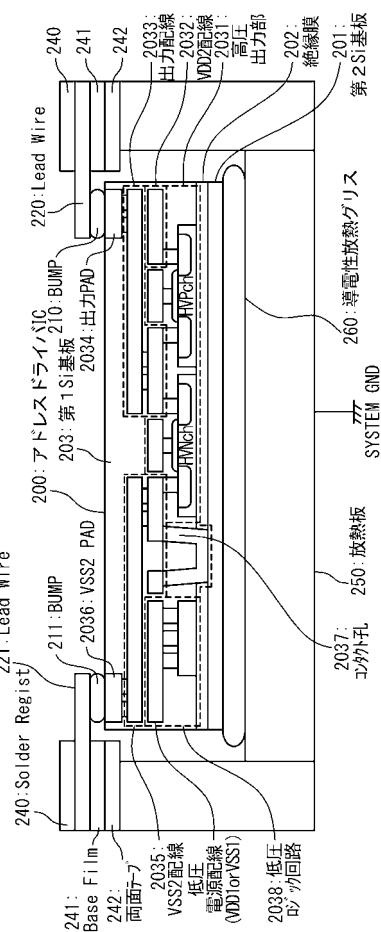

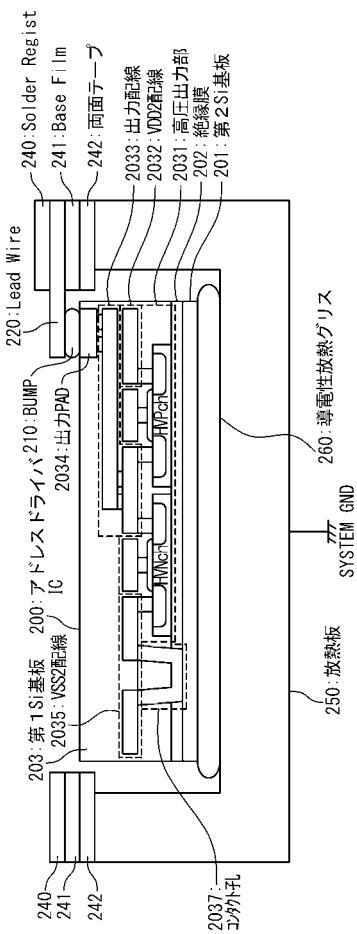

図6は、本実施形態における半導体装置の構成を示すより詳細な断面図である。図6は、図5において、アドレスドライバIC200の構成を詳細に示している。

【0028】

本実施形態におけるアドレスドライバIC200は、SOI(Silicon On Insulator)チップである。アドレスドライバIC200は、放熱板250と面した支持基板である第2シリコン(Si)基板201と、第2Si基板201上に形成された酸化シリコン膜(SiO<sub>2</sub>膜)である絶縁膜202と、絶縁膜202上に形成された第1Si基板203とが、この順番で積層されて形成される。本実施形態において、第2Si基板201側をドライバIC200の裏面側と呼び、第1Si基板203側をドライバIC200の表面側と呼ぶ。

10

【0029】

第1Si基板203には、回路素子が形成される。第1Si基板203には、低圧ロジック部2038、高圧出力部2031と、が形成されている。

【0030】

低圧ロジック部2038は、ビアを介して配線層と接続される。低圧ロジック2038は、配線層を介してVDD1やVSS1を入力し、配線層を介して高圧出力部2031と接続され、また、画像データを入力する入力パッド2039に接続される。低圧ロジック部2038の構成は、本発明に影響せず、その回路構成や配線の接続関係は従来の技術によりため、説明を省略する。

20

【0031】

高圧出力部2031には、HVPchとHVNchとが形成される。HVPchは、第1Si基板203に形成されたVDD2配線2032とビアを介して接続されて、VDD2配線2032を介してVDD2を入力する。また、HVPchとHVNchとは、ビアを介して第1Si基板203に形成された出力配線2033と接続される。出力配線2033は、ビアを介して出力パッド2034と接続されている。出力パッド2034上には、前述した通り、バンプ210が設けられており、バンプ210は、TCPのインナーリード220と接続されている。HVPchとHVNchとは、出力配線2033、出力パッド2034、バンプ210、インナーリード220と電気的に接続されており、インナーリード220を介してデータ線へ出力信号を出力する。また、HVPchとHVNchは、図示されない第1Si基板203に形成された配線層を介して低圧ロジック部2038と接続される。このような高圧出力部2031の構成は、従来の技術により構成されるため、これ以上の説明を省略する。

30

【0032】

本実施形態において重要なのは、高圧出力部2031におけるGND電位VSS2との接続構成である。高圧出力部2031のHVNchは、第1Si基板203に形成されたVSS2配線2035とビアを介して接続される。VSS2配線2035は、ビアを介してGNDパッド2036と接続される。GNDパッド2036上には、前述の通り、バンプ211が形成されており、バンプ211は、TCPのインナーリード221と接続されている。インナーリード221は、GND電位VSS2と接続されている。そのため、高圧出力部2031のHVNchは、VSS2配線2035、VSS2パッド2036、バンプ211を介して、インナーリード221と電気的に接続されて、GND電位VSS2を入力する。

40

【0033】

さらに、本実施形態の高圧出力部2031は、コントクト孔2037を備える。コントクト孔2037は、第1Si基板203から絶縁膜202を貫通して第2Si基板201へ達する。コントクト孔2037は、金属膜配線により構成されており、VSS2配線2035と、第2Si基板201とを電気的に接続する。

【0034】

10

20

30

40

50

ここで、本実施形態の半導体装置は、特許文献2に開示される技術を適用してコンタクト孔2037を形成する。特許文献2は、基板コンタクト用領域を備えるSOIチップ半導体装置を開示している。以下、特許文献2の半導体装置を説明するが、本説明において各構成に付される符号は、特許文献2におけるものであること留意されたい。特許文献2の半導体装置は、回路素子を形成する第2Si基板に $10 \times 10 \mu\text{m}$ 四方の基板コンタクト用領域10を備える。基板コンタクト用領域10は、第2Si基板2からSiO<sub>2</sub>膜3を貫通して第1Si基板1に達するコンタクト孔13を設けている。このコンタクト孔13は、金属、例えばタンゲステン(W)15cで充填されている。さらに、基板コンタクト用領域10は、基板コンタクト用領域10の底面から第2Si基板2の主表面上に設けられた所定の外部接続用電極200Gまでを接続する、例えば、アルミニウム(A1)による金属膜配線16Gを備える。金属膜配線16Gは、コンタクト孔13と基板コンタクト用領域10の底面において電気的に接続されている。そのため、第1Si基板1と外部接続用電極200Gとは、コンタクト孔13、及び金属配線膜16Gにより電気的に接続される。

10

#### 【0035】

以上が、特許文献2の説明である。特許文献2における外部接続用電極200Gが、本実施形態におけるVSS2配線2035となる。本実施形態におけるコンタクト孔2037は、特許文献2における基板コンタクト用領域10およびコンタクト孔13を含む。本実施形態のコンタクト孔2037は、第2Si基板201とVSS2配線2035とを電気的に接続する。

20

#### 【0036】

前述のとおり、第2Si基板201は、導電性放熱グリス260を介して放熱板250と電気的に接続されている。また、放熱板250は、システムGNDと接続されている。そのため、放熱板250と第2Si基板201とは、導電性放熱グリス260により電気的に接続される。高圧出力部2031のHVNchは、VSS2配線2035、コンタクト孔2037、第2Si基板201、導電性放熱グリス260を介して、放熱板250と電気的に接続される。このような経路で、高圧出力部2031はシステムGNDからGND電位VSS2を供給されるため、高圧出力部2031がTCPのインナーリードを介してシステムGNDと接続する場合に比べて配線長を短くすることができる。その結果、高圧出力部2031からシステムGNDへ至るまでの配線インピーダンスを低減することができ、GND電位であるVSS2の安定化を図ることができる。なお、本実施形態では特許文献2の開示する技術により第2Si基板201と、VSS2配線2035とを電気的に接続している。しかし、特許文献2の開示された技術以外でも、第2Si基板201と、VSS2配線2035とを電気的に接続することができれば、適用可能である。

30

#### 【0037】

なお、本実施形態の半導体装置においてアドレスドライバIC200は、TCPのインナーリード221を介してVSS2を供給される経路と、導電性放熱グリス260を介してVSS2を供給される経路との、2つの経路を備える。TCPのインナーリード221を介してVSS2を供給される経路は、高圧出力部2031のHVNchが、VSS2配線2035と、VSS2パッド2036と、バンプ211と、リード線221とを介してVSS2と接続される経路である。一方、導電性放熱グリス260を介してVSS2を供給される経路は、高圧出力部2031のHVNchが、VSS2配線2035、コンタクト孔2037、第2Si基板201、導電性放熱グリス260、放熱板250を介してシステムGNDと接続される経路である。

40

#### 【0038】

これを、インナーリード221を介してVSS2を供給される経路を省いて、導電性放熱グリス260を介してVSS2を供給される経路のみを用いた構成としても良い。図7は、本実施形態の半導体装置におけるインナーリード221を介してVSS2を供給される経路を省いた構成を示す断面図である。図7の半導体装置においてアドレスドライバIC200は、高圧出力部2031のHVNchから、VSS2配線2035、コンタクト

50

孔 2 0 3 7、第 2 S i 基板 2 0 1、導電性放熱グリス 2 6 0、放熱板 2 5 0 を介してシステム G N D へ接続する経路のみを備える。このように構成することで、アドレスドライバ I C 2 0 0 を簡易な構成で実現することできる。

#### 【 0 0 3 9 】

また、本実施形態の半導体装置におけるアドレスドライバ I C 2 0 0 は、T C P 実装されている。これを、アドレスドライバ I C 2 0 0 が、C O F ( C h i p O n F i l m ) 実装される構成としてもよい。図 8 は、本実施形態の半導体装置におけるアドレスドライバ I C 2 0 0 を C O F 実装した場合を示す断面図である。このように構成することで、フリップチップへの対応が可能となる。なお、C O F 実装の場合においても、前述した、アドレスドライバ I C 2 0 0 は、導電性放熱グリスを介して G N D 電位を供給される経路のみを用いた構成とすることが可能である。

10

#### 【 0 0 4 0 】

ここまで、本実施形態の半導体装置を説明してきた。本実施形態の半導体装置によれば、S O I チップであるアドレスドライバ I C 2 0 0 と放熱板 2 5 0 との接触面に、導電性放熱グリス 2 6 0 が塗布されている。また、アドレスドライバ I C 2 0 0 は、回路素子を構成する第 1 S i 基板 2 0 3 から絶縁層 2 0 2 を貫通して放熱板 2 5 0 と面する第 2 S i 基板 2 0 1 に達するコンタクト孔 2 0 3 7 を備える。コンタクト孔 2 0 3 7 は、第 2 S i 基板 2 0 1 と、第 1 S i 基板 2 0 3 に形成されるV S S 2 配線 2 0 3 5 とを電気的に接続する。V S S 2 配線 2 0 3 5 は高圧出力部 2 0 3 1 のH V N c h と接続される。そのため、高圧出力部 2 0 3 1 のH V N c h は、V S S 2 配線 2 0 3 5 、コンタクト孔 2 0 3 7 、第 2 S i 基板 2 0 1 、導電性放熱グリス 2 6 0 、及び放熱板 2 5 0 を介してシステム G N D と電気的に接続される。高圧出力部 2 0 3 1 とシステム G N D とがこのような経路で電気的に接続されることで、T C P のインナーリード 2 2 1 を介してシステム G N D と接続される場合に比べて配線長を短くすることができる。そのため、配線インピーダンスを低減することができ、高圧出力部 2 0 3 1 におけるG N D 電位 V S S 2 の電位の揺れを抑えることができる。これにより、アドレスドライバ I C 2 0 0 へ、安定したG N D 電位を供給することが可能となる。

20

#### 【 0 0 4 1 】

以上、実施形態を参照して本願発明を説明したが、本願発明は、上記実施形態に限定されるものではない。本願発明の構成や詳細には、本願発明のスコープ内で当業者が理解し得る様々な変更をすることができる。

30

#### 【 符号の説明 】

#### 【 0 0 4 2 】

1 0 高圧出力部

1 0 - 1 ~ 3 高圧出力部

1 1 低圧ロジック部

1 0 0 半導体チップ

1 0 1 高圧出力部

1 0 2 V D D 2 配線

1 0 3 出力配線

1 0 4 出力パッド

1 0 5 V S S 2 配線

1 0 6 V S S 2 パッド

40

1 1 0 バンプ

1 1 1 バンプ

1 2 0 インナーリード

1 2 1 インナーリード

1 3 0 接続用部材(ネジ)

1 4 0 ソルダレジスト

50

1 4 1 ベースフィルム

|           |            |    |

|-----------|------------|----|

| 1 4 2     | 両面テープ      |    |

| 1 5 0     | 放熱板        |    |

| 1 6 0     | 非導電性放熱グリス  |    |

| 2 0 0     | アドレスドライバIC |    |

| 2 0 1     | 第2シリコン基板   |    |

| 2 0 2     | 絶縁膜        |    |

| 2 0 3     | 第1シリコン基板   |    |

| 2 0 0 - 1 | 出力セル       |    |

| 2 1 0     | バンプ        | 10 |

| 2 1 1     | バンプ        |    |

| 2 2 0     | インナーリード    |    |

| 2 2 1     | インナーリード    |    |

| 2 4 0     | ソルダレジスト    |    |

| 2 4 1     | ベースフィルム    |    |

| 2 4 2     | 両面テープ      |    |

| 2 5 0     | 放熱板        |    |

| 2 6 0     | 導電性放熱グリス   |    |

| 2 0 3 1   | 高圧出力部      |    |

| 2 0 3 2   | VDD2配線     |    |

| 2 0 3 3   | 出力配線       | 20 |

| 2 0 3 4   | 出力パッド      |    |

| 2 0 3 5   | VSS2配線     |    |

| 2 0 3 6   | VSS2パッド    |    |

| 2 0 3 7   | コントラクト孔    |    |

| 2 0 3 8   | 低圧ロジック部    |    |

| 2 0 3 9   | 入力パッド      |    |

【 図 1 】

【 図 2 】

【 図 3 】

〔 四 4 〕

【図5】

【図6】

【図7】

【図8】