(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6975541号

(P6975541)

(45) 発行日 令和3年12月1日(2021.12.1)

(24) 登録日 令和3年11月10日(2021.11.10)

(51) Int.Cl.

H01L 29/786 (2006.01)

F 1

H01L 29/78 618B

H01L 29/78 620

請求項の数 11 (全 106 頁)

(21) 出願番号 特願2017-44532 (P2017-44532)

(22) 出願日 平成29年3月9日 (2017.3.9)

(65) 公開番号 特開2017-168836 (P2017-168836A)

(43) 公開日 平成29年9月21日 (2017.9.21)

審査請求日 令和2年3月9日 (2020.3.9)

(31) 優先権主張番号 特願2016-48802 (P2016-48802)

(32) 優先日 平成28年3月11日 (2016.3.11)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 綿引 隆

(56) 参考文献 特開2016-028423 (JP, A)

)

米国特許出願公開第2015/0243

738 (US, A1)

特開2016-027619 (JP, A)

)

最終頁に続く

(54) 【発明の名称】複合体、およびトランジスタ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の領域と、前記第1の領域中に点在する複数の第2の領域と、が混在した複合酸化物半導体において、

前記第1の領域は、少なくともインジウムと元素M(元素Mは、Al、Ga、Y、またはSnのいずれか一つ、または複数)と亜鉛と、を含み、

前記第2の領域は、インジウムと亜鉛を含み、

前記第2の領域は、インジウムが、前記第1の領域よりも、高濃度に存在し、

前記複数の第2の領域の一つの第2の領域の端部と、前記複数の第2の領域の他の一つの第2の領域の端部は、連結した領域を有し、

前記第1の領域は、前記複数の第2の領域を、立体的に挟んでいる複合酸化物半導体。

## 【請求項 2】

第1の領域と、前記第1の領域中に点在する複数の第2の領域と、が混在した複合酸化物半導体において、

前記第1の領域は、少なくともインジウムと元素M(元素Mは、Al、Ga、Y、またはSnのいずれか一つ、または複数)と亜鉛と、を含み、

前記第2の領域は、インジウムと亜鉛を含み、

前記第2の領域は、インジウムが、前記第1の領域よりも、高濃度に存在し、

前記第1の領域は、前記複数の第2の領域を、立体的に挟んでいる複合酸化物半導体。

## 【請求項 3】

10

20

請求項 1 または請求項 2 において、

前記第 1 の領域におけるインジウム、元素 M、及び亜鉛の原子数比が、 $I_n : M : Z_n = 4 : 2 : 3 \sim 4 : 1$  の組成である複合酸化物半導体。

**【請求項 4】**

請求項 1 乃至請求項 3 のいずれか一において、

前記第 2 の領域におけるインジウム、元素 M、及び亜鉛の原子数比が、 $I_n : M : Z_n = 2 : 0 : 3$  の組成である複合酸化物半導体。

**【請求項 5】**

請求項 1 または請求項 2 において、

前記第 1 の領域におけるインジウム、元素 M、及び亜鉛の原子数比が、 $I_n : M : Z_n = 1 : 1 : 1$  の組成である複合酸化物半導体。 10

**【請求項 6】**

請求項 1、請求項 2、および請求項 5 のいずれか一において、

前記第 2 の領域におけるインジウム、元素 M、及び亜鉛の原子数比が、 $I_n : M : Z_n = 2 : 0 : 1$  の組成である複合酸化物半導体。

**【請求項 7】**

請求項 1 乃至請求項 6 のいずれか一において、

前記第 2 の領域の c 軸方向の厚みは、0.1 nm 以上 1 nm 未満である複合酸化物半導体。

**【請求項 8】**

20

請求項 1 乃至請求項 7 のいずれか一において、

前記第 1 の領域は非単結晶である複合酸化物半導体。

**【請求項 9】**

請求項 1 乃至請求項 8 のいずれか一において、

前記第 1 の領域は結晶部を含み、

前記結晶部の c 軸が、前記複合酸化物半導体膜の被形成面の法線ベクトルに平行である部分を有する複合酸化物半導体。

**【請求項 10】**

請求項 1 乃至請求項 9 のいずれか一において、

前記第 2 の領域は非単結晶である複合酸化物半導体。 30

**【請求項 11】**

請求項 1 乃至請求項 10 のいずれか一に記載の前記複合酸化物半導体を有するトランジスタ。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、物、方法、または、製造方法に関する。または、本発明は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関する。特に、本発明の一態様は、酸化物半導体、または当該酸化物半導体の製造方法に関する。または、本発明の一態様は、半導体装置、表示装置、液晶表示装置、発光装置、蓄電装置、記憶装置、それらの駆動方法、または、それらの製造方法に関する。 40

**【0002】**

なお、本明細書等において、半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。撮像装置、表示装置、液晶表示装置、発光装置、電気光学装置、発電装置（薄膜太陽電池、有機薄膜太陽電池等を含む）、及び電子機器は、半導体装置を有している場合がある。

**【背景技術】**

**【0003】**

非特許文献 1において、 $I_{n_1-x} Ga_{1+x} O_3 (ZnO)_m$  ( $x$  は -1  $\times$  1 を満

50

たす数、 $m$ は自然数)で表されるホモロガス相が存在することが述べられている。また、非特許文献1では、ホモロガス相の固溶域(solid solution range)について述べられている。例えば、 $m=1$ の場合のホモロガス相の固溶域は、 $x$ が-0.33から0.08の範囲であることが述べられており、 $m=2$ の場合のホモロガス相の固溶域は、 $x$ が-0.68から0.32の範囲であることが述べられている。

#### 【0004】

また、In-Ga-Zn系酸化物半導体を用いてトランジスタを作製する技術が開示されている(例えば、特許文献1参照)。

#### 【先行技術文献】

##### 【特許文献】

10

##### 【0005】

##### 【特許文献1】特開2007-96055号公報

##### 【非特許文献】

##### 【0006】

【非特許文献1】M. Nakamura, N. Kimizuka, and T. Mohri、「The Phase Relations in the In<sub>2</sub>O<sub>3</sub>-Ga<sub>2</sub>ZnO<sub>4</sub>-ZnO System at 1350」、J. Solid State Chem.、1991、Vol. 93, pp. 298-315

#### 【発明の概要】

##### 【発明が解決しようとする課題】

20

##### 【0007】

非特許文献1では、In<sub>x</sub>Zn<sub>y</sub>Ga<sub>z</sub>O<sub>w</sub>の例が示されており、 $x$ ,  $y$ 及び $z$ がZnGa<sub>2</sub>O<sub>4</sub>近傍の組成、つまり $x$ ,  $y$ 及び $z$ が( $x$ ,  $y$ ,  $z$ )=(0, 1, 2)に近い値を有する場合には、スピネル型の結晶構造が形成、あるいは混在しやすいことが記載されている。スピネル型の結晶構造を有する化合物として、AB<sub>2</sub>O<sub>4</sub>(A及びBは金属)で表される化合物が知られている。

##### 【0008】

しかしながら、スピネル型の結晶構造がIn-Ga-Zn系酸化物半導体中に形成、あるいは混在すると、当該In-Ga-Zn系酸化物半導体を有する半導体装置(例えばトランジスタ)の電気特性または信頼性に悪影響を与える場合がある。

30

##### 【0009】

上述の問題に鑑み、本発明の一態様は、新規な酸化物半導体を提供することを課題の一とする。または、本発明の一態様は、半導体装置に良好な電気特性を付与することを課題の一とする。または、信頼性の高い半導体装置を提供することを課題の一とする。または、新規な構成の半導体装置を提供することを課題の一とする。または、新規な構成の表示装置を提供することを課題の一とする。

##### 【0010】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

40

#### 【課題を解決するための手段】

##### 【0011】

本発明の一態様は、第1の領域と、複数の第2の領域と、が混合した複合酸化物半導体において、第1の領域は、少なくともインジウムと元素M(元素Mは、Al、Ga、Y、またはSnのいずれか一つ、または複数)と亜鉛と、を含み、第2の領域は、インジウムと亜鉛を含み、第2の領域は、インジウムが、第1の領域よりも、高濃度に存在し、第2の領域は、第1の領域よりも、高い導電性を有し、複数の第2の領域の一つの端部と、複数の第2の領域の他の一つの端部は、重なっており、第1の領域は、複数の第2の領域を、立体的にはさんでいる。

50

**【0012】**

上記構成の複合酸化物半導体は、インジウム、元素M、及び亜鉛の原子数比が、 $I_n : M : Z_n = 5 : 1 : 6$ の組成、またはその近傍値である。

**【0013】**

上記構成の第1の領域におけるインジウム、元素M、及び亜鉛の原子数比が、 $I_n : M : Z_n = 4 : 2 : 3$ の組成、またはその近傍値である。

**【0014】**

上記構成の第2の領域におけるインジウム、元素M、及び亜鉛の原子数比が、 $I_n : M : Z_n = 2 : 0 : 3$ の組成、またはその近傍値である。

**【0015】**

上記構成の複合酸化物半導体は、インジウム、元素M、及び亜鉛の原子数比が、 $I_n : M : Z_n = 4 : 2 : 3$ の組成、またはその近傍値である。 10

**【0016】**

上記構成の第1の領域におけるインジウム、元素M、及び亜鉛の原子数比が、 $I_n : M : Z_n = 1 : 1 : 1$ の組成、またはその近傍値である。

**【0017】**

上記構成の第2の領域におけるインジウム、元素M、及び亜鉛の原子数比が、 $I_n : M : Z_n = 2 : 0 : 1$ の組成、またはその近傍値である。

**【0018】**

上記構成の第2の領域のc軸方向の厚みは、0.1nm以上1nm未満である。 20

**【0019】**

上記構成の第1の領域は非単結晶である。

**【0020】**

上記構成の第1の領域は結晶部を含み、結晶部のc軸が、複合酸化物半導体膜の被形成面の法線ベクトルに平行である部分を有する。

**【0021】**

上記構成の第2の領域は非単結晶である。

**【0022】**

また、本発明の他の一態様は、上記構成の複合酸化物半導体を有することを特徴とするトランジスタである。 30

**【0023】**

また、本発明の他の一態様は、上記のいずれかの酸化物半導体と、表示素子と、を有する表示装置である。また、本発明の他の一態様は、当該表示装置と、タッチセンサと、を有する、表示モジュールである。また、本発明の他の一態様は、上記のいずれかの酸化物半導体、上記の半導体装置、上記の表示装置、または上記の表示モジュールと、操作キーまたはバッテリと、を有する電子機器である。

**【発明の効果】****【0024】**

本発明の一態様により、新規な酸化物半導体を提供することができる。または、本発明の一態様により、半導体装置に良好な電気特性を付与することができる。または、信頼性の高い半導体装置を提供することができる。または、新規な構成の半導体装置を提供することができる。または、新規な構成の表示装置を提供することができる。 40

**【0025】**

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

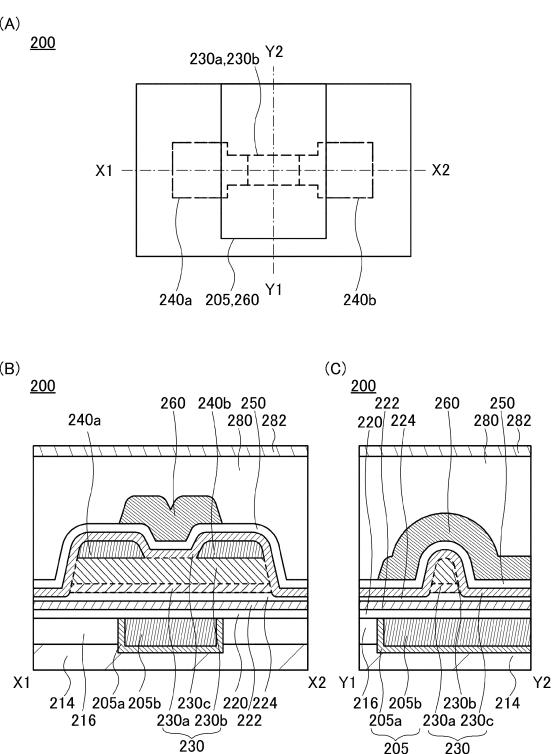

**【図面の簡単な説明】****【0026】**

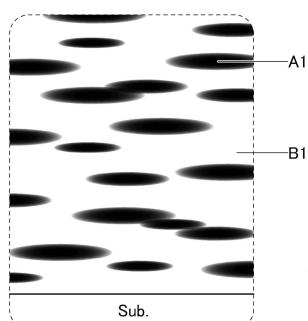

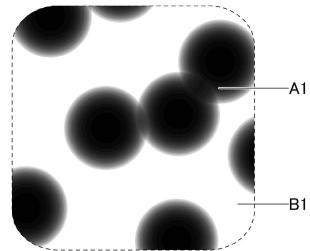

【図1】酸化物半導体の構造の概念図。 50

- 【図 2】酸化物半導体の構造の概念図。

- 【図 3】酸化物半導体の構造の概念図。

- 【図 4】酸化物半導体の構造の概念図。

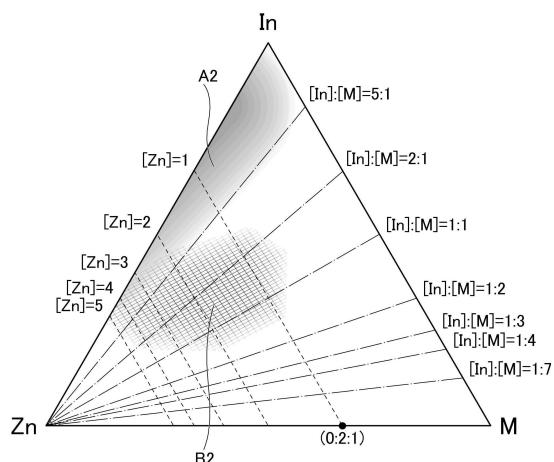

- 【図 5】酸化物半導体の原子数比を説明する図。

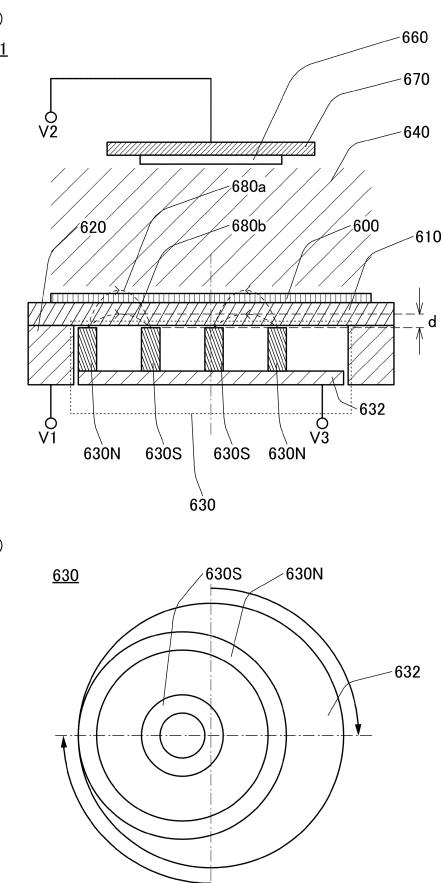

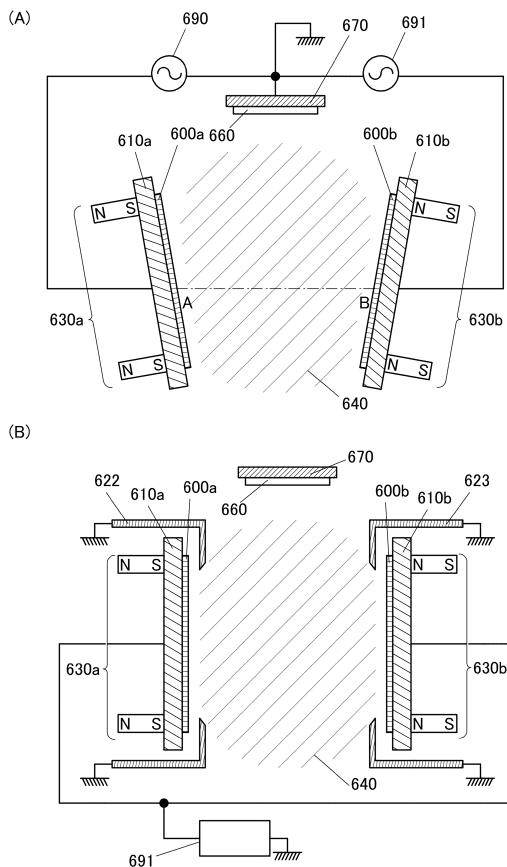

- 【図 6】スパッタリング装置を説明する図。

- 【図 7】スパッタリング装置を説明する図。

- 【図 8】スパッタリング装置を説明する図。

- 【図 9】スパッタリング装置を説明する図。

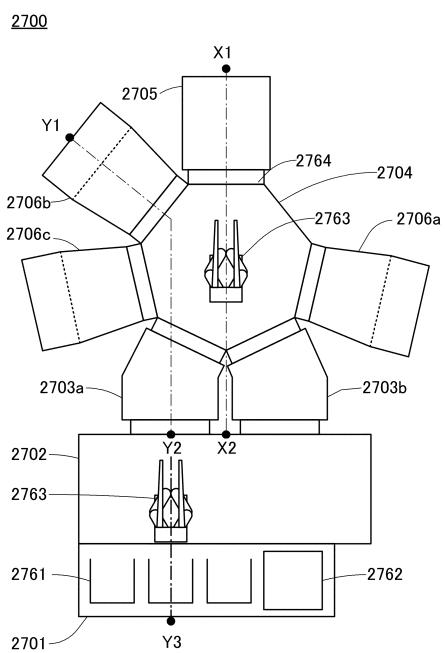

- 【図 10】成膜装置の一例を示す上面図。

- 【図 11】成膜装置の一例を示す断面図。 10

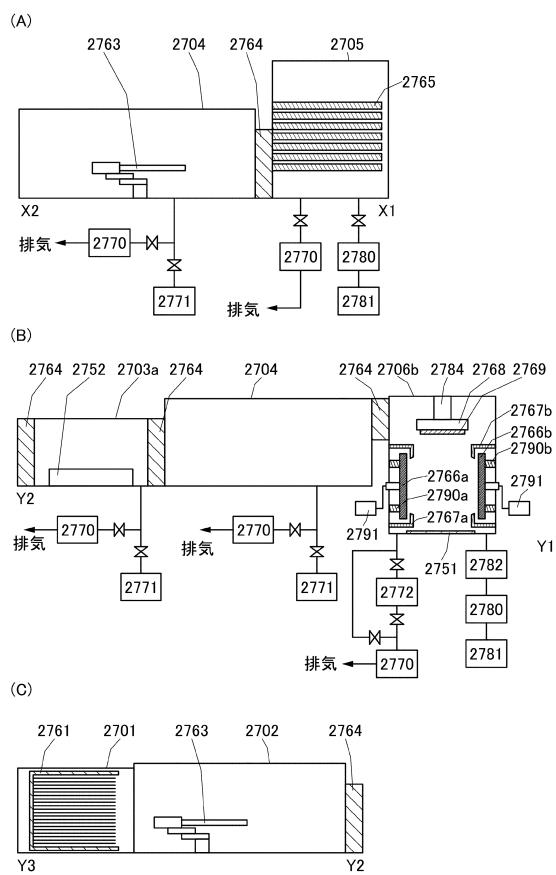

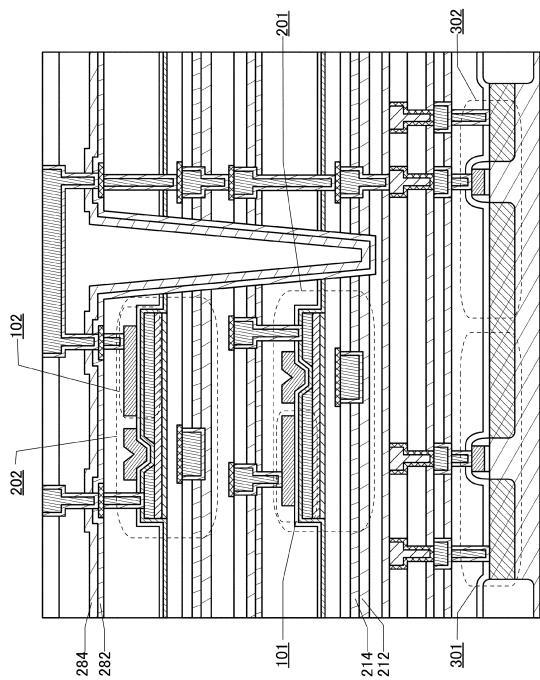

- 【図 12】実施の形態に係る、トランジスタの上面図および断面構造を説明する図。

- 【図 13】実施の形態に係る、トランジスタの上面図および断面構造を説明する図。

- 【図 14】実施の形態に係る、トランジスタの上面図および断面構造を説明する図。

- 【図 15】実施の形態に係る、トランジスタの上面図および断面構造を説明する図。

- 【図 16】実施の形態に係る、トランジスタの上面図および断面構造を説明する図。

- 【図 17】実施の形態に係る、トランジスタの上面図および断面構造を説明する図。

- 【図 18】実施の形態に係る、トランジスタの上面図および断面構造を説明する図。

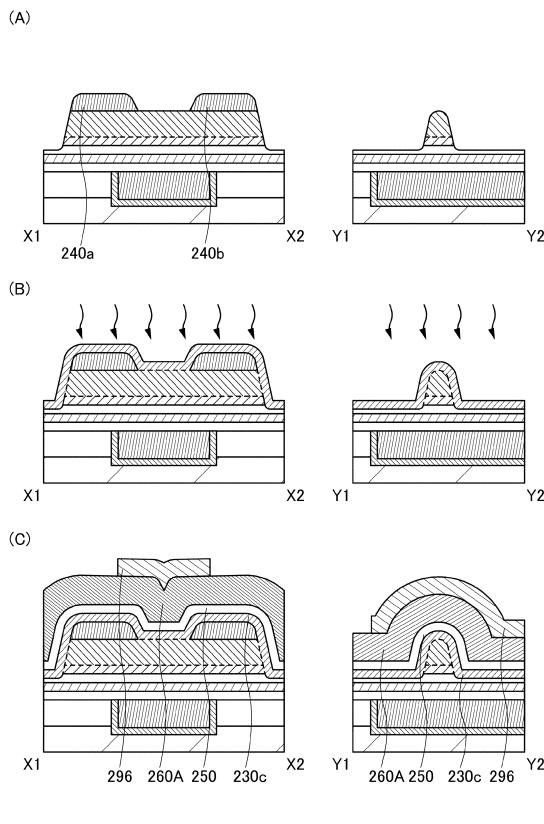

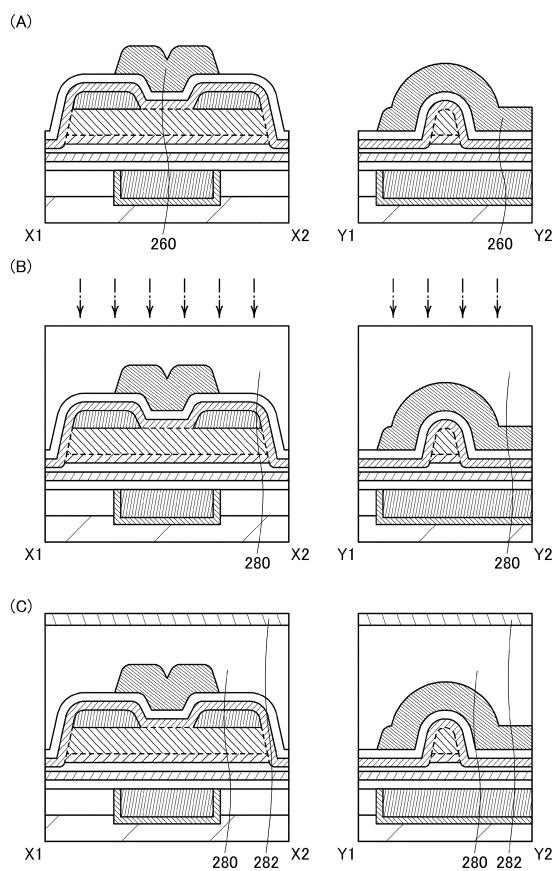

- 【図 19】実施の形態に係る、トランジスタの作製方法例を説明する図。

- 【図 20】実施の形態に係る、トランジスタの作製方法例を説明する図。 20

- 【図 21】実施の形態に係る、トランジスタの作製方法例を説明する図。

- 【図 22】実施の形態に係る、トランジスタの作製方法例を説明する図。

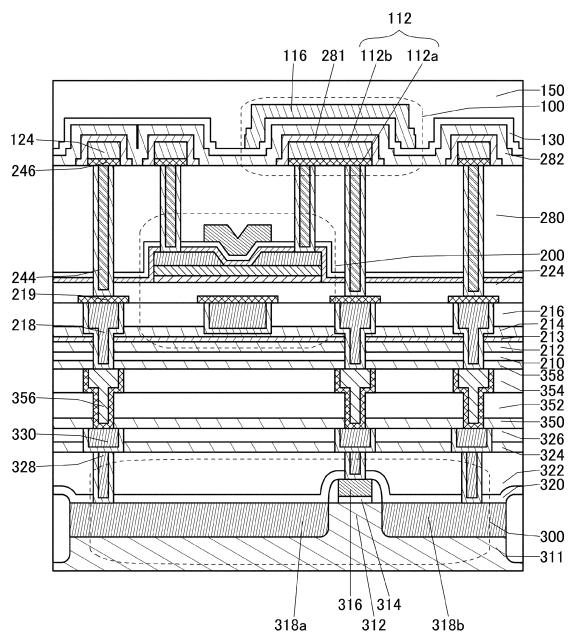

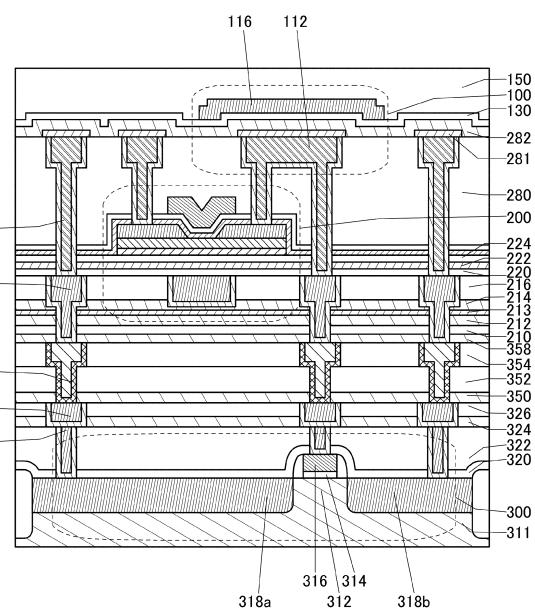

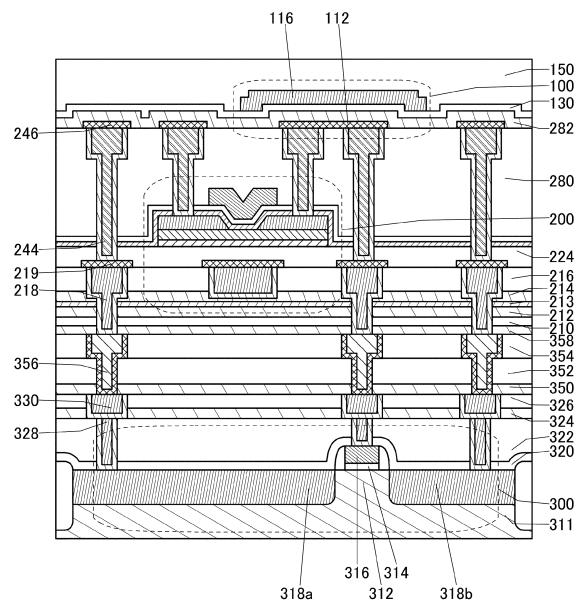

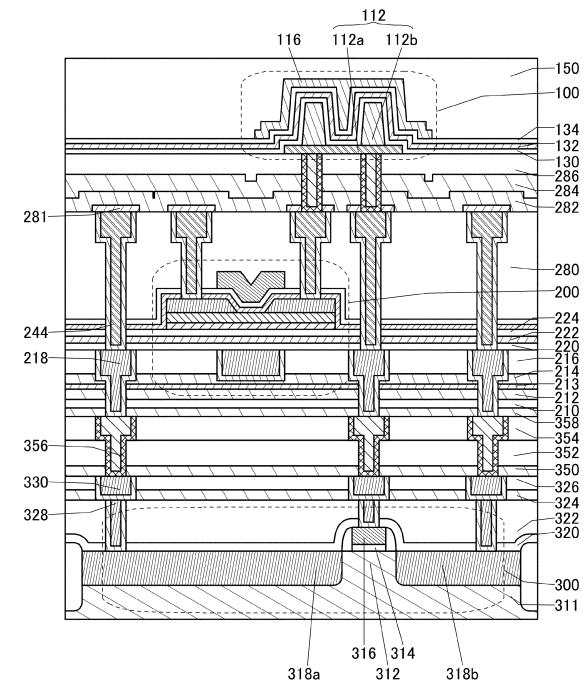

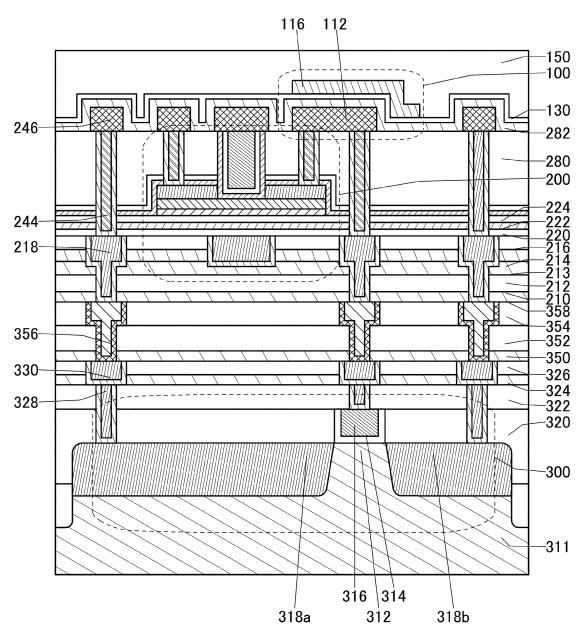

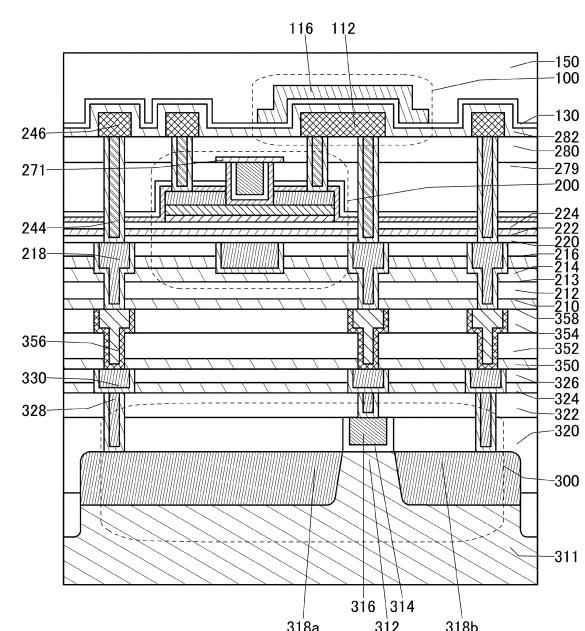

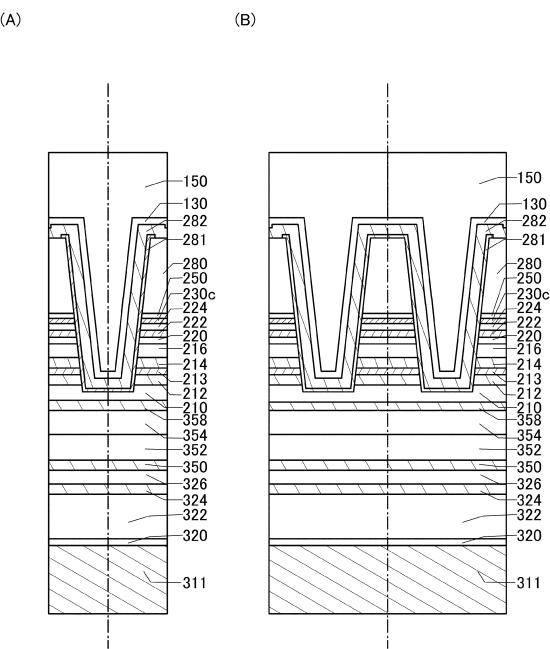

- 【図 23】実施の形態に係る、半導体装置の断面構造を説明する図。

- 【図 24】実施の形態に係る、半導体装置の断面構造を説明する図。

- 【図 25】実施の形態に係る、半導体装置の断面構造を説明する図。

- 【図 26】実施の形態に係る、半導体装置の断面構造を説明する図。

- 【図 27】実施の形態に係る、半導体装置の断面構造を説明する図。

- 【図 28】実施の形態に係る、半導体装置の断面構造を説明する図。

- 【図 29】実施の形態に係る、半導体装置の断面構造を説明する図。

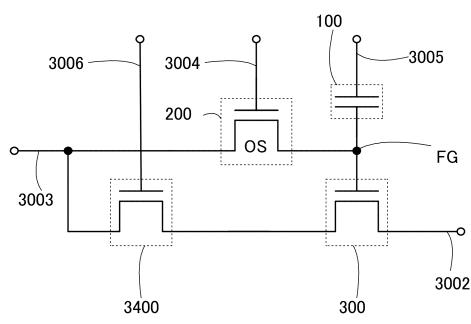

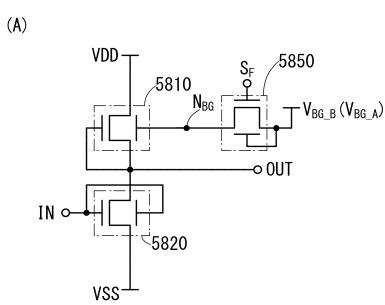

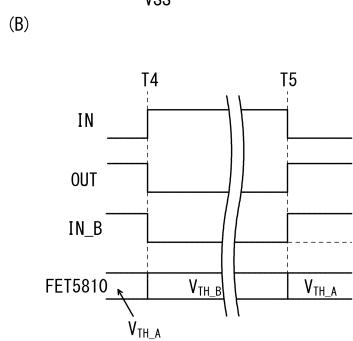

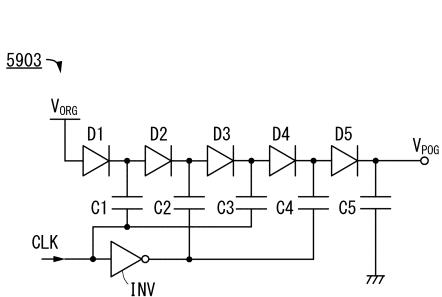

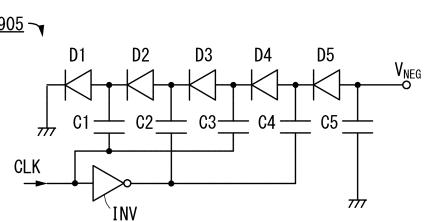

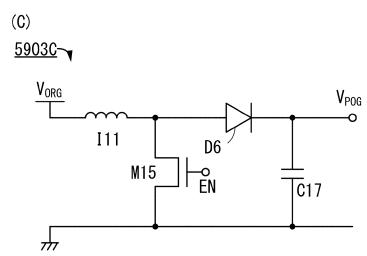

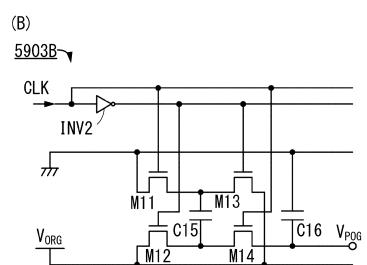

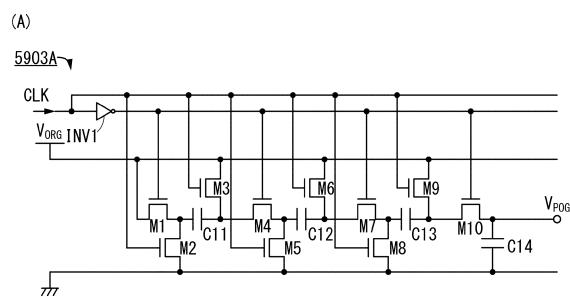

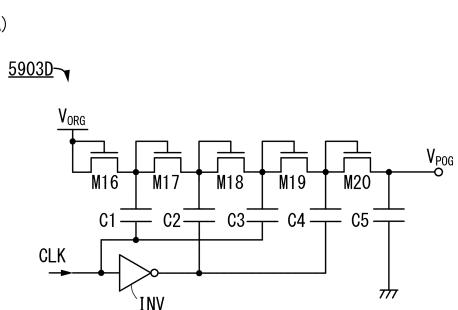

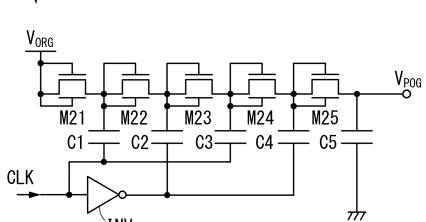

- 【図 30】実施の形態に係る、半導体装置の回路図。 30

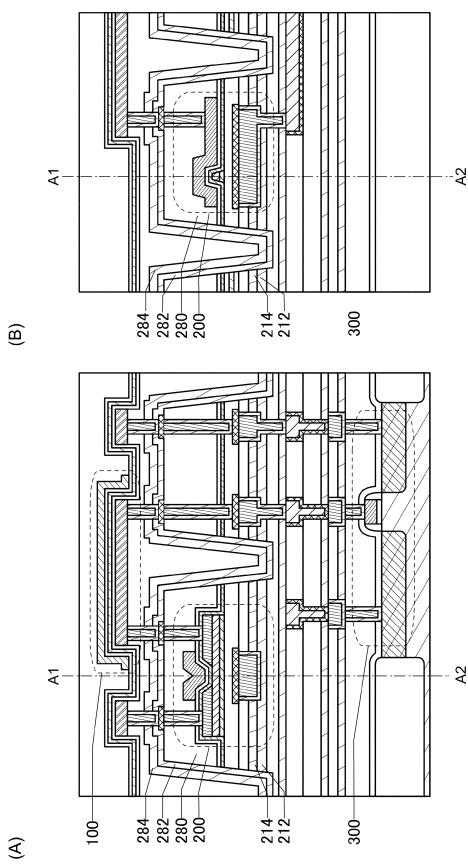

- 【図 31】実施の形態に係る、半導体装置の断面構造を説明する図。

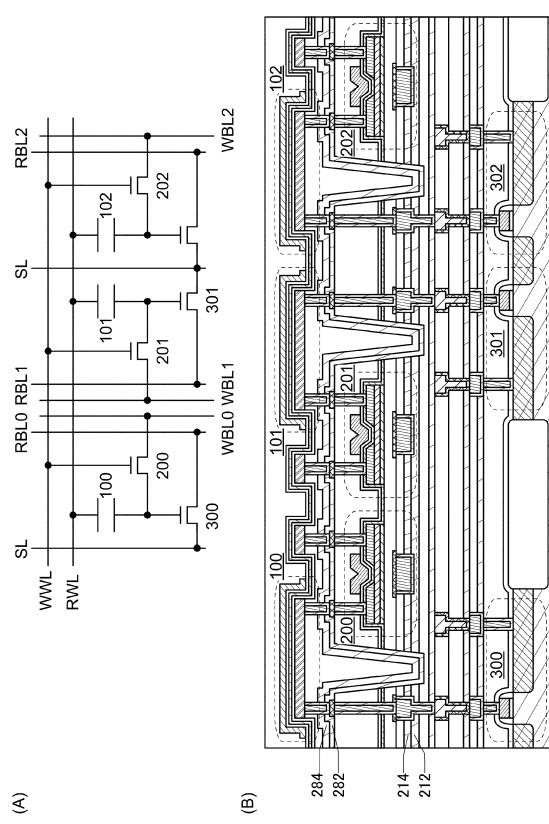

- 【図 32】実施の形態に係る、半導体装置の回路図および断面構造を説明する図。

- 【図 33】実施の形態に係る、半導体装置の断面構造を説明する図。

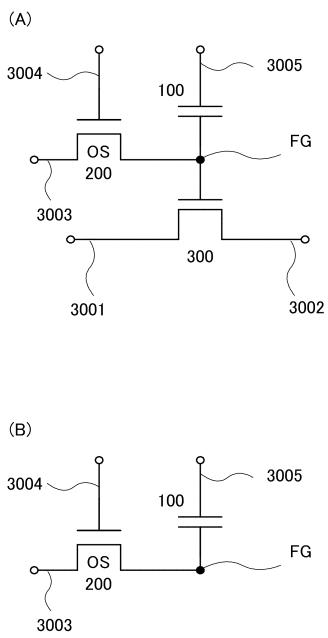

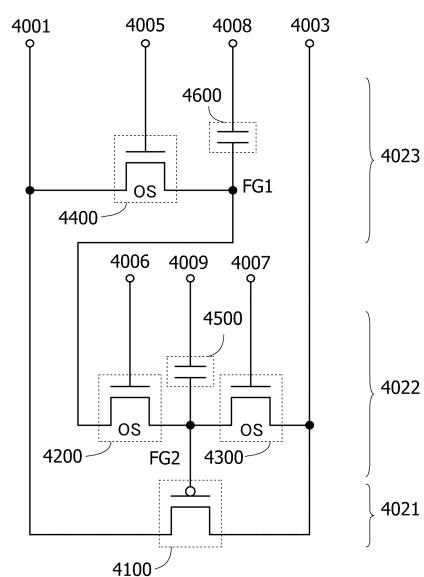

- 【図 34】本発明の一態様に係る記憶装置を示す回路図。

- 【図 35】本発明の一態様に係る記憶装置を示す回路図。

- 【図 36】本発明の一態様を説明するための回路図およびタイミングチャート。 40

- 【図 37】本発明の一態様を説明するためのグラフおよび回路図。

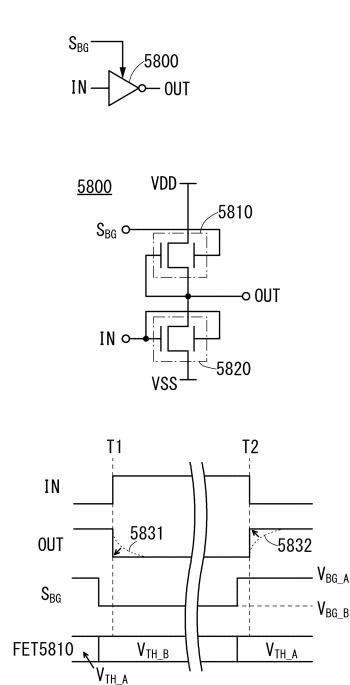

- 【図 38】本発明の一態様を説明するための回路図およびタイミングチャート。

- 【図 39】本発明の一態様を説明するための回路図およびタイミングチャート。

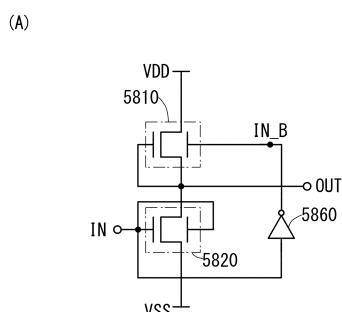

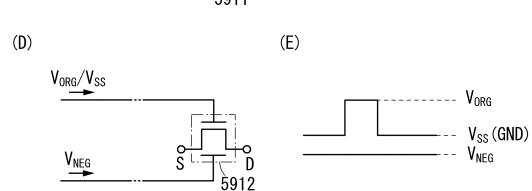

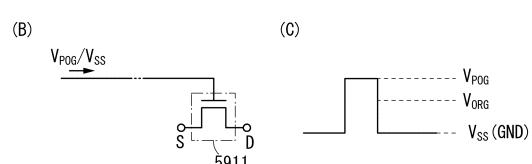

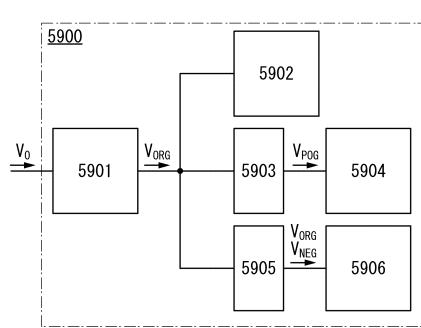

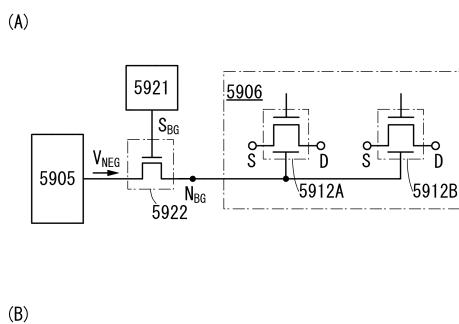

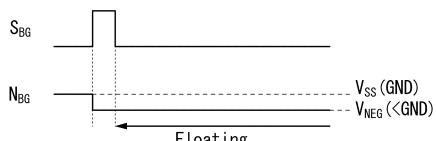

- 【図 40】本発明の一態様を説明するためのブロック図、回路図および波形図。

- 【図 41】本発明の一態様を説明するための回路図およびタイミングチャート。

- 【図 42】本発明の一態様を説明するための回路図。

- 【図 43】本発明の一態様を説明するための回路図。

- 【図 44】本発明の一態様を説明するための回路図。

- 【図 45】本発明の一態様を説明するための回路図。

- 【図 46】本発明の一態様を説明するための回路図。

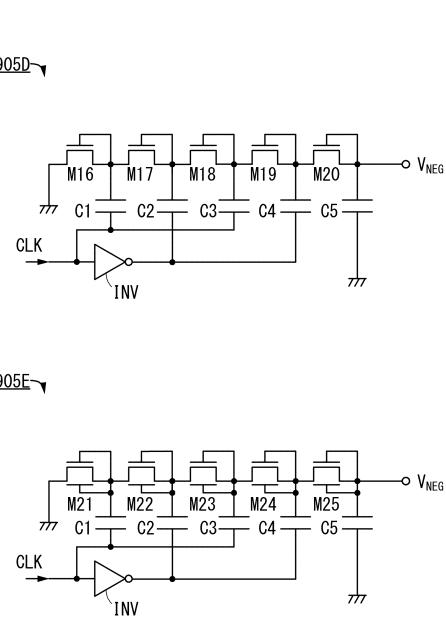

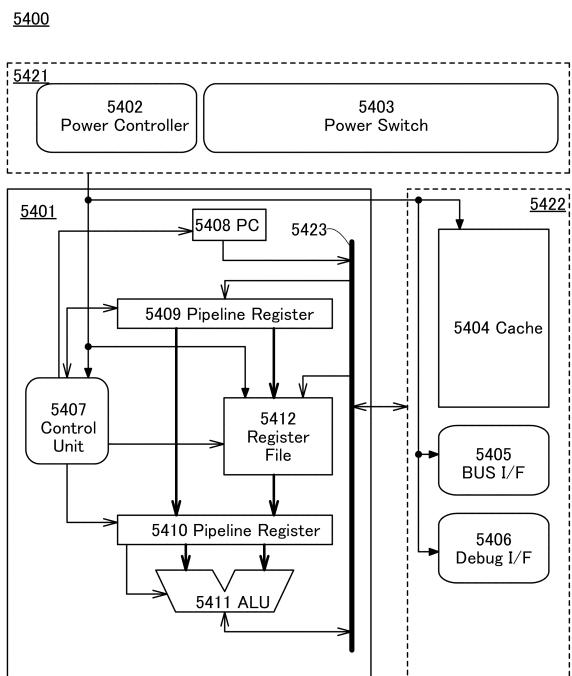

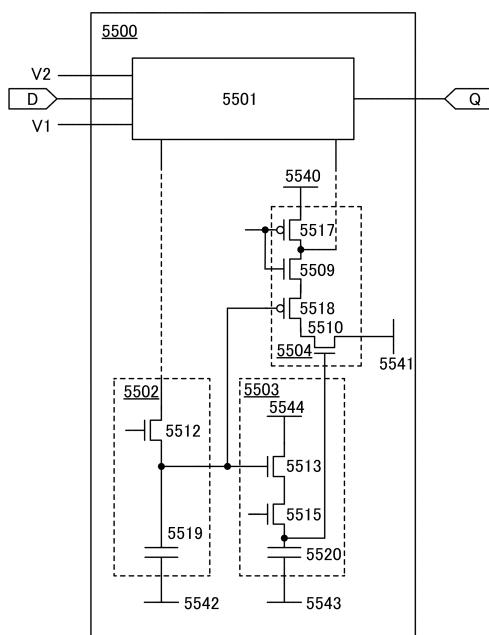

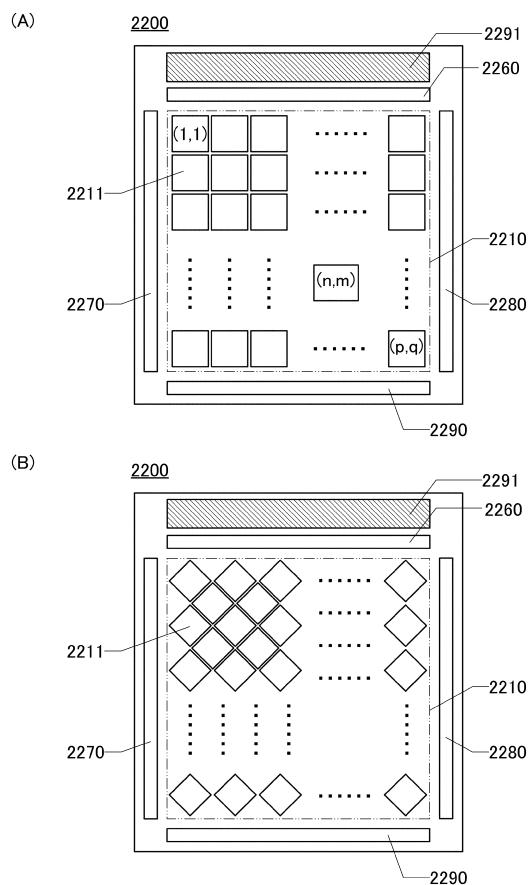

- 【図 47】本発明の一態様に係る半導体装置を示すブロック図。

- 【図 48】本発明の一態様に係る半導体装置を示す回路図。

- 【図 49】本発明の一態様に係る半導体装置を示す上面図。

- 【図 50】本発明の一態様に係る半導体装置を示すブロック図。 50

- 【図 51】本発明の一態様に係る半導体装置を示す断面図。

【図52】本発明の一態様に係る半導体装置を示す断面図。

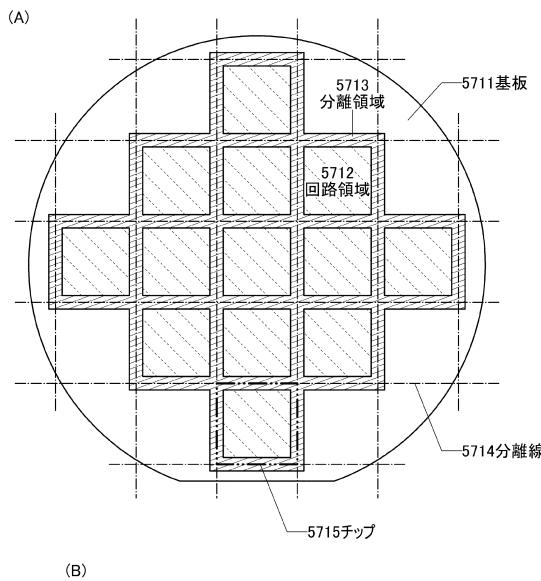

【図53】本発明の一態様に係る半導体装置を示す上面図。

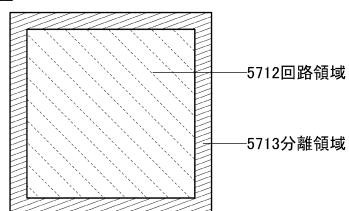

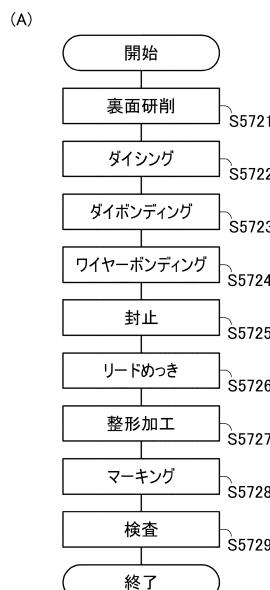

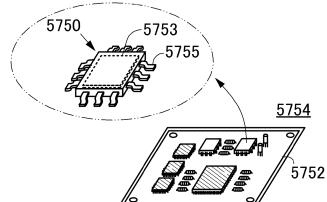

【図54】本発明の一態様を説明するためのフローチャート、および半導体装置を示す斜視図。

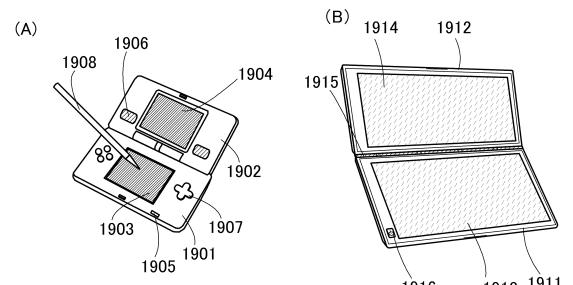

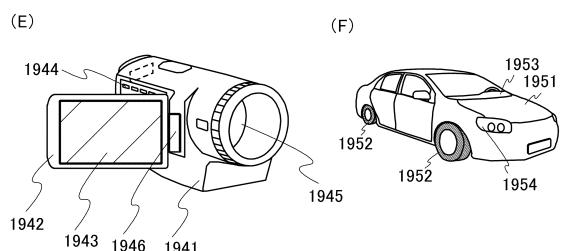

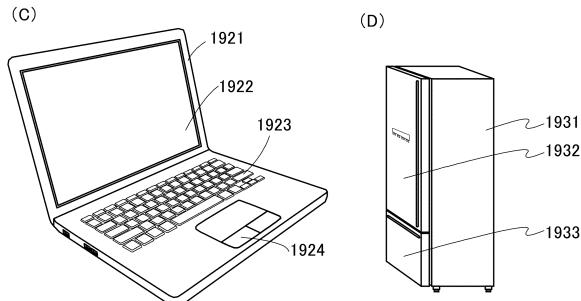

【図55】本発明の一態様に係る電子機器を示す斜視図。

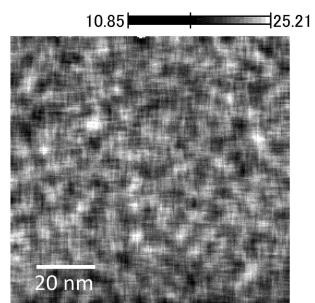

【図56】本実施例に係る試料の断面のEDXマッピング。

【図57】本実施例に係る試料の断面のBF-STEM像。

【図58】本実施例に係る試料のXRD測定結果とXRD分析位置を示す図。

【発明を実施するための形態】

【0027】

10

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

【0028】

また、図面において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模式的に示したものであり、図面に示す形状又は値などに限定されない。

【0029】

20

また、本明細書にて用いる「第1」、「第2」、「第3」という序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

【0030】

また、本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。

【0031】

また、本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。そして、ドレイン（ドレイン端子、ドレイン領域またはドレイン電極）とソース（ソース端子、ソース領域またはソース電極）の間にチャネル領域を有しており、チャネル領域を介して、ソース・ドレイン間に電流を流すことができるものである。なお、本明細書等において、チャネル領域とは、電流が主として流れる領域をいう。

30

【0032】

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができるものとする。

【0033】

40

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

【0034】

また、本明細書等において、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多い膜を指し、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多い膜を指す。

【0035】

50

また、本明細書等において、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる場合がある。

**【0036】**

また、本明細書等において、「平行」とは、二つの直線が - 10°以上 10°以下の角度で配置されている状態をいう。したがって、- 5°以上 5°以下の場合も含まれる。また、「略平行」とは、二つの直線が - 30°以上 30°以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が 80°以上 100°以下の角度で配置されている状態をいう。したがって、85°以上 95°以下の場合も含まれる。また、「略垂直」とは、二つの直線が 60°以上 120°以下の角度で配置されている状態をいう。

**【0037】**

また、本明細書等において、「膜」という用語と、「層」という用語とは、場合によっては、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

**【0038】**

なお、「半導体」と表記した場合でも、例えば、導電性が十分低い場合は「絶縁体」としての特性を有する場合がある。また、「半導体」と「絶縁体」は境界が曖昧であり、厳密に区別できない場合がある。したがって、本明細書に記載の「半導体」は、「絶縁体」と言い換えることができる場合がある。同様に、本明細書に記載の「絶縁体」は、「半導体」と言い換えることができる場合がある。

**【0039】**

(実施の形態 1)

本実施の形態では、本発明の一態様である酸化物半導体について説明する。

**【0040】**

酸化物半導体は、少なくともインジウムを含むことが好ましい。特にインジウムおよび亜鉛を含むことが好ましい。また、それに加えて、アルミニウム、ガリウム、イットリウムまたはスズなどが含まれていることが好ましい。また、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニア、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。

**【0041】**

ここで、酸化物半導体が、インジウム、元素M及び亜鉛を有する場合を考える。なお、元素Mは、アルミニウム、ガリウム、イットリウムまたはスズなどとする。そのほかの元素Mに適用可能な元素としては、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニア、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、マグネシウムなどがある。ただし、元素Mとして、前述の元素を複数組み合わせても構わない場合がある。なお、酸化物半導体が有するインジウム、元素M、及び亜鉛の原子数比のそれぞれの項を [In]、[M]、および [Zn] とする。

**【0042】**

<酸化物半導体の構造>

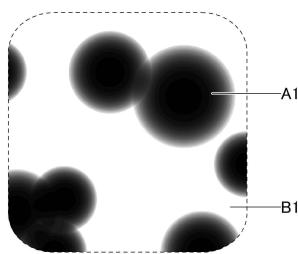

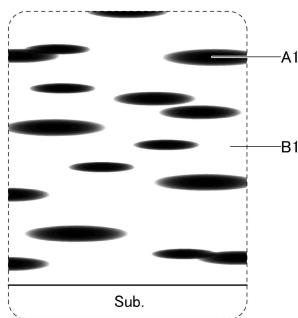

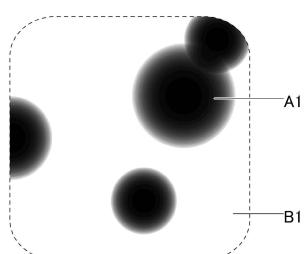

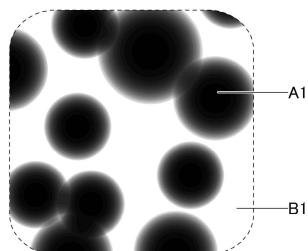

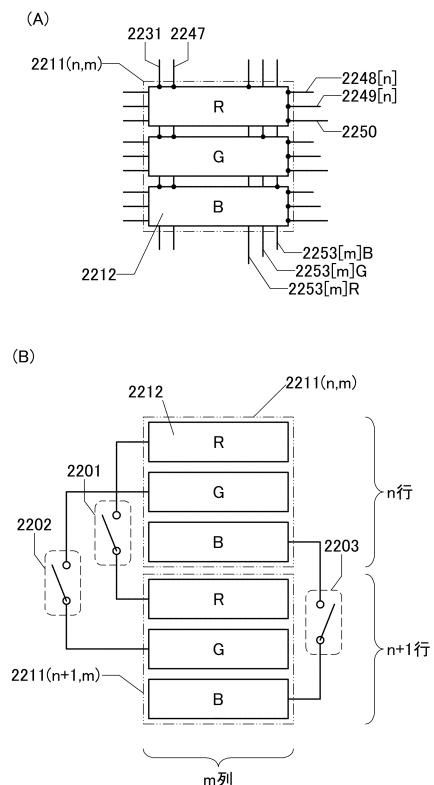

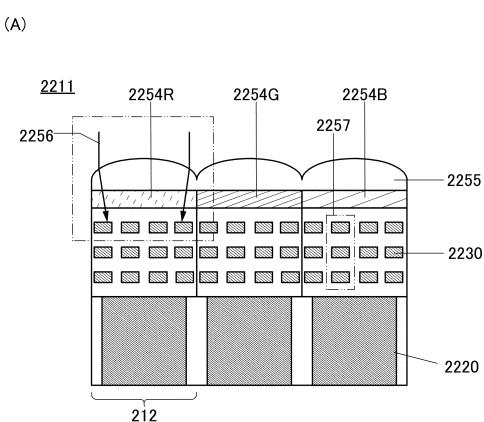

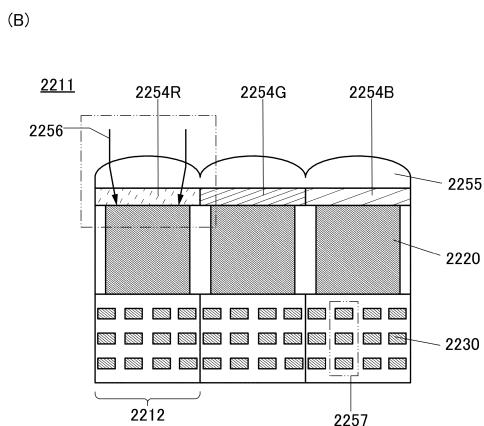

本発明における酸化物半導体の概念図を図1乃至図4に示す。

**【0043】**

本発明の酸化物半導体の概念図を図1乃至図4に示す。なお、図1(A)、図2(A)、図3(A)、及び図4(A)は、酸化物半導体の上面(ここでは、a-b面方向と呼ぶ)の概念図であり、図1(B)、図2(B)、図3(B)、及び図4(B)は、基板Sub.上に酸化物半導体が形成された断面(ここでは、c軸方向と呼ぶ)の概念図である。

**【0044】**

なお、図1乃至図4においては、基板上に酸化物半導体が形成される場合について例示したが、これに限定されず、基板と酸化物半導体との間に下地膜または層間膜などの絶縁膜、あるいは酸化物半導体などの他の半導体膜が形成されていてもよい。

10

20

30

40

50

**【 0 0 4 5 】**

本発明の酸化物半導体は、図1(A)、および図1(B)に示すように、領域A1と、領域B1とが、混合している構造を有する複合酸化物半導体である。領域A1は、 $[In] : [M] : [Zn] = x : y : z$  ( $x > 0, y > 0, z > 0$ ) となるInが多い領域である。一方、領域B1は、 $[In] : [M] : [Zn] = a : b : c$  ( $a > 0, b > 0, c > 0$ ) となるInが少ない領域である。

**【 0 0 4 6 】**

なお、本明細書において、領域A1の元素Mに対するInの原子数比が、領域B1の元素Mに対するInの原子数比よりも大きいことを、領域A1は、領域B1と比較して、Inの濃度が高いとする。従って、本明細書において、領域A1をIn-richな領域、また、領域B1をIn-poorな領域、ともいう。10

**【 0 0 4 7 】**

例えば、領域A1は、領域B1よりも、Inの濃度が1.1倍以上、好ましくは2倍以上10倍以下であるとよい。また、領域A1は、少なくともInを有する酸化物であればよく、元素M、およびZnは、必ずしも含まれなくともよい。

**【 0 0 4 8 】**

## &lt;原子数比&gt;

ここで、本発明の一態様の複合酸化物半導体が有する元素の原子数比について説明する。

**【 0 0 4 9 】**

本発明の酸化物半導体において、例えば、領域A1が、In、元素M、およびZnを有する場合に、各元素の原子数比は図5に示す相図を用いて示すことができる。In、元素M、およびZnの原子数比を、x、y、およびzを用いて、 $x : y : z$ と表す。ここで原子数比は座標( $x : y : z$ )として図中に表すことができる。なお、図5には、酸素の原子数比については記載しない。20

**【 0 0 5 0 】**

図5において、破線は、 $[In] : [M] : [Zn] = (1+ ) : (1- ) : 1$  の原子数比(-1 1)となるライン、 $[In] : [M] : [Zn] = (1+ ) : (1- ) : 2$  の原子数比となるライン、 $[In] : [M] : [Zn] = (1+ ) : (1- ) : 3$  の原子数比となるライン、 $[In] : [M] : [Zn] = (1+ ) : (1- ) : 4$  の原子数比となるライン、および $[In] : [M] : [Zn] = (1+ ) : (1- ) : 5$  の原子数比となるラインを表す。30

**【 0 0 5 1 】**

また、一点鎖線は、 $[In] : [M] : [Zn] = 1 : 1 :$  の原子数比( 0 )となるライン、 $[In] : [M] : [Zn] = 1 : 2 :$  の原子数比となるライン、 $[In] : [M] : [Zn] = 1 : 3 :$  の原子数比となるライン、 $[In] : [M] : [Zn] = 1 : 4 :$  の原子数比となるライン、 $[In] : [M] : [Zn] = 1 : 7 :$  の原子数比となるライン、 $[In] : [M] : [Zn] = 2 : 1 :$  の原子数比となるライン、及び $[In] : [M] : [Zn] = 5 : 1 :$  の原子数比となるラインを表す。

**【 0 0 5 2 】**

また、図5に示す、 $[In] : [M] : [Zn] = 0 : 2 : 1$  の原子数比またはその近傍値の酸化物半導体は、スピネル型の結晶構造となる傾向がある。40

**【 0 0 5 3 】**

図5で示す領域A2は、領域A1が有するインジウム、元素M、及び亜鉛の原子数比の好ましい範囲の一例について示している。なお、領域A2は、 $[In] : [M] : [Zn] = (1+ ) : 0 : (1- )$  の原子数比(-1 1)となるライン上も含むものとする。

**【 0 0 5 4 】**

図5で示す領域B2は、領域B1が有するインジウム、元素M、及び亜鉛の原子数比の好ましい範囲の一例について示している。なお、領域B2は、 $[In] : [M] : [Zn] = 4 : 2 : 3$  から4.1、およびその近傍値を含む。近傍値には、例えば、原子数比が[50

$I_n$  :  $M$  :  $Zn$  = 5 : 3 : 4 が含まれる。また、領域 B 2 は、 $I_n$  :  $M$  :  $Zn$  = 5 : 1 : 6、およびその近傍値を含む。

#### 【0055】

領域 A 2 は、 $I_n$  の濃度が高いため、領域 B 2 よりも、導電性が高くなり、キャリア移動度（電界効果移動度）を高める機能を有する。したがって、領域 A 1 を有する酸化物半導体を用いたトランジスタのオン電流及びキャリア移動度を高めることができる。

#### 【0056】

一方、領域 B 2 は、 $I_n$  の濃度が低いため、領域 A 2 よりも、導電性が低く、リーク電流を低減する機能を有する。したがって、領域 B 1 を有する酸化物半導体を用いたトランジスタのオフ電流を低くすることができる。

10

#### 【0057】

本発明の酸化物半導体において、領域 A 1 と、領域 B 1 とが、複合体を形成している。つまり、領域 A 1 では、キャリア移動が生じやすく、領域 B 1 では、キャリア移動が生じにくい。そのため、本発明の酸化物半導体は、キャリア移動度が高く、かつ、スイッチング特性が高い、半導体特性が良好な材料として用いることができる。

#### 【0058】

一例として、図 1 (A) に示すように、領域 A 1 は、a - b 面方向において、基本的には、円に近い形状で形成される。また、図 1 (B) に示すように、領域 A 1 は、c 軸方向において、基本的には、橢円に近い形状で形成される。従って、領域 A 1 は、アイランド状であり、領域 B 1 に立体的にはさまれている状態で存在しうる。つまり、領域 A 1 は、領域 B 1 に内包されている構造である。

20

#### 【0059】

また、図 1 (A)、および図 1 (B) に示すように、領域 A 1 は、領域 B 1 中に、不規則に偏在している。そのため、複数の領域 A 1 がつながって存在していてもよい。つまり、複数の領域 A 1 が、a - b 面方向において、円が重畠した形状、または c 軸方向において、橢円が端部で連結した形状となる場合がある。ただし、全ての領域 A 1 が、a - b 面方向に連結した場合、トランジスタのスイッチング特性、例えばトランジスタのオフ電流が上昇するため、図 1 (A)、図 1 (B) に示すように、領域 A 1 は、領域 B 1 内に、点在していた方が好ましい。

#### 【0060】

30

なお、領域 A 1 が点在する割合は、複合酸化物半導体の作成条件、または組成により、調節することができる。例えば、図 2 に示すように、領域 A 1 の割合が少ない複合酸化物半導体、または、図 3 に示すように、領域 A 1 の割合が多い複合酸化物半導体を形成することができる。また、本発明の複合酸化物半導体は、領域 B 1 に対し、領域 A 1 の割合が小さいとは限らない。領域 A 1 の割合が非常に大きい複合酸化物半導体では、観察する範囲により、領域 A 1 内に領域 B 1 が形成されている場合もある。

#### 【0061】

また、例えば、領域 A 1 が形成するアイランド状のサイズは、複合酸化物半導体の作成条件、または組成により、適宜調節することができる。図 1 乃至図 3 では、さまざまなサイズのアイランド状の領域が形成されている概念図を示したが、図 4 に示すように、同程度の大きさの領域 A 1 が点在する場合がある。

40

#### 【0062】

また、領域 A 1 と、領域 B 1 とは、明確な境界が観察できない場合がある。なお、領域 A 1 及び領域 B 1 のサイズは、EDX マッピングで評価することができる。例えば、領域 A 1 は、断面写真の EDX マッピングにおいて、領域 A 1 の厚み（径ともいう）が、0.1 nm 以上 5 nm 以下、または 0.3 nm 以上 3 nm 以下で観察される場合がある。なお、好ましくは領域 A 1 の厚みは、0.1 nm 以上 1 nm 以下とする。

#### 【0063】

このように、本発明の一態様の酸化物半導体は、領域 A 1 と領域 B 1 とが混合している複合酸化物半導体であり、かつ領域 A 1 の機能と、領域 B 1 の機能と、がそれぞれ異なり、

50

領域 A 1 と領域 B 1 とが、相補的に機能している。例えば、元素 M を Ga とした In - Ga - Zn 酸化物（以下、IGZO とする）の場合、本発明の一態様の酸化物半導体を、Complementary IGZO（略称：C / IGZO）と呼称することができる。

#### 【0064】

一方で、例えば、領域 A 1 と領域 B 1 とが層状で積層された構成の場合、領域 A 1 と領域 B 1 との間には相互作用がない、または相互作用が起きにくいため、領域 A 1 の機能と領域 B 1 の機能とが、それぞれ独立に機能する場合がある。この場合、領域 A 1 によって、キャリア移動度を高くすることが出来たとしても、トランジスタのオフ電流が高くなる場合がある。したがって、上述した複合酸化物半導体、または C / IGZO とすることで、キャリア移動度が高い機能と、スイッチング特性が良好である機能と、を同時に兼ね備えることが出来る。これは、本発明の複合体酸化物半導体で得られる優れた効果である。10

#### 【0065】

なお、酸化物半導体をスパッタリング装置にて成膜する場合、ターゲットの原子数比からずれた原子数比の膜が形成される。特に、成膜時の基板温度によっては、[Zn]において、ターゲットの原子数比よりも膜の原子数比が小さくなる場合がある。

#### 【0066】

また、本発明の一態様である複合酸化物半導体の特性は、原子数比によって一義的に定まらない。従って、図示する領域は、複合酸化物半導体が有する領域 A 1、および領域 B 1 が有する好ましい原子数比を示す領域であり、境界は厳密ではない。20

#### 【0067】

ここで、酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体と、に分けられる。非単結晶酸化物半導体としては、CAAC-OS (c-axis aligned crystalline oxide semiconductor)、多結晶酸化物半導体、nc-OS (nanocrystalline oxide semiconductor)、擬似非晶質酸化物半導体 (a-like OS : amorphous-like oxide semiconductor) および非晶質酸化物半導体などがある。20

#### 【0068】

CAAC-OS は、c 軸配向性を有し、かつ a - b 面方向において複数のナノ結晶が連結し、歪みを有した結晶構造となっている。30

#### 【0069】

nc-OS は、微小な領域（例えば、1 nm 以上 10 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。また、nc-OS は、異なるナノ結晶間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、nc-OS は、分析方法によっては、a-like OS や非晶質酸化物半導体と区別が付かない場合がある。

#### 【0070】

a-like OS は、nc-OS と非晶質酸化物半導体との間の構造を有する酸化物半導体である。a-like OS は、鬆または低密度領域を有する。即ち、a-like OS は、nc-OS および CAAC-OS と比べて、不安定な構造である。40

#### 【0071】

酸化物半導体は、様々な構造をとり、それぞれが様々な特性を有する。本発明の酸化物半導体は、非晶質酸化物半導体、a-like OS、nc-OS、CAAC-OS のうち、二種以上を有する複合酸化物半導体であってもよい。

#### 【0072】

例えば、領域 A 1 は、非単結晶であることが好ましい。一方、領域 B 1 は、CAAC-OS、多結晶酸化物半導体、および nc-OS 等の領域のうち少なくとも一を有することが好ましい。また、領域 A 1 と、領域 B 1 とが異なる結晶を有していてもよい。

#### 【0073】

<酸化物半導体を有するトランジスタ>

10

20

30

40

50

続いて、上記酸化物半導体をトランジスタに用いる場合について説明する。

**【0074】**

なお、上記複合酸化物半導体をトランジスタに用いることで、キャリア移動度が高く、かつ、スイッチング特性が高いトランジスタを実現することができる。また、信頼性の高いトランジスタを実現することができる。

**【0075】**

また、トランジスタには、キャリア密度の低い酸化物半導体を用いることが好ましい。例えば、酸化物半導体は、キャリア密度が  $8 \times 10^{11} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{10} / \text{cm}^3$  未満であり、 $1 \times 10^{-9} / \text{cm}^3$  以上とすればよい。

10

**【0076】**

なお、高純度真性または実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができます。また、高純度真性または実質的に高純度真性である酸化物半導体は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。

**【0077】**

また、酸化物半導体のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体にチャネル領域が形成されるトランジスタは、電気特性が不安定となる場合がある。

20

**【0078】**

従って、トランジスタの電気特性を安定にするためには、酸化物半導体中の不純物濃度を低減することが有効である。また、酸化物半導体中の不純物濃度を低減するためには、近接する膜中の不純物濃度も低減することが好ましい。不純物としては、水素、窒素、アルカリ金属、アルカリ土類金属、鉄、ニッケル、シリコン等がある。

**【0079】**

ここで、酸化物半導体中における各不純物の影響について説明する。

**【0080】**

酸化物半導体において、第14族元素の一つであるシリコンや炭素が含まれると、酸化物半導体において欠陥準位が形成される。このため、酸化物半導体におけるシリコンや炭素の濃度と、酸化物半導体との界面近傍のシリコンや炭素の濃度（二次イオン質量分析法（S I M S : Secondary Ion Mass Spectrometry）により得られる濃度）を、 $2 \times 10^{18} \text{ atoms} / \text{cm}^3$  以下、好ましくは  $2 \times 10^{17} \text{ atoms} / \text{cm}^3$  以下とする。

30

**【0081】**

また、酸化物半導体にアルカリ金属またはアルカリ土類金属が含まれると、欠陥準位を形成し、キャリアを生成する場合がある。従って、アルカリ金属またはアルカリ土類金属が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体中のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。具体的には、S I M S により得られる酸化物半導体中のアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18} \text{ atoms} / \text{cm}^3$  以下、好ましくは  $2 \times 10^{16} \text{ atoms} / \text{cm}^3$  以下とする。

40

**【0082】**

また、酸化物半導体において、窒素が含まれると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を半導体に用いたトランジスタはノーマリーオン特性となりやすい。従って、該酸化物半導体において、窒素はできる限り低減されていることが好ましい、例えば、酸化物半導体中の窒素濃度は、S I M S において、 $5 \times 10^{19} \text{ atoms} / \text{cm}^3$  未満、好ましくは  $5 \times 10^{18} \text{ atoms} / \text{cm}^3$  以下、より好ましくは  $1 \times 10^{18} \text{ atoms} / \text{cm}^3$  以下、さらに好ましくは  $5 \times 10^{17} \text{ atoms} / \text{cm}^3$  以下とする。

50

## 【0083】

また、酸化物半導体に含まれる水素は、金属原子と結合する酸素と反応して水になるため、酸素欠損（V<sub>o</sub>）を形成する場合がある。該酸素欠損（V<sub>o</sub>）に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することがある。従って、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体において、S I M Sにより得られる水素濃度を、 $1 \times 10^{20}$  atoms / cm<sup>3</sup>未満、好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup>未満、より好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>未満とする。

10

## 【0084】

なお、酸化物半導体中の酸素欠損（V<sub>o</sub>）は、酸素を酸化物半導体に導入することで、低減することができる。つまり、酸化物半導体中の酸素欠損（V<sub>o</sub>）に、酸素が補填されることで、酸素欠損（V<sub>o</sub>）は消失する。従って、酸化物半導体中に、酸素を拡散させることで、トランジスタの酸素欠損（V<sub>o</sub>）を低減し、信頼性を向上させることができる。

## 【0085】

なお、酸素を酸化物半導体に導入する方法として、例えば、酸化物半導体に接して、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物を設けることができる。つまり、酸化物には、化学量論的組成よりも酸素が過剰に存在する領域（以下、過剰酸素領域ともいう）が形成されていることが好ましい。特に、トランジスタに酸化物半導体を用いる場合、トランジスタ近傍の下地膜や、層間膜などに、過剰酸素領域を有する酸化物を設けることで、トランジスタの酸素欠損を低減し、信頼性を向上させることができる。

20

## 【0086】

不純物が十分に低減された酸化物半導体をトランジスタのチャネル形成領域に用いることで、安定した電気特性を付与することができる。

## 【0087】

<酸化物半導体の成膜方法>

以下では、スパッタリング法による酸化物半導体の成膜方法の一例について説明する。

## 【0088】

酸化物半導体を成膜する際の温度としては、室温以上140℃未満とすることが好ましい。なお、室温とは、温度調節を行わない場合だけでなく、温度調節を行う場合も含むものとする。

30

## 【0089】

また、スパッタリングガスは、希ガス（代表的にはアルゴン）、酸素、希ガス及び酸素の混合ガスを適宜用いる。混合ガスの場合、希ガスに対して酸素のガス比が、5%以上30%以下、好ましくは7%以上20%以下とする。

## 【0090】

なお、スパッタリングガスとして酸素を含むと、酸化物半導体の成膜と同時に、下層の膜に、酸素を添加し、酸素過剰領域を設けることができる。また、スパッタリングガスの高純度化も必要である。例えば、スパッタリングガスとして用いる酸素ガスやアルゴンガスは、露点が-40℃以下、好ましくは-80℃以下、より好ましくは-100℃以下、より好ましくは-120℃以下にまで高純度化したガスを用いることで酸化物半導体に水分等が取り込まれることを可能な限り防ぐことができる。

40

## 【0091】

また、スパッタリング法で酸化物半導体を成膜する場合、スパッタリング装置におけるチャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空（ $5 \times 10^{-7}$  Paから $1 \times 10^{-4}$  Pa程度まで）排気することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体、特に炭素または水素を含む気体が逆流しないようにしておくことが好ましい。

50

**【 0 0 9 2 】**

また、ターゲットとして、In - Ga - Zn 金属酸化物ターゲットを用いることができる。例えば、[In] : [Ga] : [Zn] = 4 : 2 : 4 . 1 [原子数比]、または[In] : [Ga] : [Zn] = 5 : 1 : 6 [原子数比]、またはその近傍値の原子数比である金属酸化物ターゲットを用いることが好ましい。

**【 0 0 9 3 】**

また、スパッタリング装置において、ターゲットを回転または移動させても構わない。例えば、成膜中にマグネットユニットを上下または / 及び左右に揺動させることによって、本発明の複合酸化物半導体を形成することができる。例えば、ターゲットを、0 . 1 Hz 以上 1 kHz 以下のビート(リズム、拍子、パルス、周波、周期またはサイクルなどとい換えてよい。)で回転または移動させればよい。または、マグネットユニットを、0 . 1 Hz 以上 1 kHz 以下のビートで揺動させればよい。なお、スパッタリング装置の詳細については、後の実施の形態で述べる。10

**【 0 0 9 4 】**

例えば、スパッタリングガスとして、酸素のガス比が 10 % 程度の希ガス、および酸素の混合ガスを用い、基板温度を 130 °C とし、[In] : [Ga] : [Zn] = 4 : 2 : 4 . 1 [原子数比] の In - Ga - Zn 金属酸化物ターゲットを揺動させながら成膜を行うことで、本発明の酸化物半導体を形成することができる。

**【 0 0 9 5 】**

まず、希ガスまたは酸素ガスが成膜室中で電離し、陽イオンと電子とに分かれてプラズマを形成する。プラズマ中の陽イオンは、ターゲットホルダに印加された電位によって、ターゲットに向けて加速される。陽イオンが In - Ga - Zn 金属酸化物ターゲットに衝突することで、スパッタ粒子が生成され、基板上にスパッタ粒子が堆積する。20

**【 0 0 9 6 】**

まず、陽イオンが In - Ga - Zn 金属酸化物ターゲットに衝突することで、相対原子質量が、In よりも軽い Ga、および Zn が、ターゲットから優先的に弾き出される。弾き出された In、Ga、および Zn が、酸素と結合し、基板上に堆積することで、領域 B1 が成膜される。この時、ターゲットの表面には、In が偏析した状態となる。

**【 0 0 9 7 】**

続いて、ターゲットの表面に偏析した In が、複数の粒子のような構造となり、ターゲットから弾き出される。複数の粒子のような構造となった偏析した In が、酸素と結合し、先に成膜された領域 B1 上に衝突し、円に近い形状に広がることで、アイランド状の領域 A1 が堆積する。なお、偏析した In が弾き出されたため、ターゲットの表面には、In、Ga、Zn が、元の原子数比に近い状態で存在する。30

**【 0 0 9 8 】**

ここで、さらに、陽イオンがターゲットに衝突することで、相対原子質量が、In よりも軽い Ga、および Zn が、ターゲットから優先的に弾き出される。なお、この時、ターゲットの表面には、In が偏析した状態となる。再び、領域 B1 が、先に成膜された領域 B1、および領域 A1 上に堆積することで、領域 A1 を挟み込むように、領域 B1 が成膜される。40

**【 0 0 9 9 】**

なお、ターゲット表面の一領域では、In が偏析し、他のターゲット表面の一領域では、偏析した In が弾き出される。つまり、In が偏析する機構、および偏析した In が弾き出される機構が、同時に生じることで、領域 A1 は、領域 B1 に挟まれ、不規則に偏在する構造となる。

**【 0 1 0 0 】**

上記の成膜モデルを経ることによって、図 1 乃至 図 4 に示すような、領域 A1 と領域 B1 とが混合している複合酸化物半導体が形成されると考える。

**【 0 1 0 1 】**

本発明の酸化物半導体は、領域 A2 で示される原子数比で構成される In が多い領域 A150

と、領域B2で示される原子数比で構成されるInが少ない領域B1とが、混在し、複合酸化物半導体を形成している。つまり、領域A1ではキャリア移動が生じやすく、領域B1では、キャリア移動が生じにくい。そのため、本発明の酸化物半導体は、キャリア移動度が高く、かつ、スイッチング特性が高い、半導体特性が良好な材料として用いることができる。

#### 【0102】

以上、本実施の形態に示す構成は、他の実施の形態または他の実施例に示す構成と適宜、組み合わせて用いることができる。

#### 【0103】

##### (実施の形態2)

10

本実施の形態においては、本発明の一態様の酸化物を成膜することができるスパッタリング装置及び成膜装置について、図6乃至図11を用いて説明する。なお、以下に示すスパッタリング装置では、理解を容易にするため、または成膜時における動作を説明するため、基板およびターゲットなどを配置した状態で示す。ただし、基板およびターゲットなどは、使用者が設置する物であるため、本発明の一態様に係るスパッタリング装置が基板およびターゲットを有さない場合もある。

#### 【0104】

##### <スパッタリング装置>

スパッタリング装置としては、例えば平行平板型スパッタリング装置、及び対向ターゲット式スパッタリング装置を用いることができる。なお、平行平板型スパッタリング装置を用いた成膜法を、PESP (parallel electrode SP) と呼ぶこともできる。また、対向ターゲット式スパッタリング装置を用いた成膜法を、VDS (vapor deposition SP) と呼ぶこともできる。

20

#### 【0105】

##### [平行平板型スパッタリング装置(PESP)]

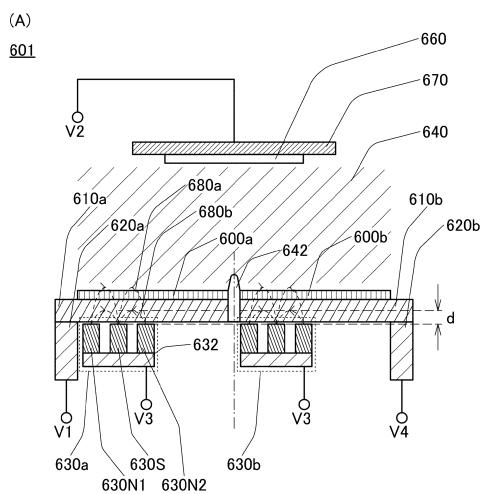

まず、平行平板型スパッタリング装置について、説明する。図6(A)は、平行平板型のスパッタリング装置である成膜室601の断面図である。図6(A)に示す成膜室601は、ターゲットホルダ620と、バッキングプレート610と、ターゲット600と、マグネットユニット630と、基板ホルダ670と、を有する。なお、ターゲット600は、バッキングプレート610上に配置される。また、バッキングプレート610は、ターゲットホルダ620上に配置される。また、マグネットユニット630は、バッキングプレート610を介してターゲット600下に配置される。また、基板ホルダ670は、ターゲット600と向かい合って配置される。なお、本明細書では、複数のマグネット(磁石)を組み合わせたものをマグネットユニットと呼ぶ。マグネットユニットは、カソード、カソードマグネット、磁気部材、磁気部品などと呼びかえることができる。マグネットユニット630は、マグネット630Nと、マグネット630Sと、マグネットホルダ632と、を有する。なお、マグネットユニット630において、マグネット630Nおよびマグネット630Sは、マグネットホルダ632上に配置される。また、マグネット630Nは、マグネット630Sと間隔を空けて配置される。なお、成膜室601に基板660を搬入する場合、基板660は基板ホルダ670上に配置される。

30

#### 【0106】

ターゲットホルダ620とバッキングプレート610とは、ネジ(ボルトなど)を用いて固定されており、等電位となる。また、ターゲットホルダ620は、バッキングプレート610を介してターゲット600を支持する機能を有する。

#### 【0107】

また、バッキングプレート610には、ターゲット600が固定される。例えば、インジウムなどの低融点金属を含むボンディング材によってバッキングプレート610とターゲット600とを固定することができる。

#### 【0108】

図6(A)に、マグネットユニット630によって形成される磁力線680aおよび磁力

40

50

線 6 8 0 b を示す。

**【 0 1 0 9 】**

磁力線 6 8 0 a は、ターゲット 6 0 0 の上面近傍における水平磁場を形成する磁力線の一つである。ターゲット 6 0 0 の上面近傍は、例えば、ターゲット 6 0 0 から垂直距離が 0 mm 以上 10 mm 以下、特に 0 mm 以上 5 mm 以下の領域である。

**【 0 1 1 0 】**

磁力線 6 8 0 b は、マグネットユニット 6 3 0 の上面から、垂直距離 d における水平磁場を形成する磁力線の一つである。垂直距離 d は、例えば、0 mm 以上 20 mm 以下または 5 mm 以上 15 mm 以下である。

**【 0 1 1 1 】**

このとき、強力なマグネット 6 3 0 N および強力なマグネット 6 3 0 S を用いることで、基板 6 6 0 の上面近傍においても強い磁場を発生させることができる。具体的には、基板 6 6 0 の上面における水平磁場の磁束密度を 10 G 以上 100 G 以下、好ましくは 15 G 以上 60 G 以下、さらに好ましくは 20 G 以上 40 G 以下とすることができます。

10

**【 0 1 1 2 】**

なお、水平磁場の磁束密度の測定は、垂直磁場の磁束密度が 0 G のときの値を測定すればよい。

**【 0 1 1 3 】**

成膜室 6 0 1 における磁場の磁束密度を上述の範囲とすることで、密度が高く、結晶性の高い酸化物を成膜することができる。また、得られる酸化物は、複数種の結晶相を含むことが少なく、ほとんど単一の結晶相を含む酸化物となる。

20

**【 0 1 1 4 】**

図 6 (B) に、マグネットユニット 6 3 0 の上面図を示す。マグネットユニット 6 3 0 は、円形または略円形のマグネット 6 3 0 N と、円形または略円形のマグネット 6 3 0 S と、がマグネットホルダ 6 3 2 に固定されている。そして、マグネットユニット 6 3 0 を、マグネットユニット 6 3 0 の上面における中央または略中央の法線ベクトルを回転軸として回転させることができる。例えば、マグネットユニット 6 3 0 を、0.1 Hz 以上 1 kHz 以下のビート (リズム、拍子、パルス、周波、周期またはサイクルなどと言い換えてよい。) で回転させればよい。

**【 0 1 1 5 】**

30

したがって、ターゲット 6 0 0 上の磁場の強い領域は、マグネットユニット 6 3 0 の回転とともに変化する。磁場の強い領域は高密度プラズマ領域となるため、その近傍においてターゲット 6 0 0 のスペッタリング現象が起こりやすい。例えば、磁場の強い領域が特定の箇所となる場合、ターゲット 6 0 0 の特定の領域のみが使用されることになる。一方、図 6 (B) に示すようにマグネットユニット 6 3 0 を回転させることで、ターゲット 6 0 0 と基板 6 6 0 との間に、プラズマ 6 4 0 が生じるため、ターゲット 6 0 0 を均一に使用することができる。また、マグネットユニット 6 3 0 を回転させることによって、均一な厚さおよび均一な質を有する膜を成膜することができる。

**【 0 1 1 6 】**

また、マグネットユニット 6 3 0 を回転させることにより、基板 6 6 0 の上面における磁力線の向きも変化させることができる。

40

**【 0 1 1 7 】**

なお、ここではマグネットユニット 6 3 0 を回転させる例を示したが、本発明の一態様はこれに限定されるものではない。例えば、マグネットユニット 6 3 0 を上下または / および左右に揺動させても構わない。例えば、マグネットユニット 6 3 0 を、0.1 Hz 以上 1 kHz 以下のビートで揺動させればよい。または、ターゲット 6 0 0 を回転または移動させても構わない。例えば、ターゲット 6 0 0 を、0.1 Hz 以上 1 kHz 以下のビートで回転または移動させればよい。または、基板 6 6 0 を回転させることで、相対的に基板 6 6 0 の上面における磁力線の向きを変化させても構わない。または、これらを組み合わせても構わない。

50

**【0118】**

成膜室601は、バッキングプレート610の内部または下部などに水路を有してもよい。そして、水路に流体（空気、窒素、希ガス、水、オイルなど）を流すことで、スパッタ時にターゲット600の温度の上昇による放電異常や、部材の変形による成膜室601の損傷などを抑制することができる。このとき、バッキングプレート610とターゲット600とをボンディング材を介して密着させると、冷却性能が高まるため好ましい。

**【0119】**

なお、ターゲットホルダ620とバッキングプレート610との間にガスケットを有すると、成膜室601内に外部や水路などから不純物が混入しにくくなるため好ましい。

**【0120】**

マグネットユニット630において、マグネット630Nとマグネット630Sとは、それぞれターゲット600側に異なる極を向けて配置されている。ここでは、マグネット630Nをターゲット600側がN極となるように配置し、マグネット630Sをターゲット600側がS極となるように配置する場合について説明する。ただし、マグネットユニット630におけるマグネットおよび極の配置は、この配置に限定されるものではない。また、図6(A)の配置に限定されるものでもない。

**【0121】**

成膜時、ターゲットホルダ620に接続する端子V1に印加される電位V1は、例えば、基板ホルダ670に接続する端子V2に印加される電位V2よりも低い電位である。また、基板ホルダ670に接続する端子V2に印加される電位V2は、例えば、接地電位である。また、マグネットホルダ632に接続する端子V3に印加される電位V3は、例えば、接地電位である。なお、端子V1、端子V2および端子V3に印加される電位は上記の電位に限定されない。また、ターゲットホルダ620、基板ホルダ670、マグネットホルダ632の全てに電位が印加されなくても構わない。例えば、基板ホルダ670が電気的に浮いていても構わない。なお、図6(A)では、ターゲットホルダ620に接続する端子V1に電位V1を印加する、いわゆるDCスパッタリング法の例を示したが、本発明の一態様は、これに限定されない。例えば、ターゲットホルダ620に、周波数が13.56MHzまたは27.12MHzなどの高周波電源を接続する、いわゆるRFスパッタリング法を用いても構わない。

**【0122】**

また、図6(A)では、バッキングプレート610およびターゲットホルダ620と、マグネットユニット630およびマグネットホルダ632と、が電気的に接続されない例を示したが、これに限定されない。例えば、バッキングプレート610およびターゲットホルダ620と、マグネットユニット630およびマグネットホルダ632と、が電気的に接続されており、等電位となっていても構わない。

**【0123】**

また、得られる酸化物の結晶性をさらに高めるために、基板660の温度を高くしても構わない。基板660の温度を高くすることで、基板660の上面におけるスパッタ粒子のマイグレーションを助長させることができる。したがって、より密度が高く、より結晶性の高い酸化物を成膜することができる。なお、基板660の温度は、例えば、100以上450以下、好ましくは150以上400以下、さらに好ましくは170以上350以下とすればよい。

**【0124】**

また、成膜ガス中の酸素分圧が高すぎると、複数種の結晶相を含む酸化物が成膜されやすいため、成膜ガスはアルゴンなどの希ガス（ほかにヘリウム、ネオン、クリプトン、キセノンなど）と酸素との混合ガスを用いると好ましい。例えば、全体に占める酸素の割合を50体積%未満、好ましくは33体積%以下、さらに好ましくは20体積%以下、より好ましくは15体積%以下とすればよい。

**【0125】**

また、ターゲット600と基板660との垂直距離を、10mm以上600mm以下、好

10

20

30

40

50

ましくは20mm以上400mm以下、さらに好ましくは30mm以上200mm以下、より好ましくは40mm以上100mm以下とする。ターゲット600と基板660との垂直距離を上述の範囲まで近くすることで、スパッタ粒子が、基板660に到達するまでの間におけるエネルギーの低下を抑制できる場合がある。また、ターゲット600と基板660との垂直距離を上述の範囲まで遠くすることで、スパッタ粒子の基板660への入射方向を垂直に近づけることができるため、スパッタ粒子の衝突による基板660へのダメージを小さくすることができる場合がある。

#### 【0126】

図7(A)に、図6(A)とは異なる成膜室の例を示す。

#### 【0127】

図7(A)に示す成膜室601は、ターゲットホルダ620aと、ターゲットホルダ620bと、バッキングプレート610aと、バッキングプレート610bと、ターゲット600aと、ターゲット600bと、マグネットユニット630aと、マグネットユニット630bと、部材642と、基板ホルダ670と、を有する。なお、ターゲット600aは、バッキングプレート610a上に配置される。また、バッキングプレート610aは、ターゲットホルダ620a上に配置される。また、マグネットユニット630aは、バッキングプレート610aを介してターゲット600a下に配置される。また、ターゲット600bは、バッキングプレート610b上に配置される。また、バッキングプレート610bは、ターゲットホルダ620b上に配置される。また、マグネットユニット630bは、バッキングプレート610bを介してターゲット600b下に配置される。

10

#### 【0128】

マグネットユニット630aは、マグネット630N1と、マグネット630N2と、マグネット630Sと、マグネットホルダ632と、を有する。なお、マグネットユニット630aにおいて、マグネット630N1、マグネット630N2およびマグネット630Sは、マグネットホルダ632上に配置される。また、マグネット630N1およびマグネット630N2は、マグネット630Sと間隔を空けて配置される。なお、マグネットユニット630bは、マグネットユニット630aと同様の構造を有する。なお、成膜室601に基板660を搬入する場合、基板660は基板ホルダ670上に配置される。

#### 【0129】

ターゲット600a、バッキングプレート610aおよびターゲットホルダ620aと、ターゲット600b、バッキングプレート610bおよびターゲットホルダ620bとは、部材642によって離間されている。なお、部材642は絶縁体であることが好ましい。ただし、部材642が導電体または半導体であっても構わない。また、部材642が、導電体または半導体の表面を絶縁体で覆ったものであっても構わない。

30

#### 【0130】

ターゲットホルダ620aとバッキングプレート610aとは、ネジ(ボルトなど)を用いて固定されており、等電位となる。また、ターゲットホルダ620aは、バッキングプレート610aを介してターゲット600aを支持する機能を有する。また、ターゲットホルダ620bとバッキングプレート610bとは、ネジ(ボルトなど)を用いて固定されており、等電位となる。また、ターゲットホルダ620bは、バッキングプレート610bを介してターゲット600bを支持する機能を有する。

40

#### 【0131】

バッキングプレート610aは、ターゲット600aを固定する機能を有する。また、バッキングプレート610bは、ターゲット600bを固定する機能を有する。

#### 【0132】

図7(A)に、マグネットユニット630aによって形成される磁力線680aおよび磁力線680bを示す。

#### 【0133】

磁力線680aは、ターゲット600aの上面近傍における水平磁場を形成する磁力線の一つである。ターゲット600aの上面近傍は、例えば、ターゲット600aから垂直距

50

離が 0 mm 以上 10 mm 以下、特に 0 mm 以上 5 mm 以下の領域である。

**【 0 1 3 4 】**

磁力線 630b は、マグネットユニット 630a の上面から、垂直距離 d における水平磁場を形成する磁力線の一つである。垂直距離 d は、例えば、0 mm 以上 20 mm 以下または 5 mm 以上 15 mm 以下である。

**【 0 1 3 5 】**

このとき、強力なマグネット 630N1、強力なマグネット 630N2 および強力なマグネット 630S を用いることで、基板 660 の上面近傍においても強い磁場を発生させることができる。具体的には、基板 660 の上面における水平磁場の磁束密度を 10 G 以上 100 G 以下、好ましくは 15 G 以上 60 G 以下、さらに好ましくは 20 G 以上 40 G 以下とすることができます。10

**【 0 1 3 6 】**

成膜室 601 における磁場の磁束密度を上述の範囲とすることで、密度が高く、結晶性の高い酸化物を成膜することができる。また、得られる酸化物は、複数種の結晶相を含むことが少なく、ほとんど単一の結晶相を含む酸化物となる。

**【 0 1 3 7 】**

なお、マグネットユニット 630b もマグネットユニット 630a と同様の磁力線が形成される。

**【 0 1 3 8 】**

図 7 (B) に、マグネットユニット 630a およびマグネットユニット 630b の上面図を示す。マグネットユニット 630a は、長方形または略長方形のマグネット 630N1 と、長方形または略長方形のマグネット 630N2 と、長方形または略長方形のマグネット 630S と、がマグネットホルダ 632 に固定されていることわかる。そして、マグネットユニット 630a を、図 7 (B) に示すように左右に揺動させることができる。例えば、マグネットユニット 630a を、0.1 Hz 以上 1 kHz 以下のビートで揺動させればよい。20

**【 0 1 3 9 】**

したがって、ターゲット 600a 上の磁場の強い領域は、マグネットユニット 630a の揺動とともに変化する。磁場の強い領域は高密度プラズマ領域となるため、その近傍においてターゲット 600a のスパッタリング現象が起こりやすい。例えば、磁場の強い領域が特定の箇所となる場合、ターゲット 600a の特定の領域のみが使用されることになる。一方、図 7 (B) に示すようにマグネットユニット 630a を揺動させることで、ターゲット 600a と基板 660 との間に、プラズマ 640 が生じるため、ターゲット 600a を均一に使用することができる。また、マグネットユニット 630a を揺動させることによって、均一な厚さ、質を有する膜を成膜することができる。30

**【 0 1 4 0 】**

また、マグネットユニット 630a を揺動させることにより、基板 660 の上面における磁力線の状態も変化させることができる。これは、マグネットユニット 630b においても同様である。

**【 0 1 4 1 】**

なお、ここではマグネットユニット 630a およびマグネットユニット 630b を揺動させる例を示したが、本発明の一態様はこれに限定されるものではない。例えば、マグネットユニット 630a およびマグネットユニット 630b を回転させても構わない。例えば、マグネットユニット 630a およびマグネットユニット 630b を、0.1 Hz 以上 1 kHz 以下のビートで回転させればよい。または、ターゲット 600 を回転または移動させても構わない。例えば、ターゲット 600 を、0.1 Hz 以上 1 kHz 以下のビートで回転または移動させればよい。または、基板 660 を回転させることで、相対的に基板 660 の上面における磁力線の状態を変化させることができる。または、これらを組み合わせても構わない。40

**【 0 1 4 2 】**

成膜室 601 は、バッキングプレート 610a およびバッキングプレート 610b の内部または下部などに水路を有してもよい。そして、水路に流体（空気、窒素、希ガス、水、オイルなど）を流すことで、スパッタ時にターゲット 600a およびターゲット 600b の温度の上昇による放電異常や、部材の変形による成膜室 601 の損傷などを抑制することができる。このとき、バッキングプレート 610a とターゲット 600a とをボンディング材を介して密着させると、冷却性能が高まるため好ましい。また、バッキングプレート 610b とターゲット 600b とをボンディング材を介して密着させると、冷却性能が高まるため好ましい。

#### 【0143】

なお、ターゲットホルダ 620a とバッキングプレート 610aとの間にガスケットを有すると、成膜室 601 内に外部や水路などから不純物が混入しにくくなるため好ましい。

10 また、ターゲットホルダ 620b とバッキングプレート 610b との間にガスケットを有すると、成膜室 601 内に外部や水路などから不純物が混入しにくくなるため好ましい。

#### 【0144】

マグネットユニット 630aにおいて、マグネット 630N1 およびマグネット 630N2 とマグネット 630S とはそれぞれターゲット 600a 側に異なる極を向けて配置されている。ここでは、マグネット 630N1 およびマグネット 630N2 をターゲット 600a 側が N 極となるように配置し、マグネット 630S をターゲット 600a 側が S 極となるように配置する場合について説明する。ただし、マグネットユニット 630a におけるマグネットおよび極の配置は、この配置に限定されるものではない。また、図 7 (A) の配置に限定されるものでもない。これは、マグネットユニット 630b についても同様である。

20

#### 【0145】

成膜時、ターゲットホルダ 620a に接続する端子 V1 に印加される電位と、ターゲットホルダ 620b に接続する端子 V4 に印加される電位は、交互に高低が入れ替わってもよい。また、基板ホルダ 670 に接続する端子 V2 に印加される電位は、例えば、接地電位である。また、マグネットホルダ 632 に接続する端子 V3 に印加される電位は、例えば、接地電位である。なお、端子 V1、端子 V2、端子 V3 および端子 V4 に印加される電位は上記の電位に限定されない。また、ターゲットホルダ 620a、ターゲットホルダ 620b、基板ホルダ 670、マグネットホルダ 632 の全てに電位が印加されなくても構わない。例えば、基板ホルダ 670 が電気的に浮いていても構わない。なお、図 7 (A) では、ターゲットホルダ 620a に接続する端子 V1 に印加される電位と、ターゲットホルダ 620b に接続する端子 V4 に印加される電位は、交互に高低が入れ替わる、いわゆる A C スパッタリング法の例を示したが、本発明の一態様は、これに限定されない。

30

#### 【0146】

また、図 7 (A) では、バッキングプレート 610a およびターゲットホルダ 620a と、マグネットユニット 630a およびマグネットホルダ 632 と、は電気的に接続されない例を示したが、これに限定されない。例えば、バッキングプレート 610a およびターゲットホルダ 620a と、マグネットユニット 630a およびマグネットホルダ 632 と、が電気的に接続されており、等電位となっていても構わない。また、バッキングプレート 610b およびターゲットホルダ 620b と、マグネットユニット 630b およびマグネットホルダ 632 と、は電気的に接続されない例を示したが、これに限定されない。例えば、バッキングプレート 610b およびターゲットホルダ 620b と、マグネットユニット 630b およびマグネットホルダ 632 と、が電気的に接続されており、等電位となっていても構わない。

40

#### 【0147】

また、得られる酸化物の結晶性をさらに高めるために、基板 660 の温度を高くしても構わない。基板 660 の温度を高くすることで、基板 660 の上面におけるスパッタ粒子のマイグレーションを助長させることができる。したがって、より密度が高く、より結晶性の高い酸化物を成膜することができる。なお、基板 660 の温度は、例えば、100 以

50

上 450 以下、好ましくは 150 以上 400 以下、さらに好ましくは 170 以上

350 以下とすればよい。

#### 【0148】

また、成膜ガス中の酸素分圧が高すぎると、複数種の結晶相を含む酸化物が成膜されやすいため、成膜ガスはアルゴンなどの希ガス（ほかにヘリウム、ネオン、クリプトン、キセノンなど）と酸素との混合ガスを用いると好ましい。例えば、全体に占める酸素の割合を 50 体積%未満、好ましくは 33 体積%以下、さらに好ましくは 20 体積%以下、より好ましくは 15 体積%以下とすればよい。

#### 【0149】

また、ターゲット 600a と基板 660 との垂直距離を、10 mm 以上 600 mm 以下、

好ましくは 20 mm 以上 400 mm 以下、さらに好ましくは 30 mm 以上 200 mm 以下

、より好ましくは 40 mm 以上 100 mm 以下とする。ターゲット 600a と基板 660

との垂直距離を上述の範囲まで近くすることで、スパッタ粒子が、基板 660 に到達する

までの間におけるエネルギーの低下を抑制できる場合がある。また、ターゲット 600a

と基板 660 との垂直距離を上述の範囲まで遠くすることで、スパッタ粒子の基板 660

への入射方向を垂直に近づけることができるため、スパッタ粒子の衝突による基板 660

へのダメージを小さくすることができる場合がある。

10

#### 【0150】

また、ターゲット 600b と基板 660 との垂直距離を、10 mm 以上 600 mm 以下、

好ましくは 20 mm 以上 400 mm 以下、さらに好ましくは 30 mm 以上 200 mm 以下

、より好ましくは 40 mm 以上 100 mm 以下とする。ターゲット 600b と基板 660

との垂直距離を上述の範囲まで近くすることで、スパッタ粒子が、基板 660 に到達する

までの間におけるエネルギーの低下を抑制できる場合がある。また、ターゲット 600b

と基板 660 との垂直距離を上述の範囲まで遠くすることで、スパッタ粒子の基板 660

への入射方向を垂直に近づけることができるため、スパッタ粒子の衝突による基板 660

へのダメージを小さくすることができる場合がある。

20

#### 【0151】

##### [対向ターゲット式スパッタリング装置（V D S P）]

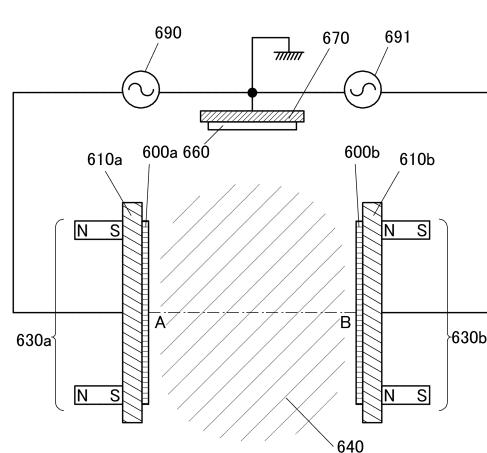

次に、対向ターゲット式スパッタリング装置について、説明する。図 8 (A) は、対向ターゲット式スパッタリング装置における成膜室の断面図である。図 8 (A) に示す成膜室は、ターゲット 600a およびターゲット 600b と、ターゲット 600a およびターゲット 600b をそれぞれ保持するバッキングプレート 610a およびバッキングプレート 610b と、バッキングプレート 610a およびバッキングプレート 610b を介してターゲット 600a およびターゲット 600b の背面にそれぞれ配置されるマグネットユニット 630a およびマグネットユニット 630b と、を有する。また、基板ホルダ 670 は、ターゲット 600a およびターゲット 600b の間に配置される。基板ホルダ 670 は、ターゲット 600a とターゲット 600b とが向かい合っている間の領域（ターゲット間領域ともいう。）の上側に配置される。なお、成膜室に基板 660 を搬入したのち、基板 660 は基板ホルダ 670 に固定される。

30

#### 【0152】

また、図 8 (A) に示すように、基板ホルダ 670 は、ターゲット間領域の上側に配置されるが、下側に配置されても構わない。また、下側および上側に配置されても構わない。下側および上側に基板ホルダ 670 を配置することにより、二以上の基板を同時に成膜することができるため、生産性を高めることができる。

40

#### 【0153】

また、図 8 (A) に示すように、バッキングプレート 610a およびバッキングプレート 610b には、電位を印加するための電源 690 および電源 691 が接続されている。バッキングプレート 610a に印加する電位と、バッキングプレート 610b に印加する電位の高低が交互に入れ替わる、いわゆる A C 電源を用いると好ましい。また、図 8 (A) に示す電源 690 および電源 691 は A C 電源を用いた例を示しているが、これに限られ

50

ない。例えば、電源 690 および電源 691 として R F 電源、D C 電源などを用いてもよい。または、電源 690 と電源 691 とで、異なる種類の電源を用いてもよい。

#### 【0154】

また、基板ホルダ 670 は GND に接続されていることが好ましい。また、基板ホルダ 670 はフローティングの状態であってもよい。

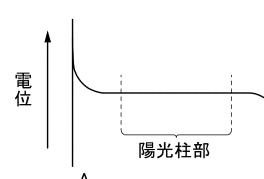

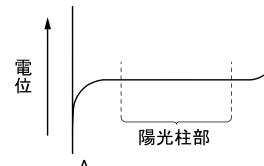

#### 【0155】

図 8 (B) および図 8 (C) は、図 8 (A) の一点鎖線 A - B 間におけるプラズマ 640 の電位分布を示している。図 8 (B) に示す電位分布は、バッキングプレート 610a に高電位を印加し、バッキングプレート 610b に低電位を印加した状態を示す。即ち、ターゲット 600b に向けて陽イオンが加速される。図 8 (C) に示す電位分布は、バッキングプレート 610a に低電位を印加し、バッキングプレート 610b に高電位を印加した状態を示す。即ち、ターゲット 600a に向けて陽イオンが加速される。図 8 (B) と、図 8 (C) との状態を交互に入れ替わるようにして成膜することができる。

10

#### 【0156】

図 8 (A) に示す構成は、ターゲット 600a とターゲット 600b とが平行に向かい合って配置されている。また、マグネットユニット 630a とマグネットユニット 630b とが、マグネットの異なる極を向かい合わせるように配置されている。このとき、磁力線は、マグネットユニット 630b からマグネットユニット 630a に向かう。そのため、成膜時には、マグネットユニット 630a とマグネットユニット 630b とで形成される磁場にプラズマ 640 が閉じ込められる。よって、基板ホルダ 670 および基板 660 は、プラズマ 640 の外側に位置する。基板 660 がプラズマ 640 の高電界領域に曝されないため、プラズマ 640 による損傷を低減させることができる。

20

#### 【0157】

対向ターゲット式スパッタリング装置は、高真空であってもプラズマを安定に生成することができる。例えば、0.005Pa 以上 0.09Pa 以下でも成膜が可能である。そのため、成膜時に混入する不純物の濃度を低減することができる。

#### 【0158】

対向ターゲット式スパッタリング装置を用いることによって、高真空での成膜が可能となるため、またプラズマによる損傷の少ない成膜が可能となるため、基板 660 の温度が低い場合でも結晶性の高い膜を成膜することができる。例えば、基板 660 の温度が、10 以上 100 未満であっても結晶性の高い膜を成膜することができる。

30

#### 【0159】

図 9 (A) に示す構成は、ターゲット 600a とターゲット 600b とが平行ではなく、傾いた状態で向かい合って (V 字状に) 配置されている点が図 8 (A) に示した構成と異なる。よって、ターゲットの配置以外については、図 8 (A) の説明を参照する。また、マグネットユニット 630a とマグネットユニット 630b とが異なる極が向かい合うように配置されている。基板ホルダ 670 および基板 660 は、ターゲット間領域の上に配置される。ターゲット 600a およびターゲット 600b を、図 9 (A) に示すような配置とすることで、基板 660 に到達するスパッタ粒子の割合が高くなるため、堆積速度を高くすることができる。

40

#### 【0160】

図 9 (B) に、対向ターゲット式スパッタリング装置の別の例を示す。

#### 【0161】

図 9 (B) は、対向ターゲット式スパッタリング装置における成膜室の断面模式図である。図 8 (A) に示す成膜室とは異なり、ターゲットシールド 622 およびターゲットシールド 623 が設けられている。また、バッキングプレート 610a およびバッキングプレート 610b と接続する電源 691 を有する。基板ホルダ 670 は、ターゲット間領域の上側に配置される。これにより、基板 660 がプラズマ 640 の高電界領域に曝されないため、プラズマ 640 による損傷を低減させることができる。

#### 【0162】

また、図9(B)に示すように、基板ホルダ670は、ターゲット間領域の上側に配置されるが、下側に配置されても構わない。また、下側および上側に配置されても構わない。下側および上側に基板ホルダ670を配置することにより、二以上の基板を同時に成膜することができるため、生産性を高めることができる。

#### 【0163】

また、図9(B)に示すように、ターゲットシールド622およびターゲットシールド623は、GNDに接続されている。つまり、電源691の電位が与えられたバッキングプレート610aおよびバッキングプレート610bと、GNDが与えられたターゲットシールド622およびターゲットシールド623と、の間に印加される電位差によって、プラズマ640が形成される。

10

#### 【0164】

以上に示した対向ターゲット式スパッタリング装置は、プラズマがターゲット間の磁場に閉じこめられるため、基板へのプラズマダメージを低減することができる。また、ターゲットの傾きによって、基板へのスパッタ粒子の入射角度を浅くすることができるため、堆積される膜の段差被覆性を高めることができる。また、高真空における成膜が可能であるため、膜に混入する不純物の濃度を低減することができる。

#### 【0165】

なお、成膜室に、平行平板型スパッタリング装置、イオンビームスパッタリング装置を適用しても構わない。

#### 【0166】

20

#### <成膜装置>

以下では、本発明の一態様に係るスパッタリング用ターゲットを設置することが可能な成膜室を有する成膜装置について説明する。

#### 【0167】

まずは、成膜時などに膜中に不純物の混入が少ない成膜装置の構成について図10および図11を用いて説明する。

#### 【0168】

図10は、枚葉式マルチチャンバーの成膜装置2700の上面図を模式的に示している。成膜装置2700は、基板を収容するカセットポート2761と、基板のアライメントを行うアライメントポート2762と、を備える大気側基板供給室2701と、大気側基板供給室2701から、基板を搬送する大気側基板搬送室2702と、基板の搬入を行い、かつ室内の圧力を大気圧から減圧、または減圧から大気圧へ切り替えるロードロック室2703aと、基板の搬出を行い、かつ室内の圧力を減圧から大気圧、または大気圧から減圧へ切り替えるアンロードロック室2703bと、真空中の基板の搬送を行う搬送室2704と、基板の加熱を行う基板加熱室2705と、ターゲットが配置され成膜を行う成膜室2706a、成膜室2706bおよび成膜室2706cと、を有する。なお、成膜室2706a、成膜室2706bおよび成膜室2706cは、上述した成膜室の構成を参照することができる。

30

#### 【0169】

また、大気側基板搬送室2702は、ロードロック室2703aおよびアンロードロック室2703bと接続され、ロードロック室2703aおよびアンロードロック室2703bは、搬送室2704と接続され、搬送室2704は、基板加熱室2705、成膜室2706a、成膜室2706bおよび成膜室2706cと接続する。

40

#### 【0170】

なお、各室の接続部にはゲートバルブ2764が設けられており、大気側基板供給室2701と、大気側基板搬送室2702を除き、各室を独立して真空状態に保持することができる。また、大気側基板搬送室2702および搬送室2704は、搬送口ポート2763を有し、基板を搬送することができる。

#### 【0171】

また、基板加熱室2705は、プラズマ処理室を兼ねると好ましい。成膜装置2700は

50

、処理と処理の間で基板を大気暴露することなく搬送することができるため、基板に不純物が吸着することを抑制できる。また、成膜や熱処理などの順番を自由に構築することができる。なお、搬送室、成膜室、ロードロック室、アンロードロック室および基板加熱室は、上述の数に限定されず、設置スペースやプロセス条件に合わせて、適宜最適な数を設けることができる。

#### 【0172】

次に、図10に示す成膜装置2700の一点鎖線X1-X2、一点鎖線Y1-Y2、および一点鎖線Y2-Y3に相当する断面を図11に示す。

#### 【0173】

図11(A)は、基板加熱室2705と、搬送室2704の断面を示しており、基板加熱室2705は、基板を収容することができる複数の加熱ステージ2765を有している。

10 なお、基板加熱室2705は、バルブを介して真空ポンプ2770と接続されている。真空ポンプ2770としては、例えば、ドライポンプ、およびメカニカルブースターポンプ等を用いることができる。

#### 【0174】

また、基板加熱室2705に用いることのできる加熱機構としては、例えば、抵抗発熱体などを用いて加熱する加熱機構としてもよい。または、加熱されたガスなどの媒体からの熱伝導または熱輻射によって、加熱する加熱機構としてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)、LRTA(Lamp Rapid Thermal Anneal)などのRTA(Rapid Thermal Anneal)を用いることができる。LRTAは、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する。GRTAは、高温のガスを用いて熱処理を行う。ガスとしては、不活性ガスが用いられる。

#### 【0175】

また、基板加熱室2705は、マスフローコントローラ2780を介して、精製機2781と接続される。なお、マスフローコントローラ2780および精製機2781は、ガス種の数だけ設けられるが、理解を容易にするため一つのみを示す。基板加熱室2705に導入されるガスは、露点が-80以下、好ましくは-100以下であるガスを用いることができ、例えば、酸素ガス、窒素ガス、および希ガス(アルゴンガスなど)を用いる。

20

#### 【0176】

搬送室2704は、搬送口ボット2763を有している。搬送口ボット2763は、各室へ基板を搬送することができる。また、搬送室2704は、バルブを介して真空ポンプ2770と、クライオポンプ2771と、接続されている。このような構成とすることで、搬送室2704は、大気圧から低真空または中真空(0.1から数百Pa程度)まで真空ポンプ2770を用いて排気され、バルブを切り替えて中真空から高真空または超高真空(0.1Paから $1 \times 10^{-7}$ Pa)まではクライオポンプ2771を用いて排気される。

#### 【0177】

また、例えば、クライオポンプ2771は、搬送室2704に対して2台以上並列に接続してもよい。このような構成とすることで、1台のクライオポンプがリジェネ中であっても、残りのクライオポンプを使って排気することが可能となる。なお、上述したリジェネとは、クライオポンプ内にため込まれた分子(または原子)を放出する処理をいう。クライオポンプは、分子(または原子)をため込みすぎると排気能力が低下してくるため、定期的にリジェネが行われる。

#### 【0178】

図11(B)は、成膜室2706bと、搬送室2704と、ロードロック室2703aの断面を示している。

#### 【0179】

10

20

30

40

50

ここで、図11(B)を用いて、成膜室(スパッタリング室)の詳細について説明する。図11(B)に示す成膜室2706bは、ターゲット2766aと、ターゲット2766bと、ターゲットシールド2767aと、ターゲットシールド2767bと、マグネットユニット2790aと、マグネットユニット2790bと、基板ホルダ2768と、電源2791と、を有する。図示しないが、ターゲット2766aおよびターゲット2766bは、それぞれバッキングプレートを介してターゲットホルダに固定される。また、ターゲット2766aおよびターゲット2766bには、電源2791が電気的に接続されている。マグネットユニット2790aおよびマグネットユニット2790bは、それぞれターゲット2766aおよびターゲット2766bの背面に配置される。ターゲットシールド2767aおよびターゲットシールド2767bは、それぞれターゲット2766aおよびターゲット2766bの端部を囲うように配置される。なお、ここでは基板ホルダ2768には、基板2769が支持されている。基板ホルダ2768は、可変部材2784を介して成膜室2706bに固定される。可変部材2784によって、基板ホルダ2768を移動させることができる。基板ホルダ2768は、ターゲット2766aとターゲット2766bとの間の領域(ターゲット間領域ともいう。)の上側に配置される。例えば、基板2769を支持した基板ホルダ2768をターゲット間領域の上側に配置することによって、プラズマによる損傷を低減させることができる。また、基板ホルダ2768は、図示しないが、基板2769を保持する基板保持機構や、基板2769を背面から加熱するヒーター等を備えていてもよい。

## 【0180】

10

また、図11(B)に示すように、基板ホルダ2768は、ターゲット間領域の上側に配置されるが、下側に配置されても構わない。また、下側および上側に配置されても構わない。下側および上側に基板ホルダ2768を配置することにより、二以上の基板を同時に成膜することができるため、生産性を高めることができる。

## 【0181】

20

また、ターゲットシールド2767によって、ターゲット2766からスパッタリングされる粒子が不要な領域に堆積することを抑制できる。ターゲットシールド2767は、累積されたスパッタ粒子が剥離しないように、加工することが望ましい。例えば、表面粗さを増加させるブラスト処理、またはターゲットシールド2767の表面に凹凸を設けてよい。

30

## 【0182】

また、成膜室2706bは、ガス加熱機構2782を介してマスフローコントローラ2780と接続され、ガス加熱機構2782はマスフローコントローラ2780を介して精製機2781と接続される。ガス加熱機構2782により、成膜室2706bに導入されるガスを40以上400以下に加熱することができる。なお、ガス加熱機構2782、マスフローコントローラ2780、および精製機2781は、ガス種の数だけ設けられるが、理解を容易にするため一つのみを示す。成膜室2706bに導入されるガスは、露点が-80以下、好ましくは-100以下であるガスを用いることができ、例えば、酸素ガス、窒素ガス、および希ガス(アルゴンガスなど)を用いる。

## 【0183】

40

なお、ガスの導入口の直前に精製機を設ける場合、精製機から成膜室2706bまでの配管の長さを10m以下、好ましくは5m以下、さらに好ましくは1m以下とする。配管の長さを10m以下、5m以下または1m以下とすることで、配管からの放出ガスの影響を長さに応じて低減できる。さらに、ガスの配管には、フッ化鉄、酸化アルミニウム、酸化クロムなどで内部が被覆された金属配管を用いるとよい。前述の配管は、例えばSUS316L-EP配管と比べ、不純物を含むガスの放出量が少なく、ガスへの不純物の入り込みを低減できる。また、配管の継手には、高性能超小型メタルガスケット継手(UPG継手)を用いるとよい。また、配管を全て金属で構成することで、樹脂等を用いた場合と比べ、生じる放出ガスおよび外部リークの影響を低減できて好ましい。

## 【0184】

50

また、成膜室 2706b は、バルブを介してターボ分子ポンプ 2772 および真空ポンプ 2770 と接続される。

【0185】

また、成膜室 2706b は、クライオトラップ 2751 が設けられる。

【0186】

クライオトラップ 2751 は、水などの比較的融点の高い分子（または原子）を吸着することができる機構である。ターボ分子ポンプ 2772 は大きいサイズの分子（または原子）を安定して排気し、かつメンテナンスの頻度が低いため、生産性に優れる一方、水素や水の排気能力が低い。そこで、水などに対する排気能力を高めるため、クライオトラップ 2751 が成膜室 2706b に接続された構成としている。クライオトラップ 2751 の冷凍機の温度は 100K 以下、好ましくは 80K 以下とする。また、クライオトラップ 2751 が複数の冷凍機を有する場合、冷凍機ごとに温度を変えると、効率的に排気することが可能となるため好ましい。例えば、1 段目の冷凍機の温度を 100K 以下とし、2 段目の冷凍機の温度を 20K 以下とすればよい。なお、クライオトラップに替えて、チタンサブリメーションポンプを用いることで、さらに高真空とすることができる場合がある。また、クライオポンプやターboro 分子ポンプに替えてイオンポンプを用いることでもさらに高真空とすることができる場合がある。10

【0187】

なお、成膜室 2706b の排気方法は、これに限定されず、先の搬送室 2704 に示す排気方法（クライオポンプと真空ポンプとの排気方法）と同様の構成としてもよい。もちろん、搬送室 2704 の排気方法を成膜室 2706b と同様の構成（ターboro 分子ポンプと真空ポンプとの排気方法）としてもよい。20

【0188】

なお、上述した搬送室 2704、基板加熱室 2705、および成膜室 2706b の背圧（全圧）、ならびに各気体分子（原子）の分圧は、以下の通りとすると好ましい。とくに、形成される膜中に不純物が混入され得る可能性があるので、成膜室 2706b の背圧、ならびに各気体分子（原子）の分圧には注意する必要がある。

【0189】

上述した各室の背圧（全圧）は、 $1 \times 10^{-4}$  Pa 以下、好ましくは  $3 \times 10^{-5}$  Pa 以下、さらに好ましくは  $1 \times 10^{-5}$  Pa 以下である。上述した各室の質量電荷比 (m/z) が 18 である気体分子（原子）の分圧は、 $3 \times 10^{-5}$  Pa 以下、好ましくは  $1 \times 10^{-5}$  Pa 以下、さらに好ましくは  $3 \times 10^{-6}$  Pa 以下である。また、上述した各室の m/z が 28 である気体分子（原子）の分圧は、 $3 \times 10^{-5}$  Pa 以下、好ましくは  $1 \times 10^{-5}$  Pa 以下、さらに好ましくは  $3 \times 10^{-6}$  Pa 以下である。また、上述した各室の m/z が 44 である気体分子（原子）の分圧は、 $3 \times 10^{-5}$  Pa 以下、好ましくは  $1 \times 10^{-5}$  Pa 以下、さらに好ましくは  $3 \times 10^{-6}$  Pa 以下である。30

【0190】

なお、真空チャンバー内の全圧および分圧は、質量分析計を用いて測定することができる。例えば、株式会社アルバック製四重極形質量分析計 (Q-massともいう。) Qulee CGM-051 を用いればよい。40

【0191】

また、上述した搬送室 2704、基板加熱室 2705、および成膜室 2706b は、外部リーケまたは内部リーケが少ない構成とすることが望ましい。

【0192】

例えば、上述した搬送室 2704、基板加熱室 2705、および成膜室 2706b のリーケートは、 $3 \times 10^{-6}$  Pa · m<sup>3</sup> / s 以下、好ましくは  $1 \times 10^{-6}$  Pa · m<sup>3</sup> / s 以下である。また、m/z が 18 である気体分子（原子）のリーケートが  $1 \times 10^{-7}$  Pa · m<sup>3</sup> / s 以下、好ましくは  $3 \times 10^{-8}$  Pa · m<sup>3</sup> / s 以下である。また、m/z が 28 である気体分子（原子）のリーケートが  $1 \times 10^{-5}$  Pa · m<sup>3</sup> / s 以下、好ましくは  $1 \times 10^{-6}$  Pa · m<sup>3</sup> / s 以下である。また、m/z が 44 である気体分子（原50

子) のリークレートが  $3 \times 10^{-6}$  Pa · m<sup>3</sup> / s 以下、好ましくは  $1 \times 10^{-6}$  Pa · m<sup>3</sup> / s 以下である。

#### 【0193】

なお、リークレートに関しては、前述の質量分析計を用いて測定した全圧および分圧から導出すればよい。

#### 【0194】

リークレートは、外部リークおよび内部リークに依存する。外部リークは、微小な穴やシール不良などによって真空系外から気体が流入することである。内部リークは、真空系内のバルブなどの仕切りからの漏れや内部の部材からの放出ガスに起因する。リークレートを上述の数値以下とするために、外部リークおよび内部リークの両面から対策をとる必要がある。

10

#### 【0195】

例えば、成膜室 2706b の開閉部分はメタルガスケットでシールするとよい。メタルガスケットは、フッ化鉄、酸化アルミニウム、または酸化クロムによって被覆された金属を用いると好ましい。メタルガスケットは O リングと比べ密着性が高く、外部リークを低減できる。また、フッ化鉄、酸化アルミニウム、酸化クロムなどによって被覆された金属の不動態を用いることで、メタルガスケットから放出される不純物を含む放出ガスが抑制され、内部リークを低減することができる。

#### 【0196】

また、成膜装置 2700 を構成する部材として、不純物を含む放出ガスの少ないアルミニウム、クロム、チタン、ジルコニウム、ニッケルまたはバナジウムを用いる。また、前述の部材を鉄、クロムおよびニッケルなどを含む合金に被覆して用いてもよい。鉄、クロムおよびニッケルなどを含む合金は、剛性があり、熱に強く、また加工に適している。ここで、表面積を小さくするために部材の表面凹凸を研磨などによって低減しておくと、放出ガスを低減できる。

20

#### 【0197】

または、前述の成膜装置 2700 の部材をフッ化鉄、酸化アルミニウム、酸化クロムなどで被覆してもよい。

#### 【0198】

成膜装置 2700 の部材は、極力金属のみで構成することが好ましく、例えば石英などで構成される覗き窓などを設置する場合も、放出ガスを抑制するために表面をフッ化鉄、酸化アルミニウム、酸化クロムなどで薄く被覆するとよい。

30

#### 【0199】

成膜室に存在する吸着物は、内壁などに吸着しているために成膜室の圧力に影響しないが、成膜室を排気した際のガス放出の原因となる。そのため、リークレートと排気速度に相關はないものの、排気能力の高いポンプを用いて、成膜室に存在する吸着物をできる限り脱離し、あらかじめ排気しておくことは重要である。なお、吸着物の脱離を促すために、成膜室をベーキングしてもよい。ベーキングすることで吸着物の脱離速度を 10 倍程度大きくすることができる。ベーキングは 100 以上 450 以下で行えばよい。このとき、不活性ガスを成膜室に導入しながら吸着物の除去を行うと、排気するだけでは脱離しつらい水などの脱離速度をさらに大きくすることができる。なお、導入する不活性ガスをベーキングの温度と同程度に加熱することで、吸着物の脱離速度をさらに高めることができる。ここで不活性ガスとして希ガスを用いると好ましい。また、成膜する膜種によっては不活性ガスの代わりに酸素などを用いても構わない。例えば、酸化物を成膜する場合は、主成分である酸素を用いた方が好ましい場合もある。なお、ベーキングは、ランプを用いて行うと好ましい。

40

#### 【0200】

または、加熱した希ガスなどの不活性ガスまたは酸素などを導入することで成膜室内の圧力を高め、一定時間経過後に再び成膜室を排気する処理を行うと好ましい。加熱したガスの導入により成膜室内の吸着物を脱離させることができ、成膜室内に存在する不純物を低

50

減することができる。なお、この処理は2回以上30回以下、好ましくは5回以上15回以下の範囲で繰り返し行うと効果的である。具体的には、温度が40以上400以下、好ましくは50以上200以下である不活性ガスまたは酸素などを導入することで成膜室内の圧力を0.1Pa以上10kPa以下、好ましくは1Pa以上1kPa以下、さらに好ましくは5Pa以上100Pa以下とし、圧力を保つ期間を1分以上300分以下、好ましくは5分以上120分以下とすればよい。その後、成膜室を5分以上300分以下、好ましくは10分以上120分以下の期間排気する。

#### 【0201】

また、ダミー成膜を行うことでも吸着物の脱離速度をさらに高めることができる。ダミー成膜とは、ダミー基板に対してスパッタリング法などによる成膜を行うことで、ダミー基板および成膜室内壁に膜を堆積させ、成膜室内の不純物および成膜室内壁の吸着物を膜中に閉じこめることをいう。ダミー基板は、放出ガスの少ない基板が好ましい。ダミー成膜を行うことで、後に成膜される膜中の不純物濃度を低減することができる。なお、ダミー成膜はベーキングと同時にあってもよい。

#### 【0202】

次に、図11(B)に示す搬送室2704、およびロードロック室2703aと、図11(C)に示す大気側基板搬送室2702、および大気側基板供給室2701の詳細について以下説明を行う。なお、図11(C)は、大気側基板搬送室2702、および大気側基板供給室2701の断面を示している。

#### 【0203】

図11(B)に示す搬送室2704については、図11(A)に示す搬送室2704の記載を参照する。

#### 【0204】

ロードロック室2703aは、基板受け渡しステージ2752を有する。ロードロック室2703aは、減圧状態から大気まで圧力を上昇させ、ロードロック室2703aの圧力が大気圧になった時に、大気側基板搬送室2702に設けられている搬送口ボット2763から基板受け渡しステージ2752に基板を受け取る。その後、ロードロック室2703aを真空引きし、減圧状態としたのち、搬送室2704に設けられている搬送口ボット2763が基板受け渡しステージ2752から基板を受け取る。

#### 【0205】

また、ロードロック室2703aは、バルブを介して真空ポンプ2770、およびクライオポンプ2771と接続されている。真空ポンプ2770、およびクライオポンプ2771の排気系の接続方法は、搬送室2704の接続方法を参考とすることで接続できるため、ここでの説明は省略する。なお、図10に示すアンロードロック室2703bは、ロードロック室2703aと同様の構成とすることができます。

#### 【0206】

大気側基板搬送室2702は、搬送口ボット2763を有する。搬送口ボット2763により、カセットポート2761とロードロック室2703aとの基板の受け渡しを行うことができる。また、大気側基板搬送室2702、および大気側基板供給室2701の上方にHEPAフィルタ(High Efficiency Particulate Air Filter)等のゴミまたはパーティクルを清浄化するための機構を設けてよい。

#### 【0207】

大気側基板供給室2701は、複数のカセットポート2761を有する。カセットポート2761は、複数の基板を収容することができる。

#### 【0208】

ターゲットは、表面温度が100以下、好ましくは50以下、さらに好ましくは室温程度(代表的には25)とする。大面積の基板に対応するスパッタリング装置では大面積のターゲットを用いることが多い。ところが、大面積に対応した大きさのターゲットをつなぎ目なく作製することは困難である。現実には複数のターゲットとなるべく隙間のな

10

20

30

40

50

いように並べて大きな形状としているが、どうしても僅かな隙間が生じてしまう。こうした僅かな隙間から、ターゲットの表面温度が高まることで亜鉛などが揮発し、徐々に隙間が広がっていくことがある。隙間が広がると、バッキングプレートや、バッキングプレートとターゲットとの接合に用いているボンディング材の金属がスパッタリングされたり、不純物濃度を高める要因となる。したがって、ターゲットは、十分に冷却されていることが好ましい。

#### 【0209】

具体的には、バッキングプレートとして、高い導電性および高い放熱性を有する金属（具体的には銅）を用いる。また、バッキングプレート内に水路を形成し、水路に十分な量の冷却水を流すことで、効率的にターゲットを冷却できる。

10

#### 【0210】

なお、ターゲットが亜鉛を含む場合、酸素ガス雰囲気で成膜することにより、プラズマダメージが軽減され、亜鉛の揮発が起こりにくい酸化物を得ることができる。

#### 【0211】

上述した成膜装置を用いることで、水素濃度が、二次イオン質量分析法（S I M S : Secondary Ion Mass Spectrometry）において、 $2 \times 10^0$  atoms / cm<sup>3</sup> 以下、好ましくは $5 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下、より好ましくは $1 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは $5 \times 10^{-8}$  atoms / cm<sup>3</sup> 以下である酸化物半導体を成膜することができる。

20

#### 【0212】

また、窒素濃度が、S I M Sにおいて、 $5 \times 10^{-9}$  atoms / cm<sup>3</sup> 未満、好ましくは $1 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下、より好ましくは $5 \times 10^{-8}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは $1 \times 10^{-8}$  atoms / cm<sup>3</sup> 以下である酸化物半導体を成膜することができる。

#### 【0213】

また、炭素濃度が、S I M Sにおいて、 $5 \times 10^{-9}$  atoms / cm<sup>3</sup> 未満、好ましくは $5 \times 10^{-8}$  atoms / cm<sup>3</sup> 以下、より好ましくは $1 \times 10^{-8}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは $5 \times 10^{-7}$  atoms / cm<sup>3</sup> 以下である酸化物半導体を成膜することができる。

30

#### 【0214】

不純物及び酸素欠損の少ない酸化物は、キャリア密度の低い酸化物である。具体的には、キャリア密度を $8 \times 10^{-11}$  / cm<sup>3</sup> 未満、好ましくは $1 \times 10^{-11}$  / cm<sup>3</sup> 未満、さらに好ましくは $1 \times 10^{-10}$  / cm<sup>3</sup> 未満であり、 $1 \times 10^{-9}$  / cm<sup>3</sup> 以上とすることができます。そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。C A A C - O Sは、不純物濃度が低く、欠陥準位密度が低い。即ち、安定な特性を有する酸化物であるといえる。

#### 【0215】

また、T D Sによるm/zが2（水素分子など）である気体分子（原子）、m/zが18である気体分子（原子）、m/zが28である気体分子（原子）及びm/zが44である気体分子（原子）の放出量が、それぞれ $1 \times 10^{-9}$  個 / cm<sup>3</sup> 以下、好ましくは $1 \times 10^{-8}$  個 / cm<sup>3</sup> 以下である酸化物半導体を成膜することができる。

40

#### 【0216】

以上の成膜装置を用いることで、酸化物への不純物の混入を抑制できる。さらには、以上の成膜装置を用いて、酸化物に接する膜を成膜することで、酸化物に接する膜から酸化物へ不純物が混入することを抑制できる。

#### 【0217】

以上、本実施の形態に示す構成は、他の実施の形態または他の実施例に示す構成と適宜、組み合わせて用いることができる。

#### 【0218】

（実施の形態3）

50

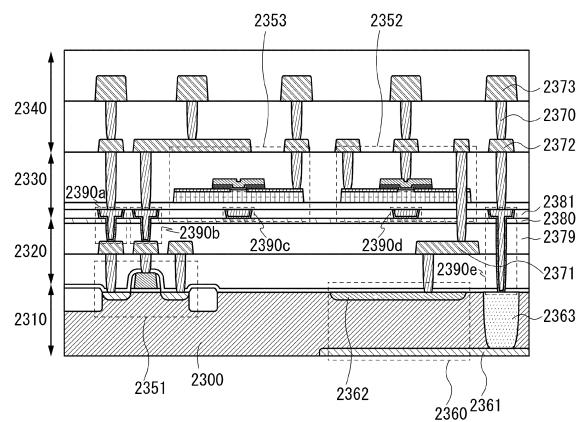

本実施の形態では、半導体装置の一形態を、図12乃至図22を用いて説明する。

【0219】

<トランジスタ構造1>

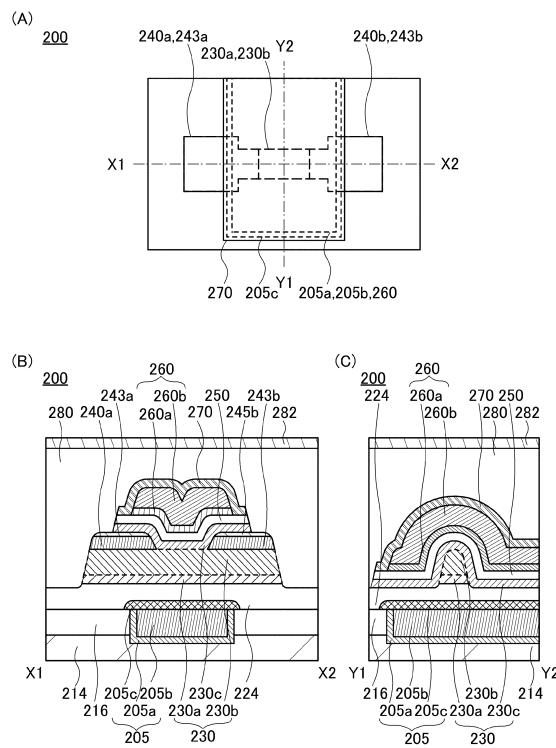

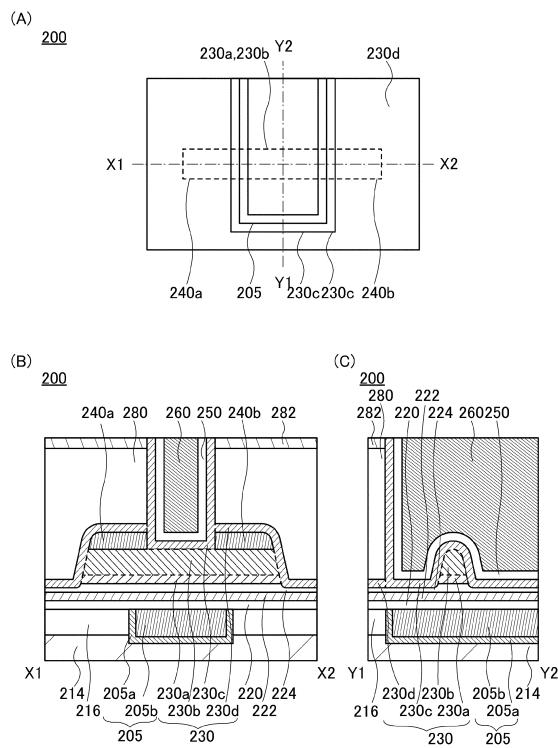

以下では、本発明の一態様に係るトランジスタの一例について説明する。図12(A)、図12(B)、および図12(C)は、本発明の一態様に係るトランジスタの上面図および断面図である。図12(A)は上面図であり、図12(B)は、図12(A)に示す一点鎖線X1-X2、図12(C)は、一点鎖線Y1-Y2に対応する断面図である。なお、図12(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

【0220】

トランジスタ200は、ゲート電極として機能する導電体205(導電体205a、および導電体205b)、および導電体260と、ゲート絶縁層として機能する絶縁体220、絶縁体222、絶縁体224、および絶縁体250と、チャネルが形成される領域を有する酸化物230(酸化物230a、酸化物230b、および酸化物230c)と、ソースまたはドレインの一方として機能する導電体240aと、ソースまたはドレインの他方として機能する導電体240bと、過剰酸素を有する絶縁体280と、バリア性を有する絶縁体282と、を有する。

【0221】

また、酸化物230は、酸化物230aと、酸化物230a上の酸化物230bと、酸化物230b上の酸化物230cと、を有する。なお、トランジスタ200をオンさせると、主として酸化物230bに電流が流れる(チャネルが形成される)。一方、酸化物230aおよび酸化物230cは、酸化物230bとの界面近傍(混合領域となっている場合もある)は電流が流れる場合があるものの、そのほかの領域は絶縁体として機能する場合がある。

【0222】

また、図12に示すように、酸化物230cは、酸化物230a、および酸化物230bの側面を覆うように設けることが好ましい。絶縁体280と、チャネルが形成される領域を有する酸化物230bとの間に、酸化物230cが介在することにより、絶縁体280から、水素、水、およびハロゲン等の不純物が、酸化物230bへ拡散することを抑制することができる。

【0223】

導電体205には、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウムから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜(窒化タンタル膜、窒化チタン膜、窒化モリブデン膜、窒化タンガステン膜)等である。特に、窒化タンタル膜などの金属窒化物膜は、水素または酸素に対するバリア性があり、また、酸化しにくい(耐酸化性が高い)ため、好ましい。又は、インジウム錫酸化物、酸化タンガステンを含むインジウム酸化物、酸化タンガステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの導電性材料を適用することもできる。

【0224】

例えば、導電体205aとして、水素に対するバリア性を有する導電体として、窒化タンタル等を用い、導電体205bとして、導電性が高いタンガステンを積層するとよい。当該組み合わせを用いることで、配線としての導電性を保持したまま、酸化物230への水素の拡散を抑制することができる。なお、図12では、導電体205a、および導電体205bの2層構造を示したが、当該構成に限定されず、単層でも3層以上の積層構造でもよい。例えば、バリア性を有する導電体と導電性が高い導電体との間に、バリア性を有する導電体、および導電性が高い導電体に対して密着性が高い導電体を形成してもよい。

【0225】

絶縁体224は、酸化シリコン膜や酸化窒化シリコン膜などの、酸素を含む絶縁体であることが好ましい。特に、絶縁体224としては、過剰酸素を含む(化学量論的組成よりも

10

20

30

40

50

過剰に酸素を含む)絶縁体を用いることが好ましい。このような過剰酸素を含む絶縁体を、トランジスタ200を構成する酸化物230に接して設けることにより、酸化物230中の酸素欠損を補償することができる。

#### 【0226】

また、絶縁体224が、過剰酸素領域を有する場合、絶縁体222は、酸素、水素、および水に対するバリア性を有することが好ましい。絶縁体222が、酸素に対するバリア性を有することで、過剰酸素領域の酸素は、トランジスタ300側へ拡散することなく、効率よく酸化物230へ供給することができる。また、導電体205が、絶縁体224が有する過剰酸素領域の酸素と反応することを抑制することができる。

#### 【0227】

絶縁体222は、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化ハフニウム、酸化タンタル、酸化ジルコニア、チタン酸ジルコニア酸鉛(PZT)、チタン酸ストロンチウム(SrTiO<sub>3</sub>)または(Ba, Sr)TiO<sub>3</sub>(BST)などの絶縁体を単層または積層で用いることが好ましい。特に、酸化アルミニウム、および酸化ハフニウム、などの、酸素や水素に対してバリア性のある絶縁膜を用いることが好ましい。このような材料を用いて形成した場合、酸化物230からの酸素の放出や、外部からの水素等の不純物の混入を防ぐ層として機能する。

#### 【0228】

または、これらの絶縁体に、例えば、酸化アルミニウム、酸化ビスマス、酸化ゲルマニウム、酸化ニオブ、酸化シリコン、酸化チタン、酸化タンゲステン、酸化イットリウム、酸化ジルコニアを添加してもよい。またはこれらの絶縁体を窒化処理しても良い。上記の絶縁体に酸化シリコン、酸化窒化シリコンまたは窒化シリコンを積層して用いてもよい。

#### 【0229】

なお、絶縁体220、絶縁体222、および絶縁体224が、2層以上の積層構造を有していてもよい。その場合、同じ材料からなる積層構造に限定されず、異なる材料からなる積層構造でもよい。

#### 【0230】

また、絶縁体220及び絶縁体224の間に、high-k材料を含む絶縁体222を有することで、特定の条件で絶縁体222が電子を捕獲し、しきい値電圧を増大させることができる。つまり、絶縁体222が負に帯電する場合がある。

#### 【0231】

例えば、絶縁体220、および絶縁体224に、酸化シリコンを用い、絶縁体222に、酸化ハフニウム、酸化アルミニウム、酸化タンタルのような電子捕獲準位の多い材料を用いた場合、半導体装置の使用温度、あるいは保管温度よりも高い温度(例えば、125以上450以下、代表的には150以上300以下)の下で、導電体205の電位をソース電極やドレイン電極の電位より高い状態を、10ミリ秒以上、代表的には1分以上維持することで、トランジスタ200を構成する酸化物から導電体205に向かって、電子が移動する。この時、移動する電子の一部が、絶縁体222の電子捕獲準位に捕獲される。

#### 【0232】

絶縁体222の電子捕獲準位に必要な量の電子を捕獲させたトランジスタは、しきい値電圧がプラス側にシフトする。なお、導電体205の電圧の制御によって電子の捕獲する量を制御することができ、それに伴ってしきい値電圧を制御することができる。当該構成を有することで、トランジスタ200は、ゲート電圧が0Vであっても非導通状態(オフ状態ともいう)であるノーマリーオフ型のトランジスタとなる。

#### 【0233】

また、電子を捕獲する処理は、トランジスタの作製過程におこなえばよい。例えば、トランジスタのソース導電体あるいはドレイン導電体に接続する導電体の形成後、あるいは、前工程(ウェハー処理)の終了後、あるいは、ウェハーダイシング工程後、パッケージ後等、工場出荷前のいずれかの段階で行うとよい。

10

20

30

40

50

## 【0234】

また、絶縁体220、絶縁体222、および絶縁体224の膜厚を適宜調整することで、しきい値電圧を制御することができる。例えば、絶縁体220、絶縁体222、および絶縁体224の合計膜厚が薄くすることで導電体205からの電圧が効率的にかかる為、消費電力が低いトランジスタを提供することができる。絶縁体220、絶縁体222、および絶縁体224の合計膜厚は、65nm以下、好ましくは20nm以下であることが好ましい。

## 【0235】

従って、非導通時のリーク電流の小さいトランジスタを提供することができる。また、安定した電気特性を有するトランジスタを提供することができる。または、オン電流の大きいトランジスタを提供することができる。または、サブスレッショルドスイング値の小さいトランジスタを提供することができる。または、信頼性の高いトランジスタを提供することができる。

10

## 【0236】

酸化物230a、酸化物230b、および酸化物230cは、In-M-Zn酸化物(MはAl、Ga、Y、またはSn)等の金属酸化物で形成される。また、酸化物230として、In-Ga酸化物、In-Zn酸化物を用いてもよい。

## 【0237】

なお、酸化物230bに用いる酸化物として、先の実施の形態で説明した酸化物半導体を用いることができる。

20

## 【0238】

また、酸化物230aと酸化物230b、酸化物230bと酸化物230cが、酸素以外に共通の元素を有する(主成分とする)ことで、欠陥準位密度が低い混合層を形成することができる。例えば、酸化物230bがIn-Ga-Zn酸化物の場合、酸化物230a、酸化物230cとして、In-Ga-Zn酸化物、Ga-Zn酸化物、酸化ガリウムなどを用いるとよい。

## 【0239】

このとき、キャリアの主たる経路は酸化物230bとなる。酸化物230aと酸化物230bとの界面、および酸化物230bと酸化物230cとの界面における欠陥準位密度を低くすることができるため、界面散乱によるキャリア伝導への影響が小さく、高いオン電流が得られる。

30

## 【0240】

トラップ準位に電子が捕獲されることで、捕獲された電子は固定電荷のように振る舞うため、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。酸化物230a、酸化物230cを設けることにより、トラップ準位を酸化物230bより遠ざけることができる。当該構成とすることで、トランジスタのしきい値電圧がプラス方向にシフトすることを防止することができる。

## 【0241】

酸化物230a、酸化物230cは、酸化物230bと比較して、導電率が十分に低い材料を用いる。このとき、酸化物230b、酸化物230bと酸化物230aとの界面、および酸化物230bと酸化物230cとの界面が、主にチャネル領域として機能する。

40

## 【0242】

例えば、酸化物230bに、図5の領域A2と、領域B2とが、複合体を形成している酸化物を用いる場合、酸化物230aおよび酸化物230cには、[M]/[In]が1以上、好ましくは2以上である酸化物を用いることが好ましい。また、酸化物230cとして、十分に高い絶縁性を得ることができる[M]/([Zn]+[In])が1以上である酸化物を用いることが好適である。

## 【0243】

絶縁体250は、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化ハフニウム、酸化タンタル、酸化ジルコニア、チタン酸ジルコン酸鉛

50

(P Z T)、チタン酸ストロンチウム(SrTiO<sub>3</sub>)または(Ba, Sr)TiO<sub>3</sub>(B S T)などの絶縁体を単層または積層で用いることができる。またはこれらの絶縁体に例えば酸化アルミニウム、酸化ビスマス、酸化ゲルマニウム、酸化ニオブ、酸化シリコン、酸化チタン、酸化タングステン、酸化イットリウム、酸化ジルコニアを添加してもよい。またはこれらの絶縁体を窒化処理しても良い。上記の絶縁体に酸化シリコン、酸化窒化シリコンまたは窒化シリコンを積層して用いてもよい。

#### 【0244】

また、絶縁体250は、絶縁体224と同様に、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁体を用いることが好ましい。このような過剰酸素を含む絶縁体を酸化物230に接して設けることにより、酸化物230中の酸素欠損を低減することができる。10

#### 【0245】

また、絶縁体250は、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム、窒化シリコンなどの、酸素や水素に対してバリア性のある絶縁膜を用いることができる。このような材料を用いて形成した場合、酸化物230からの酸素の放出や、外部からの水素等の不純物の混入を防ぐ層として機能する。

#### 【0246】

なお、絶縁体250は、絶縁体220、絶縁体222、および絶縁体224と同様の積層構造を有していてもよい。絶縁体250が、電子捕獲準位に必要な量の電子を捕獲させた絶縁体を有することで、トランジスタ200は、しきい値電圧をプラス側にシフトすることができる。当該構成を有することで、トランジスタ200は、ゲート電圧が0Vであっても非導通状態(オフ状態ともいう)であるノーマリーオフ型のトランジスタとなる。20

#### 【0247】

また、図12に示すトランジスタにおいて、酸化物230と導電体260の間に、絶縁体250の他にバリア膜を設けてもよい。もしくは、酸化物230cにバリア性があるものを用いてもよい。

#### 【0248】

例えば、過剰酸素を含む絶縁膜を酸化物230に接して設け、さらにバリア膜で包み込むことで、酸化物を化学量論比組成とほぼ一致するような状態、または化学量論的組成より酸素が多い過飽和の状態とすることができます。また、酸化物230への水素等の不純物の侵入を防ぐことができる。30

#### 【0249】

導電体240aと、および導電体240bは、一方がソース電極として機能し、他方がドレイン電極として機能する。

#### 【0250】

導電体240aと、導電体240bとは、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニア、モリブデン、銀、タンタル、またはタングステンなどの金属、またはこれを主成分とする合金を用いることができる。特に、窒化タンタル膜などの金属窒化物膜は、水素または酸素に対するバリア性があり、また、耐酸化性が高いため、好ましい。40

#### 【0251】

また、図では単層構造を示したが、2層以上の積層構造としてもよい。例えば、窒化タンタル膜とタングステン膜を積層するとよい。また、チタン膜とアルミニウム膜を積層するとよい。また、タングステン膜上にアルミニウム膜を積層する二層構造、銅-マグネシウム-アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、タングステン膜上に銅膜を積層する二層構造としてもよい。

#### 【0252】

また、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する50

三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。

#### 【0253】

また、ゲート電極として機能を有する導電体260は、例えばアルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクステンから選ばれた金属、または上述した金属を成分とする合金か、上述した金属を組み合わせた合金等を用いて形成することができる。特に、窒化タンタル膜などの金属窒化物膜は、水素または酸素に対するバリア性があり、また、耐酸化性が高いため、好ましい。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属を用いてもよい。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体、ニッケルシリサイド等のシリサイドを用いてもよい。また、図では単層構造を示したが、2層以上の積層構造としてもよい。

10

#### 【0254】

例えば、アルミニウム上にチタン膜を積層する二層構造とするとよい。また、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタンクステン膜を積層する二層構造、窒化タンタル膜または窒化タンクステン膜上にタンクステン膜を積層する二層構造としてもよい。

#### 【0255】

また、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タンクステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた一または複数の金属を組み合わせた合金膜、もしくは窒化膜を用いてもよい。

20

#### 【0256】

また、導電体260は、インジウム錫酸化物、酸化タンクステンを含むインジウム酸化物、酸化タンクステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属の積層構造とすることもできる。

#### 【0257】

30

続いて、トランジスタ200の上方には、絶縁体280、および絶縁体282を設ける。

#### 【0258】

絶縁体280には、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物を用いることが好ましい。つまり、絶縁体280には、化学量論的組成よりも酸素が過剰に存在する領域（以下、過剰酸素領域ともいう）が形成されていることが好ましい。特に、トランジスタ200に酸化物半導体を用いる場合、トランジスタ200近傍の層間膜などに、過剰酸素領域を有する絶縁体を設けることで、トランジスタ200の酸素欠損を低減することで、信頼性を向上させることができる。

#### 【0259】

40

過剰酸素領域を有する絶縁体として、具体的には、加熱により一部の酸素が脱離する酸化物材料を用いることが好ましい。加熱により酸素を脱離する酸化物とは、TDS分析にて、酸素原子に換算しての酸素の脱離量が $1.0 \times 10^{18}$  atoms/cm<sup>3</sup>以上、好ましくは $3.0 \times 10^{20}$  atoms/cm<sup>3</sup>以上である酸化物膜である。なお、上記TDS分析時における膜の表面温度としては100以上700以下、または100以上500以下の範囲が好ましい。

#### 【0260】

例えばこのような材料として、酸化シリコンまたは酸化窒化シリコンを含む材料を用いることが好ましい。または、金属酸化物を用いることもできる。なお、本明細書中において、酸化窒化シリコンとは、その組成として窒素よりも酸素の含有量が多い材料を指し、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多い材料を示す。

50

**【0261】**

また、トランジスタ200を覆う絶縁体280は、その下方の凹凸形状を被覆する平坦化膜として機能してもよい。

**【0262】**

絶縁体282は、例えば、酸化アルミニウム、および酸化ハフニウム、などの、酸素や水素に対してバリア性のある絶縁膜を用いることが好ましい。このような材料を用いて形成した場合、酸化物230からの酸素の放出や、外部からの水素等の不純物の混入を防ぐ層として機能する。

**【0263】**

上記構成を有することで、オン電流が大きい酸化物半導体を有するトランジスタを提供することができる。または、オフ電流が小さい酸化物半導体を有するトランジスタを提供することができる。または、上記構成を有するトランジスタを半導体装置に用いることで、半導体装置の電気特性の変動を抑制すると共に、信頼性を向上させることができる。または、消費電力が低減された半導体装置を提供することができる。10

**【0264】**

<トランジスタ構造2>

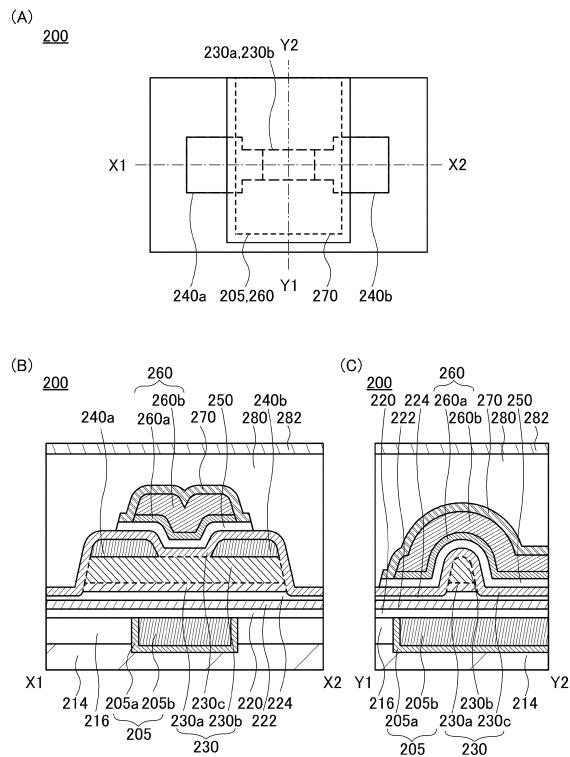

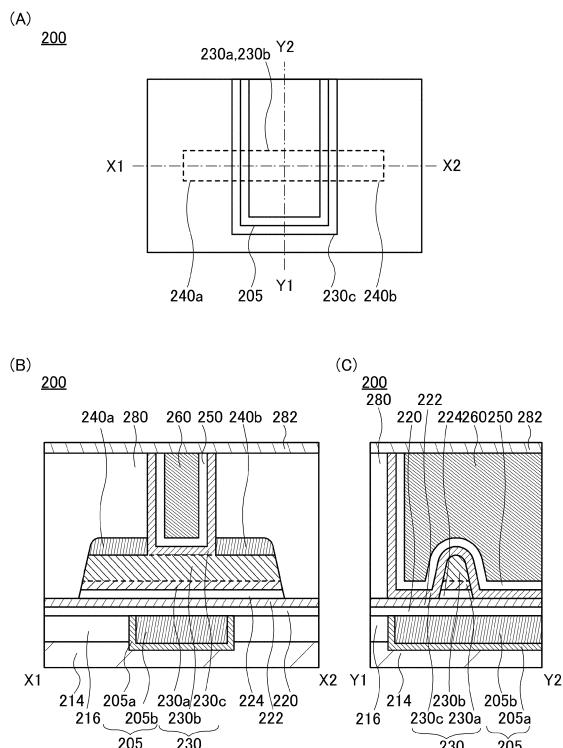

図13には、トランジスタ200に適応できる構造の一例を示す。図13(A)はトランジスタ200の上面を示す。なお、図の明瞭化のため、図13(A)において一部の膜は省略されている。また、図13(B)は、図13(A)に示す一点鎖線X1-X2に対応する断面図であり、図13(C)はY1-Y2に対応する断面図である。20

**【0265】**

なお、図13に示すトランジスタ200において、図12に示したトランジスタ200を構成する構造と同機能を有する構造には、同符号を付記する。

**【0266】**

図13に示す構造は、導電体260を、2層構造で設けている。例えば、導電体260aとして、In-Ga-Zn酸化物に代表される酸化物を用いることができる。In-Ga-Zn酸化物に代表される酸化物半導体は、窒素または水素が供給されることで、キャリア密度が高くなる。別言すると、酸化物導電体(Oxide Conductor)として機能する。そこで、導電体260bとして、金属窒化物を設けることで、酸化物半導体はキャリア密度が高くなるため、導電体260aはゲート電極として機能する。30

**【0267】**

導電体260aとして、In-Ga-Zn酸化物に代表される酸化物半導体を用いることができる。また、導電体260aとして、インジウム錫酸化物(Indium Tin Oxide:ITO)、酸化タンクス滕を含むインジウム酸化物、酸化タンクス滕を含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、シリコンを含むインジウム錫酸化物(Indium-Silicon Oxide:ITSOともいう)等の透光性を有する導電性材料を適用することもできる。

**【0268】**

導電体260bとして、金属窒化物を用いることで、金属窒化物中の構成元素(特に窒素)が導電体260aに拡散し低抵抗化する、また、導電体260bの成膜時のダメージ(例えば、スパッタリングダメージなど)により低抵抗化することができる。なお、導電体260bを、2層以上の積層構造としてもよい。例えば、金属窒化物上に、低抵抗の金属膜を積層することで、駆動電圧が小さなトランジスタを提供することができる。40

**【0269】**

また、導電体260aの形成方法としては、スパッタリング法を用い、形成時に酸素ガスを含む雰囲気で形成することが好ましい。形成時に酸素ガスを含む雰囲気で導電体260aを形成することで、絶縁体250中に、過剰酸素領域を形成することができる。なお、導電体260aの形成方法としては、スパッタリング法に限定されず、その他の方法、例えばALD法を用いてもよい。

**【0270】**

さらに、図13に示す構造は、導電体260を覆うように、絶縁体270を設ける。絶縁体280に酸素が脱離する酸化物材料を用いる場合、絶縁体270は、酸素に対してバリア性を有する物質を用いる。当該構成により、導電体260aの酸素欠損が補償されることで、キャリア密度が低下することを抑制し、また、導電体260bが、拡散した酸素により酸化することを防止することができる。

**【0271】**

例えば、絶縁体270には、酸化アルミニウムなどの金属酸化物を用いることができる。また絶縁体270は、導電体260の酸化を防止する程度の膜厚で設けられていればよい。

10

**【0272】**

また、図に示すように、絶縁体220、および絶縁体222を設けず、バリア性を有する導電体を用いて、導電体205cを設けてもよい。本構成とすることで、絶縁体224が過剰酸素領域を有する場合でも、導電体205bが、過剰酸素領域の酸素と反応し、酸化物を生成することを抑制することができる。

**【0273】**

また、導電体240a、および導電体240b上に、絶縁体243a、および絶縁体243bを設けてもよい。絶縁体243a、および絶縁体243bは、酸素に対してバリア性を有する物質を用いる。当該構成により、導電体240a、および導電体240bが、酸化物230cを成膜する際に、酸化することを抑制することができる。また、絶縁体280が有する過剰酸素領域の酸素が、導電体240a、および導電体240bと反応し、酸化することを防止することができる。

20

**【0274】**

絶縁体243a、および絶縁体243bには、例えば、金属酸化物を用いることができる。特に、酸化アルミニウム、酸化ハフニウム、酸化ガリウムなどの、酸素や水素に対してバリア性のある絶縁膜を用いることが好ましい。また、CVD法で形成した窒化シリコンを用いてもよい。

**【0275】**

従って、当該構成とすることで、導電体240a、導電体240b、導電体205、および導電体260の材料選択の幅を広げることができる。例えば、導電体205b、および導電体260bに、アルミニウムなどの耐酸化性が低い一方で導電性が高い材料を用いることができる。また、例えば、成膜、または加工がしやすい導電体を用いることができる。

30

**【0276】**

また、導電体205、および導電体260の酸化を抑制し、絶縁体224、および絶縁体280から、脱離した酸素を効率的に酸化物230へと供給することができる。また、導電体205、および導電体260に導電性が高い導電体を用いることで、消費電力が小さいトランジスタ200を提供することができる。

**【0277】**

<トランジスタ構造3>

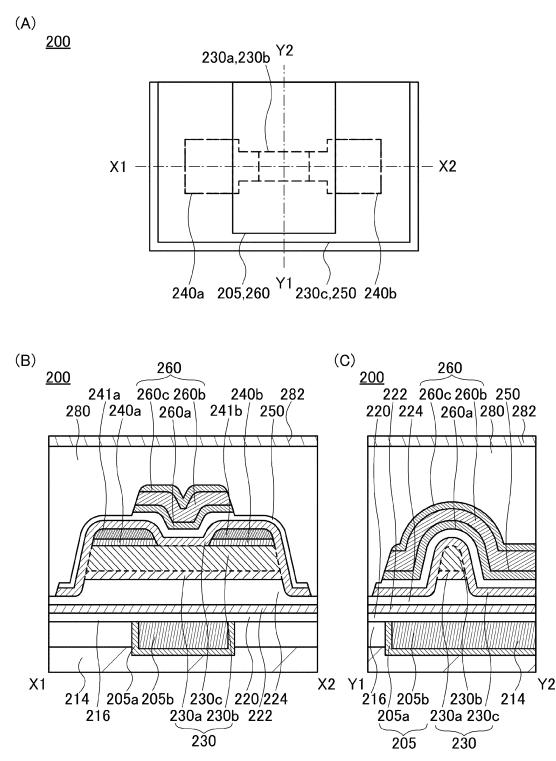

図14には、トランジスタ200に適応できる構造の一例を示す。図14(A)はトランジスタ200の上面を示す。なお、図の明瞭化のため、図14(A)において一部の膜は省略されている。また、図14(B)は、図14(A)に示す一点鎖線X1-X2に対応する断面図であり、図14(C)はY1-Y2に対応する断面図である。

40

**【0278】**

なお、図14に示すトランジスタ200において、図12に示したトランジスタ200を構成する構造と同機能を有する構造には、同符号を付記する。

**【0279】**

図14に示す構造は、導電体260を、2層構造で設けている。2層構造としては、同じ材料を積層して設けてもよい。例えば、導電体260aは、熱CVD法、MOCVD法ま

50

たは A L D 法を用いて形成する。特に、A L D 法を用いて形成することが好ましい。A L D 法等により形成することで、絶縁体 2 5 0 に対する成膜時のダメージを減らすことができる。また、A L D 法等により形成することで、被覆性の高い導電体 2 6 0 a を成膜することができる。従って、信頼性が高いトランジスタ 2 0 0 を提供することができる。

#### 【 0 2 8 0 】

続いて、導電体 2 6 0 b はスパッタリング法を用いて形成する。この時、絶縁体 2 5 0 上に、導電体 2 6 0 a を有することで、導電体 2 6 0 b の成膜時のダメージが、絶縁体 2 5 0 に影響することを抑制することができる。また、A L D 法と比較して、スパッタリング法は成膜速度が速いため、歩留まりが高く、生産性を向上させることができる。

#### 【 0 2 8 1 】

さらに、図 1 4 に示す構造は、導電体 2 6 0 を覆うように、絶縁体 2 7 0 を設ける。絶縁体 2 8 0 に酸素が脱離する酸化物材料を用いる場合、絶縁体 2 7 0 は、酸素に対してバリア性を有する物質を用いる。当該構成により、導電体 2 6 0 a の酸素欠損が補償されることで、キャリア密度が低下することを抑制し、また、導電体 2 6 0 b が、拡散した酸素により酸化することを防止することができる。

#### 【 0 2 8 2 】

例えば、絶縁体 2 7 0 には、酸化アルミニウムなどの金属酸化物を用いることができる。また絶縁体 2 7 0 は、導電体 2 6 0 の酸化を防止する程度の膜厚で設けられていればよい。

#### 【 0 2 8 3 】

##### <トランジスタ構造 4 >

図 1 5 には、トランジスタ 2 0 0 に適応できる構造の一例を示す。図 1 5 ( A ) はトランジスタ 2 0 0 の上面を示す。なお、図の明瞭化のため、図 1 5 ( A ) において一部の膜は省略されている。また、図 1 5 ( B ) は、図 1 5 ( A ) に示す一点鎖線 X 1 - X 2 に対応する断面図であり、図 1 5 ( C ) は Y 1 - Y 2 に対応する断面図である。

#### 【 0 2 8 4 】

なお、図 1 5 に示すトランジスタ 2 0 0 において、図 1 2 に示したトランジスタ 2 0 0 を構成する構造と同機能を有する構造には、同符号を付記する。

#### 【 0 2 8 5 】

図 1 5 に示す構造は、ゲート電極と機能する導電体 2 6 0 が、導電体 2 6 0 a 、導電体 2 6 0 b 、および導電体 2 6 0 c を有する。また、酸化物 2 3 0 c は、酸化物 2 3 0 b の側面を覆っていればよく、絶縁体 2 2 4 上で切断されていてもよい。

#### 【 0 2 8 6 】

図 1 5 に示す構造は、導電体 2 6 0 を、3 層構造で設けている。また、単層、2 層構造、または 4 層以上の積層構造としてもよい。なお、2 層構造、とする場合、は同じ材料を積層して設けててもよい。例えば、導電体 2 6 0 a は、熱 C V D 法、M O C V D 法または A L D 法を用いて形成する。特に、A L D 法を用いて形成することが好ましい。A L D 法等により形成することで、絶縁体 2 5 0 に対する成膜時のダメージを減らすことができる。また、A L D 法等により形成することで、被覆性の高い導電体 2 6 0 a を成膜することができる。従って、信頼性が高いトランジスタ 2 0 0 を提供することができる。

#### 【 0 2 8 7 】

続いて、導電体 2 6 0 b はスパッタリング法を用いて形成する。この時、絶縁体 2 5 0 上に、導電体 2 6 0 a を有することで、導電体 2 6 0 b の成膜時のダメージが、絶縁体 2 5 0 に影響することを抑制することができる。また、A L D 法と比較して、スパッタリング法は成膜速度が速いため、歩留まりが高く、生産性を向上させることができる。

#### 【 0 2 8 8 】

また、導電体 2 6 0 b は、タンタル、タンゲステン、銅、アルミニウムなどの導電性が高い材料を用いて形成する。さらに、導電体 2 6 0 b 上に形成する導電体 2 6 0 c は、窒化タンゲステンなどの耐酸化性が高い導電体を用いて形成することが好ましい。

#### 【 0 2 8 9 】

10

20

30

40

50

例えば、絶縁体 280 に酸素が脱離する酸化物材料を用いる場合、過剰酸素領域を有する絶縁体 280 と接する面積が大きい導電体 260c に耐酸化性が高い導電体を用いることで、過剰酸素領域から脱離される酸素が導電体 260 に吸収されることを抑制することができる。また、導電体 260 の酸化を抑制し、絶縁体 280 から、脱離した酸素を効率的に酸化物 230 へと供給することができる。また、導電体 260b に導電性が高い導電体を用いることで、消費電力が小さいトランジスタ 200 を提供することができる。

#### 【0290】

また、図 15 (C) に示すように、トランジスタ 200 のチャネル幅方向において、酸化物 230b が導電体 260 に覆われている。また、絶縁体 224 が凸部を有することによって、酸化物 230b の側面も導電体 260 で覆うことができる。例えば、絶縁体 224 の凸部の形状を調整することで、絶縁体 224 と酸化物 230c が接する領域において、導電体 260 の底面が、酸化物 230b の底面よりも、基板側となる構造となることが好みしい。つまり、トランジスタ 200 は、導電体 260 の電界によって、酸化物 230b を電気的に取り囲むことができる構造を有する。このように、導電体の電界によって、酸化物 230b を電気的に取り囲むトランジスタの構造を、surrounded channel (s-channel) 構造とよぶ。s-channel 構造のトランジスタ 200 は、酸化物 230b 全体 (バルク) にチャネルを形成することもできる。s-channel 構造では、トランジスタのドレイン電流を大きくすることができ、さらに大きいオン電流 (トランジスタがオン状態のときにソースとドレインの間に流れる電流) を得ることができる。また、導電体 260 の電界によって、酸化物 230b に形成されるチャネル形成領域の全領域を空乏化することができる。したがって、s-channel 構造では、トランジスタのオフ電流をさらに小さくすることができる。なお、チャネル幅を小さくすることで、s-channel 構造によるオン電流の増大効果、オフ電流の低減効果などを高めることができる。

#### 【0291】

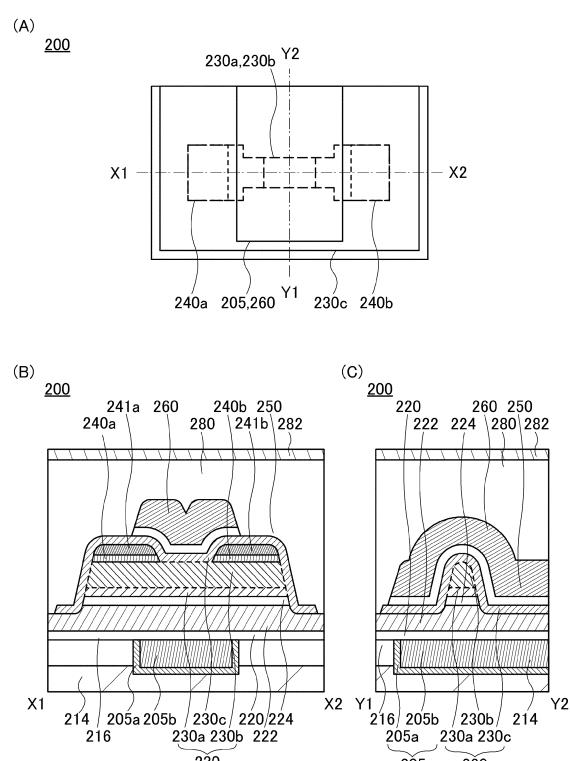

##### <トランジスタ構造 5>

図 16 には、トランジスタ 200 に適応できる構造の一例を示す。図 16 (A) はトランジスタ 200 の上面を示す。なお、図の明瞭化のため、図 16 (A) において一部の膜は省略されている。また、図 16 (B) は、図 16 (A) に示す一点鎖線 X1 - X2 に対応する断面図であり、図 16 (C) は Y1 - Y2 に対応する断面図である。

#### 【0292】

なお、図 16 に示すトランジスタ 200において、図 12 に示したトランジスタ 200 を構成する構造と同機能を有する構造には、同符号を付記する。

#### 【0293】

図 16 に示す構造は、ソースまたはドレインとして機能する導電体が積層構造を有する。導電体 240a、および導電体 240b は、酸化物 230b と密着性が高い導電体を用い、導電体 241a、導電体 241b は、導電性が高い材料を用いることが好みしい。また、導電体 240a、および導電体 240b は、ALD 法を用いて形成することが好みしい。ALD 法等により形成することで、被覆性を向上させることができる。

#### 【0294】

例えば、酸化物 230b に、インジウムを有する金属酸化物を用いる場合、導電体 240a、および導電体 240b には、窒化チタンなどを用いればよい。また、導電体 241a、および導電体 241b に、タンタル、タングステン、銅、アルミニウムなどの導電性が高い材料を用いることで、信頼性が高く、消費電力が小さいトランジスタ 200 を提供することができる。

#### 【0295】

また、図 16 (C) に示すように、トランジスタ 200 のチャネル幅方向において、酸化物 230b が、導電体 260 に覆われている。また、絶縁体 222 が凸部を有することによって、酸化物 230b の側面も導電体 260 で覆うことができる。

#### 【0296】

10

20

30

40

50

ここで、絶縁体 222 に、酸化ハフニウムなどの high-k 材料を用いる場合、絶縁体 222 の比誘電率が大きいため、 $\text{SiO}_2$  膜換算膜厚 (EOT: Equivalent Oxide Thickness) を小さくすることができる。従って、酸化物 230 にかかる導電体 205 からの電界の影響を弱めることなく、絶縁体 222 の物理的な厚みにより、導電体 205 と、酸化物 230 との間の距離を広げることができる。従って、絶縁体 222 の膜厚により、導電体 205 と、酸化物 230 との間の距離を調整することができる。

#### 【0297】

例えば、絶縁体 222 の凸部の形状を調整することで、絶縁体 222 と酸化物 230c が接する領域において、導電体 260 の底面が、酸化物 230b の底面よりも、基板側となる構造となることが好ましい。つまり、トランジスタ 200 は、導電体 260 の電界によって、酸化物 230b を電気的に取り囲むことができる構造を有する。このように、導電体の電界によって、酸化物 230b を電気的に取り囲むトランジスタの構造を、surrounded channel (s-channel) 構造とよぶ。s-channel 構造のトランジスタ 200 は、酸化物 230b 全体 (バルク) にチャネルを形成することもできる。s-channel 構造では、トランジスタのドレイン電流を大きくすることができ、さらに大きいオン電流 (トランジスタがオン状態のときにソースとドレインの間に流れる電流) を得ることができる。また、導電体 260 の電界によって、酸化物 230b に形成されるチャネル形成領域の全領域を空乏化することができる。したがって、s-channel 構造では、トランジスタのオフ電流をさらに小さくすることができる。なお、チャネル幅を小さくすることで、s-channel 構造によるオン電流の増大効果、オフ電流の低減効果などを高めることができる。

#### 【0298】

##### <トランジスタ構造 6>

図 17 には、トランジスタ 200 に適応できる構造の一例を示す。図 17 (A) はトランジスタ 200 の上面を示す。なお、図の明瞭化のため、図 17 (A) において一部の膜は省略されている。また、図 17 (B) は、図 17 (A) に示す一点鎖線 X1-X2 に対応する断面図であり、図 17 (C) は Y1-Y2 に対応する断面図である。

#### 【0299】

なお、図 17 に示すトランジスタ 200 において、図 12 に示したトランジスタ 200 を構成する構造と同機能を有する構造には、同符号を付記する。

#### 【0300】

図 17 に示すトランジスタ 200 は、絶縁体 280 に形成された開口部に、酸化物 230c、絶縁体 250、導電体 260 が形成されている。また、導電体 240a および導電体 240b の一方の端部と、絶縁体 280 に形成された開口部の端部が一致している。さらに、導電体 240a および導電体 240b の三方の端部が、酸化物 230a および酸化物 230b の端部の一部と一致している。従って、導電体 240a および導電体 240b は、酸化物 230 または絶縁体 280 の開口部と、同時に整形することができる。そのため、マスクおよび工程を削減することができる。また、歩留まりや生産性を向上させることができる。

#### 【0301】

また、導電体 240a、導電体 240b、および酸化物 230b は、過剰酸素領域を有する絶縁体 280 と、酸化物 230d を介して接する。そのため、絶縁体 280 と、チャネルが形成される領域を有する酸化物 230b との間に、酸化物 230d が介在することにより、絶縁体 280 から、水素、水、およびハロゲン等の不純物が、酸化物 230b へ拡散することを抑制することができる。

#### 【0302】

さらに、図 17 に示すトランジスタ 200 は、導電体 240a および導電体 240b と、導電体 260 と、がほとんど重ならない構造を有するため、導電体 260 と導電体 240a および 240b との間に生じる寄生容量を小さくすることができる。即ち、動作周波数

10

20

30

40

50

が高いトランジスタ 200 を提供することができる。

**【0303】**

<トランジスタ構造 8 >

図 18 には、トランジスタ 200 に適応できる構造の一例を示す。図 18 (A) はトランジスタ 200 の上面を示す。なお、図の明瞭化のため、図 18 (A) において一部の膜は省略されている。また、図 18 (B) は、図 18 (A) に示す一点鎖線 X1 - X2 に対応する断面図であり、図 18 (C) は Y1 - Y2 に対応する断面図である。

**【0304】**

なお、図 18 に示すトランジスタ 200 において、図 17 に示したトランジスタ 200 を構成する構造と同機能を有する構造には、同符号を付記する。

10

**【0305】**

図 18 に示すトランジスタ 200 は、酸化物 230d を有さない構造である。例えば、導電体 240a、および導電体 240b に耐酸化性が高い導電体を用いる場合、酸化物 230d は、必ずしも設けなくてもよい。そのため、マスクおよび工程を削減することができる。また、歩留まりや生産性を向上させることができる。

**【0306】**

また、絶縁体 224 は、酸化物 230a、および酸化物 230b と重畠する領域にのみ設けてよい。この場合、絶縁体 222 をエッティングストッパーとして、酸化物 230a、酸化物 230b、および絶縁体 224 を加工することができる。従って、歩留まりや生産性を高めることができる。

20

**【0307】**

さらに、図 18 に示すトランジスタ 200 は、導電体 240a および導電体 240b と、導電体 260 と、がほとんど重ならない構造を有するため、導電体 260 と導電体 240a および 240bとの間に生じ寄生容量を小さくすることができる。即ち、動作周波数が高いトランジスタ 200 を提供することができる。

**【0308】**

<トランジスタの作製方法 >

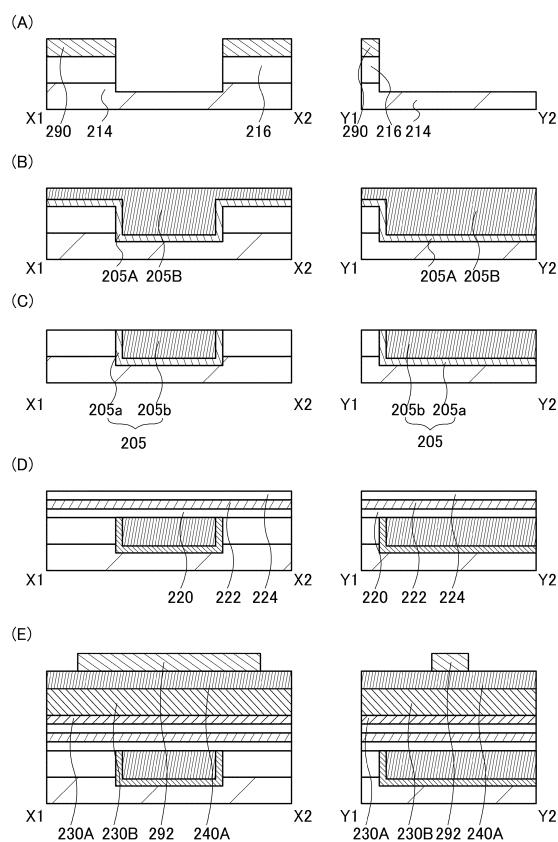

以下に、図 12 に示したトランジスタの作製方法の一例を図 19 乃至図 22 を参照して説明する。

30

**【0309】**

はじめに、基板を準備する(図示しない)。基板に大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有していることが好ましい。例えば、バリウムホウケイ酸ガラスやアルミニノホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、シリコンや炭化シリコンからなる単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム、ガリウムヒ素、インジウムヒ素、インジウムガリウムヒ素からなる化合物半導体基板、SOI (Silicon On Insulator) 基板、GOI (Germanium on Insulator) 基板などを適用することもでき、これらの基板上に半導体素子が設けられたものを、基板として用いてよい。

40

**【0310】**

また、基板として、可撓性基板を用いて半導体装置を作製してもよい。可撓性を有する半導体装置を作製するには、可撓性基板上にトランジスタを直接作製してもよいし、他の作製基板にトランジスタを作製し、その後可撓性基板に剥離、転置してもよい。なお、作製基板から可撓性基板に剥離、転置するために、作製基板と酸化物半導体を含むトランジスタとの間に剥離層を設けるとよい。

**【0311】**

次に、絶縁体 214、絶縁体 216 を形成する。続いて、絶縁体 216 上にリソグラフィ法等を用いてレジストマスク 290 を形成し、絶縁体 214、および絶縁体 216 の不要な部分を除去する(図 19 (A))。その後、レジストマスク 290 を除去することにより、開口部を形成することができる。

50

## 【0312】

ここで、被加工膜の加工方法について説明する。被加工膜を微細に加工する場合には、様々な微細加工技術を用いることができる。例えば、リソグラフィ法等で形成したレジストマスクに対してスリミング処理を施す方法を用いてもよい。また、リソグラフィ法等でダミーパターンを形成し、当該ダミーパターンにサイドウォールを形成した後にダミーパターンを除去し、残存したサイドウォールをレジストマスクとして用いて、被加工膜をエッチングしてもよい。また、被加工膜のエッチングとして、高いアスペクト比を実現するために、異方性のドライエッチングを用いることが好ましい。また、無機膜または金属膜からなるハードマスクを用いてもよい。

## 【0313】

10

レジストマスクの形成に用いる光は、例えばi線（波長365nm）、g線（波長436nm）、h線（波長405nm）、またはこれらを混合させた光を用いることができる。そのほか、紫外線やKrFレーザ光、またはArFレーザ光等を用いることもできる。また、液浸露光技術により露光を行ってもよい。また、露光に用いる光として、極端紫外光（EUV：Extreme Ultra-violet）やX線を用いてもよい。また、露光に用いる光に換えて、電子ビームを用いることもできる。極端紫外光、X線または電子ビームを用いると、極めて微細な加工が可能となるため好ましい。なお、電子ビームなどのビームを走査することにより露光を行う場合には、フォトマスクは不要である。

## 【0314】

20

また、レジストマスクとなるレジスト膜を形成する前に、被加工膜とレジスト膜との密着性を改善する機能を有する有機樹脂膜を形成してもよい。当該有機樹脂膜は、例えばスピノコート法などにより、その下方の段差を被覆して表面を平坦化するように形成することができ、当該有機樹脂膜の上方に設けられるレジストマスクの厚さのばらつきを低減できる。また、特に微細な加工を行う場合には、当該有機樹脂膜として、露光に用いる光に対する反射防止膜として機能する材料を用いることが好ましい。このような機能を有する有機樹脂膜としては、例えばBARC（Bottom Anti-Reflection Coating）膜などがある。当該有機樹脂膜は、レジストマスクの除去と一緒に除去するか、レジストマスクを除去した後に除去すればよい。

## 【0315】

30

続いて、絶縁体214、および絶縁体216上に、導電体205A、および導電体205Bを成膜する。導電体205A、および導電体205Bは、スパッタリング法、蒸着法、CVD法（熱CVD法、MOCVD法、PECVD法等を含む）などにより成膜することができる。また、プラズマによるダメージを減らすには、熱CVD法、MOCVD法またはALD法が好ましい（図19（B））。

## 【0316】

40

続いて、導電体205A、および導電体205Bの不要な部分を除去する。例えば、エッチバック処理、または、機械的化学的研磨法（CMP：Chemical Mechanical Polishing）処理などにより、絶縁体216が露出するまで、導電体205A、および導電体205Bの一部を除去することで、導電体205を形成する（図19（C））。この際、絶縁体216をストップ層として使用することもでき、絶縁体216が薄くなる場合がある。

## 【0317】

ここで、CMP処理とは、被加工物の表面を化学的・機械的な複合作用により平坦化する手法である。より具体的には、研磨ステージの上に研磨布を貼り付け、被加工物と研磨布との間にスラリー（研磨剤）を供給しながら研磨ステージと被加工物とを各々回転または揺動させて、スラリーと被加工物表面との間での化学反応と、研磨布と被加工物との機械的研磨の作用により、被加工物の表面を研磨する方法である。

## 【0318】

なお、CMP処理は、1回のみ行ってもよいし、複数回行ってもよい。複数回に分けてCMP処理を行う場合は、高い研磨レートの一次研磨を行った後、低い研磨レートの仕上げ

50

研磨を行うのが好ましい。このように研磨レートの異なる研磨を組み合わせてもよい。

#### 【0319】

次に、絶縁体220、絶縁体222、および絶縁体224を形成する(図19(D))。なお、絶縁体220、および絶縁体222は必ずしも設ける必要はない。例えば、絶縁体224が過剰酸素領域を有する場合、導電体205上に、バリア性を有する導電体を形成してもよい。バリア性を有する導電体を形成することで、導電体205が、過剰酸素領域の酸素と反応し、酸化物を生成することを抑制することができる。

#### 【0320】

絶縁体220、絶縁体222、および絶縁体224として、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよい。特に、絶縁体222には、酸化ハフニウムなどのhigh-k材料を用いることが好ましい。

10

#### 【0321】

絶縁体220、絶縁体222、および絶縁体224は、例えば、スパッタリング法、化学気相堆積(CVD: Chemical Vapor Deposition)法(熱CVD法、有機金属CVD(MOCVD: Metal Organic Chemical Vapor Deposition)法、プラズマ励起CVD(PECVD: Plasma Enhanced Chemical Vapor Deposition)法等を含む)、分子線エピタキシー(MBE: Molecular Beam Epitaxy)法、原子層堆積(ALD: Atomic Layer Deposition)法またはパルスレーザ堆積(PLD: Pulsed Laser Deposition)法などを用いて形成することができる。特に、当該絶縁体をCVD法、好ましくはALD法等によって成膜すると、被覆性を向上させることができるために好ましい。また、プラズマによるダメージを減らすには、熱CVD法、MOCVD法またはALD法が好ましい。また、TEOS(Tetra-Ethyl-Ortho-Silicate)若しくはシラン等と、酸素若しくは亜酸化窒素等とを反応させて形成した段差被覆性のよい酸化シリコン膜を用いることもできる。

20

#### 【0322】

なお、絶縁体220、絶縁体222、および絶縁体224は、連続成膜することができる。連続的に成膜することで、絶縁体220と絶縁体222との界面、および絶縁体222と絶縁体224との界面に不純物が付着することなく、信頼性が高い絶縁体を形成することができる。

30

#### 【0323】

続いて、酸化物230aとなる酸化物230Aと、酸化物230bとなる酸化物230Bを順に成膜する。当該酸化物は、大気に触れさせることなく連続して成膜することができる。

#### 【0324】

その後、酸化物230A上に、導電体240a、および導電体240bとなる導電膜240Aを形成する。導電膜240Aには、水素または酸素に対するバリア性があり、また、耐酸化性が高い材質を用いることが好ましい。また、図では単層で表しているが、2層以上の積層構造としてもよい。続いて、上記と同様の方法によりレジストマスク292を形成する(図19(E))。

40

#### 【0325】

レジストマスク292を用いて、導電膜240Aの不要な部分をエッチングにより除去し、島状の導電層240Bを形成する(図20(A))。その後、導電層240Bをマスクとして酸化物230A、および酸化物230Bの不要な部分をエッチングにより除去する。

#### 【0326】

このとき、同時に絶縁体224も、島状に加工してもよい。例えば、バリア性を有する絶縁体222をエッチングストッパー膜として用いることで、絶縁体220、絶縁体222

50

、および絶縁体 224 の合計膜厚が薄い構造においても、下方にある配線層まで、オーバーエッティングされることを防止することができる。また、絶縁体 220、絶縁体 222、および絶縁体 224 の合計膜厚が薄くすることで導電体 205 からの電圧が効率的にかかる為、消費電力が低いトランジスタを提供することができる。

#### 【0327】

その後レジストマスクを除去することにより、島状の酸化物 230a、島状の酸化物 230b、および島状の導電層 240B の積層構造を形成することができる（図 20（B））。

#### 【0328】

続いて、加熱処理を行うことが好ましい（図 20（C）、図中矢印は加熱処理を表す。）

10

。加熱処理は、250 以上 400 以下、好ましくは 320 以上 380 以下の温度で、不活性ガス雰囲気、酸化性ガスを 10 ppm 以上含む雰囲気、または減圧状態で行えばよい。また、加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを 10 ppm 以上含む雰囲気で行ってもよい。加熱処理により、酸化物 230a、および酸化物 230b の不純物である水素を除去することができる。また、酸化物 230a の下方に形成された絶縁体から、酸化物 230a、および酸化物 230b に酸素が供給され、酸化物中の酸素欠損を低減することができる。

#### 【0329】

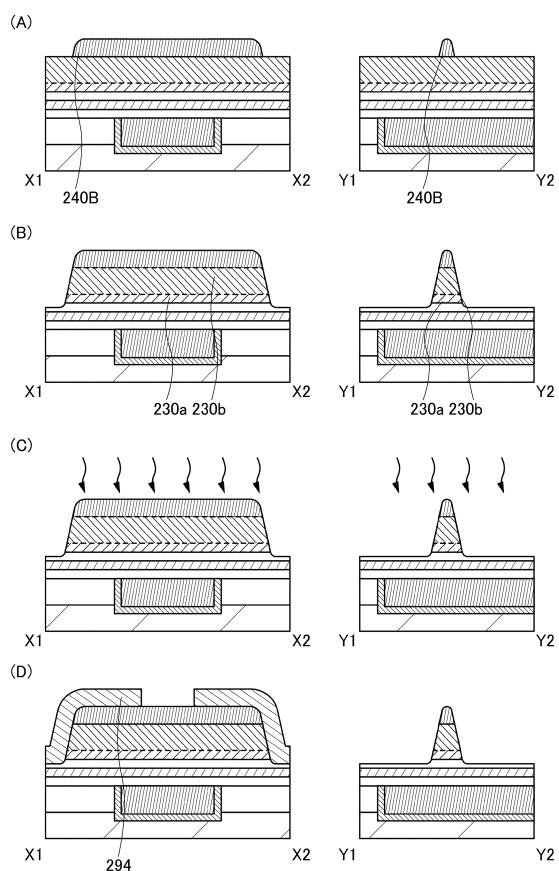

次に、島状の導電層 240B 上に上記と同様の方法によりレジストマスク 294 を形成する（図 20（D））。続いて、導電層 240B の不要な部分をエッティングにより除去した後、レジストマスク 294 を除去することにより、導電体 240a、および導電体 240b を形成する（図 21（A））。この際、絶縁体 222 または絶縁体 224 の一部をエッティングして薄くすることで、s-channel 構造を形成してもよい。

20

#### 【0330】

なお、ここで、加熱処理を行なってもよい。加熱処理の条件は、図 20（C）で説明した加熱処理と同等の条件で行えばよい。加熱処理により、酸化物 230a、および酸化物 230b の不純物である水素を除去することができる。また、酸化物 230a の下方に形成された絶縁体から、酸化物 230a、および酸化物 230b に酸素が供給され、酸化物中の酸素欠損を低減することができる。さらに、酸化性ガスで加熱処理を行う場合、チャネルが形成される領域に、直接酸化性ガスが接することで、効率的に、チャネルが形成される領域の酸素欠損を低減することができる。

30

#### 【0331】

続いて、酸化物 230c を成膜する。また、ここで、加熱処理を行なってもよい（図 21（B）、図中矢印は加熱処理を表す。）。加熱処理の条件は、図 21（C）で説明した加熱処理と同等の条件で行えばよい。加熱処理により、酸化物 230a、および酸化物 230b の不純物である水素を除去することができる。また、酸化物 230a の下方に形成された絶縁体から、酸化物 230a、および酸化物 230b に酸素が供給され、酸化物中の酸素欠損を低減することができる。さらに、酸化性ガスで加熱処理を行う場合、チャネルが形成される領域に、直接酸化性ガスが接することで、効率的に、チャネルが形成される領域の酸素欠損を低減することができる。

40

#### 【0332】

絶縁体 250、および導電体 260 となる導電膜 260A を順に成膜する。また、導電膜 260A には、水素または酸素に対するバリア性があり、また、耐酸化性が高い材質を用いることが好ましい。また、図では単層で表しているが、2 層以上の積層構造としてもよい。

#### 【0333】

例えば、2 層構造は、同じ材料を積層して設けてもよい。第 1 の導電膜は、熱 CVD 法、MOCVD 法または ALD 法を用いて形成する。特に、ALD 法を用いて形成することが好ましい。ALD 法等により形成することで、絶縁体 250 に対する成膜時のダメージを減らすことができる。また、ALD 法等により形成することで、被覆性の高い導電膜 26

50

0 A を成膜することができる。従って、信頼性が高いトランジスタ 200 を提供することができる。

#### 【 0 3 3 4 】

続いて、第 2 の導電膜は、スパッタリング法を用いて形成する。この時、絶縁体 250 上に、第 1 の導電膜を有することで、第 2 の導電膜の成膜時のダメージが、絶縁体 250 に影響することを抑制することができる。また、ALD 法と比較して、スパッタリング法は成膜速度が速いため、歩留まりが高く、生産性を向上させることができる。なお、導電膜 260 A を成膜する際に、塩素を含まない成膜ガスを用いて、形成することが好ましい。

#### 【 0 3 3 5 】

次に、導電膜 260 A 上に、上記と同様の方法によりレジストマスク 296 を形成する(図 21 (C))。続いて、導電膜 260 A の不要な部分をエッチングにより除去することで、導電体 260 を形成した後、レジストマスク 296 を除去する(図 22 (A))。

#### 【 0 3 3 6 】

続いて、導電体 260 上に、絶縁体 280 を形成する。絶縁体 280 は、酸化シリコン膜や酸化窒化シリコン膜などの、酸素を含む絶縁体である。過剰酸素を含む絶縁体を形成する方法としては、CVD 法やスパッタリング法における成膜条件を適宜設定して膜中に酸素を多く含ませた酸化シリコン膜や酸化窒化シリコン膜を形成することができる。また、酸化シリコン膜や酸化窒化シリコン膜を形成した後、イオン注入法やイオンドーピング法やプラズマ処理によって酸素を添加してもよい。

#### 【 0 3 3 7 】

特に、酸素プラズマ処理を行うことが好ましい(図 22 (B)、図中矢印はプラズマ処理を表す。)。代表的な酸素プラズマ処理は、酸素ガスのグロー放電プラズマで生成されたラジカルで酸化物半導体の表面を処理することであるが、プラズマを生成するガスとしては酸素のみでなく、酸素ガスと希ガスの混合ガスであってもよい。例えば、250 以上 400 以下、好ましくは 300 以上 400 以下の温度で、酸化性ガスを含む雰囲気、または減圧状態で行えばよい。

#### 【 0 3 3 8 】

酸素プラズマ処理により、絶縁体 280、および酸化物 230 が、脱水化、または脱水素化されるとともに、絶縁体 280 に過剰な酸素を導入することで、過剰酸素領域を形成することができる。また、脱水化、または脱水素化された酸化物 230 には、酸素欠損が生じ、低抵抗化する。一方で、絶縁体 280 の過剰な酸素により、酸化物 230 の酸素欠損が補填される。従って、酸素プラズマ処理により、絶縁体 280 は、過剰酸素領域が形成されると同時に、不純物である水素、および水を除去することができる。また、酸化物 230 は、酸素欠損を補填しながら、不純物である水素、または水を除去することができる。したがって、トランジスタ 200 の電気特性の向上および、電気特性のばらつきを軽減することができる。

#### 【 0 3 3 9 】

続いて、絶縁体 280 上に、絶縁体 282 を形成する(図 22 (C))。絶縁体 282 は、スパッタリング装置により成膜することが好ましい。スパッタリング法を用いることで、容易に絶縁体 282 の下層である絶縁体 280 に過剰酸素領域を形成することができる。

#### 【 0 3 4 0 】

スパッタリング法による成膜時には、ターゲットと基板との間には、イオンとスパッタされた粒子とが存在する。例えば、ターゲットは、電源が接続されており、電位 E0 が与えられる。また、基板は、接地電位などの電位 E1 が与えられる。ただし、基板が電気的に浮いていてもよい。また、ターゲットと基板の間には電位 E2 となる領域が存在する。各電位の大小関係は、E2 > E1 > E0 である。

#### 【 0 3 4 1 】

プラズマ内のイオンが、電位差 E2 - E0 によって加速され、ターゲットに衝突することにより、ターゲットからスパッタされた粒子がはじき出される。このスパッタされた粒子

10

20

30

40

50

が成膜表面に付着し、堆積することにより成膜が行われる。また、一部のイオンはターゲットによって反跳し、反跳イオンとして形成された膜を介して、形成された膜の下部にある絶縁体280に取り込まれる場合がある。また、プラズマ内のイオンは、電位差E2-E1によって加速され、成膜表面を衝撃する。この際、イオンの一部のイオンは、絶縁体280の内部まで到達する。イオンが絶縁体280に取り込まれることにより、イオンが取り込まれた領域が絶縁体280に形成される。つまり、イオンが酸素を含むイオンであった場合において、絶縁体280に過剰酸素領域が形成される。

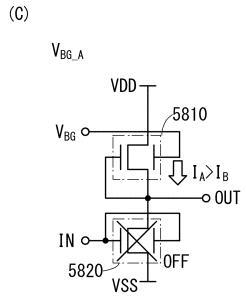

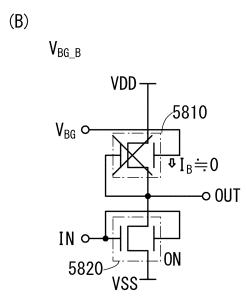

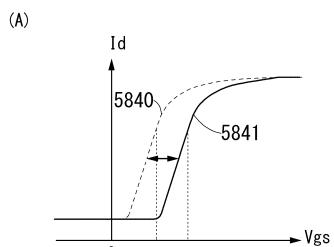

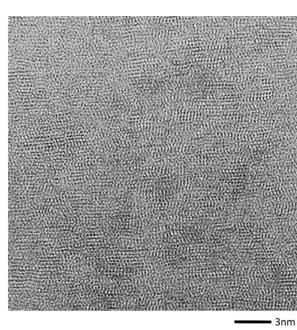

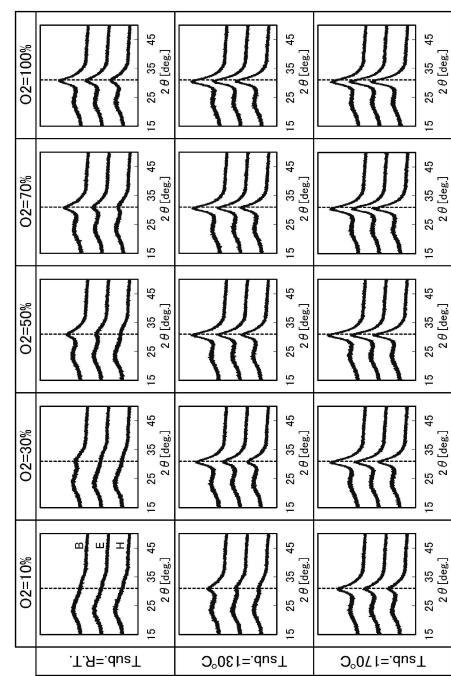

#### 【0342】