(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7166884号

(P7166884)

(45)発行日 令和4年11月8日(2022.11.8)

(24)登録日 令和4年10月28日(2022.10.28)

(51)国際特許分類

|         |                 |     |         |       |

|---------|-----------------|-----|---------|-------|

| G 0 6 F | 21/12 (2013.01) | F I | G 0 6 F | 21/12 |

| G 0 6 F | 1/08 (2006.01)  |     | G 0 6 F | 1/08  |

| H 0 4 N | 1/00 (2006.01)  |     | H 0 4 N | 1/00  |

| B 4 1 J | 29/38 (2006.01) |     | B 4 1 J | 29/38 |

| B 4 1 J | 29/42 (2006.01) |     | B 4 1 J | 29/42 |

請求項の数 20 (全16頁) 最終頁に続く

(21)出願番号 特願2018-213732(P2018-213732)

(22)出願日 平成30年11月14日(2018.11.14)

(65)公開番号 特開2020-80097(P2020-80097A)

(43)公開日 令和2年5月28日(2020.5.28)

審査請求日 令和3年11月5日(2021.11.5)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100126240

弁理士 阿部 琢磨

100124442

弁理士 黒岩 創吾

(72)発明者 青柳 剛

東京都大田区下丸子3丁目30番2号キ

ャノン株式会社内

審査官 吉田 歩

最終頁に続く

(54)【発明の名称】 ソフトウェアの改ざんを検知することが可能な情報処理装置

## (57)【特許請求の範囲】

## 【請求項1】

情報処理装置であって、

所定のソフトウェアを実行する第1コントローラと、

クロック信号を受け付けることで動作し、前記所定のソフトウェアが改ざんされている

か否か検証する第2コントローラと、

前記第1コントローラに電圧を供給する電源電圧回路と、

前記所定のソフトウェアが改ざんされていないことに基づいて、前記電源電圧回路が前

記第1コントローラに供給する電圧を変更する電源制御コントローラと、を備え、

前記第2コントローラは、受け付けるクロック信号が第1周波数のクロック信号から前

記第1周波数よりも高い第2周波数のクロック信号に切り替わった後、前記第2周波数の

クロック信号を受け付けている状態で前記所定のソフトウェアが正常か否かを検証する

こと特徴とする情報処理装置。

## 【請求項2】

前記第1コントローラと前記第2コントローラに、少なくとも前記第1周波数のクロック

信号を供給する信号生成回路と、を有することを特徴とする請求項1に記載の情報処理

装置。

## 【請求項3】

前記信号生成回路は、前記第1コントローラによる前記電源電圧回路が供給する電圧を

変更した後、前記第1周波数のクロック信号より高い第3周波数のクロック信号を出力す

る、ことを特徴とする請求項 2 に記載の情報処理装置。

【請求項 4】

前記第 2 周波数と前記第 3 周波数は、同じである、ことを特徴とする請求項 3 に記載の情報処理装置。

【請求項 5】

前記所定のソフトウェアが改ざんされておらず且つ前記信号生成回路によって供給されるクロック信号が前記第 2 周波数のクロック信号から前記第 1 周波数のクロック信号に切り替わることに基づいて、前記電源制御コントローラは、前記第 1 コントローラに供給する電圧を変更させることを特徴とする請求項 2 乃至 4 のいずれか 1 項に記載の情報処理装置。

10

【請求項 6】

前記第 1 周波数のクロック信号及び前記第 2 周波数のクロック信号が入力され、前記第 1 周波数のクロック信号及び前記第 2 周波数のクロック信号の何れか一方を出力する、出力切り替え回路を有することを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の情報処理装置。

【請求項 7】

前記第 2 コントローラは、前記出力切り替え回路が出力する周波数を設定する、ことを特徴とする請求項 6 に記載の情報処理装置。

【請求項 8】

前記出力切り替え回路は、前記ソフトウェアが改ざんされていない場合に、前記第 1 周波数のクロック信号を出力する、ことを特徴とする請求項 6 または 7 に記載の情報処理装置。

20

【請求項 9】

前記出力切り替え回路は、前記第 1 コントローラおよび前記第 2 コントローラに第 1 周波数のクロック信号および第 2 周波数のクロック信号を出力する、ことを特徴とする請求項 6 乃至 8 のいずれか 1 項に記載の情報処理装置。

【請求項 10】

前記第 1 周波数のクロック信号が入力され、前記第 2 周波数のクロック信号を出力する周波数変更回路を備える、ことを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の情報処理装置。

30

【請求項 11】

前記第 2 コントローラによる前記ソフトウェアが改ざんされたことを示す情報を通知する通知手段をさらに備える、ことを特徴とする請求項 1 乃至 10 のいずれか 1 項に記載の情報処理装置。

【請求項 12】

前記通知手段は、光を出力する光出力手段である、ことを特徴とする請求項 11 に記載の情報処理装置。

【請求項 13】

前記第 2 コントローラは、前記第 1 コントローラが実行するソフトウェアの一部と予め保持した正解値とを比較することにより、前記ソフトウェアが改ざんされているか否かを検証する、ことを特徴とする請求項 1 乃至 12 のいずれか 1 項に記載の情報処理装置。

40

【請求項 14】

前記第 2 コントローラによる前記所定のソフトウェアが改ざんされているか否かを検証で行う処理は、前記所定のソフトウェアをリードする処理、前記所定のソフトウェアに対応する値と比較される比較用データをリードする処理、前記所定のソフトウェアに対応する値と比較用データとを比較する処理、前記所定のソフトウェアに対応する値と比較用データとが一致するかどうかを判断する処理、の少なくとも 1 つである、ことを特徴とする請求項 1 乃至 13 のいずれか 1 項に記載の情報処理装置。

【請求項 15】

前記第 1 コントローラのプロセス情報を記憶するメモリを有し、

50

前記第1コントローラによる前記電源電圧回路が出力する電圧の設定処理とは、前記メモリから前記プロセス情報をリードする処理、前記メモリからリードした前記情報を前記電源制御コントローラに出力する処理、の少なくとも1つである、ことを特徴とする請求項1乃至14のいずれか1項に記載の情報処理装置。

【請求項16】

前記第1コントローラと前記第2コントローラとは同期関係である、ことを特徴とする請求項1乃至15のいずれか1項に記載の情報処理装置。

【請求項17】

前記ソフトウェアは、前記第1コントローラのポートデータである、ことを特徴とする請求項1乃至16のいずれか1項に記載の情報処理装置。

10

【請求項18】

用紙に画像を印刷する印刷手段をさらに備える、ことを特徴とする請求項1乃至17のいずれか1項に記載の情報処理装置。

10

【請求項19】

原稿の画像を読み取る読み取手段をさらに備える、ことを特徴とする請求項1乃至18のいずれか1項に記載の情報処理装置。

【請求項20】

第1コントローラに電圧を出力する、

前記第1コントローラが実行する所定のソフトウェアを検証する、

前記第1コントローラに供給すべき電圧に対応する情報を保持する、

20

保持された前記情報に基づいて前記第1コントローラに供給される電圧を設定する、

少なくとも前記所定のソフトウェアの検証処理中に、前記ソフトウェアを検証する第2コントローラに第1周波数のクロック信号を出力する、

少なくとも前記第1コントローラに供給すべき電圧の設定処理中に、前記第1コントローラに前記第1周波数より低速の第2周波数のクロック信号を出力する、ことを特徴とする情報処理装置の制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ソフトウェアの改ざんを検知することが可能な情報処理装置等に関する。

30

【背景技術】

【0002】

ソフトウェアの改ざんを検知（以下、改ざん検知と呼ぶ）して、改ざんが検知されたソフトウェアの実行を禁止する機能を有する情報処理装置が知られている。例えば、メインC P Uが実行するソフトウェアをサブC P Uが検証を行い、検証が成功したソフトウェアをメインC P Uが実行する。検証が失敗すると、当該ソフトウェアの実行を禁止する。

【0003】

また、情報処理装置には、デバイス（例えば、C P U）の個体差に応じて電源電圧を変えるA S V（Adaptive Supply Voltage）と呼ばれる技術を搭載しているものもある（特許文献1）。F A S Tの個体（所定の電圧よりも低い電圧でも所定の周波数での動作が可能な個体）に関しては、所定の電圧よりも低い電圧を供給することにより、所定の周波数での動作を実現する。これにより、消費電力の低減を図ることができる。また、S L O Wの個体（所定の電圧よりも高い電圧でなければ所定の周波数で動作しない個体）に関しては、所定の電圧よりも高い電圧を供給することにより、所定の周波数での動作を実現する。以下、デバイスの個体差に応じた電圧を設定することをA S V処理と呼ぶ。

40

【0004】

デバイスがS L O Wの個体であった場合に、当該デバイスに必要な電圧を入力してから所定の周波数のクロック信号を入力しないと、デバイスの動作が不安定になる可能性がある。従って、デバイスに必要な電圧が入力されるまでは、所定の周波数よりも低い周波数の

50

クロック信号を入力しておく。そして、デバイスに必要な電圧が入力されてから、Phase Locked Loop回路（以下、PLL回路とする）等を使って、所定の周波数のクロック信号をデバイスに入力する。

【先行技術文献】

【特許文献】

【0005】

【文献】特開2005-322860号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上記したように、ASV処理によりデバイスに必要な電圧が入力されるまでは、デバイスが確実に動作できるように低速のクロック信号を入力する必要がある。そのため、デバイスが動作する前に実行される処理であるデバイスが実行するソフトウェアの改ざん検知処理は、低速のクロック信号で実行されることになる。その結果、改ざん検知処理に要する時間が長くなる。

【0007】

そこで、本発明では、改ざん検知処理に要する時間を短くすることが可能な情報処理装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明は、情報処理装置であって、所定のソフトウェアを実行する第1コントローラと、クロック信号を受け付けることで動作し、前記所定のソフトウェアが改ざんされているか否か検証する第2コントローラと、前記第1コントローラに電圧を供給する電源電圧回路と、前記所定のソフトウェアが改ざんされていないことに基づいて、前記電源電圧回路が前記第1コントローラに供給する電圧を変更する電源制御コントローラと、を備え、前記第2コントローラは、受け付けるクロック信号が第1周波数のクロック信号から前記第1周波数よりも高い第2周波数のクロック信号に切り替わった後、前記第2周波数のクロック信号を受け付けている状態で前記所定のソフトウェアが正常か否かを検証すること特徴とする。

【発明の効果】

【0009】

本発明によれば、改ざん検知処理に要する時間を短くすることが可能な情報処理装置を提供することを目的とする。

【図面の簡単な説明】

【0010】

【図1】画像形成装置の全体構成図

【図2】ASICのブロック図

【図3】サブCPU103が実行する処理を示したフローチャート

【図4】メインCPU101が実行する処理を示したフローチャート

【図5】ブートプログラムの検証に関わるブロックの詳細を示した図

【図6】ブートプログラムの検証方法の処理フロー

【図7】ASV処理に関わるブロックの詳細を示した図

【図8】プロセス情報格納部に格納される情報の詳細を示した図

【図9】ASV処理の詳細を示したフローチャート

【発明を実施するための形態】

【0011】

以下、図面を参照して、本発明の実施形態を詳細に説明する。

【0012】

本実施形態では、情報処理装置として、プリント機能及びスキャン機能を有する画像形成装置を例に説明する。

10

20

30

40

50

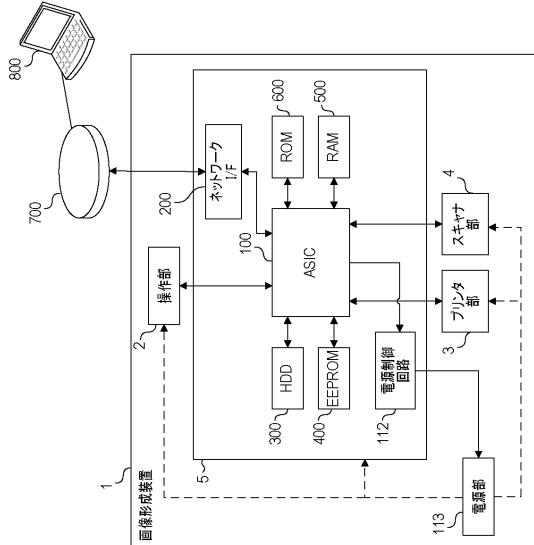

## 【0013】

図1は、画像形成装置の全体構成図である。

## 【0014】

ネットワーク700には、画像形成装置1、PC(Personal Computer)800が互いに通信可能に接続されている。また、PC800には、Webブラウザがインストールされている。Webブラウザは、URL(Uniform Resource Locator)の入力を受け付け、Webサーバ(図示省略)からWebページを受信し、PC800の操作部(図示省略)にWebページを表示することができる。

## 【0015】

画像形成装置1は、PC800のWebブラウザを介してユーザに画像形成装置1の各種設定を行わせるためのWebサーバを備えている。PC800のWebブラウザは、Webブラウザのアドレス入力欄に画像形成装置1のIPアドレスまたはホスト名が入力されると、画像形成装置1から各種設定を行うためのWebページを受信して、表示部に表示する。ユーザは、各種設定を行うためのWebページを介して、画像形成装置1の設定を行うことができる。

10

## 【0016】

次に、画像形成装置1の構成について説明する。画像形成装置1は、複数の機能部(プリンタ部3、スキャナ部4)、コントロールユニット5、操作部2、プリンタ部3、スキャナ部4、及び、電源部113を備えている。

20

## 【0017】

電源部113は、コントロールユニット5、操作部2、プリンタ部3、スキャナ部4に電力を供給する。操作部2は、タッチパネルを有する液晶表示部、及び、キーボードを備える。また、操作部2は、画像形成装置1の電力状態をスリープ状態に移行する節電ボタンを有する。スタンバイ状態で節電ボタンが押下されると、画像形成装置1の電力状態は、スタンバイ状態より省電力のスリープ状態に移行する。また、スリープ状態で節電ボタンが押下されると、画像形成装置1の電力状態は、スタンバイ状態に移行する。上記したスリープ状態は、プリンタ部3又はスキャナ部4への電力が停止されるスリープ状態であれば、コントロールユニット5への電力が停止されるディープスリープ状態であっても良い。また、コントロールユニット5への電力供給が停止されないスリープ状態であっても良い。

30

## 【0018】

プリンタ部3は、ユーザから受け付けた印刷指示に従って、コントロールユニット5が受信した画像データを用いて用紙に画像を印刷する。プリンタ部5の印刷方式は、トナーを用紙に定着させて画像を印刷する電子写真方式を採用していてもよいし、インクを用紙に吐出して画像を印刷するインクジェット方式を採用していてもよい。スキャナ部4は、ユーザから受け付けた読み取指示に従って、原稿の画像を読み取り、読み取った画像の画像データをコントロールユニット5に送信する。

## 【0019】

コントロールユニット5は、ASIC(Application Specific Integrated Circuit)100を有する。また、コントロールユニット5は、ROM(Read Only Memory)600、RAM(Random Access Memory)500を有する。コントロールユニット5は、HDD(Hard Disk Drive)300、EEPROM(Electrically Erasable Programmable ROM)400、ネットワークI/F(インターフェイス)200を有する。また、コントロールユニット5は、電源制御回路112を有する。

40

## 【0020】

コントロールユニット5は、画像形成装置1が有する各種機能を実行する。ASIC100は、ROM600又はHDD300に記憶された制御プログラムを読み出して、印刷制御や読み取制御などの各種制御を行う。RAM109は、揮発性メモリであり、制御プログラムを実行するときに使用されるワークメモリである。HDD300は、磁気ディスク

50

などの記憶媒体であり、制御プログラムや画像データなどを記憶する。EEPROM400は、不揮発性メモリであり、制御プログラムが実行するときに参照する設定値などを記憶している。

【0021】

ネットワークI/F200は、ネットワーク700を介して、PC800から印刷データや各種データを受信する。

【0022】

電源制御回路112は、節電ボタンなどからスリープ状態への移行要求を受け付けた時に、電源部（電源部）113からプリンタ部3およびスキャナ部4に供給される電力を停止する。これにより、画像形成装置1は、スリープ状態に移行する。また、電源制御回路112は、節電ボタンなどからスリープ状態からの復帰要求を受け付けた時に、電源部113からプリンタ部3およびスキャナ部4に電力が供給されるよう制御する。

10

【0023】

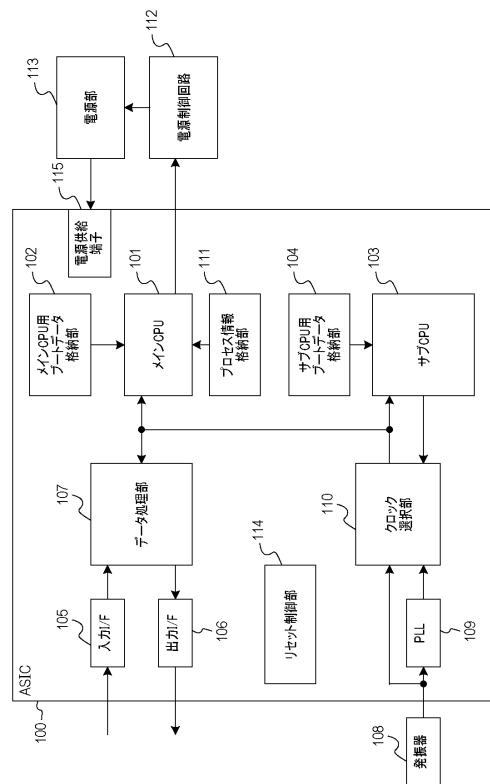

<ASIC100の構成>

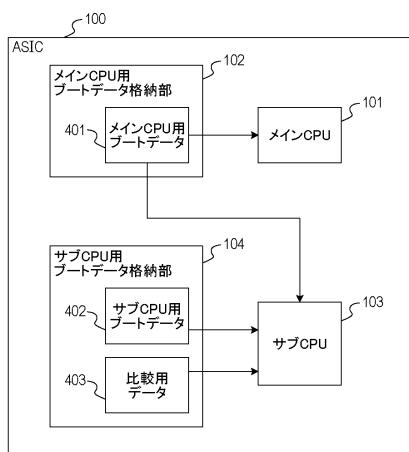

図2は、ASICのブロック図である。

【0024】

ASIC100は、メインCPU（実行手段）101、メインCPU用のブートデータを格納する格納部102、サブCPU（検証手段）103、及び、サブCPU用のブートデータを格納する格納部104を有する。また、ASIC100は、入力インターフェイス105、出力インターフェイス106、データ処理部107、及び、PLL109、クロック選択部（信号選択部）110を有する。また、ASIC100は、プロセス情報格納部（保持部）111、リセット制御部114、及び、電源供給端子115を有する。本発明のクロック信号出力部は、発振部108、PLL109、クロック選択部110を含む。

20

【0025】

メインCPU101は、ASIC100内の各デバイスの制御を行う。メインCPU101は、基本的には、1.0Vの電源電圧が供給されている場合に1200MHzの周波数のクロック信号で動作することが可能である。しかし、メインCPU101は、個体差によっては、電源電圧が1.0V未満であっても1200MHzで動作可能な場合もあるし、電源電圧が1.0Vより高い電源電圧を供給しないと1200MHzで動作しない場合もある。

30

【0026】

格納部102は、メインCPU101がブートするときに実行するプログラムやブート時に使用する各種データ（以下、プログラム及び各種データをまとめて、ブートデータとする）を格納する。格納部102は、ROM（リードオンリーメモリ）である。

【0027】

サブCPU103は、メインCPU101の補助的な制御を行う。

【0028】

格納部104は、サブCPU103がブートするときに実行するプログラムやブート時に使用する各種データを格納する。格納部104は、ROMである。

40

【0029】

本実施形態では、サブCPU103は、画像形成装置1の電源オン時（ASIC100のリセット時）に、メインCPU101より先にブートする。つまり、サブCPU103は、画像形成装置1の電源オン時（ASIC100のリセット時）に、格納部104に格納されているブートデータを使用してブートし、格納部102に格納されているブートデータの検証を行う。サブCPU103によるブートデータの検証によって、メインCPU101が実行するブートデータの改ざんが無いと判定すれば、メインCPU101は、格納部102に格納されたブートプログラムを実行する。

【0030】

入力インターフェイス（以下、I/Fとする）105は、ASIC100の外部からデ

50

ータの入力を行なうインターフェイスである。出力インターフェイス 106 は、外部にデータの出力を行なうインターフェイスである。

【0031】

データ処理部 107 は、入力 I/F 105 から入力されたデータに対して、所定の処理を行うモジュールである。例えば、データ処理部 107 は、画像データを受信して、受信した画像データに対して画像処理（拡大、縮小、補正等）を行う。

【0032】

発振器 108 は、ASIC 100 にクロック信号を供給する。発振器 108 は、例えば、10MHz のクロック信号を供給する。PLL (Phase Locked Loop) 109 は、発振器 108 から供給されたクロック信号の周波数を、所望の周波数に変換して出力する回路である。PLL 109 は、入力されたクロック信号の周波数 (10MHz) を、例えば、120 倍の 1200MHz のクロック信号に変換して、出力する。

10

【0033】

クロック選択部 (MUX (マルチプレクサ)) 110 には、発振器 108 が供給するクロック信号及び PLL 109 が供給するクロック信号が入力される。クロック選択部 110 は、発振器 108 が供給したクロック信号、及び、PLL 109 が供給したクロック信号のいずれか 1 つを出力する。本実施形態では、クロック選択部 110 は、サブCPU 103 からの指示に従って、発振器 108 が供給したクロック信号、及び、PLL 109 が供給したクロック信号のいずれか 1 つを出力する。ASIC 100 内の各モジュール（メインCPU 101、サブCPU 103、データ処理部 107、及び、その他の回路）は、お互いにデータの受け渡しを同期関係で行うため、各モジュールに入力されるクロック信号は、位相が同期している必要がある。そこで、本実施形態では、各モジュールに供給されるクロック信号は、クロック選択部 110 から出力されたクロック信号を分岐したものである。各モジュールに入力されるクロック信号は位相が同期していれば、クロック信号の周波数は異なっていても良い。

20

【0034】

プロセス情報格納部 111 は、メインCPU 101 のプロセス情報（3 ビットの情報）を格納する。プロセス情報格納部 111 は、ROM である。

【0035】

電源制御回路 112 は、電源部 113 が出力する電圧を変更する。電源制御回路 112 は、プロセス情報格納部 111 に格納されているプロセス情報に基づいて、電源部 113 から出力される電圧を変更する。電源部 113 は、電源供給端子 115 を介して、ASIC 100 に電圧を印加する。電源部 113 は、電源制御回路 112 から出力される電圧制御信号に基づいて、ASIC 100 に所定の電圧を印加する。

30

【0036】

リセット制御部 114 は、ASIC 100 内の各モジュールにリセット信号を出力する。画像形成装置 1 の電源オン時（ASIC 100 のリセット時）に、リセット制御部 114 は、サブCPU 103 及び格納部 104 のリセットを解除する。次に、サブCPU 103 からの指示に従って、リセット制御部 114 は、メインCPU 101 のリセットを解除する。

40

【0037】

ASIC 100 は低速動作モード、高速動作モードの 2 つの動作モードで動作可能である。低速動作モードにおいては、クロック選択部 110 は、サブCPU 103 からの指示に従って、発振器 108 から入力されたクロック信号を選択して出力する。出力されたクロック信号は、図 2 に示すように、メインCPU 101、サブCPU 103、データ処理部 107 の動作用のクロック信号として使用される。また、図 2 では図示していないが、上記以外の他の回路に対しても、クロック信号が入力される。

【0038】

図 2 では、クロック選択部 110 から出力されたクロック信号が直接各モジュールに供給されているが、分周回路等を使用して周波数を落としたクロックを各モジュールに供給

50

しても良い。

【0039】

高速動作モードにおいては、クロック選択部110は、サブCPU103からの指示に従って、PLL109から入力されたクロック信号を選択して出力する。出力されたクロック信号は、図2に示すように、メインCPU101、サブCPU103、データ処理部107の動作用のクロック信号として使用される。また、図1では図示していないが、上記以外の他の回路に対しても、クロック信号が入力される。

【0040】

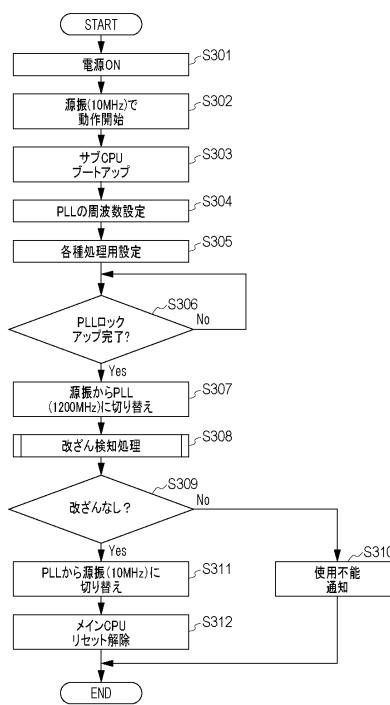

<サブCPUの動作フロー>

図3は、サブCPU103が実行する処理を示したフローチャートである。

10

【0041】

ユーザにより、画像形成装置の電源がオンされると(S301)、ASIC100にリセット信号が入力される。ASIC100がリセットされると、初期設定に基づいて、ASIC100は低速動作モードとなる。サブCPU103には、発振器108から出力されたクロック信号(10MHz)が入力される(S302)。リセット制御部114は、ハードウェアシーケンスにより、サブCPU103及び格納部104のリセットを解除する。これにより、サブCPU103は、格納部104に格納されているブートデータを実行する(S303)。

【0042】

ブートしたサブCPU103は、PLL109が1200MHzのクロック信号を出力するように設定する。これにより、PLL109が、1200MHzのクロック信号を発振する(S304)。

20

【0043】

その後、サブCPU103は、データ処理部107が所定の処理を実行するように、各種パラメータを設定する(S305)。そして、サブCPU103は、PLL109のロックアップタイムが経過したかどうかを判定する(S306)。ロックアップタイムとは、PLL109が所定の周波数(ここでは、1200MHz)を安定して発振するまでに要する時間である。

【0044】

ロックアップタイムが経過したと判定した場合(S306: Yes)、サブCPU103は、クロック選択部110の出力を、発振器108から出力されたクロック信号からPLL109から出力されたクロック信号に切り替える(S307)。これにより、ASIC100が高速動作モードとなる。

30

【0045】

そして、本実施形態では、サブCPU103は、メインCPU101のブートデータの検証を行う(S308)。例えば、CPU103は、予め格納部104に格納しておいた正解値と格納部102に記憶されたブートデータのハッシュ値とを比較して、一致すればブートデータの改ざんがなかったと判定し、一致しなかったらブートデータの改ざんがあったと判定する。なお、ブートデータの改ざんの検知方法については、図4及び図5で詳細に説明する。

40

【0046】

ブートデータの改ざんがあったと判定した場合(S309: No)、メインCPU101によるブートデータの実行を行わずに、サブCPU103は、ユーザや管理者に改ざんがあった旨を通知する(S310)。通知方法は、不図示のLED(光出力手段)の点灯等であっても良いし、音による通知であっても良い。

【0047】

ブートデータの改ざんがなかったと判定した場合(S309: Yes)、サブCPU103は、クロック選択部110の出力を、PLL109から出力されたクロック信号から発振器108から出力されたクロック信号に切り替える(S311)。これにより、ASIC100が低速動作モードとなる。

50

**【0048】**

そして、サブCPU103は、メインCPU101及びその他の各回路のリセットを解除する(S312)。これにより、メインCPU101のブートが開始する。

**【0049】**

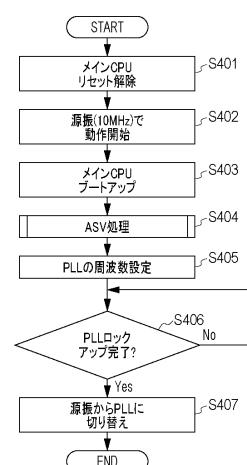

<メインCPUの動作フロー>

図4は、メインCPU101が実行する処理を示したフローチャートである。

**【0050】**

メインCPU101のリセットが解除されると(S401)、メインCPU101は、発振器108から出力されるクロック信号で動作を開始する(S402)。メインCPU101は、格納部102に格納されているブートデータを実行する(S403)。このブートデータは、検証済みであり、改ざんがなかったと判定されたものである。そして、本実施形態では、メインCPU101は、ASV処理を実行する(S404)。ASV処理の詳細な説明は、図6、図7及び図8で行う。

10

**【0051】**

ASV処理が終了すると、メインCPU101は、PLL109が、1200MHzのクロック信号を出力するように設定する(S405)。その後、メインCPU101は、PLL109のロックアップタイムが経過したかどうかを判定する(S406)。メインCPU101は、PLL109のロックアップタイムが経過したと判定すると(S406: Yes)、クロック選択部110の出力を、発振器108から出力されたクロック信号をPLL109から出力されたクロック信号に切り替える(S407)。これにより、ASIC100が高速動作モードとなる。その後、メインCPU101は、データ処理部107でのデータ処理を制御する。

20

**【0052】**

ASIC100が高速動作モードになった時点で、ASIC100の各種設定は、データ処理部にて実行する各種データ処理用の設定が行われている。また、メインCPU101の電源電圧は、メインCPU101のプロセスに適した電圧に変更されているため、メインCPU101は、各種のデータ処理を実行することができる。

**【0053】**

以上のフローにより、メインCPU101がASV処理を行う前に、サブCPU103がPLL109から出力される高い周波数のクロック信号により改ざん検知処理を行うことができる。改ざん検知処理を短時間で完了させることができると、サブCPU103が改ざん検知処理を終了した後に、メインCPU101に供給されるクロック信号を発振器108からの低い周波数のクロック信号に切り替えることによって、メインCPU101がASV処理を行うことができる。

30

**【0054】**

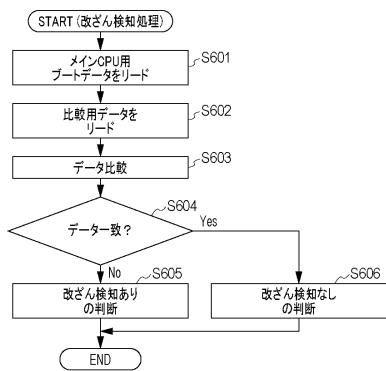

<改ざん検知処理>

次に、図3のS308のブートプログラムの改ざん検知処理の詳細について説明する。図5は、ブートプログラムの検証に関わるブロックの詳細を示した図である。

**【0055】**

格納部102は、メインCPU101用のブートデータ401を格納する。メインCPU101は、リセットが解除されると、格納部102に格納されたメインCPU101用のブートデータ401をリードして実行する。これにより、メインCPU101のブートが開始される。格納部104は、サブCPU103用のブートデータ402を格納する。サブCPU103は、リセットが解除されると、格納部104に格納されたサブCPU103用のブートデータ402をリードして実行する。これにより、サブCPU103のブートが開始される。

40

**【0056】**

また、格納部104は、メインCPU101が実行するブートデータと比較される比較用データ(正解値)を格納する。

**【0057】**

50

図6は、ブートプログラムの検証方法の処理フローを示した図である。

【0058】

サブCPU103は、格納部102に格納されたメインCPU用のブートデータ401の先頭データから、所定のデータ量（例えば、100KByte）のデータをリードする（S601）。リードされたデータは、サブCPU103が持つバッファメモリに格納される。サブCPU103は、格納部102からリードしたデータと同量の比較用データ403をリードする（S602）。そして、サブCPU103は、バッファメモリに格納していたメインCPU101用のブートデータ401と、比較用データ403との比較を行う（S603）。比較結果として、両者が異なる場合（S604：No）は、サブCPU103は、ブートデータ401の改ざんがあったと判定する（S605）。

10

【0059】

一方、比較結果として、両者が一致する場合（S604：Yes）、サブCPU103は、ブートデータ401の改ざんが無かったと判断する（S606）。

【0060】

本実施形態では、メインCPU101用のブートデータ401のそのものと、比較用データ403との比較を行っている。が、メインCPU101用のブートデータ401のハッシュ値を算出し、そのハッシュ値と予め記憶していた正解値とを比較することにより、ブートデータ401の検証を行っても良い。

【0061】

また、本実施形態では、ブートデータ401の一部（100KByte）の検証を行つたが、ブートデータ401の全てを検証しても良い。

20

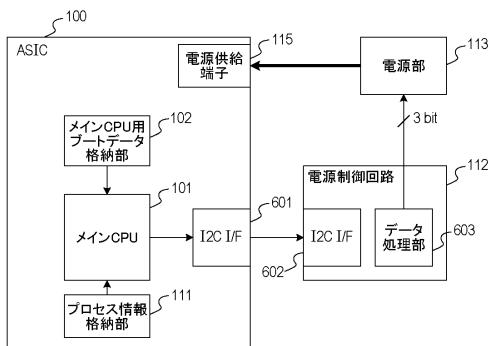

【0062】

<ASV処理>

次に、図3のS304のASV処理の詳細について説明する。図7は、ASV処理に関するブロックの詳細を示した図である。

【0063】

プロセス情報格納部111は、メインCPU101のプロセス情報を格納している。プロセス情報格納部111は、ROMである。本実施形態では、メインCPU101のプロセスがSLOWからFASTまで8段階に分けられており、3ビットのデータがプロセスの情報としてプロセス情報格納部111に格納されている。

30

【0064】

図8は、プロセス情報格納部111に格納される情報の詳細を示した図である。図7に示すように、TYPICALのプロセスを「4」として、3ビットのデータ「100」で表す。そして、最もSLOWのプロセスを「0」として、3ビットのデータ「000」で表す。また、最もFASTのプロセスを「7」として、3ビットのデータ「111」で表す。

【0065】

図7に戻り、電源制御回路112は、プロセス情報格納部111に格納されているプロセス情報を、メインCPU101から受信する。電源制御回路112は、受信したプロセス情報に基づいて、電源部113から出力する電圧を変更するための制御信号を出力する。メインCPU101は、3ビットのデータを電源制御回路112にに出力する。ASIC100と電源制御回路112とは、シリアルバスで接続されている。ASIC100のI2CI（アイ・スクエアード・シー）I/F部601と、電源制御回路112のI2CI/F部602とは、アイ・スクエアード・シーで通信を行う。

40

【0066】

電源制御回路112のデータ処理部603は、I2CI/F部602を介して入力された3ビットのプロセス情報を、3ビットの制御信号として、電源部113に出力する。電源部113は、画像形成装置1の電源オン時は、TYPICAL電圧、つまり、本実施形態では、1.0Vの電圧を出力する。その後、電力供給部113は、電源制御回路112から入力された制御信号に基づいて、電源供給端子115に所定の電圧を供給する。例え

50

ば、図 7 に示すように、メイン C P U 1 0 1 が T Y P I C A L のチップの場合、プロセス情報格納部 1 1 1 から出力される 3 ビットのデータが「1 0 0」となる。そして、メイン C P U 1 0 1 に供給される電源電圧が 1 . 0 V となる。また、メイン C P U 1 0 1 が最も S L O W のプロセスの場合、プロセス情報格納部 1 1 1 から出力される 3 ビットのデータが「0 0 0」となる。そして、メイン C P U 1 0 1 に供給される電源電圧は、1 . 1 2 V (図 8 参照) となる。また、メイン C P U 1 0 1 が最も F A S T のプロセスの場合、プロセス情報格納部 1 1 1 から出力される 3 ビットのデータが「1 1 1」となる。そして、メイン C P U 1 0 1 に供給される電源電圧は、0 . 9 1 V (図 8 参照) となる。

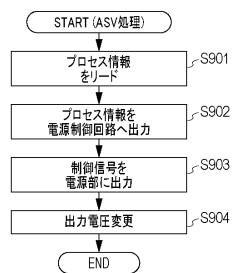

#### 【0 0 6 7】

図 9 は、A S V 处理の詳細を示したフローチャートである。

10

#### 【0 0 6 8】

メイン C P U 1 0 1 は、プロセス情報格納部 1 1 1 から 3 ビットで記録されているプロセス情報をリードする (S 9 0 1)。本実施形態では、プロセス情報格納部 1 1 1 の特定のアドレスのデータを読み出すことにより、3 ビットで記録されているメイン C P U 1 0 1 のプロセス情報をリードする。メイン C P U 1 0 1 は、3 ビットのプロセス情報を電源制御回路 1 1 2 に出力する (S 9 0 2)。本実施形態では、メイン C P U 1 0 1 は、I 2 C のプロトコルに従って、プロセス情報を送信する。

#### 【0 0 6 9】

電源制御回路 1 1 2 は、A S I C 1 0 0 から入力された 3 ビットのプロセス情報を受信する。そして、データ処理部 6 0 3 は、電源部 1 1 3 の出力電圧を変更するための制御信号を、電源部 1 1 3 に出力する (S 9 0 3)。電源部 1 1 3 には、出力電圧を制御するために 3 ビットの入力端子が設けられている。電源部 1 1 3 は、入力端子に入力された制御信号に基づいて、メイン C P U 1 0 1 に供給する電源電圧を調整する (S 9 0 4)。

20

#### 【0 0 7 0】

3 ビットの制御信号と電源部 1 1 3 が output する電源電圧との関係は、図 8 に示している。3 ビットのデータが「1 0 0」の場合、電源部 1 1 3 は、メイン C P U 1 0 1 に 1 . 0 V を出力する。また、3 ビットのデータが「1 1 0」の場合、電源部 1 1 3 は、メイン C P U 1 0 1 に 0 . 9 4 V を出力する。

#### 【0 0 7 1】

( その他の実施例 )

30

上記した実施形態では、クロック選択部 1 1 0 は、発振器 1 0 8 から供給されたクロック信号又は P L L 1 0 9 から供給されたクロック信号の何れかを出力する。クロック選択部 1 1 0 は、周波数が異なる 3 つ以上のクロック信号が入力され、そのうちの何れか 1 つを出力するものであっても良い。

#### 【0 0 7 2】

例えば、クロック選択部 1 1 0 は、サブ C P U 1 0 3 によるブートデータの検証時に 1 2 0 0 M H z のクロック信号をサブ C P U 1 0 3 出力し、メイン C P U 1 0 1 による A S V 处理時に 1 0 M H z のクロック信号をメイン C P U 1 0 1 に出力する。そして、クロック選択部 1 1 0 は、A S V 处理が完了したら、メイン C P U 1 0 1 に 1 2 0 0 M H z のクロック信号を出力する。クロック選択部 1 1 0 は、出力するクロック信号の周波数が高速、低速、高速の順になれば、周波数は 1 0 M H z や 1 2 0 0 M H z に限定されない。ブートデータの検証時のクロック信号の周波数は、A S V 处理完了後のクロック信号の周波数と同じでなくても構わない。

40

#### 【0 0 7 3】

上記した実施形態では、本発明の情報処理装置の一例として画像形成装置 1 0 0 について説明したが、本発明の情報処理装置は、画像形成装置でなくても構わない。例えば、本発明の画像形成装置は、パーソナルコンピュータ、タブレット、スマートフォン、ゲーム機、遊技機、空気調和機、A T M であっても良い。

#### 【0 0 7 4】

また、本発明の目的は、前述した実施形態の機能を実現するソフトウェアのプログラム

50

コードを記録した記録媒体を、システムあるいは装置に供給するよう構成することによっても達成される。この場合、そのシステムあるいは装置のコンピュータ（またはC P UやM P U）が記録媒体に格納されたプログラムコードを読み出し実行することにより、上記機能が実現されることとなる。なお、この場合、そのプログラムコードを記憶した記録媒体は本発明を構成することになる。

【0075】

プログラムコードを供給するための記録媒体としては、例えば、フレキシブルディスク、ハードディスク、光ディスク、光磁気ディスク、C D - R O M、C D - R、磁気テープ、不揮発性のメモリカード、R O Mなどを用いることができる。

【0076】

また、コンピュータが読み出したプログラムコードを実行することにより、前述した実施形態の機能が実現される場合に限られない。例えば、そのプログラムコードの指示に基づき、コンピュータ上で稼働しているO S（オペレーティングシステム）などが実際の処理の一部または全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれる。

10

【0077】

さらに、記録媒体から読み出されたプログラムコードが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書込まれた後、前述した実施形態の機能が実現される場合も含まれる。つまり、プログラムコードがメモリに書込まれた後、そのプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるC P Uなどが実際の処理の一部または全部を行い、その処理によって実現される場合も含まれる。

20

【符号の説明】

【0078】

1 画像形成装置

101 メインC P U（実行手段）

103 サブC P U（検証手段）

30

40

50

【図面】

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

10

20

【図7】

| プロセス    | プロセス段階 | 格納情報 (3bit) | 電源電圧 (V) |

|---------|--------|-------------|----------|

| SLOW    | 0      | 000         | 1.12     |

| ↑       | 1      | 001         | 1.09     |

| ↑       | 2      | 010         | 1.06     |

| ↑       | 3      | 011         | 1.03     |

| TYPICAL | 4      | 100         | 1.00     |

| ↓       | 5      | 101         | 0.97     |

| ↓       | 6      | 110         | 0.94     |

| FAST    | 7      | 111         | 0.91     |

30

40

50

【図 9】

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類

**G 0 6 F** 21/64 (2013.01)

**F I**

**G 0 6 F** 21/64

(56)参考文献

特開2012-078952 (JP, A)

米国特許出願公開第2005/0138409 (US, A1)

米国特許出願公開第2016/0320827 (US, A1)

(58)調査した分野 (Int.Cl. , DB名)

**G 0 6 F** 21/12

**G 0 6 F** 1/08

**H 0 4 N** 1/00

**B 4 1 J** 29/38

**B 4 1 J** 29/42

**G 0 6 F** 21/64