(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2017년09월25일

(11) 등록번호 10-1781057

(24) 등록일자 2017년09월18일

- (51) 국제특허분류(Int. Cl.)

*G06F 9/30* (2017.01)    *G06F 15/80* (2006.01)

*G06F 9/38* (2006.01)

(52) CPC특허분류

*G06F 9/30036* (2013.01)

*G06F 15/8053* (2013.01)

(21) 출원번호                      10-2016-7015679

(22) 출원일자(국제)              2014년11월14일

심사청구일자                      2017년08월14일

(85) 번역문제출일자              2016년06월13일

(65) 공개번호                      10-2016-0085873

(43) 공개일자                      2016년07월18일

(86) 국제출원번호                PCT/US2014/065825

(87) 국제공개번호                WO 2015/073915

국제공개일자                      2015년05월21일

(30) 우선권주장

14/082,073 2013년11월15일 미국(US)

(56) 선행기술조사문헌

WO2006106342 A1\*

US20070061550 A1\*

US20080140750 A1\*

(73) 특허권자

**퀄컴 인코포레이티드**

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

(72) 발명자

**칸, 라힐**

미국 92121-1714 캘리포니아 샌 디에고 모어하우스 드라이브 5775

(74) 대리인

**특허법인 나에드Law**

(74) 대리인

특허법인 남앤드남

심사관 : 김경완

(54) 발명의 명칭 실행 유닛들과 벡터 데이터 메모리 사이에 병합 회로를 갖는 벡터 프로세싱 엔진, 및 관련된 방법

(57) 윤 악

벡터 데이터 메모리에 저장되는 출력 벡터 데이터의 실시간적인 병합을 제공하기 위해서 실행 유닛들과 벡터 데이터 메모리 사이의 데이터 흐름 경로들에서 병합 회로를 이용하는 벡터 프로세싱 엔진(VPE)들이 개시된다. 관련된 벡터 프로세싱 명령들, 시스템들 및 방법들이 또한 개시된다. VPF에서 실행 유닛들과 벡터 데이터 메모리

(뒤면에 계속)

대표도

사이의 데이터 흐름 경로들에 병합 회로가 제공된다. 병합 회로는 출력 벡터 데이터 샘플 세트가 저장되기 위해서 실행 유닛들로부터 벡터 데이터 메모리로 출력 데이터 흐름 경로들을 통해 제공되고 있는 동안 실시간적으로 벡터 프로세싱 연산들을 수행한 결과로서 실행 유닛들로부터의 출력 벡터 데이터 샘플 세트를 병합하도록 구성된다. 병합된 출력 벡터 데이터 샘플 세트는 실행 유닛들에서 수행될 후속 벡터 프로세싱 연산들을 지원시킬 수 있는 추가적인 사후-프로세싱 단계들을 필요로 하지 않고도 벡터 데이터 메모리에 병합된 형태로 저장된다.

(52) CPC특허분류

*G06F 9/30032* (2013.01)

*G06F 9/3887* (2013.01)

*G06F 9/3897* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

벡터 프로세싱 연산을 실행하는 적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트를 실시간으로(in-flight) 병합하도록 구성되는 벡터 프로세싱 엔진(VPE)으로서,

적어도 하나의 벡터 데이터 파일;

적어도 하나의 실행 유닛; 및

적어도 하나의 병합 회로를 포함하고,

상기 적어도 하나의 벡터 데이터 파일은,

벡터 프로세싱 연산을 위해 적어도 하나의 입력 데이터 흐름 경로에서 입력 벡터 데이터 샘플 세트를 제공하고, 그리고

저장될 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 적어도 하나의 출력 데이터 흐름 경로로부터 수신하도록 구성되고,

상기 적어도 하나의 실행 유닛은 상기 적어도 하나의 입력 데이터 흐름 경로에서 제공되고, 상기 적어도 하나의 실행 유닛은,

상기 적어도 하나의 입력 데이터 흐름 경로를 통해 상기 입력 벡터 데이터 샘플 세트를 수신하고, 그리고

상기 적어도 하나의 출력 데이터 흐름 경로를 통해 상기 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해 상기 입력 벡터 데이터 샘플 세트에 대해 상기 벡터 프로세싱 연산을 실행하도록 구성되고, 그리고

상기 적어도 하나의 병합 회로는,

상기 결과적 출력 벡터 데이터 샘플 세트를 수신하고,

상기 결과적 출력 벡터 데이터 샘플 세트가 상기 적어도 하나의 벡터 데이터 파일에 저장되는 것 없이 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해 상기 수신된 결과적 출력 벡터 데이터 샘플 세트의 결과적 출력 벡터 데이터 샘플들을 병합하고 – 상기 적어도 하나의 병합 회로는, 상기 결과적 출력 벡터 데이터 샘플들을 가산(adding)하는 것, 상기 결과적 출력 벡터 데이터 샘플들 중에서 최대 벡터 데이터 샘플을 결정하는 것, 또는 상기 결과적 출력 벡터 데이터 샘플들 중에서 최소 벡터 데이터 샘플을 결정하는 것에 의해 상기 결과적 출력 벡터 데이터 샘플들을 병합하도록 구성됨 –,

복수의 래치들(latches) 중 선택된 하나 또는 그 초과의 래치들에 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 저장하고, 그리고

상기 적어도 하나의 출력 데이터 흐름 경로를 통해 상기 선택된 하나 또는 그 초과의 래치들에 저장된 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하도록 구성되고, 그리고

상기 적어도 하나의 병합 회로는 상기 복수의 래치들에 대응하는 복수의 병렬 선택기들을 더 포함하고, 상기 적어도 하나의 병합 회로는 상기 복수의 래치들 중 선택된 하나 또는 그 초과의 래치들에 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 저장하도록 상기 복수의 선택기들을 제어하게 구성되는, 벡터 프로세싱 엔진(VPE).

#### 청구항 2

제 1 항에 있어서,

상기 적어도 하나의 벡터 데이터 파일은,

상기 벡터 프로세싱 연산을 위해 상기 적어도 하나의 입력 데이터 흐름 경로에서 상기 적어도 하나의

벡터 데이터 파일의 폭의 입력 벡터 데이터 샘플 세트를 제공하고, 그리고

저장될 상기 적어도 하나의 벡터 데이터 파일의 폭의 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 상기 적어도 하나의 출력 데이터 흐름 경로로부터 수신하도록 구성되는, 벡터 프로세싱 엔진(VPE).

### 청구항 3

제 1 항에 있어서,

상기 적어도 하나의 벡터 데이터 파일은,

상기 적어도 하나의 입력 데이터 흐름 경로에서 적어도 하나의 벡터 데이터 파일 출력을 통해 상기 입력 벡터 데이터 샘플 세트를 제공하고, 그리고

상기 적어도 하나의 출력 데이터 흐름 경로에서 적어도 하나의 벡터 데이터 파일 입력을 통해 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 수신하도록 추가로 구성되고,

상기 적어도 하나의 실행 유닛은,

상기 적어도 하나의 입력 데이터 흐름 경로에서 적어도 하나의 실행 유닛 입력을 통해 상기 입력 벡터 데이터 샘플 세트를 수신하고, 그리고

상기 적어도 하나의 입력 데이터 흐름 경로에서 적어도 하나의 실행 유닛 출력을 통해 상기 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해 상기 입력 벡터 데이터 샘플 세트를 코드 시퀀스 벡터 데이터 샘플 세트와 곱하도록 구성되며, 그리고

상기 적어도 하나의 병합 회로는,

상기 적어도 하나의 실행 유닛으로부터 상기 적어도 하나의 입력 데이터 흐름 경로에서 적어도 하나의 병합 회로 입력을 통해 상기 결과적 출력 벡터 데이터 샘플 세트를 수신하고, 그리고

상기 적어도 하나의 출력 데이터 흐름 경로에서 적어도 하나의 병합 회로 출력을 통해 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하도록 추가로 구성되는, 벡터 프로세싱 엔진(VPE).

### 청구항 4

제 3 항에 있어서,

상기 코드 시퀀스 벡터 데이터 샘플 세트는 적어도 하나의 CDMA 칩 코드 시퀀스를 포함하는, 벡터 프로세싱 엔진(VPE).

### 청구항 5

제 1 항에 있어서,

상기 적어도 하나의 병합 회로는 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해 상기 결과적 출력 벡터 데이터 샘플 세트의 상기 결과적 출력 벡터 데이터 샘플들 중 적어도 두 개를 가산하도록 구성되는 적어도 하나의 가산기를 포함하는, 벡터 프로세싱 엔진(VPE).

### 청구항 6

제 5 항에 있어서,

상기 적어도 하나의 가산기는 가산기 트리(tree)에서 제공되는 복수의 가산기들을 포함하고, 상기 복수의 가산기들의 각각은 상이한 비트 폭을 갖는 복수의 추가 병합된 결과적 출력 벡터 데이터 샘플 세트들을 제공하도록 구성되는, 벡터 프로세싱 엔진(VPE).

### 청구항 7

제 5 항에 있어서,

상기 적어도 하나의 병합 회로는 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트들 중 하나를 선택하

도록 구성되는 병합 선택기를 더 포함하는, 벡터 프로세싱 엔진(VPE).

#### 청구항 8

제 1 항에 있어서,

상기 적어도 하나의 병합 회로는 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해, 두 개의 결과적 출력 벡터 데이터 샘플들 중에서 최대 벡터 데이터 값이 갖는 상기 두 개의 결과적 출력 벡터 데이터 샘플들 중의 하나를 선택하도록 구성되는 적어도 하나의 최대 벡터 데이터 샘플 선택기를 포함하는, 벡터 프로세싱 엔진(VPE).

#### 청구항 9

제 8 항에 있어서,

상기 적어도 하나의 최대 벡터 데이터 샘플 선택기는 상이한 비트 폭을 각각 갖는 복수의 최대 병합된 결과적 출력 벡터 데이터 샘플 세트들을 제공하도록 각각 구성된 복수의 최대 값 데이터 샘플 선택기들을 포함하는, 벡터 프로세싱 엔진(VPE).

#### 청구항 10

제 1 항에 있어서,

상기 적어도 하나의 병합 회로는 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해, 두 개의 결과적 출력 벡터 데이터 샘플들 중에서 최소 벡터 데이터 값이 갖는 상기 두 개의 결과적 출력 벡터 데이터 샘플들 중의 하나를 선택하도록 구성되는 적어도 하나의 최소 벡터 데이터 샘플 선택기를 포함하는, 벡터 프로세싱 엔진(VPE).

#### 청구항 11

제 10 항에 있어서,

상기 적어도 하나의 최소 벡터 데이터 샘플 선택기는 상이한 비트 폭을 각각 갖는 복수의 최소 병합된 결과적 출력 벡터 데이터 샘플 세트들을 제공하도록 각각 구성된 복수의 최소 값 데이터 샘플 선택기들을 포함하는, 벡터 프로세싱 엔진(VPE).

#### 청구항 12

제 1 항에 있어서,

상기 적어도 하나의 병합 회로는 상기 결과적 출력 벡터 데이터 샘플들을 선택적으로 병합하기 위해서 프로그램 가능 병합 데이터 경로 구성 입력에 기초하여 재구성되도록 구성가능한, 벡터 프로세싱 엔진(VPE).

#### 청구항 13

제 12 항에 있어서,

상기 적어도 하나의 병합 회로는 상기 적어도 하나의 실행 유닛에 의해 실행될 상기 VPE의 각각의 클록 사이클에서 상기 결과적 출력 벡터 데이터 샘플들을 선택적으로 병합하기 위해서 상기 프로그램가능 병합 데이터 경로 구성 입력에 기초하여 재구성되도록 추가로 구성되는, 벡터 프로세싱 엔진(VPE).

#### 청구항 14

제 12 항에 있어서,

상기 적어도 하나의 병합 회로는 상기 적어도 하나의 실행 유닛에 의해 실행될 다음 벡터 명령에 따라 상기 결과적 출력 벡터 데이터 샘플들을 선택적으로 병합하기 위해서 상기 프로그램가능 병합 데이터 경로 구성 입력에 기초하여 재구성되도록 추가로 구성되는, 벡터 프로세싱 엔진(VPE).

#### 청구항 15

제 1 항에 있어서,

상기 적어도 하나의 실행 유닛은 상기 적어도 하나의 실행 유닛을 위한 프로그램가능 입력 데이터 흐름 경로 구성에 기초하여 상기 입력 벡터 데이터 샘플 세트로부터의 입력 벡터 데이터 샘플들의 상이한 비트 폭들을 프로세싱하도록 구성가능한, 벡터 프로세싱 엔진(VPE).

### 청구항 16

제 1 항에 있어서,

크로스바(crossbar) 회로를 더 포함하고,

상기 크로스바 회로는 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 상기 복수의 래치들 중 선택된 하나 또는 그 초과의 래치들에 라우팅하도록 구성되어서, 상기 크로스바 회로가, 상기 적어도 하나의 벡터 데이터 파일에서의 저장에 앞서 병합 벡터 프로세싱 연산들의 상이한 반복들 중에 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트가 상기 복수의 래치들에 스택(stack)되는 것을, 허용하도록 구성되게 하는, 벡터 프로세싱 엔진(VPE).

### 청구항 17

적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트를 실시간으로 병합하기 위한 장치로서,

적어도 하나의 벡터 데이터 파일로부터 벡터 프로세싱 연산을 위한 적어도 하나의 입력 데이터 흐름 경로에서 입력 벡터 데이터 샘플 세트를 제공하기 위한 수단;

상기 적어도 하나의 입력 데이터 흐름 경로에 제공되는 적어도 하나의 실행 유닛에서 상기 적어도 하나의 입력 데이터 흐름 경로를 통해 상기 입력 벡터 데이터 샘플 세트를 수신하기 위한 수단;

상기 적어도 하나의 입력 데이터 흐름 경로를 통해 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해서 상기 입력 벡터 데이터 샘플 세트에 대해 상기 벡터 프로세싱 연산을 실행하기 위한 수단;

상기 결과적 출력 벡터 데이터 샘플 세트가 상기 적어도 하나의 벡터 데이터 파일에 저장되는 것 없이 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해 수신된 결과적 출력 벡터 데이터 샘플 세트의 결과적 출력 벡터 데이터 샘플들을 병합하기 위한 수단 – 상기 결과적 출력 벡터 데이터 샘플들을 병합하는 것은 상기 결과적 출력 벡터 데이터 샘플들을 가산하는 것, 상기 결과적 출력 벡터 데이터 샘플들 중에서 최대 벡터 데이터 샘플을 결정하는 것, 또는 상기 결과적 출력 벡터 데이터 샘플들 중에서 최소 벡터 데이터 샘플을 결정하는 것을 포함함 –;

복수의 래치들 중 선택된 하나 또는 그 초과의 래치들에 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 저장하기 위한 수단;

상기 적어도 하나의 출력 데이터 흐름 경로를 통해 상기 선택된 하나 또는 그 초과의 래치들에 저장된 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위한 수단; 및

상기 적어도 하나의 출력 데이터 흐름 경로로부터의 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 상기 적어도 하나의 벡터 데이터 파일에 저장하기 위한 수단을 포함하고,

상기 병합하기 위한 수단은 상기 복수의 래치들에 대응하는 복수의 병렬 선택기들을 포함하고, 상기 병합하기 위한 수단은 상기 복수의 래치들 중 선택된 하나 또는 그 초과의 래치들에 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 저장하도록 상기 복수의 선택기들을 제어하게 구성되는, 적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트를 실시간으로 병합하기 위한 장치.

### 청구항 18

벡터 프로세싱을 실행하는 적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트의 실시간 병합 방법으로서,

벡터 프로세싱 연산을 위해 적어도 하나의 입력 데이터 흐름 경로에서 적어도 하나의 벡터 데이터 파일로부터 입력 벡터 데이터 샘플 세트를 제공하는 단계;

상기 적어도 하나의 입력 데이터 흐름 경로에 제공되는 적어도 하나의 실행 유닛에서 상기 적어도 하나의 입력

데이터 흐름 경로를 통해 상기 입력 벡터 데이터 샘플 세트를 수신하는 단계;

상기 적어도 하나의 입력 데이터 흐름 경로를 통해 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해서 상기 입력 벡터 데이터 샘플 세트에 대해 상기 벡터 프로세싱 연산을 실행하는 단계;

상기 결과적 출력 벡터 데이터 샘플 세트가 상기 적어도 하나의 벡터 데이터 파일에 저장되는 것 없이 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해 상기 결과적 출력 벡터 데이터 샘플 세트의 결과적 출력 벡터 데이터 샘플들을 적어도 하나의 병합 회로에 의해 병합하는 단계 – 상기 결과적 출력 벡터 데이터 샘플들을 병합하는 것은 상기 결과적 출력 벡터 데이터 샘플들을 가산하는 것, 상기 결과적 출력 벡터 데이터 샘플들 중에서 최대 벡터 데이터 샘플을 결정하는 것, 또는 상기 결과적 출력 벡터 데이터 샘플들 중에서 최소 벡터 데이터 샘플을 결정하는 것을 포함함 –;

복수의 래치들 중 선택된 하나 또는 그 초과의 래치들에 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 저장하는 단계 – 상기 복수의 래치들 중 선택된 하나 또는 그 초과의 래치들에 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 저장하는 것은, 상기 벡터 프로세싱 연산의 제어하에 상기 복수의 래치들에 대응하는 복수의 병렬 선택기들을 사용하여 상기 선택된 하나 또는 그 초과의 래치들을 선택하는 것을 포함함 –;

상기 적어도 하나의 출력 데이터 흐름 경로를 통해 상기 선택된 하나 또는 그 초과의 래치들에 저장된 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하는 단계; 및

상기 적어도 하나의 출력 데이터 흐름 경로로부터의 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 상기 적어도 하나의 벡터 데이터 파일에 저장하는 단계를 포함하는, 벡터 프로세싱을 실행하는 적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트의 실시간 병합 방법.

## 청구항 19

제 18 항에 있어서,

상기 결과적 출력 벡터 데이터 샘플들을 병합하는 것은, 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해 적어도 하나의 가산기에서 상기 결과적 출력 벡터 데이터 샘플들 중 두 개를 가산하는 것을 포함하는, 벡터 프로세싱을 실행하는 적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트의 실시간 병합 방법.

## 청구항 20

제 19 항에 있어서,

상기 적어도 하나의 가산기는 가산기 트리에서 제공되는 복수의 가산기들을 포함하고, 상기 복수의 가산기들의 각각은 상이한 비트 폭을 각각 갖는 복수의 병합된 결과적 출력 벡터 데이터 샘플 세트들을 제공하도록 구성되는, 벡터 프로세싱을 실행하는 적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트의 실시간 병합 방법.

## 청구항 21

제 20 항에 있어서,

상기 적어도 하나의 출력 데이터 흐름 경로에서 상기 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트로서 제공하기 위해서 상기 복수의 병합된 결과적 출력 벡터 데이터 샘플 세트들 중 하나를 선택하는 단계를 더 포함하는, 벡터 프로세싱을 실행하는 적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트의 실시간 병합 방법.

## 청구항 22

제 18 항에 있어서,

프로그램가능 병합 데이터 경로 구성 입력을 수신하는 단계; 및

상기 프로그램가능 병합 데이터 경로 구성 입력에 기초하여 상기 결과적 출력 벡터 데이터 샘플 세트를 선택적으로 병합하는 단계를 더 포함하는, 벡터 프로세싱을 실행하는 적어도 하나의 실행 유닛에 의해 생성된 결과적

출력 벡터 데이터 샘플 세트의 실시간 병합 방법.

### 청구항 23

제 22 항에 있어서,

상기 적어도 하나의 실행 유닛에 의해 실행될 VPE의 각각의 클록 사이클에서 상기 결과적 출력 벡터 데이터 샘플들을 선택적으로 병합하는 단계를 더 포함하는, 벡터 프로세싱을 실행하는 적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트의 실시간 병합 방법.

### 청구항 24

제 22 항에 있어서,

상기 적어도 하나의 실행 유닛에 의해 실행될 다음 벡터 명령에 대해 상기 결과적 출력 벡터 데이터 샘플들을 선택적으로 병합하는 단계를 더 포함하는, 벡터 프로세싱을 실행하는 적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트의 실시간 병합 방법.

### 청구항 25

삭제

### 청구항 26

삭제

### 청구항 27

삭제

## 발명의 설명

### 기술 분야

[0001]

본 출원은 “VECTOR PROCESSING ENGINES HAVING PROGRAMMABLE DATA PATH CONFIGURATIONS FOR PROVIDING MULTI-MODE VECTOR PROCESSING, AND RELATED VECTOR PROCESSORS, SYSTEMS, AND METHODS”라는 명칭으로 2013년 3월 13일에 출원된 미국 특허 출원 일련번호 제13/798,641호(123249)와 관련되며, 이 출원은 그 전체가 인용에 의해 본원에 통합된다.

[0002]

본 출원은 “VECTOR PROCESSING CARRY-SAVE ACCUMULATORS EMPLOYING REDUNDANT CARRY-SAVE FORMAT TO REDUCE CARRY PROPAGATION, AND RELATED VECTOR PROCESSORS, SYSTEMS, AND METHODS”라는 명칭으로 2013년 3월 13일에 출원된 미국 특허 출원 일련번호 제13/798,618호(123248)와 관련되며, 이 출원은 그 전체가 인용에 의해 본원에 통합된다.

[0003]

본 출원은 또한 “VECTOR PROCESSING ENGINES (VPEs) EMPLOYING A TAPPED-DELAY LINE(S) FOR PROVIDING PRECISION FILTER VECTOR PROCESSING OPERATIONS WITH REDUCED SAMPLE RE-FETCHING AND POWER CONSUMPTION, AND RELATED VECTOR PROCESSOR SYSTEMS AND METHODS”라는 명칭으로 2013년 11월 15일에 출원된 미국 특허 출원 일련번호 제14/082,075호(124362)와 관련되며, 이 출원은 그 전체가 인용에 의해 본원에 통합된다.

[0004]

본 출원은 또한 “VECTOR PROCESSING ENGINES (VPEs) EMPLOYING A TAPPED-DELAY LINE(S) FOR PROVIDING PRECISION CORRELATION/COVARIANCE VECTOR PROCESSING OPERATIONS WITH REDUCED SAMPLE RE-FETCHING AND POWER CONSUMPTION, AND RELATED VECTOR PROCESSOR SYSTEMS AND METHODS”라는 명칭으로 2013년 11월 15일에 출원된 미국 특허 출원 일련번호 제14/082,079호(124364)와 관련되며, 이 출원은 그 전체가 인용에 의해 본원에 통합된다.

[0005]

본 출원은 또한 “VECTOR PROCESSING ENGINES (VPEs) EMPLOYING FORMAT CONVERSION CIRCUITRY IN DATA FLOW PATHS BETWEEN VECTOR DATA MEMORY AND EXECUTION UNITS TO PROVIDE IN-FLIGHT FORMAT-CONVERTING OF INPUT VECTOR DATA TO EXECUTION UNITS FOR VECTOR PROCESSING OPERATIONS, AND RELATED VECTOR PROCESSOR SYSTEMS AND METHODS”라는 명칭으로 2013년 11월 15일에 출원된 미국 특허 출원 일련번호 제14/082,088호(124365)와

관련되며, 이 출원은 그 전체가 인용에 의해 본원에 통합된다.

[0006] 본 출원은 또한 “VECTOR PROCESSING ENGINES (VPEs) EMPLOYING REORDERING CIRCUITRY IN DATA FLOW PATHS BETWEEN EXECUTION UNITS AND VECTOR DATA MEMORY TO PROVIDE IN-FLIGHT REORDERING OF OUTPUT VECTOR DATA STORED TO VECTOR DATA MEMORY, AND RELATED VECTOR PROCESSOR SYSTEMS AND METHODS”라는 명칭으로 2013년 11월 15일에 출원된 미국 특허 출원 일련번호 제14/082,081호(124450)와 관련되며, 이 출원은 그 전체가 인용에 의해 본원에 통합된다.

[0007] 본 출원은 또한 “VECTOR PROCESSING ENGINES (VPEs) EMPLOYING DESPREADING CIRCUITRY IN DATA FLOW PATHS BETWEEN EXECUTION UNITS AND VECTOR DATA MEMORY TO PROVIDE IN-FLIGHT DESPREADING OF SPREAD-SPECTRUM SEQUENCES, AND RELATED VECTOR PROCESSING INSTRUCTIONS, SYSTEMS, AND METHODS”라는 명칭으로 2013년 11월 15일에 출원된 미국 특허 출원 일련번호 제14/082,067호(124363U2)와 관련되며, 이 출원은 그 전체가 인용에 의해 본원에 통합된다.

[0008] 개시내용의 분야는 단일 명령 다중 데이터(SIMD) 프로세서들 및 다중 명령 다중 데이터(MIMD) 프로세서들을 포함하는, 벡터 및 스칼라 연산들을 프로세싱하기 위한 벡터 프로세서들 및 관련 시스템들에 관한 것이다.

## 배경 기술

[0009] 무선 통신 시스템들은 디지털 정보계에서 가장 유행하는 기술들 중 하나가 빠르게 되고 있는 중이다. 기술의 진보로 인해 더 작고 더 강력한 무선 통신 디바이스들이 만들어져 왔다. 예컨대, 무선 컴퓨팅 디바이스들은 보통 휴대용 무선 전화들, 개인휴대단말(PDA)들 및 페이징 디바이스들을 포함하는데, 이들은 작고 경량이어서 사용자가 휴대하기가 용이하다. 특히, 휴대용 무선 전화들, 예컨대 셀룰러 전화들 및 인터넷 프로토콜(IP) 전화들은 무선 네트워크들을 통해 음성 및 데이터 패킷들을 통신할 수 있다. 게다가, 이러한 많은 무선 통신 디바이스들은 다른 타입들의 디바이스들을 포함한다. 예컨대, 무선 전화는 디지털 스틸 카메라, 디지털 비디오 카메라, 디지털 레코더 및/또는 오디오 파일 플레이어를 포함할 수 있다. 또한, 무선 전화들은 인터넷에 액세스하기 위하여 사용될 수 있는 웹 인터페이스를 포함할 수 있다. 게다가, 무선 통신 디바이스들은 지정된 무선 통신 기술 표준들(예컨대, 코드 분할 다중 액세스(CDMA), 광대역 CDMA(WCDMA) 및 롱 텀 에벌루션(LTE))에 따라 고속 무선 통신 데이터를 프로세싱하기 위한 복합 프로세싱 자원들을 포함할 수 있다. 따라서, 이들 무선 통신 디바이스들은 중요한 컴퓨팅 능력들을 포함한다.

[0010] 무선 컴퓨팅 디바이스들이 더 작고 더 강력해짐에 따라, 무선 컴퓨팅 디바이스들은 점점 더 자원에 의해 제약을 받는다. 예컨대, 스크린 크기, 이용가능한 메모리 및 파일 시스템 공간량, 및 입출력량의 능력들이 디바이스의 작은 크기에 의해 제한받을 수 있다. 게다가, 배터리 크기, 배터리에 의해 공급되는 전력량 및 배터리 수명이 또한 제한받는다. 디바이스의 배터리 수명을 증가시키기 위한 하나의 방법은 전력을 덜 소비하는 프로세서들을 설계하는 것이다.

[0011] 이와 관련하여, 베이스밴드 프로세서들은 벡터 프로세서들을 포함하는 무선 통신 디바이스들을 위해 사용될 수 있다. 벡터 프로세서들은 벡터들, 즉 데이터의 어레이들에 대해 실행되는 고레벨 연산들을 제공하는 벡터 아키텍처를 가진다. 벡터 프로세싱은 하나의 데이터 세트에 대하여 벡터 명령을 실행하고 이후 벡터 내의 후속 엘리먼트들에 대해 벡터 명령을 재패치(re-fetching) 및 디코딩하는 것과 대조적으로, 벡터 명령을 한번 패치하고 이후 데이터 엘리먼트들의 전체 어레이에 걸쳐 벡터 명령을 여러 번 실행하는 것을 수반한다. 이러한 프로세스는 프로그램을 실행하는데 필요한 에너지를 감소시키는 것을 가능하게 하는데, 왜냐하면 다른 팩터들 중에서 각각의 벡터 명령은 보다 적은 횟수로 패치될 필요가 있기 때문이다. 벡터 명령들이 다수의 클록 사이클들 동안 긴 벡터들에 대하여 동시에 동작하기 때문에, 단순한 인-오더 벡터 명령 디스패치(in-order vector instruction dispatch)로 고도의 병렬화(parallelism)가 달성될 수 있다.

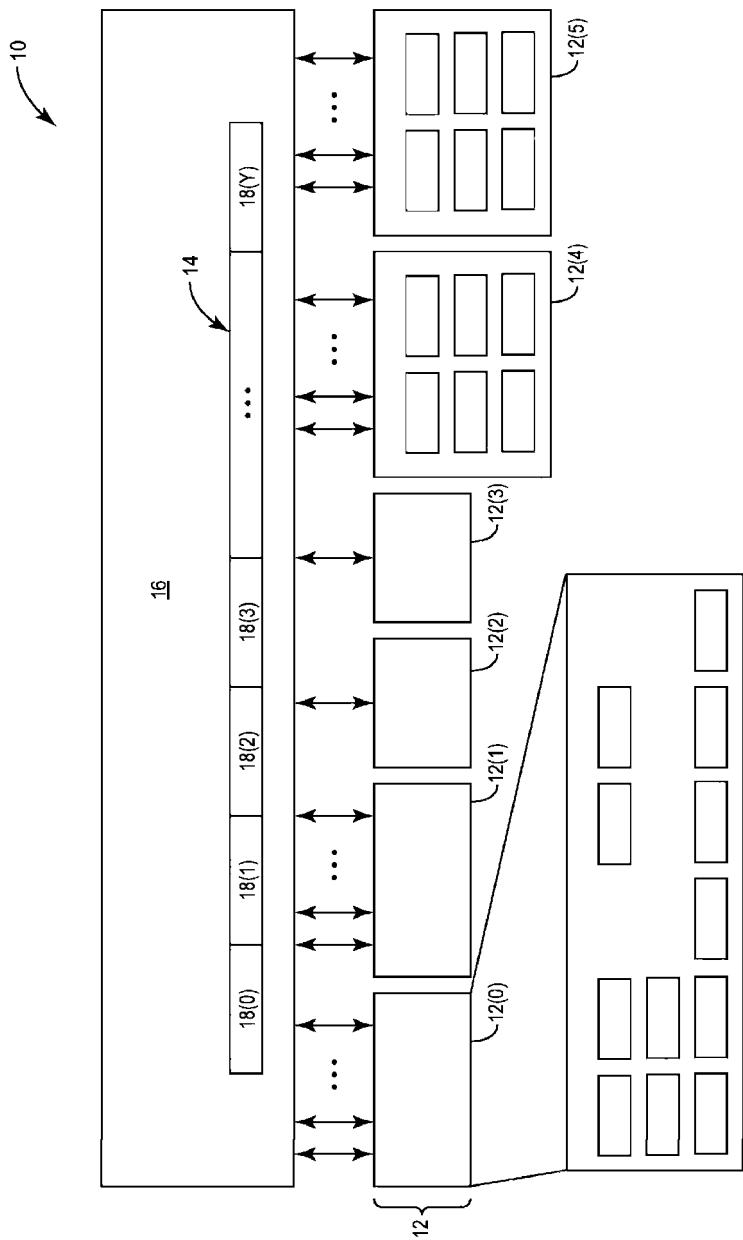

[0012] 도 1은 무선 컴퓨터 디바이스와 같은 컴퓨팅 디바이스에서 사용될 수 있는 예시적인 베이스밴드 프로세서(10)를 예시한다. 베이스밴드 프로세서(10)는 다수의 프로세싱 엔진들(PE들)(12)을 포함하며, 프로세싱 엔진들(PE들) 각각은 특정 애플리케이션들에 대한 기능-특정 벡터 프로세싱을 제공하는데 전용된다. 이러한 예에서, 6개의 개별 PE들(12(0)-12(5))이 베이스밴드 프로세서(10)에 제공된다. PE들(12(0)-12(5))은 공유 메모리(16)로부터 PE들(12(0)-12(5))로 제공되는 소정의 X 비트 폭 벡터 데이터(14)에 대한 벡터 프로세싱을 제공하도록 각각 구성된다. 예컨대, 벡터 데이터(14)는 폭이 512 비트일 수 있다. 벡터 데이터(14)는 작은 배수의 X 비트 폭 벡터 데이터 샘플 세트들(18(0)-18(Y))(예컨대, 16 비트 및 32 비트 샘플 세트들)로 정의될 수 있다. 이러한 방식으로, PE들(12(0)-12(5))은 고도의 병렬화를 달성하기 위하여 PE들(12(0)-12(5))에 병렬로 제공되는 다수의

벡터 데이터 샘플 세트들(18)에 대한 벡터 프로세싱을 제공할 수 있다. 각각의 PE(12(0)-12(5))는 벡터 데이터(14)에 대해 프로세싱되는 벡터 명령의 결과들을 저장하기 위한 벡터 레지스터 파일(VR)을 포함할 수 있다.

[0013] 도 1의 베이스밴드 프로세서(10)의 각각의 PE(12(0)-12(5))는 특정 타입들의 소정의 연산들을 효율적으로 수행하도록 특별히 설계된 특정 전용 회로소자 및 하드웨어를 포함한다. 예컨대, 도 1의 베이스밴드 프로세서(10)는 독립된 WCDMA PE들(12(0), 12(1)) 및 LTE PE들(12(4), 12(5))을 포함하는데, 왜냐하면 WCDMA 및 LTE가 상이한 타입들의 전문화된 연산들을 수반하기 때문이다. 따라서, 독립된 WCDMA-특정 PE들(12(0), 12(1)) 및 LTE-특정 PE들(12(4), 12(5))을 제공함으로써, PE들(12(0), 12(1), 12(4), 12(5)) 각각은 고효율 연산을 위하여 WCDMA 및 LTE에 대해 자주 수행되는 기능들에 특정한 전문화된 전용 회로소자를 포함하도록 설계될 수 있다. 이러한 설계는 상당히 많은 비관련 연산들을 지원하도록 융통성이 있으나 덜 효율적인 방식으로 설계된 더 일반적인 회로소자 및 하드웨어를 포함하는 스칼라 프로세싱 엔진들과 대조적이다.

[0014] 특정한 무선 베이스밴드 연산들은 이전의 프로세싱 연산들로부터 결정된 데이터 샘플들의 병합을 요구한다. 예컨대, 그것은 실행 유닛들의 데이터 경로들보다 더 넓은 가변 폭들의 벡터 데이터 샘플들을 누산시키기 위해 요구될 수 있다. 다른 예로서, 그것은 벡터 프로세싱 연산들에서 출력 벡터 데이터의 병합을 제공하기 위해, 상이한 실행 유닛들로부터의 출력 벡터 데이터 샘플들의 내적 곱셈을 제공하기 위해 요구될 수 있다. 이러한 벡터 프로세싱 연산들에서의 벡터 데이터 샘플들은 벡터 데이터 레인들을 크로스하는 데이터 경로들을 제공하는 복잡한 라우팅을 포함할 수 있다. 그러나, 이는 복잡성을 증가시키고, 그리고 상이한 벡터 데이터 레인들을 크로스 오버하여 병합될 출력 벡터 데이터의 병렬화 어려움들 때문에, 벡터 프로세싱 엔진(VPE)의 효율성을 감소시킬 수 있다. 벡터 프로세서들은, 실행 유닛들로부터 벡터 데이터 메모리로 저장되는 출력 벡터 데이터의 사후-프로세싱 병합을 수행하는 회로를 또한 포함할 수 있다. 벡터 데이터 메모리에 저장된, 사후-프로세싱된 출력 벡터 데이터 샘플들은 벡터 데이터 메모리로부터 폐지되고, 원하는 대로 병합되며, 그리고 다시 벡터 데이터 메모리에 저장된다. 그러나, 이러한 사후-프로세싱은 VPE의 후속 벡터 프로세싱 연산들을 지연시킬 수 있고, 그리고 실행 유닛들의 계산 컴포넌트들이 충분히 이용되지 않게 할 수 있다.

### 발명의 내용

[0015] 본원에 개시된 실시예들은 벡터 데이터 메모리에 저장될 출력 벡터 데이터의 실시간 병합을 제공하기 위해서 실행 유닛들과 벡터 데이터 메모리 사이의 데이터 흐름 경로들에서 병합 회로를 이용하는 벡터 프로세싱 엔진들(VPE들)을 포함한다. 관련된 벡터 프로세싱 명령들, 시스템들 및 방법들이 또한 개시된다. 병합 회로는 VPE의 벡터 데이터 메모리와 실행 유닛들 사이의 데이터 흐름 경로들에 제공된다. 병합 회로는, 출력 벡터 데이터 샘플 세트가 저장되기 위해 실행 유닛들로부터 출력 데이터 흐름 경로들을 통해 벡터 데이터 메모리로 제공되고 있는 동안에 실시간으로 벡터 프로세싱 연산들을 수행하는 결과로서 실행 유닛들로부터의 출력 벡터 데이터 샘플 세트를 병합하도록 구성된다. 출력 벡터 데이터 샘플 세트들의 실시간 병합은, 실행 유닛들에 의해 제공되는 출력 벡터 데이터 샘플 세트의 원하는 프로그래밍된 출력 벡터 데이터 샘플들이 벡터 데이터 메모리에 저장되기 이전에 병합될 수 있고, 따라서 출력 벡터 데이터 샘플 세트가 벡터 데이터 메모리에 병합된 포맷으로 저장됨을 의미한다. 비제한적인 예로서, 출력 벡터 데이터의 병합은 병합된 출력 벡터 데이터 샘플 세트들 및 출력 스칼라 데이터 샘플 세트를 제공하기 위해 출력 벡터 데이터 샘플 세트들을 추가하는 것을 포함할 수 있다. 또 다른 비제한적인 예로서, 출력 벡터 데이터 샘플 세트들의 병합은 실행 유닛들로부터의 비교되는 출력 벡터 데이터 샘플 세트들 간의 최대 및/또는 최소 출력 벡터 데이터를 생성하는 것을 포함할 수 있다. 병합된 출력 벡터 데이터 샘플 세트는 실행 유닛들에서 수행될 후속 벡터 프로세싱 연산들을 지연시킬 수 있는 추가적인 사후-프로세싱 단계들을 필요로 하지 않고 벡터 데이터 메모리에 병합된 형태로 저장된다.

[0016] 따라서, VPE에서 데이터 흐름 경로들의 효율성이 출력 벡터 데이터의 병합에 의해 제한되지 않는다. 실행 유닛들에서 후속 벡터 프로세싱은 출력 벡터 데이터 샘플 세트들이 벡터 데이터 메모리에 병합된 형태로 저장되어야 할 때 데이터 흐름 제한들에 의해서 보다는 계산 자원들에 의해서만 단지 제한된다. VPE는 실행 유닛들의 계산 엘리먼트들의 효율성에 영향을 주지 않으면서 벡터 데이터 메모리의 원하는 목적 위치에 병합된 인트라-벡터 출력 벡터 데이터 샘플 세트들을 제공하도록 또한 구성된다.

[0017] 이와 관련하여, 일 실시예에서, 벡터 프로세싱 연산을 실행하는 적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트를 실시간으로 병합하도록 구성된 VPE가 제공된다. VPE는 적어도 하나의 벡터 데이터 파일을 포함한다. 벡터 데이터 파일(들)은 벡터 프로세싱 연산을 위해 적어도 하나의 입력 데이터 흐름 경로에서 폐지된 입력 벡터 데이터 샘플 세트를 제공하도록 구성된다. 벡터 데이터 파일(들)은 또한 적어도 하나의 출력 데이터 흐름 경로로부터 저장될 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 수신하도록

록 구성된다. VPE는 또한 적어도 하나의 입력 데이터 흐름 경로에 제공되는 적어도 하나의 실행 유닛을 포함한다. 실행 유닛(들)은 적어도 하나의 입력 데이터 흐름 경로를 통해 입력 벡터 데이터 샘플 세트를 수신하도록 구성된다. 실행 유닛(들)은 또한 적어도 하나의 출력 데이터 흐름 경로를 통해 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해서 입력 벡터 데이터 샘플 세트에 대해 벡터 프로세싱 연산을 실행하도록 구성된다. VPE는 또한 적어도 하나의 병합 회로를 포함한다. 병합 회로는 또한 결과적 출력 벡터 데이터 샘플 세트가 적어도 하나의 벡터 데이터 파일에 저장되지 않고 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해 결과적 출력 벡터 데이터 샘플 세트를 병합하도록 구성된다. 병합 회로는 또한 적어도 하나의 출력 데이터 흐름 경로를 통해 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하도록 구성된다.

[0018] 다른 실시예에서, 벡터 프로세싱 연산을 실행하는 적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트를 실시간으로 병합하도록 구성된 VPE가 제공된다. VPE는 적어도 하나의 벡터 데이터 파일 수단을 포함한다. 벡터 데이터 파일 수단은 벡터 프로세싱 연산을 위해 적어도 하나의 입력 데이터 흐름 경로 수단에서 패치된 입력 벡터 데이터 샘플 세트를 제공하기 위한 수단을 포함한다. 벡터 데이터 파일 수단은 또한 적어도 하나의 출력 데이터 흐름 경로 수단으로부터 저장될 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 수신하기 위한 수단을 포함한다. VPE는 또한 적어도 하나의 입력 데이터 흐름 경로 수단에 제공되는 적어도 하나의 실행 유닛 수단을 포함한다. 실행 유닛 수단은 적어도 하나의 입력 데이터 흐름 경로 수단을 통해 입력 벡터 데이터 샘플 세트를 수신하기 위한 수단을 포함한다. 실행 유닛 수단은 또한 적어도 하나의 입력 데이터 흐름 경로 수단을 통해 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해서 입력 벡터 데이터 샘플 세트에 대해 벡터 프로세싱 연산을 실행하기 위한 수단을 포함한다.

[0019] 게다가, VPE는 또한 적어도 하나의 병합 회로 수단을 포함한다. 병합 회로 수단은 적어도 하나의 입력 데이터 흐름 경로 수단을 통해 결과적 출력 벡터 데이터 샘플 세트를 수신하기 위한 수단을 포함한다. 병합 회로 수단은 또한 결과적 출력 벡터 데이터 샘플 세트가 적어도 하나의 벡터 데이터 파일에 저장되지 않고 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해 결과적 출력 벡터 데이터 샘플 세트를 코드 시퀀스 벡터 데이터 샘플 세트와 병합하기 위한 수단을 포함한다. 병합 회로 수단은 또한 적어도 하나의 출력 데이터 흐름 경로를 통해 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위한 수단을 포함한다.

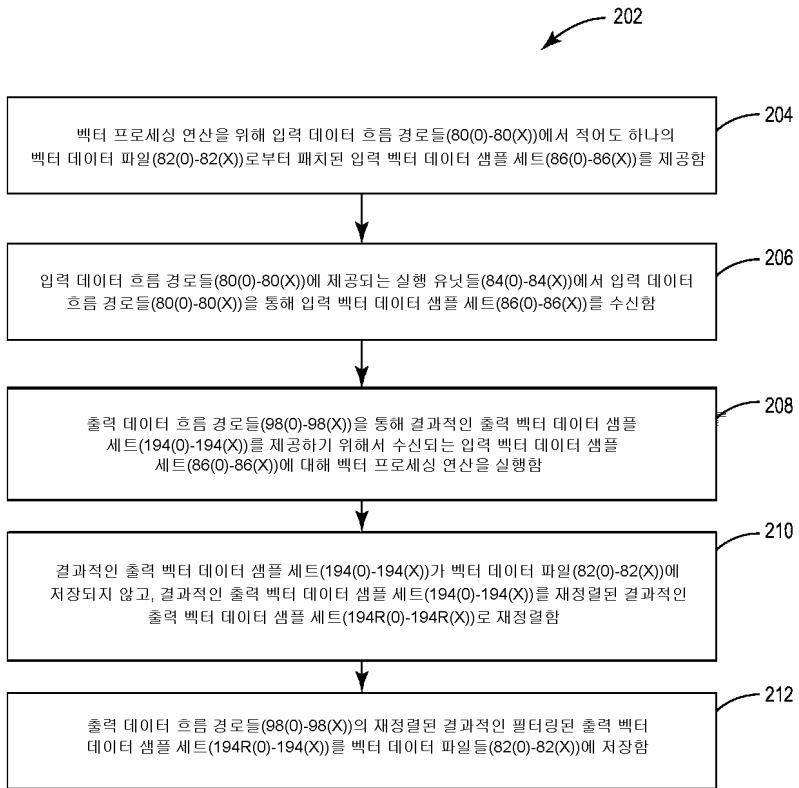

[0020] 다른 실시예에서, 벡터 프로세싱 연산을 실행하는 적어도 하나의 실행 유닛에 의해 생성된 결과적 출력 벡터 데이터 샘플 세트를 실시간으로 병합하는 방법이 제공된다. 방법은 적어도 하나의 벡터 데이터 파일로부터 벡터 프로세싱 연산을 위해 적어도 하나의 입력 데이터 흐름 경로에서 패치된 입력 벡터 데이터 샘플 세트를 제공하는 단계를 포함한다. 방법은 또한 적어도 하나의 입력 데이터 흐름 경로에 제공되는 적어도 하나의 실행 유닛에서 적어도 하나의 입력 데이터 흐름 경로를 통해 패치된 입력 벡터 데이터 샘플 세트를 수신하는 단계를 포함한다. 방법은 또한 적어도 하나의 입력 데이터 흐름 경로를 통해 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해서 입력 벡터 데이터 샘플 세트에 대해 벡터 프로세싱 연산을 실행하는 단계를 포함한다. 방법은 또한 결과적 출력 벡터 데이터 샘플 세트가 적어도 하나의 벡터 데이터 파일에 저장되지 않고 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공하기 위해 결과적 출력 벡터 데이터 샘플 세트를 병합하는 단계를 포함한다. 방법은 또한 적어도 하나의 출력 데이터 흐름 경로로부터의 적어도 하나의 병합된 결과적 출력 벡터 데이터 샘플 세트를 적어도 하나의 벡터 데이터 파일에 저장하는 단계를 포함한다.

## 도면의 간단한 설명

[0021] 도 1은 특정 애플리케이션들에 대한 기능-특정 벡터 프로세싱을 제공하는데 각각 전용되는 다수의 벡터 프로세싱 엔진(VPE)들을 포함하는 예시적인 벡터 프로세서의 개략도이다.

도 2는 VPE에 제공된 공통 회로 및 하드웨어가 별도의 VPE들을 제공할 필요성 없이, 다수의 애플리케이션들 또는 기술들에 대해 매우 효율적인 방식으로 특정 타입들의 벡터 연산들을 수행하기 위해 다수의 모드들에서 프로그래밍될 수 있도록, 프로그램 가능 데이터 경로 구성들을 가지는 VPE를 포함하는 예시적인 기저대역 프로세서의 개략도이다.

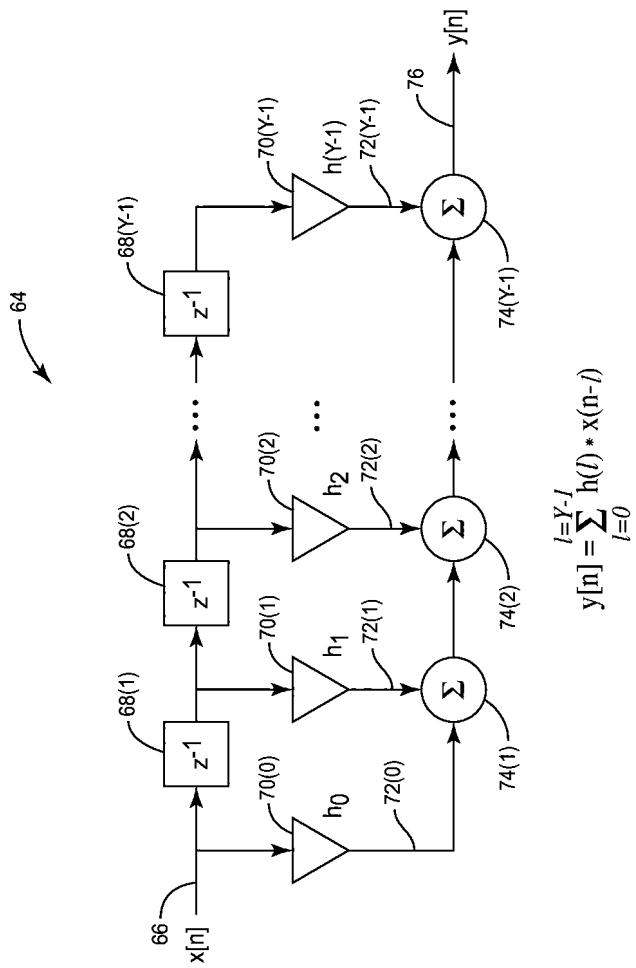

도 3은 VPE에 의해 지원되는 필터 벡터 프로세싱 연산에 제공될 수 있는 이산 유한 임펄스 응답(FIR) 필터의 개략도이다.

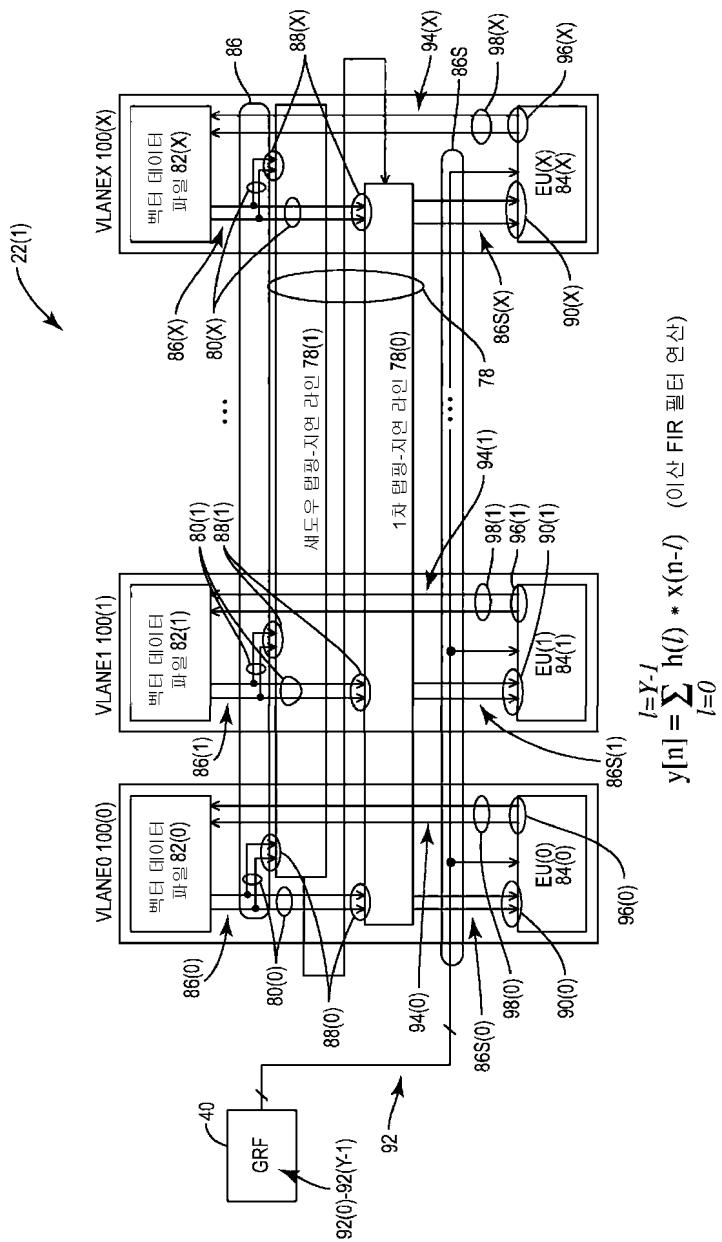

도 4는 감소된 재패치 및 전력 소비를 가진 정밀한 필터 벡터 프로세싱 연산들을 제공하기 위하여 시프트된 입력 벡터 데이터 샘플 세트들을 수신하여 필터 계수 데이터로 프로세싱될 실행 유닛들에 제공하도록 텁抨-지연 라인들을 이용하는 예시적인 VPE의 개략도이다.

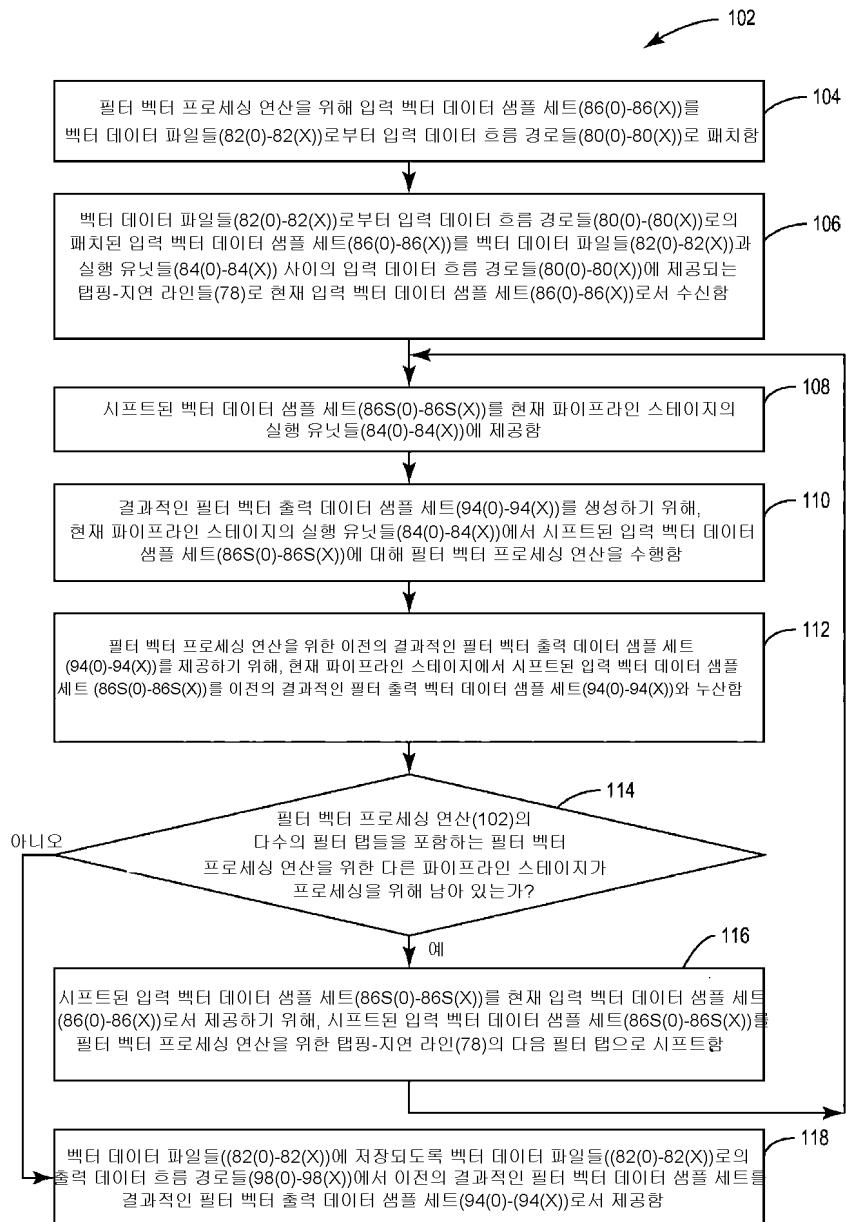

도 5는 예시적인 필터 벡터 명령에 따라 도 4의 VPE에서 수행될 수 있는 예시적인 필터 벡터 프로세싱 연산을 예시하는 흐름도이다.

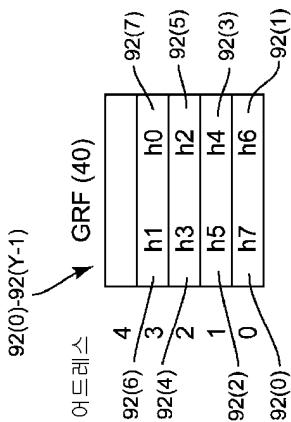

도 6a는 도 4의 VPE의 레지스터 파일에 저장된 필터 텁 계수들의 개략도이다.

도 6b는 도 4의 VPE의 벡터 데이터 파일에 저장된 예시적인 입력 벡터 데이터 샘플 세트들의 개략도이다.

도 7은 도 4의 VPE에서 제공될 수 있는 예시적인 텁핑-지연 라인 및 선택적 새도우 텁핑-지연 라인을 예시하는 개략도이고, 예시적인 텁핑-지연 라인들 각각은 VPE에 의해 수행되는 필터 벡터 프로세싱 연산들 동안 벡터 데이터 메모리로부터의 입력 벡터 데이터 샘플 세트 및 시프트된 입력 벡터 데이터 샘플 세트를 수신하여 실행 유닛들에 제공하기 위한 복수의 파이프라인 레지스터들을 포함한다.

도 8은 필터 벡터 프로세싱 연산 동안 입력 벡터 데이터 샘플 세트에서 입력 벡터 데이터 샘플들의 시프트를 위하여 파이프라인 레지스터들 사이에서 라우팅하는 인트라-레인(intra-lane) 및 인터(inter)-레인을 포함하는, 데이터 레인들의 파이프라인 레지스터들의 예시적인 상세를 예시하는, 도 7의 텁핑-지연 라인들의 보다 예시적인 상세를 예시하는 개략도이다.

도 9a는 예시적인 여덟(8) 텁 필터 벡터 프로세싱 연산의 제 1 필터 텁 실행의 부분으로서 도 4의 VPE에서 1차 텁핑-지연 라인에 처음에 저장된 입력 벡터 샘플 세트의 개략도이다.

도 9b는 도 9a에 예시된 예시적인 여덟(8) 텁 필터 벡터 프로세싱 연산 필터 벡터 프로세싱 연산의 제 1 필터 텁 실행의 부분으로서 도 4의 VPE에서, 새도우 텁핑-지연 라인에 처음에 저장된 새도우 입력 벡터 데이터 샘플 세트 및 레지스터 파일에 저장된 필터 텁 계수들의 개략도이다.

도 9c는 예시적인 여덟(8) 텁 필터 벡터 프로세싱 연산의 제 2 필터 텁 실행의 부분으로서 도 4의 VPE에서, 1차 텁핑-지연 라인 및 새도우 텁핑-지연 라인에 저장된 시프트된 입력 벡터 데이터 샘플 세트들, 및 레지스터 파일에 저장된 필터 텁 계수들의 개략도이다.

도 9d는 예시적인 여덟(8) 텁 필터 벡터 프로세싱 연산의 제 8 필터 텁 실행의 부분으로서 도 4의 VPE에서, 1차 텁핑-지연 라인 및 새도우 텁핑-지연 라인에 저장된 시프트된 입력 벡터 데이터 샘플 세트들, 및 레지스터 파일에 저장된 필터 텁 계수들의 개략도이다.

도 10은 예시적인 여덟(8) 텁 필터 벡터 프로세싱 연산이 완전히 실행된 후 도 4의 VPE에서 실행 유닛들의 누산 기들의 컨텐츠의 개략도이다.

도 11은 감소된 재패치 및 전력 소비로 정확한 상관/공분산 벡터 프로세싱 연산들을 제공하기 위하여 시프트된 입력 벡터 데이터 샘플 세트들을 수신하여 시퀀스 번호 데이터를 가진 프로세싱될 실행 유닛들에 제공하도록 텁핑-지연 라인들을 이용하는 예시적인 VPE의 개략도이다.

도 12a 및 도 12b는 예시적인 상관/공분산 벡터 프로세싱 연산에 따라 패치되고 인터리빙된 정시(on-time) 및 늦은(late) 입력 벡터 데이터 샘플 세트들로 도 11의 VPE에서 병렬로 수행될 수 있는 예시적인 상관/공분산 벡터 프로세싱 연산들을 예시하는 흐름도들이다.

도 13은 도 11의 VPE에서 레지스터 파일에 저장된 상관/공분산 입력 벡터 데이터 샘플 세트의 개략도이다.

도 14는 도 11의 VPE에서 제공될 수 있는 예시적인 텁핑-지연 라인 및 선택적 새도우 텁핑-지연 라인을 예시하는 개략도이고, 예시적인 텁핑-지연 라인들 각각은, VPE에 의해 수행된 상관/공분산 벡터 프로세싱 연산 동안, 벡터 데이터 메모리로부터의 입력 벡터 데이터 샘플 세트 및 시프트된 입력 벡터 데이터 샘플 세트를 수신하여 실행 유닛들에 제공하기 위한 복수의 파이프라인 레지스터들을 포함한다.

도 15a는 상관/공분산 벡터 프로세싱 연산의 제 1 프로세싱 스테이지의 부분으로서 도 11의 VPE에서 1차 텁핑-지연 라인에 처음에 제공된 벡터 데이터 파일로부터의 입력 벡터 데이터 샘플 세트의 개략도이다.

도 15b는 상관/공분산 벡터 프로세싱 연산의 제 1 프로세싱 스테이지의 부분으로서 도 11의 VPE에서 새도우 텁핑-지연 라인에 처음에 저장된 벡터 데이터 파일로부터의 새도우 입력 벡터 데이터 샘플 세트의 개략도이다.

도 15c는 상관/공분산 벡터 프로세싱 연산의 제 2 프로세싱 스테이지의 부분으로서 도 11의 VPE에서, 1차 텁핑-지연 라인 및 새도우 텁핑-지연 라인에 저장된 시프트된 입력 벡터 데이터 샘플 세트들 및 레지스터 파일에 저장된 시프트된 입력 벡터 데이터 샘플 세트의 개략도이다.

도 15d는 상관/공분산 벡터 프로세싱 연산의 제 14 프로세싱 스테이지의 부분으로서 도 11의 VPE에서, 1차 텁핑-지연 라인 및 새도우 텁핑-지연 라인에 저장된 시프트된 입력 벡터 데이터 샘플 세트들, 및 레지스터 파일에 저장된 시프트된 입력 벡터 데이터 샘플 세트의 개략도이다.

도 16은 예시적인 상관/공분산 벡터 프로세싱 연산이 완전히 실행된 후 도 11의 VPE에서 실행 유닛들의 누산기들의 컨텐츠의 개략도이다.

도 17a는 별도로 저장된 결과적 필터 출력 벡터 데이터 샘플들의 실수 및 허수 컴포넌트들로 저장되는 저장된 결과적 필터 출력 벡터 데이터 샘플 세트를 도시하는 예시적인 벡터 데이터 파일들의 다이어그램이다.

도 17b는 별도로 저장된 그의 짹수 및 홀수 결과적 필터 출력 벡터 데이터 샘플들이 저장되어 있는 저장된 결과적 필터 출력 벡터 데이터 샘플 세트를 도시하는 예시적인 벡터 데이터 파일들의 다이어그램이다.

도 18a 및 도 18b는 각각 부호가 붙은 복소수 십육(16) 비트 포맷 및 복소수 여덟(8) 비트 포맷으로 VPE의 벡터 데이터 파일에 저장된 벡터 데이터 샘플 세트의 예시적인 인터리빙된 벡터 데이터 샘플들의 다이어그램들이다.

도 19는 벡터 프로세싱 연산을 실행하기 위하여 포맷-변환된 입력 벡터 데이터 샘플 세트를 적어도 하나의 실행 유닛에 제공하기 위하여, 입력 벡터 데이터 샘플 세트가 벡터 데이터 파일로부터 재패치되도록 요구받지 않고 벡터 데이터 파일과 적어도 하나의 실행 유닛 사이의 적어도 하나의 입력 데이터 흐름 경로에 입력 벡터 데이터 샘플 세트의 실시간(in-flight) 포맷-변환을 제공하도록 구성된 포맷 변환 회로를 이용하는 예시적인 VPE의 개략도이다.

도 20은 도 19의 VPE에서 수행될 수 있는 벡터 데이터 파일과 적어도 하나의 실행 유닛 사이의 적어도 하나의 입력 데이터 흐름 경로에서 입력 벡터 데이터 샘플 세트의 예시적인 실시간 포맷-변환을 예시하는 흐름도이다.

도 21은 도 19의 VPE에서 텁핑-지연 라인들과 실행 유닛들 사이에 제공된 예시적인 포맷 변환 회로의 개략도이고, 포맷 변환 회로는 입력 데이터 흐름 경로의 텁핑-지연 라인들에 의해 실행 유닛들에 제공되는 입력 벡터 데이터 샘플 세트의 실시간 포맷-변환을 제공하도록 구성된다.

도 22는 실행 유닛들에서의 수신 이전에 입력 데이터 흐름 경로에서 입력 벡터 데이터 샘플 세트의 실시간 포맷-변환을 제공하기 위하여 도 19의 VPE에 프로그래밍을 제공하기 위한 예시적인 벡터 명령 데이터 포맷을 예시한다.

도 23은 재정렬된 결과적 출력 데이터 샘플 세트를 제공 및 저장하기 위하여, 결과적 출력 벡터 데이터 샘플 세트가 적어도 하나의 벡터 데이터 파일에 저장되지 않고, 적어도 하나의 실행 유닛과 적어도 하나의 벡터 데이터 파일 사이의 적어도 하나의 출력 데이터 흐름 경로에서 결과적 출력 벡터 데이터 샘플 세트의 실시간 재정렬을 제공하도록 구성된 재정렬 회로를 이용하는 예시적인 VPE의 개략도이다.

도 24는 벡터 데이터 파일에 재정렬된 형태로 저장되도록 도 23의 VPE에서 벡터 데이터 파일과 적어도 하나의 실행 유닛 사이의 적어도 하나의 출력 데이터 흐름 경로에서 출력 벡터 데이터 샘플 세트의 예시적인 실시간 디인터리빙을 예시하는 흐름도이다.

도 25는 벡터 데이터 파일에 저장된 출력 벡터 데이터 샘플 세트들의 실시간 재정렬을 제공하기 위하여 실행 유닛들과 벡터 데이터 파일 사이의 출력 데이터 흐름 경로들에서 재정렬 회로를 이용하는 예시적인 VPE의 개략도이다.

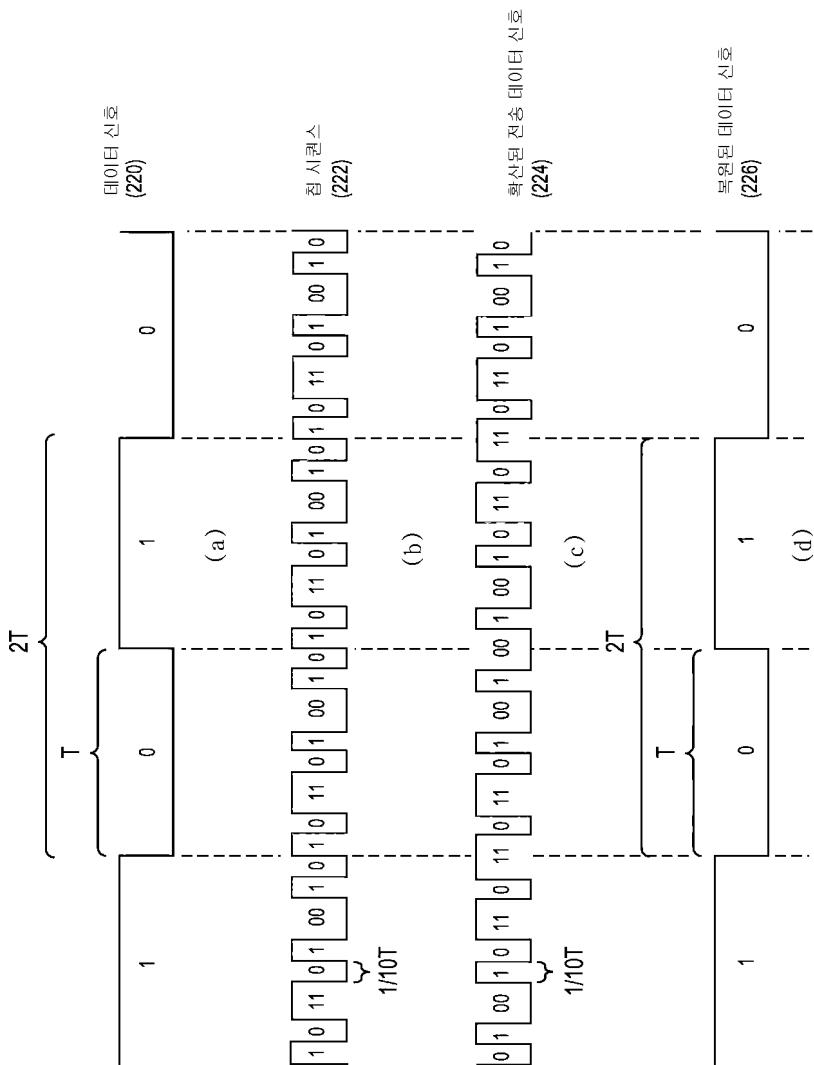

도 26의 a는 통신 신호를 표현하는 예시적인 벡터 데이터 샘플 시퀀스의 다이어그램이다.

도 26의 b는 예시적인 코드 분할 다중 액세스(CDMA) 칩 시퀀스의 다이어그램이다.

도 26의 c는 도 26의 b의 CDMA 칩 시퀀스가 확산된 후 도 26의 a의 벡터 데이터 샘플 시퀀스의 다이어그램이다.

도 26의 d는 도 26의 a의 본래 벡터 데이터 샘플 시퀀스를 복원하기 위하여 도 26의 b의 CDMA 칩 시퀀스를 사용하여 도 26의 c의 확산된 벡터 데이터 샘플 시퀀스를 역확산하는 다이어그램이다.

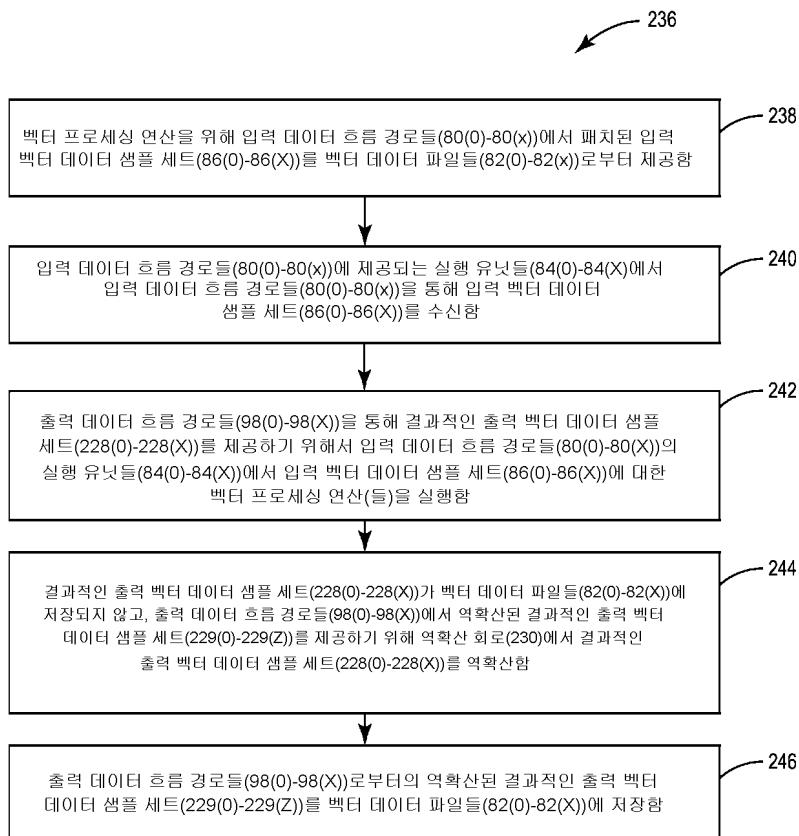

도 27은 역확산된 결과적 출력 벡터 데이터 샘플 세트를 제공 및 저장하기 위하여, 결과적 출력 벡터 데이터 샘플 세트가 적어도 하나의 벡터 데이터 파일에 저장되지 않고, 적어도 하나의 실행 유닛과 적어도 하나의 벡터 데이터 파일 사이의 적어도 하나의 출력 데이터 흐름 경로에서 결과적 출력 벡터 데이터 샘플 세트의 역확산을 제공하도록 구성된 역확산 회로를 이용하는 예시적인 VPE의 개략도이다.

도 28은 적어도 하나의 벡터 데이터 파일에 역화산된 결과적 출력 벡터 데이터 샘플 세트를 제공 및 저장하기 위하여, 도 27의 VPE에서 적어도 하나의 벡터 데이터 파일과 적어도 하나의 실행 유닛 사이의 적어도 하나의 출력 데이터 흐름 경로에서 결과적 출력 벡터 데이터 샘플 세트의 예시적인 역화산을 예시하는 흐름도이다.

도 29는 적어도 하나의 벡터 데이터 파일에 역화산된 결과적 출력 벡터 데이터 샘플 세트들을 제공 및 저장하기 위하여 결과적 출력 벡터 데이터 샘플 세트들의 역화산을 제공하도록 도 27의 VPE에서 적어도 하나의 실행 유닛과 적어도 하나의 벡터 데이터 파일 사이의 출력 데이터 흐름 경로들에서의 예시적인 역화산 회로의 개략도이다.

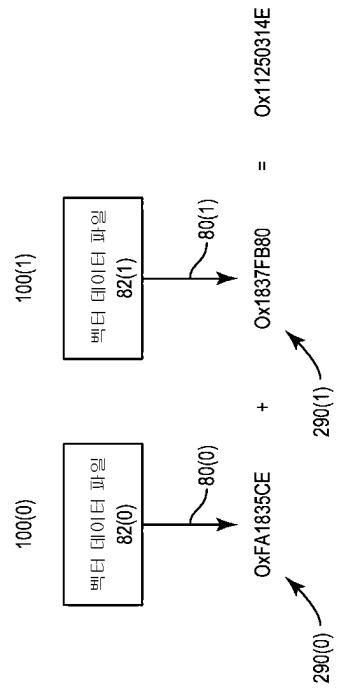

도 30은 병합(merge)될 예시적인 벡터 데이터 샘플 및 병합된 결과적 벡터 데이터 샘플들을 예시하는 다이어그램이다.

도 31은 병합된 결과적 출력 벡터 데이터 샘플 세트를 제공 및 저장하기 위하여, 결과적 출력 벡터 데이터 샘플 세트가 적어도 하나의 벡터 데이터 파일에 저장되지 않고, 적어도 하나의 실행 유닛과 적어도 하나의 벡터 데이터 파일 사이의 적어도 하나의 출력 데이터 흐름 경로에서 결과적 출력 벡터 데이터 샘플 세트의 병합을 제공하도록 구성된 병합 회로를 이용하는 예시적인 VPE의 개략도이다.

도 32는 벡터 데이터 파일 내 가산-병합된 결과적 출력 벡터 데이터 샘플 세트를 제공 및 저장하기 위하여, 도 31의 VPE에서 벡터 데이터 파일과 적어도 하나의 실행 유닛 사이의 적어도 하나의 출력 데이터 흐름 경로에서 결과적 출력 벡터 데이터 샘플 세트의 예시적인 가산-병합을 예시하는 흐름도이다.

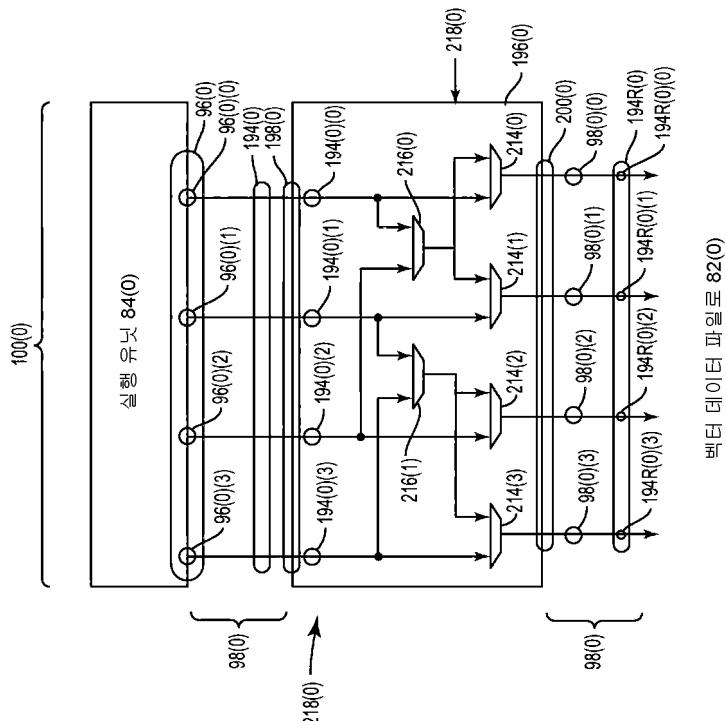

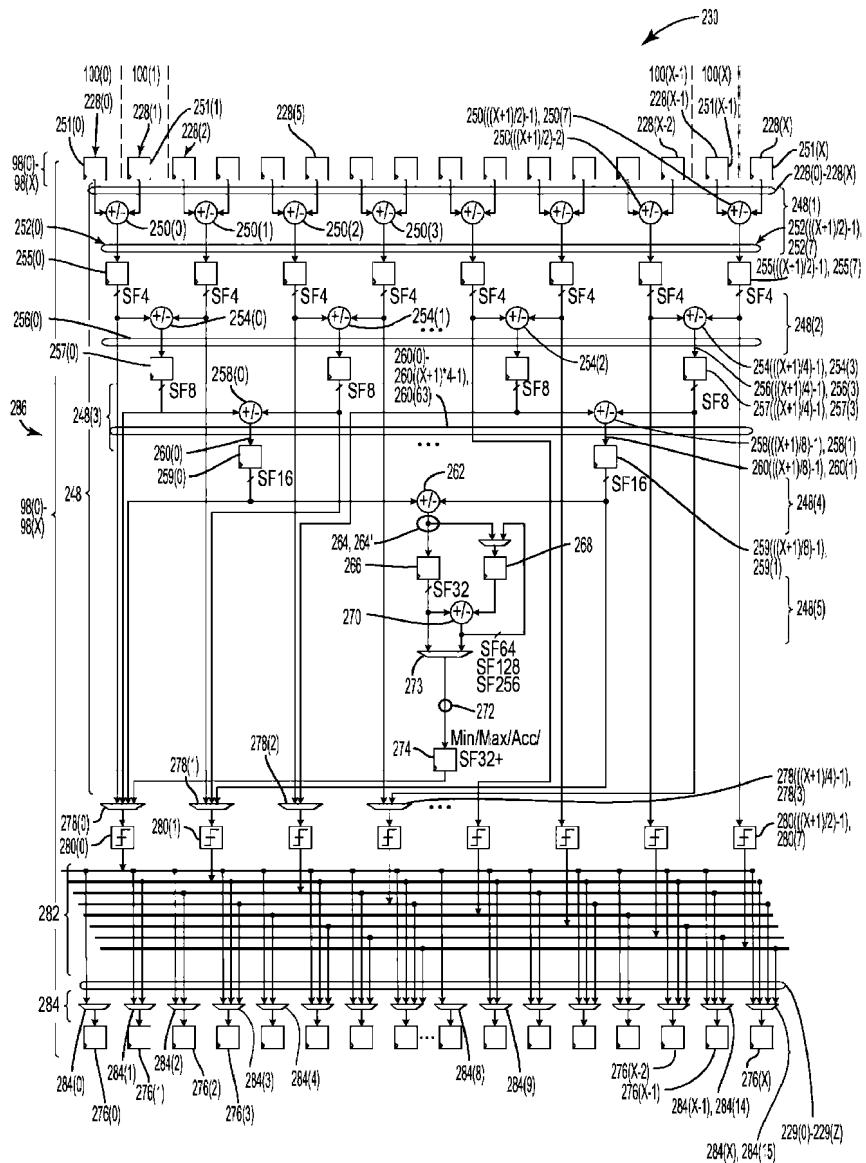

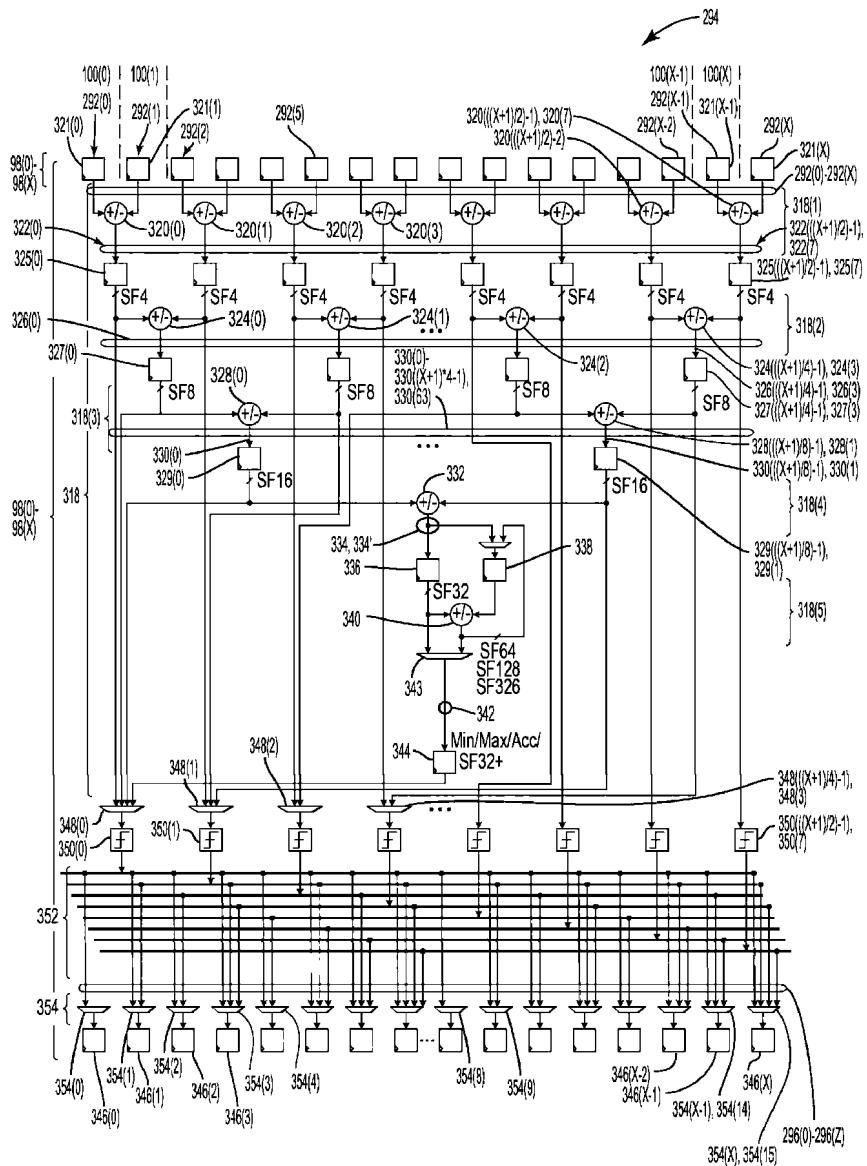

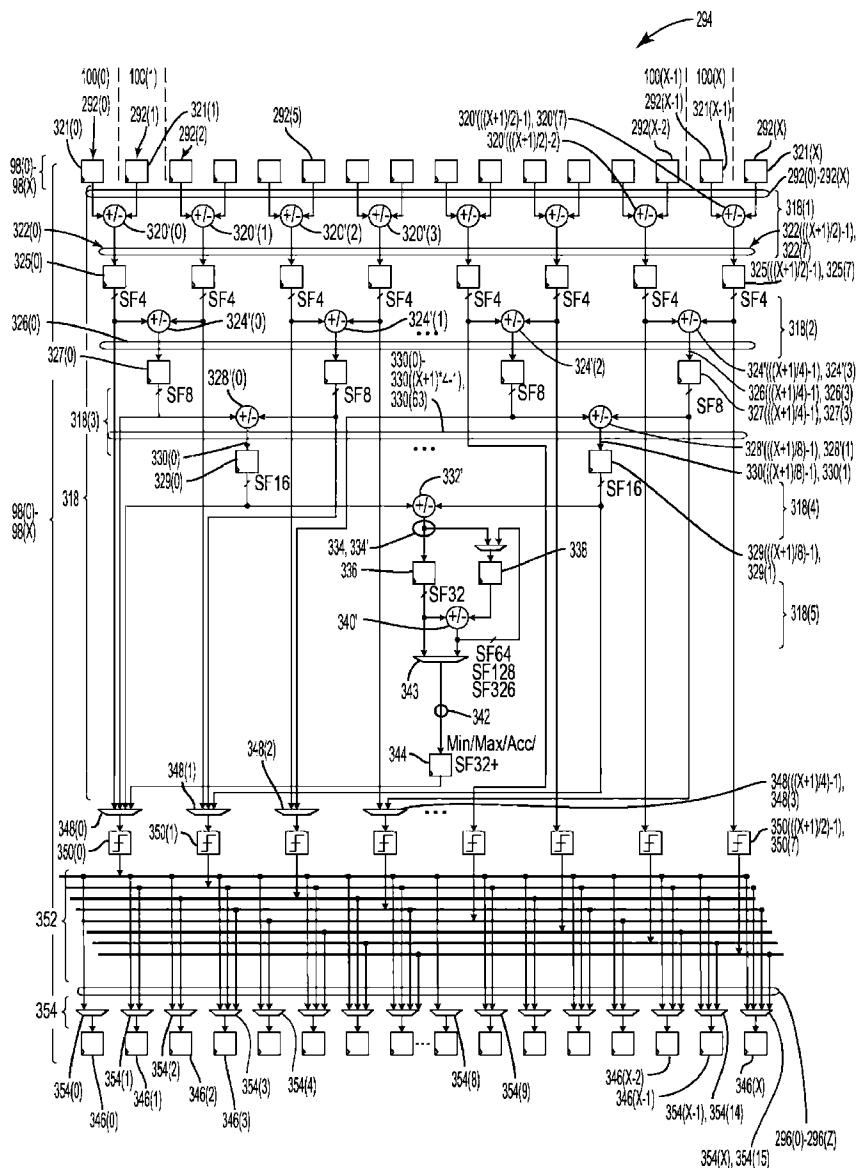

도 33은 결과적 출력 벡터 데이터 샘플 세트들의 가산-병합 및 벡터 데이터 파일로의 가산-병합된 결과적 출력 벡터 데이터 샘플 세트의 저장을 제공하기 위하여 도 31의 VPE에서 실행 유닛들과 벡터 데이터 파일 사이의 출력 데이터 흐름 경로들에서의 예시적인 병합 회로의 개략도이다.

도 34는 결과적 출력 벡터 데이터 샘플 세트들의 최대/최소 병합을 제공하고 그리고 벡터 데이터 파일 내의 최대/최소-병합 결과적 출력 벡터 데이터 샘플 세트들의 저장을 제공하기 위하여 도 31의 VPE에서 실행 유닛들과 벡터 데이터 파일 사이의 출력 데이터 흐름 경로들에서의 예시적인 병합 회로의 개략도이다.

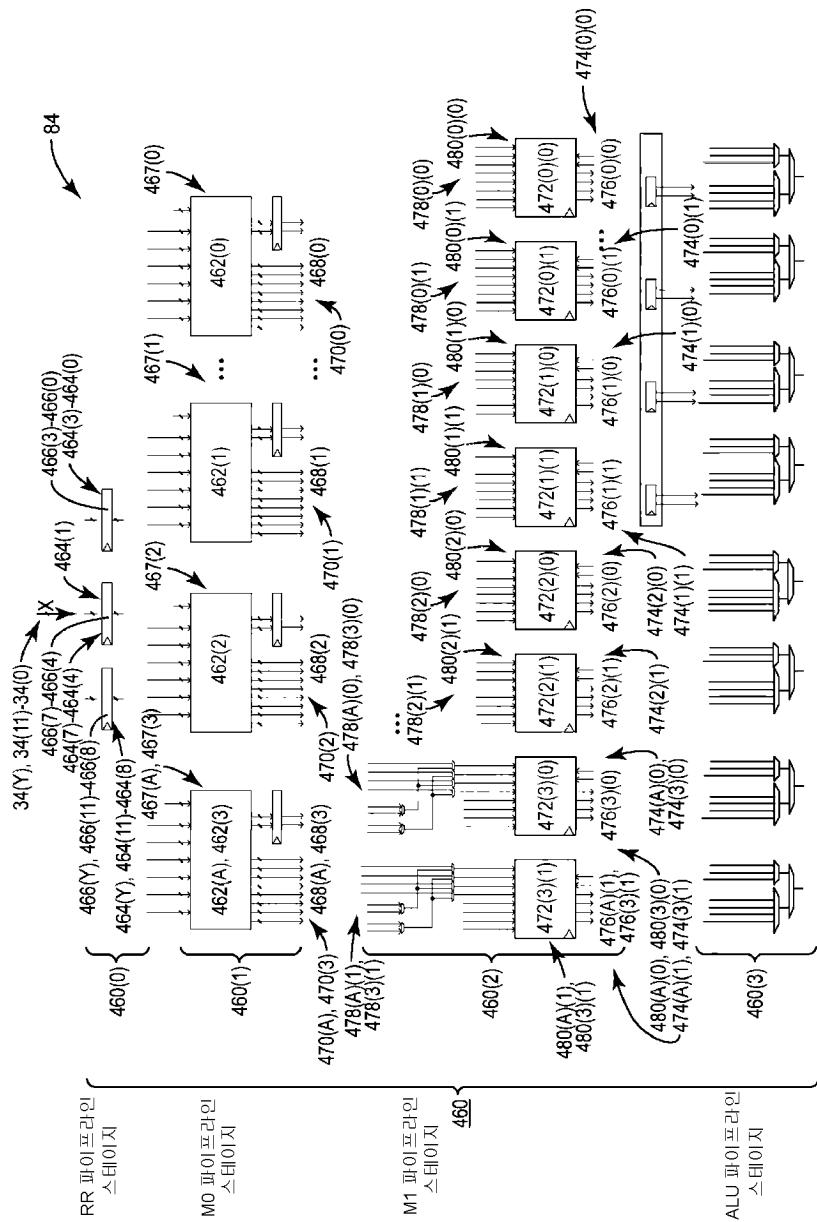

도 35는 VPE에 제공될 수 있는 예시적인 벡터 프로세싱 스테이지들의 개략도이고, 특정 벡터 프로세싱 스테이지들은 프로그램 가능 데이터 경로 구성들을 가지는 예시적인 벡터 프로세싱 블록들을 포함한다.

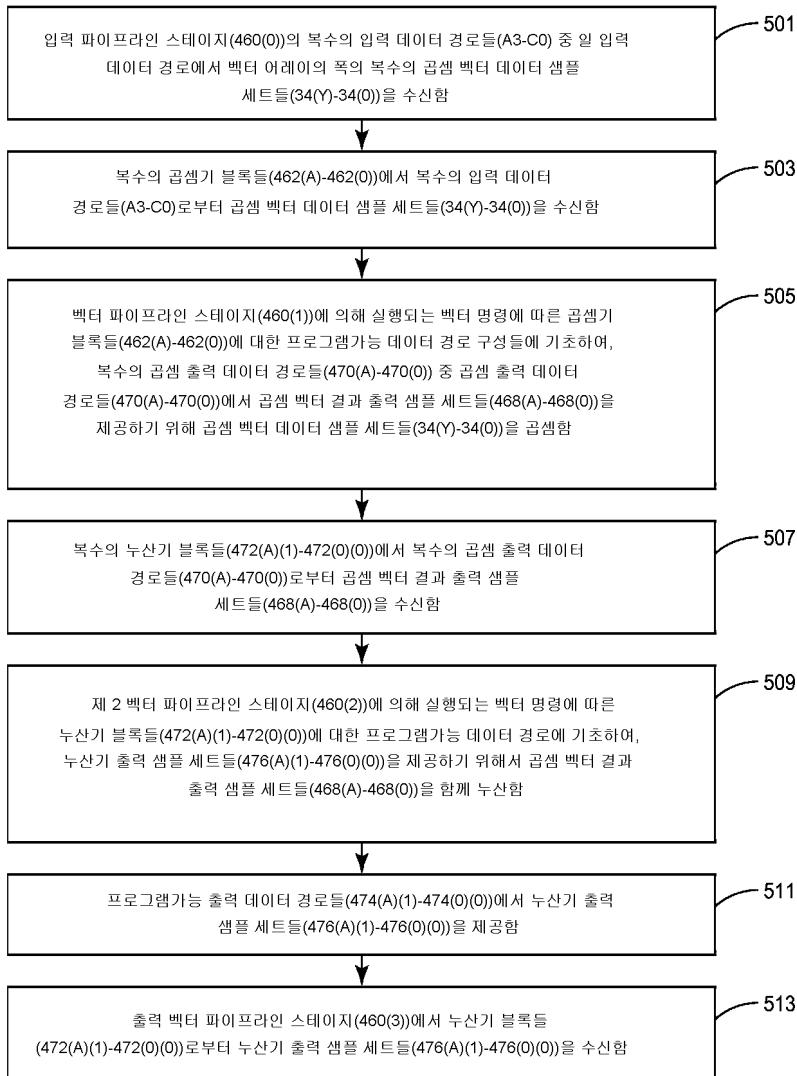

도 36은 곱셈기 블록들과 누산기 블록들의 예시적인 벡터 프로세싱을 예시하는 흐름도이고, 상기 블록들 각각은 도 35의 예시적인 VPE에 프로그램 가능 데이터 경로 구성들을 가지며 상이한 벡터 프로세싱 스테이지들에 제공된다.

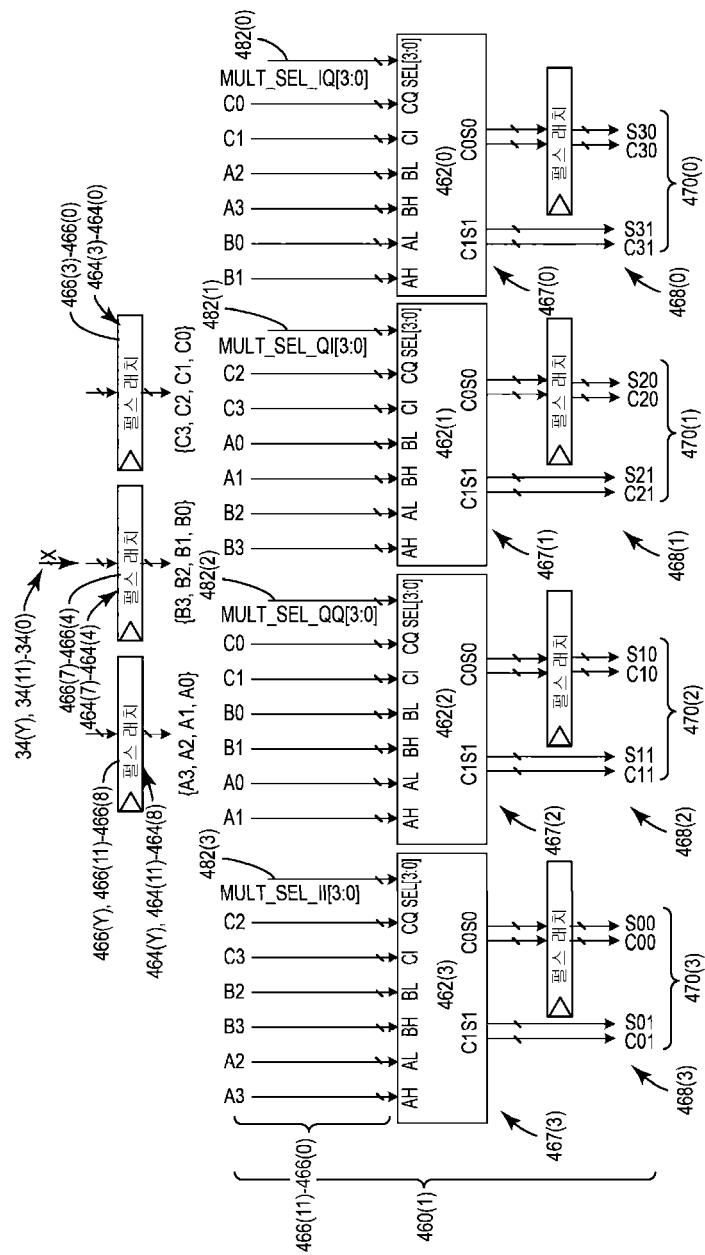

도 37은 도 35의 VPE의 벡터 프로세싱 스테이지에 제공된 복수의 곱셈기 블록들의 더 상세한 개략도이고, 복수의 곱셈기 블록들 각각은 프로그램 가능 데이터 경로 구성들을 가져서, 복수의 곱셈기 블록들은 특정 상이한 타입들의 벡터 곱셈 연산들을 수행하도록 다중 모드들로 프로그래밍될 수 있다.

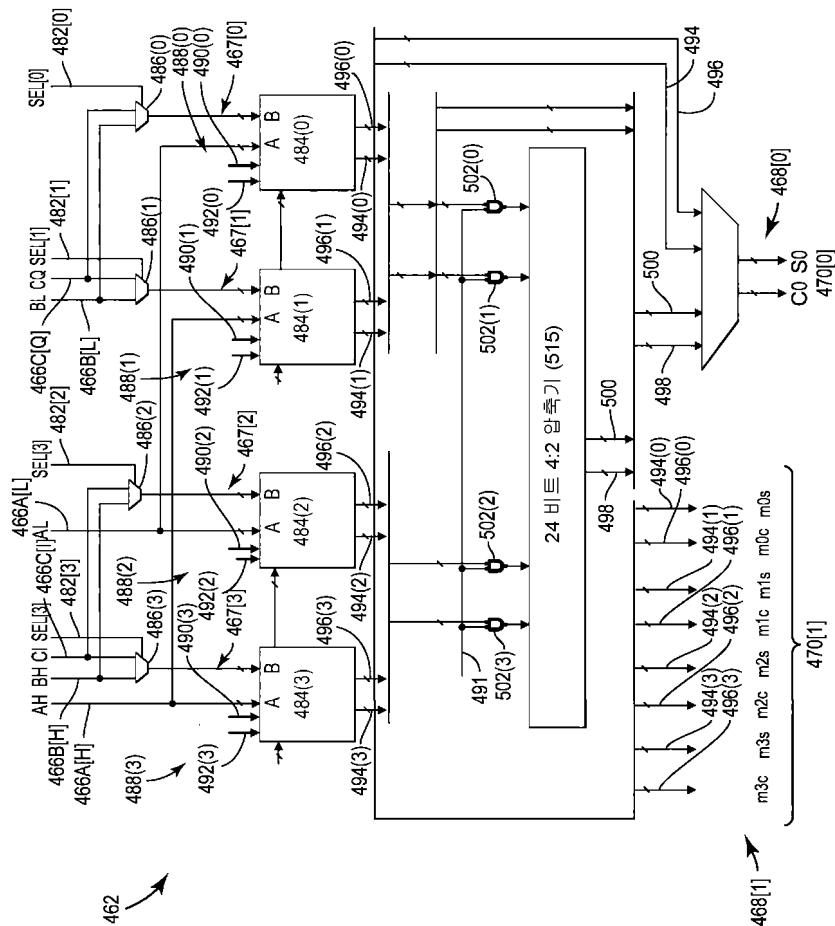

도 38은 8 비트 × 8 비트 입력 데이터 샘플 세트들과 16 비트 × 16 비트 입력 벡터 데이터 샘플 세트들에 대한 곱셈 연산들을 제공하도록 프로그래밍될 수 있는 프로그램 가능 데이터 경로 구성들을 가진 도 37의 복수의 곱셈기 블록들 중 일 곱셈기 블록의 내부 컴포넌트들의 개략도이다.

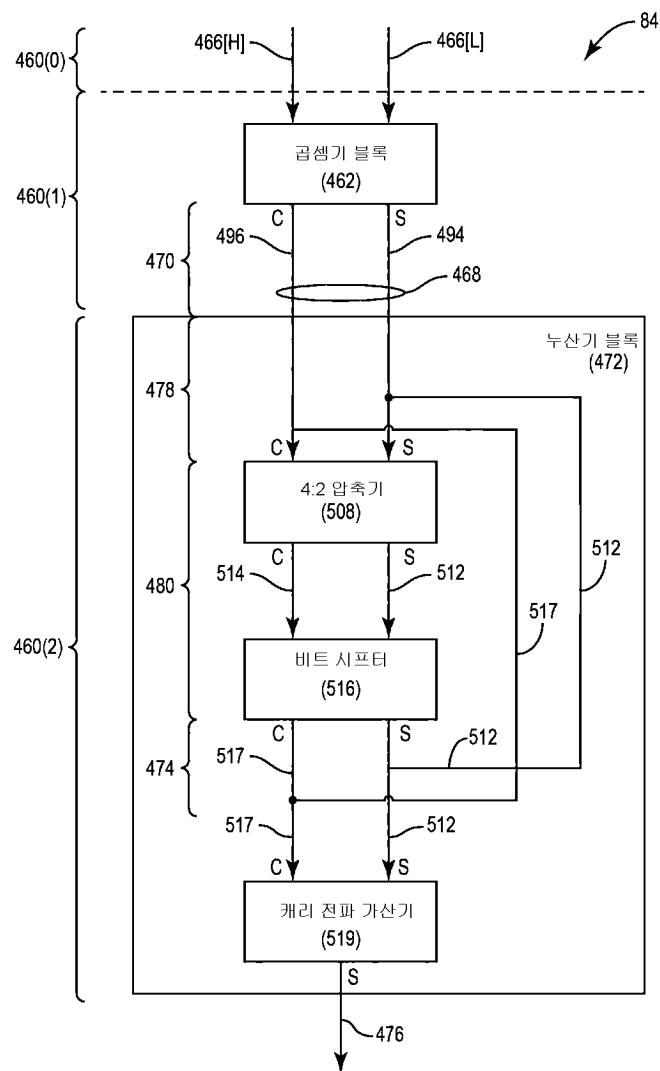

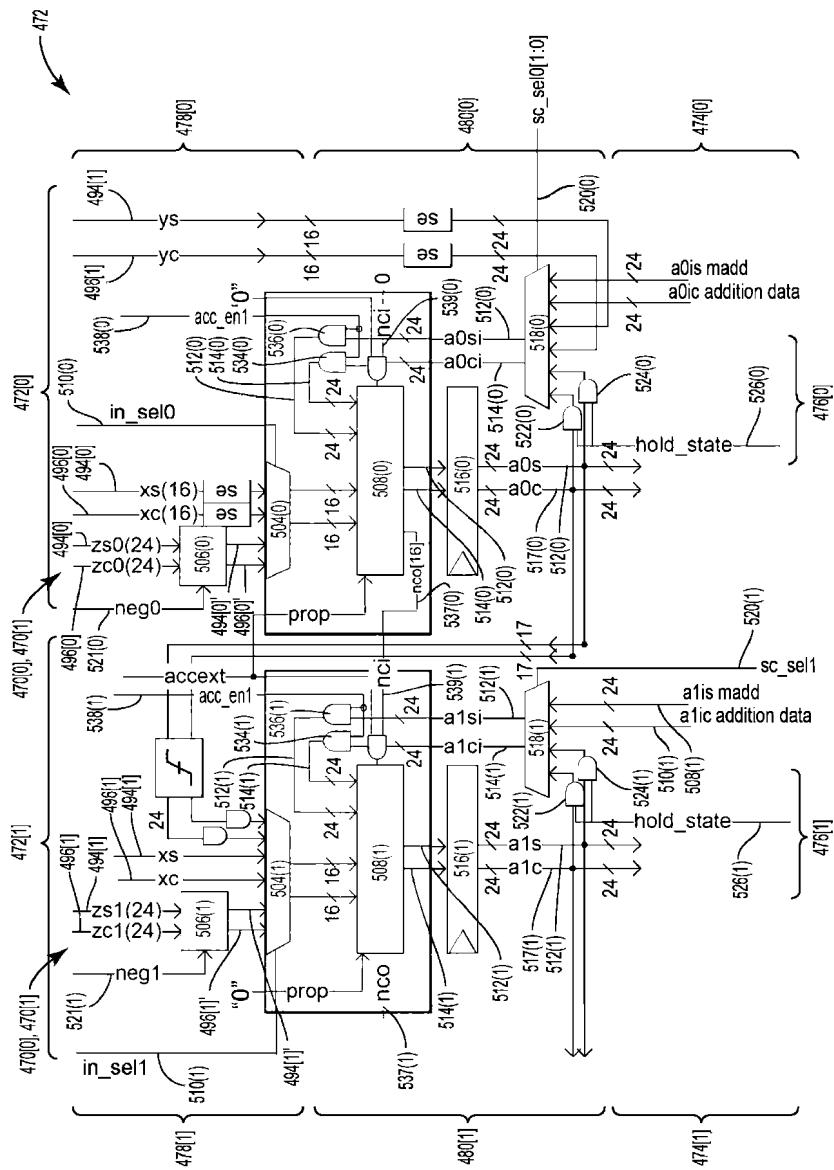

도 39는 도 38의 VPE에서 곱셈기 블록 및 누산기 블록의 일반화된 개략도이고, 누산기 블록은 캐리 전파를 감소시키기 위하여 리던던트 캐리-절약 포맷을 이용하는 캐리-절약 누산기 구조를 이용한다.

도 40은 도 35의 VPE에 제공된, 도 39의 누산기 블록의 예시적인 내부 컴포넌트들의 상세한 개략도이고, 누산기 블록은 프로그램 가능 데이터 경로 구성들을 가져서, 누산기 블록은 리던던트 캐리-절약 포맷으로 특정의 상이한 타입들의 벡터 누산 연산들을 수행하도록 다수의 모드들로 프로그래밍될 수 있다.

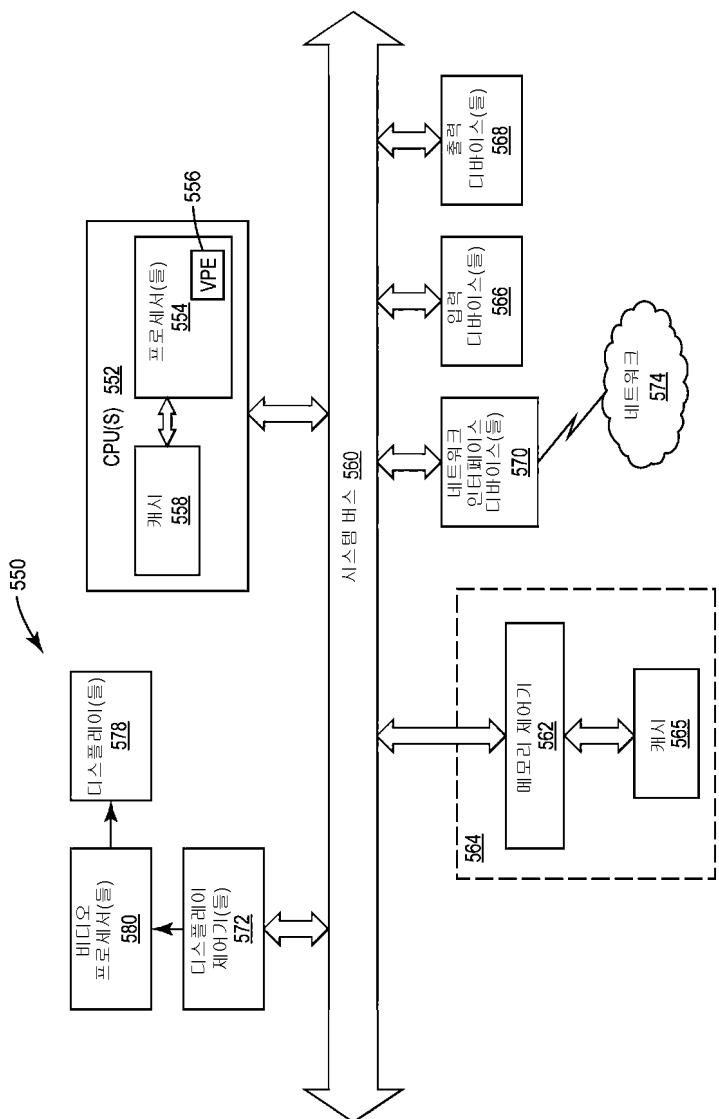

도 41은 본원에 개시된 실시예들에 따른, 벡터 프로세싱 회로들 및 벡터 프로세싱 연산들을 제공하기 위하여 본원에 개시된 VPE들을 포함할 수 있는 벡터 프로세서를 포함할 수 있는 예시적인 프로세서-기반 시스템의 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

[0022] 이제 도시된 도면들을 참조하여, 본 개시내용의 몇몇 예시적인 실시예들이 설명된다. 단어 "예시적"은 "예, 예증, 또는 예시로서 제공하는 것"을 의미하기 위하여 본원에서 사용된다. "예시적"으로서 본원에 설명된 임의의

실시예가 반드시 다른 실시예들에 비해 바람직하거나 유리한 것으로 이해될 필요는 없다.

[0023] 본원에 개시된 실시예들은 벡터 데이터 메모리에 저장될 출력 벡터 데이터의 실시간 병합을 제공하기 위해서 실행 유닛들과 벡터 데이터 메모리 사이의 데이터 흐름 경로들에서 병합 회로를 이용하는 벡터 프로세싱 엔진(VPE)을 포함한다. 관련된 벡터 프로세싱 명령들, 시스템들 및 방법들이 또한 개시된다. 병합 회로는 VPE의 벡터 데이터 메모리와 실행 유닛들 사이의 데이터 흐름 경로들에 제공된다. 병합 회로는, 출력 벡터 데이터 샘플 세트가 저장되기 위해 실행 유닛들로부터 출력 데이터 흐름 경로들을 통해 벡터 데이터 메모리로 제공되고 있는 동안에 실시간으로 벡터 프로세싱 연산들을 수행하는 결과로서 실행 유닛들로부터의 출력 벡터 데이터 샘플 세트를 병합하도록 구성된다. 출력 벡터 데이터 샘플들의 실시간 병합은, 실행 유닛들에 의해 제공되는 출력 벡터 데이터 샘플 세트의 원하는 프로그래밍된 출력 벡터 데이터 샘플들이 벡터 데이터 메모리에 저장되기 이전에 병합될 수 있고, 따라서 출력 벡터 데이터 샘플 세트가 벡터 데이터 메모리에 병합된 포맷으로 저장됨을 의미한다. 비제한적인 예로서, 출력 벡터 데이터의 병합은 병합된 출력 벡터 데이터 샘플 세트들 및 출력 스칼라 데이터 샘플 세트를 제공하기 위해 출력 벡터 데이터 샘플 세트들을 추가하는 것을 포함할 수 있다. 또 다른 비제한적인 예로서, 출력 벡터 데이터 샘플 세트들의 병합은 실행 유닛들로부터의 비교되는 출력 벡터 데이터 샘플 세트들 간의 최대 및/또는 최소 출력 벡터 데이터를 생성하는 것을 포함할 수 있다. 병합된 출력 벡터 데이터 샘플 세트는 실행 유닛들에서 수행될 후속 벡터 프로세싱 연산들을 지연시킬 수 있는 추가적인 사후-프로세싱 단계들을 필요로 하지 않고 벡터 데이터 메모리에 병합된 형태로 저장된다.

[0024] 따라서, VPE에서 데이터 흐름 경로들의 효율성이 출력 벡터 데이터의 병합에 의해 제한되지 않는다. 실행 유닛들에서 후속 벡터 프로세싱은 출력 벡터 데이터 샘플 세트들이 벡터 데이터 메모리에 병합된 형태로 저장되어야 할 때 데이터 흐름 제한들에 의해서 보다는 계산 자원들에 의해서만 단지 제한된다. VPE는 실행 유닛들의 계산 엘리먼트들의 효율성에 영향을 주지 않으면서 벡터 데이터 메모리의 원하는 목적 위치에 병합된 인트라-벡터 출력 벡터 데이터 샘플 세트들을 제공하도록 또한 구성된다.

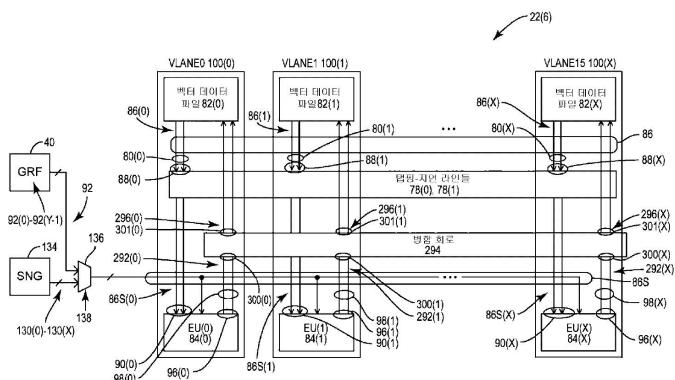

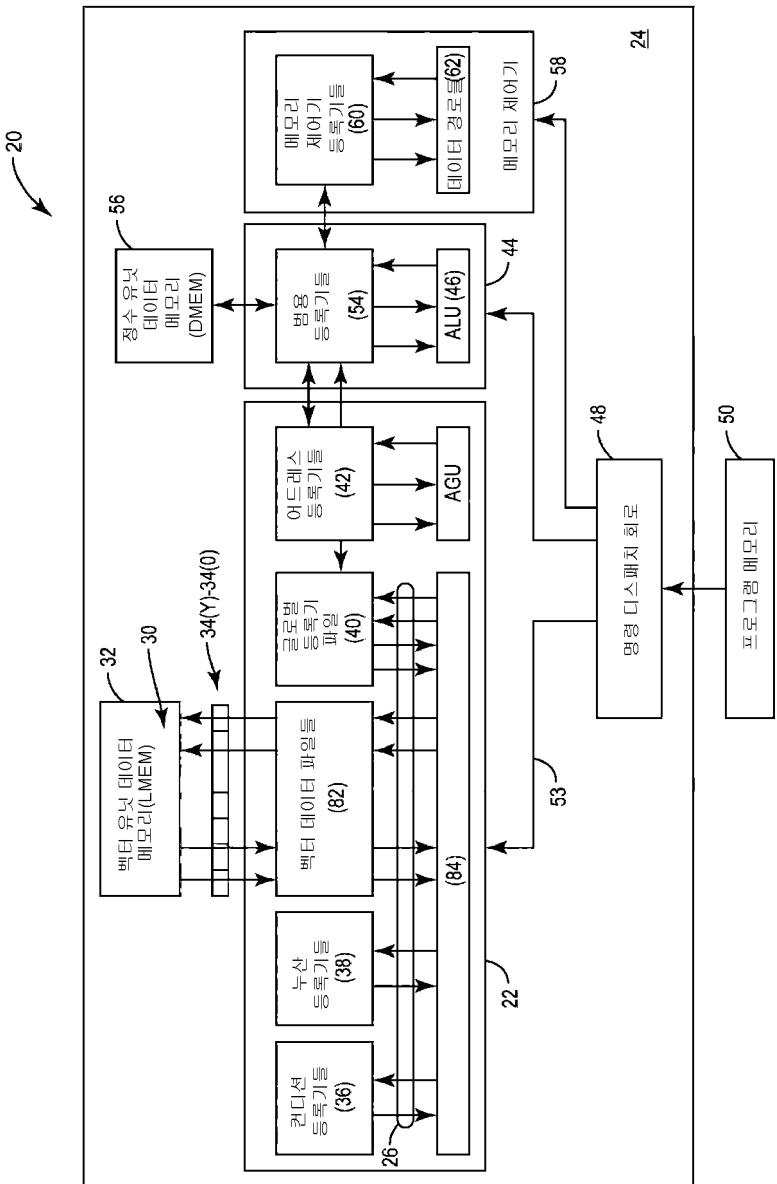

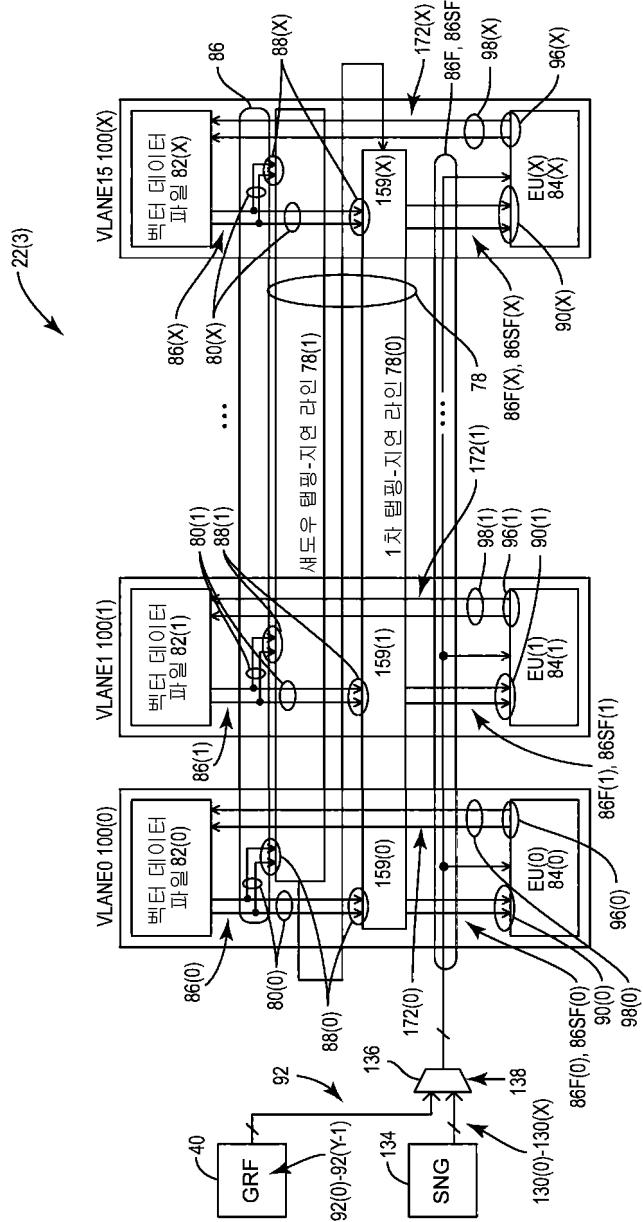

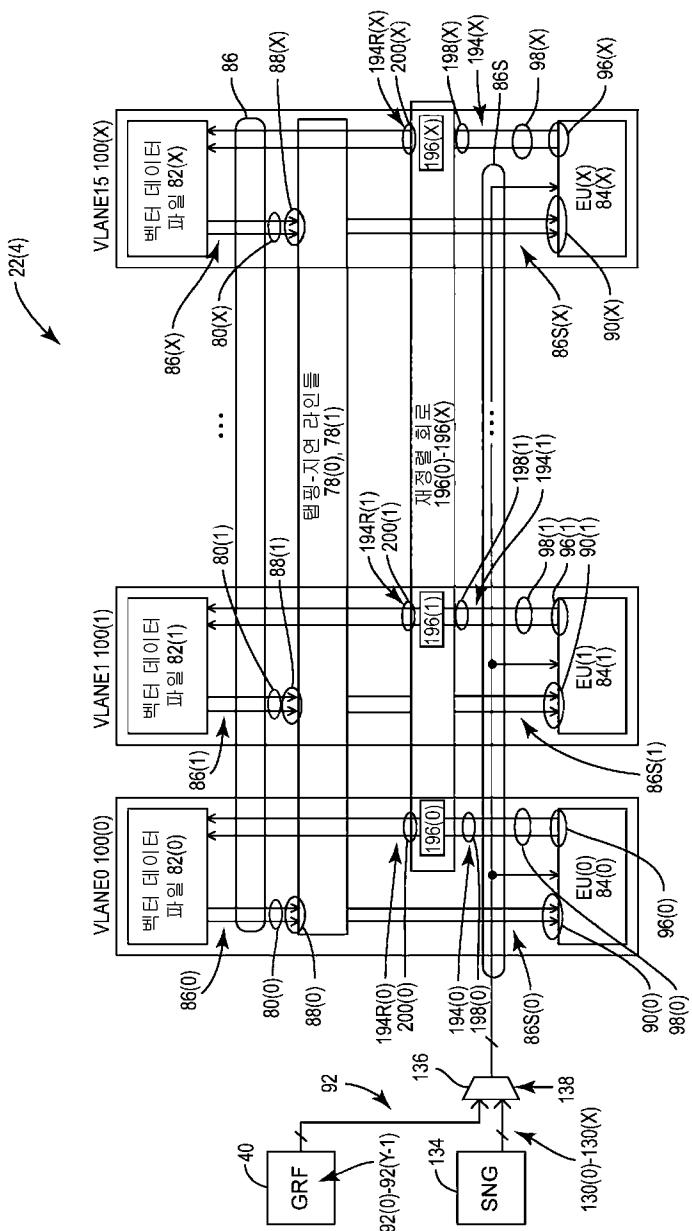

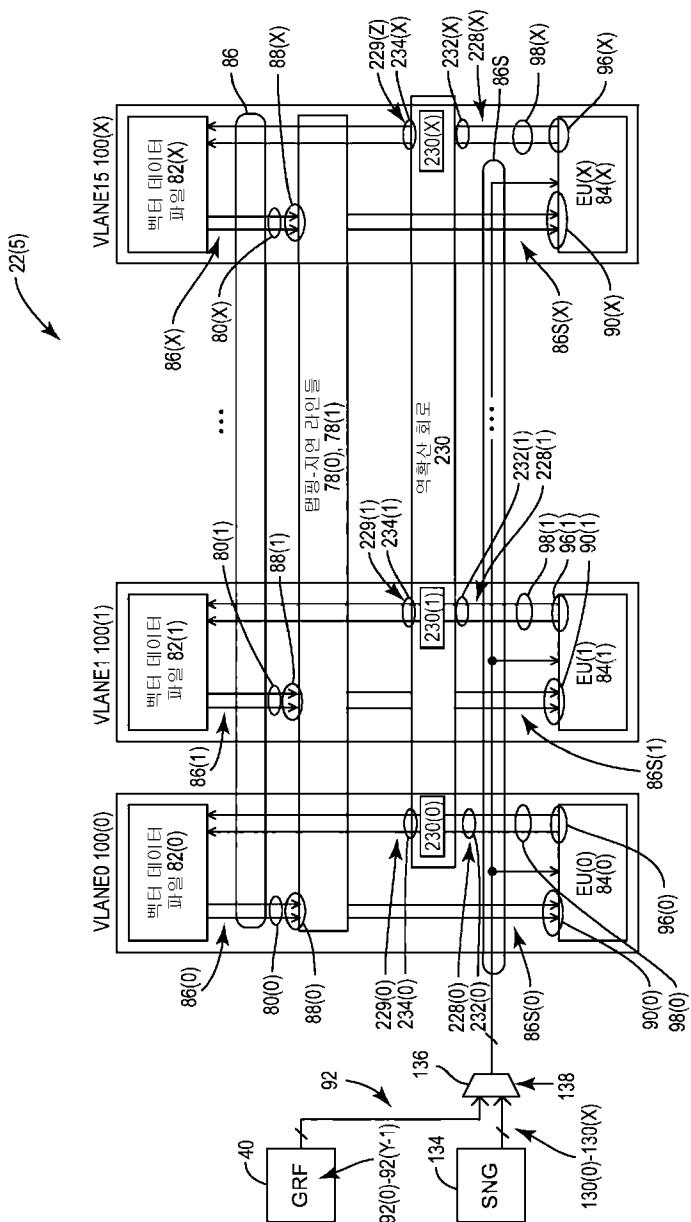

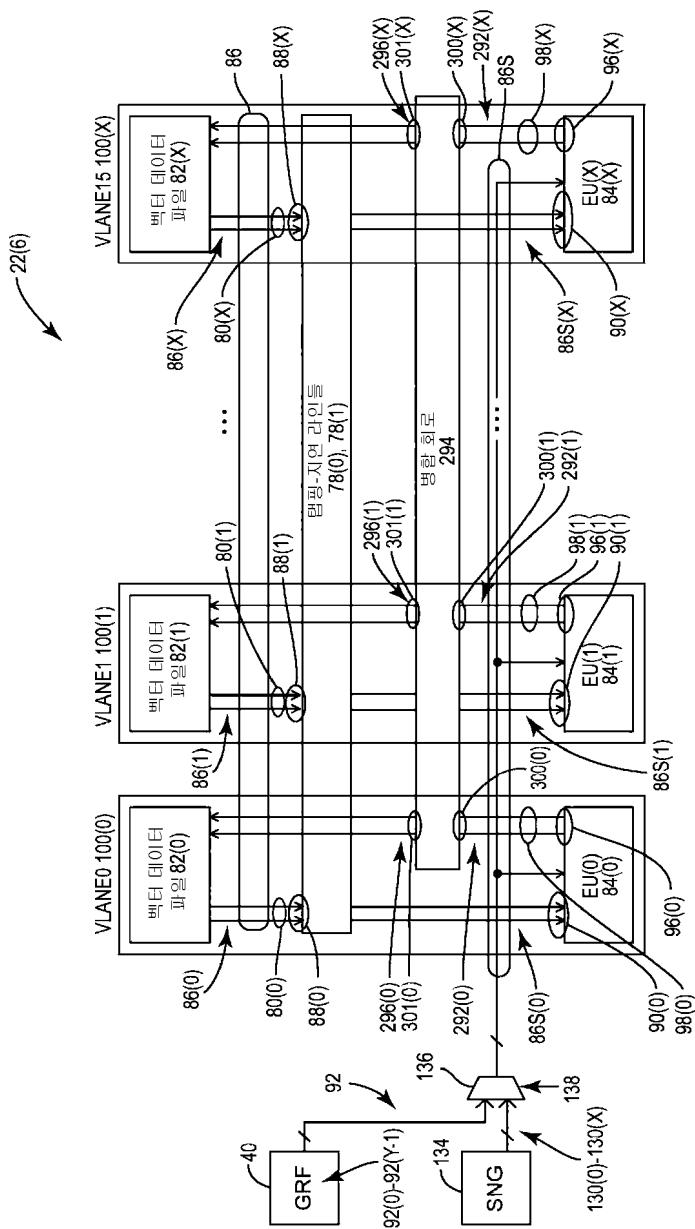

[0025] 이와 관련하여, 도 2는 또한 벡터 프로세싱 엔진(VPE)(22)으로 지칭되는 예시적인 벡터 프로세싱 유닛(22)을 포함하는 기저대역 프로세서(20)의 개략도이다. 아래에 더 상세히 논의될 바와 같이, VPE(22)는 본원에 개시된 예시적인 벡터 프로세싱 연산들을 비롯하여 벡터 프로세싱 동작들을 제공하기 위해 실행 유닛들(84) 및 다른 특정 예시적인 회로 및 기능을 포함한다. 기저대역 프로세서(20) 및 그의 VPE(22)는 반도체 다이(24)에 제공될 수 있다. 이 실시예에서, 아래에 더 상세히 논의될 바와 같이, 기저대역 프로세서(20)는 상이한 프로그램가능 데이터 경로 구성을 제공하도록 프로그램될 수 있는 프로그램가능 데이터 경로들(26)을 포함하는 공통의 VPE(22)를 포함한다. 이런 방식으로, VPE(22) 내의 벡터 데이터 파일들(82)과 실행 유닛들(84) 사이의 프로그램가능 데이터 경로들(26)은, 기저대역 프로세서(20)에 별도의 VPE들(22)을 제공할 필요성 없이 상이한 동작 모드들에서 상이한 특정 타입들의 벡터 프로세싱 연산들을 제공하기 위해 프로그램 및 재프로그램될 수 있다.

[0026] 도 3에서 시작하는 효율적인 프로세싱을 위해 본 개시내용에서 VPE(22)에 의해 제공되도록 구성된 특정 회로 및 벡터 프로세싱 연산들을 논의하기 전에, 도 2의 기저대역 프로세서(20)의 컴포넌트들이 먼저 설명된다. 이런 비제한적 예에서 기저대역 프로세서(20)는 512 비트 벡터 프로세서이다. 기저대역 프로세서(20)는 기저대역 프로세서(20)에서 벡터 프로세싱을 제공하는 VPE(22)를 지원하기 위하여 VPE(22) 이외에 컴포넌트들을 포함한다. 기저대역 프로세서(20)는 벡터 유닛 데이터 메모리(LMEM)(32)로부터의 벡터 데이터(30)를 수신 및 저장하기 위해 구성된 벡터 데이터 파일들(82)로 또한 알려진 벡터 레지스터들을 포함한다. 예컨대, 벡터 데이터(30)는 X 비트 폭이고, 'X'는 설계 선택(예컨대, 512 비트들)에 따라 정의된다. 벡터 데이터(30)는 벡터 데이터 샘플 세트들(34)로 나누어질 수 있다. 비제한적인 예로서, 벡터 데이터(30)는 256 비트 폭일 수 있고, 보다 작은 벡터 데이터 샘플 세트들(34(Y)-34(0))을 포함할 수 있다. 예로서, 일부 벡터 데이터 샘플 세트들(34(Y)-34(0))은 16 비트 폭일 수 있고, 벡터 데이터 샘플 세트들(34(Y)-34(0))의 다른 것들은 32 비트 폭일 수 있다. VPE(22)는 높은 병렬도를 달성하기 위하여 VPE(22)에 병렬로 제공된 특정 선택된 벡터 데이터 샘플 세트들(34(Y)-34(0))에 대해 벡터 프로세싱을 제공할 수 있다. 벡터 데이터 파일들(82)은 또한, VPE(22)가 벡터 데이터(30)를 프로세싱할 때 생성된 결과들을 저장하도록 구성된다. 특정 실시예들에서, VPE(22)는 보다 빠른 벡터 명령 실행 시간들을 제공하기 위하여 레지스터 기록들을 감소시키기 위해 중간 벡터 프로세싱 결과들을 벡터 데이터 파일들(82)에 저장하지 않도록 구성된다. 이 구성은 스칼라 프로세싱 디지털 신호 프로세서들(DSP들)과 같은 레지스터들에 중간 결과들을 저장하는 스칼라 프로세싱 엔진들에 의해 실행되는 스칼라 명령들과 반대이다.

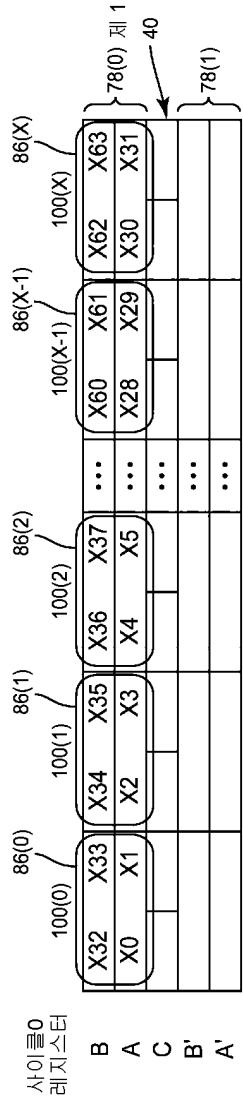

[0027] 도 2의 기저대역 프로세서(20)는 또한 벡터 명령들의 조건적 실행에 사용하기 위해 조건들을 VPE(22)에 제공하고 업데이트된 조건들을 벡터 명령 실행의 결과로서 저장하도록 구성된 조건 레지스터들(36)을 포함한다. 기저 대역 프로세서(20)는 또한 누산 레지스터들(38), 글로벌 레지스터들을 포함하는 글로벌 레지스터 파일(40), 및

어드레스 레지스터들(42)을 포함한다. 누산 레지스터들(38)은 벡터 데이터(30)에 대한 특정 특수화된 동작들을 실행한 결과로서 누산된 결과들을 저장하기 위해 VPE(22)에 의해 사용되도록 구성된다. 글로벌 레지스터 파일(40)은 VPE(22)에 의해 지원된 특정 벡터 명령들에 대한 스칼라 오퍼랜드(operand)들을 저장하도록 구성된다. 어드레스 레지스터들(42)은 벡터 로드에 의해 어드레스 가능한 어드레스들을 저장하고, 벡터 유닛 데이터 메모리(32)로부터 벡터 데이터(30)를 리트리브하기 위해 VPE(22)에 의해 지원되는 명령들을 저장하고, 벡터 유닛 데이터 메모리(32)에 벡터 프로세싱 결과들을 저장하도록 구성된다.

[0028] 도 2를 계속 참조하여, 이 실시예에서 기저대역 프로세서(20)는 또한 VPE(22)에 의해 제공된 벡터 프로세싱 이외에 기저대역 프로세서(20)에서 스칼라 프로세싱을 제공하기 위해 스칼라 프로세서(44)(또한 "정수 유닛"으로 지칭됨)를 포함한다. 매우 효율적인 동작을 위해 실행된 명령 타입에 기초하여 벡터 및 스칼라 명령 동작들을 둘다를 지원하도록 구성된 CPU(central processing unit)를 제공하는 것이 바람직할 수 있다. 이 실시예에서, 스칼라 프로세서(44)는 비제한적인 예로서 32 비트 축소 명령 집합 컴퓨팅(RISC: reduced instruction set computing) 스칼라 프로세서이다. 스칼라 프로세서(44)는 이 예에서 스칼라 명령 프로세싱을 지원하기 위해 산술 논리 유닛(ALU)(46)을 포함한다. 기저대역 프로세서(20)는 프로그램 메모리(50)로부터 명령들을 패치하고, 패치된 명령들을 디코딩하고, 그리고 명령 타입에 기초하여 패치된 명령들을 스칼라 프로세서(44)로 지향하거나 벡터 데이터 경로(53)를 통해 VPE(22)로 지향도록 구성된 명령 디스패치 회로(48)를 포함한다. 스칼라 프로세서(44)는 스칼라 명령들을 실행할 때 스칼라 프로세서(44)에 의해 사용하기 위한 범용 레지스터들(54)을 포함한다. 정수 유닛 데이터 메모리(DMEM: integer unit data memory)(56)는 스칼라 명령 실행을 위한 스칼라 프로세서(44)에 의해 액세스하기 위한 데이터를 메인 메모리로부터 범용 레지스터들(54)로 제공하기 위해 기저대역 프로세서(20)에 포함된다. DMEM(56)은 비제한적 예로서 캐시 메모리일 수 있다. 기저대역 프로세서(20)는 또한, 스칼라 프로세서(44)가 메모리 제어기 데이터 경로들(62)을 통해 메인 메모리에 액세스를 요구하는 벡터 명령들을 실행할 때 범용 레지스터들(54)로부터 메모리 어드레스들을 수신하도록 구성된 메모리 제어기 레지스터들(60)을 포함하는 메모리 제어기(58)를 포함한다.

[0029] VPE(22)에 의한 벡터 명령 프로세싱에 의해 지원되도록 요구될 수 있는 하나의 타입의 특수화된 벡터 프로세싱 연산은 필터링이다. 필터 연산은 샘플링된 입력 시간 함수의 컨볼루션의 양자화된 시간-도메인 표현 및 필터의 가중 함수의 표현을 계산한다. 시간 도메인에서 컨볼루션은 주파수 도메인에서 곱셈에 대응한다. 따라서, 디지털 필터들은 일정하게 이격된 샘플 간격에서 수행되는 곱셈들 및 가산들의 확장된 시퀀스에 의해 VPE(22)에서 실현될 수 있다. 예컨대, 이산 FIR(finite impulse response) 필터는 필터 함수를 계산하기 위해 "Y" 계산 필터 계수들을 갖는 지연 라인 상의 유한수(Y)의 지연 텁들을 사용하여 구현될 수 있다.

[0030] 이와 관련하여, 도 3은 도 2의 VPE(22) 내의 필터 벡터 프로세싱 연산을 통해 지원되도록 요구될 수 있는 예시적인 이산 FIR 필터(64)의 개략도이다. 디지털화된 입력 신호(66(x[n]))는 "필터 지연 텁들(68(1)-68(Y-1))"로 불리는 지연 구조들을 통해 디지털화된 입력 신호 샘플들(x[0], x[1], ..., x[n])을 통과시킴으로써 필터링 될 수 있다. 필터 지연 텁들(68(1)-68(Y-1))은, 필터 샘플 피승수들(72(0)-72(Y-1))(즉, h(1)\*x[n-1])을 제공하기 위해 필터 계수들(h[0]-h(Y-1))로 각각 곱셈될 모든 디지털화된 입력 신호 샘플들(즉, x[0], x[1], ..., x[n])에 대해 클록 디지털화된 입력 신호 샘플들(즉, x[0], x[1], ..., x[n])을 곱셈기들(70(0)-70(Y-1))로 시프트한다. 필터 샘플 피승수들(72(0)-72(Y-1))은 결과적 필터링된 출력 신호(76)(즉, y[n])를 제공하기 위해 합산기들(즉, 가산기들)(74(1)-74(Y-1))에 의해 함께 합산된다. 따라서, 도 3의 이산 FIR 필터(64)는 다음과 같이 요약될 수 있다.

$$y[n] = \sum_{l=0}^{l=Y-1} h(l) * x[n-l]$$

[0031]

[0032] 여기서, n은 입력 신호 샘플들의 수이고,

[0033] x[n]은 디지털화된 입력 신호(66)이고,

[0034] y[n]은 결과적 필터링된 출력 신호(76)이고,

[0035] h(l)은 필터 계수들이고,

[0036] Y는 필터 계수들의 수이다.

[0037] 필터 계수들(h(l))은 복소수일 수 있다. 일 양상에서, VPE(22)는 (예컨대, 글로벌 레지스터 파일(40)로부터)

필터 계수들을 수신할 수 있다. VPE(22)는 FIR 필터 기능을 수행하기 위해 수신된 필터 계수들을 직접적으로 사용할 수 있고, 이러한 경우에 위의 수학식에서 필터 계수들( $h(1)$ )은 수신된 필터 계수들을 나타낼 수 있다. 대안적으로, VPE(22)는 FIR 필터 기능을 수행하기 위해 수신된 필터 계수들을 사용하기 전에 그들의 복소 공액을 계산할 수 있고, 이러한 경우에, 위의 수학식에서 필터 계수들( $h(1)$ )은 수신된 필터 계수들의 공액들을 나타낼 수 있다.

[0038] 도 3에서 위의 이산 FIR 필터(64)는 다음과 같이 재구성될 수 있다.

$$y[n]=x[n]*h_0 + x[n-1]*h_1 + \dots + x[n-7]*h_7$$

[0040] 그러나, 도 3의 이산 FIR 필터(64)와 같은 필터링 연산은 벡터 프로세서에서 제공되는 특수화된 데이터 흐름 경로들로 인해 벡터 프로세서들에서 병렬화하기에 어려울 수 있다. 필터링될 입력 벡터 데이터 샘플 세트(예컨대, 벡터화된 디지털화된 입력 신호(66))가 필터 지연 텁들(예컨대, 68(1)-68(Y-1)) 사이에서 시프트될 때, 입력 벡터 데이터 샘플 세트는 벡터 데이터 파일로부터 재페치되고, 따라서 전력 소비를 증가시키고 스루풋을 감소시킨다. 벡터 데이터 파일로부터 입력 벡터 데이터 샘플 세트들의 재페치를 최소화하기 위해 벡터 프로세서 내의 데이터 흐름 경로는 효율적인 병렬화된 프로세싱을 위해 필터 지연 텁들(예컨대, 68(1)-68(Y-1))과 동일한 수의 곱셈기들(예컨대, 70(0)-70(Y-1))을 제공하도록 구성될 수 있다. 그러나, 다른 벡터 프로세싱 연산들은 더 적은 곱셈기들을 요구할 수 있고, 이로써 데이터 흐름 경로에서 곱셈기들의 비효율적인 스케일링 및 낮은 활용을 제공한다. 곱셈기들의 수가 확장성을 제공하기 위한 필터 지연 텁들의 수 미만으로 감소되면, 병렬화는 필터 프로세싱의 상이한 단계들에 대한 동일한 입력 벡터 데이터 샘플 세트를 획득하기 위해 메모리에 요구되는 더 많은 재페치들에 의해 제한된다.

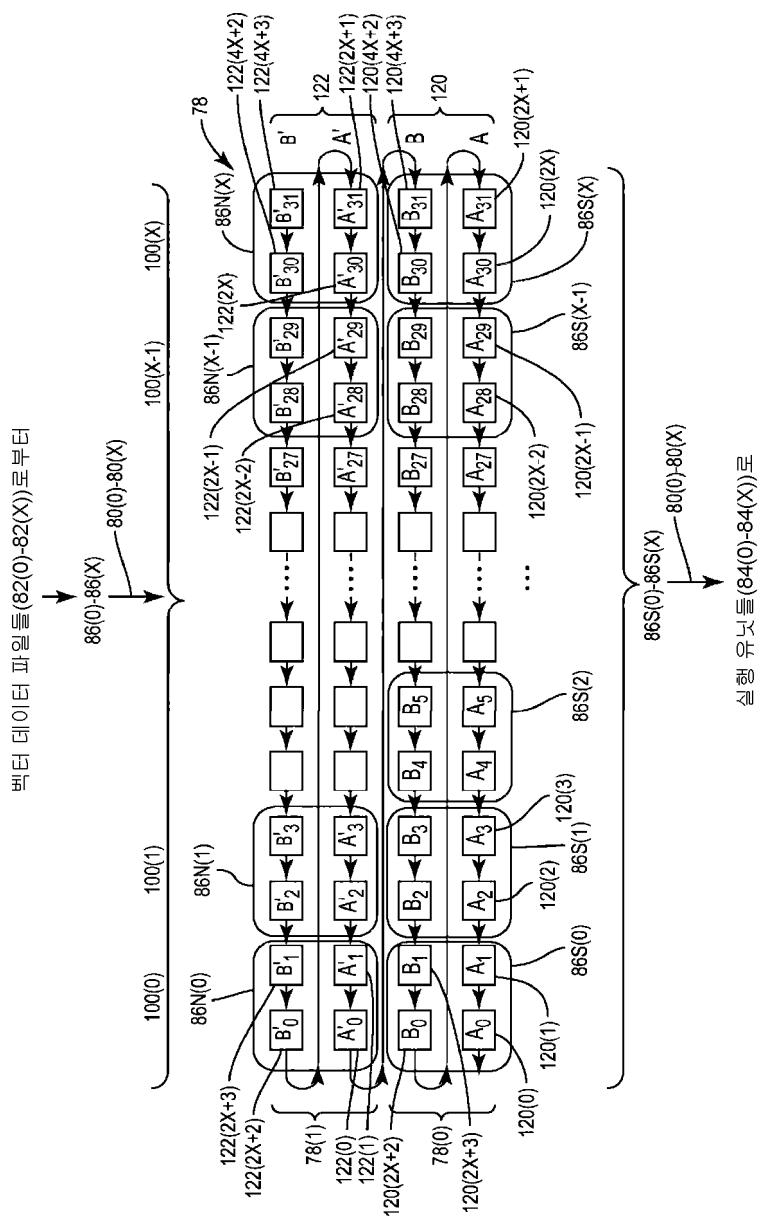

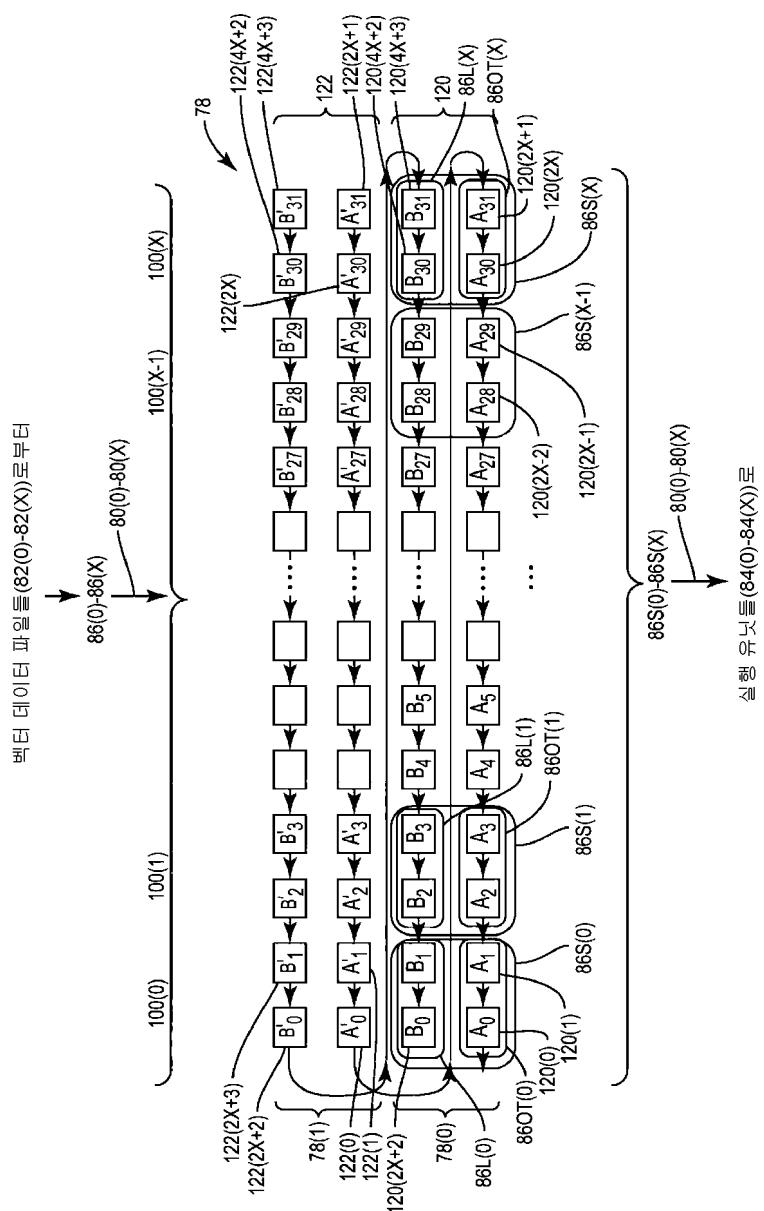

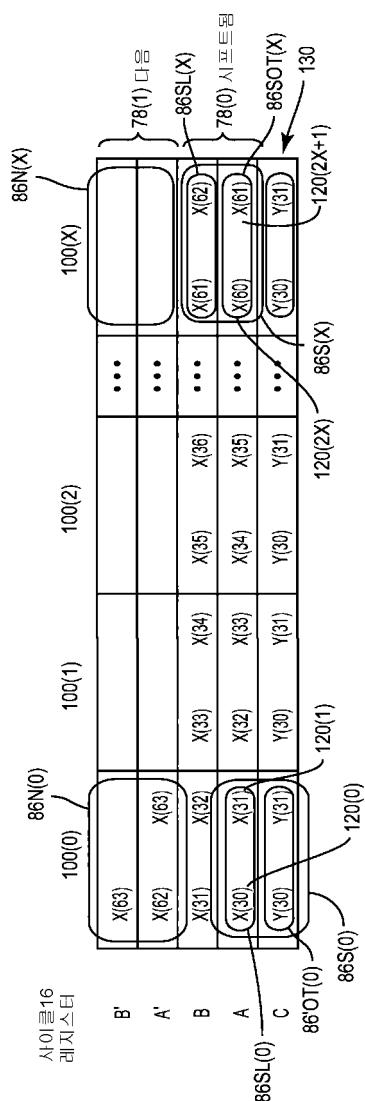

[0041] 이와 관련하여, 도 4는 도 2의 VPE(22)로서 제공될 수 있는 예시적인 VPE(22(1))의 개략도이다. 아래에 더 상세히 설명될 바와 같이, 도 4의 VPE(22(1))는 벡터 데이터 샘플 재페치가 제거 또는 감소되고 전력 소비가 감소된, VPE(22(1)) 내의 정밀 필터 벡터 프로세싱 연산들을 제공한다. 벡터 데이터 샘플 재페치를 요구하는 중간 결과들의 저장을 요구하고 이로써 결과적으로 전력 소비를 증가시키는 필터 벡터 프로세싱 연산들과 비교하여 VPE(22(1))에서 정밀 필터 벡터 프로세싱 연산들이 제공될 수 있다. 전력 소비를 감소시키고 프로세싱 효율을 개선하기 위해 벡터 데이터 파일로부터 입력 벡터 데이터 샘플들의 재페치를 제거 또는 최소화하기 위해, 텁핑-지연 라인들(78)이 VPE(22(1)) 내의 실행 유닛들(84(0)-84(X))(또한 "EU"로 라벨링됨)과 벡터 데이터 파일들(82(0)-82(X)) 사이의 입력 데이터 흐름 경로들(80(0)-80(X))에 포함된다. 'X'+1은 이러한 예에서 벡터 데이터 샘플들의 프로세싱을 위해 VPE(22(1))에 제공되는 병렬 입력 데이터 레인들의 최대수이다. 텁핑-지연 라인들(78)은 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 입력 벡터 데이터 샘플들(86)의 서브세트 또는 전부로서 텁핑-지연 라인들(88(0)-88(X)) 상에서 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 벡터 데이터 파일들(82(0)-82(X))의 대응하는 서브세트 또는 전부로부터 수신하도록 구성된다. 입력 벡터 데이터 샘플 세트(86(0)-86(X))는, 이러한 예에서 86(0), 86(1), ..., 및 86(X)인 'X+1' 입력 벡터 데이터 샘플들(86)에 포함된다.

[0042] 도 4를 계속해서 참조하면, 텁핑-지연 라인들(78)은 필터 벡터 프로세싱 연산을 위해 실행 유닛들(84(0)-84(X))에 의해 프로세싱될 벡터 데이터 파일들(82(0)-82(X))로부터 폐치된 입력 벡터 데이터 샘플 세트들(86(0)-86(X))을 저장한다. 아래의 도 6 및 7에 관련하여 아래에 더 상세히 논의될 바와 같이, 텁핑-지연 라인들(78)은 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 실행 유닛들(84(0)-84(X))에 제공하기 위해 VPE(22(1))에 의해 실행될 필터 벡터 명령에 따라 필터 벡터 프로세싱 동작의 각각의 필터 지연 텁(즉, 필터 프로세싱 스테이지)에 대한 입력 벡터 데이터 샘플 세트들(86(0)-86(X))을 시프트하도록 구성된다. 시프트된 입력 벡터 데이터 샘플들(86S) 모두는 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 포함한다. 텁핑-지연 라인들(78)은 필터 벡터 프로세싱 연산 동안에 실행 유닛들(84(0)-84(X))의 실행 유닛 입력들(90(0)-90(X))에 시프트된 입력 벡터 데이터 샘플(86S(0)-86S(X))을 제공한다. 이러한 방식으로, 필터 벡터 프로세싱 연산의 필터 텁들에 대한 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))에 대해 수행되는 연산들에 기초한 중간 필터 결과들은 VPE(22(1))에 의해 수행되는 필터 벡터 프로세싱 연산의 각각의 프로세싱 스테이지 동안에 저장, 시프트되고 그리고 벡터 데이터 파일들(82(0)-82(X))로부터 재페치되지 않아도 된다. 따라서, 텁핑-지연 라인들(78)은 전력 소비를 감소시키고, VPE(22(1))에 의해 수행되는 필터 벡터 프로세싱 연산들에 대한 프로세싱 효율을 증가시킬 수 있다.

[0043] "벡터 프로세싱 스테이지"로 또한 지칭되는, VPE(22(1)) 내의 프로세싱 스테이지는 특정 작업 또는 동작을 수행하도록 설계된 회로 및 연관된 벡터 데이터 경로들을 포함한다. 벡터 프로세싱 연산은 몇몇의 상이한 프로세싱

스테이지들에서 VPE(22(1))에 의해 실행될 수 있다. 각각의 프로세싱 스테이지는 VPE(22(1))의 하나 또는 다수의 클록 사이클들에 걸쳐 수행될 수 있다. 결과적으로, VPE(22(1)) 내의 벡터 프로세싱 연산의 실행은 완료하는데 많은 클록 사이클들이 걸릴 수 있는데, 왜냐하면 벡터 프로세싱 연산의 각각의 프로세싱 스테이지가 하나 또는 그 초과의 클록 사이클들 각각을 소비할 수 있기 때문이다. 예컨대, 프로세싱 스테이지는 도 4의 VPE(22(1))의 텁핑-지연 라인들(78)로의 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 패치를 포함할 수 있다. VPE(22(1)) 내의 벡터 프로세싱 스테이지들이 파이프라이닝될 수 있다.

[0044] 실행 유닛들(84(0)-84(X))은 패치된 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 프로세싱하는 하나 또는 그 초과의 파이프라인 스테이지들을 포함할 수 있다. 예컨대, 실행 유닛들(84(0)-84(X)) 내의 하나의 파이프라인 스테이지는 누산 연산들을 수행하도록 구성된 누산 기들을 포함하는 누산 스테이지를 포함할 수 있다. 다른 예로서, 실행 유닛들(84(0)-84(X)) 내의 다른 파이프라인 스테이지는 곱셈 연산들을 수행하도록 구성된 곱셈기들을 포함하는 곱셈 스테이지를 포함할 수 있다.

[0045] 계속해서 도 4를 참조하면, 실행 유닛들(84(0)-84(X))은 필터 벡터 프로세싱 연산을 위해 도 2의 글로벌 레지스터 파일(40)에 저장된 필터 계수들(92(0)-92(Y-1)) 사이로부터 필터 계수(92)를 수신하고, 여기서 'Y'는 필터 벡터 프로세싱 연산을 위한 필터 계수들의 수와 동일할 수 있다. 실행 유닛들(84(0)-84(X)) 각각은 실행 유닛들(84(0)-84(X))에서 중간 필터 벡터 데이터 출력 샘플들을 제공하기 위해 벡터 필터 프로세싱 연산의 각각의 프로세싱 스테이지 동안에 수신된 필터 계수(92(0), 90(1), ..., 90(Y-1)) 중 하나와 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))의 시프트된 입력 벡터 데이터 샘플(86S(0), 86S(1), ..., 86S(X))을 곱셈하도록 구성된다. 중간 필터 벡터 데이터 출력 샘플 세트들은 실행 유닛들(84(0)-84(X)) 각각에서 누산된다(즉, 이전의 누산된 필터 출력 벡터 데이터 샘플이 현재 누산된 필터 출력 벡터 데이터 샘플에 가산됨). 이것은 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X)) 내의 각각의 시프트된 입력 벡터 데이터 샘플 세트(86S(0), 86S(1), ..., 86S(X))에 대해 출력 데이터 흐름 경로들(98(0)-98(X)) 상의 실행 유닛 출력들(96(0)-96(X)) 상에서 실행 유닛들(84(0)-84(X))에 의해 각각 제공되는 마지막, 결과적 필터 출력 벡터 데이터 샘플 세트(94(0)-94(X))를 제공한다. 결과적 필터 출력 벡터 데이터 샘플 세트(94(0)-94(X))는, 이러한 예에서, 94(0), 94(1), ..., 및 94(X)인 'X+1' 결과적 필터 출력 벡터 데이터 샘플들(94)을 포함한다. 결과적 필터 출력 벡터 데이터 샘플 세트(94(0)-94(X))는, 실행 유닛들(84(0)-84(X))에 의해 생성된 중간 필터 벡터 데이터 출력 샘플 세트들을 저장 및 시프트하지 않고서, VPE(22(1))에 의한 추가의 사용 및/또는 프로세싱을 위해 각각의 벡터 데이터 파일들(82(0)-82(X))에 다시 저장된다.

[0046] 도 4를 계속 참조하고, 아래에 더 상세히 논의될 바와 같이, 텁핑-지연 라인들(78)은 프로세싱된 벡터 명령에 따라 제어되도록 프로그램 가능하다. 필터 벡터 명령이 프로세싱되지 않는다면, 텁핑-지연 라인들(78)은 벡터 데이터 파일들(82(0)-82(X))과 실행 유닛들(84(0)-84(X)) 사이의 입력 데이터 흐름 경로들(80(0)-80(X))에 포함되지 않도록 프로그램될 수 있다. 이러한 실시예에서, 텁핑-지연 라인들(78)은 필터 벡터 프로세싱 연산의 각각의 필터 텁에 대한 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 제공하기 위해 벡터 데이터 파일들(82(0)-82(X))로부터 수신된 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 로딩 및 시프트하도록 구성된다. 따라서, 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))는 필터 벡터 프로세싱 연산의 필터 텁의 실행을 위해 실행 유닛들(84(0)-84(X))에 제공될 수 있다. 텁핑-지연 라인들(78) 없이, 필터 벡터 프로세싱 연산의 후속 필터 텁들에 대해 시프트된 중간 입력 벡터 데이터 샘플 세트를 다시 실행 유닛들(84(0)-84(X))에 제공하기 위해 별개의 시프팅 프로세스가 수행되어야 할 것이고, 이로써 레이턴시를 증가시키고 부가적인 전력을 소비한다. 또한, VPE(22(1)) 내의 입력 및 출력 데이터 흐름 경로들(80(0)-80(X), 98(0)-98(X))의 효율은 필터 벡터 프로세싱 연산 동안에 벡터 데이터 파일들(82(0)-82(X))로부터 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))의 재패치 지연에 의해 제한되지 않는다.

[0047] 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))는 실행 유닛들(84(0)-84(X))에 로컬화된 텁핑-지연 라인들(78)에 의해 제공된다. 실행 유닛들(84(0)-84(X)) 내의 벡터 프로세싱은 데이터 흐름 제한들보다는 계산 자원들에 의해서만 제한된다. 이것은, 실행 유닛들(84(0)-84(X))이, 벡터 데이터 파일들(82(0)-82(X))로부터 패치될 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 대기해야 하지 않고서 벡터 프로세싱 연산들을 수행하기 위해 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 계속해서 또는 실질적으로 계속해서 수신하기에 바쁘다는 것을 의미한다.

[0048] 또한, 도 4의 VPE(22(1))에 의해 수행되는 필터 벡터 프로세싱 연산들은 텁핑-지연 라인들(78)을 사용함으로써 더 정밀할 수 있는데, 왜냐하면 실행 유닛들(84(0)-84(X)) 내의 중간 필터 프로세싱 스테이지들에 대한 출력 누산들이 벡터 데이터 파일들(82(0)-82(X))에 저장될 필요가 없기 때문이다. 실행 유닛들(84(0)-84(X))로부터의

중간 출력 벡터 데이터 샘플 세트들의 벡터 데이터 파일들(82(0)-82(X)) 내의 저장은 라운딩을 발생시킬 수 있다. 따라서, 다음 중간 출력 벡터 데이터 샘플 세트가 벡터 프로세싱 연산을 위해 실행 유닛들(84(0)-84(X))에 제공될 때, 임의의 라운딩 에러가 벡터 프로세싱 연산의 각각의 곱셈 단계 동안에 전파 및 부가될 것이다. 이와 반대로, 도 4의 VPE(22(1))의 예에서, 실행 유닛들(84(0)-84(X))에 의해 계산된 중간 출력 벡터 데이터 샘플 세트들은 벡터 데이터 파일들(82(0)-82(X))에 저장될 필요가 없다. 실행 유닛들(84(0)-84(X))은 다음 필터 지연 텁들에 대해 이전의 중간 출력 벡터 데이터 샘플 세트들과 중간 출력 벡터 데이터 샘플 세트들을 누산할 수 있는데, 왜냐하면 텁핑-지연 라인들(78)이 프로세싱될 벡터 프로세싱 연산 동안에 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 실행 유닛들(84(0)-84(X))에 제공하기 때문이고, 결과들은 이전의 필터 지연 텁들에 대해 이전의 벡터 데이터 샘플 세트들과 누산된다.

[0049] 도 4를 계속 참조하면, VPE(22(1))는 이러한 실시예에서 병렬화된 프로세싱을 위해 복수의 벡터 데이터 레인들(VLANE0-VLANEX)로 라벨링됨(100(0)-100(X))을 포함한다. 각각의 벡터 데이터 레인(100(0)-100(X))은 이러한 실시예에서 벡터 데이터 파일(82) 및 실행 유닛(84)을 포함한다. 예로서 벡터 데이터 레인(100(0))을 취하면, 그 안의 벡터 데이터 파일(82(0))은 필터 벡터 프로세싱을 위해 실행 유닛(84(0))에 의해 수신될 입력 벡터 데이터 샘플(86(0))을 입력 데이터 흐름 경로(80(0)) 상에서 제공하도록 구성된다. 위에서 논의된 바와 같이, 입력 벡터 데이터 샘플(86(0))을 시프트하고 필터 벡터 프로세싱을 위해 시프트된 입력 벡터 데이터 샘플 세트(86S(0))를 실행 유닛(84(0))에 제공하기 위해, 텁핑-지연 라인들(78)이 입력 데이터 흐름 경로(80(0))에 제공된다. 벡터 데이터 파일(82(0))은 또한, VPE(22(1))에 의해 프로세싱될 현재 또는 다음 벡터 명령에 따라 필요로 되거나 요구될 때, 후속 벡터 프로세싱 연산을 위해 벡터 데이터 파일(82(0))에 다시 저장될 출력 데이터 흐름 경로(98(0))로부터의 필터 벡터 프로세싱의 결과로서 실행 유닛(84(0))에 의해 제공되는 결과적 필터 출력 벡터 데이터 샘플(94(0))을 수신하도록 구성된다.

[0050] 요구되는 바에 따라, 임의의 수의 벡터 데이터 레인들(100(0)-100(X))이 VPE(22(1))에 제공될 수 있다. VPE(22(1))에 제공되는 벡터 데이터 레인들(100(0)-100(X))의 수는, 부가적인 벡터 데이터 레인들(100(0)-100(X))을 제공하는 데에 수반되는 부가적인 회로, 공간, 및 전력 소비에 대한(versus), 효율성 목적들을 위한 병렬화된 벡터 프로세싱을 위한 트레이드오프들에 기초할 수 있다. 하나의 비제한적인 예로서, 16개의 벡터 데이터 레인들(100)이 VPE(22(1))에 제공될 수 있으며, 각각의 벡터 데이터 레인(100)은, VPE(22(1)) 내에 벡터 데이터의 최대 512 비트의 병렬화된 프로세싱을 제공하기 위해, 삼십이(32) 비트들의 데이터 폭 능력을 갖는다.

[0051] 도 4를 계속해서 참조하면, 일 예로서, 하지만 모든 벡터 데이터 파일들(82(0)-82(X))에 대해 적용 가능한 예로서, 벡터 데이터 레인(100(0)) 내의 벡터 데이터 파일(82(0))을 사용하여, 벡터 데이터 파일(82(0))은 입력 벡터 데이터 샘플(86(0)) 중 하나 또는 다수의 샘플들이 벡터 프로세싱을 위해 저장되도록 허용한다. 입력 벡터 데이터 샘플(86(0))의 폭은, VPE(22(1))에 의해 실행되는 특정 벡터 명령에 따른 입력 벡터 데이터 샘플(86(0))의 프로그래밍에 따라 제공된다. 입력 데이터 흐름 경로(80(0))의 폭은, 텁핑-지연 라인들(78) 및 실행 유닛(84(0))에 입력 벡터 데이터 샘플(86(0))의 상이한 폭들을 제공하기 위해, 벡터 명령 단위(vector-instruction-by-vector-instruction basis)(주어진 벡터 명령에 대한 클록 사이클 단위(clock-cycle-by-clock-cycle basis)를 포함함)으로 프로그램 가능하고 재프로그램 가능하다. 이러한 방식으로, 벡터 데이터 레인(100(0))은, 실행되는 벡터 명령의 타입에 따라, 입력 벡터 데이터 샘플(86(0))의 상이한 폭들의 프로세싱을 제공하기 위해 프로그램되고 재프로그램될 수 있다.

[0052] 예컨대, 벡터 데이터 파일(82(0))은 삼십이(32) 비트 폭(wide)일 수 있고, 또한 최대 삼십이(32) 비트 폭일 수 있는 입력 벡터 데이터 샘플들(86)을 저장할 수 있다. 입력 벡터 데이터 샘플(86(0))은 벡터 데이터 파일(82(0))의 전체 폭(예컨대, 32 비트들)을 소비할 수 있거나, 또는 벡터 데이터 파일(82(0)) 폭의 더 작은 샘플 크기들로 제공될 수 있다. 입력 벡터 데이터 샘플(86(0)) 크기는, VPE(22(1))에 의해 실행되는 벡터 명령에 기초하는 입력 벡터 데이터 샘플(86(0))의 크기에 대한 입력 데이터 흐름 경로(80(0)) 구성의 프로그래밍에 기초하여 구성될 수 있다. 예컨대, 입력 벡터 데이터 샘플(86(0))은 하나의 벡터 명령에 대해 두개(2)의 개별적인 16 비트 벡터 데이터 샘플들을 포함할 수 있다. 다른 예로서, 입력 벡터 데이터 샘플(86(0))은, 한개(1)의 32 비트 벡터 데이터 샘플과 대조적으로, 다른 벡터 명령에 대해 벡터 데이터 파일(82(0))에 네개(4)의 8 비트 벡터 데이터 샘플들을 포함할 수 있다. 다른 예에서, 입력 벡터 데이터 샘플(86(0))은 한개(1)의 32 비트 벡터 데이터 샘플을 포함할 수 있다. VPE(22(1))는 또한, 각각의 벡터 명령 및/또는 주어진 벡터 명령의 각각의 클록 사이클에 대해 벡터 데이터 파일(82(0))에 실행 유닛(84(0))에 의해 제공되는 결과적 필터 출력 벡터 데이터 샘플들(94(0))의 상이한 크기들을 수신하기 위해, 벡터 데이터 파일(82(0))에 대한 출력 데이터 흐름 경로(98(0))를 프로그램 및 재프로그래밍할 수 있다.

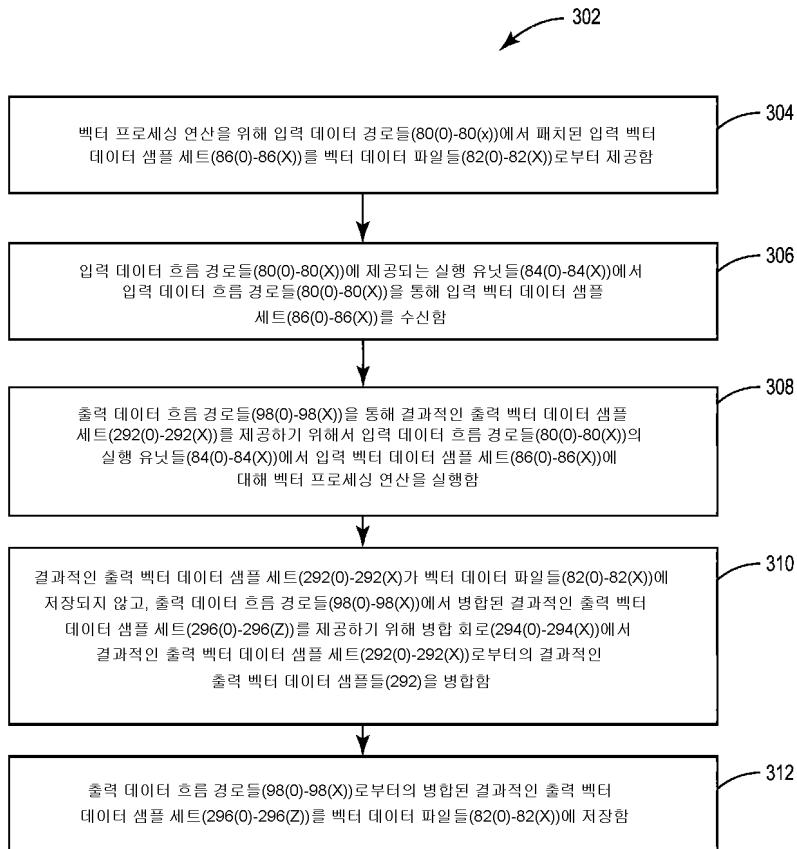

[0053] 이제, 본 실시예에서 입력 데이터 흐름 경로들(80(0)-80(X)) 내의 실행 유닛들(84(0)-84(X))에 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 제공하기 위한 탭핑-지연 라인들(78) 및 도 4의 VPE(22(1))의 부가적인 세부사항들 및 피쳐들의 추가의 설명이 설명될 것이다. 이와 관련하여, 도 5는, 예시적인 필터 벡터 명령에 따라, 탭핑-지연 라인들(78)을 이용하여 도 4의 VPE(22(1))에서 수행될 수 있는 예시적인 필터 벡터 프로세싱 연산(102)을 예시하는 흐름도이다. 도 5의 필터 벡터 프로세싱 연산(102)에서 수행되는 예시적인 태스크들이 도 6a 내지 도 10에 제공되는 예들과 관련하여 설명될 것이다.

[0054] 도 5를 참조하여, 필터 벡터 프로세싱 연산(102)을 위해, 필터 벡터 명령에 따라 필터 벡터 프로세싱 연산(102)에서 프로세싱될 입력 벡터 데이터 샘플 세트(86(0)-86(X))가 벡터 데이터 파일들(82(0)-82(X))로부터 입력 데이터 흐름 경로들(80(0)-80(X))로 패치된다(블록(104)). 도 4에서 VPE(22(1))와 관련하여 상기 논의된 바와 같이, 입력 벡터 데이터 샘플 세트(86(0)-86(X))에는, 실행 유닛들(84(0)-84(X)) 내의 글로벌 레지스터 파일(40)로부터 수신된 필터 계수들(92(0)-92(Y-1))이 곱해진다. 예컨대, 도 6a는 글로벌 레지스터 파일(40) 내의 필터 계수들(92(0)-92(Y-1))(즉, h7-h0)을 예시한다. 이러한 예에서, 수행될 필터 벡터 프로세싱 연산(102)에 여덟개(8)의 필터 탭들을 제공하는 글로벌 레지스터 파일(40)에 저장된 여덟개(8)의 필터 계수들(92)이 존재한다. 이러한 예에서, 상기 논의된 도 3의 이산 FIR 필터(64) 방정식으로부터의 필터 벡터 프로세싱 연산(102)은  $y[n] = x[n]*h0 + x[n-1]*h1 + \dots + x[n-7]*h7$  임을 주목한다.

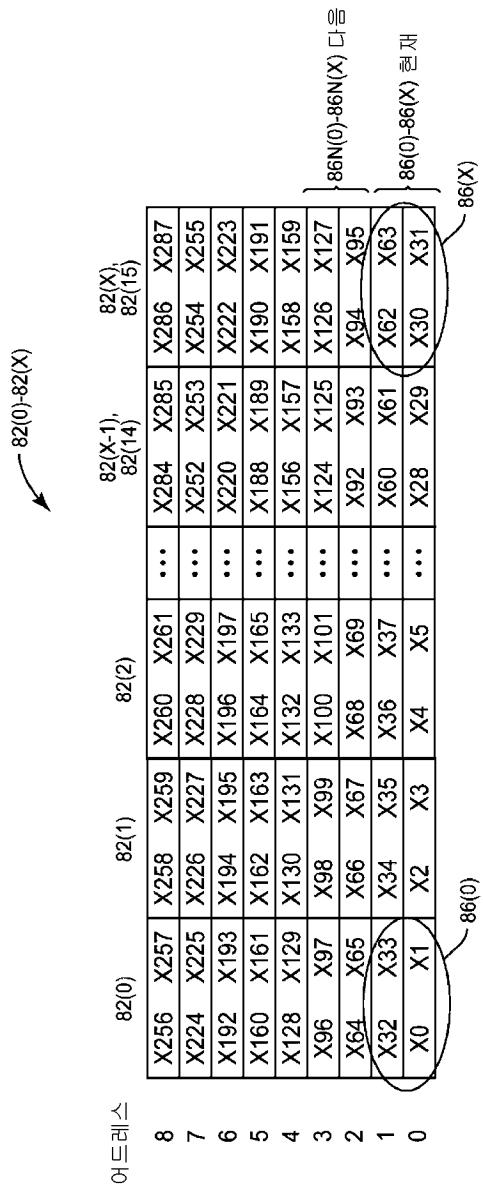

[0055] 도 6b는 필터 벡터 프로세싱 연산(102)에 의해 필터링될 입력 신호를 나타내는, 도 4의 VPE(22(1)) 내의 벡터 데이터 파일들(82(0)-82(X)) 내에 저장되는 예시적인 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 예시한다. 이러한 예에서, 샘플(X0)은 가장 오래된 샘플이고, 샘플(X63)은 가장 최근의 샘플이다. 다시 말해, 이러한 예에서, 샘플(X63)은 시간적으로 샘플(X0) 이후에 발생한다. 도 6b에 도시된 바와 같이, 벡터 데이터 파일들(82(0)-82(X))의 각각의 어드레스는 16 비트 폭이기 때문에, 벡터 데이터 파일들(82(0)-82(X))에 저장된 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 ADDRESS 0 및 ADDRESS 1에 걸친다(span). 이는, 도 4의 VPE(22(1)) 예에서의 실행 유닛들(84(0)-84(X))의 32 비트 폭 능력을 지원하기 위해, 벡터 데이터 파일들(82(0)-82(X))이 32 비트 폭의 입력 벡터 데이터 샘플들(86)을 제공하도록 허용한다. 이와 관련하여, 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 포함하는, 유크네개(64)의 총 입력 벡터 데이터 샘플 서브세트들(즉, X0-X63)이 존재하며, 각각의 8 비트 폭은 총 512 비트들이다. 유사하게, ADDRESS 2 및 ADDRESS 3은, 벡터 데이터 파일들(82(0)-82(X)) 내에 저장된 다른 제 2 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 저장한다. 도 6b의 이러한 예에서는, 256개의 총 입력 벡터 데이터 샘플들(86)(즉, X0-X255)을 예시하는, 각각의 벡터 데이터 파일(82(0)-82(X))의 여덟개(8)의 어드레스들(ADDRESS 0-7)이 도시되어 있지만, 이는 제한적인 것이 아님을 주목한다.

[0056] 도 4의 VPE(22(1)) 내의 벡터 데이터 레인들(100(0)-100(X)) 중에서 어느 하나, 일부, 또는 전부는, 필터 벡터 프로세싱 연산(102)에 수반되는 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 폭에 따라서 벡터 명령의 프로그래밍에 따라 필터 벡터 프로세싱 연산(102)을 제공하기 위해 이용될 수 있다. 벡터 데이터 파일들(82(0)-82(X))의 전체 폭이 요구되는 경우, 모든 벡터 데이터 레인들(100(0)-100(X))이 필터 벡터 프로세싱 연산(102)을 위해 이용될 수 있다. 필터 벡터 프로세싱 연산(102)은, 필터 벡터 프로세싱 연산(102)을 위해 이용될 수 있는 벡터 데이터 레인들(100(0)-100(X))의 서브세트만을 요구할 수 있음을 주목한다. 이는, 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 폭이 모든 벡터 데이터 파일들(82(0)-82(X))의 폭 미만이기 때문일 수 있는데, 이 경우, 필터 벡터 프로세싱 연산(102)과 동시에 수행될 다른 벡터 프로세싱 연산들을 위해 부가적인 벡터 데이터 레인들(100)을 이용할 것이 요구된다. 본 예를 논의하는 목적들로, 필터 벡터 프로세싱 연산(102)에서 이용되는 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 모든 벡터 데이터 레인들(100(0)-100(X))을 수반하는 것으로 가정한다.

[0057] 도 5를 다시 참조하면, 벡터 데이터 파일들(82(0)-82(X))로부터의 패치된 입력 벡터 데이터 샘플 세트(86(0)-86(X))가 입력 데이터 흐름 경로들(80(0)-80(X))에 제공되어, 탭핑-지연 라인들(78) 내로 현재 입력 벡터 데이터 샘플 세트(86(0)-86(X))로서 로딩된다(블록(106)). 입력 벡터 데이터 샘플 세트(86(0)-86(X))는, 필터 벡터 프로세싱 연산(102)을 위해 실행 유닛들(84(0)-84(X))에 의해 프로세싱될 입력 벡터 데이터 샘플 세트(86(0)-86(X))로서 1차 탭핑-지연 라인(78(0)) 내로 로딩된다. 1차 탭핑-지연 라인(78(0)) 내로 로딩된 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 필터 벡터 프로세싱 연산(102)의 제 1 필터 탭 연산을 위해 시프트되지 않는다. 하지만, 상기 논의된 바와 같이 그리고 도 7과 관련하여 하기에서 더 상세히 논의되는 바와 같이, 탭핑-지연 라인들(78)의 목적은, 필터 벡터 프로세싱 연산(102)의 이후의 필터 탭 연산들을 위해, 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 실행 유닛들(84(0)-84(X))에 제공하기 위하여 입력 벡터 데이터 샘플

세트(86(0)-86(X))의 시프트를 제공하는 것이다. 실행 유닛들(84(0)-84(X))에 의해 실행되는 필터 벡터 프로세싱 연산(102)의 각각의 프로세싱 스테이지 동안, 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 실행 유닛들(84(0)-84(X))에 제공하기 위해, 입력 벡터 데이터 샘플들(86)은 1차 템핑-지연 라인(78(0))에서 시프트된다. 이러한 방식으로, 입력 벡터 데이터 샘플 세트(86(0)-86(X))는, 필터 벡터 프로세싱 연산(102)의 각각의 필터 텁 연산을 위해, 저장되고, 벡터 데이터 파일들(82(0)-82(X)) 내에서 시프트되고, 재패치될 필요가 없다.

[0058] 선택적인 색도우 템핑-지연 라인(78(1))이 VPE(22(1))에 제공되는 경우, 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))가 또한, 벡터 데이터 파일들(82(0)-82(X))로부터 색도우 템핑-지연 라인(78(1)) 내로 로딩될 수 있다. 도 7과 관련하여 하기에서 더 상세히 논의될 바와 같이, 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))는, 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))의 적어도 일부가 되도록, 필터 벡터 프로세싱 연산(102) 동안 1차 템핑-지연 라인(78(0)) 내로 시프트된다. 따라서, 필터 벡터 프로세싱 연산(102)을 위해 실행될 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))가 벡터 데이터 파일들(82(0)-82(X))로부터 1차 템핑-지연 라인(78(0))으로 패치될 때까지, 실행 유닛들(84(0)-84(X))이 대기할 것을 요구하였을 경우에 초래되었을 패치 지연없이, 1차 템핑-지연 라인(78(0))이, 필터 벡터 프로세싱 연산(102) 동안 이용가능한 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 가질 수 있다.

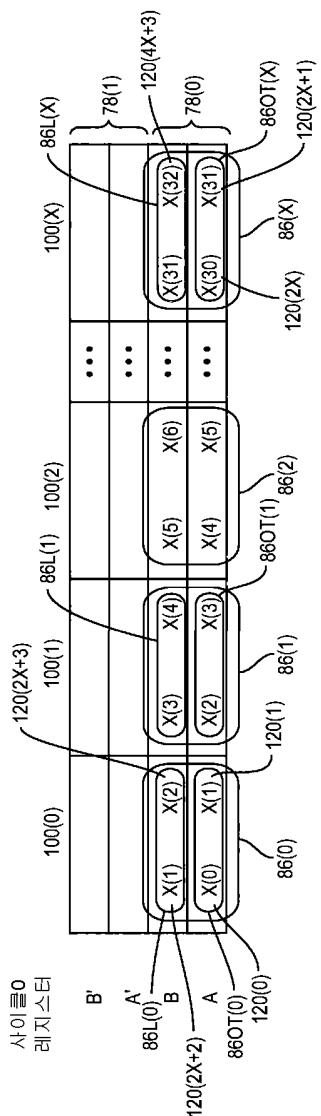

[0059] 이와 관련하여, 도 7은 도 4에서 VPE(22(1)) 내에 제공될 수 있는 예시적인 템핑-지연 라인들(78)을 예시한다. 이러한 실시예에서, 템핑-지연 라인들(78)은 색도우 템핑-지연 라인(78(1)) 및 1차 템핑-지연 라인(78(0))을 포함한다. 이러한 예에서 1차-템핑 지연 라인(78(0))은, 길이에 있어서 8 비트들까지의 입력 벡터 데이터 샘플들(86)의 분해능을 허용하기 위해, 복수의 8 비트 1차 파이프라인 레지스터들(120)로 구성된다. 하기에서 도 9a와 관련하여 논의될 바와 같이, 본 예에서, 실행 유닛들(84(0)-84(X))에 의해 프로세싱되는 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 필터 벡터 프로세싱 연산(102)의 제 1 필터 텁을 위해 시프트되지 않을 것이다. 실행 유닛들(84(0)-84(X))은 필터 벡터 프로세싱 연산(102)을 위해 이후의 필터 텁들을 프로세싱하기 때문에, 1차 템핑-지연 라인(78(0))에 저장된 입력 벡터 샘플 세트(86(0)-86(X)) 내의 입력 벡터 데이터 샘플들(86)은, 도 7에서 화살표들에 의해 나타낸 바와 같이, 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))가 되도록, 1차 파이프라인 레지스터들(120(0)-120(4X+3))에서 시프트된다. 이러한 방식으로, 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 저장 및 시프트하고, 벡터 데이터 파일들(82(0)-82(X))로부터, 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))의 필터 벡터 프로세싱 연산(102)을 수신하고 수행함으로써, 실행 유닛들(84(0)-84(X))이 완전히 활용된다.

[0060] 이러한 실시예에서, 1차 파이프라인 레지스터들(120(0)-120(4X+3))이 집합적으로, 도 4에서의 벡터 데이터 파일들(82(0)-82(X))의 폭이다. 폭이 512 비트인 벡터 데이터 파일들(82(0)-82(X))("X"는 십오(15)임)의 예에서는, 512 비트들의 총 폭을 제공하기 위해 육십네개(64)의 총 1차 파이프라인 레지스터들(120(0)-120(63))(각각 팔(8) 비트 폭임)이 존재할 것이다(즉, 각각 64 레지스터들 x 8 비트들). 따라서, 이러한 예에서, 1차 템핑-지연 라인(78(0))은 한개(1)의 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 전체 폭을 저장할 수 있다. 본 예에서는 팔(8) 비트 폭의 1차 파이프라인 레지스터들(120(0)-120(4X+3))을 제공함으로써, 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 8 비트 필터 벡터 프로세싱 연산들에 대해 팔(8) 비트들의 벡터 데이터 샘플 크기까지 아래로 1차 파이프라인 레지스터들(120(0)-120(4X+3)) 내에서 시프트될 수 있다. 필터 벡터 프로세싱 연산을 위해, 예컨대 16 비트 또는 32 비트 샘플들과 같은, 더 큰 크기의 입력 벡터 데이터 샘플(86) 크기들이 요구되는 경우, 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 한 번에 두개(2)의 1차 파이프라인 레지스터들(120) 만큼 1차 파이프라인 레지스터들(120(0)-120(4X+3)) 내에서 시프트될 수 있다.

[0061] 도 7을 계속해서 참조하면, 색도우 템핑-지연 라인(78(1))이 또한, 템핑-지연 라인(78) 내에 제공된다. 색도우 템핑-지연 라인(78(1))은, 이후의 벡터 프로세싱 연산을 위해 벡터 데이터 파일들(82(0)-82(X))로부터 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))를 래칭 또는 파이프라이닝하는 데에 사용될 수 있다. 필터 벡터 프로세싱 연산(102)에 대한 각각의 필터 텁이 실행 유닛들(84(0)-84(X))에 의해 실행될 때, 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))로부터의 다음 입력 벡터 데이터 샘플들(86N)은, 색도우 템핑-지연 라인(78(1))으로부터 1차 템핑-지연 라인(78(0))으로 시프트된다. 색도우 템핑-지연 라인(78(1)) 또한, 1차 템핑-지연 라인(78(0))과 유사하게, 길이에 있어서 8 비트들까지의 입력 벡터 데이터 샘플들(86)의 분해능을 허용하기 위해, 복수의 8 비트 색도우 파이프라인 레지스터들(122)로 구성된다. 1차 파이프라인 레지스터들(120(0)-120(4X+3))처럼, 색도우 템핑-지연 라인(78(1)) 내에 제공되는 색도우 파이프라인 레지스터들(122(0)-122(4X+3))은 집합적으로 벡터 데이터 파일들(82(0)-82(X))의 폭인데, 이는 본 예에서 512 비트들이다. 따라서, 색도우 템핑-지연

라인(78(1))의 색도우 파이프라인 레지스터들(122(0)-122(4X+3)) 또한, 한개(1)의 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 전체 폭을 저장할 수 있다. 따라서, 이러한 실시예에서, 1차 텁抨-지연 라인(78(0)) 내에 포함되는 색도우 파이프라인 레지스터들(122(0)-122(4X+3))의 수는 벡터 데이터 레인들(100(0)-100(X))의 수의 4 배이며, 이는 본 예에서 총 열여섯개(16)이다(즉, X=15). 따라서, 색도우 파이프라인 레지스터들(122)의 수 또한, 총 512 비트들에 대해 본 예에서 총 육십네개(64)이다(즉, 각각 64 레지스터들 x 8 비트들). 1차 텁抨-지연 라인(78(0))과 관련하여 상기 논의된 바와 같이, 본 예에서 팔(8) 비트 폭의 색도우 파이프라인 레지스터들(122(0)-122(4X+3))을 제공함으로써, 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))는 8 비트 필터 벡터 프로세싱 연산들에 대해 팔(8) 비트들의 벡터 데이터 샘플 크기까지 아래로 시프트될 수 있다.

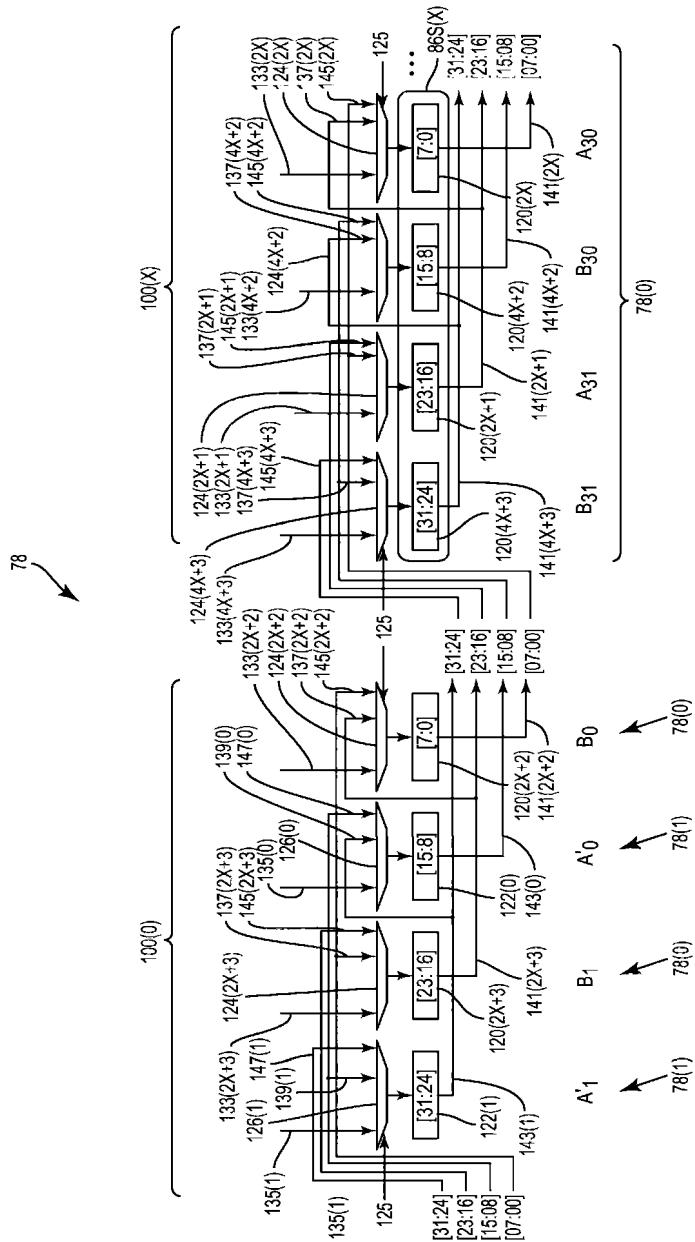

[0062] 도 8은 도 7에서의 1차 및 색도우 텁抨-지연 라인들(78(0), 78(1)) 내에 존재하는 선택된 1차 파이프라인 및 색도우 파이프라인 레지스터들(120, 122)을 예시하는 개략도이다. 도 8은 1차 및 색도우 파이프라인 레지스터들(120, 122) 간에 입력 벡터 데이터 샘플들(86)을 시프트시키는 예를 논의하는 것을 용이하게 하기 위해 제공된다. 상기 논의된 바와 같이, 입력 벡터 데이터 샘플들(86)은 또한, 1차 및 색도우 텁抨-지연 라인들(78(0), 78(1)) 내에서 뿐만 아니라, 색도우 텁抨-지연 라인(78(1))으로부터 1차 텁抨-지연 라인(78(0))으로 시프트될 수 있다. 파이프라인 레지스터들(120, 122)은, 요구되는 경우 8 비트의 분해능으로 시프트하는 입력 벡터 데이터 샘플(86)을 허용하기 위해, 본 예에서 각각 8 비트 폭이다. 이는 하기에서 보다 상세히 논의될 것이다. 1차 및 색도우 텁抨-지연 라인들(78(0), 78(1))은 또한, 하기에서 보다 상세히 또한 논의될 바와 같이, 입력 벡터 데이터 샘플들(86)의 16 비트 및 32 비트 시프팅 분해능을 수행할 수 있다.

[0063] 이와 관련하여, 도 8은, 도 7에서의 1차 텁抨-지연 라인(78(0)) 내의 입력 벡터 데이터 샘플(86S(X))에 대한 저장 레지스터들을 형성하는 1차 파이프라인 레지스터들(120(4X+3), 120(2X+1), 120(4X+2), 및 120(2X))로의 입력 벡터 데이터 샘플들(86)의 시프팅을 예시한다. 1차 파이프라인 레지스터들(120(4X+3) 및 120(4X+2))은 각각, 도 7에서의 1차 텁抨-지연 라인(78(0)) 내의 레지스터들(B<sub>31</sub> 및 B<sub>30</sub>)이다. 1차 파이프라인 레지스터들(120(2X+1) 및 120(2X))은 각각, 도 7에서의 1차 텁抨-지연 라인(78(0)) 내의 레지스터들(A<sub>31</sub> 및 A<sub>30</sub>)이다. 도 7에 예시된 바와 같이, 레지스터들(B<sub>31</sub> 및 B<sub>30</sub>)에 대한 1차 파이프라인 레지스터들(120(4X+3) 및 120(4X+2))은, 색도우 텁抨-지연 라인(78(1)) 내의 인접하는 색도우 파이프라인 레지스터들(122)로부터, 시프트된 입력 벡터 데이터 샘플들(86)을 수신하도록 구성된다. 따라서, 도 8의 예에서, 레지스터들(A'<sub>0</sub> 및 A'<sub>1</sub>)에 대한 색도우 파이프라인 레지스터들(122(0), 122(1))은 각각, 입력 벡터 데이터 샘플들(86)을 B<sub>31</sub> 및 B<sub>30</sub>에 대한 1차 파이프라인 레지스터들(120(4X+3) 및 120(4X+2))로 시프트시키도록 구성된 것으로 예시된다. 유사하게, 도 8의 예에서, 1차 텁抨-지연 라인(78(0)) 내의 레지스터들(B<sub>1</sub> 및 B<sub>0</sub>)에 대한 1차 파이프라인 레지스터들(120(2X+3) 및 120(2X+2))은 각각, 입력 벡터 데이터 샘플들(86)을 레지스터들(A<sub>31</sub> 및 A<sub>30</sub>)에 대한 인접하는 1차 파이프라인 레지스터들(120(2X+1) 및 120(2X))로 시프트시키도록 구성된 것으로 예시된다. 이제, 이를 레지스터들 간의 입력 벡터 데이터 샘플들(86)의 예시적인 시프팅이 논의될 것이다.

[0064] 도 8을 계속해서 참조하면, 입력 벡터 데이터 샘플들(86)의 시프팅 뿐만 아니라, 도 4에서의 벡터 데이터 파일들(82(0)-82(X))로부터 새로운 입력 벡터 데이터 샘플 세트들(86(0)-86(X))을 로딩하기 위해 1차 및 색도우 파이프라인 레지스터들(120, 122)을 구성하는 유연성을 제공하기 위하여, 입력 벡터 데이터 샘플 선택기가 1차 및 색도우 파이프라인 레지스터들(120, 122) 각각과 연관된다. 이와 관련하여, 입력 벡터 데이터 샘플 선택기들(124(0)-124(4X+3))이 각각, 1차 텁抨-지연 라인(78(0)) 내의 1차 파이프라인 레지스터들(120(0)-120(4X+3))로 시프팅 또는 로딩된 벡터 데이터에 대해 제공된다. 입력 벡터 데이터 샘플 선택기들(126(0)-126(4X+3))이 각각, 색도우 텁抨-지연 라인(78(1)) 내의 색도우 파이프라인 레지스터들(122(0)-122(4X+3))로 시프팅 또는 로딩된 벡터 데이터에 대해 제공된다. 입력 벡터 데이터 샘플 선택기들(124(0)-124(4X+3)) 및 입력 벡터 데이터 샘플 선택기들(126(0)-126(4X+3))은 본 예에서 각각 멀티플렉서이다. 하기에서 보다 상세히 논의될 바와 같이, 입력 벡터 데이터 샘플 선택기들(124(0)-124(4X+3), 126(0)-126(4X+3))은, 1차 및 색도우 파이프라인 레지스터들(120(0)-120(4X+3), 122(0)-122(4X+3))로 시프팅 또는 로딩될 입력 벡터 데이터를 선택하기 위해 데이터 폭 시프트 제어 입력들(125)에 의해 각각 제어될 수 있다.

[0065] 도 8에서는, 레지스터들(B<sub>31</sub>, B<sub>30</sub>, A<sub>31</sub> 및 A<sub>30</sub>) 각각에 대응하는 1차 파이프라인 레지스터들(120(4X+3), 120(4X+2), 120(2X+1), 120(2X)) 각각에 대한 입력 벡터 데이터 샘플 선택기들(124(4X+3), 124(4X+2), 124(2X+1), 124(2X)) 만이 도시되어 있음을 주목한다. 도 8에는, 레지스터들(A'<sub>1</sub>, A'<sub>0</sub>, B<sub>1</sub>, 및 B<sub>0</sub>) 각각에 대응하는 파이프라인 레지스터들(122(1), 122(0), 120(2X+3), 120(2X+2)) 각각에 대한 입력 벡터 데이터 샘플 선택

기들(126(1), 126(0), 124(2X+3), 124(2X+2)) 만이 도시된다.

[0066] 도 8을 계속해서 참조하면, 벡터 프로세싱 연산을 위해 1차 및 색도우 텁抨-지연 라인들(78(0), 78(1)) 내로 새로운 입력 벡터 데이터가 로딩될 예정인 경우, 입력 벡터 데이터 샘플 선택기들(124(4X+3), 124(4X+2), 124(2X+1), 124(2X))로 하여금 로드 데이터 흐름 경로들(133(4X+3), 133(4X+2), 133(2X+1), 133(2X))을 선택하도록 하기 위해, 도 4에서의 VPE(22(1))에 의해 데이터 폭 시프트 제어 입력들(125)이 구성될 수 있다. 로드 데이터 흐름 경로들(133(4X+3), 133(4X+2), 133(2X+1), 133(2X))을 선택하는 것은, 벡터 데이터 파일들(82(0)-82(X))로부터의 입력 벡터 데이터가 1차 파이프라인 레지스터들(120(4X+3), 120(4X+2), 120(2X+1), 120(2X)) 내에 저장되도록 허용한다. 벡터 데이터 파일들(82(0)-82(X))로부터의 입력 벡터 데이터를 로딩하는 것은, 예로서 VPE(22(1))에 의해 프로세싱될 새로운 또는 다음 벡터 명령에 대해 수행될 수 있다. 유사하게, 데이터 폭 시프트 제어 입력들(125)은 또한, 입력 벡터 데이터 샘플 선택기들(126(1), 124(2X+3), 126(0), 124(2X+2))로 하여금 입력 데이터 흐름 경로들(135(1), 133(2X+3), 135(0), 133(2X+2))을 선택하도록 하기 위해, 도 4에서의 VPE(22(1))에 의해 구성될 수 있다. 로드 데이터 흐름 경로들(135(1), 133(2X+3), 135(0), 133(2X+2))을 선택하는 것은 벡터 데이터 파일들(82(0)-82(X))로부터의 입력 벡터 데이터가 파이프라인 레지스터들(122(1), 120(2X+3), 124(0), 120(2X+2)) 내에 저장되도록 허용한다.

[0067] 도 8을 계속해서 참조하면, 1차 텁抨-지연 라인(78(0)) 및 색도우 텁抨-지연 라인(78(1)) 내에 저장된 벡터 데이터가 벡터 프로세싱 연산을 위해 시프트될 것이 요구되는 경우, 데이터 폭 시프트 제어 입력들(125)은, 입력 벡터 데이터 샘플 선택기들(124(4X+3), 124(4X+2), 124(2X+1), 124(2X))로 하여금 벡터 데이터 샘플 시프팅을 위해 입력 데이터 흐름 경로들(137(4X+3), 137(4X+2), 137(2X+1), 137(2X))을 선택하도록 하기 위해, 도 4의 VPE(22(1))에 의해 구성될 수 있다. 데이터 폭 시프트 제어 입력들(125)은 또한, 입력 벡터 데이터 샘플 선택기들(126(1), 124(2X+3), 126(0), 124(2X+2))이 벡터 데이터 샘플 시프팅을 위해 입력 데이터 흐름 경로들(139(1), 137(2X+3), 139(0), 137(2X+2))을 선택하게 한다. 그 내에서 예시되는 바와 같이, 입력 벡터 데이터 샘플 선택기들(124(4X+3), 124(4X+2), 124(2X+1), 124(2X)) 및 입력 벡터 데이터 샘플 선택기들(126(1), 124(2X+3), 126(0), 124(2X+2)) 각각은, 벡터 데이터가 다른 레지스터들로 시프트될 수 있게 허용하는, 출력 데이터 흐름 경로들(141(4X+3), 141(4X+2), 141(2X+1), 141(2X) 및 143(1), 141(2X+3), 143(0), 124(2X+2))을 각각 포함한다. 도 8에 도시된 출력 데이터 흐름 경로들은, 이제 전체로서 도시되지만, 1차 텁抨-지연 라인(78(0)) 내의 입력 벡터 데이터 샘플 선택기들(124(0)-124(4X+3)) 및 색도우 텁抨-지연 라인(78(1)) 내의 입력 벡터 데이터 샘플 선택기들(126(0)-126(4X+3)) 각각에 대해 포함되는 출력 데이터 흐름 경로들(141(0)-141(4X+3) 및 143(0)-143(4X+3))의 일부이다.

[0068] 예들로서, 8 비트 벡터 데이터 시프트 동안, 입력 벡터 데이터 샘플 선택기들(124(4X+3), 124(4X+2), 124(2X+1), 124(2X)) 및 입력 벡터 데이터 샘플 선택기들(126(1), 124(2X+3), 126(0), 124(2X+2))은 입력 데이터 흐름 경로들(137(4X+3), 137(4X+2), 137(2X+1), 137(2X), 139(1), 137(2X+3), 139(0), 137(2X+2))을 각각 선택하도록 구성된다. 이와 관련하여, 일례로, 1차 파이프라인 레지스터(120(2X+1))(즉, A<sub>31</sub>)에서의 벡터 데이터는 도 8에 예시된 바와 같이, 출력 데이터 흐름 경로(141(2X+1)) 상에서 1차 파이프라인 레지스터(120(2X))(즉, A<sub>30</sub>)로 시프트된다. 1차 파이프라인 레지스터(120(4X+3))(즉, B<sub>31</sub>)에서의 벡터 데이터는 도 8에 예시된 바와 같이, 출력 데이터 흐름 경로(141(4X+3)) 상에서 1차 파이프라인 레지스터(120(4X+2))(즉, B<sub>30</sub>)로 시프트된다. 색도우 파이프라인 레지스터(122(0))(즉, A'<sub>0</sub>)에서의 벡터 데이터는 도 8에 예시된 바와 같이, 출력 데이터 흐름 경로(143(0)) 상에서 1차 파이프라인 레지스터(120(4X+3))(즉, B<sub>31</sub>)로 시프트된다. 1차 파이프라인 레지스터(120(2X+3))(즉, B<sub>1</sub>)에서의 벡터 데이터는 도 8에 예시된 바와 같이, 출력 데이터 흐름 경로(141(2X+3)) 상에서 1차 파이프라인 레지스터(120(4X+2))(즉, B<sub>30</sub>)로 시프트된다. 색도우 파이프라인 레지스터(122(1))(즉, A'<sub>1</sub>)에서의 벡터 데이터는 도 8에 예시된 바와 같이, 출력 데이터 흐름 경로(143(1)) 상에서 색도우 파이프라인 레지스터(122(0))(즉, A'<sub>0</sub>)로 시프트된다. 1차 파이프라인 레지스터(120(2X+2))(즉, B<sub>0</sub>)에서의 벡터 데이터는 도 8에 예시된 바와 같이, 출력 데이터 흐름 경로(141(2X+2)) 상에서 1차 파이프라인 레지스터(120(2X+1))(즉, A<sub>31</sub>)로 시프트된다.

[0069] 도 8을 계속해서 참조하면, 16 비트 벡터 데이터 시프트 동안, 입력 벡터 데이터 샘플 선택기들(124(4X+3), 124(4X+2), 124(2X+1), 124(2X)) 및 입력 벡터 데이터 샘플 선택기들(126(1), 124(2X+3), 126(0), 124(2X+2))은 입력 데이터 흐름 경로들(145(4X+3), 145(4X+2), 145(2X+1), 145(2X), 147(1), 145(2X+3), 147(0),

145(2X+2))을 각각 선택하도록 구성된다. 이와 관련하여, 일례로, 1차 파이프라인 레지스터(120(2X+2))(즉, B<sub>0</sub>)에서의 벡터 데이터는 도 8에 예시된 바와 같이, 출력 데이터 흐름 경로(141(2X+2)) 상에서 1차 파이프라인 레지스터(120(2X))(즉, A<sub>30</sub>)로 시프트된다. 색도우 파이프라인 레지스터(122(0))(즉, A'<sub>0</sub>)에서의 벡터 데이터는 도 8에 예시된 바와 같이, 출력 데이터 흐름 경로(143(0)) 상에서 1차 파이프라인 레지스터(120(4X+2))(즉, B<sub>30</sub>)로 시프트된다. 1차 파이프라인 레지스터(120(2X+3))(즉, B<sub>1</sub>)에서의 벡터 데이터는 도 8에 예시된 바와 같이, 출력 데이터 흐름 경로(141(2X+3)) 상에서 1차 파이프라인 레지스터(120(2X+1))(즉, A<sub>31</sub>)로 시프트된다. 색도우 파이프라인 레지스터(122(1))(즉, A'<sub>1</sub>)에서의 벡터 데이터는 도 8에 예시된 바와 같이, 출력 데이터 흐름 경로(143(1)) 상에서 1차 파이프라인 레지스터(120(4X+3))(즉, B<sub>31</sub>)로 시프트된다.

[0070] 1차 및 색도우 텁핑-지연 라인들(78(0), 78(1))에서 32 비트 벡터 데이터 시프트가 요구된다면, 1차 파이프라인 레지스터들(120(0)-120(4X+3)) 및 색도우 파이프라인 레지스터들(122(0)-122(4X+3))에 저장된 벡터 데이터는 2 개의 16 비트 벡터 데이터 시프트 연산들에서 원하는 경우, 시프트될 수 있다.

[0071] 도 7에서, 레지스터들(B<sub>31</sub>, B<sub>30</sub>)에 대한 1차 파이프라인 레지스터들(120(4X+3), 120(4X+2)) 및 레지스터들(A<sub>31</sub>, A<sub>30</sub>)에 대한 1차 파이프라인 레지스터들(120(2X+1), 120(2X))은 논리적으로는 시프트된 입력 벡터 데이터 샘플들(86S(X))로 서로 연관되지만, 물리적으로는 도 8에 예시된 바와 같이 서로 인접하지 않는다는 점에 주목한다. 도 6b에 예시된 바와 같이, 벡터 데이터 파일들(82(0)-82(X))에서 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 저장 패턴으로 인해 이 예에서는 이러한 배열이 제공된다. 도 6b에 또한 예시된 바와 같이, 벡터 데이터 파일들(82(0)-82(X))에 저장된 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 어드레스 0과 어드레스 1에 이른다. 그러나 본 명세서의 개시내용은 벡터 데이터 파일들(82(0)-82(X))에서 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 이러한 저장 패턴으로 한정되는 것은 아니라는 점에 주목한다.

[0072] 추가로, 도 8과 관련하여, 텁핑-지연 라인들(78(0), 78(1))은 실행될 벡터 명령에 따라 텁핑-지연 라인들(78(0), 78(1))에 대한 프로그램가능 입력 데이터 경로 구성에 기초하여 벡터 데이터 파일들(82(0)-82(X))과 실행 유닛들(84(0)-84(X)) 간의 입력 데이터 흐름 경로들(80(0)-80(X))에서 선택적으로 제공되거나 제공되지 않도록 구성가능하다. 예컨대, 벡터 명령이 필터 벡터 프로세싱 명령이 아니고 그리고/또는 다르게는 텁핑-지연 라인들(78(0), 78(1))이 입력 벡터 데이터 샘플 세트들(86(0)-86(X))을 시프트할 것을 요구한다면, 텁핑-지연 라인들(78(0), 78(1))은 입력 벡터 데이터 샘플 세트들(86(0)-86(X))을 래치하지 않도록 구성될 수 있다. 1차 및 색도우 텁핑-지연 라인들(78(0), 78(1))을 바이패스함으로써 벡터 데이터 파일들(82(0)-82(X))로부터 각각의 실행 유닛들(84(0)-84(X))로 입력 벡터 데이터 샘플 세트들(86(0)-86(X))이 제공될 수 있다. 이러한 프로그램가능 데이터 경로 구성은 추가로, 입력 데이터 흐름 경로들(80(0)-80(X))에서 1차 및 색도우 텁핑-지연 라인들(78(0), 78(1))이 제공되거나 제공되지 않게 한다. 1차 및 색도우 텁핑-지연 라인들(78(0), 78(1))은 원하는 경우, 각각의 벡터 명령에 대해 입력 데이터 흐름 경로들(80(0)-80(X))에서 제공되거나 제공되지 않도록 프로그램될 수 있다.

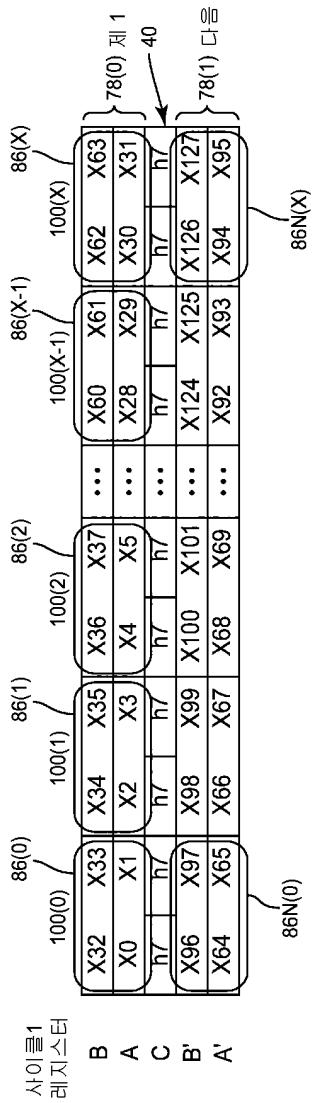

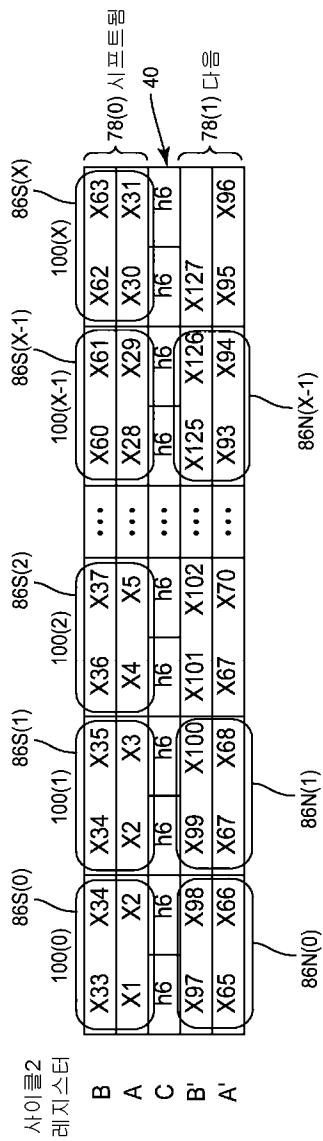

[0073] 도 9a는 필터 벡터 프로세싱 명령의 제 1 클록 사이클(CYCLE0) 동안 벡터 데이터 파일들(82(0)-82(X))로부터 1 차 텁핑-지연 라인(78(0))으로 로딩되는 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 예시한다. 1차 텁핑-지연 라인(78(0)) 및 색도우 텁핑-지연 라인(78(1))은 도 7로부터 단순화된 형태로 도시된다. 글로벌 레지스터 파일(40)이 또한 도시된다. 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 입력 벡터 데이터 샘플들(X0-X63)로서 1차 텁핑-지연 라인(78(0))에 로딩된다. 예컨대, 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 1차 텁핑-지연 라인(78(0))(그리고 또한 아래 더 상세히 논의되는 바와 같이, 색도우-텅핑-지연 라인(78(1)))으로 로딩하도록 특수 벡터 명령이 지원될 수도 있다. 이 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 도 6b에 도시된 벡터 데이터 파일들(82(0)-82(X))의 어드레스들 0 및 1에 저장되었다. 이 예에서, X0, X1, X32 및 X33은 제 1 입력 벡터 데이터 샘플(86(0))을 형성하는데, 이는 단지 이 예의 경우 도 4의 VPE(22(1))에서의 벡터 데이터 파일들(82(0)-82(X))의 저장 패턴이라는 점에 주목한다. 다른 입력 벡터 데이터 샘플들(86)은 도 9a에 도시된 바와 같이 비슷하게 형성된다(예컨대, 86(1), 86(2), … 86(X)). 입력 벡터 데이터 샘플들(86)을 함께 그룹화하여 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 형성하도록 다른 패턴들이 제공될 수 있다.

[0074] 도 9b는 필터 벡터 프로세싱 명령의 제 2 클록 사이클(CYCLE1) 동안 색도우 텁핑-지연 라인(78(1))으로 로딩되는 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))를 예시한다. 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(1))는 벡터 데이터 파일들(82(0)-82(X))로부터의 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X))가 필터 벡터 프로세싱 연산의 실행을 셋업하도록 1차 텁핑-지연 라인(78(0))으로 로딩된 후 색도우 텁핑-지연 라인

(78(1))으로 로딩된다. 이러한 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))는 입력 벡터 데이터 샘플들(X(64)-X(127))로서 색도우 텁핑-지연 라인(78(1))으로 로딩된다. 이러한 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))는 도 6b에 도시된 벡터 데이터 파일들(82(0)-82(X))의 어드레스를 2 및 3에 저장되었다. 이 예에서, X64, X65, X96 및 X97은 제 1 입력 벡터 데이터 샘플(86(0))을 형성하는데, 이는 단지 이 예의 경우 도 4의 VPE(22(1))에서의 벡터 데이터 파일들(82(0)-82(X))의 저장 패턴 때문이라는 점에 주목한다. 입력 벡터 데이터 샘플들(86)을 함께 그룹화하여 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 형성하도록 다른 패턴들이 제공될 수 있다. 글로벌 레지스터 파일(40)로부터의 제 1 필터 계수들(92(0))은 또한 필터 벡터 프로세싱 연산(102)에서 사용하기 위해 도 9b의 실행 유닛들(84(0)-84(X))로 레지스터("C")에서 제공되는 것으로 도시된다.

[0075] 도 7을 다시 참조하면, 입력 벡터 데이터 샘플들(86)이 필터 벡터 프로세싱 연산(102)의 각각의 프로세싱 스테이지 동안 1차 텁핑-지연 라인(78(0))에서 시프트될 때, 색도우 파이프라인 레지스터들(122)에 저장된 다음 입력 벡터 데이터 샘플들(86N)이 또한 색도우 텁핑-지연 라인(78(1))의 색도우 파이프라인 레지스터들(122)에서 시프트된다. 도 7에서 제 1 색도우 파이프라인 레지스터(122(0))에 저장된 입력 벡터 데이터 샘플(86)이 각각의 시프트 동안 1차 텁핑-지연 라인(78(0))의 마지막 1차 파이프라인 레지스터(120(4X+3))로 시프트된다. 따라서 이런 식으로, 필터 벡터 프로세싱 연산(102) 프로세싱 스테이지들이 실행 유닛들(84(0)-84(X))에서 진행할 때, 색도우 텁핑-지연 라인(78(1))에 초기에 저장된 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))의 적어도 일부가 1차 텁핑-지연 라인(78(0))으로 시프트되어 프로세싱을 위해 실행 유닛들(84(0)-84(X))에 제공된다. 이 예에서 시프트들의 수는 필터 벡터 프로세싱 연산(102)에서 제공되는 필터 텁들의 수에 좌우될 것이다. 벡터 데이터 파일들(82(0)-82(X))로부터의 1차 텁핑-지연 라인(78(0)) 및 색도우 텁핑-지연 라인(78(1))으로 패치되는 입력 벡터 데이터 샘플 세트(86(0)-86(X))에서 입력 벡터 데이터 샘플들(86)의 수가 필터 벡터 프로세싱 연산(102)에서 필터 텁들의 수보다 더 많다면, 실행 유닛들(84(0)-84(X))은 어떠한 추가 입력 벡터 데이터 샘플 세트들(86(0)-86(X))도 벡터 데이터 파일들(82(0)-82(X))로부터 재패치되지 않고 필터 벡터 프로세싱 연산(102)을 수행할 수 있다. 그러나 필터 벡터 프로세싱 연산(102)에서 필터 텁들의 수가 벡터 데이터 파일들(82(0)-82(X))로부터의 1차 텁핑-지연 라인(78(0)) 및 색도우 텁핑-지연 라인(78(1))으로 패치되는 입력 벡터 데이터 샘플 세트(86(0)-86(X))에서 입력 벡터 데이터 샘플들(86)의 수보다 더 많다면, 필터 벡터 프로세싱 연산(102)의 일부로서 벡터 데이터 파일들(82(0)-82(X))로부터 추가 입력 벡터 데이터 샘플 세트들(86(0)-86(X))이 패치될 수 있다. 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))에 대해 필터 벡터 프로세싱 연산(102)이 완료된 후, 다음에는 텁핑-지연 라인들(78(0), 78(1))에 프로세싱되지 않은 입력 벡터 데이터 샘플(86S)이 존재한다면 다음 상관 벡터 프로세싱 연산을 위한 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))로서 1차 텁핑-지연 라인(78(0))에 저장된 이전의 다음 입력 벡터 샘플 데이터 세트(86N(0)-86N(X))가 실행 유닛들(84(0)-84(X))에 제공될 수 있다.

[0076] 색도우 텁핑-지연 라인(78(1))을 제공하기 위한 다른 예시적인 근거는 다음과 같다. 현재 필터 벡터 프로세싱 연산(102)이 벡터 데이터 레인들(100(0)-100(X))의 폭으로 제공될 수 있는 것보다 더 많은 입력 벡터 데이터 샘플들(86)을 수반한다면, 색도우 텁핑-지연 라인(78(1))으로 로딩되는 추가 입력 벡터 데이터 샘플 세트(86(0)-86(X))가 필터 벡터 프로세싱 연산(102) 동안 지연 없이 실행 유닛들(84(0)-84(X))에 이용가능할 것이다. 앞서 논의된 바와 같이, 필터 벡터 프로세싱 연산(102)이 실행 동안 시프트된 입력 벡터 데이터 샘플 세트들(86S(0)-86S(X))에 걸쳐 진행할 때, 색도우 텁핑-지연 라인(78(1))으로 로딩되는 추가적인 다음 입력 벡터 데이터 샘플 세트들(86N(0)-86N(X))이 1차 텁핑-지연 라인(78(0))으로 시프트된다. 따라서 이런 식으로, 실행 유닛들(84(0)-84(X))에 의한 벡터 프로세싱에 사용하기 위한 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))가 지연 없이 이용가능하다. 실행 유닛들(84(0)-84(X))은 벡터 데이터 파일들(82(0)-82(X))의 폭의 단일 패치된 입력 벡터 데이터 샘플 세트(86(0)-86(X))가 전체 필터 벡터 프로세싱 연산(102)을 수행하기에 충분한지 여부에 관계 없이 필터 벡터 프로세싱 연산(102) 동안 계속해서 충분히 이용될 수 있다.

[0077] 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X)) 및 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))가 각각 1차 텁핑-지연 라인(78(0)) 및 색도우 텁핑-지연 라인(78(1))으로 로딩된 후, 1차 텁핑-지연 라인(78(0))에 제공된 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X))가 필터 벡터 프로세싱 연산(102)의 제 1 프로세싱 스테이지에서 프로세싱되도록 각각의 실행 유닛들(84(0)-84(X))에 제공된다(도 5의 블록(108)). 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X))가 실행 유닛들(84(0)-84(X))에 의해 프로세싱된 후 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 실행 유닛들(84(0)-84(X))에 의해 프로세싱될 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))가 되도록 1차 텁핑-지연 라인(78(0))에서 시프트된다. 도 4의 VPE(22(1))에서 예시된 것과 같이, 시프트된 입력 벡터 데이터 샘플(86S(0))은 실행 유닛(84(0))에 제공되고, 시프트된 입력 벡터 데이터 샘플(86S

(1)은 실행 유닛(84(1))에 제공되는 식이다.

[0078] 다음에, 실행 유닛들(84(0)-84(X))이 필터 벡터 프로세싱 연산(102)을 수행한다(도 5의 블록(110)). 보다 구체적으로, 실행 유닛들(84(0)-84(X))은 이 예에서는 연산:  $y[n] = x[n-7]*h7$ 에 따라 제 1 반복에서 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 현재 필터 계수(92(0))와 곱하여, 여기서  $x[n-7]$ 은 결과적 필터 출력 벡터 데이터 샘플 세트(94(0)-94(X))를 제공할 제 1 입력 벡터 데이터 샘플 세트(86(0)-86(X))이다. 필터 벡터 프로세싱 연산(102)의 다음 반복(도 5의 블록(110))에서, 필터 벡터 프로세싱 연산(102)에 대한 다음 시프트된 입력 벡터 데이터 샘플 세트들(86S(0)-86S(X))이 현재 필터 계수(92(1)-92(Y-1))와 곱해진다. 실행 유닛들(84(0)-84(X))은 새로운 이전의 결과적 필터 출력 벡터 데이터 샘플 세트(94(0)-94(X))를 제공하도록 결과적 필터 벡터 출력 벡터 데이터 샘플 세트(94(0)-94(X))를 실행 유닛들(84(0)-84(X))에 의해 계산된 이전의 결과적 필터 출력 벡터 데이터 샘플 세트(94(0)-94(X))와 누산한다(도 5의 블록(112)). 필터 벡터 프로세싱 연산(102)의 제 1 프로세싱 스테이지에는, 이전의 결과적 필터 출력 벡터 데이터 샘플 세트가 없다.

[0079] 필터 벡터 프로세싱 연산(102)의 모든 프로세싱 스테이지들이 완료되었다면(도 5의 블록(114)), 누산된 이전의 결과적 필터 출력 벡터 데이터 샘플 세트(94(0)-94(X))는 벡터 데이터 파일들(82(0)-82(X))에 제공되어 저장되도록 출력 데이터 흐름 경로들(98(0)-98(X))에서 결과적 필터 출력 벡터 데이터 샘플 세트(94(0)-94(X))로서 제공된다(도 5의 블록(116)). 필터 벡터 프로세싱 연산(102)의 모든 프로세싱 스테이지들이 완료되지 않았다면(도 5의 블록(114)), 텁抨-지연 라인들(78(0), 78(1))에 저장된 샘플들이 필터 벡터 프로세싱 연산(102)에 대한 다음 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 제공하도록 텁抨-지연 라인들(78(0), 78(1)) 내에서 시프트된다(도 5의 블록(118)). 필터 벡터 프로세싱 연산(102)이 완료할 때까지 이전의 결과적 필터 출력 벡터 데이터 샘플 세트와 누산될 중간 결과로서 다음 결과적 필터 출력 벡터 데이터 샘플 세트를 계산하기 위해 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))가 제공된다. 텁抨-지연 라인들(78(0), 78(1))에서 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 제공하기 위한 입력 벡터 데이터 샘플들(86)의 시프트는 도 7에 관하여 앞서 상세히 미리 설명되었다. 필터 벡터 프로세싱 연산(102)을 위해 실행 유닛들(84(0)-84(X))에 의해 제공되는 중간 결과들의 최종 누산은 도 4에 예시된 바와 같이, 실행 유닛들(84(0)-84(X))로부터의 결과적 필터 출력 벡터 데이터 샘플 세트(94(0)-94(X))로서 제공된다.

[0080] 도 9c는 입력 벡터 데이터 샘플 세트(86(0)-86(X))가 다음 필터 프로세싱 연산( $y[n] = x[n-6] * h6$ )을 위한 다음 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))가 되도록 필터 벡터 프로세싱 연산(102)의 제 2 프로세싱 스테이지에서 시프트될 때 텁抨-지연 라인들(78)의 컨텐츠를 예시한다. 1차 텁抨-지연 라인(78(0))에서 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))는 실행되는 벡터 명령에 의해 규정된 입력 벡터 데이터 샘플 시프트의 폭에 따라 1차 파이프라인 레지스터들(120(0)-120(4X+3))에서 시프트된다. 예컨대, 도 9c에 예시된 바와 같이, 시프트된 입력 벡터 데이터 샘플(86S(0))에서 샘플(X2)이 시프트된다. 필터 벡터 프로세싱 연산(102)의 다음 필터 텁에 대한 실행을 위해 새로운 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))가 실행 유닛들(84(0)-84(X))에 제공된다. 실행 유닛들(84(0)-84(X))에 제공되는 필터 계수(92)는 또한 다음 필터 계수(92)이기도 하며, 이는 이 예에서 "h6"이다.

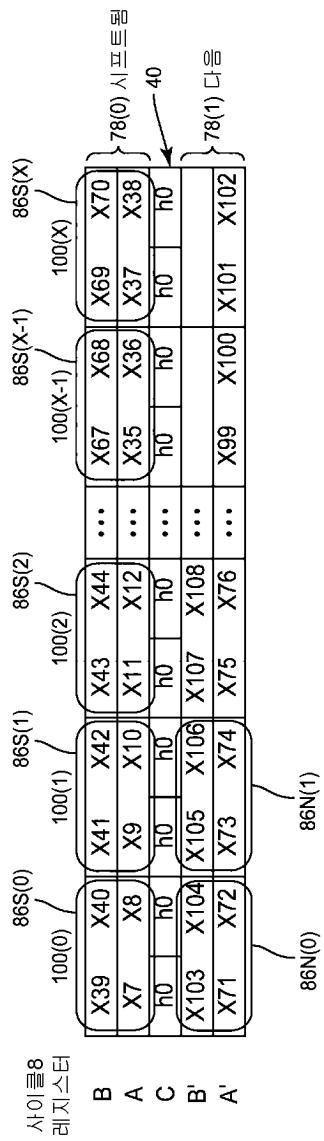

[0081] 도 5를 계속 참조하면, 다음 필터 계수(92)와 곱해지도록(도 5의 블록(110)) 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 1차 텁抨-지연 라인(78(0))으로부터 실행 유닛들(84(0)-84(X))로 제공(도 5의 블록(108))함으로써 프로세스가 반복된다. 결과적 필터 벡터 출력 벡터 데이터 샘플 세트(94(0)-94(X))가 이전의 결과적 필터 출력 벡터 데이터 샘플 세트(94(0)-94(X))와 누산된다(도 5의 블록(112)). 도 9d는 예시적인 필터 벡터 프로세싱 연산(102)의 마지막 프로세싱 스테이지 동안 텁抨-지연 라인들(78(0), 78(1))에 존재하는 입력 벡터 데이터 샘플들(86)의 상태를 예시한다. 도 9d에 도시된 바와 같이 이 예에서는, 필터 계수들(92)( $"h7" - "h0"$ )(즉, 92(0)-92(Y-1)) 때문에 필터 벡터 프로세싱 연산(102)에 8개의 필터 텁들(Y)이 있었다. "h0"은 도 9d에 도시된 바와 같이, 필터 벡터 프로세싱 연산(102)의 마지막 필터 계수(92)이다. 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))는, 필터 벡터 프로세싱 연산(102)에 대한 최종 8번째 프로세싱 스테이지에서 입력 벡터 데이터 샘플(X(39))이 1차 텁抨-지연 라인(78(0))의 시프트된 입력 벡터 데이터 샘플(86S(0))에 저장되도록 (필터 텁들의 수보다 1회 더 적은) 7회 시프트된다.

[0082] 앞서 설명한 필터 벡터 프로세싱 연산(102)의 예는 VPE(22(1))의 벡터 데이터 레인들(100(0)-100(X)) 각각을 이용하여 필터 벡터 프로세싱 연산(102)을 제공하지만, 이것이 필수적이진 않다는 점에 주목한다. 필터 벡터 프로세싱 연산(102)은 단지 벡터 데이터 레인들(100(0)-100(X))의 서브세트만이 필터 벡터 프로세싱 연산(102)에 이용될 것을 요구할 수도 있다. 예컨대, 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 폭은 모든 벡터 데이터 파일들(82(0)-82(X))의 폭 미만일 수도 있으며, 여기서는 필터 벡터 프로세싱 연산(102)과 동시에 수행될 다른

벡터 프로세싱 연산들을 위한 추가 벡터 데이터 레인들(100)을 이용하는 것이 바람직하다. 이 시나리오에서, 도 7의 텁핑-지연 라인들(78(0), 78(1))은 최종 벡터 데이터 레인(100(X))에 도달하기 전에 벡터 데이터 레인(100)에서 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))로서 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))를 새도록 텁핑-지연 라인(78(1))에서 1차 텁핑-지연 라인(78(0))으로 시프트하도록 수정될 필요가 있을 수도 있다.

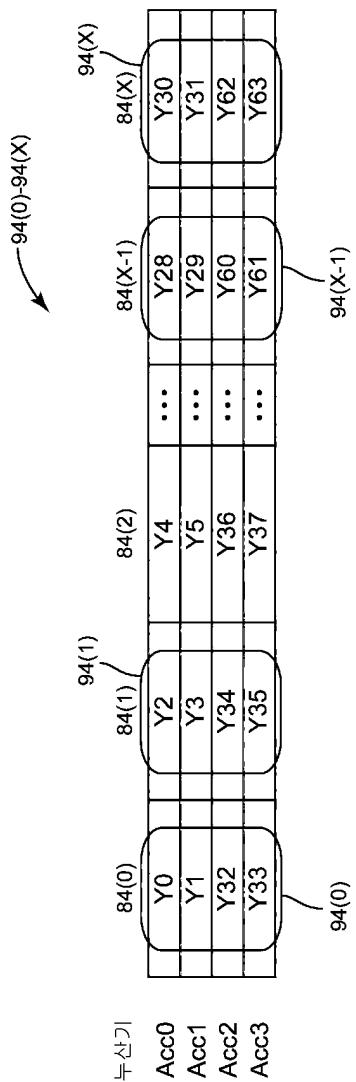

[0083] 도 10은 위의 예에서 예시적인 8개의 텁 필터 벡터 프로세싱 스테이지들이  $y[n] = x[n]*h_0 + x[n-1]*h_1 + \dots + x[n-7]*h_7$ 에 따라 완전히 실행된 후, 도 4의 VPE(22(1))에서 실행 유닛들(84(0)-84(X))의 누산기들의 컨텐츠 (즉, 결과적 필터 출력 벡터 데이터 샘플들(94))의 개략도이다. 누산기들(Acc0-Acc3)은 도 10에 도시되는데, 이 예에서 각각의 실행 유닛(84(0)-84(X))이 각각의 벡터 데이터 레인(100(0)-100(X))에 대해 별별로 배치된 4개의 누산기들을 갖기 때문이다. 누산된 결과적 출력 벡터 데이터 샘플들은 추가 분석 및/또는 프로세싱을 위해 그 내부에 저장될 집합적인 결과적 필터 출력 벡터 데이터 샘플 세트(94(0)-94(X))로서 출력 데이터 흐름 경로들(98(0)-98(X)) 상에서 벡터 데이터 파일들(82(0)-82(X))로 제공될 수 있다. 특수 벡터 명령은 원하는 경우, 벡터 데이터 파일들(82(0)-82(X))로부터 도 2의 벡터 유닛 메모리(32)로 결과적 필터 출력 벡터 데이터 샘플 세트(94(0)-94(X))의 행들을 이동시키도록 VPE(22(1))에 의해 지원될 수 있다.

[0084] 필터 벡터 프로세싱 연산(102) 이외의 다른 타입들의 벡터 프로세싱 연산들이 또한 위에서 논의된 도 4의 VPE(22(1))에서 제공된 것과 같은 또는 비슷한 텁핑-지연 라인들(78)의 사용에 의해 VPE에서 프로세싱 효율들을 누릴 수 있다. 예컨대, VPE에서 입력 벡터 데이터 샘플 세트들(86)의 시프트를 수반하는 다른 특수 벡터 프로세싱 연산은 (본 명세서에서는 "상관 벡터 프로세싱 연산"으로 지칭되는) 상관/공분산 벡터 프로세싱 연산이다. 일례로, CDMA 시스템에서 사용자 신호와 다른 사용자들의 신호들 간의 양호한 분리를 제공하기 위해 CDMA 시스템에서 사용자 신호를 복조하기 위한 DSSC(direct spread-spectrum code)(즉, 칩 시퀀스)를 선택하기 위한 상관 연산들을 제공하기 위해 벡터 프로세싱을 이용하는 것이 바람직할 수도 있다. 신호들의 분리는 원하는 사용자의 국소적으로 생성된 칩 시퀀스와 수신된 신호를 상관시킴으로써 이루어진다. 신호가 원하는 사용자의 칩 시퀀스와 매칭한다면, 상관 함수는 높을 것이고 CDMA 시스템은 그 신호를 추출할 수 있다. 원하는 사용자의 칩 시퀀스가 그 신호와 거의 또는 전혀 공통점이 없다면, 상관은 가능한 한 0에 가까워야 하는데(따라서 신호를 제거해야 하는데), 이는 상호-상관으로 지칭된다. 칩 시퀀스가 0이 아닌 임의의 시간 오프셋으로 신호와 상관된다면, 상관은 가능한 0에 가까워야 한다. 이는 자기-상관으로 지칭되며, 다중-경로 간섭을 거부하는 데 사용된다.

[0085] 그러나, 상관 연산들은 벡터 프로세서들에서 제공되는 특수화된 데이터 흐름 경로들로 인해 벡터 프로세서들에서 병렬화하기에 어려울 수 있다. 상관될 신호를 나타내는 입력 벡터 데이터 샘플 세트가 지연 텁들 사이에서 시프트될 때, 입력 벡터 데이터 샘플 세트는 벡터 데이터 파일로부터 재패치되고, 따라서 전력 소비를 증가시키고 스루풋을 감소시킨다. 메모리로부터 입력 벡터 데이터 샘플 세트의 재패치를 최소화하기 위해, 데이터 흐름 경로는 효율적인 병렬화된 프로세싱을 위해 지연 텁들과 동일한 수의 곱셈기들을 제공하도록 구성될 수 있다. 그러나, 다른 벡터 프로세싱 연산들은 더 적은 곱셈기들을 요구할 수 있고, 이로써 데이터 흐름 경로에서 곱셈기들의 비효율적인 스케일링 및 낮은 활용을 제공한다. 곱셈기들의 수가 확장성을 제공하기 위한 지연 텁들의 수 미만으로 감소되면, 병렬화는 상관 프로세싱의 상이한 단계들에 대한 동일한 입력 벡터 데이터 샘플 세트를 획득하기 위해 메모리에 요구되는 더 많은 재패치들에 의해 제한된다.

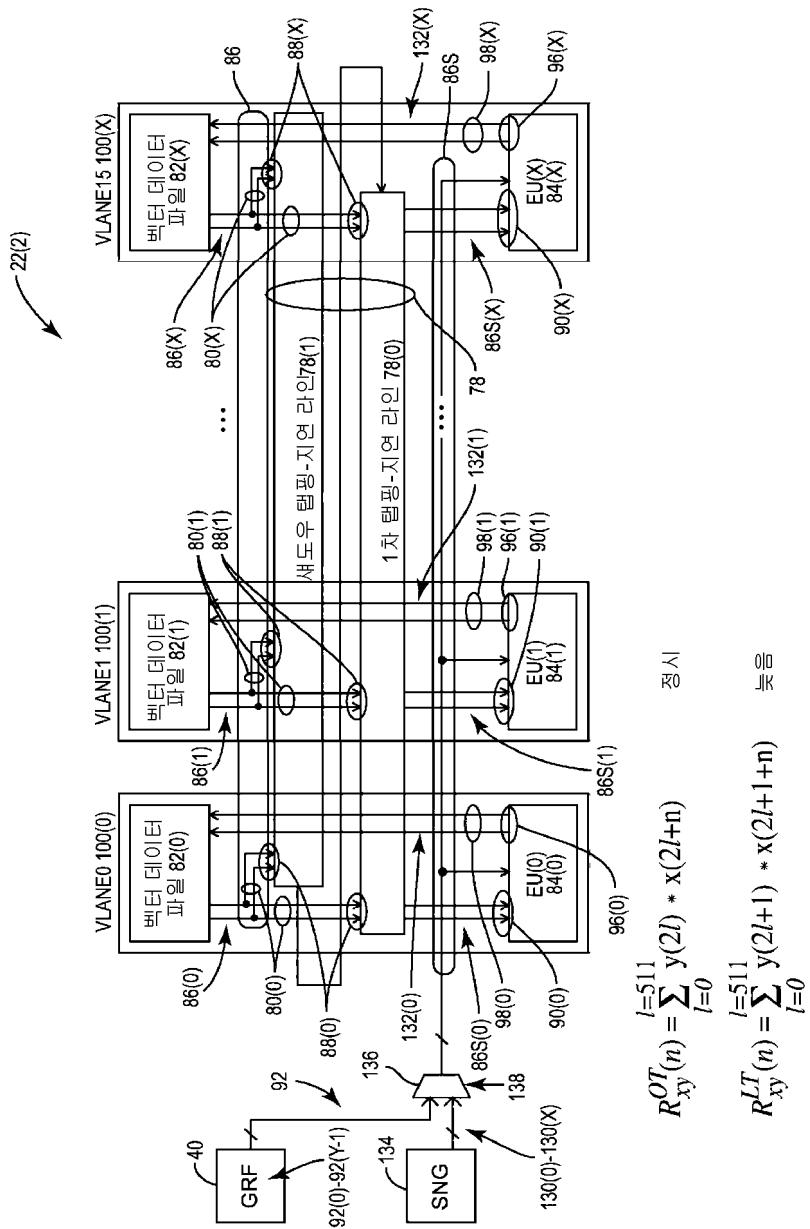

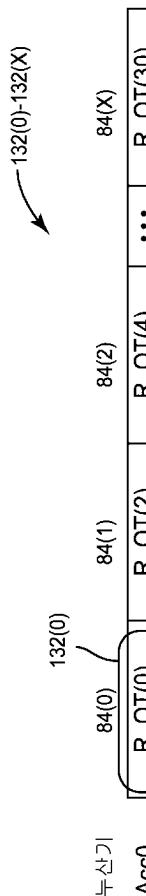

[0086] 이와 관련하여, 도 11은 도 2의 VPE(22)로서 제공될 수 있는 다른 예시적인 VPE(22(2))의 개략도이다. 아래에 더 상세히 설명될 바와 같이, 도 11의 VPE(22(2))는 벡터 데이터 샘플 재패치가 제거 또는 감소되고 전력 소비가 감소된, VPE(22(2)) 내의 정밀 상관 벡터 프로세싱 연산들을 제공하도록 구성된다. 벡터 데이터 샘플 재패치를 요구하는 중간 결과들의 저장을 요구하고 이로써 결과적으로 전력 소비를 증가시키는 상관 벡터 프로세싱 연산들과 비교하여 VPE(22(2))에서 정밀 상관 벡터 프로세싱 연산들이 제공될 수 있다. 전력 소비를 감소시키고 프로세싱 효율을 개선하기 위해 벡터 데이터 파일로부터 입력 벡터 데이터 샘플들의 재패치를 제거 또는 최소화하기 위해, 도 4의 VPE(22(1))에 포함된 텁핑-지연 라인들(78)이 또한 VPE(22(2)) 내의 실행 유닛들(84(0)-84(X))("EU"로 또한 라벨링됨)과 벡터 데이터 파일들(82(0)-82(X)) 사이의 입력 데이터 흐름 경로들(80(0)-80(X))에 포함된다. 'X'+1은 이러한 예에서 벡터 데이터 샘플들의 프로세싱을 위해 VPE(22(2))에 제공되는 병렬 입력 데이터 레인들의 최대 수이다. 위에서 이전에 논의된 바와 같이, 텁핑-지연 라인들(78)은 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 입력 벡터 데이터 샘플들(86)의 서브세트 또는 전부로서 텁핑-지연 라인 입력들(88(0)-88(X)) 상에서 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 벡터 데이터 파일들(82(0)-82(X))의 대응하는 서브세트 또는 전부로부터 수신하도록 구성된다. 입력 벡터 데이터 샘플들(86) 모두는 입력 벡터 데이터

샘플 세트(86(0)-86(X))를 포함한다. 아래에 더 상세히 논의될 바와 같이, 벡터 데이터 파일들(82(0)-82(X))로부터의 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 결과적 상관된 출력 벡터 데이터 샘플 세트(132(0)-132(X))를 제공하기 위해 VPE(22(2))에서 기준 벡터 데이터 샘플 세트(130(0)-130(X))와 상관된다. 기준 벡터 데이터 샘플 세트(130(0)-130(X))는, 이러한 예에서 130(0), 130(1), ..., 및 130(X)인 'X+1' 기준 벡터 데이터 샘플들(130)에 포함된다. 결과적 상관된 출력 벡터 데이터 샘플 세트(132(0)-132(X))는 이러한 예에서 132(0), 132(1), ..., 및 132(X)인 'X+1' 결과적 상관된 출력 벡터 데이터 샘플(132)에 포함된다.

[0087] 도 11을 계속해서 참조하면, 텁抨-지연 라인들(78)은 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 제공하기 위해 VPE(22(2))에 의해 실행될 상관 벡터 명령에 따라 상관 벡터 프로세싱 연산의 각각의 상관 지연 텁(즉, 상관 프로세싱 스테이지)에 대한 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 시프트한다. 시프트된 입력 벡터 데이터 샘플들(86S) 전부는 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 포함한다. 텁抨-지연 라인들(78)은 상관 벡터 프로세싱 동작 동안에 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 실행 유닛들(84(0)-84(X))의 실행 유닛 입력들(90(0)-90(X))에 제공하기 위해 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 시프트한다. 이러한 방식으로, 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))에 대해 수행되는 연산들에 기초한 중간 상관 결과들은 VPE(22(2))에 의해 수행되는 상관 벡터 프로세싱 연산의 각각의 프로세싱 스테이지 동안에 저장, 시프트되고, 벡터 데이터 파일들(82(0)-82(X))로부터 재폐치되지 않아도 된다. 따라서, 텁抨-지연 라인들(78)은 전력 소비를 감소시키고, VPE(22(2))에 의해 수행되는 상관 벡터 프로세싱 연산들에 대한 프로세싱 효율을 증가시킬 수 있다.

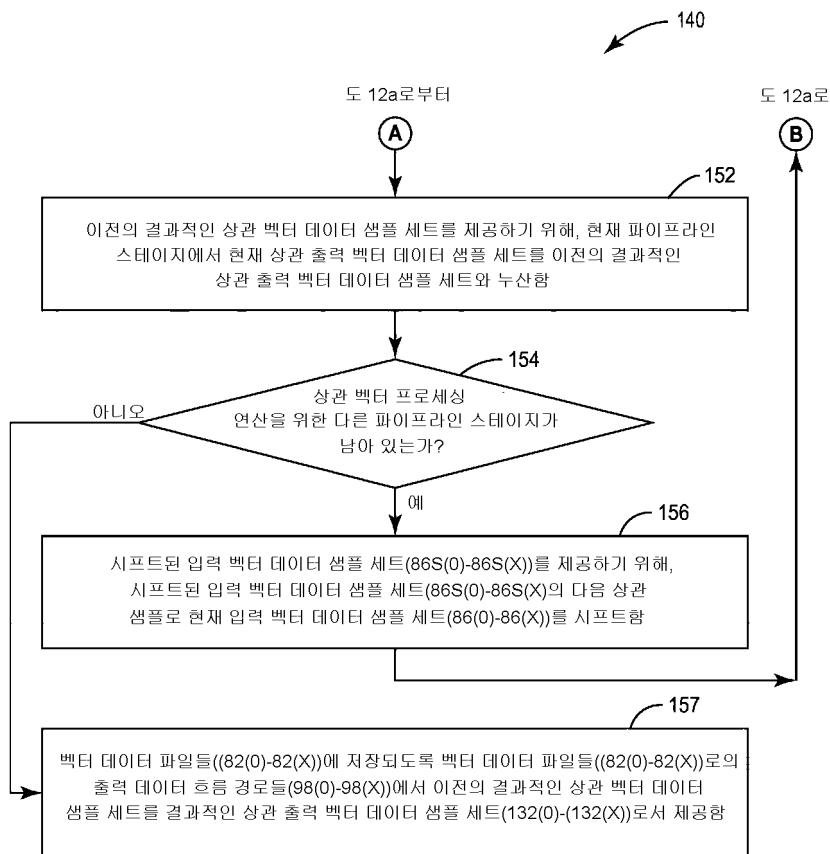

[0088] 도 11을 계속 참조하면, 실행 유닛들(84(0)-84(X))은 또한 상관 벡터 프로세싱 동작을 위해 SNG(sequence number generator)(134)에 저장된 기준 벡터 데이터 샘플 세트(130(0)-130(X)) 사이로부터 기준 벡터 데이터 샘플(130)을 수신한다. 실행 유닛들(84(0)-84(X))은 상관 벡터 프로세싱 동작의 부분으로서 입력 벡터 데이터 샘플 세트(86(0)-86(X))와 기준 벡터 데이터 샘플 세트(130(0)-130(X))를 상관시키도록 구성된다. 그러나, 시퀀스 번호 생성기(134)는 또한 레지스터 또는 다른 파일일 수 있다는 것을 주목하라. 기준 벡터 데이터 샘플 세트(130(0)-130(X))를 제공하기 위해 시퀀스 번호 생성기(134)가 이러한 실시예에 제공되는데, 왜냐하면 상관 벡터 프로세싱 동작이 이러한 예에서 CDMA 상관 벡터 명령에 대한 것이기 때문이다. 기준 벡터 데이터 샘플 세트(130(0)-130(X))는, 기준 벡터 데이터 샘플 세트(130(0)-130(X))와 입력 벡터 데이터 샘플 세트(86(0)-86(X)) 사이의 상관이 높은 경우에, 입력 벡터 데이터 샘플 세트(86(0)-86(X))로부터의 신호 추출에서 사용하기 위한 생성된 칩 시퀀스로서 제공된다.

[0089] 예컨대, CDMA 벡터 상관 명령에 대한 상관 벡터 프로세싱 동작은 입력 벡터 데이터 샘플 세트(86(0)-86(X)) 내의 정시 입력 벡터 데이터 샘플들(86)과 입력 벡터 데이터 샘플 세트(86(0)-86(X)) 내의 늦은 입력 벡터 데이터 샘플들 사이의 상관을 제공할 수 있다. 예컨대, 입력 벡터 데이터 샘플 세트(86(0)-86(X)) 내의 정시 입력 벡터 데이터 샘플들(86)은 입력 벡터 데이터 샘플 세트(86(0)-86(X)) 내의 짹수 입력 벡터 데이터 샘플들(86)(예컨대, 86(0), 86(2), 86(4), ..., 86(X-1))일 수 있다. 입력 벡터 데이터 샘플 세트(86(0)-86(X)) 내의 늦은 입력 벡터 데이터 샘플들(86)은 입력 벡터 데이터 샘플 세트(86(0)-86(X)) 내의 홀수 입력 벡터 데이터 샘플들(86)(예컨대, 86(1), 86(3), 86(5), ..., 86(X))일 수 있다. 대안적으로, 정시 입력 벡터 데이터 샘플들(86)은 홀수 입력 벡터 데이터 샘플들(86)일 수 있고, 늦은 입력 벡터 데이터 샘플들(86)은 짹수 입력 벡터 데이터 샘플들(86)일 수 있다. 상관 벡터 프로세싱 동작의 결과들, 정시 입력 벡터 데이터 샘플들(86) 및 늦은 입력 벡터 데이터 샘플들(86)에 대한 결과적 상관된 출력 벡터 데이터 샘플 세트(132(0)-132(X))는 신호 추출을 위해 입력 벡터 데이터 샘플 세트(86(0)-86(X))로부터 정시 또는 늦은 입력 벡터 데이터 샘플들을 사용할지를 결정하는데 사용될 수 있다. 예컨대, 정시 상관 벡터 프로세싱 연산은 다음에 따라 제공될 수 있다.

$$R_{xy}^{OT}[n] = \sum_{l=0}^{l=511} y[2l]^* x[2l+n], \text{ 여기서}$$

[0090] n은 입력 신호 샘플들의 수이고,

[0091] x[n]은 디지털화된 입력 신호(66)이고,

[0092] y[n]은 기준 신호이고,

[0093] l은 샘플 수이다.

[0095] 늦은 상관 벡터 프로세싱 동작은 다음에 따라 제공될 수 있다.

$$R_y^{LT}[n] = \sum_{l=0}^{l=511} y[2l+1]*x[2l+1+n]$$

[0096] 여기서, n은 입력 신호 샘플들의 수이고,

[0097] x[n]은 디지털화된 입력 신호(66)이고,

[0098] y[n]은 기준 신호이고,

[0100] 1은 샘플 수이다.

[0101] 기준 신호 y[n](즉, 기준 벡터 데이터 샘플들)은 복소수일 수 있다. 일 양상에서, VPE(22(2))는 (예전대, 시퀀스 번호 생성기(134)로부터) 기준 신호를 수신할 수 있다. VPE(22(2))는 정시 및 늦은 상관 연산들을 수행하기 위해 수신된 기준 신호를 직접적으로 사용할 수 있고, 이러한 경우에 위의 수학식들에서 기준 신호 y[n]은 수신된 기준 신호를 나타낼 수 있다. 대안적으로, VPE(22(2))는 정시 및 늦은 상관 연산들을 수행하기 위해 기준 신호를 사용하기 전에 수신된 기준 신호의 복소 공액을 계산할 수 있고, 이러한 경우에 위의 수학식들 내의 기준 신호 y[n]는 수신된 기준 신호의 공액들을 나타낼 수 있다.

[0102] 도 11을 계속 참조하면, 실행 유닛들(84(0)-84(X)) 각각은, 실행 유닛들(84(0)-84(X))에서 중간 상관 출력 벡터 데이터 샘플들을 제공하기 위해 상관 벡터 프로세싱 연산의 각각의 프로세싱 스테이지 동안에 기준 벡터 데이터 샘플 세트(130(0)-130(X))와 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))의 시프트된 입력 벡터 데이터 샘플들(86S(0), 86S(1), ..., 86S(X))을 곱셈하도록 구성된다. 중간 상관 출력 벡터 데이터 샘플 세트들은 실행 유닛들(84(0)-84(X)) 각각에서 누산된다(즉, 이전의 누산된 상관 출력 벡터 데이터 샘플이 현재 상관 출력 벡터 데이터 샘플에 부가됨). 이것은, 실행 유닛들(84(0)-84(X))에 의해 생성된 중간 상관 벡터 데이터 출력 샘플 세트들을 저장 및 시프트하지 않고서, VPE(22(2))에 의한 추가의 사용 및/또는 프로세싱을 위해 각각의 벡터 데이터 파일들(82(0)-82(X))에 다시 저장될 각각의 입력 벡터 데이터 샘플 세트(86(0), 86(1), ..., 86(X))에 대해, 출력 데이터 흐름 경로들(98(0)-98(X)) 상의 실행 유닛 출력들(96(0)-96(X)) 상에서 실행 유닛들(84(0)-84(X))에 의해 각각 제공되는 마지막, 결과적 상관된 출력 벡터 데이터 샘플 세트(132(0)-132(X))를 제공한다.

[0103] 또한, 도 11의 VPE(22(2))에 제공된 동일한 컴포넌트들 및 아키텍처가 도 4의 VPE(22(1))에 제공된다는 것을 주목하라. 시퀀스 번호 생성기(134)가 부가되어, 기준 벡터 데이터 샘플 세트(130(0)-130(X))와 프로세싱될 필터 계수들(92(0)-92(Y-1)) 또는 다른 데이터를 제공할 수 있는 글로벌 레지스터 파일(40)과 멀티플렉서(136)에 의해 멀티플렉싱된다. 따라서, 도 11의 VPE(22(2))는 멀티플렉서(136)의 제어에 의해 여기서 그리고 아래에 더 상세히 논의되는 상술된 필터 벡터 프로세싱 연산들 및 상관 벡터 프로세싱 연산들 둘 모두를 제공할 수 있다. 멀티플렉서(136)는 VPE(22(2))에 의해 실행될 벡터 명령에 기초하여 제어되는 선택기 신호(138)에 의해 제어될 수 있다. 필터 벡터 명령에 대해, 선택기 신호(138)는 실행 유닛들(84(0)-84(X))에 제공될 글로벌 레지스터 파일(40)로부터 필터 계수들(92(0)-92(Y-1))을 제공하도록 구성될 수 있다. 상관 벡터 명령에 대해, 선택기 신호(138)는 실행 유닛들(84(0)-84(X))에 제공될 시퀀스 번호 생성기(134)로부터 기준 벡터 데이터 샘플 세트(130(0)-130(X))를 선택하도록 구성될 수 있다.

[0104] 도 11을 계속 참조하여 그리고 아래에 더 상세히 논의될 바와 같이, 탭핑-지연 라인들(78(0), 78(1))은 프로세싱되는 벡터 명령에 따라 제어되도록 프로그램 가능하다. 탭핑-지연 라인들(78)을 사용하지 않는 상관 벡터 명령 또는 다른 명령이 프로세싱되지 않는다면, 탭핑-지연 라인들(78)은 벡터 데이터 파일들(82(0)-82(X))과 실행 유닛들(84(0)-84(X)) 사이의 입력 데이터 흐름 경로들(80(0)-80(X))에 포함되지 않도록 프로그램될 수 있다. 이러한 실시예에서, 이전에 논의된 바와 같이, 2 개의 탭핑-지연 라인들(78), 1차 탭핑-지연 라인들(78(0)) 및 새도우 탭핑-지연 라인들(78(1))이 제공되고, 새도우 탭핑-지연 라인들(78(1))은 이러한 실시예에서 선택적이다. 이전에 논의된 바와 같이, 탭핑-지연 라인들(78) 없이, 시프트된 중간 입력 벡터 데이터 샘플 세트를 다시 실행 유닛들(84(0)-84(X))에 제공하기 위해 별개의 시프팅 프로세스가 수행되어야 할 것이고, 이로써 레이턴시를 증가시키고, 부가적인 전력을 소비한다. 또한, VPE(22(2)) 내의 입력 및 출력 데이터 흐름 경로들(80(0)-80(X), 98(0)-98(X))의 효율은 상관 벡터 프로세싱 연산 동안에 벡터 데이터 파일들(82(0)-82(X))로부터의 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))의 재배치 지연에 의해 제한되지 않는다. 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))는 실행 유닛들(84(0)-84(X))에 로컬화된 탭핑-지연 라인들(78)에

의해 제공된다. 실행 유닛들(84(0)-84(X)) 내의 벡터 프로세싱은 데이터 흐름 제한들보다는 계산적인 자원들에 의해서만 제한된다.

[0105] 또한, 도 11의 VPE(22(2))에 의해 수행되는 상관 벡터 프로세싱 연산들은 텁핑-지연 라인들(78)을 사용함으로써 더 정밀하게 이루어질 수 있는데, 왜냐하면 실행 유닛들(84(0)-84(X))에서 중간 상관 프로세싱 스테이지들에 대한 출력 누산들이 벡터 데이터 파일들(82(0)-82(X))에 저장될 필요가 없기 때문이다. 실행 유닛들(84(0)-84(X))로부터의 중간 벡터 데이터 샘플 세트들의 벡터 데이터 파일들(82(0)-82(X)) 내의 저장은 라운딩을 발생시킬 수 있다. 따라서, 다음 중간 출력 벡터 데이터 샘플 세트가 벡터 프로세싱 연산을 위해 실행 유닛들(84(0)-84(X))에 제공될 때, 임의의 라운딩 에러가 벡터 프로세싱 연산의 각각의 곱셈 단계 동안에 전파 및 부가될 것이다. 이와 반대로, 도 11의 VPE(22(2))의 예에서, 실행 유닛들(84(0)-84(X))에 의해 계산된 중간 상관 출력 벡터 데이터 샘플 세트들은 벡터 데이터 파일들(82(0)-82(X))에 저장될 필요가 없다. 이전의 중간 상관 출력 벡터 데이터 샘플 세트들은 다음 상관 출력 벡터 데이터 샘플 세트들에 대해 중간 상관 출력 벡터 데이터 샘플 세트들과 누산될 수 있는데, 왜냐하면 텁핑-지연 라인들(78)이 프로세싱될 벡터 프로세싱 연산 동안에 시프트된 입력 벡터 데이터 샘플 세트들(86S(0)-86S(X))을 실행 유닛들(84(0)-84(X))에 제공하기 때문이고, 결과들은 이전의 상관 출력 벡터 데이터 샘플 세트들에 대해 이전의 벡터 데이터 샘플 세트들과 누산된다.

[0106] 위의 도 4의 VPE(22(1))에 제공된 컴포넌트들의 이전 논의는 도 11의 VPE(22(2))에 대해 동일하게 적용 가능하고, 따라서 다시 설명되지 않을 것이다.

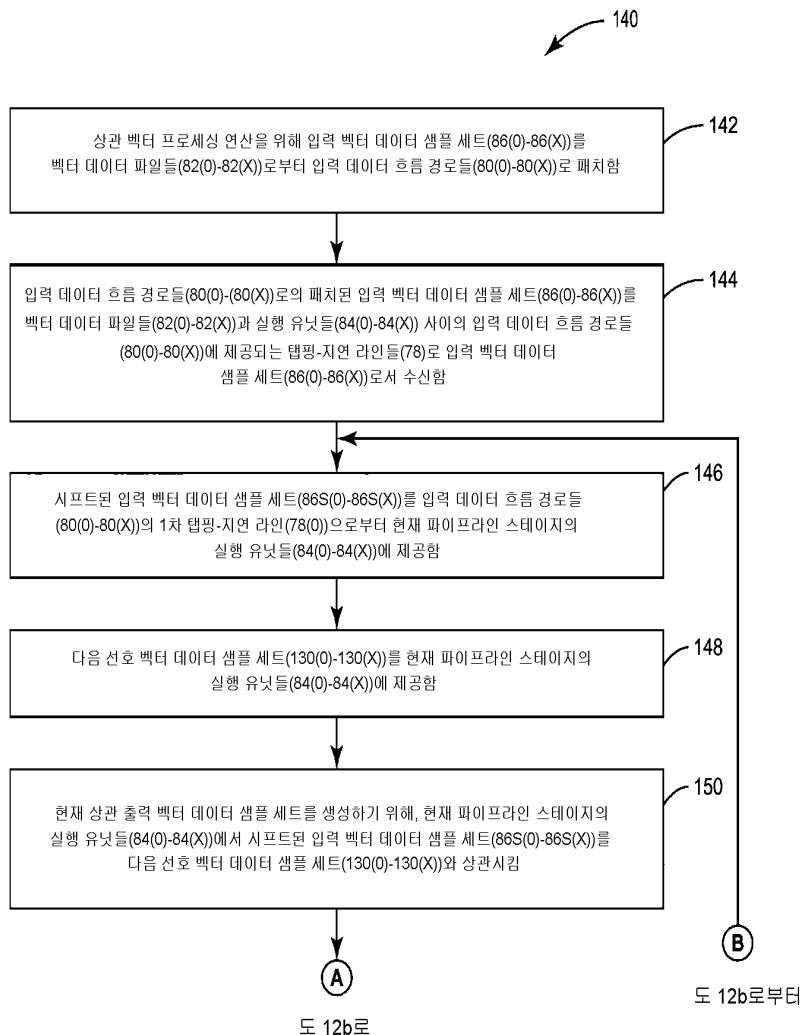

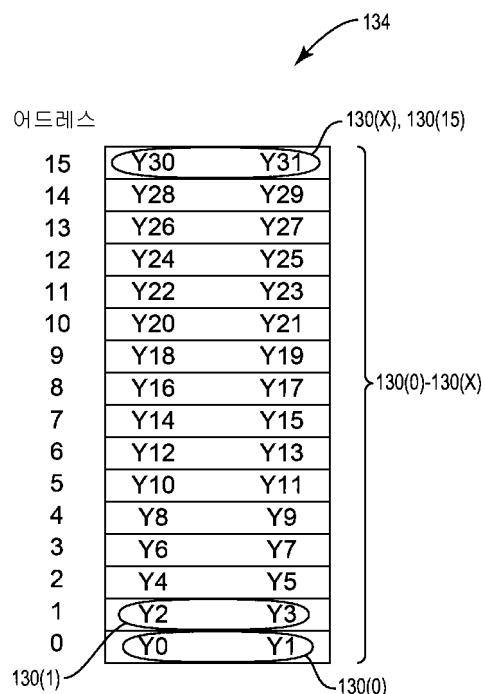

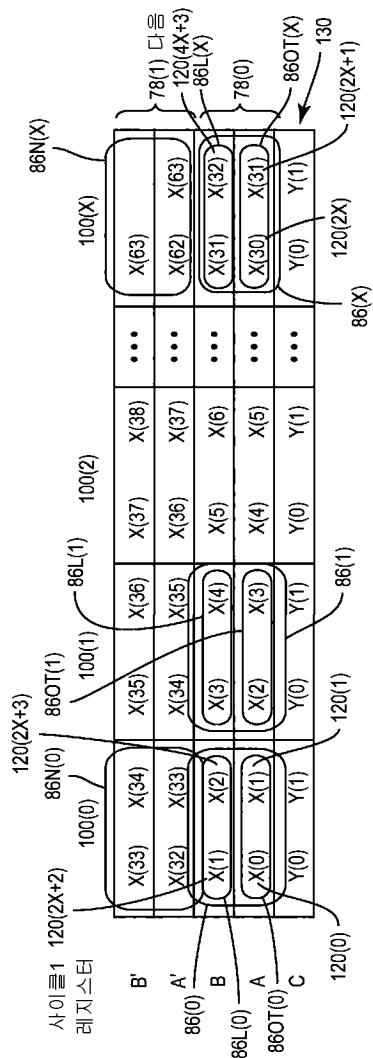

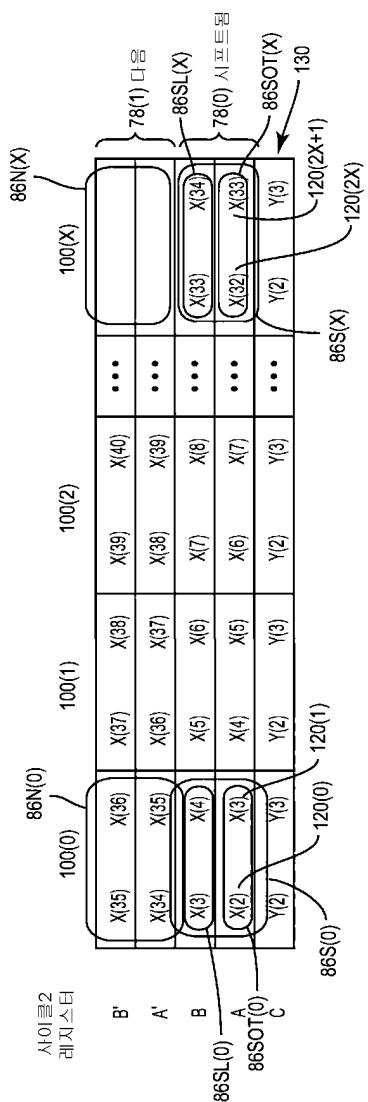

[0107] 이러한 실시예에서 입력 데이터 흐름 경로들(80(0)-80(X))에서 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 실행 유닛들(84(0)-84(X))에 제공하기 위한 텁핑-지연 라인들(78) 및 도 11의 VPE(22(2))의 부가적인 세부사항들 및 특징들의 추가의 설명이 이제 설명될 것이다. 이와 관련하여, 도 12a 및 12b는 예시적인 상관 벡터 명령에 따라 텁핑-지연 라인들(78)을 사용하는 도 11의 VPE(22(2))에서 수행될 수 있는 예시적인 상관 벡터 프로세싱 동작(140)을 예시한 흐름도들이다. 도 12a 및 12b는 예시적인 상관/공분산 벡터 프로세싱 연산에 따라 폐지된 인터리브된 정시 및 늦은 입력 벡터 데이터 샘플 세트들에 대해 도 11의 VPE(22(2))에서 동시에 수행될 수 있는 예시적인 상관/공분산 벡터 프로세싱 동작들을 예시한 흐름도들이다.

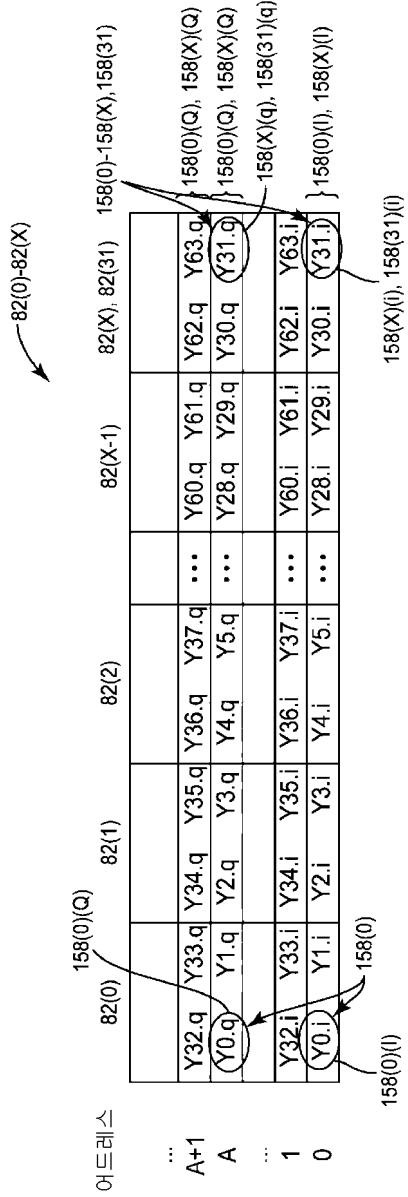

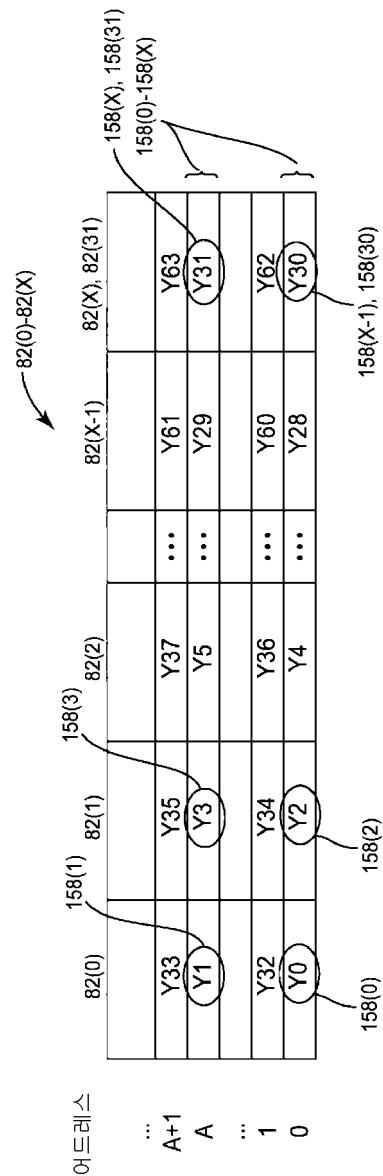

[0108] 도 12a 및 12b에서 상관 벡터 프로세싱 연산(140)에서 수행되는 예시적인 작업들은 도 13-17b에 제공된 예들을 참조하여 설명될 것이다. 도 12a를 참조하면, 상관 벡터 명령에 따라 상관 벡터 프로세싱 연산(140)에서 프로세싱될 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 상관 벡터 프로세싱 연산(140)을 위해 벡터 데이터 파일들(82(0)-82(X))로부터 입력 데이터 흐름 경로들(80(0)-80(X))로 폐지된다(블록 142). 도 11의 VPE(22(2))에 관련하여 앞서 논의된 바와 같이, 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 실행 유닛들(84(0)-84(X)) 내의 시퀀스 번호 생성기(134)로부터 수신된 기준 벡터 데이터 샘플 세트(130(0)-130(X))에 의해 곱셈된다. 예컨대, 도 13은 시퀀스 번호 생성기(134) 내의 기준 벡터 데이터 샘플 세트(130(0)-130(X))를 예시한다. 이러한 예에서, 입력 벡터 데이터 샘플 세트(86(0)-86(X)) 내의 열여섯개(16)의 입력 벡터 데이터 샘플들(86(0), 86(1), ..., 86(15))과 상관될 글로벌 레지스터 파일(40)에 저장된 열 여섯(16) 개의 기준 벡터 데이터 샘플들(130(0), 130(1), ..., 130(15))이 존재한다. 위에서 이전에 논의된 도 6b는 벡터 데이터 파일들(82(0)-82(X))에 저장된 예시적인 입력 벡터 데이터 샘플 세트(86(0)-86(X))를 예시하였고, 이것은 또한 이러한 예에서 적용 가능하고, 따라서 여기서 다시 설명되지 않을 것이다.

[0109] 도 11의 VPE(22(2)) 내의 벡터 데이터 레인들(100(0)-100(X)) 중 하나, 일부 또는 전부는 상관 벡터 프로세싱 연산(140)에서 상관될 기준 벡터 데이터 샘플 세트(130(0)-130(X)) 및 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 폭에 의존하는 벡터 명령의 프로그래밍에 따라 상관 벡터 프로세싱 연산(140)을 제공하도록 사용될 수 있다. 벡터 데이터 파일들(82(0)-82(X))의 전체 폭이 요구되면, 모든 벡터 데이터 레인들(100(0)-100(X))은 상관 벡터 프로세싱 연산(140)을 위해 사용될 수 있다. 상관 벡터 프로세싱 연산(140)이 상관 벡터 프로세싱 연산(140)을 위해 사용될 수 있는 벡터 데이터 레인들(100(0)-100(X))의 서브세트만을 요구할 수 있다는 것을 주목하라. 이것은, 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 폭이 모든 벡터 데이터 파일들(82(0)-82(X))의 폭 미만이기 때문일 수 있고, 여기서 다른 벡터 프로세싱 연산들이 상관 벡터 프로세싱 연산(140)과 동시에 수행되도록 부가적인 벡터 데이터 레인들(100)을 사용하는 것이 바람직하다. 현재 예를 논의할 목적으로, 상관 벡터 프로세싱 연산(140)에서 사용되는 입력 벡터 데이터 샘플 세트(86(0)-86(X)) 및 기준 벡터 데이터 샘플 세트(130(0)-130(X))가 VPE(22(2))에서 모든 벡터 데이터 레인들(100(0)-100(X))을 수반한다고 가정된다.

[0110] 도 12a를 다시 참조하면, 폐지된 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 상관 벡터 프로세싱 연산(140)을 위한 제 1 입력 벡터 데이터 샘플 세트(86S(0)-86(X))로서 텁핑 지연 라인들(78)로 로딩되도록 벡터 데이터 파일

일들(82(0)-82(X))로부터의 입력 데이터 흐름 경로들(80(0)-80(X))에 제공된다(블록 144). 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 상관 벡터 프로세싱 연산(140)을 위해 실행 유닛들(84(0)-84(X))에 의해 프로세싱될 입력 벡터 데이터 샘플 세트(86(0)-86(X))로서 1차 텁핑 지연 라인(78(0))으로 로딩된다. 1차 텁핑 지연 라인(78(0))으로 로딩되는 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 상관 벡터 프로세싱 연산(140)의 제 1 연산을 위해 시프트되지 않는다. 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))는 또한 실행 유닛들(84(0)-84(X))에 의해 프로세싱될 다음 입력 벡터 데이터 샘플 세트(86N(0)-86N(X))로서 새도우 텁핑 지연 라인(78(1))으로 로딩될 수 있다. 위에서 이전에 논의되고 아래에 더 상세히 논의되는 바와 같이, 텁핑 지연 라인들(78)의 목적은 상관 벡터 프로세싱 연산(140)의 연산 동안에 후속 상관 연산들을 위해 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 실행 유닛들(84(0)-84(X))에 제공하기 위해 입력 벡터 데이터 샘플 세트(86(0)-86(X))의 시프팅을 제공하는 것이다. 실행 유닛들(84(0)-84(X))에 의해 실행되는 상관 벡터 프로세싱 연산(140)의 각각의 프로세싱 스테이지 동안에, 입력 벡터 데이터 샘플들(86)은 시프트된 입력 벡터 데이터 샘플 세트(86S(0)-86S(X))를 실행 유닛들(84(0)-84(X))에 제공하기 위해 1차 텁핑 지연 라인(78(0))에서 시프트된다. 이러한 방식으로, 입력 벡터 데이터 샘플 세트(86(0)-86(X))는 벡터 데이터 파일들(82(0)-82(X))에서 저장, 시프트되고 상관 벡터 프로세싱 연산(140)의 각각의 상관 연산을 위해 재패치되지 않아도 된다.