# (19) **日本国特許庁(JP)**

# (12) 公 表 特 許 公 報(A)

(11)特許出願公表番号

特表2004-538536 (P2004-538536A)

(43) 公表日 平成16年12月24日 (2004. 12. 24)

(51) Int.C1.7

FI

テーマコード (参考)

GO6F 12/12 GO6F 12/08

GO6F 12/12 503 GO6F 12/12

5B005

551 GO6F 12/08 507G

#### 審查請求 未請求 予備審查請求 有 (全 27 頁)

(21) 出願番号 特願2001-550561 (P2001-550561) (86) (22) 出願日 平成12年11月27日 (2000.11.27) (85) 翻訳文提出日 平成14年6月28日 (2002.6.28) (86) 国際出願番号 PCT/US2000/042305 (87) 国際公開番号 W02001/050269 (87) 国際公開日 平成13年7月12日 (2001.7.12)

(31) 優先権主張番号 09/476,444

(32) 優先日 平成11年12月30日 (1999.12.30)

(33) 優先権主張国 米国(US) (71) 出願人 591003943

インテル・コーポレーション

アメリカ合衆国 95052 カリフォル ニア州・サンタクララ・ミッション カレ

ッジ ブーレバード・2200

(74)代理人 100091915

弁理士 本城 雅則

(74) 代理人 100099106

弁理士 本城 吉子

(72) 発明者 クラーク、ローレンス・ティー

アメリカ合衆国 アリゾナ州 85048 フェニックス イースト・デザート・ウ

ィロー・ロード3161

最終頁に続く

(54) 【発明の名称】ラウンド・ロビンおよびロッキング・キャッシュの置換法を実行する方法および装置

# (57)【要約】

本発明は、キャッシュ置換法に関するものである。第1 の複数のレジスタは、特定のキャッシュ・ラインと関連 して互いにデイジー・チェイン状に結合される。同様に 、第2の複数のレジスタが特定のキャッシュ・ラインと 関連して互いにデイジー・チェイン状に結合される。第 1のデイジー・チェインは、キャッシュ・ラインのフィ ル命令(fill order)を定義し、また第2の デイジー・チェインは、キャッシュ・ラインのロック命 令(lock order)を定義する。

### 【特許請求の範囲】

### 【請求項1】

第1シフト・レジスタと共に結合された第1の複数のラッチであって、前記第1の複数の ラッチの各々はキャッシュのラインと関連付けられ、前記レジスタは前記キャッシュのラ インに対しフィル命令を定義する、第1の複数のラッチと、

第2シフト・レジスタと共に結合された第2の複数のラッチであって、前記第2の複数の ラッチの各々はキャッシュ・ラインと関連付けられ、前記レジスタは前記キャッシュのラ インに対しロック命令を定義する、第2の複数のラッチと、

から構成されることを特徴とする装置。

# 【請求項2】

前記第1の複数のラッチの第1開始レジスタの出力を増幅し、前記第1の複数のラッチにおける他の各レジスタに対する入力を駆動するバッファをさらに含むことを特徴とする請求項1記載の装置。

# 【請求項3】

前記第1の複数のラッチにおける他の各レジスタは前記複数のラッチにおけるその後続に 対する入力を駆動することを特徴とする請求項2記載の装置。

### 【請求項4】

前記第1の複数のラッチおよび前記第2の複数のラッチは、数において異なっていることを特徴とする請求項1記載の装置。

### 【請求項5】

前記第1の複数のラッチの第1開始レジスタは、キャッシュ・ラインと関連付けられ、第 2キャッシュ・ラインのアドレスと最大の差異を有するアドレスは前記第2の複数のラッチの第2開始レジスタと関連付けられることを特徴とする請求項1記載の装置。

### 【請求項6】

第 2 フィル・ラインが次のロック・ラインと同じ拡がりとなるように前記第 1 および第 2 の複数のラッチを結合する結合論理をさらに含むことを特徴とする請求項 5 記載の装置。

## 【請求項7】

前記第1の複数のラッチの1つのラッチのみが3より大きいファンアウトを有することを 特徴とする請求項1記載の装置。

### 【請求項8】

前記キャッシュは、変換索引バッファ(translation lookaside buffer: TLB)であることを特徴とする請求項1記載の装置。

### 【請求項9】

ロックされるべきラインは、先行するロック・レジスタ・ビットにおける論理 1 と現在ビットの論理 0 との一致によって決定されること特徴とする請求項 1 記載の装置。

### 【請求項10】

前記第1シフト・レジスタは循環バッファとして構成されることを特徴とする請求項1記載の装置。

### 【請求項11】

前記第1シフト・レジスタにおける循環シフトの長さは、前記第2シフト・レジスタ中のビットを設定することにより決定されることを特徴とする請求項10記載の装置。

### 【請求項12】

各ラッチは、マスター・スレイブ・フリップフロップを含むことを特徴とする請求項 1 記載の装置。

### 【請求項13】

連想記憶装置のアレイ(CAM)と、

前記CAMに結合されたランダム・アクセス・メモリ (RAM)と、

前記CAMに結合され、前記RAM中の非ロック・ラインに対するラウンド・ロビン置換法を実行している間、前記CAMに前記RAMの特定のラインをロックさせる制御論理と

10

20

30

50

40

から構成されることを特徴とするシステム。

# 【請求項14】

前記制御論理は、

デイジー・チェイン状に共に結合された第1の複数のラッチであって、前記複数のラッチの各々は前記RAMのラインと関連付けられ、前記デイジー・チェインは前記RAMのラインに対しフィル命令を定義する、第1の複数のラッチと、

デイジー・チェイン状に共に結合された第2の複数のラッチであって、前記第2の複数の ラッチの各レジスタはキャッシュ・ラインと関連付けられ、前記デイジー・チェインは前 記キャッシュ・ラインに対しロック命令を定義する、第2の複数のラッチと、

から構成されることを特徴とする請求項13記載のシステム。

【請求項15】

ロック開始ラインを定義する段階と、

フィル開始ラインおよび前記ロック開始ラインからの距離を定義する段階と、

ロックが転送される時間毎にフィル・ポインタを前記フィル開始ラインにリセットする段階と、

から構成される方法。

【請求項16】

転送されるロック・ラインに応答して、ライン 1 を前記フィル開始ラインにより近くに表示するためにロック・インジケータを変更する段階をさらに含むことを特徴とする請求項 1 5 記載の方法。

【請求項17】

前記フィル開始ラインを第1フィルに満たす段階と、

前記ロック開始ラインに最も近い非ロック・ラインを第2フィルに満たす段階と、

から構成されることを特徴とする請求項15記載の方法。

【請求項18】

実行時に、デジタル処理システムを稼動させる実行可能なコンピュータ・プログラムの命 令を収容するコンピュータの読み取り可能な格納媒体において、

ロック・データをキャッシュ・ラインへ転送するキャッシュ内のロック・モードを初期化 する段階と、

前記キャッシュ・ラインをロックする段階と、

前記キャッシュをフィル・モードに戻す段階と、

から構成される方法。

【発明の詳細な説明】

【発明の属する技術分野】

本願発明は、キャッシュ置換法に関するものである。さらに詳しくは、本願発明は結合型 ラウンド・ロビン・キャッシュ置換およびキャッシュ・ラインのロッキング法に関するも のである。

【従来の技術】

新しいデータ・セットがキャッシュから転送される場合、どんなデータが置き換えられるかを定義する様々な方法が存在する。直接マップ法における1つの好ましい方法は、最低使用頻度(1east recently used:LRU)方式である。最低使用頻度方式では、その名前が暗示するように、最低の使用頻度であるデータのブロックがあらゆる入力データと置き換えられる。コンピュータ・ソフトウェアの実行およびデータの使用に共通した基準となる位置を占めるために、この方式はかなり効果的なキャッシュ置換法であるように思われた。しかしながら、セット・アソシエイティブ性(set associativity)が増大するにつれて、LRU方式に対する複雑さおよびオーバヘッドが、ハードウェア条件への強化要求となり、このような方式に対する魅力を減退させている。

さらに、別々のデコーダを具備しない連想記憶装置(content addressable memory)(CAM)ベースのキャッシュでは、高いセット・アソシエイテ

10

20

30

40

50

10

20

30

40

50

ィブ性が達成され、どこへフィル・データ(fill data)を書き込むべきかを識別することは極めて問題となってくる。使用されている1つの可能な解決法は、ラウンド・ロビン・キャッシュ置換法(round robin replacement scehme)であるが、循環シフト・レジスタが転送されるべきラインを識別するループを形成する。これは、最も古いデータをキャッシュに退避させる効果をもつが、その置換は使用頻度とは全く独立している。このように、それは極めて大量のキャッシュ・スラッシング(cache thrashing)の原因となる。

データがキャッシュから早まって追い出されるのを防止するいくつかの方法は、経路をロックするのを許容することであった。これらのシステムは、多くの細分性(granularity)を提供することができなかった。例えば、双方向キャッシュでは、たとえ保持されるべきデータのブロックが比較的小さくても、キャッシュの半分がロックされるであろう。これは、しばしば非効率なキャッシュの使用となる。

### 【発明の概要】

第1の複数のラッチが、レジスタを形成して互いにデイジー・チェイン(いもずる)状に結合され、各ラッチは特定のキャッシュ・ラインと結合される。同様に、第2の複数のラッチが、互いにデイジー・チェイン状に結合され、各ラッチはキャッシュ・ラインと結合される。第1レジスタはキャッシュ・ラインのフィル命令(fill order)を定義し、また第2レジスタはキャッシュ・ラインのロック命令(lock order)を定義する。

### 【好適な実施例の詳細な説明】

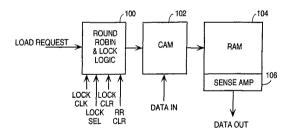

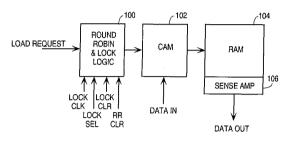

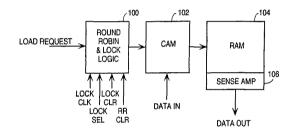

図 1 は、 本 願 発 明 の 一 実 施 例 の ブ ロ ッ ク 図 で あ る 。 連 想 記 憶 装 置 の ア レ イ ( C A M ) 1 0 2 は、ランダム・アクセス・メモリ装置(RAM)104ヘアドレスを指定するために用 いられる。 С А М 1 0 2 および R А М 1 0 4 の結合によって、典型的には、例えばキャッ シュとなり、ある実施例において特定すればレベル・ゼロ・キャッシュとなり、あるいは 別の実施例で可能であるなら変換索引バッファ(translation lookas ide buffer:TLB)となる。いずれの場合でも、CAM102は対応する入 力に応じたアドレスを含み、これは前の例ではコードまたはデータのラインであり、後の 例ではページ・テーブルの入力である。CAM入力内に収容されたデータは、ハずれの例 においても、「タグ」入力と呼ばれる。ラウンド・ロビンおよびロック論理100のよう な制 御 論 理 装 置 は C A M 1 0 2 に 結 合 さ れ る 。 デ ー タ が C A M 1 0 2 お よ び R A M 1 0 4 に書き込まれたとき、すなわち、ラインがキャッシュ・フィル動作に置き換えられたとき 、制御論理装置は、CAMがアドレスしたキャッシュによって使用される置換法を制御す る。 C A M 1 0 2 および R A M 1 0 4 双方の回路は、当業者によく知られた手段によって 形 成 さ れ 得 る 。 C A M 1 0 2 は C A M 1 0 2 の 内 容 参 照 可 能 な 特 性 を 介 し て マ ッ チ ン グ 入 力(もし1つあるならば)を決定するためにアドレス指定される。もしマッチが検出され ると、データは、RAM104に結合されたセンス増幅器106からの出力として、RA M 1 0 4 から読み出され、あるいは前述のフィル動作中にRAM104へデータを書き込 むために用いられたのと同じ回路によって、RAM104への書き込み動作が実行されて もよい。 一般的に、タグ・データを格納するために R A M セルを使用するより典型的な構 造に比べて、この形式のキャッシュ回路構造はより好ましい低電力特性を提供する。 転送要求を受け取ることに加えて、ラウンド・ロビンおよびロック論理100は、ロック ・クロック,ロック選択,ロック・クリア,およびラウンド・ロビン・クリアを含む多く の制御信号を受け取る。ロック・クロックは、それが表明(assert)されたとき、 転送要求がロックであることを示す。ロック・クロックが表明されていないとき、その転 送はフィル(fi11)となる。ここに用いられるように、ロックは、次の転送によって 上書きされないように、ロックされるべきラインへの転送である。フィルは、通常のキャ ッシュ置換法の一部として自由に上書きできる転送である。ロック・クリアは、ロック・ レジスタ(以下さらに説明される)をクリアし、前に転送されたロックの次の上書きを許 容する。ラウンド・ロビン・クリアは、ラウンド・ロビン・レジスタ(同様に、以下さら

に説明される)を予め定める値へリセットする。ロック選択信号は一組のマルチプレクサ

に対するモード選択として用いられ、一組のマルチプレクサはラウンド・ロビン・レジスタおよびワード線を使用可能にするロック・レジスタからの信号を選択する。

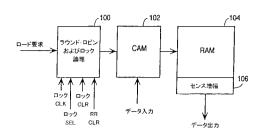

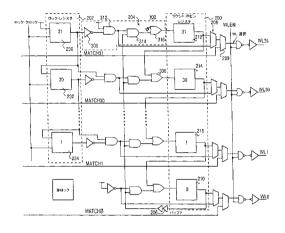

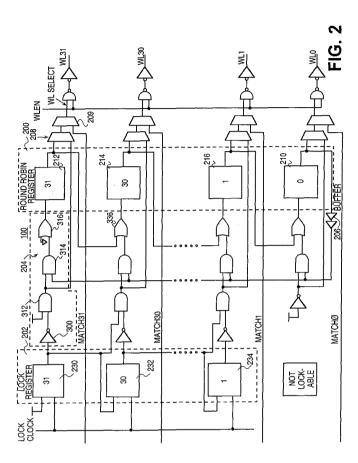

図2は、本願発明の一実施例におけるラウンド・ロビン・ロック論理のブロック図である 。 複 数 の ラ ウ ン ド ・ ロ ビ ン ・ ラ ッ チ 2 1 2 , 2 1 4 , 2 1 6 , 2 1 0 は 、 各 々 キ ャ ッ シ ュ ・ラインの1つに結合される。図示された実施例では、アレイ中に32本あると仮定され る。しかしながら、さらに多くのあるいはさらに少ないライン(従って、ラッチについて も)が本願発明の範囲および目的の範囲内にある。従って、32個のラウンド・ロビン・ ラッチが提供され、ラウンド・ロビン・レジスタ200を構成する。第2の複数のラッチ 2 3 0 , 2 3 2 , 2 3 4 は、ロック・レジスタ 2 0 2 を構成するが、 1 つのラッチは複数 のキャッシュ・ラインの各々に結合される。図示された実施例において、31個のロック ・ラッチがあり、 3 2 本のキャッシュ・ラインのうち 3 1 本までをロックすることを許容 する。1またはそれ以上のラインがロックされるのを防ぐことによって、システムは、新 しいデータをキャッシュ中に転送することを必要とするが、しかし、全ラインがロックさ れ、そのような転送が阻止されるデッドロック状態を回避する。ロック・ラッチは、ラウ ンド・ロビン・ラッチと同じように、デイジー・チェイン状に結合される。このように、 ロック・レジスタは、ロック・クロックに応答して、アレイ中の指令された一連のロック をトップからボトムまで強制する。ラウンド・ロビン・レジスタ200は、循環フィルが アレイ中のボトム・ラインから始まって最も高位の非ロック・ラインまで生起し、そして ボトムへ下方移動し、その後循環する。結合論理204は、ロックされたラインに上書き しないことを確保する。ある実施例では、レジスタ200および204は被パルス・ラッ チであり、別の実施例では、それらはマスター・スレイブ・フリップフロップである。被 パルス・ラッチは、領域的には能率的であるが、プロセス・スキュー(process skew)にわたって不十分な保持時間としてこのような問題に対してより敏感となる。 ロック・レジスタは、動作中のアレイのワード・ライン31に対応する開始ラッチ230 を含み、正の電源供給に結合された入力を有する。このように、ロック・クロックが与え られると、レジスタ230の出力およびそれに対応して図示されるようなデイジー・チェ イン状に結合されたレジスタ232の入力に、高値が現れる。マスター・スレイブ・フリ ップフロップではなく被パルス・ラッチを用いる実施例における1つの問題点は、十分な 遅延が回路に確立され、ロック・クロックが表明された際にラッチ230およびラッチ2 3 2 の両方(またはチェイン中のさらに多く)が設定されるのを避けなければならない。 この問題を解決するために、本願発明のパルス・ラッチの実施例では、ロック・クロック は、ロック・レジスタ中の1つのラッチがその入力値を受け取るために十分な長さの時間 を与えられた短パルスであるが、しかし、意図した目標ラッチの出力に結合されたラッチ が同じデータを受け取らないようにするため十分に短くする。このように、ロック・クロ ックの次の表明では、高値がレジスタ230と同様に、レジスタ232の出力に現れる。 この手法で、31個のロック・クロックの表明の後に、高値がロック・ラッチ234に到 達するまで、ロック・レジスタ中を循環する。この時点において、ロック・レジスタ20 2中の31個の全てのラッチは、ラッチ中に論理1を格納する。

ラウンド・ロビン・レジスタ200のラッチは、ラウンド・ロビン・リセット信号の表明の後に、ラッチ210を除く全てのラッチがクリアにされるように結合される。ラッチ210は、ラウンド・ロビン開始ビットであり、ラウンド・ロビン・クリア信号に応答して設定される。この信号は、またキャッシュを初期化するために全チップ・リセットに与えられる。ラッチ210が設定されると、フィルがワード・ライン・ゼロから開始することが必要である。スタートアップに加えて、ラウンド・ロビン・リセット信号は、ロック・ビットがラウンド・ロビン・ビットと同時に設定される論理的にイリーガルな状態、すなわちロックされたラインがライン・フィルのための次の目標となるために選択されることがないことを確保する。ロック動作が実行されるとき、置換のためにロックできない位置にボトムを設定するこの手法は、最小の論理を必要とする。キャッシュの効率性に関する本手法との関連性は、次に述べられる。

10

20

30

40

50

20

30

50

ワード・ライン・ゼロのフィルに続いて、結合論理204の助けを借りて、次のフィル・ ラインはロックされていない最も高位のラインに認定される。このように、ワード・ライ ン 3 1 がまだロックされていない場合、ラッチ 2 3 0 の出力はゼロとなり、それはインバ ータ300によって反転されてANDゲート312を出力「1」に設定し、さらにそれは A N D ゲート 3 1 4 を出力「 1 」にして、 O R ゲート 3 1 6 はその後レジスタ 2 1 2 の出 力を高値に駆動し、それによりワード・ライン31を選択する。マルチプレクサ208は ロック選択信号を使用し、どのラウンド・ロビン・レジスタまたはロック・レジスタがワ ード・ラインを選択するかを決定する。このように、ロック動作において、ワード・ライ ン(WL)選択は、ゲート312の出力からマルチプレクサ208,209を介して選択 される。表明されるべきWLは、ロックの状態でフィルされるべきラインを示し、前の口 ック・ラッチが論理1に設定され、かつ現在が論理0であることの一致に基づく。論理か ら推論されるように、各ロック動作であるWL表明後に、ロック・クロックが表明される 。 ( 非ロック ) ライン・フィルのために、マルチプレクサ 2 0 8 は対応するラウンド・ロ ビン・ラッチに収容された論理1をマルチプレクサ209を経由してWL選択ノードへ送 ることによりWLを表明する。高信号は、次のフィルが生じるラインを示し、ポインタと してふるまって、ラウンド・ロビン・レジスタを通して伝播する。マルチプレクサ209 は、マルチプレクサ208の出力とCAMマッチ信号との間で選択し、アドレスを行うた めにCAMを使用するキャッシュ読み取りおよび書き込み動作の間に、CAMがWL選択 を表明するのを許容する。別の実施例では、マッチ信号に代わって、デコーダ出力が第2 の入力をマルチプレクサ209に提供する。

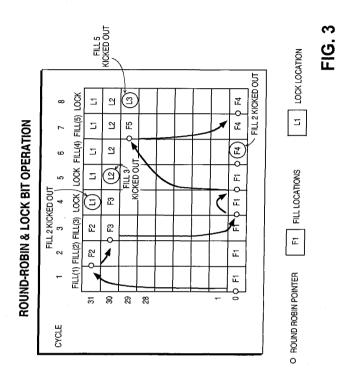

図3は、8周期の期間中における転送の実行過程を示す。サイクル1において、フィル1 がワード・ライン 0 に転送され、そのフィル・ポインタはワード・ライン 3 1 へ位置を示 すために進行する。サイクル2において、フィル2がワード・ライン31へ転送され、そ のフィル・ポインタはワード・ライン30へ位置を示すために進行する。サイクル3にお いて、フィル3がワード・ライン30へ転送される。その後、サイクル4において、ロッ ク 1 がロック開始ライン(ワード・ライン 3 1 )へ転送され、フィル 2 を押し出し、その フィル・ポインタがワード・ライン 0 へ位置を示すためにリセットされる。サイクル 5 に おいて、ロック2が次のロック・ライン(ワード・ライン30)へ転送され、フィル3を 押し出し、再びそのフィル・ポインタがワード・ライン0へ位置を示すためにリセットさ れる。サイクル6において、フィル4が転送され、フィル1を押し出し、そのフィル・ポ インタは最も高位のライン、このケースではワード・ライン29へ位置を示すために進む 。サイクル 7 で、フィル 5 はワード・ライン 2 9 を満たす。サイクル 8 で、ロック 3 はフ ィル 5 を押し出し、そのフィル・ポインタはワード・ライン 0 へ位置を示すためにリセッ トされる。これは、単にフィルおよびロック・パターンの一例である。代わって、もし口 ック 1 , 2 , 3 が最初の 3 つのサイクルで成されると共に、フィル 1 から 5 が次の 5 つの サイクルで成されるならば、データがキャッシュから押し出されることはないであろう。

このように、ソフトウェアを適切に設計することによって、各ロック後のフィル部分を再スタートするという潜在的なあらゆる不利益を取り除くことができる。例えば、あらゆるキャッシュ・ラインを満たす(fill)前に、ソフトウェアは初期時にロックされる必要のある全てのコードまたはデータをロックしてもよい。ロックを最初にすることによって、既にキャッシュへ転送されたコードでラインをロックするという潜在的な負の影響が軽減される得る。ロックすることが望ましいコードの例は、非常に迅速に応答すべきであるルーチンまたは同様のコードを処理するクリティカル割込みである。しかしながら、上記記述は本願発明の一実施例の動作を図示的に説明するものである。

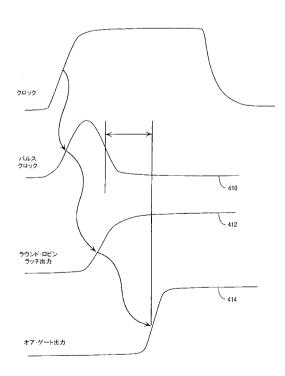

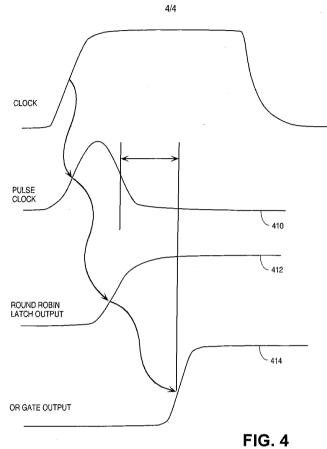

図4は、本願発明の一実施例における一組の信号に対するタイミング図を示す。パルス・クロック信号410は、上述したパルス・ラッチの実施例で用いられる。このパルスは、隣接するラッチからの信号が次のラッチに伝播する前に低に戻るために十分短くすべきであろう。このように、ラウンド・ロビン・ラッチ(図2の212)の出力は、信号412として示される。この出力は、パルス・クロック410に応答して高へ遷移する。信号414によって示されるORゲート(図1の336)の出力がそのORゲートへの信号412の印加に基づいて高へ遷移する前に、パルス・クロック410は低でなければならない

ある実施例において、いくつかのCAMが複数のバンクを有するより大きなキャッシュを 形成するために用いられ、各CAMは関連するラウンド・ロビンおよびロック論理装置を 具備する。各バンクはラウンド・ロビンおよびロック手法をそのバンク内で実行し、他の 全てのバンクからは独立する。

上述した明細書において、本願発明は特定の実施例に関連して説明された。しかしながら、様々な修正および変更が、添付の請求項に示されたように、本願発明のより広い精神および範囲から逸脱しないで成される。従って、本願明細書および図面は、限定的な認識ではなくむしろ解説のために成されているものとみなされる。

【図面の簡単な説明】

【図1】

本願発明の一実施例のブロック図である。

【図2】

本願発明の一実施例におけるラウンド・ロビン・ロック論理のブロック図である。

【図3】

8周期の期間中における転送の実行過程を示す。

【図4】

本 願 発 明 の 一 実 施 例 に お け る 一 組 の 信 号 に 対 す る タ イ ミ ン グ 図 を 示 す 。

10

20

30

# 【図1】

# 【図2】

# 【図4】

# 【図3】

# 【国際公開パンフレット】

### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization International Bureau

#

(43) International Publication Date 12 July 2001 (12.07.2001)

PCT

English

(10) International Publication Number WO 01/50269 A2

- (51) International Patent Classification7:

- (21) International Application Number: PCT/US00/42305

(22) International Filing Date: 27 November 2000 (27.11.2000)

- (25) Filing Language:

- English

- (30) Priority Data: 09/476,444 30 December 1999 (30.12.1999) US

- (71) Applicant (for all designated States except US): INTEL CORPORATION (US/US); 2200 Mission College Boule-vard, Santa Clara, CA 95052 (US).

A2

(72) Inventors; and

(75) Inventors/Applicants (for US only): CLARK, Lawrence,

T. [US/US]; 3161 E. Desert Willow Road, Phoemix, AZ

85084 (US). CLARK, Matthew, M. [US/US]; 261 W.

Pecan Place, Tempe, AZ 85284 (US).

- G06F 12/00 (74) Agents: MALLIE, Michael, J. et al.; Blakely, Sokoloff, Taylor & Zafman LLP, 7th Floor, 12400 Wilshire Boule-CT/US00/42305 vard, Los Angeles, CA 90025 (US).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CR, CU, CZ, DE, DK, DM, DZ, EE, ES, FI, CB, GD, GE, GH, GM, HR, HU, ID, E, N, IS, P, E, KG, RF, RR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW). Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TI, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR). OAPI patent (BF, BI, CF, CG, CI, CM, GA, GN, GW, ML, MR, NE, SN, TD, TG).

#### Published:

Without international search report and to be republished upon receipt of that report.

(54) Title: A METHOD AND APPARATUS TO PERFORM A ROUND ROBIN AND LOCKING CACHE REPLACEMENT SCHEME

(54) Title: A METHOD AND APPARATUS TO PERFORM A ROUND ROBIN AND LOCKING CACHE REPLACEMENT SCHEME

(54) Title: A METHOD AND APPARATUS TO PERFORM A ROUND ROBIN AND LOCKING CACHE REPLACEMENT SCHEME

(54) Title: A METHOD AND APPARATUS TO PERFORM A ROUND ROBIN AND LOCKING CACHE REPLACEMENT SCHEME

(54) Title: A METHOD AND APPARATUS TO PERFORM A ROUND ROBIN AND LOCKING CACHE REPLACEMENT SCHEME

(54) Title: A METHOD AND APPARATUS TO PERFORM A ROUND ROBIN AND LOCKING CACHE REPLACEMENT SCHEME

(55) Title: A METHOD AND APPARATUS TO PERFORM A ROUND ROBIN AND LOCKING CACHE REPLACEMENT SCHEME

(56) Title: A METHOD AND APPARATUS TO PERFORM A ROUND ROBIN AND LOCKING CACHE REPLACEMENT SCHEME SCH (57) Abstract: A first plurality of registers are daisy chained together with each register associated with a particular cache line. Similarly, a second plurality of registers are daisy chained together with each register associated with a cache line. The first daisy chain defines a fill order of cache lines and the second daisy chain defines a lock order for the cache lines.

PCT/US00/42305

# A METHOD AND APPARATUS TO PERFORM A ROUND ROBIN AND LOCKING CACHE REPLACEMENT SCHEME

### BACKGROUND

#### (1) Field of the Invention

The invention relates to cache replacement schemes. More specifically, the invention relates to combined round robin cache replacement and cache line locking schemes.

### (2) Background

Various schemes exist for defining what data is replaced when a new data set is loaded into a cache. One favored scheme in direct mapped caches is a least recently used (LRU) scheme. In an LRU scheme, as the name implies, the block of data that has been used least recently is replaced with any incoming data. Because of the locality of reference common to computer software execution and data usage, this has been found to be a fairly efficient cache replacement scheme. However, as set associativity increases, the complexity and overhead for an LRU scheme make such schemes less attractive due to increasing hardware requirements.

Additionally, in content addressable memory (CAM)-based caches without separate decoders, high set-associativity is achieved, and identifying where to write fill data becomes increasingly problematic. One possible solution that has been employed is a round robin replacement scheme in which a circular shift register loops through identifying the line to be loaded. This has the effect of throwing away the oldest information in the cache, but the replacement is completely independent of the frequency of use. Thus, it can result in a greater amount of cache thrashing.

Some prior solutions to prevent data from being kicked out of the cache prematurely was to allow way locking. These systems failed to provide much granularity. For example, in a two-way cache, half the cache would be

1

PCT/US00/42305

locked, even if the block of data to be retained was relatively small. This often results in inefficient cache usage.

### BRIEF SUMMARY OF THE INVENTION

A first plurality of latches are daisy chained together, forming a register, with each latch associated with a particular cache line. Similarly, a second plurality of latches are daisy chained together with each latch associated with a cache line. The first register defines a fill order of cache lines and the second register defines a lock order for the cache lines.

### **BRIEF DESCRIPTION OF THE DRAWINGS**

Figure 1 is a block diagram of one embodiment of the invention.

Figure 2 is a block diagram of the round robin lock logic in one embodiment of the invention.

Figure 3 shows an exemplary series of loads during an eight cycle period.

Figure 4 is a timing diagram for a subset of signals in one embodiment of the invention.

### DETAILED DESCRIPTION

Figure 1 is a block diagram of one embodiment of the invention. A content addressable memory array (CAM) 102 is used to address into a random access memory unit (RAM) 104. The combination of CAM 102 and RAM 104 may typically be, for example, a cache and more particularly in one embodiment, a level zero cache, or possibly in an alternate embodiment, a translation lookaside buffer (TLB). In either case the CAM 102 contains the addresses corresponding to the corresponding entry, which is a line of code or data in the former case, and a page table entry in the latter. The data contained within the CAM entry is referred to as the "tag" entry in either case. A control logic unit, such as round robin and lock logic 100 is coupled to the CAM 102. The control logic unit controls the replacement scheme employed by the CAM addressed cache when data is to be written into the

CAM 102 and RAM 104, e.g., which line is to be replaced on a cache fill operation. Both circuits, the CAM 102 and the RAM 104, may be written through means well known to those skilled in the art. The CAM 102 is accessed to determine the matching entry (if there is one) via the content-addressable nature of the CAM 102. If a match is found, data is read from RAM 104 as output through sense amp 106, which is coupled thereto, or a write operation to the RAM 104 may be performed through the same circuitry as used to write data into the RAM 104 during the aforementioned fill operation. In general, this form of cache circuit architecture has more favorable low-power characteristics as compared to more typical architectures utilizing RAM cells to store the tag data.

Round robin and lock logic 100, in addition to receiving load requests, receives a number of control signals, including a lock clock, a lock select, a lock clear, and a round robin clear. The lock clock when asserted indicates that the load request is a lock. When the lock clock is not asserted, the load is a fill. As used herein, lock is a load into a line that is to be locked, so as not to be overwritten by subsequent loads. A fill is a load that may be freely overwritten as part of the usual cache replacement scheme. Lock clear clears the lock register (discussed further below) to permit the subsequent overwriting of the previous loaded locks. Round robin clear resets the round robin register (also discussed further below) to a predetermined value. The lock select signal used as the mode select for a set of multiplexers that choose between signals from the round robin registers and the lock registers for word line enablement.

Figure 2 is a block diagram of the round robin lock logic in one embodiment of the invention. The plurality of round robin latches 212, 214, 216, 210, are each associated with one line of a cache. In the shown embodiment, it is presumed that there are 32 lines in the array. However, more or fewer lines (and therefore, latches) are within the scope and contemplation of the invention. Accordingly, 32 round robin latches are provided, comprising the round robin register 200. A second plurality of latches, 230, 232, 234, comprising the lock register 202, also have one latch

associated with each of a plurality of cache lines. In the shown embodiment, there are 31 lock latches which permit the locking of up to 31 of the 32 cache lines. By preventing one or more lines from being locked, the system avoids a deadlock condition in which new data needs to be loaded in the cache, but all lines are locked, preventing such a load. The lock latches are daisy chained together as are the round robin latches. In this manner, the lock register forces an ordered series of locks from top to bottom in the array responsive to the lock clock. The round robin register 200 cause circular fills beginning with a bottom line in the array followed by the highest unlocked line in the array and proceeding downward to the bottom and then circularly. Combinational logic 204 ensures that fills do not overwrite locked lines. In one embodiment, registers 200 and 204 are pulsed latches, and in an alternate embodiment, they are master slave flip-flops. The pulsed latches are more area efficient, but tend to be more susceptible to such issues as insufficient hold times over process skews.

The lock registers include the start latch 230 which corresponds to word line 31 of the array in operation has its input coupled to a positive power supply. Thus, when the lock clock is asserted, a high value appears at the output of register 230, and therefore, correspondingly on the input of register 232 which is daisy chained as shown. One issue that arises in an embodiment in using pulsed latches rather than master-slave flipflops is that sufficient delay must be built into the circuit to avoid both latches 230 and 232 (or more in the chain) from being set when lock clock is asserted. To resolve this issue, in the pulse latch embodiment of the invention, lock clock is a short pulse timed to be sufficiently long to allow one latch in the lock register to receive its input value, but sufficiently short to avoid the latch connected to output of the intended target latch from receiving the same data. Thus, on the next assertion of the lock clock, a high value will appear at the output of register 232, as well as 230. In this manner, the high value cycles down through the lock register 202 until it reaches lock latch 234 after 31 assertions of the lock clock. At that point, all 31 latches in the lock register 202 will have logical one's stored therein.

Round robin register 200 latches are coupled such that after assertion of the round robin reset signal, all latches except latch 210 are cleared. Latch 210 is the round robin start bit and is set responsive to a round robin clear signal. This signal is also asserted on a full-chip reset to initialize the cache. When latch 210 is set, that necessitates that fills will begin at word line zero. In addition to startup, the round robin reset signal is asserted responsive to a lock occurring. This ensures that a lock bit cannot be set coincident with the round robin bit which would constitute a logically illegal condition, i.e., that a locked line was selected to be the next target for a line fill. This scheme of setting the bottom, unlockable location for replacement when a lock operation is performed requires a minimum of logic. The implications of this scheme on the cache efficiency is addressed subsequently.

Accordingly, following a fill of word line zero, with the aid of combinational logic 204, the next fill line is identified to be the highest line that is not locked. Thus, if word line 31 is not yet locked, the output of latch 230 will be a zero, which will be inverted by inverter 310 causing AND gate 312 to output a "1," which causes AND gate 314 to also output a "1" to OR gate 316 which will then drive register 212 to output a high value, thereby selecting word line 31. Multiplexers 208 employ the lock select signal to determine whether the round robin register or the lock register selects the word lines. Thus, on a lock operation, the word line (WL) select is chosen to be taken from the output of gate 312, via the multiplexors 208 and 209. Thus the WL to be asserted, indicating the line to be filled on a lock is based on the coincidence of the previous lock latch being set to logical one and the present one being a logical zero. As can be inferred from the logic, the lock clock is asserted after each lock operation WL assertion. For a (non-locking) line fill, the multiplexor 208 asserts the WL by passing the logical one contained in the corresponding round robin latch to the WL SELECT node via multiplexor 209. The high signal will propagate through the round robin registers behaving as a pointer indicating a line for a next fill to occur. Multiplexor 209 selects between the output of multiplexor 208 and a CAM match signal which permits the CAM to assert the WL select during cache

read and write operations that utilize the CAM for addressing. In an alternative embodiment, instead of a match signal, a decoder output may provide the second input to multiplexor 209.

Notably, start register 210 is the only register of the round robin registers with high fanout. As used herein, "high" fanout is deemed to be more than three inputs to be driven by the output of the device experiencing the fanout. Buffer 206 is used to buffer up the signal to accommodate the fanout as register 210 must drive an input signal for each of the other round robin registers. Conversely, the other round robin registers drive inputs only to their nearest neighbors. Consequently, they can be kept very small. This is desirable since there are two latches (in the pulsed-latch embodiment) per line in the cache, a number typically 32 in TLB's, but numbering into the thousands in the case of caches. This desirability of small size is the primary reason for employing an embodiment having the latch storage elements as pulsed latches rather than master-slave flipflops. In controlling the fanout, the device sizes and corresponding power consumption of the circuitry isreduced. Since the start register is at the bottom, layout of the buffer is simplified as area is available at the edge of the array, which corresponds to the sense and write circuitry area of the CAM and RAM circuits.

Figure 3 shows an exemplary series of loads during an eight cycle period. In cycle one, fill one is loaded into word line zero, and the fill pointer advances to point to word line 31. In cycle two, fill two is loaded into word line 31, and the fill pointer is advanced to point to word line 30. In cycle three, fill three is loaded into word line 30. Then in cycle four, lock one is loaded into the lock starting line (word line 31), kicking out fill two and the fill pointer is reset to point to word line zero. In cycle five, lock two is loaded into the next lock line (word line 30), kicking out fill three and again, the fill pointer is reset to point to word line zero. At cycle six, fill four is loaded, kicking out fill one, and the fill pointer is advanced to point to the highest unlocked line, in this case, word line 29. At cycle seven, fill five fills word line 29. At cycle eight, lock three kicks out fill five, and the fill pointer is reset to point to word line zero. This is merely one exemplary fill and lock

pattern. Alternatively, if locks one, two, and three had been done in the first three cycles with fills one through five done in the next five cycles, no data would have been kicked out of the cache. Thus, proper software design can eliminate any potential penalty of restarting the fill portion after each lock. For example, software may lock all code or data which needs to be locked at initialization before filling any cache lines. By doing the locks first, the potential negative impact of locking lines on code already loaded into the cache may be alleviated. An example of code which is desirable to lock will be critical interrupt handling routines or similar code which should respond very quickly. However, the above description is illustrative to explain of the operation of one embodiment of the invention.

Figure 4 shows a timing diagram of a subset of signals of one embodiment of the invention. The pulse clock signal 410 is used in the pulse latch embodiment described above. The pulse should be short enough that it will have gone back low before the signal from an adjacent latch can propagate to it neighbor. Thus, the output of round robin latch (212 of Figure 2) is shown as signal 412. This output goes high responsive to the pulse clock 410. The pulse clock 410 must be low before the output of OR gate (336 of Figure 1) represented by signal 414 is asserted high based on the application of signal 412 to the OR gate.

In one embodiment, several CAMs, each with an associated round robin and lock logic unit, are used to form a larger cache having a plurality of banks. Each bank implements the round robin and lock scheme within the bank and independent of all other banks.

In the foregoing specification, the invention has been described with reference to specific embodiments thereof. It will, however, be evident that various modifications and changes can be made thereto without departing from the broader spirit and scope of the invention as set forth in the appended claims. The specification and drawings are, accordingly, to be regarded in an illustrative rather than a restrictive sense.

PCT/US00/42305

### CLAIMS

What is claimed is:

- An apparatus comprising:

- a first plurality of latches coupled together in a first shift register, each latch of the first plurality associated with a line of a cache, the register defining a fill order for the cache lines; and

- a second plurality of latches coupled together in a second shift register, each latch of the second plurality associated with a cache line, the register defining a lock order for the cache lines.

- 2. The apparatus of claim 1 further comprising:

- a buffer to amplify an output of a first start register of the first plurality to drive an input for each other register in the first plurality of latches.

- The apparatus of claim 2 wherein each other register in the first plurality only drives an input for its successor in the plurality of latches.

- 4. The apparatus of claim 1 wherein the first plurality of latches and the second plurality of latches are different in number.

- 5. The apparatus of claim 1 wherein a first start register of the first plurality of latches is associated with a cache line an address with a maximum difference from an address of a second cache line associated with a second start register of the second plurality.

- 6. The apparatus of claim 5 further comprising:

combinational logic coupling the first and second plurality of latches such that a second fill line is coextensive with a next lock line.

- The apparatus of claim 1 wherein only one latch of the first plurality of latches has fanout greater than three.

- 8. The apparatus of claim 1 wherein the cache is a translation lookaside buffer (TLB).

- 9. The apparatus of claim 1 where the line to be locked is determined by the coincidence of a logical one in the preceding lock register bit and a logical zero in the present bit.

- 10. The apparatus of claim 1 wherein the first shift register is configured as a circular buffer.

- 11. The apparatus of claim 10 wherein a length of a circular shift in the first shift register is determined by setting bits in the second shift register.

- The apparatus of claim 1 wherein each latch comprises a masterslave flipflop.

- 13. A system comprising:

- a content addressable memory array (CAM);

a random access memory (RAM) coupled to the CAM; and

control logic coupled to the CAM to cause the CAM to lock

specified lines of the RAM while implementing a round robin replacement

scheme for unlocked lines in the RAM.

- 14. The system of claim 13 wherein the control logic comprises: a first plurality of latches coupled together in a daisy chain, each latch of the plurality associated with a line of the RAM, the daisy chain defining a fill order for the RAM lines; and

- a second plurality of latches coupled together in a daisy chain, each register of the second plurality associated with a cache line, the daisy chain defining a lock order for the cache lines.

- 15. A method comprising:

defining a lock starting line;

defining a fill starting line a distance from the lock starting line;

and

resetting a fill pointer to the fill starting line each time a lock is

- loaded.

16. The method of claim 15 further comprising:

changing a lock indicator to indicate a line one line closer to the

- fill starting line responsive to a lock line being loaded.

17. The method of claim 15 further comprising:

filling the fill starting line on a first fill; and

filling an unlocked line most proximate to the lock starting line

- filling an unlocked line most proximate to the lock starting line on a second fill.

PCT/US00/42305

18. A computer readable storage media containing executable computer program instructions which when executed cause a digital processing system to perform a method comprising:

initializing a lock mode in a cache loading lock data into a cache

line; and

locking the cache line; and retrieving the cache to fill mode.

PCT/US00/42305

1/4

FIG. 1

2/4

PCT/US00/42305

3/4

PCT/US00/42305

# 【国際公開パンフレット(コレクトバージョン)】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization International Bureau

#

(43) International Publication Date 12 July 2001 (12.07.2001)

PCT

(10) International Publication Number WO 01/50269 A3

- G06F 12/12 (51) International Patent Classification7:

- (21) International Application Number: PCT/US00/42305

- (22) International Filing Date: 27 November 2000 (27.11.2000)

(25) Filing Language:

01/50269 A3

- English

- (26) Publication Language: English

- (30) Priority Data: 09/476,444

- 30 December 1999 (30.12.1999) US

- (71) Applicant (for all designated States except US): INTEL CORPORATION (US/US): 2200 Mission College Boulevard, Santa Clara, CA 95052 (US).

- (81) Designated States (notional): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CR, CU, CZ, DE, DK, DM, DZ, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, RK, KZ, LC, LK, LR, LS, LT, LU, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, PL, PT, RO, RU, SD, SS, ES, GS, JS, KS, LT, TJ, TM, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW), Eurasian patent (AM, AZ, BY, RG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, TI, LU, MC, NL, PT, SE, TR, OAP) patent (BF, BL, CF, CG, CI, CM, GA, GN, GW, ML, MR, NE, SN, TD, TG).

(88) Date of publication of the international search report: 13 December 2001

(72) Inventors; and

(75) Inventors/Applicants (for US only): CLARK, Lawrence,

T. [US/US]; 3161 E. Desert Willow Road, Phoemix, AZ

85048 (US). CLARK, Matthew, M. [US/US]; 261 W.

Pecan Place, Tempe, AZ 85284 (US).

(74) Agents: MALLIE, Michael, J. et al.; Blakely, Sokoloff, Taylor & Zafman LLP, 7th Floor, 12400 Wilshire Boule-vard, Los Angeles, CA 90025 (US).

For two-letter codes and other abbreviations, refer to the "Guid-ance Notes on Codes and Abbreviations" appearing at the begin-ning of each regular issue of the PCT Gazette.

(54) Title: A METHOD AND APPARATUS TO PERFORM A ROUND ROBIN AND LOCKING CACHE REPLACEMENT SCHEME

(57) Abstract: A first plurality of registers are daisy chained together with each register associated with a particular cache line. Similarly, a second plurality of registers are daisy chained together with each register associated with a cache line. The first daisy chain defines a fill order of cache lines and the second daisy chain defines a lock order for the cache lines.

# 【国際調査報告】

|                                                                                       | INTERNATIONAL SEARCH REPO                                                                                                                                                                                                                                                    | ORT                           | Inte .ional App                |                       |  |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------|-----------------------|--|

|                                                                                       |                                                                                                                                                                                                                                                                              | PCT/US 00                     |                                | /42305                |  |

| A. CLASSIF<br>IPC 7                                                                   | ROATION OF SUBJECT MATTER<br>606F12/12                                                                                                                                                                                                                                       |                               |                                |                       |  |

|                                                                                       | international Patent Classification (IPC) onto both national classification                                                                                                                                                                                                  | ion and IPC                   |                                |                       |  |

| B. F(ELDS S                                                                           | SEARCHED<br>cumentation searched (classification system followed by classification                                                                                                                                                                                           | numbole)                      |                                |                       |  |

| IPC 7                                                                                 | G06F                                                                                                                                                                                                                                                                         |                               |                                |                       |  |

| Decumentati                                                                           | ion searched other than minimum documentation to the extent that su                                                                                                                                                                                                          | ch documents are incl         | uded in the fields so          | earched               |  |

| Electronic da                                                                         | ata base consulted during the international search (name of data base                                                                                                                                                                                                        | e and, where practical        | , search terms used            | )                     |  |

| EPO-In                                                                                | ternal, PAJ                                                                                                                                                                                                                                                                  |                               |                                |                       |  |

| C. DOCUME                                                                             | ENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                               |                               |                                |                       |  |

| Category °                                                                            | Citation of document, with indication, where appropriate, of the relation                                                                                                                                                                                                    | vant passages                 |                                | Relevant to claim No. |  |

| Х                                                                                     | GB 2 284 911 A (PLESSEY SEMICONDUCTORS<br>LTD) 21 June 1995 (1995-06-21)                                                                                                                                                                                                     |                               | 13,18                          |                       |  |

| А                                                                                     | the whole document                                                                                                                                                                                                                                                           |                               |                                | 1,10,11,<br>14-17     |  |

| А                                                                                     | US 5 937 429 A (LIU PEICHUN PETER<br>10 August 1999 (1999-08-10)<br>column 3, line 41 -column 5, line                                                                                                                                                                        | 1-3,10,<br>12-15,18           |                                |                       |  |

| A                                                                                     | US 5 928 352 A (DOWECK JACOB ET 27 July 1999 (1999-07-27) column 4, line 7 -column 5, line                                                                                                                                                                                   | 1,8,13,<br>15,18              |                                |                       |  |

| A                                                                                     | US 5 029 072 A (MOYER WILLIAM C<br>2 July 1991 (1991-07-02)<br>column 1, line 30 -column 2, line                                                                                                                                                                             | 1,8,13,<br>15,18              |                                |                       |  |

|                                                                                       |                                                                                                                                                                                                                                                                              |                               |                                |                       |  |

| Ш.                                                                                    | ther documents are listed in the continuation of box C.                                                                                                                                                                                                                      | X Patent family               | members are listed             | l in annex.           |  |

| "Special c  'A' docum consi 'E' earlier filing 'L' docum which citati 'O' docum later | irradional fling date<br>the application bit<br>every underlying the<br>behavior of the property of the<br>behavior of the property of the<br>current is taken alone<br>Jamed invention<br>ventive step when the<br>rec other such docu-<br>ue to a person skilled<br>tamily |                               |                                |                       |  |

|                                                                                       | e actual completion of the international search  5 July 2001                                                                                                                                                                                                                 | Date of mailing o             | f the international se<br>2001 | анси героп            |  |

|                                                                                       | I mailing address of the ISA<br>European Patent Office, P.B. 5816 Patentlaan 2<br>N. – 2201 VF 1894W,<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo ni,<br>Fax: (+31-70) 340-3016                                                                                                | Authorized officer N1elsen, 0 |                                |                       |  |

|                                          |   | mation on patent family mer |                      |                            | 00/42305                               |

|------------------------------------------|---|-----------------------------|----------------------|----------------------------|----------------------------------------|

| Patent document<br>cited in search repor | t | Publication<br>date         | Patent far<br>member | nity<br>(s)                | Publication date                       |

| GB 2284911                               | Α | 21-06-1995                  | NONE                 |                            |                                        |

| US 5937429                               | A | 10-08-1999                  | NONE                 |                            |                                        |

| US 5928352                               | Α | 27-07-1999                  | NONE                 |                            |                                        |

| US 5029072                               | A | 02-07-1991                  | JP 704               | 1180 C<br>6325 B<br>6744 A | 19-02-1996<br>17-05-1995<br>11-07-1987 |

| *****                                    |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

|                                          |   |                             |                      |                            |                                        |

# フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,CH,CY,DE,DK,ES,FI,FR,GB,GR,IE,IT,LU,MC,NL,PT,SE,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CR,CU,CZ,DE,DK,DM,DZ,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NO,NZ,PL,PT,RO,RU,SD,SE,SG,SI,SK,SL,TJ,TM,TR,TT,TZ,UA,UG,US,UZ,VN,YU,ZA,ZW

(72)発明者 クラーク,マシュー・エム アメリカ合衆国 アリゾナ州 85284 テンピ ウエスト・ピーカン・プレイス261 Fターム(参考) 5B005 JJ13 MM01 QQ04