(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2007-508620

(P2007-508620A)

(43) 公表日 平成19年4月5日(2007.4.5)

(51) Int.C1.

GO6F 13/362 (2006.01)

F 1

GO6F 13/362 51 OA

テーマコード(参考)

5B061

|               |                              | 審査請求 未請求 予備審査請求 未請求 (全 24 頁)                                                |

|---------------|------------------------------|-----------------------------------------------------------------------------|

| (21) 出願番号     | 特願2006-533965 (P2006-533965) | (71) 出願人 504199127                                                          |

| (86) (22) 出願日 | 平成16年9月22日 (2004.9.22)       | フリースケール セミコンダクター イン<br>コーポレイテッド                                             |

| (85) 翻訳文提出日   | 平成18年3月24日 (2006.3.24)       | アメリカ合衆国 78735 テキサス州<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501                  |

| (86) 國際出願番号   | PCT/US2004/031053            | (74) 代理人 100116322                                                          |

| (87) 國際公開番号   | W02005/038563                | 弁理士 桑垣 衛                                                                    |

| (87) 國際公開日    | 平成17年4月28日 (2005.4.28)       | (72) 発明者 ベッドウェル、ライアン デイ。<br>アメリカ合衆国 78640 テキサス州<br>カイル ホーガン 159             |

| (31) 優先権主張番号  | 10/682,571                   | (72) 発明者 クルーズ、アーナルド アール。<br>アメリカ合衆国 78739 テキサス州<br>オースティン ニーダム レーン 65<br>35 |

| (32) 優先日      | 平成15年10月9日 (2003.10.9)       |                                                                             |

| (33) 優先権主張国   | 米国(US)                       |                                                                             |

最終頁に続く

(54) 【発明の名称】マルチマスタ共用資源システム中で使用するための通信ステアリング

## (57) 【要約】

メモリ・アレイとインタフェイスするプロセッサ(11)を有する処理システム(12)の低電力モード中に、漏れ電流が、メモリ・アレイ(28)中において取り除かれる。2つの電力プレーンが、作成されるので、プロセッサ(18)は、このアレイの電源が切られるときにメモリ・アレイ(28)をバイパスしながら、システム・メモリ(80)を使用して命令を実行し続けることができる。スイッチ(56)は、命令の実行から、またはこのプロセッサ以外のどこかのこのシステム中を起源とするソースからもたらされるプロセッサにより開始される制御に応じて供給電圧端子に対する電気的接続を選択的に除去する。メモリ・アレイ(28)に対する電力の復旧に応じてすぐに、メモリ・アレイに対するアレイをサポートする2つの電力プレーンのうちのどちらが配置されるかに応じて、データは、使用不可能としてマークする必要があることもあり、またはマークする必要がないこともある。所定の判断基準を使用して、電力の復旧のタイミングを制御することができる。複数のアレイを実装して、漏れ電流を独立に低減させることができる

**【特許請求の範囲】****【請求項 1】**

システム・バスと、

該システム・バスに結合された第1のバス・マスタと、

該システム・バスに結合された第2のバス・マスタと、

該システム・バスに結合され、該第1のバス・マスタおよび該第2のバス・マスタのうちの少なくとも一方のバス・マスタによって所有されるように構成可能な資源と、

該資源と、該第1のバス・マスタおよび該第2のバス・マスタのうちの少なくとも一方のバス・マスタとの間で、該資源の所有権に基づいて通信経路を確立する追加信号ステアリング・ロジックと、

からなり、該通信経路を使用して、該資源と、該第1のバス・マスタおよび該第2のバス・マスタのうちの該少なくとも一方のバス・マスタとの間で、少なくとも1つの追加信号を転送する、データ処理システム。

**【請求項 2】**

システム・バスを有するデータ処理システムにおいて追加信号を伝えるための方法であつて、

該システム・バスに結合された資源と、該システム・バスに結合された複数のバス・マスタのうちの少なくとも1つのバス・マスタとの間で該資源の所有権に基づいて通信経路を確立する工程と、

該資源と、該複数のバス・マスタのうちの該少なくとも1つのバス・マスタとの間で、該通信経路を介して該システム・バスからは分離されて、追加信号を転送する工程と、

からなる方法。

**【請求項 3】**

システム・バスと、

該システム・バスに結合された第1のバス・マスタと、

該システム・バスに結合された第2のバス・マスタと、

該システム・バスに結合され、該第1のバス・マスタおよび該第2のバス・マスタによつて使用可能であり、該第1のバス・マスタおよび該第2のバス・マスタのうちの少なくとも一方のバス・マスタによって所有されるように構成可能な資源と、

該資源と、該第1のバス・マスタおよび該第2のバス・マスタのうちの少なくとも一方のバス・マスタとの間で通信経路を確立する追加信号ステアリング・ロジックと、

からなり、該通信経路を使用して、該資源と、該第1のバス・マスタおよび該第2のバス・マスタのうちの該少なくとも一方のバス・マスタとの間で、少なくとも1つの追加信号を転送し、該通信経路が、該資源によつて決定されるデータ処理システム。

**【請求項 4】**

システム・バスを有するデータ処理システムにおいて追加信号を伝えるための方法であつて、

該システム・バスに結合された資源と、該システム・バスに結合された複数のバス・マスタのうちの少なくとも1つのバス・マスタとの間で、該資源によつて決定される通信経路を確立すること、および

該資源と、該複数のバス・マスタのうちの該少なくとも1つのバス・マスタとの間で、該通信経路を介して該システム・バスから分離されて該追加信号を転送すること、

からなる方法。

**【請求項 5】**

第1のバス・マスタと、

第2のバス・マスタと、

該第1のバス・マスタおよび該第2のバス・マスタによりアクセス可能な共用再構成可能資源と、

からなり、該共用再構成可能資源は、該第1のバス・マスタおよび該第2のバス・マスターのうちの少なくとも一方のバス・マスターと、複数の周辺機能から選択される第1の周辺

10

20

30

40

50

機能を実施するための回路と、の間で、通信経路を確立する、データ処理システム。

**【請求項 6】**

第1のマスタと第1の周辺機能を実施するための回路との間に第1の通信経路を確立するために、再構成可能資源を構成する工程と、

第2のマスタと第2の周辺機能を実施するための回路との間に第2の通信経路を確立ために、該再構成可能資源を構成する工程と、

からなり、

該第1の周辺機能および該第2の周辺機能のそれぞれが、複数の周辺機能から選択される、再構成可能資源を動作させるための方法。

**【請求項 7】**

複数の周辺機能に関連する情報を記憶するように構成可能な再構成可能チャネル・ストレージと、

該複数の周辺機能のそれぞれを実施するように構成可能な再構成可能チャネル回路と、

該再構成可能チャネル・ストレージおよび該再構成可能チャネル回路に結合され、該複数の周辺機能のうちの選択される機能を実施するために、該再構成可能チャネル・ストレージおよび該再構成可能チャネル回路を構成する制御ロジックと、

からなる共用再構成可能資源。

**【請求項 8】**

第1のマスタおよび第2のマスタと情報をやりとりするバス・インターフェイスと、

該バス・インターフェイスに結合され、複数のエンドポイントがそれぞれ該第1のマスタおよび該第2のマスタのうちの一方に割付け可能である、該複数のエンドポイントからなるエンドポイント・ストレージ回路と、

USBホストと情報をやりとりするシリアル・インターフェイス・エンジンと、

該バス・インターフェイス、エンドポイント・ストレージ回路、およびシリアル・インターフェイス・エンジンに結合され、該シリアル・インターフェイス・エンジンに結合されたUSBプロトコル・ロジックと、該USBプロトコル・ロジックから受け取られる情報に基づいて割込みを生成するエンドポイント割込みロジックと、割込みステアリング・レジスタと、該割込みステアリング・レジスタによって提供されるステアリング情報に基づいて該第1のマスタおよび該バス・マスタのうちの対応する一方に該割込みをそれぞれ経路指定する割込みステアリング・ロジックと、からなるUSB機能コントローラと、

からなる共用ユニバーサル・シリアル・バス(USB)資源。

**【請求項 9】**

複数のエンドポイントがそれぞれ、複数のバス・マスタのうちの1つに割付け可能である、複数のエンドポイントと、

同複数のエンドポイントに結合され、USBホストからの通信に基づいて割込みを生成するエンドポイント割込みロジック、該複数のバス・マスタによりアクセス可能な少なくとも1つの割込みステアリング・レジスタ、および同割込みステアリング・レジスタによって提供されるステアリング情報に基づいて該複数のバス・マスタのうちの対応するバス・マスタに該各割込みを経路指定する割込みステアリング・ロジック、からなるUSB機能コントローラと、

からなる共用ユニバーサル・シリアル・バス(USB)資源。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、通信ステアリングに関し、より詳細には、マルチマスタ共用資源システム中で使用するための通信ステアリングに関する。

**【背景技術】**

**【0002】**

複数のバス・マスタがデータ処理システム中でより頻繁に使用されるようになりつつあるので、これらの複数のマスタと、1つ以上の共用資源の間で情報をやりとりするための

10

20

30

40

50

新しいアプローチが必要になっている。共用すべき必要がある資源の1実施例は、U S B (Universal Serial Busユニバーサル・シリアル・バス)規格に準拠した回路である。このU S Bは、U S B - I F (Universal Serial Bus - Implementers Forumユニバーサル・シリアル・バス - インプリメンターズ・フォーラム)による規格として定義されてきている。

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0 0 0 3】**

残念ながら、このU S B規格はマルチマスタ・システムにおけるエンドポイントの共用制御を可能にするためのメカニズムを含んではいない。

10

**【課題を解決するための手段】**

**【0 0 0 4】**

本発明は、添付図面によって、実施例として限定する目的ではなく示されている。これらの図面中において同様な参照番号は同様な要素を示している。

**【発明を実施するための最良の形態】**

**【0 0 0 5】**

これらの図面中の要素は、簡略化し明確にするように示され、必ずしも寸法通りに示されていない。例えば、これらの図面中における要素の一部の寸法は、本発明のこれらの実施形態の理解を高めるために、他の要素と比べて誇張されている。

**【0 0 0 6】**

このU S B仕様は、U S Bエンドポイントの使用をU S Bデバイス中に存在するデータ・チャネルおよび制御チャネルとして定義している。これらのU S Bエンドポイントは、データのソースまたはシンクであり、メモリおよび追加ロジックを用いて実装され、1つのプロセッサまたはマイクロコントローラによって制御される。一部のケースでは、ある数のエンドポイントを1つのプロセッサによって制御し、他のエンドポイントを異なるプロセッサによって制御し、それによってこれらのすべてのエンドポイントの共用制御を実現することが望ましい。

20

**【0 0 0 7】**

この用語「共用資源」は、複数のバス・マスタ（例えば、バス・マスター12、14）によってアクセス可能である資源を意味するように使用される。このようなシステムは、複数のバス・マスターのうちの1つ以上のバス・マスターが共用資源の所有権を有し、その所有しているマスターが、所有していないマスターによる資源へのアクセス可能性を決定することができる。本発明の1実施形態において、資源を所有するマスターがゼロ個（すなわち、マスターが存在しない）の場合にはマスターは、他のマスターによるこの資源に対するアクセス可能性を決定する権限をもたない。所有されていない資源に対するアクセス可能性は、様々な方法で決定することができる。1実施例としては、どのようなマスターでも、所有されていない資源に対する完全なアクセスを有することができる。代替実施形態では、異なる方法で、所有されていない資源に対するアクセス可能性を決定することができる。一部の実施形態においては、どのようなマスターによっても所有されていない資源により、すべてのマスターが所有権を請求することが可能になる。したがって、一部の実施形態では、所有権が明け渡されるようにすることもできる。本発明の一部の実施形態においては、1つの資源が複数のマスターによって所有される場合、この資源は所有されていないものと見なされる。本発明の代替実施形態においては、1つの資源が複数のマスターによって所有される場合には、この資源に対するアクセス可能性は、これら複数の所有しているマスターによって一緒に決定することができる。

30

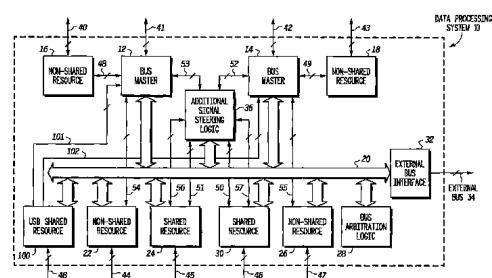

**【0 0 0 8】**

図1は、本発明の1実施形態によるデータ処理システム10をブロック図形式で示している。本発明の1実施形態において、データ処理システム10は、すべてバス20に双方に結合されて情報のやりとりをスムーズに実行する複数のバス・マスター12、14と、複数の共用資源24、30、100と、複数の非共用資源22、26を含んでいる。図1

40

50

のこの実施形態において、バス・マスター12、14は、プロセッサなどの1つのバス・マスター、または1つ以上のプロセッサ、ならびにサポート回路(supporting circuit)を備えるサブシステムを表すことができる。共用資源24、30、100は、オプションとして複数のバス・マスター12、14によって共用されることもあることに留意されたい。非共用資源22、26は、バス・マスター12、14によって共用されず、したがってバス・マスター12、14のうちの一方によってしかアクセスされない。本明細書中で使用している用語「バス」は、データ、アドレス、制御、ステータスなどの1つ以上の様々なタイプの情報を転送するために使用することができる複数の信号または導体を意味する。これらの用語「導体」および「信号」は、本明細書中では、交換可能なように使用される。本発明の1実施形態において、バス20は、1つ以上のバス・プロトコルを使用して実装される。バス調停ロジック28を使用して、バス・マスター12と14の間の調停を行って、これら複数のバス・マスター12、14のうちのどちらがバス20の支配権を有するかを決定する。

#### 【0009】

本発明の一部の実施形態においては、バス・マスター12は、バス20を介するのではなく、導体48を介して1つ以上の非共用資源(例えば、16)に双方向に結合することができる。同様に、本発明の一部の実施形態においては、バス・マスター14は、バス20を介するのではなく、導体49を介して1つ以上の非共用資源(例えば、18)に双方向に結合することができる。この例示の実施形態において、非共用資源16は、バス・マスター12によってしかアクセスされず、バス・マスター14によってはアクセスされない。同様に、非共用資源18は、バス・マスター14によってしかアクセスされず、バス・マスター12によってはアクセスされない。本発明の一部の実施形態は、データ処理システム10の外部にある外部バス34にバス20を結合することができる外部バス・インターフェイス32を含んでいる。本発明の1実施形態においては、データ処理システム10は、1つの集積回路上で実装される。本発明の代替実施形態は、任意の適切な回路を使用した任意の方法でデータ処理システム10を実装することができる。

#### 【0010】

本発明の一部の実施形態においては、非共用資源16は、1つ以上の端子40を介してデータ処理システム10の外部にある回路に結合することができる。バス・マスター12は、1つ以上の端子41を介してデータ処理システム10の外部にある回路に結合することができる。バス・マスター14は、1つ以上の端子42を介してデータ処理システム10の外部にある回路に結合することができる。非共用資源18は、1つ以上の端子43を介してデータ処理システム10の外部にある回路に結合することができる。USB共用資源100は、1つ以上の端子48を介してデータ処理システム10の外部にある回路に結合することができる。非共用資源22は、1つ以上の端子44を介してデータ処理システム10の外部にある回路に結合することができる。共用資源24は、1つ以上の端子45を介してデータ処理システム10の外部にある回路に結合することができる。共用資源30は、1つ以上の端子46を介してデータ処理システム10の外部にある回路に結合することができる。また非共用資源26は、1つ以上の端子47を介してデータ処理システム10の外部にある回路に結合することができる。本発明の代替実施形態は、端子40～48のうちの任意の組合せを使用してもよいし、また使用しなくてもよい。端子40～48は、使用可能な任意の方法で実装することができる。

#### 【0011】

引き続き図1を参照すると、共用資源24は、バス・マスター12および14によって共用することができる。また共用資源24は、どのバス・マスターによっても所有することができないか、またはバス・マスター12および14のうちのどちらか一方だけによって所有することもできる。USB共用資源100は、パーティションに区分することができ、その結果、1つ以上の部分は、バス・マスター12および14により共用することができる。また、USB共用資源100は、パーティションに区分することができ、その結果、1つ以上の部分は、どのバス・マスターによっても所有することができないか、またはバス・マ

10

20

30

30

40

50

スタ 1 2 および 1 4 のどちらか一方だけによって所有することもできる。本発明の様々な実施形態は、リセット後に所望の任意の方法で、共用資源またはその一部分の所有権を割り付けることができることに留意されたい。1 実施例として、本発明の 1 実施形態では、U S B 共用資源 1 0 0 のすべての部分は、リセットから出てくることができ、その結果、所定の単 1 バス・マスタ（例えば、バス・マスタ 1 2 ）は、所有権を有することになる。

#### 【 0 0 1 2 】

本発明のこの例示の実施形態においては、追加信号ステアリング・ロジック 3 6 を使用して、どのバス・マスタ、またはバス・マスタ 1 2 、 1 4 が、追加信号 5 6 、 5 7 のうちのどの 1 つ以上の信号を受け取るかを決定する。バス 2 0 に含まれるこれらの信号は、バス 2 0 によって実装されるバス・プロトコルによって定義される信号であることに留意されたい。追加信号 5 6 、 5 7 は、データ処理システム 1 0 中のバス・マスタ 1 2 、 1 4 のサブセットに対して選択的に提供することができる信号を含んでいる。本発明の代替実施形態においては、これらの 1 つ以上のバス信号を、バス・マスタ 1 2 、 1 4 のサブセットに選択的に提供する必要がある場合には、追加信号ステアリング・ロジック 3 6 を使用して、これらのバス信号 2 0 のうちの 1 つ以上の信号を方向付けすることができることに留意されたい。バス・マスタ 1 2 、 1 4 のサブセットは、ある種のケースではすべてのバス・マスタのフルセットを含むことができるが、一般的には、追加信号 5 6 、 5 7 はデータ処理システム 1 0 中においてこれらのバス・マスタ 1 2 、 1 4 のすべてに対するよりも少なく方向付けが行われる。信号 5 0 および 5 1 を使用して、追加信号 5 6 、 5 7 のステアリングについての制御および / またはステータスを実現する。

10

20

30

40

#### 【 0 0 1 3 】

本発明のこの例示の実施形態においては、追加信号ステアリング・ロジック 3 6 は、追加信号 5 7 を受け取り、方向付けするために共用資源 3 0 に結合される。追加信号 5 7 は、共用資源 3 0 と適切なバス・マスタ 1 2 、 1 4 との間でそれぞれ信号 5 3 または 5 2 を介して追加信号ステアリング・ロジック 3 6 によって方向付ける必要がある 1 つ以上の信号を含んでいる。追加信号 5 7 は、所望の任意の機能を有することができるが、これらの信号は一般に、すべてのバス・マスタ 1 2 、 1 4 に対してほぼ同時に供給すべきではなく、その代わりにバス・マスタ 1 2 、 1 4 のサブセットに対してしか提供すべきでない信号である。追加信号 5 7 の 1 実施例は、共用資源 3 0 の所有権を有し、この割込みに対して応答する必要があるバス・マスタに対してしか方向付けされ供給されるべきでない割込み信号である。本発明の他の実施形態は、追加信号ステアリング・ロジック 3 6 を使用して、この全体のバス・マスタ（例えば、 1 2 、 1 4 ）のサブセットに対して所望の任意の信号を方向付けすることができる。方向付けすることができる他の追加信号の一部の実施例は、リセット信号、 D M A 要求信号および D M A 認可信号、モード制御信号（例えば、電力制御モード）、カスタム・プロトコル・ハンドシェイク信号、プライベート・メッセージ・チャネル、ならびに 1 つ以上の他の所望の任意の信号である。本発明の一部の実施形態では、追加信号 5 7 のうちの 1 つ以上の信号を、選択された状況下においてこれらのバス・マスタ 1 2 、 1 4 のすべてに方向付けすることができる実施形態が存在し得ることに留意されたい。さらに、本発明の一部の実施形態では、信号 5 2 、 5 3 、 5 6 、および 5 7 のうちのどの信号も、双方向でなくともよく、また一部の信号、またはすべての信号が双方向であってもよい。

30

40

#### 【 0 0 1 4 】

追加信号ステアリング・ロジック 3 6 は、信号 5 0 を介して共用資源 3 0 に対して双方向に結合される。信号 5 0 は、追加信号 5 7 の方向付け（steering）において使用される制御情報および / またはステータス情報を提供するために使用される 1 つ以上の信号を含んでいる。本発明の代替実施形態は、任意のタイプの信号を使用してこの制御情報および / またはステータス情報を伝えることができる。すべての必要な制御情報および / またはステータス情報は、追加信号ステアリング・ロジック 3 6 中に存在し、あるいは別の方針で追加信号ステアリング・ロジック 3 6 に対して与えられるので、本発明の一部の実施形態は、信号 5 0 を必要としないこともある。

50

**【 0 0 1 5 】**

本発明のこの例示の実施形態において、追加信号ステアリング・ロジック36は、追加信号56を受け取り方向付けするために共用資源24に結合される。追加信号56は、共用資源24と適切なバス・マスター12、14の間でそれぞれ信号53または52を介して追加信号ステアリング・ロジック36によって方向付けする必要がある1つ以上の信号を含んでいる。追加信号56は、所望の任意の機能を有することができるが、これらの信号は、一般的にすべてのバス・マスター12、14に対してほぼ同時に供給すべきではなく、その代わりにバス・マスター12、14のサブセットだけにしか供給すべきでない信号である。追加信号56の1つの可能な実施例は、共用資源24の所有権を有し、この割込みに応答する必要があるバス・マスターに対してしか方向付けされ供給されるべきでない割込み信号である。本発明の他の実施形態は、追加信号ステアリング・ロジック36を使用して、これらの全体のバス・マスター（例えば、12、14）のサブセットに所望の任意の信号を方向付けすることができる。本発明の一部の実施形態では、選択された状況下において追加信号56のうちの1つ以上の信号をすべてのバス・マスター12、14に対して方向付けすることができるシナリオが存在し得ることに留意されたい。

**【 0 0 1 6 】**

追加信号ステアリング・ロジック36は、信号51を介して共用資源24に対して双方に結合される。信号51は、追加信号56の方向付けにおいて使用される制御情報および／またはステータス情報を提供するために使用される1つ以上の信号を含んでいる。本発明の代替実施形態は、任意のタイプの信号を使用して、この制御情報および／またはステータス情報を伝えることができる。すべての必要な制御情報および／またはステータス情報は、追加信号ステアリング・ロジック36中に存在し、あるいは別の方法で追加信号ステアリング・ロジック36に対して与えられるので、本発明の一部の実施形態は、信号51を必要としないこともある。

**【 0 0 1 7 】**

本発明の一部の実施形態においては、追加信号ステアリング・ロジック36によって実施されるステアリング機能のすべてまたは一部分は、共用資源それ自体の一部分として含めることができる。例えば、図1に示す実施形態において、信号101および102についてのステアリング機能は、USB共用資源100内の回路によって実施され、したがって信号101および102は、追加信号ステアリング・ロジック36を通過させて正しいバス・マスター12、14に対して方向付けする必要はない。図1に示す本発明の実施形態においては、信号101を使用して、例えば割込みなどの1つ以上の追加信号をバス・マスター12に対して供給することができる。同様に、信号102を使用して、例えば割込みなどの1つ以上の追加信号をバス・マスター14に対して供給することができる。本発明の代替実施形態は、信号101および102を追加信号ステアリング・ロジック36に供給して、信号101および102をそれぞれ信号53および52を介してこの正しいバス・マスター12、14に方向付けすることができる。

**【 0 0 1 8 】**

本発明のこの例示の実施形態においては、非共用資源22は、バス・マスター12によってしかアクセスされず、したがって、非共用資源22に関連するこれらの追加信号は、信号54を介して直接にバス・マスター12に双方向に結合される。信号54は、そもそも1つのバス・マスター12に対してしか供給されないので、信号54は、追加信号ステアリング・ロジック36によって方向付けする必要はない。同様に、本発明のこの例示の実施形態においては、非共用資源26は、バス・マスター14によってしかアクセスされず、したがって、非共用資源26に関連するこれらの追加信号は、信号55を介して直接にバス・マスター14に双方向に結合される。信号55は、そもそも1つのバス・マスター14に対してしか供給されないので、信号55は、追加信号ステアリング・ロジック36によって方向付けする必要はない。

**【 0 0 1 9 】**

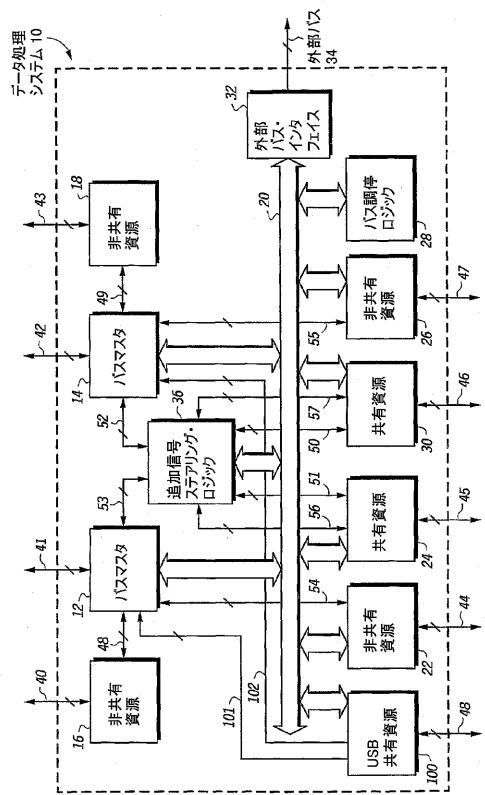

図2は、本発明の1実施形態による、図1の追加信号ステアリング・ロジック36の一

10

20

30

40

50

部分をブロック図形式で示している。この例示の実施形態において、追加信号ステアリング・ロジック36は、信号56および57についての実際のステアリング機能を実施するステアリング回路60を含んでいる。信号56および57は、信号53を介してバス・マスター12へ、または信号52を介してバス・マスター14へと方向付けすることができる。信号50および51は、それぞれ共用資源30および24からの情報を提供する。制御回路62に提供され、または記憶される他の制御情報と一緒に信号50および51を使用して、ステアリング回路60によって実施されるステアリング機能を制御する。

#### 【0020】

制御回路62は、レジスタ70を含んでいる。本発明の1実施形態においては、レジスタ70は、ステアリング・モード・セレクタ・レジスタ71、ステアリング・マップ・セレクタ・レジスタ72、マップ定義レジスタ73、マップ定義レジスタ74、および資源所有権レジスタ75を含んでいる。本発明の代替実施形態は、より多くの、より少ない、または異なるレジスタを使用して、ステアリング回路60を制御するための制御情報の一部分を提供することができる。本発明の1実施形態においては、レジスタ70の一部またはすべては、バス・マスター12および14のうちの少なくとも一方によって読み取り、書き込むことができるソフトウェア・プログラマブル・レジスタである。

#### 【0021】

所望の任意の経路指定スキームは、追加信号56および57をこれら所望の1つ以上のバス・マスター12、14に対して方向付けするために使用することができる。しかし、本発明のこの例示の実施形態においては、共用資源24、20ごとの少なくとも1つのステアリング・モード・セレクタ・レジスタ71、共用資源24、20ごとの少なくとも1つのステアリング・マップ・セレクタ・レジスタ72が存在し、また少なくとも1つのマップ定義レジスタ73、74が存在する。各ステアリング・モード・セレクタ・レジスタ71を使用して、その対応する共用資源24、30についての複数のステアリング・モードのうちの1つを選択することができる。この選択されたステアリング・モードは、次いでマップ定義レジスタ73、74のうちの一方に記憶されたマップ定義の使用を必要として、どの1つ以上のバス・マスター12、14が、ステアリング回路60によって方向付けされる信号を受け取るべきかを決定することができる。各ステアリング・マップ・セレクタ・レジスタを使用して、複数のマップ定義レジスタ73、74のうちの一方を選択することができる。

#### 【0022】

本発明の1実施形態においては、追加信号56および57は、選択されているステアリング・モードに応じて、またオプションとしてマップ定義レジスタ73、74に記憶されるマップ定義に応じて、複数の方法でバス・マスター12、14に経路指定することができる。例えば、1つのステアリング・モードは、この追加信号（例えば、56）を方向付けすることができ、その結果、この追加信号は、この共用資源（例えば、24）の所有権を現在有するバス・マスター（例えば、12）に供給される。マップ定義レジスタは、このステアリング・モードでは、必要とされない。第2のステアリング・モードは、追加信号56、57を方向付けすることができ、その結果、この追加信号は、マップ定義レジスタ73、74の一方に記憶されるプログラマブル経路指定マップによって決定されるように1つ以上のバス・マスター12、14に供給される。このプログラマブル経路指定マップは、1つ以上のバス・マスター12、14によってプログラムすることができる。本発明の一部の実施形態においては、共用資源24、30の所有権を有するマスターしか、共用資源24、30に対応するマップ定義レジスタ73、74に書き込むことができず、したがってこれらを変更することができない。本発明の代替実施形態は、1つ以上のマップ定義のプログラミングを異なった方法で制御することができる。

#### 【0023】

第3のステアリング・モードは、この追加信号（56または57のうちの一方）を方向付けすることができ、その結果、この追加信号は、マップ定義レジスタ73、74に記憶される複数のプログラマブル経路指定マップのうちの1つによって決定されるように、1

10

20

30

40

50

つ以上のバス・マスタ 12、14 に供給される。このプログラマブル経路指定マップは、どちらのバス・マスタ 12、14 が、追加信号 56、57 を供給し、またはこれらの追加信号に関連する共用資源 24、30 の所有権を現在有するかに基づいて選択することができる。本発明の一部の実施形態においては、共用資源 24、30 の所有権を有するバス・マスタしか、この共用資源 24、30 に対応するマップ定義レジスタ 73、74 に書き込むことができず、したがってこれらを変更することができない。本発明の代替実施形態は、1つ以上のマップ定義のプログラミングを異なった方法で制御することができる。

#### 【0024】

第 4 のステアリング・モードは、この追加信号（56 または 57 のうちの一方）を方向付けすることができ、その結果、この追加信号は、マップ定義レジスタ 73、74 に記憶される複数のプログラマブル経路指定マップのうちの 1 つによって決定されるように、1 つ以上のバス・マスタ 12、14 に供給される。このプログラマブル経路指定マップは、追加信号 56、57 を供給し、またはこれらの追加信号に関連する共用資源 24、30 の現在の状態に基づいて選択することができる。本発明の一部の実施形態においては、マップ定義レジスタ 73、74 は、共用資源 24、30 のいくつかの状態のそれぞれに対応する静的マップとすることができます。本発明の他の実施形態においては、マップ定義レジスタ 73、74 は、1 つ以上のバス・マスタ 24、30（例えば、この所有しているマスター）によってプログラム可能とすることもできる。本発明の一部の実施形態においては、共用資源 24、30 の所有権を有するバス・マスタしか、この共用資源 24、30 に対応するマップ定義レジスタ 73、74 に書き込むことができず、したがってこれらを変更することができない。本発明の代替実施形態は、1 つ以上のマップ定義のプログラミングまたは確立を異なった方法で制御することができる。

#### 【0025】

第 5 のステアリング・モードは、この追加信号（56 または 57 のうちの一方）を方向付けすることができ、その結果、この追加信号は、マップ定義レジスタ 73、74 に記憶される複数のプログラマブル経路指定マップのうちの 1 つによって決定されるように、1 つ以上のバス・マスタ 12、14 に供給される。このプログラマブル経路指定マップは、追加信号 56、57 を供給し、またはこれらの追加信号に関連する共用資源 24、30 によって選択することができる。本発明の一部の実施形態においては、共用資源 24、30 それ自体しか、この共用資源 24、30 に対応するマップ定義レジスタ 73、74 に書き込むことができず、したがってこれらを変更することができない。本発明の代替実施形態は、1 つ以上のマップ定義のプログラミングを異なった方法で制御することができる。

#### 【0026】

本発明の代替実施形態では、ステアリング回路 60 を制御するために使用される制御回路 62 についての所望の任意の構成を使用することができる。制御回路 62 の代替実施形態は、レジスタを有さなくともよく、あるいは、より少ない、より多くの、または異なるレジスタ 70 を有していてもよい。制御回路 62 は、信号 61 を介してステアリング回路 60 に双方向に結合される。制御回路 62 は、バス 20 に双方向に結合され、その結果、レジスタ 70 は、例えば 1 つ以上のバス・マスタ 12、14 によって読み取り、書き込むことができる。本発明の 1 実施形態においては、信号 50、51 は、どの共用資源 24、30 が、信号 56、57 を供給し、またはこれらの信号に関連するか、どのステアリング・モードを使用するか、またどのマップ定義を使用するかに関連する情報を提供する。本発明の代替実施形態においては、信号 50、51 は、どの共用資源 24、30 が、信号 56、57 を供給し、またはこれらの信号に関連するかに関する情報を提供し、レジスタ 70 を使用して、このステアリング・モード情報およびマップ定義情報の残りをステアリング回路 60 に提供する。

#### 【0027】

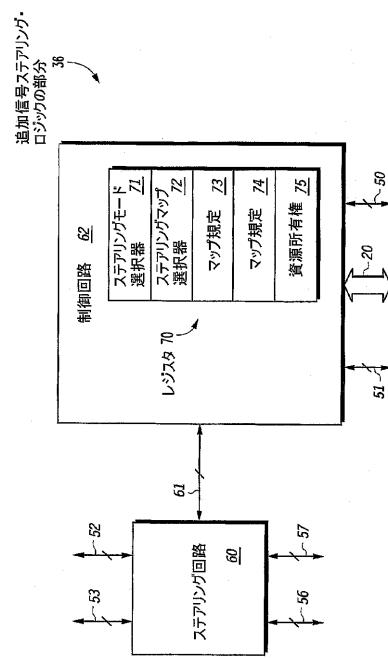

図 3 は、他の回路と一緒に、本発明の 1 実施形態による、図 1 の共用資源 24 の一部分をロック図形式で示している。本発明のこの例示の実施形態において、共用資源 24 は、バス 20 に双方向に結合されたバス・インタフェイス 310 を含んでいる。バス・イン

10

20

30

40

50

タフェイス 310 は、導体 320 によって再構成可能制御ロジック 304 に双方向に結合され、導体 326 によって再構成可能チャネル・ストレージ回路 300 に双方向に結合され、その結果、304 および 300 内のレジスタおよび他の回路は、バス 20 を介して読み取りアクセス可能および / または書き込みアクセス可能とすることができる。1 実施形態においては、再構成可能チャネル・ストレージ回路 300 は、再構成可能チャネル・ストレージ回路 301 ~ 303 を含んでいる。本発明の代替実施形態は、再構成可能チャネル・ストレージ回路 300 内に、より少ない、より多い、または同じ数の再構成可能チャネル・ストレージ回路 301 ~ 303 を有していてもよい。再構成可能チャネル・ストレージ回路 300 は、導体 322 を介して再構成可能制御ロジック 304 に双方向に結合される。本発明の 1 実施形態においては、信号 322 を使用して、再構成可能チャネル・ストレージ回路 300 と再構成可能制御ロジック 304との間で、制御情報および / またはステータス情報を転送する。再構成可能チャネル・ストレージ回路 300 は、信号 328 を介して再構成可能チャネル回路 312 に双方向に結合される。再構成可能チャネル回路 312 は、導体 324 を介して、再構成可能制御ロジック 304 に双方向に結合される。再構成可能チャネル回路 312 は、導体 45 を介してバス 330 に双方向に結合される。

10

20

30

#### 【0028】

図 3 に示す本発明の実施形態においては、ペリフェラル機能回路 306 ~ 308 ごとに 1 つの再構成可能チャネル・ストレージ回路 301 ~ 303 が存在する。本発明の代替実施形態は、ペリフェラル機能回路 306 ~ 308 ごとに任意数の再構成可能チャネル・ストレージ回路 301 ~ 303 を有することもできる。各ペリフェラル機能回路 306 ~ 308 は、例えば、タイマ機能、通信機能、変換機能、データ処理機能、ストレージ機能など、1 つ以上の任意タイプの所望の機能を実施することができる。さらに、本発明の一部の実施形態においては、再構成可能チャネル回路 312 は、再構成可能回路を含んでいて、例えば、タイマ機能、通信機能、変換機能、データ処理機能、ストレージ機能など、1 つ以上の任意タイプの所望の機能を実施する。したがって、機能を実施する回路は、( 例えば、再構成可能チャネル回路 312 中に配置することができる ) 共用資源 24 と同じ集積回路上に配置することもでき、あるいは代わりに( 例えば、任意のペリフェラル機能回路 306 ~ 308 中に配置することができる ) 共用資源 24 を組み込んでいる集積回路の外側に配置することもできる。

30

#### 【0029】

図 3 に示す本発明の実施形態においては、再構成可能制御ロジック 304 を使用して、追加信号ステアリング・ロジック 36 ( 図 1 参照 ) に対して信号 56 および信号 51 を供給する。また再構成可能制御ロジック 304 を使用して、バス・マスター 12、14 のうちの一方から 1 つ以上のペリフェラル機能回路 306 ~ 308 に対して使用される通信経路を決定し、または選択する。この通信経路は、バス 20、バス・インターフェイス 310、再構成可能チャネル・ストレージ回路 301 ~ 303 のうちの 1 つ ( どの 1 つかは再構成可能制御ロジック 304 によって決定される ) 、再構成可能チャネル回路 312、信号 45、およびバス 330 を使用する。

40

#### 【0030】

本発明の 1 実施形態においては、再構成可能チャネル回路 312 を使用して、再構成可能チャネル・ストレージ回路 300 とペリフェラル機能回路 306 ~ 308 の間の通信経路を決定し、または選択することに留意されたい。本発明の一部の実施形態においては、再構成可能チャネル回路 312 は、再構成可能制御ロジック 304 を介してプログラムされる。本発明の代替実施形態においては、再構成可能チャネル回路 312 は、バス・インターフェイス 310 を介してバス・マスター 12 または 14 によってプログラムすることができる。本発明の一部の実施形態においては、再構成可能チャネル・ストレージ回路 300 は、再構成可能制御ロジック 304 によって再構成することができるストレージ回路としてもっぱら機能することができる。同様に再構成可能チャネル回路 312 は、この機能が、再構成可能制御ロジック 304 によって選択可能な所望の機能を実施するようにもっぱら機能することもできる。本発明の代替実施形態は、共用資源 24 のストレージ部分、機

50

能部分、および制御部分をどのような方法でも、パーティションに区分することができる。本発明の代替実施形態は、再構成可能チャネル回路312を使用することができます、その代わりに再構成可能制御ロジック304を直接に使用して、再構成可能チャネル・ストレージ回路300とペリフェラル機能回路306～308の間の通信経路を決定し、または選択することができることに留意されたい。

### 【0031】

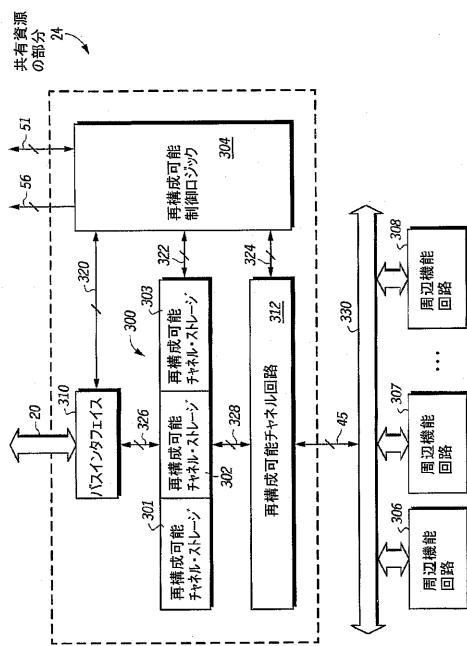

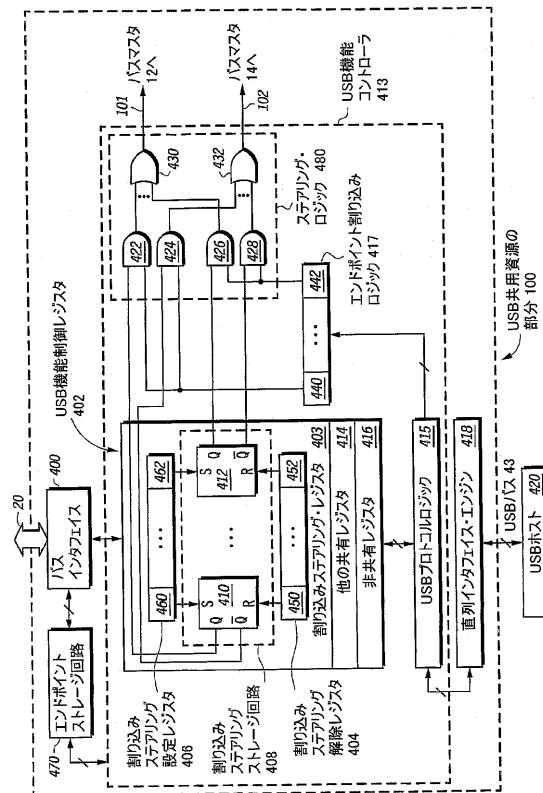

図4は、他の回路と一緒に、本発明の1実施形態による、図1のUSB共用資源100の一部分をブロック図形式で示している。1実施形態においては、USB共用資源100は、ユニバーサル・シリアル・バス(USB)規格に準拠し、USBバス43を介してUSBホスト420と情報をやりとりする。USB共用資源100はまた、バス20にも結合される。図4に示す本発明の実施形態においては、USB共用資源100は、エンドポイント・ストレージ回路470およびバス・インターフェイス400に双方向に結合されるUSB機能コントローラ413を含んでいる。バス・インターフェイス400は、エンドポイント・ストレージ回路470に双方向に結合され、バス20に双方向に結合される。本発明の1実施形態においては、USB機能コントローラ413は、USBプロトコル・ロジック415を介してシリアル・インターフェイス・エンジン418に双方向に結合される。シリアル・インターフェイス・エンジン418は、USBバス43に双方向に結合される。

### 【0032】

本発明の1実施形態においては、USB機能コントローラ413は、USBプロトコル・ロジック415に結合される複数のUSB機能制御レジスタ402を含んでいる。USBプロトコル・ロジック415は、エンドポイント割込みロジック417に結合されて、いつ割込みをバス・マスター12、14に提供すべきかに関する割込み情報を提供する。ステアリング・ロジック480は、エンドポイント割込みロジック417およびUSB機能制御レジスタ402からの情報を受け取り、それに応答して割込み信号101および102をそれぞれバス・マスター12および14に提供する。追加信号ステアリング・ロジック36を使用してどのバス・マスター12、14がどの追加信号を受け取るかを決定する共用資源24(図1参照)と違って、USB共用資源100は、このステアリング機能を実施するための回路を含んでいる。その結果、信号101および102は、追加信号ステアリング・ロジック36によって実現されるこのステアリング機能は、USB共用資源100内で実施される。

### 【0033】

本発明の1実施形態においては、ステアリング・ロジック480は、それぞれ、1入力がUSB機能制御レジスタ402に結合され、1入力がエンドポイント割込みロジック417に結合されているANDゲート422、424、426、および428を含んでいる。ステアリング・ロジック480はまた、ANDゲート422、424、426、および428からの入力を受け取り、出力101および102をそれぞれバス・マスター12、14に供給する複数のORゲート430、432も含んでいる。

### 【0034】

本発明の1実施形態においては、各エンドポイントは、対応するビット460または462、対応するラッチ410または412、対応するビット450または452、およびエンドポイント割込みロジックの対応する一部分440または442を有する。図4に示す特定の回路は、単に例示の目的で示されているにすぎないことに留意されたい。本発明の代替実施形態では、適切な任意の回路を使用して、USB機能コントローラ413によって必要とされるステアリング機能を実装することができる。

### 【0035】

本発明の1実施形態においては、USB機能制御レジスタ402は、割込みステアリング・レジスタ403、他の共用レジスタ414、および非共用レジスタ416を含んでいる。本発明の1実施形態においては、割込みステアリング・レジスタ403は、割込みス

10

20

30

40

50

テアリング・ストレージ回路408に結合されて、セット信号およびリセット信号を供給して、それぞれラッチ410、412をセット/リセットする割込みステアリング・セット・レジスタ406および割込みステアリング・クリア・レジスタ404を含んでいる。本発明の代替実施形態は、割込みステアリング・レジスタ403を実装するために使用される方法と同様にしてセット・レジスタ、クリア・レジスタ、および複数のセット/リセット・ラッチを使用して実装される複数の他の共用レジスタ414を含むことができる。

#### 【0036】

共用レジスタ403および414、エンドポイント割込みロジック417、ならびにステアリング・ロジック480の使用を介して、USB機能コントローラ413は、マルチマスター・システム中のエンドポイントの共用制御を可能にする機能を有することに留意されたい。図1に示すマルチマスター・システムは、2つのバス・マスター12、14を使用しているが、本発明の代替実施形態は、データ処理システム10の外部にあるバス・マスターを含めて、任意数または任意タイプのバス・マスターを使用することもできる。

#### 【0037】

次にUSB共用資源100の機能について、さらに詳細に説明することにする。USBプロトコル・ロジック415は、シリアル・インターフェイス・エンジン418に対してデータを提供し、またそこからデータを受け取る。シリアル・インターフェイス・エンジン418は、USBホスト420に対してデータを提供し、そこからデータを受け取り、このUSB規格に従って機能する。

#### 【0038】

本発明の1実施形態においては、USB共用資源100は、所有されていない共用資源であると考えられる。しかし、USB共用資源100は、パーティションに区分され、その結果、1つ以上の部分（例えば、USBエンドポイント）を異なるバス・マスター12および14に割り付けることができる。本発明の1実施形態においては、これらのUSBエンドポイントは、エンドポイント・ストレージ回路470に記憶することができる。本発明の1実施形態においては、割込みステアリング・レジスタ403を追加して、エンドポイント割込みを複数のバス・マスター12、14のうちの一方に方向付けしている。

#### 【0039】

本発明のこの例示の実施形態においては、割込みステアリング・レジスタ403は、割込みステアリング・セット・レジスタ406、割込みステアリング・クリア・レジスタ404、および割込みステアリング・ストレージ回路408を使用して実装されている。この例示の実施形態においては、バス・マスター12、14の選択を指定してこの割込みを受け取る2つのロジック状態しか使用可能ではない。したがって、この例示の実施形態では、エンドポイント割込みは、たった2つのバス・マスター12、14のうちの1つに対してしか方向付けすることができない。しかし、本発明の代替実施形態は、割込みステアリング・レジスタ403を実装することができ、その結果、エンドポイント割込みを複数のバス・マスターに対して方向付けすることができる。本発明のこの例示の実施形態においては、割込みステアリング・セット・レジスタ406も割込みステアリング・クリア・レジスタ404も共に、このメモリ・マップ/プログラマのモデル中のレジスタであり、バス20およびバス・インターフェイス400を介して書き込むことができることに留意されたい。レジスタ406および404の読み取りは、本発明のこの例示の実施形態においては、使用されないが、本発明の代替実施形態は、所望のどのような方法でもレジスタ406および404の読み取りを扱うことができることに留意されたい。

#### 【0040】

本発明の1実施形態においては、バス・マスター12も14も共に、共用レジスタ414および割込みステアリング・レジスタ403に書き込み、これらを修正することができる。これは、レジスタ414および403の内容の破損をもたらすこともあることに留意されたい。このメモリ・マップ/プログラマのモデル中の一意のアドレスに配置される別の割込みステアリング・セット・レジスタ406の使用と、このメモリ・マップ中の異なるアドレスに配置される別の割込みステアリング・クリア・レジスタ404の使用により、

10

20

30

40

50

複数のバス・マスタ 12、14は、レジスタ 403 中の非選択ビットに影響を及ぼすことなく、レジスタ 403 中の選択されたビットを独立にセットし、またはクリアすることができるようになる。本発明の一部の実施形態では、1つ以上の他の共用レジスタ 414 をレジスタ 403 と同様にして（すなわち、別々のセット・レジスタおよびクリア・レジスタ 406、404 を使用して）実装することができることに留意されたい。例えば、エンドポイント・オペレーションに関連した他の共用レジスタ 414 のすべてまたは一部分は、レジスタ 403 と同様にして実装することができる。本発明の代替実施形態は、レジスタ 401、および1つ以上のレジスタ 414 の内容の破損を回避する異なるメカニズムを使用することもできる。かかるメカニズムの1実施例は、レジスタ 402 および 414 に対する原子読み取り修正書き込みアクセス（atomic read-modify-write access）である。

#### 【0041】

本発明のこの例示の実施形態において、ビット 460 に対する「1」の書き込みは、対応するラッチ 410 をセットすることになり、ビット 460 に対する「0」の書き込みは、ラッチ 410 に対して影響を及ぼさないことになる。同様に、ビット 450 に対する「1」の書き込みは、対応するラッチ 410 をクリアすることになり、ビット 450 に対する「0」の書き込みは、ラッチ 410 に対して影響を及ぼさないことになる。このメカニズムは、バス・マスタ 12 とバス・マスタ 14 の両方によるレジスタ 403 のビットごとの制御を可能にすることに留意されたい。USB 共用資源 100 を使用した一部の用途では、バス・マスタ 12 は、レジスタ・ビット 403 の一部分をセットすることになり、バス・マスタ 14 は、レジスタ・ビット 403 のオーバーラップしていない異なる部分をクリアすることになる。この場合には、レジスタ 403 のビット中の「1」は、この対応するエンドポイント割込みをバス・マスタ 12 へと方向付けし、レジスタ 403 のビット中の「0」は、この対応するエンドポイント割込みをバス・マスタ 14 へと方向付けする。

#### 【0042】

本発明の1実施形態では、非共用レジスタ 416 は、複数のバス・マスタ 12、14 を用いて適切に動作するように修正する必要はない。例えば、非共用レジスタ 416 中のあるレジスタは、読み取り専用にすることができ、非共用レジスタ 416 中の他のレジスタは、所定のソフトウェア規定によって指定されるように1つのバス・マスタ 12、14 によってアクセスすることができる。

#### 【0043】

本発明の1実施形態においては、USB プロトコル・ロジック 415 およびエンドポイント割込みロジック 417 は、複数のマスタ使用のために修正する必要はない。しかし、エンドポイント割込みロジック 417 によって提供されるこれらの割込み出力は、今やレジスタ 403 の対応するビットによって指定されるバス・マスタへとステアリング・ロジック 480 によって方向付けされる必要がある。ステアリング・ロジック 480 は、どのような方法でも実装することができ、図 4 に示す回路は、ただステアリング・ロジック 480 の1つの可能性のある実装形態にすぎない。1つのバス・マスタ（例えば 12 または 14）しか、USB 共用資源 100 を利用していなかった場合には、ステアリング・ロジック 480 は、必要とされないはずであることに留意されたい。この場合には、すべての割込みがこの1つのバス・マスタに進むはずなので、方向付けは必要とされないはずである。

#### 【0044】

図 4 に示す残りの回路は、標準の USB 回路と同様にして機能することができる。

前述の明細書では、特定の実施形態について本発明を説明している。しかし、添付の特許請求の範囲で述べる本発明の範囲を逸脱することなく、様々な修正および変更を行うことができることが、当業者には理解されよう。したがって、この明細書および図面は、限定的な意味ではなくて例示的な意味で考慮すべきであり、すべてのかかる修正形態は、本発明の範囲内に含めるべきであることが意図されている。

#### 【0045】

10

20

30

40

50

利点、他の長所、および問題に対する解決法について、特定の実施形態に関して以上で説明してきている。しかし、どのような利点、長所、または解決方法をも引き起こし、より明確になるようにさせ得るこれらの利点、長所、問題に対する解決法、および1つ（または複数）のどのような要素も、任意の請求項またはすべての請求項の重要な、必要な、あるいは必須の特徴または要素として解釈すべきではない。本明細書中で使用しているように、用語「からなる（含む）（comprises）」、「からなる（含む）（comprising）」またはこの任意の他の変形は、要素のリストを含む工程、方法、物、または装置が、これらの要素を含むだけでなく、かかる工程、方法、物、または装置に明示的にリストアップされない、または固有の他の要素も含むことができるよう、非排他的包含を範囲に含むことを意図している。

10

## 【0046】

追加テキスト(1)

〔請求項1〕 システム・バスと、

該システム・バスに結合された第1のバス・マスタと、

該システム・バスに結合された第2のバス・マスタと、

該システム・バスに結合され、該第1のバス・マスタおよび該第2のバス・マスタのうちの少なくとも一方のバス・マスタによって所有されるように構成可能な資源と、

該資源と、該第1のバス・マスタおよび該第2のバス・マスタのうちの少なくとも一方のバス・マスタとの間で、該資源の所有権に基づいて通信経路を確立する追加信号ステアリング・ロジックと、

からなり、該通信経路を使用して、該資源と、該第1のバス・マスタおよび該第2のバス・マスタのうちの該少なくとも一方のバス・マスタとの間で、少なくとも1つの追加信号を転送するデータ処理システム。

20

## 【0047】

〔請求項2〕 前記データ処理システムが、前記資源の所有権を示す資源所有権ストレージ回路をさらに備える、請求項1に記載のデータ処理システム。

〔請求項3〕 前記資源所有権ストレージ回路は、前記第1のバス・マスタが前記資源を所有するかどうか、前記第2のバス・マスタが前記資源を所有するかどうか、および前記第1のバス・マスタも前記第2のバス・マスタも前記資源を所有しないかどうかのうちの少なくとも1つを示す、請求項2に記載のデータ処理システム。

30

## 【0048】

〔請求項4〕 前記第1のバス・マスタも前記第2のバス・マスタも共に前記資源の所有権を請求するときに、前記資源所有権ストレージ回路は、前記資源が所有されていないことを示す、請求項2に記載のデータ処理システム。

## 【0049】

〔請求項5〕 前記第1のバス・マスタも前記第2のバス・マスタも前記資源の所有権を請求しないときに、前記資源所有権ストレージ回路は、前記資源が所有されていないことを示す、請求項2に記載のデータ処理システム。

40

## 【0050】

〔請求項6〕 前記追加信号ステアリング・ロジックが、前記資源所有権ストレージ回路内に記憶される情報に基づいて前記通信経路を確立する、請求項2に記載のデータ処理システム。

## 【0051】

〔請求項7〕 前記追加信号ステアリング・ロジックが、前記資源と、前記第1のバス・マスタおよび前記第2のバス・マスタのうちの一方のバス・マスタだけとの間で前記通信経路を確立する、請求項1に記載のデータ処理システム。

50

## 【0052】

〔請求項8〕 前記追加信号ステアリング・ロジックが、前記資源と、前記第1のバス・マスタおよび前記第2のバス・マスタのうちのそれぞれとの間で前記通信経路を確立する、請求項1に記載のデータ処理システム。

## 【0053】

〔請求項9〕 前記少なくとも1つの追加信号が、前記システム・バスの一部分ではない、請求項1に記載のデータ処理システム。

〔請求項10〕 前記システム・バスが、システム・バス・プロトコルに従って動作し、前記少なくとも1つの追加信号が、該システム・バス・プロトコルの外側で動作する、請求項1に記載のデータ処理システム。

## 【0054】

〔請求項11〕 前記資源からなるペリフェラルをさらに含む、請求項1に記載のデータ処理システム。

〔請求項12〕 前記ペリフェラルが、第2の資源からなり、前記追加信号ステアリング・ロジックが、該第2の資源に関連する少なくとも1つの追加信号を転送するために、該第2の資源と、前記第1のバス・マスタおよび前記第2のバス・マスタのうちの少なくとも一方のバス・マスタとの間で該第2の資源の所有権に基づいて第2の通信経路を確立する、請求項11に記載のデータ処理システム。 10

## 【0055】

〔請求項13〕 前記システム・バスに結合された第2の資源をさらに含み、前記追加信号ステアリング・ロジックが、該第2の資源に関連する少なくとも1つの追加信号を転送するために、該第2の資源と、前記第1のバス・マスタおよび前記第2のバス・マスタのうちの少なくとも一方のバス・マスタとの間で該第2の資源の所有権に基づいて第2の通信経路を確立する、請求項1に記載のデータ処理システム。 20

## 【0056】

〔請求項14〕 前記追加信号ステアリング・ロジックが、前記資源と、前記第1のバス・マスタおよび前記第2のバス・マスタのうちの、前記資源を所有している所有するバス・マスタとの間で通信経路を確立する、請求項1に記載のデータ処理システム。

## 【0057】

〔請求項15〕 前記追加信号ステアリング・ロジックが、マップ定義を記憶するマップ・ストレージ回路からなり、前記追加信号ステアリング・ロジックが、該マップ定義に基づいて前記通信経路を確立する、請求項1に記載のデータ処理システム。 30

## 【0058】

〔請求項16〕 前記マップ定義が、前記第1のバス・マスタおよび前記第2のバス・マスタのうちの、前記資源を所有している所有するバス・マスタによってプログラム可能である、請求項15に記載のデータ処理システム。

## 【0059】

〔請求項17〕 前記マップ・ストレージ回路が、複数のマップ定義を記憶し、前記追加信号ステアリング・ロジックが、前記資源の所有権に基づいて選択される該複数のマップ定義のうちの1つのマップ定義に基づいて前記通信経路を確立する、請求項15に記載のデータ処理システム。 40

## 【0060】

〔請求項18〕 前記複数のマップ定義のうちの前記1つのマップ定義は、前記第1のバス・マスタが前記資源を所有するかどうか、前記第2のバス・マスタが、前記資源を所有するかどうか、および前記資源が所有されないかどうかのうちの少なくとも1つに基づいて選択される、請求項17に記載のデータ処理システム。

## 【0061】

〔請求項19〕 前記資源が、前記追加信号ステアリング・ロジックの少なくとも一部分からなる、請求項1に記載のデータ処理システム。

〔請求項20〕 システム・バスを有するデータ処理システムにおいて追加信号を伝えるための方法であって、

該システム・バスに結合された資源と、該システム・バスに結合された複数のバス・マスタのうちの少なくとも1つのバス・マスタとの間で該資源の所有権に基づいて通信経路を確立すること、および 50

該資源と、該複数のバス・マスタのうちの該少なくとも1つのバス・マスタとの間で、該通信経路を介して該システム・バスとは別の該追加信号を転送すること、からなる方法。

## 【0062】

〔請求項21〕 前記通信経路を確立することが、前記複数のバス・マスタから、前記資源を所有している所有するバス・マスタを決定すること、および前記資源と、該所有するバス・マスタとの間で前記通信経路を確立すること、からなる、請求項20に記載の方法。

## 【0063】

〔請求項22〕 前記通信経路を確立することが、前記資源が前記複数のバス・マスタのうちのどれかによって所有されないときに、前記資源と、前記バス・マスタのうちの前記少なくとも1つのバス・マスタとの間で前記複数のバス・マスタのうちの第1のバス・マスタによって定義されるマップ定義に基づいて前記通信経路を確立することをさらに含む、請求項21に記載の方法。

## 【0064】

〔請求項23〕 前記通信経路を確立することが、前記資源と、前記複数のバス・マスタのうちの前記少なくとも1つのバス・マスタの間で、前記複数のバス・マスタのうちの、前記資源を所有している所有するバス・マスタによって定義されるマップ定義に基づいて前記通信経路を確立することからなる、請求項20に記載の方法。

## 【0065】

〔請求項24〕 前記通信経路を確立することが、前記資源の所有権に基づいて複数のマップ定義のうちの1つのマップ定義を選択すること、および前記資源と、前記複数のバス・マスタのうちの前記少なくとも1つのバス・マスタとの間で、該複数のマップ定義のうちの該選択される1つのマップ定義に基づいて前記通信経路を確立すること、からなる、請求項20に記載の方法。

## 【0066】

〔請求項25〕 システム・バスと、該システム・バスに結合された第1のバス・マスタと、該システム・バスに結合された第2のバス・マスタと、該システム・バスに結合され、該第1のバス・マスタおよび該第2のバス・マスタによって使用可能であり、該第1のバス・マスタおよび該第2のバス・マスタのうちの少なくとも一方のバス・マスタによって所有されるように構成可能な資源と、該資源と、該第1のバス・マスタおよび該第2のバス・マスタのうちの少なくとも一方のバス・マスタとの間で、通信経路を確立する追加信号ステアリング・ロジックと、からなり、該通信経路を使用して、該資源と、該第1のバス・マスタおよび該第2のバス・マスタのうちの該少なくとも一方のバス・マスタとの間で、少なくとも1つの追加信号を転送し、該通信経路が、該資源によって決定されるデータ処理システム。

## 【0067】

〔請求項26〕 前記通信経路が、前記資源の現在の状態によって決定される、請求項25に記載のデータ処理システム。

〔請求項27〕 前記資源の前記現在の状態が、前記資源の動作モードからなる、請求項26に記載のデータ処理システム。

## 【0068】

〔請求項28〕 前記通信経路が、前記資源によって定義されるマップ定義に基づいて決定される、請求項25に記載のデータ処理システム。

〔請求項29〕 前記追加信号ステアリング・ロジックが、前記マップ定義を記憶するマップ定義ストレージ回路からなる、請求項28に記載のデータ処理システム。

10

20

30

40

50

## 【0069】

〔請求項30〕 前記追加信号ステアリング・ロジックが、前記資源と、前記第1のバス・マスタと前記第2のバス・マスタの両方との間で、前記通信経路を確立する、請求項25に記載のデータ処理システム。

## 【0070】

〔請求項31〕 前記少なくとも1つの追加信号が、前記システム・バスの一部分ではない、請求項25に記載のデータ処理システム。

〔請求項32〕 前記システム・バスが、システム・バス・プロトコルに従って動作し、前記少なくとも1つの追加信号が、該システム・バス・プロトコルの外側で動作する、請求項25に記載のデータ処理システム。

10

## 【0071】

〔請求項33〕 前記資源が、前記追加信号ステアリング・ロジックの少なくとも一部分からなる、請求項25に記載のデータ処理システム。

〔請求項34〕 システム・バスを有するデータ処理システムにおいて追加信号を伝えるための方法であって、

該システム・バスに結合された資源と、該システム・バスに結合された複数のバス・マスタのうちの少なくとも1つのバス・マスタとの間で、該資源によって決定される通信経路を確立すること、および

該資源と、該複数のバス・マスタのうちの該少なくとも1つのバス・マスタとの間で、該通信経路を介して該システム・バスとは別の該追加信号を転送すること、

からなる方法。

20

## 【0072】

〔請求項35〕 前記通信経路を確立することが、

前記資源の現在の状態を決定すること、および

前記資源の該現在の状態に基づいて前記通信経路を確立すること、

からなる、請求項34に記載の方法。

30

## 【0073】

〔請求項36〕 前記通信経路を確立することが、

前記資源によって定義されるマップ定義を提供すること、および

該マップ定義に基づいて前記通信経路を確立すること、

からなる、請求項34に記載の方法。

40

## 【0074】

追加テキスト(2)

〔請求項1〕 第1のバス・マスタと、

第2のバス・マスタと、

該第1のバス・マスタおよび該第2のバス・マスタによりアクセス可能な共用再構成可能資源と、

からなり、該共用再構成可能資源が、該第1のバス・マスタおよび該第2のバス・マスタのうちの少なくとも一方のバス・マスタと、複数のペリフェラル機能から選択される第1のペリフェラル機能を実施するための回路との間で、通信経路を確立するデータ処理システム。

40

## 【0075】

〔請求項2〕 前記共用再構成可能資源が、前記第1のペリフェラル機能を実施するための前記回路の少なくとも一部分からなる再構成可能チャネル回路からなる、請求項1に記載のデータ処理システム。

## 【0076】

〔請求項3〕 前記共用再構成可能資源が、前記第1のペリフェラル機能を実施する際に使用するための前記再構成可能チャネル回路によりアクセス可能な再構成可能チャネル・ストレージからなる、請求項2に記載のデータ処理システム。

50

## 【0077】

[請求項 4] 前記再構成可能チャネル回路が、前記複数のペリフェラル機能から選択される第2のペリフェラル機能を実施するように構成可能である、請求項2に記載のデータ処理システム。

【0078】

[請求項5] 前記共用再構成可能資源が、前記第1のバス・マスタおよび前記第2のバス・マスタの少なくとも一方のバス・マスタと、前記第2のペリフェラル機能を実施するための回路との間で、第2の通信経路を確立し、前記再構成可能チャネル回路が、前記第2のペリフェラル機能を実施するための該回路の少なくとも一部分からなる、請求項4に記載のデータ処理システム。

【0079】

[請求項6] 前記第2のペリフェラル機能を実施するための前記回路が、シリアル・ペリフェラル・インターフェイス(SPI)、ユニバーサル非同期式レシーバ/トランスマッタ(UART)、ユニバーサル・シリアル・バス(USB)、入力キャプチャ、出力比較、汎用入出力、タイマ、および同期式シリアル・インターフェイス(SSI)のうちの少なくとも1つからなる、請求項5に記載のデータ処理システム。

【0080】

[請求項7] 前記データ処理システムが、前記共用再構成可能資源に結合された第1のペリフェラル機能回路をさらに備え、該第1のペリフェラル機能回路が、前記第1のペリフェラル機能を実施するための前記回路の少なくとも第1の部分からなる、請求項1に記載のデータ処理システム。

【0081】

[請求項8] 前記共用再構成可能資源が、前記第1のペリフェラル機能を実施するための前記回路の少なくとも第2の部分からなる、請求項7に記載のデータ処理システム。

【0082】

[請求項9] 前記共用再構成可能資源が、前記第1のバス・マスタおよび前記第2のバス・マスタの少なくとも一方のバス・マスタと、前記複数のペリフェラル機能から選択される第2のペリフェラル機能を実施するための回路との間で、第2の通信経路を確立する、請求項8に記載のデータ処理システム。

【0083】

[請求項10] 前記データ処理システムが、前記共用再構成可能資源に結合された第2のペリフェラル機能回路をさらに備え、該第2のペリフェラル機能回路が、前記第2のペリフェラル機能を実施するための前記回路の少なくとも第1の部分からなり、前記共用再構成可能資源が、前記第2のペリフェラル機能を実施するための前記回路の少なくとも第2の部分からなる、請求項9に記載のデータ処理システム。

【0084】

[請求項11] 前記第2のペリフェラル機能を実施するための前記回路が、シリアル・ペリフェラル・インターフェイス(SPI)、ユニバーサル非同期式レシーバ/トランスマッタ(UART)、ユニバーサル・シリアル・バス(USB)、入力キャプチャ、出力比較、汎用入出力、タイマ、および同期式シリアル・インターフェイス(SSI)のうちの少なくとも1つからなる、請求項8に記載のデータ処理システム。

【0085】

[請求項12] 前記第1のペリフェラル機能を実施するための前記回路が、シリアル・ペリフェラル・インターフェイス(SPI)、ユニバーサル非同期式レシーバ/トランスマッタ(UART)、ユニバーサル・シリアル・バス(USB)、入力キャプチャ、出力比較、汎用入出力、タイマ、および同期式シリアル・インターフェイス(SSI)のうちの少なくとも1つからなる、請求項1に記載のデータ処理システム。

【0086】

[請求項13] 第1のマスタと、第1のペリフェラル機能を実施するための回路との間で、再構成可能資源を構成して第1の通信経路を確立すること、および

10

20

30

40

50

第2のマスタと、第2のペリフェラル機能を実施するための回路との間で、該再構成可能な資源を構成して第2の通信経路を確立すること、

からなり、該第1のペリフェラル機能および該第2のペリフェラル機能のそれぞれが、複数のペリフェラル機能から選択される、該再構成可能な資源を動作させるための方法。

【0087】

〔請求項14〕 前記再構成可能な資源を構成して前記第1の通信経路を確立することが、前記再構成可能な資源内でチャネル回路を構成して前記第1のペリフェラル機能を実施することからなる、請求項13に記載の方法。

【0088】

〔請求項15〕 前記再構成可能な資源を構成して前記第2の通信経路を確立することが、前記再構成可能な資源内で前記チャネル回路を構成して前記第2のペリフェラル機能を実施することからなる、請求項14に記載の方法。 10

【0089】

〔請求項16〕 前記第1のバス・マスタおよび前記第2のバス・マスタが、前記再構成可能な資源に結合された異なるマスタである、請求項15に記載の方法。

〔請求項17〕 前記第1のバス・マスタおよび前記第2のバス・マスタが、前記再構成可能な資源に結合された同じマスタである、請求項15に記載の方法。

【0090】

〔請求項18〕 前記チャネル回路を構成して前記第1のペリフェラル機能を実施すること、および前記チャネル回路を構成して前記第2のペリフェラル機能を実施することが、それぞれ前記チャネル回路に結合されたチャネル・ストレージを構成することからなる、請求項15に記載の方法。 20

【0091】

〔請求項19〕 前記第1のペリフェラル機能と、前記第2のペリフェラル機能が、同じペリフェラル機能からなる、請求項15に記載の方法。

〔請求項20〕 前記第1のペリフェラル機能と、前記第2のペリフェラル機能が、異なるペリフェラル機能からなる、請求項15に記載の方法。

【0092】

〔請求項21〕 前記複数のペリフェラル機能が、シリアル・ペリフェラル・インターフェイス(SPI)機能、ユニバーサル非同期式レシーバ/トランスマッタ(UART)機能、ユニバーサル・シリアル・バス(USB)機能、入力キャプチャ機能、出力比較機能、汎用入出力機能、タイマ機能、および同期式シリアル・インターフェイス(SSI)機能のうちの少なくとも1つからなる、請求項13に記載の方法。 30

【0093】

〔請求項22〕 複数のペリフェラル機能に関連する情報を記憶するように構成可能な再構成可能なチャネル・ストレージと、

該複数のペリフェラル機能のそれぞれを実施するように構成可能な再構成可能なチャネル回路と、

該再構成可能なチャネル・ストレージおよび該再構成可能なチャネル回路に結合された制御ロジックと、

からなり、該制御ロジックが、該再構成可能なチャネル・ストレージおよび該再構成可能なチャネル回路を構成して、該複数のペリフェラル機能のうちの選択されるペリフェラル機能を実施する共用再構成可能な資源。 40

【0094】

〔請求項23〕 前記制御ロジックが、複数のマスタのうちの少なくとも1つのマスタと、前記複数のペリフェラル機能のうちの前記選択されるペリフェラル機能を実施するための回路との間で通信経路を確立する、請求項22に記載の共用再構成可能な資源。

【0095】

〔請求項24〕 前記再構成可能なチャネル回路が、前記複数のペリフェラル機能のうちの前記選択されるペリフェラル機能を実施するための前記回路の少なくとも一部分から

50

なる、請求項 23 に記載の共用再構成可能資源。

【0096】

〔請求項 25〕 前記制御ロジックが、前記再構成可能チャネル・ストレージおよび前記再構成可能チャネル回路に対して前記複数のペリフェラル機能のうちの前記選択されるペリフェラル機能を示す、請求項 22 に記載の共用再構成可能資源。

【0097】

〔請求項 26〕 前記複数のペリフェラル機能が、第 1 のシリアル・ペリフェラル・インターフェイス (S P I) 機能、ユニバーサル非同期式レシーバ／トランスマッタ (U A R T) 機能、ユニバーサル・シリアル・バス (U S B) 機能、入力キャプチャ機能、出力比較機能、汎用入出力機能、タイマ機能、および同期式シリアル・インターフェイス (S S I) 機能からなる、請求項 22 に記載の共用再構成可能資源。10

【0098】

〔請求項 27〕 前記複数のペリフェラル機能が、第 2 のシリアル・ペリフェラル・インターフェイス (S P I) 機能、ユニバーサル非同期式レシーバ／トランスマッタ (U A R T) 機能、ユニバーサル・シリアル・バス (U S B) 機能、入力キャプチャ機能、出力比較機能、汎用入出力機能、タイマ機能、および同期式シリアル・インターフェイス (S S I) 機能からなる、請求項 26 に記載の共用再構成可能資源。

【0099】

〔請求項 28〕 前記複数のペリフェラル機能の第 1 のサブセットが、第 1 のマスタに対応し、前記複数のペリフェラル機能の第 2 のサブセットが、第 2 のマスタに対応する、請求項 22 に記載の共用再構成可能資源。20

【0100】

〔請求項 29〕 第 1 のマスタおよび第 2 のマスタと情報をやりとりするバス・インターフェイスと、

該バス・インターフェイスに結合され、各エンドポイントが、該第 1 のマスタおよび該第 2 のマスタのうちの一方に割付け可能である、複数のエンドポイントからなるエンドポイント・ストレージ回路と、

U S B ホストと情報をやりとりするシリアル・インターフェイス・エンジンと、

該バス・インターフェイス、エンドポイント・ストレージ回路、およびシリアル・インターフェイス・エンジンに結合され、30

該シリアル・インターフェイス・エンジンに結合された U S B プロトコル・ロジックと、

該 U S B プロトコル・ロジックから受け取られる情報に基づいて割込みを生成するエンドポイント割込みロジックと、

割込みステアリング・レジスタと、

該割込みステアリング・レジスタによって提供されるステアリング情報に基づいて、該第 1 のマスタおよび該バス・マスタのうちの対応する一方に該各割込みを経路指定する割込みステアリング・ロジックと、

からなる U S B 機能コントローラと、

からなる共用ユニバーサル・シリアル・バス (U S B) 資源。

【0101】

〔請求項 30〕 前記複数のエンドポイントが、前記割込みステアリング・レジスタに基づいて割り付けられる、請求項 29 に記載の共用 U S B 資源。40

〔請求項 31〕 前記複数のエンドポイントのそれぞれについて、前記割込みステアリング・レジスタが、前記第 1 のマスタおよび前記第 2 のマスタのうちの一方に対する割付けを指示する、請求項 30 に記載の共用 U S B 資源。

【0102】

〔請求項 32〕 前記割込みステアリング・レジスタが、割込みステアリング・セット・レジスタと、割込みステアリング・クリア・レジスタと、からなる、請求項 30 に記載の共用 U S B 資源。

【0103】

10

20

30

40

50

〔請求項33〕 前記割込みステアリング・レジスタが、前記割込みステアリング・セット・レジスタおよび前記割込みステアリング・クリア・レジスタに結合され、前記ステアリング情報を前記割込みステアリング・ロジックに提供する割込みステアリング・ストレージ回路をさらに含む、請求項32に記載の共用USB資源。

【0104】

〔請求項34〕 前記割込みステアリング・ストレージ回路が、複数のセット・リセット・ラッチからなる、請求項33に記載の共用USB資源。

〔請求項35〕 各エンドポイントが、複数のバス・マスターのうちの1つのバス・マスターに割付け可能である複数のエンドポイントと、

該複数のエンドポイントに結合され、

USBホストからの通信に基づいて割込みを生成するエンドポイント割込みロジックと、

該複数のバス・マスターによりアクセス可能な少なくとも1つの割込みステアリング・レジスタと、

該割込みステアリング・レジスタによって提供されるステアリング情報を基づいて該複数のバス・マスターのうちの対応するバス・マスターに該各割込みを経路指定する割込みステアリング・ロジックと、

からなるUSB機能コントローラと、

からなる共用ユニバーサル・シリアル・バス(USB)資源。

【0105】

〔請求項36〕 前記少なくとも1つの割込みステアリング・レジスタが、割込みステアリング・セット・レジスタと、割込みステアリング・クリア・レジスタと、からなる、請求項35に記載の共用USB資源。

【0106】

〔請求項37〕 前記少なくとも1つの割込みステアリング・レジスタが、前記割込みステアリング・セット・レジスタおよび前記割込みステアリング・クリア・レジスタに結合され、前記ステアリング情報を前記割込みステアリング・ロジックに提供する割込みステアリング・ストレージ回路をさらに含む、請求項36に記載の共用USB資源。

【図面の簡単な説明】

【0107】

【図1】本発明の1実施形態によるデータ処理システム10をブロック図形式で示す図。

【図2】本発明の1実施形態による、図1の追加信号ステアリング・ロジック36の一部分をブロック図形式で示す図。

【図3】本発明の1実施形態による、図1の共用資源24の一部分を他の回路と共にブロック図形式で示す図。

【図4】本発明の1実施形態による、図1のUSB共用資源100の一部分を他の回路と共に一部分はブロック図形式で、一部分は回路図形式で示す図。

〔 図 1 〕

【 図 2 】

【図3】

【 四 4 】

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                        | International application No.<br>PCT/US04/31053   |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------|------------------------------------------------------------------------------------|-----------------------|---|---------------------------------------------------------|-----|---|-----------------------------------------------------|-----|------|---------------------------------------------------------------|-----|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC(7) : G06F 13/24<br>US CL : 710/260<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |                                                   |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>U.S. : 710/263, 266, 305                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                        |                                                   |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                        |                                                   |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        |                                                   |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b><br><table border="1"> <thead> <tr> <th>Category *</th> <th>Citation of document, with indication, where appropriate, of the relevant passages</th> <th>Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td>A</td> <td>US 5,640,571 A (HEDGES et al) 17 June 1997 (17.06.1997)</td> <td>1-9</td> </tr> <tr> <td>A</td> <td>US 6,237,058 B1 (NAKAGAWA) 22 May 2001 (22.05.2001)</td> <td>1-9</td> </tr> <tr> <td>A, E</td> <td>US 6,877,057 B2 (ALEXANDER et al.) 05 April 2005 (05.04.2005)</td> <td>1-9</td> </tr> </tbody> </table>                          |                                                                                                                                                        |                                                   | Category * | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | A | US 5,640,571 A (HEDGES et al) 17 June 1997 (17.06.1997) | 1-9 | A | US 6,237,058 B1 (NAKAGAWA) 22 May 2001 (22.05.2001) | 1-9 | A, E | US 6,877,057 B2 (ALEXANDER et al.) 05 April 2005 (05.04.2005) | 1-9 |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Citation of document, with indication, where appropriate, of the relevant passages                                                                     | Relevant to claim No.                             |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | US 5,640,571 A (HEDGES et al) 17 June 1997 (17.06.1997)                                                                                                | 1-9                                               |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | US 6,237,058 B1 (NAKAGAWA) 22 May 2001 (22.05.2001)                                                                                                    | 1-9                                               |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

| A, E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | US 6,877,057 B2 (ALEXANDER et al.) 05 April 2005 (05.04.2005)                                                                                          | 1-9                                               |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        | <input type="checkbox"/> See patent family annex. |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"B" earlier application or patent published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                                                                                        |                                                   |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

| Date of the actual completion of the international search<br><br>31 October 2005 (31.10.2005)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Date of mailing of the international search report<br><br>17 NOV 2005                                                                                  |                                                   |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

| Name and mailing address of the ISA/US<br><br>Mail Stop PCT, Attn: ISA/US<br>Commissioner for Patents<br>P.O. Box 1450<br>Alexandria, Virginia 22313-1450<br>Facsimile No. (703) 305-3230                                                                                                                                                                                                                                                                                                                                                                                                                          | Authorized officer<br><br>Khanh Dang<br>Telephone No. 571-272-3626 |                                                   |            |                                                                                    |                       |   |                                                         |     |   |                                                     |     |      |                                                               |     |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,M,A,MD,MG,MK,MN,MW,MX,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 バグリカ、ジョン ジェイ .

アメリカ合衆国 7 8 7 4 8 テキサス州 オースティン クリーク ビュー ドライブ 1 0 6

2 2

(72)発明者 モイヤー、ウィリアム シー .

アメリカ合衆国 7 8 6 2 0 テキサス州 ドリッピング スプリングス ピア ブランチ ロー

ド 1 0 0 5

F ターム(参考) 5B061 CC09

【要約の続き】

。