(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5545524号

(P5545524)

(45) 発行日 平成26年7月9日(2014.7.9)

(24) 登録日 平成26年5月23日(2014.5.23)

(51) Int.Cl.

F 1

|              |           |             |      |

|--------------|-----------|-------------|------|

| HO1L 21/027  | (2006.01) | HO1L 21/30  | 502C |

| HO1L 21/3065 | (2006.01) | HO1L 21/302 | 105A |

| HO1L 27/115  | (2006.01) | HO1L 21/30  | 570  |

| HO1L 21/8247 | (2006.01) | HO1L 27/10  | 434  |

| HO1L 21/336  | (2006.01) | HO1L 29/78  | 371  |

請求項の数 15 (全 23 頁) 最終頁に続く

(21) 出願番号 特願2009-528390 (P2009-528390)

(86) (22) 出願日 平成19年8月31日 (2007.8.31)

(65) 公表番号 特表2010-503995 (P2010-503995A)

(43) 公表日 平成22年2月4日 (2010.2.4)

(86) 國際出願番号 PCT/US2007/077463

(87) 國際公開番号 WO2008/033695

(87) 國際公開日 平成20年3月20日 (2008.3.20)

審査請求日 平成22年8月10日 (2010.8.10)

(31) 優先権主張番号 11/521,851

(32) 優先日 平成18年9月14日 (2006.9.14)

(33) 優先権主張国 米国(US)

(73) 特許権者 595168543

マイクロン テクノロジー, インク.

アメリカ合衆国, アイダホ州 83716

-9632, ボイズ, サウス フェデ

ラル ウエイ 8000

(74) 代理人 100106851

弁理士 野村 泰久

(74) 代理人 100074099

弁理士 大菅 義之

(72) 発明者 フィッシャー, マーク

アメリカ合衆国, アイダホ州 83713

, ボイズ, ノース ブルックレット アヴ

エニュー 5944

最終頁に続く

(54) 【発明の名称】効率的なピッチマルチプリケーションプロセス

## (57) 【特許請求の範囲】

## 【請求項 1】

部分的に製造された集積回路の、アレイ領域内のアレイマスク要素と、周辺領域内の周辺マスク要素とを同時に画定するために、選択的に画定可能な層をパターニングするステップと、

前記パターニングの後、複数の自立スペーサーを形成するために、前記アレイ領域内でピッチマルチプリケーションを行うステップであって、

前記アレイマスク要素および前記周辺マスク要素の側壁にスペーサーを形成するステップと、

前記スペーサーと、前記アレイマスク要素および前記周辺マスク要素の上に保護材料の層を堆積するステップと、 10

前記保護材料をパターニングするステップと、

前記アレイマスク要素を優先的に除去することによって、前記自立スペーサーを形成し、かつ周辺マスク要素内に開口部も形成するステップと、

を含むステップと、

前記自立スペーサーと前記周辺マスク要素によって少なくとも部分的に画定されるパターンを基板に同時に転写するステップと、

を含む、集積回路を形成するための方法。

## 【請求項 2】

スペーサーを側壁に形成するステップは、

前記アレイマスク要素および前記周辺マスク要素の上にスペーサー材料のプランケット層を堆積するステップと、

前記スペーサーを画定するために前記プランケット層を異方性エッチングするステップと、

を含む、請求項 1 の方法。

【請求項 3】

前記保護材料の層を堆積するステップはフォトレジストを堆積するステップを含み、前記保護材料をパターニングするステップはフォトリソグラフィーを行うステップを含む、請求項 1 の方法。

【請求項 4】

前記保護材料をパターニングするステップは、前記アレイ領域内の全スペーサーを露出するために前記保護材料の一部を除去するステップを含む、請求項 1 の方法。

【請求項 5】

前記プランケット層を堆積するステップは化学気相堆積を行うステップを含む、請求項 2 の方法。

【請求項 6】

前記パターンを同時に転写するステップは、前記部分的に製造された集積回路の前記アレイ領域および前記周辺領域内に電気デバイスを形成する、請求項 1 の方法。

【請求項 7】

前記電気デバイスは電気相互接続である、請求項 6 の方法。

10

【請求項 8】

前記パターンを同時に転写するステップは、前記相互接続に直接接触するランディングパッドを形成する、請求項 7 の方法。

【請求項 9】

前記パターンを同時に転写するステップは、ピッチマルチプリケーションされていない相互接続と接触するピッチマルチプリケーションされた相互接続を形成する、請求項 7 の方法。

【請求項 10】

前記選択的に画定可能な層をパターニングするステップは、フォトレジスト層をパターニングするステップを含む、請求項 1 の方法。

30

【請求項 11】

前記選択的に画定可能な層をパターニングするステップは、感光性の層内にトレンチのパターンを形成するステップと、前記パターンを下にあるハードマスク層および一時層に転写するステップを含み、前記ハードマスク層は前記一時層の上にあり、前記パターニングされたハードマスク層および一時層は前記アレイマスク要素と前記周辺マスク要素を画定する、請求項 1 の方法。

【請求項 12】

部分的に製造された集積回路のアレイ領域の上に配置された複数の自立スペーサーのペアと、

前記複数の自立スペーサーのペアと同じ面上にある、他の複数のスペーサーのペアであつて、前記他のスペーサーのペアをなすスペーサーは、前記他のスペーサーのペアと比べて選択的にエッチング可能な一時材料の側壁に配置される、他の複数のスペーサーのペアと、を含み、

40

前記一時層内に一つ以上の開口部が設けられ、

前記他のスペーサーのペアのいくつかは、自立している部分を有し前記他のスペーサーのスペーサー間で一時材料を含む他の部分を有する、

部分的に製造された集積回路。

【請求項 13】

前記一つ以上の開口部は、前記部分的に製造された集積回路の周辺領域内に配置される、請求項 12 の部分的に製造された集積回路。

50

**【請求項 14】**

前記一つ以上の開口部は、前記部分的に製造された集積回路の前記周辺領域内の相互接続の所望の形状と配置を有する、請求項 13 の部分的に製造された集積回路。

**【請求項 15】**

前記自立スペーサーは、100nm未満の間隔を持ち、前記他のスペーサーのペアは100nmより大きい間隔を持つ、請求項 12 の部分的に製造された集積回路。

**【発明の詳細な説明】****【技術分野】****【0001】****【関連出願への参照】**

本出願は次の出願に関連する。2004年9月2日出願のAbatchevらのU.S. Patent Application No. 10/934,778, Method for Integrated Circuit Fabrication Using Pitch Multiplication、2004年8月31日出願のTranらのU.S. Patent Application No. 10/931,771, Methods for Increased Photo Alignment Margins、2005年8月29日出願のTranらのU.S. Patent Application No. 11/214,544, Pitch Reduced Patterns Relative To Photolithography Features、2006年3月2日出願のWerner JuenglingのU.S. Patent Application No. 11/366,212, Process Flow for Vertical Transistor Arrays、2006年3月2日出願のWerner JuenglingのU.S. Patent Application No. 11/367,020, Masking Process For Simultaneously Patterning Separate Regions。これらの参考の各々の全容は本明細書に引用により組み込まれる。

10

**【背景技術】****【0002】****【技術分野】**

本発明は、概して集積回路製造に関し、より具体的には、マスキング技術に関する。

**【0003】****【背景技術】**

可搬性、計算能力、記憶容量、およびエネルギー効率の増加への要望を含む多くの要因の結果として、集積回路は縮小化し続けている。また、例えば電気デバイスや相互接続線など、集積回路を形成する構成フィーチャのサイズも、この縮小化を促進するべく減少し続けている。

20

**【0004】**

フィーチャサイズの減少傾向は、例えば、ダイナミックランダムアクセスメモリ (DRAM) 、フラッシュメモリ、静态ランダムアクセスメモリ (SRAM) 、強誘電 (FE) メモリなどのメモリ回路やデバイスで顕著である。一例を挙げると、DRAMは通常、メモリセルとして知られる何百万もの同一の回路要素を含む。DRAMメモリセルは、通常は二つの電気デバイス、すなわち蓄積キャパシタとアクセス電界効果トランジスタとから構成される。各メモリセルは、1ビット (2進数) のデータを記憶することができるアドレス可能な記憶場所である。1ビットは、トランジスタを通してセルに書き込むことができ、キャパシタ内の電荷を感知することによって読み取ることができる。メモリセルを構成する電気デバイスのサイズ、およびメモリセルにアクセスする導電性ラインのサイズを減少することによって、メモリデバイスを縮小化することができる。加えて、メモリデバイス内の一定領域により多くのメモリセルを取り付けることにより、記憶容量を増加することができる。他のメモリ設計は、アクセスデバイスと記憶デバイスを組み込むことができ、もしくは、アクセスデバイスを省略することができる ( 例えば、クロスポイントMRAM、PCRAMなど ) 。

30

**【0005】**

フィーチャサイズの継続的削減のために、フィーチャ形成に使用される技術に対する要求はますます大きくなっている。例えば、導電性ラインなどのフィーチャをパターニングするためにフォトリソグラフィーが一般に使用される。これらのフィーチャのサイズをあらわすために、ピッチの概念が使用され得る。ピッチとは、繰り返しパターンの二つの隣

40

50

接フィーチャにおける同一点間の距離と定義される。これらのフィーチャは、通常は隣接フィーチャ間の空間によって画定され、この空間は、通常は絶縁体などの材料で充填される。結果として、ピッチとは、フィーチャの幅と、そのフィーチャを隣接フィーチャから分離するフィーチャの片側の空間の幅の合計と見なすことができる。しかしながら、光学機器、および光もしくは放射波長などの要因のために、各フォトリソグラフィー技術は最小ピッチを持ち、それを下回るピッチでは、特定のフォトリソグラフィー技術は信頼性のあるフィーチャを形成することができない。従って、フォトリソグラフィー技術の最小ピッチは、継続的なフィーチャの縮小化に対する妨げとなる。

#### 【 0 0 0 6 】

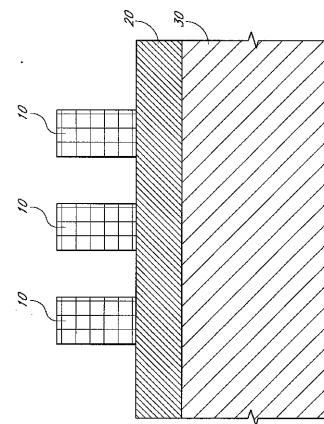

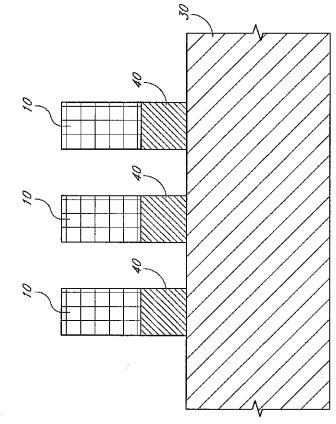

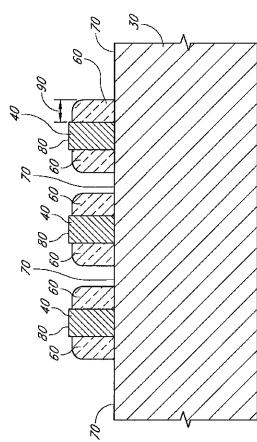

“ピッチダプリング”もしくは“ピッチマルチプリケーション”は、フォトリソグラフィー技術の性能を最小ピッチ以上に拡張するための提案方法の一つである。ピッチマルチプリケーション法は、図1A - 1Fに図示され、Lowreyらに発行されたU.S. Patent No. 5,328,810に記載されており、この全開示は本明細書に引用により組み込まれる。図1Aを参照すると、ラインのパターン10がフォトレジスト層内にフォトリソグラフィーで形成され、フォトレジスト層は、犠牲材料の層20の上にあり、層20は基板30の上にある。図1Bに示されるように、その後パターンがエッチング（好ましくは異方性エッチング）を用いて層20に転写され、その結果プレースホルダーもしくはマンドレル40が形成される。図1Cに示されるように、隣接するマンドレル40間の距離を増加するために、フォトレジストライン10を除去してマンドレル40を等方性エッチングすることができる。その後、図1Dに示されるように、スペーサー材料の層50がマンドレル40の上に堆積される。その後、スペーサー60（図1E）、すなわち、別の材料の側壁からのびる、もしくはもともとのびるよう形成された材料が、マンドレル40の両側に形成される。スペーサー形成は、図1Eに示されるように、方向性スペーサーエッチングにおいて、水平面70および80からスペーサー材料を優先的にエッチングすることによって完成される。図1Fに示されるように、その後残りのマンドレル40が除去され、スペーサー60のみを残す。スペーサー60はあわせてパターニングのためのマスクとなる。従って、以前は一定のピッチに一つのマスク要素と一つの空間を画定するパターンが含まれていた所には、今や同じ幅に二つのマスク要素と二つの空間が含まれることになる。空間は例えばスペーサー60によって画定される。結果として、フォトリソグラフィー技術で形成可能な最小フィーチャサイズが効果的に減少する。

#### 【 0 0 0 7 】

上述の例ではピッチは実際には半減するが、このピッチの減少は、従来ピッチ“ダプリング”、もしくはより一般的にはピッチ“マルチプリケーション”と称される。従って、従来、一定倍数のピッチの“マルチプリケーション”とは、実際にはその倍数だけピッチを減少することを含む。本明細書では従来の用語が保持される。

#### 【 0 0 0 8 】

スペーサー材料の層50は通常は単一の厚さ90を持ち（図1Dおよび1Eを参照）、スペーサー60によって形成されるマスク要素のサイズは通常はその厚さ90に対応するので、ピッチダプリングは、通常は一つの幅のみのマスク要素を作る。しかしながら、回路は一般的に異なるサイズのフィーチャを利用する。例えば、ランダムアクセスメモリ回路は、通常は、回路の一部分に位置するメモリセルのアレイと、いわゆる“周辺”に位置する論理回路とを含む。アレイ内では、メモリセルは通常は導電性ラインによって接続され、周辺では、導電性ラインは通常、周辺の相互接続、もしくはアレイを論理回路に接続するためのランディングパッドに接触する。しかしながら、周辺相互接続およびランディングパッドなどの周辺フィーチャは、アレイ内の導電性ラインよりも大きい可能性がある。加えて、周辺トランジスタを含む周辺の電気デバイスは、アレイ内の電気デバイスよりも大きい可能性がある。さらに、例え周辺フィーチャをアレイ内のフィーチャと同じピッチで形成することができたとしても、ピッチマルチプリケーションによって形成されるマスクパターンは、パターニングされたフォトレジストの側壁に沿って形成されるものに制限され得るので、いくつかのフィーチャを画定するために必要な柔軟性（例えば幾何学的柔軟性）

10

20

30

40

50

を実現しながらピッチマルチプリケーションを利用することは困難である。

【発明の概要】

【0009】

従って、異なるサイズのフィーチャを形成する方法、特にいくつかのフィーチャがフォトリソグラフィー技術の最小ピッチ以下で形成される方法、および、特にピッチマルチプリケーションと併用する方法が必要とされる。

【図面の簡単な説明】

【0010】

本発明は、発明を実施するための形態、および添付の図面からよりよく理解される。これらは例示を意図するものであって、本発明を限定する意図はない。

10

【図1A】先行技術のピッチダーリング法に従う、導電性ラインを形成するための一連のマスキングパターンの概略的な断面側面図である。

【図1B】先行技術のピッチダーリング法に従う、導電性ラインを形成するための一連のマスキングパターンの概略的な断面側面図である。

【図1C】先行技術のピッチダーリング法に従う、導電性ラインを形成するための一連のマスキングパターンの概略的な断面側面図である。

【図1D】先行技術のピッチダーリング法に従う、導電性ラインを形成するための一連のマスキングパターンの概略的な断面側面図である。

【図1E】先行技術のピッチダーリング法に従う、導電性ラインを形成するための一連のマスキングパターンの概略的な断面側面図である。

20

【図1F】先行技術のピッチダーリング法に従う、導電性ラインを形成するための一連のマスキングパターンの概略的な断面側面図である。

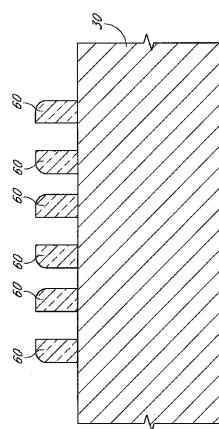

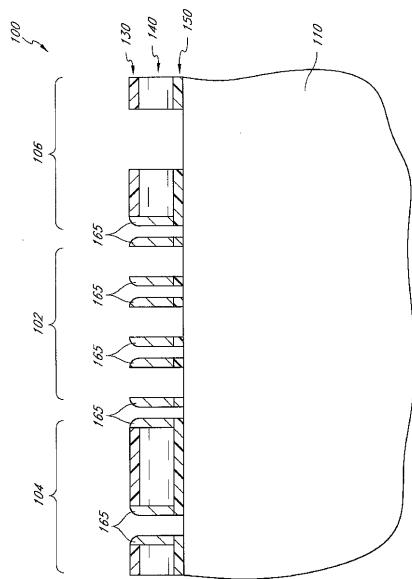

【図2A】本発明の好ましい実施形態に従う、部分的に製造された集積回路の概略的な平面図である。

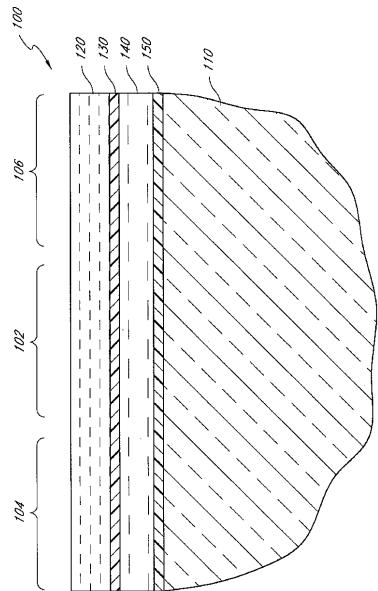

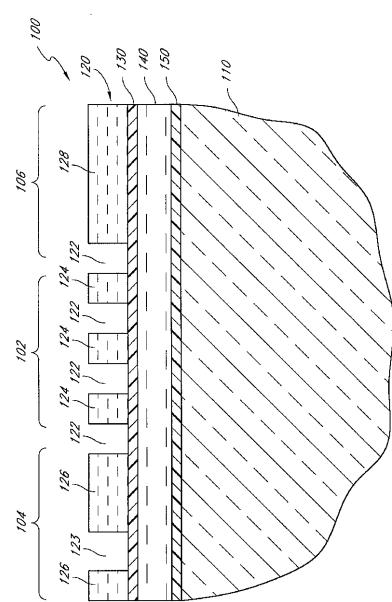

【図2B】本発明の好ましい実施形態に従う、図2Aの部分的に製造された集積回路の概略的な断面側面図である。

【図3】本発明の好ましい実施形態に従う、フォトレジスト層内にラインを形成した後の、図2A-2Bの部分的に製造された集積回路の概略的な断面側面図である。

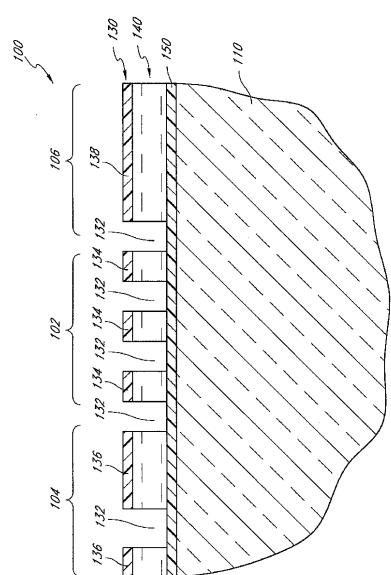

【図4】本発明の好ましい実施形態に従う、フォトレジスト層内のパターンを下にあるハードマスク層と一時層に転写し、フォトレジスト層を除去した後の、図3の部分的に製造された集積回路の概略的な断面側面図である。

30

【図5】本発明の好ましい実施形態に従う、マスク要素間の空間を広げるためにトリムエッチングを行った後の、図4の部分的に製造された集積回路の概略的な断面側面図である。

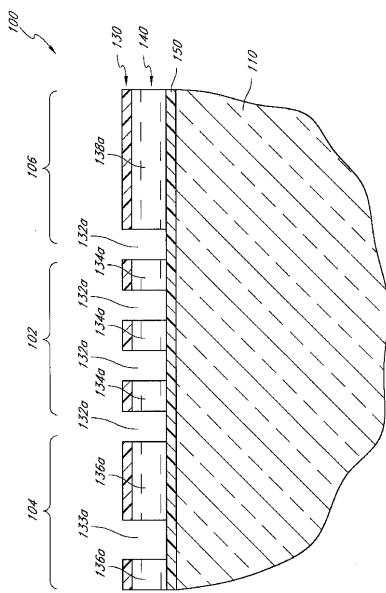

【図6】本発明の好ましい実施形態に従う、スペーサー材料の層を堆積した後の、図5の部分的に製造された集積回路の概略的な断面側面図である。

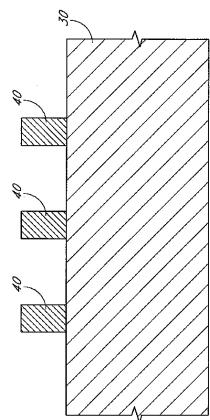

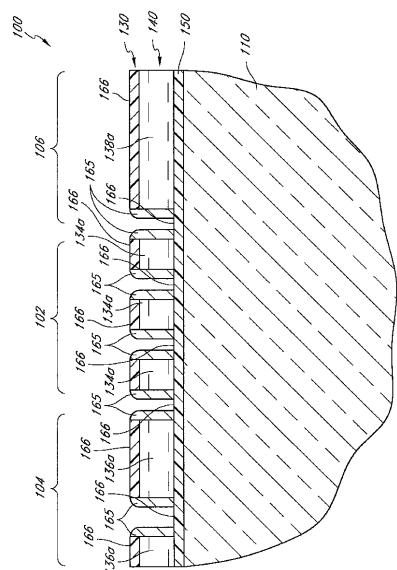

【図7A】本発明の好ましい実施形態に従う、スペーサーエッチングを行った後の、図6の部分的に製造された集積回路の概略的な断面側面図である。

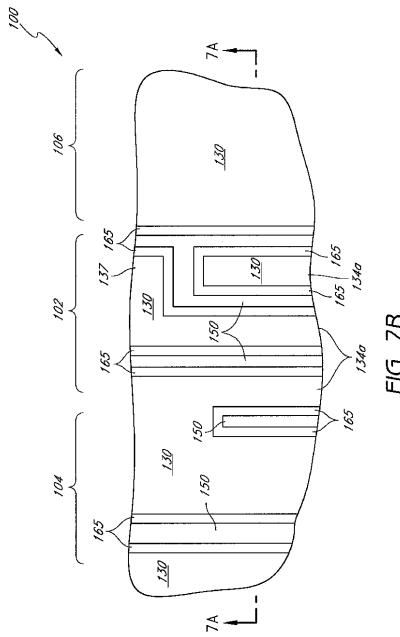

【図7B】本発明の好ましい実施形態に従う、スペーサーエッチングを行った後の、図6の部分的に製造された集積回路の概略的な平面図である。

40

【図8】本発明の好ましい実施形態に従う、保護材料の層を堆積した後の、図7A-7Bの部分的に製造された集積回路の概略的な断面側面図である。

【図9A】本発明の好ましい実施形態に従う、部分的に製造された集積回路のアレイ領域および他の選択領域内のマスク要素を露出するために、保護層をパターニングした後の、図8の部分的に製造された集積回路の概略的な断面側面図である。

【図9B】本発明の好ましい実施形態に従う、部分的に製造された集積回路のアレイ領域および他の選択領域内のマスク要素を露出するために、保護層をパターニングした後の、図8の部分的に製造された集積回路の概略的な平面図である。

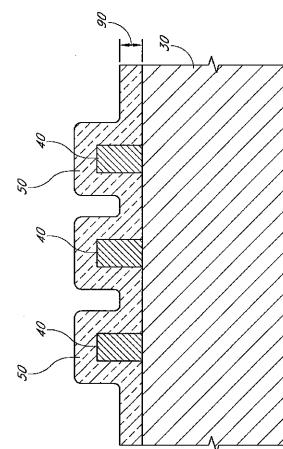

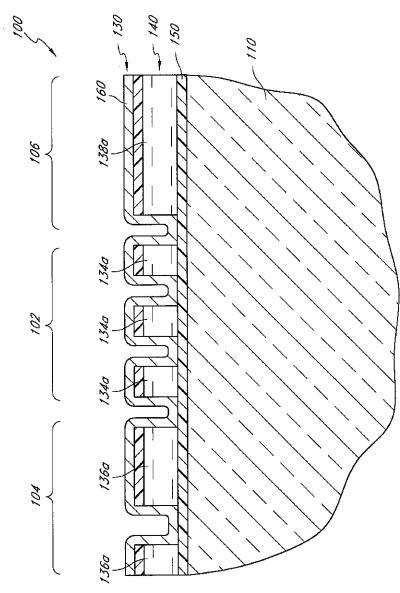

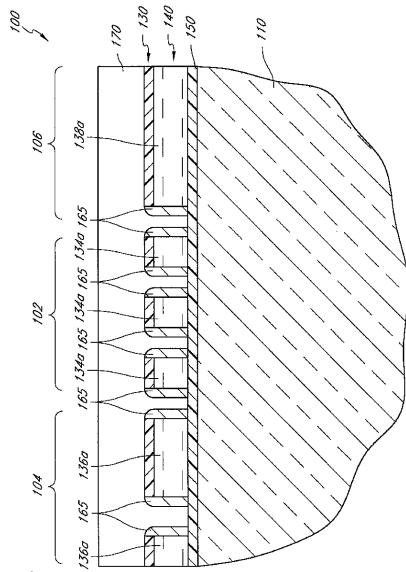

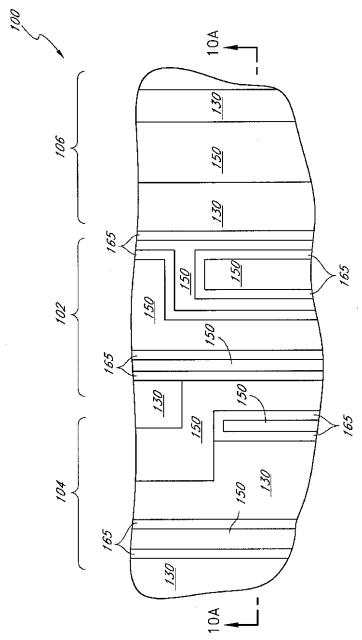

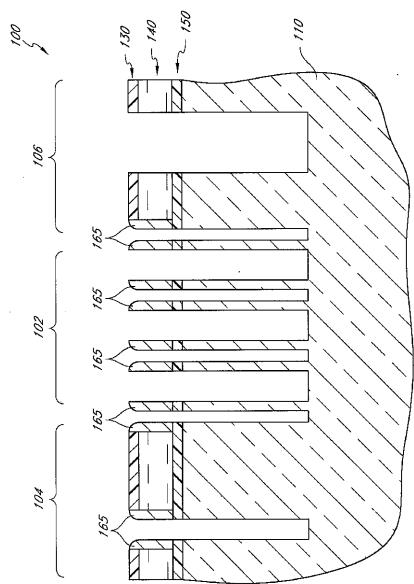

【図10A】本発明の好ましい実施形態に従う、パターニングされた保護層によって露出された領域内のハードマスクと一時層材料を除去することによって、自立スペーサーのパ

50

ターンを残し、その後保護層を除去した後の、図9A-9Bの部分的に製造された集積回路の概略的な断面側面図である。

【図10B】本発明の好ましい実施形態に従う、パターニングされた保護層によって露出された領域内のハードマスクと一時層材料を除去することによって、自立スペーサーのパターンを残し、その後保護層を除去した後の、図9A-9Bの部分的に製造された集積回路の概略的な平面図である。

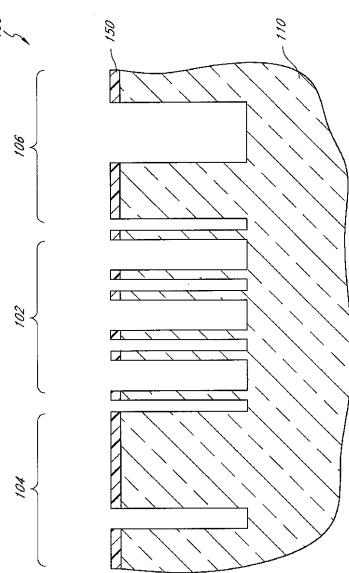

【図11】本発明の好ましい実施形態に従う、ピッチマルチプリケーションされたマスク要素と、ピッチマルチプリケーションされていないマスク要素のパターンを、下にあるハードマスク層にエッチングした後の、図10A-10Bの部分的に製造された集積回路の概略的な断面側面図である。

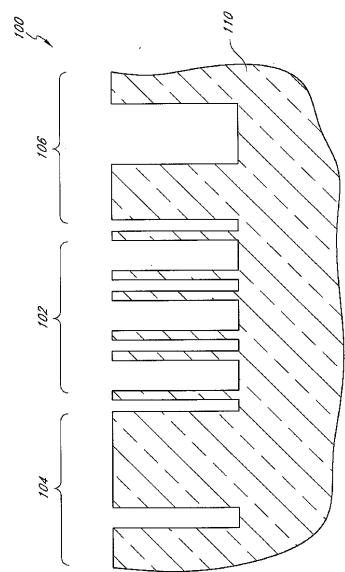

【図12】本発明の好ましい実施形態に従う、ピッチマルチプリケーションされたマスク要素と、ピッチマルチプリケーションされていないマスク要素のパターンを、下にある基板に転写した後の、図11の部分的に製造された集積回路の概略的な断面側面図である。

【図13】本発明の他の好ましい実施形態に従う、基板の上にあるマスク要素を除去した後の、図12の部分的に製造された集積回路の概略的な断面側面図である。

【図14】本発明の他の好ましい実施形態に従う、基板の上にある全てのマスク要素を除去した後の、図12もしくは13の部分的に製造された集積回路の概略的な断面側面図である。

#### 【発明を実施するための形態】

##### 【0011】

ピッチマルチプリケーションされたフィーチャと、ピッチマルチプリケーションされていないフィーチャなどの大きなフィーチャとのサイズの違いのために、ピッチマルチプリケーションされたフィーチャを大きなフィーチャに接続することは困難である可能性がある。例えば、通常、ピッチマルチプリケーションされたフィーチャは、コンタクトプラグや大きなサイズの相互接続などのフィーチャに確実に接触するためには、小さすぎる、および／もしくは密集しすぎている。ピッチマルチプリケーションされたフィーチャの小さなサイズおよび／もしくは密な間隔のために、短絡もしくは他の不整合が生じる可能性がある。ピッチマルチプリケーションされたフィーチャと、ピッチマルチプリケーションされていないフィーチャを形成するために、様々な方策が提案されてきた。ピッチマルチプリケーションされたフィーチャと、ピッチマルチプリケーションされていないフィーチャを形成するための方法例は、AbatchevらのU.S. Patent Application No. 10/934,778およびTranらのU.S. Patent Application No. 10/931,771に記載され、両出願は本出願の譲受人に譲渡されている。これらの参照の各々の全開示は本明細書に引用により組み込まれる。

##### 【0012】

ピッチマルチプリケーションされたフィーチャと、ピッチマルチプリケーションされていないフィーチャを形成し接続することが困難なことに加えて、そのプロセスフローは、異なるサイズのフィーチャを形成し重ねる必要があるために、複雑になる可能性がある。例えば、ピッチマルチプリケーションされたフィーチャは、大きなサイズのフィーチャから別々に形成され得るので、多数のマスク形成ステップとマスク統合 (mask consolidation) ステップが必要となる。当然のことながら、プロセスフローにおける各追加ステップは、プロセスフローの複雑性と費用を好ましくなく増加し得る。さらに、各追加ステップは、不整合、エッチングおよびパターン転写の複雑性、および、プロセスの結果に好ましくない変動を生じ得るその他の誤差を誘発する可能性がある。

##### 【0013】

これらの問題を考慮して、本発明の好ましい実施形態は、有利に簡単なプロセスフローを用いて、ピッチマルチプリケーションされたフィーチャとピッチマルチプリケーションされていないフィーチャの形成と接続を可能にする。好ましくは、集積回路のアレイ領域、インターフェース領域、および周辺領域に対応する、選択的に画定可能な層（例えばフォトレジスト層）の部分が同時にパターニングされる。ピッチマルチプリケーションは、

10

20

30

40

50

アレイ領域内にピッチマルチプリケーションされたスペーサーを形成するために使用される。インターフェース領域と周辺領域の少なくとも一部は保護材料を用いて保護されるが、他の部分はエッチングされ、自立スペーサーがアレイ領域内に形成される。その後保護材料が除去され、アレイ領域内のスペーサーと、インターフェース領域および周辺領域内のフィーチャを含むパターンが、その後ハードマスク層に転写される。ハードマスク層は、下にある基板をパターニングするために使用され得る。

#### 【0014】

有利なことに、好ましい実施形態に従う処理は、比較的少ないプロセスステップを用いて、ピッチマルチプリケーションされたフィーチャとピッチマルチプリケーションされていないフィーチャの形成と接続を可能にする。ステップの回数が比較的少ないと、プロセスの結果の均一性を改良することができる。追加のパターン形成およびパターン転写ステップによって誘発される不均一性を軽減することができる。さらに、本明細書で論じられるように、ピッチマルチプリケーションされていないマスク要素の、ピッチマルチプリケーションされたマスク要素への接続は、ピッチマルチプリケーションされていないマスク要素と同じ垂直面上で同時に形成することができるので、別々に形成されたマスク要素の不整合によって生じる欠陥を削減することができる。従って、ピッチマルチプリケーションされたフィーチャへの接続をより確実に形成することができ、その結果、短絡や、ピッチマルチプリケーションされたフィーチャの不完全な接続の可能性が軽減される。加えて、プロセスステップの回数が比較的少ないと、高スループットで比較的低コストの集積回路製造を有利に可能にする。

10

20

#### 【0015】

ここで図を参照するが、全体を通して類似する番号は類似する部分をあらわす。当然のことながら、これらの図は必ずしも縮尺通りに描かれていない。

#### 【0016】

最初に、ハードマスク層内にパターンを形成するために適切な層のスタックが形成される。

#### 【0017】

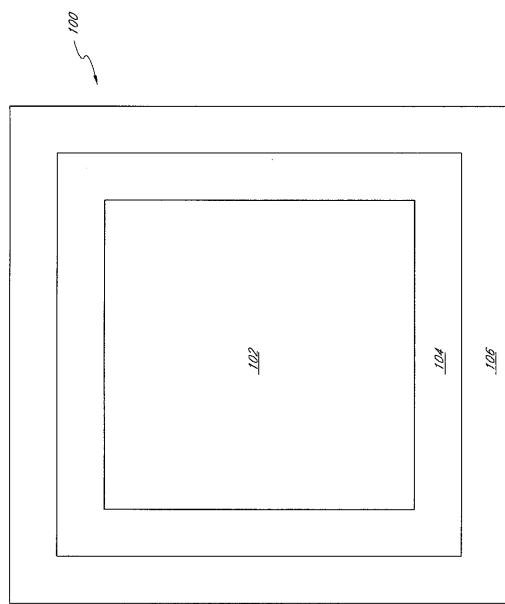

図2Aを参照すると、部分的に製造された集積回路100の平面図が示される。好ましい実施形態は任意の集積回路を形成するために使用することができるが、それらは、NANDフラッシュメモリを含む、DRAM、ROM、もしくはフラッシュメモリなどの揮発性および不揮発性のメモリデバイス用のメモリセルアレイを含む、電気デバイスのアレイを持つデバイス、または、論理アレイもしくはゲートアレイを持つ集積回路を形成するために、特に有利に適用される。論理アレイは、メモリアレイと類似するコアアレイと、サポート論理回路を持つ周辺を持つ、フィールドプログラマブルゲートアレイ(FPGA)であってもよい。結果として、集積回路100は、例えば、論理アレイと内蔵メモリの両方を含み得るメモリチップもしくはプロセッサ、または、論理アレイもしくはゲートアレイなどのフィーチャのアレイを持つ任意の他の集積回路であってもよい。

30

#### 【0018】

引き続き図2Aを参照すると、中央領域102、すなわちアレイ領域もしくは単に“アレイ”が、インターフェース領域104によって囲まれ、インターフェース領域は、“周辺”とも称される周辺領域106によって囲まれる。当然のことながら、集積回路100の製造が完了した後、アレイ102は通常、導電性ラインと、トランジスタおよびキャパシタなどの電気デバイスで密集する。メモリデバイスでは、電気デバイスが複数のメモリセルを形成し、メモリセルは、通常はワード線とビット線の交点で規則的な格子パターンに配列される。好ましくは、ピッチマルチプリケーションは、下記で述べるように、アレイ102内のトランジスタおよびキャパシタの行および／もしくは列などのフィーチャを形成するために使用され得る。

40

#### 【0019】

他方で、周辺106は、通常はアレイ102内のフィーチャよりも大きなフィーチャを含む。周辺106内の、論理回路などのフィーチャをパターニングするためには、ピッチマルチブ

50

リケーションよりもむしろ、従来のフォトリソグラフィーが好んで使用される。これは、周辺106内に位置する論理回路の幾何学的複雑性のために、ピッチマルチプリケーションを使用することが難しいからである。例えば、周辺106内のフィーチャは通常、アレイ102内で典型的なフィーチャの連続規則性を持たない。さらに、論理領域は、アレイ領域102程に稠密である必要がないので、論理領域内のピッチマルチプリケーションは必要ない。対照的に、アレイパターンの規則的格子パターンは、ピッチマルチプリケーションを助長する。加えて、周辺内のいくつかのデバイスは、電気的な制約のため、大きな形状を必要とするので、そのようなデバイスでは、ピッチマルチプリケーションは従来のフォトリソグラフィーよりも不利になる。

## 【0020】

10

インターフェース領域104は、アレイと周辺フィーチャの両方を含み得る。例えば、インターフェース領域104は、アレイ102から周辺106への移行部として機能し、アレイ102内のフィーチャと、周辺106内のフィーチャとの間の接触を可能にし得る。

## 【0021】

同心領域として概略的に図示されているが、集積回路100内のアレイ102、インターフェース104、および周辺106の領域の相対位置と数は、図示されたものとは異なっていてもよいことが当業者に理解されるだろう。例えば、集積回路100のある領域では、下記の図のいくつかに図示されるように、インターフェース104および周辺106の領域が、アレイ領域102の両側に直接配置されてもよい。さらに、考察を簡略化するため、これらの領域のある特定の特性が上述されており、領域間の明確な境界が図示されているが、ある配置においては、領域の二つ以上が重なってもよい。

20

## 【0022】

図2Bは、部分的に製造された集積回路100の断面側面図を示す。様々なマスキング層120-150が基板110の上に設けられることが好ましい。層120-150は、下記で述べるように、基板110をパターニングするためのマスクを形成するためにエッチングされる。

## 【0023】

基板110の上にある層120-150の材料は、本明細書で述べられる様々なパターン形成ステップとパターン転写ステップのための、化学物質およびプロセス条件の考慮に基づいて選ばれることが好ましい。最上位の選択的に画定可能な（例えば感光性の）層120と基板110の間の層は、選択的に画定可能な層120から得られるパターンを基板110に転写するように機能することが好ましいので、選択的に画定可能な層120と基板110の間の層130-150は、それらが他の露出された材料と比べて選択的にエッチングされ得るように選ばれることが好ましい。当然のことながら、材料のエッチング速度が、周囲の材料よりも少なくとも約2-3倍、好ましくは少なくとも約10倍、より好ましくは少なくとも約20倍、最も好ましくは少なくとも約50倍大きい時、その材料は選択的に、もしくは優先的にエッチングされると見なされる。第二のハードマスク層150の上にある層120-140の目的は、第二のハードマスク層150内に明瞭なパターンが形成されるようにすることなので、当然のことながら、適切な他の材料、化学物質、および／もしくはプロセス条件が使用される場合は、層120-140のうちの一つ以上は、省略されるかもしくは置換されてもよい。

30

## 【0024】

40

図示された実施形態では、選択的に画定可能な層120は、第一のハードマスクもしくはエッチング停止層130の上にあり、層130は一時層140の上にあり、一時層140は第二のハードマスクもしくはエッチング停止層150の上にあり、層150は、マスクを通して処理される（例えばエッチングされる）基板110の上にある。好ましくは、基板110がそれを通して処理されるマスクは、第二のハードマスク層150内に形成される。

## 【0025】

引き続き図2Bを参照すると、選択的に画定可能な層120は、好ましくは感光性であり、例えば、当該技術分野で既知の任意のフォトレジストを含む、フォトレジストで形成される。例えば、フォトレジストは、157 nm、193 nm、248 nm、もしくは365 nmの波長系、193 nmの波長の液浸系、極紫外線系（13.7 nmの波長系を含む）、もしくは電子ビームリ

50

ソグラフィーシステムに適合する任意のフォトレジストであってよい。加えて、感光性の層120を画定するために、マスク無しのリソグラフィー、もしくはマスク無しのフォトリソグラフィーを使用することができる。好ましいフォトレジスト材料の例は、フッ化アルゴン (ArF) 感受性フォトレジスト、すなわちArF光源との使用に適したフォトレジスト、および、フッ化クリプトン (KrF) 感受性フォトレジスト、すなわちKrF光源との使用に適したフォトレジストを含む。ArFフォトレジストは、比較的短波長の光 (例えば193 nm) を利用するフォトリソグラフィーシステムで使用されることが好ましい。KrFフォトレジストは、長い波長のフォトリソグラフィーシステム (248 nmのシステムなど) で使用されることが好ましい。他の実施形態では、層120および任意の次のレジスト層は、例えばレジストをパターニングするためにモールドもしくは機械力を用いることによって、ナノインプリントリソグラフィーによってパターニングされ得るレジストで形成され得る。

#### 【0026】

第一のハードマスク層130の材料は無機材料を含むことが好ましい。材料の例は、酸化ケイ素 ( $\text{SiO}_2$ )、ケイ素、もしくはケイ素豊富な酸窒化ケイ素などの反射防止絶縁膜 (DARC) を含む。図示された実施形態では、第一のハードマスク層130は反射防止絶縁膜 (DARC) である。DARCを第一のハードマスク層130に使用することは、フォトリソグラフィー技術の解像限界付近のピッチを持つパターンを形成するために特に有利となり得る。DARCは、光反射を最小化することによって解像度を高めることができ、その結果、フォトリソグラフィーがパターンのエッジを画定することができる精度が増加する。

#### 【0027】

一時層140は、好ましいハードマスク材料に対する非常に高いエッチング選択性をもたらす非晶質炭素で形成されることが好ましい。より好ましくは、非晶質炭素は、光に対して透過性が高く (いわゆる “透明炭素”)、光配向に使用される光の波長に透過性であることによって、光配向の改良をもたらすような非晶質炭素の形である。そのような透明炭素を形成するための堆積技術は、A. Helmbold, D. Meissner, *Thin Solid Films*, 283(1996) 196-203に見ることができ、その全開示は本明細書に引用により組み込まれる。

#### 【0028】

第二のハードマスク層150は、下にある基板110をエッチングするために適切で、かつ、スペーサー165 (図11) などの、露出された上にある材料と比べて選択的にエッチングすることができるようなハードマスク材料で形成され得る。例えば、スペーサー材料 (図11) が酸化ケイ素もしくはケイ素であるいくつかの実施形態では、ハードマスク材料は窒化ケイ素であり得る。スペーサー材料が窒化ケイ素もしくはケイ素である他の実施形態では、ハードマスク材料は酸化ケイ素であり得る。図示された実施形態では、ハードマスク材料は窒化物、好ましくは窒化ケイ素である。

#### 【0029】

当然のことながら、基板110は、単一の材料の層、異なる材料の複数の層、異なる材料の領域もしくは構造を中心に持つ一つの層もしくは複数の層などを含み得る。これらの材料は、半導体、絶縁体、導電体、もしくはそれらの組み合わせを含み得る。例えば、基板は、ドープされたポリシリコン、電気デバイス活性領域、シリサイド、または、タンゲステン、アルミニウム、もしくは銅の層などの金属層、またはそれらの組み合わせを含み得る。いくつかの実施形態では、下記で述べられるマスク要素は、基板内の相互接続やランディングパッドなどの導電性フィーチャの所望の配置に直接対応し得る。図示された実施形態では、基板110の上部は絶縁体を含み、マスク要素の位置は、ダマシンメタライゼーションなどにおいて、絶縁体の所望の位置に対応し得る。基板内に形成される構造の例は、相互接続、ゲートスタック、およびシャロウトレンチアイソレーション構造を含む。

#### 【0030】

本明細書で述べられる層120-150は様々な方法で形成することができる。例えば、感光性の層を形成するためにスピノンコートティングプロセスを使用することができる。ハードマスク層を形成するために、化学気相堆積などの様々な堆積プロセスを使用することができる。好ましくは、特に一時層140が非晶質炭素で形成される場合に、ハードマスク層

10

20

30

40

50

、もしくは、例えばスペーサー材料などの任意の他の材料を一時層140の上に堆積するために、低温化学気相堆積(CVD)プロセスが使用される。

【0031】

一時層140の非晶質炭素は、炭化水素化合物、もしくは、炭素前駆体などの化合物の混合物を用いて、化学気相堆積によって形成され得る。前駆体の例は、プロピレン、プロピン、プロパン、ブタン、ブチレン、ブタジエン、およびアセチレンを含む。非晶質炭素層を形成するための適切な方法は、2003年6月3日にFairbairnらに発行されたU.S. Patent No. 6,573,030 B1に記載され、その全開示は本明細書に引用により組み込まれる。加えて、非晶質炭素はドープされてもよい。ドープされた非晶質炭素を形成するための適切な方法は、YinらのU.S. Patent Application No. 10/652,174に記載され、その全開示は本明細書に引用により組み込まれる。

【0032】

次に、パターンが形成され、ハードマスク層150に転写される。

【0033】

当然のことながら、本明細書に記載のステップのいずれかにおいて、上位面から下位面にパターンを転写することは、上位面内のマスク要素にほぼ対応する集積回路フィーチャもしくはマスク要素を下位面内に形成することを含む。例えば、下位面内のラインの経路は、上位面内のラインの経路にほぼ従い、下位面内の他の要素もしくはフィーチャの位置は、上位面内の類似する要素もしくはフィーチャの位置に対応する。しかしながら、要素もしくはフィーチャの正確な形状およびサイズは、上位面と下位面で異なる可能性がある。例えば、エッチングの化学物質と条件によって、転写されるパターンを形成する要素もしくはフィーチャのサイズおよび相対的間隔は、上位面上のパターンと比べて拡大したり縮小したりする可能性があるが、下記の実施形態における第一のレジストマスクが縮小する例からわかるように、依然として同じ初期“パターン”に似ている。従って、要素もしくはフィーチャの寸法にいくらかの変化があっても、転写されるパターンは依然として初期パターンと同じパターンと見なされる。対照的に、マスク要素周辺のスペーサーの形成は、新しい(ピッチマルチプリケーションされた)パターンを形成し得る。

【0034】

図3を参照すると、アレイ要素124、インターフェース要素126、および周辺要素128で境界を画定される、空間もしくはトレチ122、123を含むパターンが、感光性の層120内に形成される。要素124、126、128は感光性材料で形成される。トレチ122、123は、例えば248 nmもしくは193 nmの光を用いるフォトリソグラフィーによって形成することができ、その過程では、層120がレチクルを通して放射に晒され、その後現像される。現像された後、残りの感光性材料、図示された実施形態ではフォトレジストが、図示された要素124、126、128を形成する(断面のみで示される)。図示された実施形態では、アレイ要素124はラインである。

【0035】

ライン124のピッチは、ライン124の幅と、隣接する空間122の幅の合計に等しい。このライン124と空間122のパターンを用いて形成される要素の限界寸法を最小化するために、ピッチは、感光性の層120をパターンングするために使用されるフォトリソグラフィー技術の限界、もしくはその付近となり得る。例えば、248 nmの光を利用するフォトリソグラフィーでは、ライン124のピッチは約100 nmとなり得る。従って、ピッチはフォトリソグラフィー技術の最小ピッチとなり得、下記で述べられるスペーサーパターンは、フォトリソグラフィー技術の最小ピッチ以下のピッチを有利に持つことができる。あるいは、位置および要素のサイズの誤差の範囲は、典型的にはフォトリソグラフィー技術の限界に近づくにつれて増加するので、ライン124は、ライン124の位置およびサイズの誤差を最小化するために、例えば約200 nmのピッチで大きな要素サイズを持つように形成され得る。

【0036】

図4を参照すると、感光性の層120内のパターンが、ハードマスク層130と一時層140に転写され、スペーサー材料の層160(図6)の堆積が可能になる。通常、スペーサー材料

10

20

30

40

50

の堆積に使用される温度は高すぎてフォトレジストが耐えられないことがわかっている。従って、下記で述べられるスペーサー材料の堆積とエッチングのプロセス条件に耐えられる材料で形成された、第一のハードマスク層130と一時層140に、感光性の層120からパターンが転写されることが好ましい。フォトレジストよりも高い熱抵抗性を持つことに加え、一時層140を形成する材料は、スペーサー165(図10)と、下にある第二のハードマスク層150の材料と比べて、選択的に除去することができるよう選択されることが好ましい。上述の通り、層140は好ましくは非晶質炭素で形成され、より好ましくは透明炭素で形成される。

【0037】

パターン転写は、単一のステップ、すなわち単一のプロセスチャンバ内で *in situ* で行われてもよい。転写は異方性エッチングを用いて行われることが好ましい。好ましいエッチング化学物質は、第一のハードマスク層130をエッチングするには  $HBr/CF_4$  から生成されるプラズマなどのフッ化炭素プラズマ、一時層140をエッチングするには  $SO_2/O_2$  プラズマなどの酸素含有プラズマを用いるエッチングを含む。エッチングは、感光性の層120と比べて第一のハードマスク層130を選択的にエッチングし、その後エッチングは一時層140を通って進行し、第二のハードマスク層150で停止する。感光性の層120の一部は、パターン転写の最中にエッチングされてもよい。感光性の層120を形成する残りのレジストは、その後、例えばプラズマ灰化を含む、当業者に知られている様々なプロセスによって単独で除去することができる。

【0038】

図4および5を参照すると、アレイ要素134、インターフェース要素136、および周辺要素138の間の空間132、133は、好ましくは、トリムエッチング後に修正された空間132a、133aおよび要素134a、136a、138aを形成するために、要素134、136、138をエッチングすることによって広げられる。要素134、136、138は、好ましくはこれらの要素を“縮小する”ために等方性エッチングを用いてエッチングされる。適切なエッチングは、例えば  $SO_2/O_2/N_2/Ar$  プラズマ、 $Cl_2/O_2/He$  プラズマ、もしくは  $HBr/O_2/N_2$  プラズマなどの酸素含有プラズマを用いるエッチングを含む。エッチングの程度は、下記の考察から理解されるように、要素134a、136a、138aの幅が、所望の間隔を持つスペーサー165(図7A)を形成することができるよう選択されることが好ましい。例えば、アレイ内の要素134、136、138の幅は約80-120 nmから約40-70 nmに削減することができる。有利なことに、この幅を減らすエッチングは、感光性の層120をパターニングするために使用されるフォトリソグラフィー技術を用いて実現されるラインよりも狭いラインをアレイ内に作ることができる。加えて、エッチングは要素134a、136a、138aのエッジを平滑化することができるので、これらの要素の均一性を改良する。要素134a、136a、138aは、フォトリソグラフィー技術の解像限界以下の限界寸法を持つようにトリミングすることができるが、当然のことながら、このトリミングは空間132a、133a、およびアレイ内の要素134a、136a、138aのピッチは変更しないので、これらの要素の同一点間の距離は同じままである。他の実施形態では、要素134、136、138にトリムエッチングを行う代わりに、もしくはそれに加えて、当然のことながら、ハードマスク層130と一時層140内に所望のサイズの要素を形成するために、感光性の層120から第一のハードマスク層130にパターンを転写する前に、感光性の層120内の要素124、126、128(図3)にトリムエッチングを行うことができる。

【0039】

図6を参照すると、スペーサー材料の層160は、好ましくは、ハードマスク層130、150の露出された上面と側壁、および一時層140の側壁を含む、露出された表面の上にコンフォーマルにプランケット堆積される。スペーサー材料は、下にあるハードマスク層150にパターンを転写するためのマスクとして機能することができる任意の材料であってよい。スペーサー材料は、好ましくは、1) 良いステップカバレッジで堆積することができ、2) 部分的に製造された集積回路100内の他の材料と適合する温度で堆積することができ、3) 一時層140および第一と第二のハードマスク層130、150に対して選択的に異方性エッチングすることができる。好ましい材料は、ケイ素(例えば非晶質ケイ素)、酸化ケイ素

10

20

30

40

50

、および窒化ケイ素を含む。図示された実施形態では、スペーサー材料は酸化ケイ素であり、これはマスキングスタックの他の選択材料と組み合わせて特別な利点をもたらす。

#### 【0040】

スペーサー材料堆積のための好ましい方法は、化学気相堆積および原子層堆積を含む。層160の厚さは、好ましくはスペーサー165(図10)の所望の幅に基づいて決定される。例えば、図示された実施形態では、層160は好ましくは約20-80 nm、より好ましくは約40-60 nmの厚さに堆積される。好ましくは、ステップカバレッジは約80%以上、より好ましくは約90%以上である。

#### 【0041】

図7Aを参照すると、部分的に製造された集積回路100の水平面166からスペーサー材料を除去するために、酸化ケイ素スペーサー層160に異方性エッチングが行われる。スペーサーエッチングとしても知られているそのようなエッチングは、例えば $CF_4/CHF_3$ 、 $C_4F_8/C$ 、 $H_2F_2$ もしくは $CHF_3/Ar$ プラズマなどのバイアスフッ化炭素プラズマを用いて、または純粋に物理的スパッタエッチング(例えばArスパッタエッチング)を用いて、酸化物材料に行うことができる。スペーサーエッチングは、マンドレル134aおよび要素136a、138aの周囲のスペーサーのペア165を画定する。

10

#### 【0042】

図7Bは、図7Aの部分的に製造された集積回路100の平面図を示す。見てわかるように、マンドレル134aはラインの形状に加えて様々な形状をとることができる。上述の通り、図示された実施形態では、基板110の上部は絶縁体であり、スペーサー165のパターンは基板110内に形成される絶縁体の所望のパターンに対応する。従って、スペーサー165間の空間は、好ましくは、基板110内のダマシン導電性相互接続などの導電体の所望の配置に対応する。例えば、後に除去される(図10A-10B)任意のマンドレル134aは、後に形成される相互接続の位置に対応する位置をとることができる。そのような場合、いくつかのマンドレル134aには、マンドレル134aを用いて形成される相互接続を他の垂直面上の電気的フィーチャと電気的に接続するためのランディングパッドを形成するために使用することができる、拡張部分137を持たせられる。

20

#### 【0043】

図8を参照すると、保護層170が部分的に製造された集積回路100の表面の上に堆積される。保護層170もまた選択的に画定可能であることが好ましい。選択的に画定可能な層120と同様に、保護層170は感光性であることが好ましく、例えば、当該技術分野で既知の任意のフォトレジストを含むフォトレジストで形成される。加えて、他の実施形態では、感光性の保護層170は、ナノインプリントリソグラフィーによるパターニングのために適切なレジストで形成することができる。

30

#### 【0044】

図9Aを参照すると、感光性の層170は、例えば感光性の層120をパターニングするために使用されたものと同じフォトリソグラフィー技術を用いてパターニングされる。好ましくは、層170はレチクルを通して放射に晒され、その後、部分的に製造された集積回路100のアレイ領域102の要素を露出するために現像される。従って、一部のスペーサーもしくはスペーサーのペア165は露出されるが、一部は保護層170によって保護される。加えて、ハードマスク層130の一部は露出されるが、一部は保護される。

40

#### 【0045】

加えて、インターフェース領域104もしくは周辺106内の要素もまたパターニングすることができ、その結果、例えば周辺内にボイド174を形成する。当然のことながら、アレイ102内のスペーサー165は、好ましくはそれを形成するために使用されるフォトリソグラフィー技術の最小ピッチもしくは解像度よりも小さなピッチもしくは要素サイズを持ち、層170内にパターニングされる要素は、好ましくはそれらを形成するために使用されるフォトリソグラフィー技術の最小ピッチもしくは解像度以上であるピッチもしくは要素サイズを持つ。

#### 【0046】

50

図9Bを参照すると、ピッチマルチプリケーションされたスペーサー165間の空間に接続172がパターニングされ得る。当然のことながら、接続172は、周辺106もしくはインターフェース領域104内の相互接続をパターニングするために使用されるような、大きな寸法の要素173の末端となり得る。従って接続172は、一つ以上のマンドレル134aを大きなマスク要素173に接続することができ、最終的に、アレイ102内のピッチマルチプリケーションされた相互接続に接続された比較的大きな相互接続の形成が可能になる。

#### 【0047】

当然のことながら、部分的に製造された集積回路100の一部の要素は、層170によって保護されたままである。そのような場合、スペーサー165は、保護層170の除去後にこれらの要素の寸法を増大させる。

10

#### 【0048】

図10A-10Bを参照すると、第一のハードマスク層130と一時層140の、露出されたままの部分、もしくは保護層170によって保護されていない部分が、好ましくは異方性エッチングによって選択的に除去される。有利なことに、ハードマスク層130と一時層140の保護されていない部分は、単一のステップで、すなわち単一のプロセスチャンバ内で *in situ* に除去することができる。ハードマスク層130は、例えばHBr/CF<sub>4</sub>を含むプラズマエッチングを用いて選択的に除去することができ、一時層140は、例えばSO<sub>2</sub>/O<sub>2</sub>プラズマエッチングを用いて選択的に除去することができる。保護層170はその後、例えばプラズマ灰化によって除去される。

#### 【0049】

20

従って、アレイ領域102内にピッチマルチプリケーションされた自立スペーサー165を残して、マンドレル134a(図9A)が除去される。図示された実施形態では、スペーサー165のピッチとスペーサー165間の空間は、フォトリソグラフィーによって元々形成されたフォトレジストライン124のピッチと空間122(図3)のおよそ半分である。例えば、フォトレジストライン124が約200 nmのピッチを持っていた場合、約100 nm以下のピッチを持つスペーサー165を形成することができる。加えて、周辺106もしくはインターフェース領域104内にパターニングされる要素は下にある層にも転写され、その結果ハードマスク層130および一時層140内に例えばボイドもしくは開口部176が形成される。

#### 【0050】

30

図11を参照すると、スペーサー165、および第一のハードマスク層130と一時層140の残りの部分によって画定されるパターンが、第二のハードマスク層150に転写される。転写は、例えばCF<sub>4</sub>/O<sub>2</sub>/CH<sub>2</sub>F<sub>2</sub>含有プラズマエッチングなどの、例えばフッ化炭素プラズマを用いるエッチングなどの異方性エッチングを用いて行われることが好ましい。

#### 【0051】

基板はその後、第二のハードマスク層150内に画定されるマスクを通して処理され得る。例えば、図12を参照すると、パターンが基板110に転写され得る。図13を参照すると、当然のことながら、基板110がエッチングされる場合、基板110のエッチングにより、スペーサー165、および層130、140の残りの部分が除去され得る。従って、第二のハードマスク層150は基板110のエッチングのための主要マスクとして使用される。他の実施形態では、スペーサー165、および層130、140の残りの部分は、基板110の処理の前もしくは後に除去され得る。図14を参照すると、ハードマスク層150は基板110の処理後に除去され得る。

40

#### 【0052】

好ましくは、基板110は、少なくとも第二のハードマスク層150と比べて基板110に選択的な異方性エッチングを用いてエッチングされる。当然のことながら、基板110が異なる材料、例えば異なる材料の層を含む場合、もし単一の化学物質では異なる材料の全てをエッチングするために十分でない場合は、これらの異なる材料を通して連続的にエッチングするために、一連の異なる化学物質、好ましくは乾式エッチング化学物質を使用することができる。基板110の組成は、例えば形成される電気デバイスに基づくことができる。

#### 【0053】

50

当然のことながら、スペーサー165によって形成され、その後第二のハードマスク層150と基板110に転写されるパターンは、例えば電気デバイスを接続するための相互接続などのラインを画定することができる。電気デバイスは、メモリデバイスのアレイ領域内のメモリセルを形成する電気デバイスのように、アレイに配置されることが好ましい。相互接続172(図9B)は、集積回路のインターフェース領域もしくは周辺領域内の大きなフィーチャと、アレイ内の、要素171によって画定されるようなピッチマルチプリケーションされたフィーチャとの間の接続を有利に画定することができる。ラインが形成された後、部分的に製造された集積回路100は、例えばメモリチップなどの完成した集積回路を形成するために、付属電気デバイスおよび電気相互接続を形成するステップを含む、次の処理ステップにかけることができる。

10

#### 【0054】

当然のことながら、図示された実施形態の様々な修正が可能である。例えば、ピッチマルチプリケーションされたパターンは、典型的には、マンドレルの壁に沿って形成されるスペーサーによって形成される、閉ループを含む。従って、非ダマシンプロセスでは、スペーサー165間の空間よりもむしろスペーサー165が導電性ラインを作るために使用される場合、各ループが二つの独立した接続されていないラインを形成するように、これらのループの末端を切断するために追加の処理ステップが使用されることが好ましい。これは、例えば維持されるラインの部分の周囲に保護マスクを形成し、保護されていないマスクの末端をエッチングで除去することによって、実現することができる。ループの末端を切断するための適切な方法は、2004年8月31日出願のTranらのU.S. Patent Application No. 10/931,771に開示され、この全開示は本明細書に引用により組み込まれる。しかしながら、有利なことに、導電材料よりもむしろ絶縁材料の位置を画定するためにスペーサー165を用いることによって、スペーサーループの末端を切断するステップを回避することができる。例えば元はマンドレルによって占められていた空間などの、スペーサー165間の空間が相互接続の位置と形状を決定する場合は、スペーサーループの末端を切断する必要がない。

20

#### 【0055】

また、場合によっては、スペーサー165は基板110を処理する前に除去することができる。例えばスペーサー165が比較的背が高くて薄い場合、このような除去が有利となり得る。そのようなスペーサーは、構造的に安定ではない可能性があり、基板110のエッチングの最中に変形する可能性があるため、基板内にエッチングされるパターンに誤差を誘発してしまう。結果として、スペーサー165、およびハードマスク層130もしくは一次層140のいくらか残っている部分を除去することは、それを通して基板110が処理されるマスク(この実施例では下位のハードマスク層150によって画定される)を有利に安定化し得る。

30

#### 【0056】

加えて、スペーサー165のピッチは二倍を超える可能性がある。例えば、スペーサー165は、マンドレル134aを除去すること、スペーサー165の周囲に追加スペーサーを形成すること、スペーサー165を除去すること、その後、元はスペーサー165の周囲にあったスペーサーの周囲に別のスペーサーのセットを形成すること、などによって、さらにピッチマルチプリケーションを行うことができる。さらなるピッチマルチプリケーションのための方法例は、LowreyらのU.S. Patent No. 5,328,810で述べられている。

40

#### 【0057】

さらに、垂直に隣接する、または隣接していないおよび/もしくは垂直に分離してもよい、複数の層もしくは垂直面に、ピッチマルチプリケーションされたフィーチャを形成するために、好ましい実施形態を集積回路製造プロセスにわたって複数回利用することができる。そのような場合、パターニングされる個々の面の各々が基板110を構成することになり、様々な層120-170が、パターニングされる個々の面の上に形成され得る。また、当然のことながら、上述した様々な層120-170の特定の組成および高さは、特定の用途によって変えることができる。例えば、層150の厚さは、基板110の特性、例えば基板の化学組成、基板が一つもしくは複数の材料層を含むかどうか、形成されるフィーチャの深さ

50

など、および利用可能なエッティング化学物質によって変えることができる。場合によっては、層120-170のうちの一つ以上の層を省略することができ、もしくは、さらに層を追加することができる。例えば、場合によっては、基板110に選択的なエッティングに対する抵抗性が増加したハードマスクを設けるために、第二のハードマスク層150内に形成されるパターンを、一つ以上の追加ハードマスク層に転写することができる。

#### 【0058】

また、マスク層を通す“処理”とは、好ましくは下にある材料をエッティングすることを含むが、マスク層を通す処理とは、マスク層の下にある層を任意の半導体製造プロセスにかけることを含み得る。例えば、処理は、マスク層を通して下にある層に行う、イオン注入、拡散ドーピング、堆積、酸化（特にポリマーマスクの下のハードマスクを使用）、窒化、などを含み得る。加えて、マスク層は化学機械研磨（CMP）のための停止層もしくは障壁として使用することができ、あるいは、CMPは、2005年8月31日出願のU.S. Patent Application No. 11/216,477で述べられるように、下にある層の平坦化とエッティングの両方を可能にするために、いずれの層に対しても行うことができる。この全開示は本明細書に引用により組み込まれる。

#### 【0059】

本発明は様々な態様を含むことが、本明細書の記載から理解されるだろう。例えば、本発明の一態様に従って、集積回路製造のための方法が提供される。この方法は、基板の上にフォトレジストパターンを形成するために、第一のフォトレジスト層をパターニングするステップを含む。フォトレジストパターンは、フォトレジスト層の下にあるハードマスク層と、ハードマスク層の下にある一時層に転写される。パターニングされたハードマスク層および一時層内の要素の側壁にスペーサーが形成される。スペーサーと、パターニングされたハードマスク層および一時層の上に第二のフォトレジスト層が堆積される。パターニングされたハードマスク層および一時層の他の部分の真上、および他のスペーサーの真上にフォトレジストを残しながら、パターニングされたハードマスク層および一時層の一部を露出し、かつスペーサーの一部を露出するために、第二のフォトレジスト層がパターニングされる。パターニングされたハードマスク層および一時層の露出された部分は、その後優先的に除去される。第二のフォトレジスト層は優先的に除去される。

#### 【0060】

本発明の別の態様に従って、集積回路を形成するための方法が提供される。方法は、部分的に製造された集積回路の、アレイ領域内のアレイマスク要素と、周辺領域内の周辺マスク要素とを同時に画定するために、選択的に画定可能な層をパターニングするステップを含む。その後、複数の自立スペーサーを形成するために、アレイ領域内でピッチマルチプリケーションが行われる。自立スペーサーと周辺マスク要素によって少なくとも部分的に画定されるパターンは、同時に基板に転写される。

#### 【0061】

本発明のなお別の態様に従って、集積回路を製造するための方法が提供される。方法は、基板にその上を覆うフォトレジスト層を設けるステップを含む。フォトレジスト層はフォトリソグラフィー技術を用いてパターニングされ、その結果、ボイドによって分離されたフォトレジスト材料を含むフォトレジストパターンを形成する。フォトレジスト材料およびボイドは、集積回路のアレイ領域と周辺領域に広がる。フォトレジストパターンは、一時層パターンを形成するために、下にある一時層に転写される。一時層パターン内の要素は、その後アレイ領域と周辺領域の両方において縮小される。スペーサー材料のブランケット層が一時層要素の上に堆積される。ブランケット層は、一時層要素の側面にスペーサーを形成するためにエッティングされる。

#### 【0062】

本発明の別の態様に従って、部分的に製造された集積回路が提供される。部分的に製造された集積回路は、ハードマスク層の上にある複数のマスク要素を含む。ハードマスク層は基板の上にある。スペーサーがマスク要素の側壁に配置される。保護層がスペーサーの一部とマスク要素の一部の真上にある。保護層はまた、他のスペーサーと他のマスク要素

10

20

30

40

50

を露出されたままにする。

【0063】

本発明のなおも別の態様に従って、部分的に製造された集積回路が提供される。部分的に製造された集積回路は、基板の上に複数のスペーサーのペアを含む。各スペーサーのペアを構成するスペーサーは、選択的にエッチング可能な材料によって分離される。パターニングされたフォトレジスト層はスペーサーのペアの一部の上にある。フォトレジストは、部分的に製造された集積回路の周辺もしくはインターフェース領域内の少なくとも一部のスペーサーの上にあり、一方部分的に製造された集積回路のアレイ領域内のスペーサーは露出される。

【0064】

本発明の別の態様に従って、部分的に製造された集積回路が提供される。部分的に製造された集積回路は、部分的に製造された集積回路のアレイ領域の上に配置された複数の自立スペーサーのペアを含む。他の複数のスペーサーのペアは、複数のスペーサーのペアと同じ面上に配置される。他のスペーサーのペアの各々を構成するスペーサーは、他のスペーサーのペアと比べて選択的にエッチング可能な一時材料の側壁に配置される。一時材料には一つ以上の開口部が備わっている。

【0065】

上記の開示に加えて、様々な省略、追加、修正が、本発明の範囲から逸脱することなく、上述の方法と構造になされてもよいことも、当業者によって理解されるだろう。そのような修正および変更の全ては、添付の請求の範囲によって規定されるように、本発明の範囲内に含まれることを意図している。

10

20

【図1A】

FIG. 1A

(PRIOR ART)

【図1B】

FIG. 1B

(PRIOR ART)

【図 1 C】

FIG. 1C

(PRIOR ART)

【図 1 D】

FIG. 1D

(PRIOR ART)

【図 1 E】

FIG. 1E

(PRIOR ART)

【図 1 F】

FIG. 1F

(PRIOR ART)

【図2A】

FIG. 2A

【 図 2 B 】

FIG. 2B

【 四 3 】

FIG. 3

【 四 4 】

FIG. 4

【 义 5 】

FIG. 5

【 囮 6 】

FIG. 6

【図7A】

FIG. 7A

【図7B】

FIG. 7B

【図 8】

【図 10B】

FIG. 10B

【図 11】

FIG. 11

【図 12】

FIG. 12

【図 13】

FIG. 13

【図14】

FIG. 14

---

フロントページの続き

|                         |                    |

|-------------------------|--------------------|

| (51)Int.Cl.             | F I                |

| H 01 L 29/788 (2006.01) | H 01 L 27/10 4 6 1 |

| H 01 L 29/792 (2006.01) | H 01 L 27/10 4 8 1 |

| H 01 L 27/10 (2006.01)  | G 03 F 7/20 5 2 1  |

| G 03 F 7/20 (2006.01)   |                    |

(72)発明者 ラッセル, ステファン

アメリカ合衆国, アイダホ州 83716, ボイズ, イースト ステージライン ドライブ 55

41

(72)発明者 マニング, エイチ. モントゴメリー

アメリカ合衆国, アイダホ州 83616, イーグル, ウエスト ハウスランド コート 369

5

審査官 植木 隆和

(56)参考文献 米国特許出願公開第2006/0046484(US, A1)

特開平03-257825(JP, A)

特開平02-005522(JP, A)

特開2006-019496(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/027

G 03 F 7/20