(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7548232号

(P7548232)

(45)発行日 令和6年9月10日(2024.9.10)

(24)登録日 令和6年9月2日(2024.9.2)

(51)国際特許分類

|        |                  |        |       |         |

|--------|------------------|--------|-------|---------|

| H 01 L | 21/28 (2006.01)  | H 01 L | 21/28 | 3 0 1 S |

| H 01 L | 29/12 (2006.01)  | H 01 L | 21/28 | 3 0 1 B |

| H 01 L | 29/78 (2006.01)  | H 01 L | 29/78 | 6 5 2 T |

| H 01 L | 29/739 (2006.01) | H 01 L | 29/78 | 6 5 3 A |

| H 01 L | 21/336 (2006.01) | H 01 L | 29/78 | 6 5 2 M |

請求項の数 10 (全21頁) 最終頁に続く

(21)出願番号 特願2021-533082(P2021-533082)

(86)(22)出願日 令和2年7月14日(2020.7.14)

(86)国際出願番号 PCT/JP2020/027413

(87)国際公開番号 WO2021/010405

(87)国際公開日 令和3年1月21日(2021.1.21)

審査請求日 令和5年3月22日(2023.3.22)

(31)優先権主張番号 特願2019-131803(P2019-131803)

(32)優先日 令和1年7月17日(2019.7.17)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 000002130

住友電気工業株式会社

大阪府大阪市中央区北浜四丁目5番33号

(74)代理人 100107766

弁理士 伊東 忠重

(74)代理人 100070150

弁理士 伊東 忠彦

(72)発明者 玉祖 秀人

大阪府大阪市中央区北浜四丁目5番33号 住友電気工業株式会社内

審査官 佐藤 靖史

最終頁に続く

(54)【発明の名称】 炭化珪素半導体装置の製造方法及び炭化珪素半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

炭化珪素基板を準備する工程と、

前記炭化珪素基板の一方の主面に絶縁膜を形成する工程と、

前記絶縁膜にコンタクトホールを形成し、前記コンタクトホールの底面において、前記炭化珪素基板の一方の主面を露出させる工程と、

前記コンタクトホールの底面の上にSi膜を形成する工程と、

前記Si膜の上にNi膜を形成する工程と、

前記Ni膜を形成する工程の後、NiとSiとが反応する第1の温度で第1の熱処理を行う工程と、

前記第1の熱処理の後、ウェットエッチングにより、前記Ni膜のうち前記Si膜と反応していない未反応部を除去する工程と、

前記未反応部を除去する工程の後、前記第1の温度よりも高い第2の温度で第2の熱処理を行う工程と、

を有する炭化珪素半導体装置の製造方法。

## 【請求項2】

前記コンタクトホールの底面の上にSi膜を形成する工程は、

前記コンタクトホールの底面及び側面と、前記絶縁膜の上面とに第1Si膜を形成する工程と、

前記第1Si膜を形成する工程の後、少なくとも前記絶縁膜の上面の前記第1Si膜を

ドライエッティングにより除去する工程と、

を有する請求項 1 に記載の炭化珪素半導体装置の製造方法。

【請求項 3】

前記第 1 の温度は、 200 以上、 400 以下である請求項 1 または請求項 2 に記載の炭化珪素半導体装置の製造方法。

【請求項 4】

前記第 2 の温度は、 800 以上、 1100 以下である請求項 1 から請求項 3 のいずれか一項に記載の炭化珪素半導体装置の製造方法。

【請求項 5】

前記コンタクトホールの底面における前記 Si 膜の膜厚は、 5 nm 以上、 100 nm 以下である請求項 1 から請求項 4 のいずれか一項に記載の炭化珪素半導体装置の製造方法。 10

【請求項 6】

前記コンタクトホールの底面における前記 Ni 膜の膜厚は、 5 nm 以上、 100 nm 以下である請求項 1 から請求項 5 のいずれか一項に記載の炭化珪素半導体装置の製造方法。

【請求項 7】

前記 Si 膜は、 前記コンタクトホールの側面にも形成されている請求項 1 から請求項 6 のいずれか一項に記載の炭化珪素半導体装置の製造方法。

【請求項 8】

前記 Si 膜の上に前記 Ni 膜が形成された状態の前記コンタクトホールの底面において、 前記 Si 膜に含まれる厚さ方向に積算される単位面積当たりの Si 原子の数を  $N_{Si}$ 、 前記 Ni 膜に含まれる厚さ方向に積算される単位面積当たりの Ni 原子の数を  $N_{Ni}$  としたとき、  $N_{Ni} - N_{Si} / 2$  の関係が成り立つ請求項 1 から請求項 7 のいずれか一項に記載の炭化珪素半導体装置の製造方法。 20

【請求項 9】

主面を有する炭化珪素基板と、

前記炭化珪素基板の主面上に設けられた絶縁膜と、

前記絶縁膜に設けられたコンタクトホールと、

前記コンタクトホールの底面の一部に設けられ、 前記炭化珪素基板と接触している第 1 の電極と、

前記コンタクトホールの側面に、 前記第 1 の電極から離れて設けられた第 2 の電極と、 30

を有し、

前記第 1 の電極は、 Si と Ni とを含み、 前記炭化珪素基板とオーミックコンタクトしている炭化珪素半導体装置。

【請求項 10】

前記コンタクトホールの底面において、 前記第 1 の電極と前記第 2 の電極との間の距離は、 0.1 μm 以上、 1 μm 以下である請求項 9 に記載の炭化珪素半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、 炭化珪素半導体装置の製造方法及び炭化珪素半導体装置に関する。 40

【0002】

本出願は、 2019 年 7 月 17 日出願の日本出願第 2019-131803 号に基づく優先権を主張し、 前記日本出願に記載された全ての記載内容を援用するものである。

【背景技術】

【0003】

炭化珪素半導体装置の製造工程においては、 ドレイン電極等を形成する際に、 炭化珪素基板の表面に Ni (ニッケル) 膜を形成し、 熱処理をすることにより、 炭化珪素基板に含まれる Si (シリコン) と Ni とにより合金化し、 オーミック電極を形成する工程がある。

【先行技術文献】

【特許文献】

**【0004】**

【文献】日本国特開2005-276978号公報

【文献】日本国特開2017-175115号公報

【文献】日本国特開2012-99598号公報

**【発明の概要】****【0005】**

本開示の炭化珪素半導体装置の製造方法は、炭化珪素基板を準備する工程と、炭化珪素基板の一方の正面に絶縁膜を形成する工程と、前記絶縁膜にコンタクトホールを形成し、前記コンタクトホールの底面において、前記炭化珪素基板の一方の正面を露出させる工程と、コンタクトホールの底面の上にSi膜を形成する工程と、を有する。更に、Si膜の上にNi膜を形成する工程と、前記Ni膜を形成する工程の後、NiとSiとが反応する第1の温度で第1の熱処理を行う工程と、第1の熱処理の後、ウェットエッチングにより、前記Ni膜のうち前記Si膜と反応していない未反応部を除去する工程と、前記未反応部を除去する工程の後、第1の温度よりも高い第2の温度で第2の熱処理を行う工程と、を有する。

10

**【図面の簡単な説明】****【0006】**

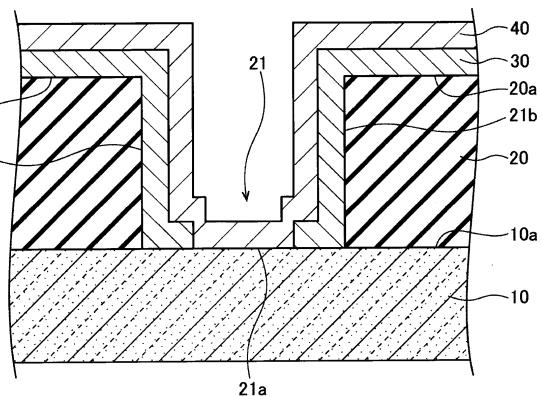

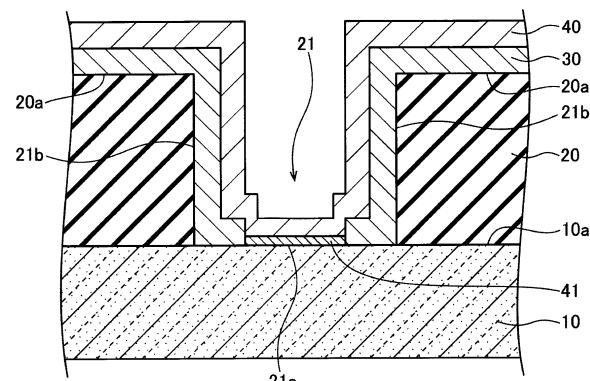

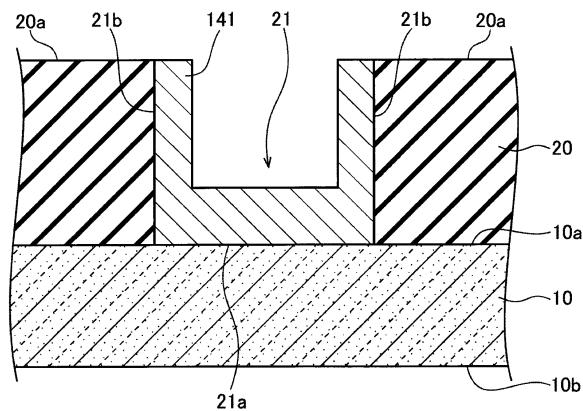

【図1】図1は、半導体装置の製造方法の説明図(1)である。

【図2】図2は、半導体装置の製造方法の説明図(2)である。

20

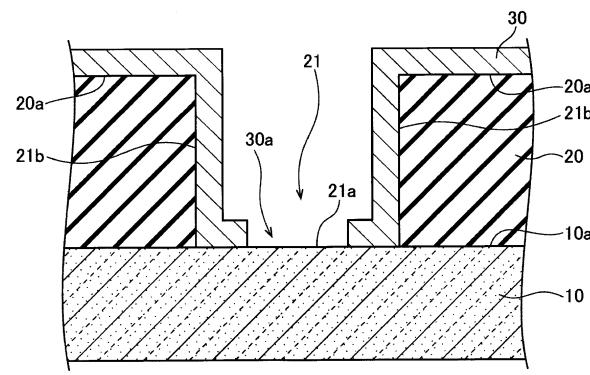

【図3】図3は、半導体装置の製造方法の説明図(3)である。

【図4】図4は、半導体装置の製造方法の説明図(4)である。

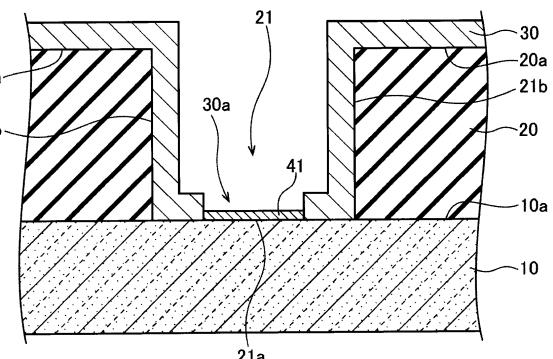

【図5】図5は、半導体装置の製造方法の説明図(5)である。

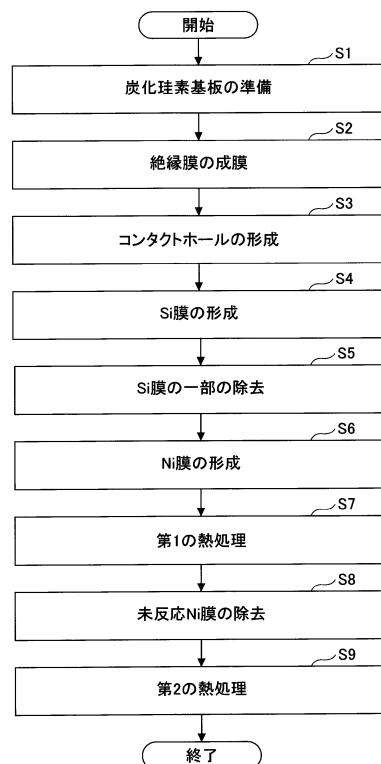

【図6】図6は、本開示の第1の実施形態の半導体装置の製造方法のフローチャートである。

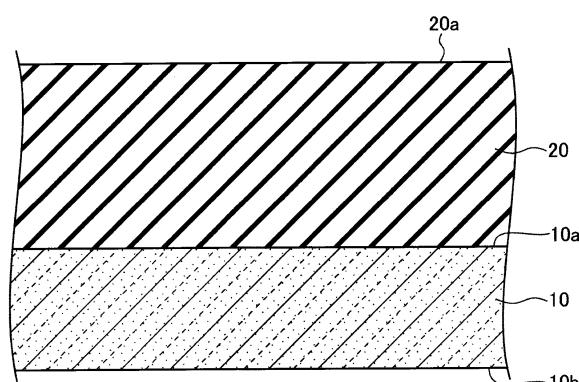

【図7】図7は、本開示の第1の実施形態の半導体装置の製造方法の説明図(1)である。

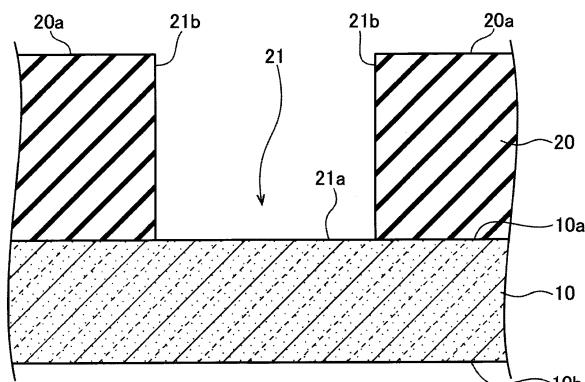

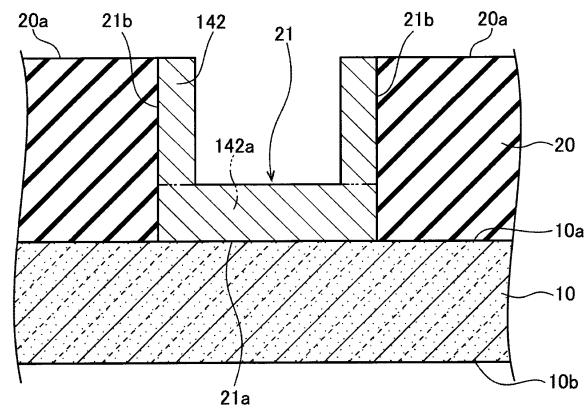

【図8】図8は、本開示の第1の実施形態の半導体装置の製造方法の説明図(2)である。

【図9】図9は、本開示の第1の実施形態の半導体装置の製造方法の説明図(3)である。

【図10】図10は、本開示の第1の実施形態の半導体装置の製造方法の説明図(4)である。

【図11】図11は、本開示の第1の実施形態の半導体装置の製造方法の説明図(5)である。

30

【図12】図12は、本開示の第1の実施形態の半導体装置の製造方法の説明図(6)である。

【図13】図13は、本開示の第1の実施形態の半導体装置の製造方法の説明図(7)である。

【図14】図14は、本開示の第1の実施形態の半導体装置の製造方法の説明図(8)である。

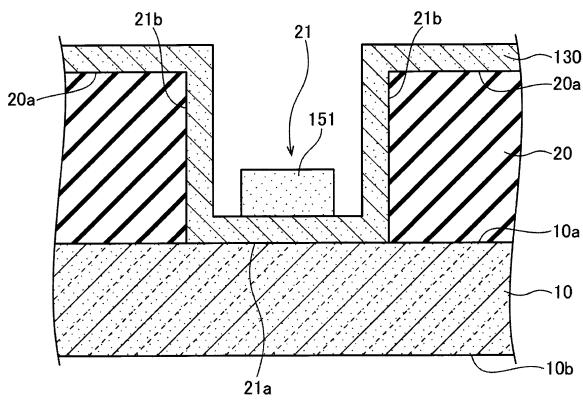

【図15】図15は、本開示の第1の実施形態の半導体装置の変形例1の製造方法の説明図(1)である。

【図16】図16は、本開示の第1の実施形態の半導体装置の変形例1の製造方法の説明図(2)である。

40

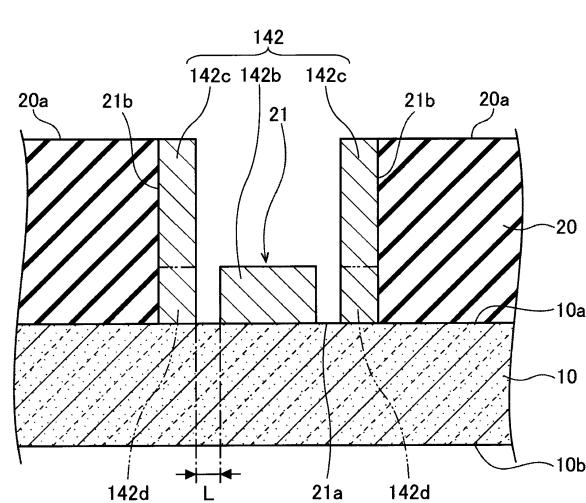

【図17】図17は、本開示の第1の実施形態の半導体装置の変形例2の製造方法の説明図(1)である。

【図18】図18は、本開示の第1の実施形態の半導体装置の変形例2の製造方法の説明図(2)である。

【図19】図19は、本開示の第1の実施形態の半導体装置の変形例3の製造方法の説明図である。

【図20】図20は、本開示の第1の実施形態の半導体装置の説明図である。

【図21】図21は、本開示の第2の実施形態の半導体装置の製造方法の説明図(1)である。

50

【図22】図22は、本開示の第2の実施形態の半導体装置の製造方法の説明図(2)である。

【図23】図23は、本開示の第2の実施形態の半導体装置の製造方法の説明図(3)である。

【図24】図24は、本開示の第2の実施形態の半導体装置の製造方法の説明図(4)である。

【図25】図25は、本開示の第2の実施形態の半導体装置の製造方法の説明図(5)である。

【図26】図26は、本開示の第2の実施形態の半導体装置の製造方法の説明図(6)である。

【図27】図27は、本開示の第2の実施形態の半導体装置の製造方法の説明図(7)である。

【図28】図28は、本開示の第2の実施形態の半導体装置の変形例の製造方法の説明図(1)である。

【図29】図29は、本開示の第2の実施形態の半導体装置の変形例の製造方法の説明図(2)である。

【図30】図30は、本開示の第2の実施形態の半導体装置の変形例の製造方法の説明図(3)である。

【図31】図31は、本開示の第2の実施形態の半導体装置の変形例の製造方法の説明図(4)である。

#### 【発明を実施するための形態】

##### 【0007】

###### [本開示が解決しようとする課題]

炭化珪素基板は、Siの他にC(炭素)が含まれているため、炭化珪素に含まれるSiがNiとの合金化に用いられると、未反応のCが生じ、この未反応のCが合金化されたオーム電極の表面等に析出する場合がある。このように、オーム電極の表面にCが析出すると、オーム電極の上に、金属配線層を形成した際に、信頼性の低下等を招くおそれがある。

##### 【0008】

このため、オーム電極の表面に炭素が析出することなく、オーム電極を形成できる炭化珪素半導体装置の製造方法が求められている。

##### 【0009】

###### [本開示の効果]

本開示によれば、炭化珪素基板の表面にオーム電極を形成する際に、炭素がオーム電極の表面に析出することを抑制できる。

##### 【0010】

実施するための形態について、以下に説明する。

##### 【0011】

###### [本開示の実施形態の説明]

最初に本開示の実施態様を列記して説明する。以下の説明では、同一または対応する要素には同一の符号を付し、それらについて同じ説明は繰り返さない。

##### 【0012】

[1] 本開示の一態様に係る半導体装置の製造方法は、炭化珪素基板を準備する工程と、前記炭化珪素基板の一方の正面に絶縁膜を形成する工程と、前記絶縁膜にコンタクトホールを形成し、前記コンタクトホールの底面において、前記炭化珪素基板の一方の正面を露出させる工程と、前記コンタクトホールの底面の上にSi膜を形成する工程と、前記Si膜の上にNi膜を形成する工程と、前記Ni膜を形成する工程の後、NiとSiとが反応する第1の温度で第1の熱処理を行う工程と、前記第1の熱処理の後、ウェットエッチングにより、前記Ni膜のうち前記Si膜と反応していない未反応部を除去する工程と、前記未反応部を除去する工程の後、前記第1の温度よりも高い第2の温度で第2の熱処

10

20

30

40

50

理を行う工程と、を有する。

【0013】

これにより、オーミック電極の表面において炭素を析出させることなく、炭化珪素基板の表面にオーミック電極を形成できる。

【0014】

〔2〕前記コンタクトホールの底面の上にSi膜を形成する工程は、前記コンタクトホールの底面及び側面と、前記絶縁膜の上面とに第1Si膜を形成する工程と、前記第1Si膜を形成する工程の後、少なくとも前記絶縁膜の上面の前記第1Si膜をドライエッチングにより除去する工程と、を有する。

【0015】

これにより、ニッケルシリサイドの反応前駆体が形成される領域が決定される。一般的にドライエッチングが難しいNiではドライエッチングによる微細加工ができないが、第1Si膜をドライエッチングすることにより、ニッケルシリサイドの反応前駆体をドライエッチングと同等の微細加工精度で形成できる。

【0016】

〔3〕前記第1の温度は、200以上、400以下である。

【0017】

これにより、ニッケルシリサイドの反応前駆体層を形成できる。

【0018】

〔4〕前記第2の温度は、800以上、1100以下である。

【0019】

これにより、反応前駆体層により、炭化珪素基板の正面と接触している部分にオーミック電極を形成できる。

【0020】

〔5〕前記コンタクトホールの底面における前記Si膜の膜厚は、5nm以上、100nm以下である。

【0021】

Si膜が5nmより薄いと、面内の局所ばらつきが、数nmのばらつきであっても、影響を無視することができず、プロセスを制御しにくくなる。また、膜厚が100nmより厚くなると、Ni膜との反応するには量が多くなりすぎ、不均一な反応前駆体ができてしまうからである。

【0022】

〔6〕前記コンタクトホールの底面における前記Ni膜の膜厚は、5nm以上、100nm以下である。

【0023】

Ni膜が5nmより薄いと、面内の局所ばらつきが、数nmのばらつきであっても、影響を無視することができず、プロセスを制御しにくくなる。また、膜厚が100nmより厚くなると、Si膜との反応するには量が多くなりすぎ、不均一な反応前駆体ができてしまうからである。

【0024】

〔7〕前記Si膜は、前記コンタクトホールの側面にも形成されている。

【0025】

一般にドライエッチングは垂直方向にエッチングレートが早く、横方向のエッチングレートが遅いため、コンタクトホールの底面だけ残そうとしても、側面にも残ることがある。もちろんプロセスを工夫することで除去することも可能である。

【0026】

〔8〕前記Si膜の上に前記Ni膜が形成された状態の前記コンタクトホールの底面において、前記Si膜に含まれる厚さ方向に積算される単位面積当たりのSi原子の数をN<sub>Si</sub>、前記Ni膜に含まれる厚さ方向に積算される単位面積当たりのNi原子の数をN<sub>Ni</sub>としたとき、N<sub>Ni</sub> / N<sub>Si</sub> / 2の関係が成り立つ。

10

20

30

40

50

## 【0027】

炭化珪素とニッケル単体を反応させたときオーミック電極を作ったとき、Ni<sub>2</sub>Siが主成分として形成される。本実施形態において反応前駆体をこの組成に合わせるために原子数をNi:Si = 2:1に合わせる必要がある。また、この組成からNiの量を増やすことで炭化珪素との反応性がよくなる。逆にこの組成からNiが減ると、Niが不足気味になり炭化珪素と反応しにくくなるからである。

## 【0028】

[9] 主面を有する炭化珪素基板と、前記炭化珪素基板の主面上に設けられた絶縁膜と、前記絶縁膜に設けられたコンタクトホールと、前記コンタクトホールの底面の一部に設けられ、前記炭化珪素基板と接触している第1の電極と、前記コンタクトホールの側面に、前記第1の電極から離れて設けられた第2の電極と、を有し、前記第1の電極は、SiとNiとを含み、前記炭化珪素基板とオーミックコンタクトしている。

10

## 【0029】

コンタクトホール底面に必要最小限の範囲でオーミック電極を形成し、不要な箇所には形成しないことができる。特にコンタクトホールの側面はエッチングダメージが残りやすいため、第2の電極をバリア膜として活用できる。またコンタクトホールの底面と、コンタクトホールの側面の電極を分離することで、基板や絶縁膜にかかる応力を緩和できるからである。

## 【0030】

[10] 前記コンタクトホールの底面において、前記第1の電極と前記第2の電極との間の距離は、0.1 μm以上、1 μm以下である。

20

## 【0031】

0.1 μmより短いと加工精度の問題により局所的に分離できない箇所が発生し始める。また1 μm以下であれば一般的な加工精度のばらつきでマージンをもって対応できるし、1 μmを超えるとデバイスの抵抗が高くなるからである。

## 【0032】

## [本開示の実施形態の詳細]

以下、本開示の一実施形態について詳細に説明するが、本実施形態はこれらに限定されるものではない。

## 【0033】

30

## [第1の実施形態]

最初に、炭化珪素半導体装置の製造方法において、炭化珪素基板の表面にオーミック電極を形成する工程について説明する。炭化珪素基板の表面に、オーミック電極を形成する際には、炭化珪素基板の表面に、スパッタリングによりNi膜を形成した後、ウェットエッチング等により、不要なNi膜を除去する。この後、加熱することにより、炭化珪素基板に含まれるSiとNiとを合金化させて、オーミック電極となるニッケルシリサイド膜を形成する。この際、Niとの合金化のために炭化珪素基板の表面のSiが奪われるため、未反応のCがニッケルシリサイド膜の表面に析出する。この後、スパッタリングによりAl膜を形成し配線層を形成した場合、オーミック電極となるニッケルシリサイド膜の表面にCが析出していると、Al膜が剥がれやすいため、信頼性の低下を招く。

40

## 【0034】

このための対策として様々な方法が検討されている。

## 【0035】

例えば、炭化珪素基板の表面に、NiとSiを含む膜を形成した後、所望の領域以外のNiとSiを含む膜を除去して、熱処理をする方法が考えられる。この方法では、NiとSiを含む膜のNiとSiとを合金化させ、オーミック電極を形成する。このため、オーミック電極を形成する際に、炭化珪素基板に含まれるSiが奪われることは殆どないため、Cの析出を極力防ぐことができる。

## 【0036】

しかしながら、Niはドライエッチングによる除去が困難であり、Siはウェットエッ

50

チングによる除去が困難であるため、NiとSiを含む膜は、ドライエッチングでもウェットエッチングでも除去することが困難である。また、所望の領域にNiとSiを含む膜を形成する方法としては、リフトオフにより形成する方法が挙げられるが、リフトオフでは、剥離した膜が再付着する場合があり、信頼性の低下を招くため好ましくはない。

#### 【0037】

従って、炭化珪素基板の表面に、NiとSiを含む膜を形成して熱処理をする方法では、所望の領域以外の領域のNiとSiを含む膜を除去することは困難であるため、所望の領域にNiとSiを含む膜を残すことは容易ではない。

#### 【0038】

また、上記以外の方法としては、レジスト等を用いることなくオーミック電極を形成する方法が考えられる。

#### 【0039】

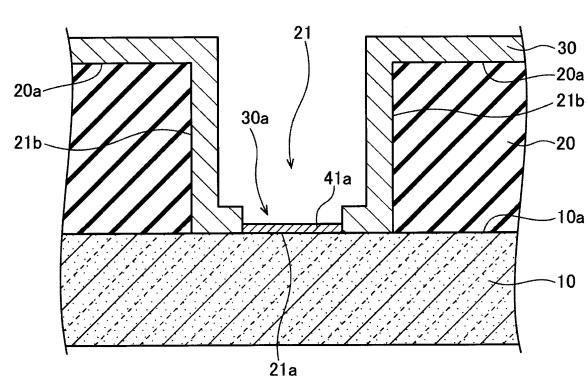

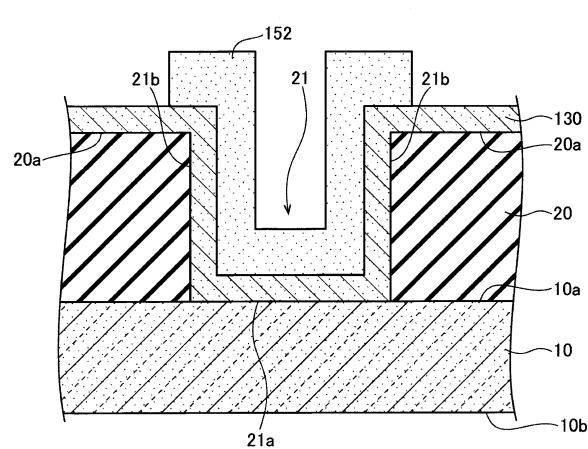

具体的には、最初に、図1に示されるように、炭化珪素基板10の表面となる主面10aに、コンタクトホール21を有する層間絶縁膜となる絶縁膜20を形成し、コンタクトホール21及び絶縁膜20を覆うTiN膜30を形成する。この後、コンタクトホール21の底面21aのTiN膜30を除去することにより開口部30aを形成し、炭化珪素基板10の主面10aを露出させる。これにより、コンタクトホール21の側面21bの絶縁膜20及び絶縁膜20の上面20aは、TiN膜30により覆われる。

#### 【0040】

次に、図2に示されるように、スパッタリングによりNi膜40を形成する。これにより、コンタクトホール21の底面21aにおいて露出している炭化珪素基板10の主面10a、及び、TiN膜30の上に、Ni膜40が形成される。

#### 【0041】

次に、図3に示されるように、500～700の温度で熱処理をすることにより、炭化珪素基板10とNi膜40との界面において、NiとSiとが合金化したニッケルシリサイドの反応前駆体層41が形成される。尚、TiN膜30は、この熱処理において、Niが絶縁膜20に進入することを防ぐために設けられている。

#### 【0042】

次に、図4に示されるように、Ni膜40を希塩酸や希硝酸を用いたウェットエッチングにより除去する。これにより、TiN膜30の開口部30aの炭化珪素基板10の主面10aには、反応前駆体層41が残る。

#### 【0043】

次に、図5に示すように、反応前駆体層41を約1000の温度で熱処理をすることにより、オーミック電極41aが形成される。

#### 【0044】

このように形成されるオーミック電極41aは、厚さが数nmと極めて薄いため、この後の工程において、配線層を形成する際の逆スパッタリングにより、オーミック電極41aが除去されてしまう場合がある。また、この方法では、オーミック電極41aの表面に未反応のCが析出してしまう。

#### 【0045】

##### (半導体装置の製造方法)

次に、第1の実施形態における半導体装置の製造方法について、図6から図14に基づき説明する。図6は、本開示の第1の実施形態の半導体装置の製造方法のフローチャートである。図7～図14は、本開示の第1の実施形態の半導体装置の製造方法の工程図である。

#### 【0046】

最初に、図7に示されるように、一方の主面10aと、他方の主面10bとを有する炭化珪素基板10を準備し(ステップS1)、炭化珪素基板10の一方の主面10aに、層間絶縁膜となる膜厚が0.8μmの絶縁膜20をCVD(chemical vapor deposition)法により形成する(ステップS2)。絶縁膜20は、酸化シリコンにより形成されてい

10

20

30

40

50

る。

【0047】

次に、図8に示されるように、絶縁膜20にコンタクトホール21を形成する（ステップS3）。具体的には、絶縁膜20の上面20aに、フォトレジストを塗布し、露光装置による露光及び現像を行うことにより、コンタクトホール21が形成される領域に開口を有する不図示のレジストパターンを形成する。この後、RIE（Reactive Ion Etching）等のドライエッチングにより、レジストパターンの形成されていない領域の絶縁膜20を除去し、炭化珪素基板10の主面10aを露出させることによりコンタクトホール21を形成する。この後、不図示のレジストパターンは、有機溶剤等により除去する。これにより、底面21aが炭化珪素基板10の主面10aとなり、側面21bが絶縁膜20となるコンタクトホール21が形成される。

10

【0048】

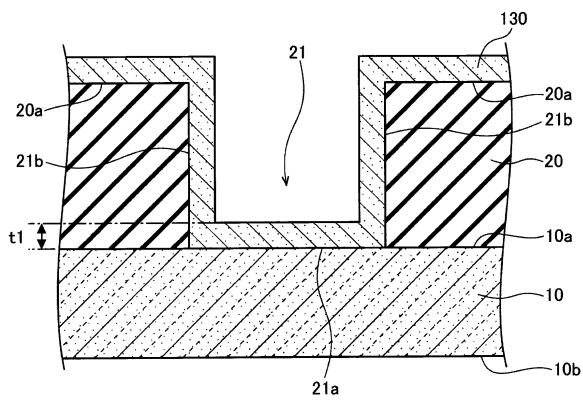

次に、図9に示されるように、コンタクトホール21の底面21a及び側面21b、絶縁膜20の上面20aを覆うSi膜130をスパッタリングにより形成する（ステップS4）。形成されるSi膜130の膜厚t1は、5nm以上、100nm以下である。Si膜130の膜厚t1は、Si膜130のうちコンタクトホール21の底面21aにおける厚さである。

【0049】

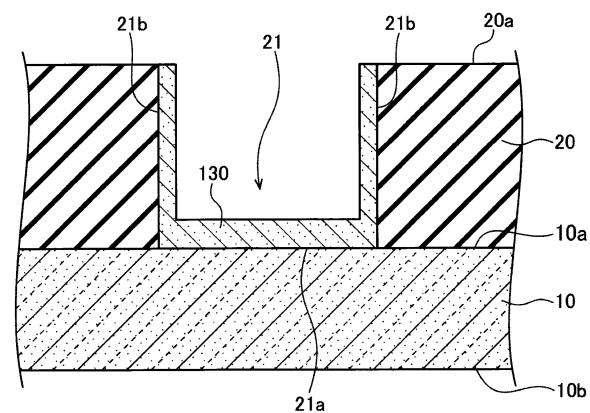

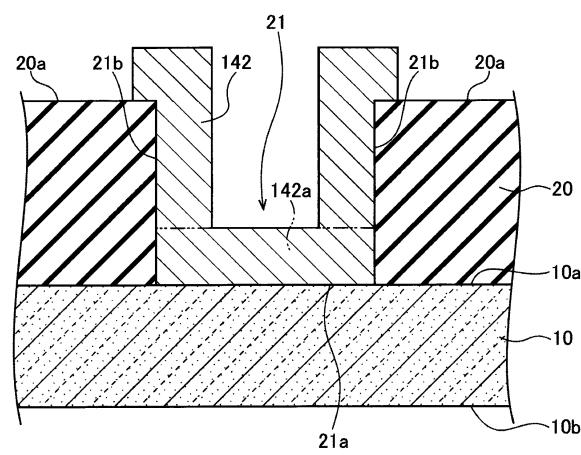

次に、図10に示されるように、絶縁膜20の上面20aのSi膜130を除去する（ステップS5）。具体的には、コンタクトホール21の底面21aを覆う不図示のレジストパターンを形成し、RIE等のドライエッチングにより、レジストパターンの形成されていない領域のSi膜130を除去する。エッチングガスには、フッ素系、または、塩素系のエッチングガスを用いる。この後、レジストパターンは有機溶剤等により除去する。これにより、コンタクトホール21の底面21a及び側面21bを覆うSi膜130が残る。RIE等のドライエッチングは、異方性を有するエッチングである。このため、レジストパターンの形成されていない領域の絶縁膜20の上面20aのSi膜130が完全に除去されても、コンタクトホール21の側面21bを覆うSi膜130は、完全には除去することはできず薄く残る。

20

【0050】

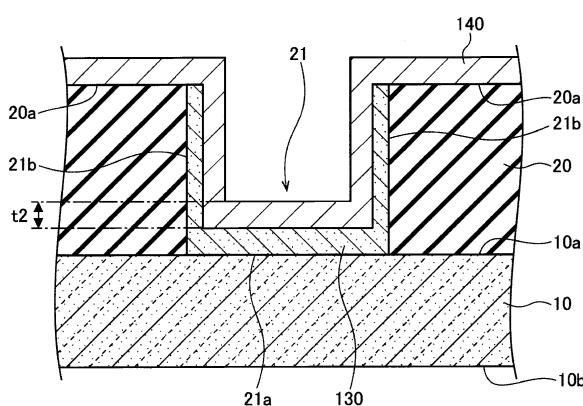

次に、図11に示されるように、コンタクトホール21の底面21a及び側面21bにおけるSi膜130の上、絶縁膜20の上面20aに、Ni膜140をスパッタリングにより形成する（ステップS6）。形成されるNi膜140の膜厚t2は、5nm以上、100nm以下である。Ni膜140の膜厚t2は、Ni膜140のうちコンタクトホール21の底面21aにおける厚さである。Si膜130及びNi膜140は、コンタクトホール21の底面21aにおいて、Si膜130に含まれる厚さ方向に積算される単位面積当たりのSi原子の数をN<sub>Si</sub>、Ni膜140に含まれる厚さ方向に積算される単位面積当たりのNi原子の数をN<sub>Ni</sub>としたとき、N<sub>Ni</sub> = N<sub>Si</sub> / 2の関係が成り立つような膜厚で形成する。尚、厚さ方向とは、Si膜130及びNi膜140の膜厚方向を意味するものとし、Si膜130及びNi膜140の膜面に対し垂直な方向である。

30

【0051】

次に、図12に示されるように、200以上、400以下、例えば、約350の温度で第1の熱処理を行う（ステップS7）。これにより、コンタクトホール21の底面21a及び側面21bにおけるSi膜130のSiとNi膜140のNiとが反応しニッケルシリサイドの反応前駆体層141が形成される。第1の熱処理における温度は、SiとNiとは反応するが、SiCに含まれるSiとNiとは反応しない温度である。本願においては、この温度を第1の温度と記載する場合がある。Ni膜140は、絶縁膜20の上面20aにも形成されているが、この工程の熱処理の温度である約350では、Ni膜140に含まれるNiが、絶縁膜20の内部に進入することはない。第1の温度は炭化珪素基板10の温度である。例えば、第1の熱処理は炉を用いて行われ、炭化珪素基板10の温度は炉内温度と実質的に等しい。

40

50

## 【0052】

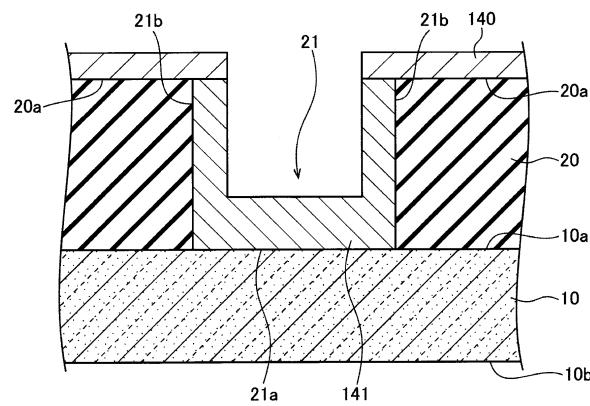

次に、図13に示されるように、ウェットエッティングにより、絶縁膜20の上面20aの未反応のNi膜140、すなわちNi膜140のうちSi膜130と反応していない部分を除去する(ステップS8)。これにより、コンタクトホール21の底面21a及び側面21bには、反応前駆体層141が残る。

## 【0053】

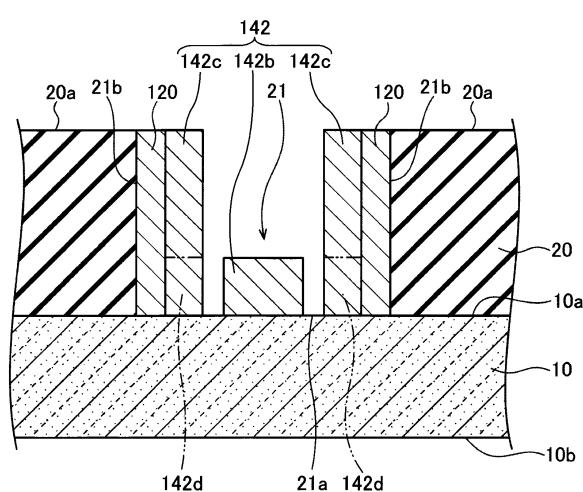

次に、図14に示されるように、800以上、1100以下、例えば、約1000の温度で第2の熱処理を行うことにより(ステップS9)、反応前駆体層141により、電極層142を形成する。電極層142は、炭化珪素基板10の正面10aとオーミック接触するオーミック領域142aを含む。オーミック領域142aはオーミック電極として機能し得る。この工程における温度は、第1の温度よりも高く、SiCに含まれるSiとNiとが反応する温度である。本願においては、この熱処理の工程の温度を第2の温度と記載する場合がある。第2の温度は炭化珪素基板10の温度である。例えば、第2の熱処理は炉を用いて行われ、炭化珪素基板10の温度は炉内温度と実質的に等しい。

10

## 【0054】

電極層142において、オーミック領域142aでは、炭化珪素基板10に含まれていたSiが進入している。

## 【0055】

本実施形態では、電極層142のオーミック領域142aを形成しているニッケルシリサイドは、殆どがSi膜130に含まれるSiと、Ni膜140に含まれるNiとにより形成されている。このため、第2の熱処理において、オーミック領域142aを形成する際には、反応前駆体層141に含まれる未反応の僅かなNiが、炭化珪素基板10から供給されるSiと反応する。このため、炭化珪素基板10から供給されるSiの量は僅かである。よって、未反応のCが生成される量も僅かであるため、電極層142の表面にCが析出することは殆どない。従って、電極層142の上にAl等の配線層を形成しても、電極層142の表面より剥がれることはない。尚、配線層は、TiNとAlとを順で積層した膜であってもよい。

20

## 【0056】

また、本実施形態においては、図1に示されるようなTiN膜の形成が不要となるため、炭化珪素半導体装置を製造する際の製造工程の工程数を減らすことができ、コストダウンを図ることができる。

30

## 【0057】

また、本実施形態においては、図11に示される状態では、コンタクトホール21の側面21bは、Si膜130により覆われているため、コンタクトホール21の側面21bを形成する酸化シリコンとNi膜140とは直接接触していない。よって、約1000の温度で第2の熱処理を行っても、絶縁膜20にNiが進入することではなく、絶縁膜20が劣化することはない。尚、酸化シリコンにより形成された絶縁膜にNi膜が直接接觸している場合には、加熱温度が500程度で、絶縁膜にNiが進入するため、絶縁膜が劣化する。

## 【0058】

40

## (変形例)

次に、本実施形態の変形例について説明する。

## 【0059】

本変形例は、図9に示す工程の後、Si膜130の上に形成される不図示のレジストパターンの大きさを変えることにより、残存するSi膜130の大きさを変えたものである。

## 【0060】

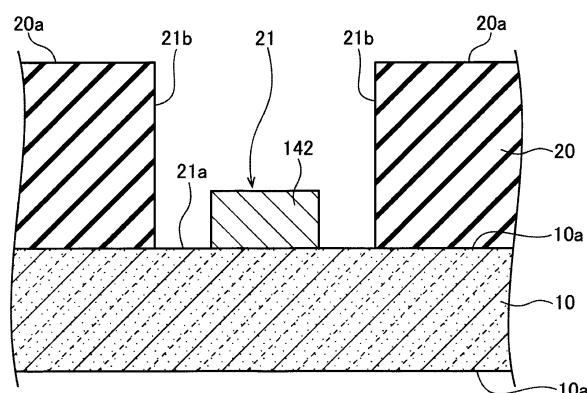

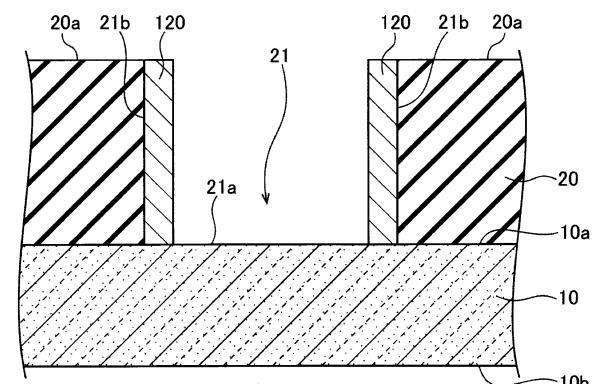

例えば、図9に示す工程(ステップS4)の後、図15に示されるように、コンタクトホール21の底面21aよりも狭い領域のSi膜130の上に、レジストパターン151を形成し、レジストパターン151の形成されていない領域のSi膜130を除去する。この後、上記と同様の工程(ステップS5～S9)を行うことにより、図16に示される

50

ように、コンタクトホール21の底面21aと接する第1の電極142bと、コンタクトホール21の側面21bと接する第2の電極142cとが、互いから離れて形成される。即ち、コンタクトホール21の底面21aにおいて、第1の電極142bと第2の電極142cとが互いから離れて形成される。第1の電極142bと第2の電極142cとの間の距離Lは、0.1μm以上、1μm以下が好ましい。尚、図16に示されるように、絶縁膜20の上面20aには、絶縁膜20と接触するN<sub>i</sub>膜は存在してはいない。

#### 【0061】

尚、第1の電極142bには炭化珪素基板10に含まれるSiが進入しており、第1の電極142bはオーミック電極として機能し得る。第2の電極142cは、炭化珪素基板10に含まれるSiが進入したオーミック領域142dを、炭化珪素基板10の主面10aの近傍に含み、オーミック領域142dはオーミック電極として機能し得る。第2の電極142cにおいて、オーミック領域142dよりも炭化珪素基板10の主面10aから離れた部分ではSiの進入はない。従って、第2の電極142cは、第1の電極142bよりも、含まれるSiの少ない部分が存在しており、よって、第2の電極142cには、第1の電極142bよりもSiの濃度の低い部分が存在している。

10

#### 【0062】

第1の電極142bが形成される際には、炭化珪素基板10より僅かにSiが進入するため、これに伴い、炭化珪素基板10に含まれる未反応のCも第1の電極142bに進入する。これに対し、第2の電極142cにおいては、炭化珪素基板10の主面10aの近傍では、未反応のCが進入する場合はあるが、第2の電極142cにおいて、炭化珪素基板10の主面10aから離れた部分では、未反応のCが進入することはない。従って、第2の電極142cには、Cを含まない領域が存在しており、よって、第1の電極142bのCの濃度よりも低い濃度の領域が存在している。

20

#### 【0063】

また、図9に示す工程（ステップS4）の後、図17に示されるように、コンタクトホール21の底面21aよりも広い領域のSi膜130の上に、レジストパターン152を形成し、レジストパターン152の形成されていない領域のSi膜130を除去する。この後、上記と同様の工程（ステップS5～S9）を行うことにより、図18に示されるように、電極層142は、コンタクトホール21の底面21a及び側面21bと、コンタクトホール21の近傍の絶縁膜20の上面20aに形成される。

30

#### 【0064】

また、図15に示されるように、コンタクトホール21の底面21aよりも狭い領域のSi膜130の上に、レジストパターン151を形成し、等方性のドライエッチングによりレジストパターン151が形成されていない領域のSi膜130を除去してもよい。この場合には、Si膜130は、側面21bには形成されず、コンタクトホール21の底面21aに形成されるため、図19に示すように、コンタクトホール21の底面21aにのみオーミック電極となる電極層142が形成される。

#### 【0065】

##### （半導体装置）

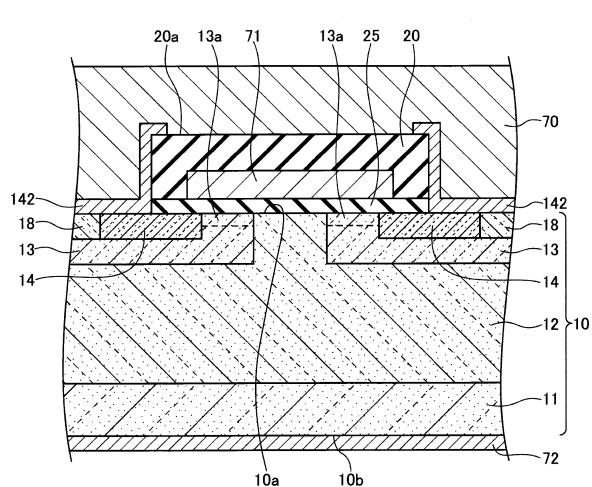

次に、第1の実施形態における半導体装置の一例について説明する。本実施形態における半導体装置は、図20に示されるように、例えば、縦型MOSFET（Metal Oxide Semiconductor Field Effect Transistor）である。具体的には、本実施形態における半導体装置は、炭化珪素基板10と、電極層142と、配線層70と、ゲート絶縁膜25と、ゲート電極71とを有し、ゲート電極71は、層間絶縁膜となる絶縁膜20に覆われている。炭化珪素基板10は、第1のn層11、第2のn層12、pボディ層13、nソース領域14、p領域18を有する。第1のn層11及びnソース領域14は、第2のn層12よりも多く不純物元素がドープされている。p領域18は、pボディ層13よりも多くの不純物元素がドープされている。

40

#### 【0066】

電極層142は、本実施形態における製造方法により製造されており、炭化珪素基板1

50

0 の一方の主面 10 a ( 図中の上面 ) 上において、 n ソース領域 14 にオーミックコンタクトしている。電極層 14 2 の厚さは、例えば、 100 ~ 200 nm 程度である。電極層 14 2 の上及び絶縁膜 20 の上面 20 a には、配線層 70 が形成されている。

#### 【 0067 】

ゲート電極 71 は、炭化珪素基板 10 の一方の主面 10 a ( 図中の上面 ) 上にゲート絶縁膜 25 を介して設けられており、 p ボディ層 13 の表面側であるチャネル領域 13 a に対向している。また炭化珪素基板 10 の他方の主面 10 b ( 図中の下面 ) 上にはドレイン電極 72 が設けられている。

#### 【 0068 】

本実施形態によれば、電極層 14 2 より配線層 70 が剥離しにくい縦型 MOSFET を得ることができる。

10

#### 【 0069 】

尚、炭化珪素基板 10 のドレイン電極 72 に面する側に p コレクタ層を形成することにより、縦型 MOSFET の代わりに縦型 IGBT ( Insulated Gate Bipolar Transistor ) としてもよい。また炭化珪素基板に形成されたトレンチ内にゲート絶縁膜を介してゲート電極が埋め込まれる構造 ( トレンチゲート構造 ) であってもよい。

#### 【 0070 】

##### 〔 第 2 の実施形態 〕

次に、第 2 の実施形態における半導体装置の製造方法について、図 21 から図 27 に基づき説明する。

20

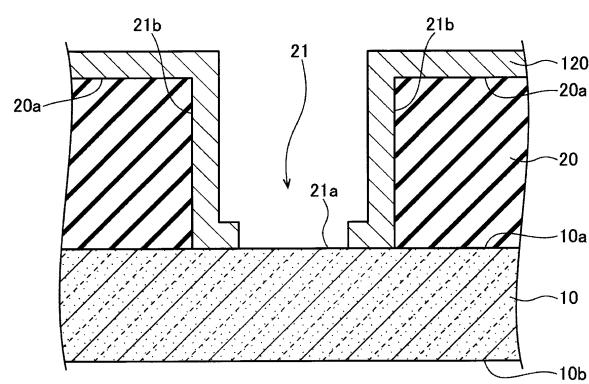

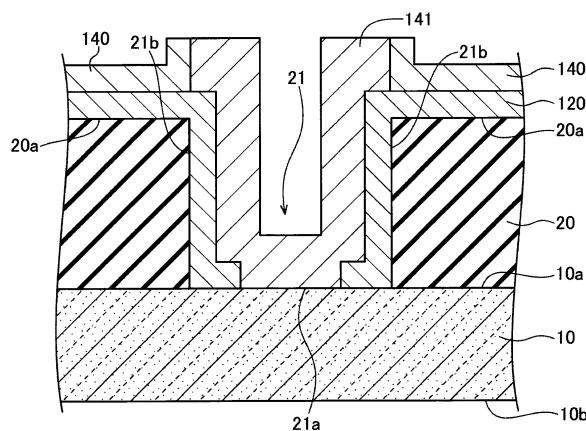

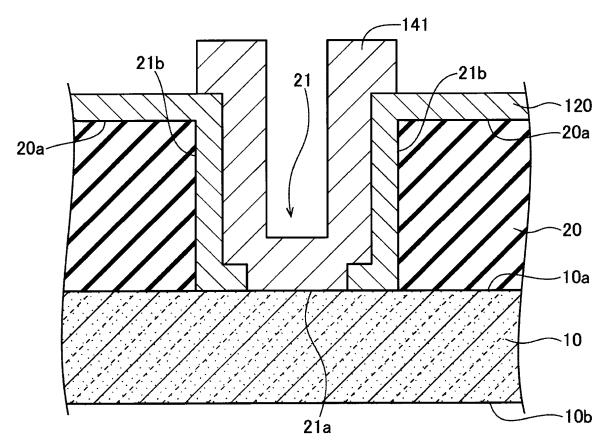

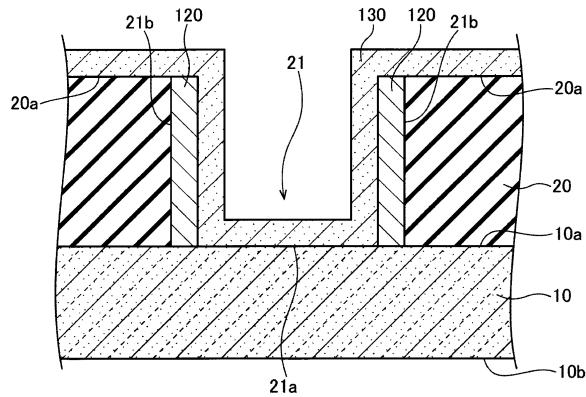

#### 【 0071 】

最初に、図 21 に示されるように、炭化珪素基板 10 の主面 10 a に、コンタクトホール 21 を有する絶縁膜 20 を形成し、コンタクトホール 21 及び絶縁膜 20 を覆う TiN 膜 120 をスパッタリングにより形成する。この後、コンタクトホール 21 の底面 21 a に形成されている TiN 膜 120 を一部除去し、炭化珪素基板 10 の主面 10 a を露出させる。尚、形成される TiN 膜 120 の膜厚は、 10 nm 以上、 200 nm 以下である。

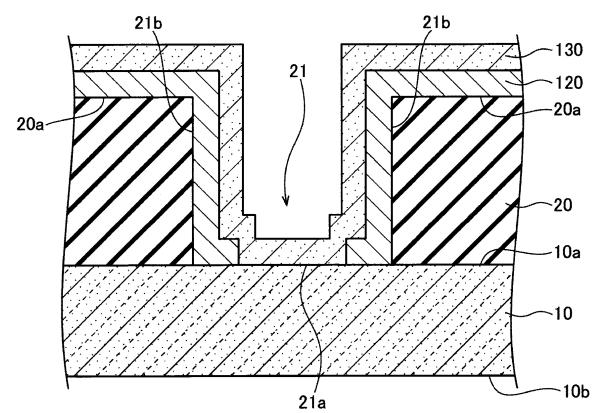

#### 【 0072 】

次に、図 22 に示されるように、露出している炭化珪素基板 10 の主面 10 a 、 TiN 膜 120 の上に、スパッタリングにより Si 膜 130 を形成する。

#### 【 0073 】

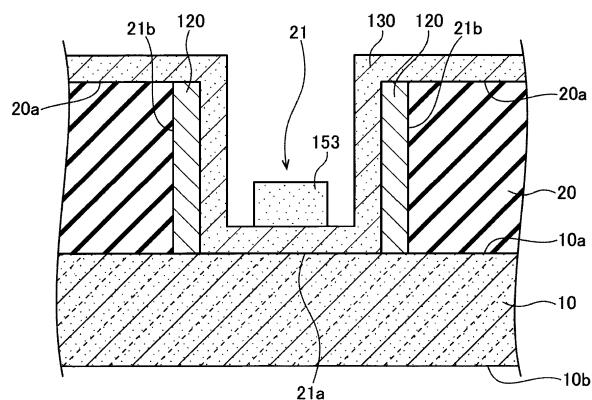

次に、図 23 に示されるように、 TiN 膜 120 を介した絶縁膜 20 の上面 20 a の上に形成された Si 膜 130 を除去する。この際、コンタクトホール 21 の近傍においては、 TiN 膜 120 を介した絶縁膜 20 の上面 20 a の上に、 Si 膜 130 の一部が残存していくてもよい。これにより、コンタクトホール 21 の底面 21 a 及び側面 21 b を覆う Si 膜 130 が残る。

30

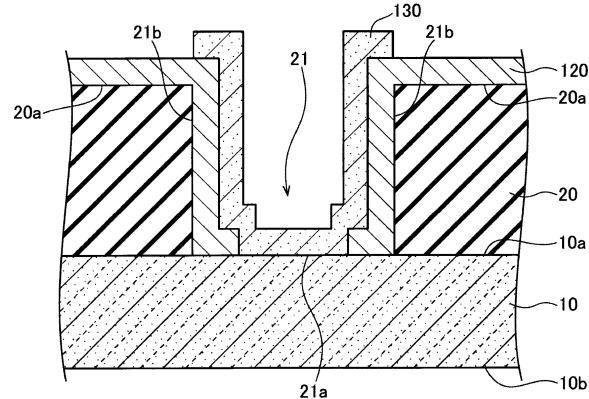

#### 【 0074 】

次に、図 24 に示されるように、 TiN 膜 120 及び Si 膜 130 の上に、 Ni 膜 140 をスパッタリングにより形成する。

#### 【 0075 】

次に、図 25 に示されるように、 300 ~ 400 、例えば、約 350 の温度で第 1 の熱処理を行う。これにより、 Si 膜 130 の Si と、 Si 膜 130 の上の Ni 膜 140 の Ni とにより、ニッケルシリサイドの反応前駆体層 141 が形成される。尚、 TiN 膜 120 の上の Ni 膜 140 がシリサイド化することはない。

40

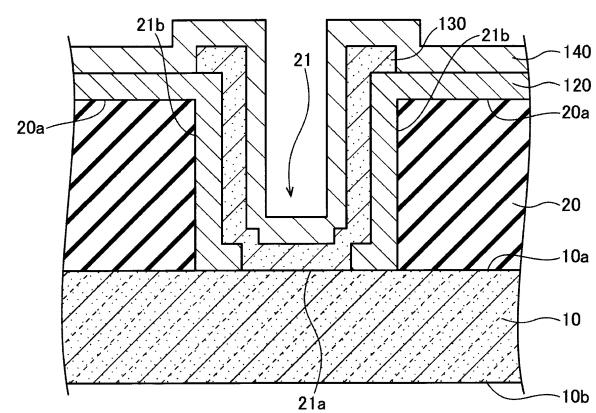

#### 【 0076 】

次に、図 26 に示されるように、ウェットエッチングにより未反応の Ni 膜 140 を除去する。これにより、コンタクトホール 21 の底面 21 a 及び側面 21 b には、反応前駆体層 141 が残る。

#### 【 0077 】

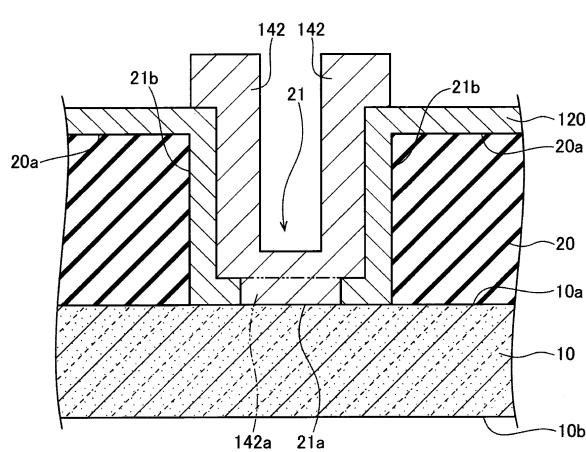

次に、図 27 に示されるように、約 1000 の温度で第 2 の熱処理を行うことにより、反応前駆体層 141 により、電極層 142 が形成される。電極層 142 は、炭化珪素基

50

板 1 0 の主面 1 0 a とオーミック接触するオーミック領域 1 4 2 a を含む。オーミック領域 1 4 2 a を形成する際に、炭化珪素基板 1 0 より供給される S i は僅かであるため、電極層 1 4 2 の表面に C が析出することは殆どない。よって、電極層 1 4 2 の上に A 1 等の配線層を形成しても、配線層が電極層 1 4 2 の表面より剥がれることはない。尚、配線層は、T i N と A 1 とを順で積層した膜であってもよい。

#### 【 0 0 7 8 】

##### ( 変形例 )

本変形例では、上記の図 2 1 に示す工程において、図 2 8 に示すように、T i N 膜 1 2 0 をコンタクトホール 2 1 の側面 2 1 b にのみに形成してもよい。この後、図 2 9 に示すように、T i N 膜 1 2 0 、コンタクトホール 2 1 の底面 2 1 a 及び絶縁膜 2 0 を覆う S i 膜 1 3 0 をスパッタリングにより形成する。この後、図 3 0 に示すように、コンタクトホール 2 1 の底面 2 1 a よりも狭い領域の S i 膜 1 3 0 の上に、レジストパターン 1 5 3 を形成し、レジストパターン 1 5 3 の形成されていない領域の S i 膜 1 3 0 を除去する。この後、上記と同様の工程（ステップ S 5 ~ S 9 ）を行うことにより、図 3 1 に示されるように、コンタクトホール 2 1 の底面 2 1 a において、第 1 の電極 1 4 2 b と第 2 の電極 1 4 2 c とが互いから離れて形成される。

#### 【 0 0 7 9 】

尚、上記以外の内容については、第 1 の本実施形態と同様である。

#### 【 0 0 8 0 】

以上、実施形態について詳述したが、特定の実施形態に限定されるものではなく、請求の範囲に記載された範囲内において、種々の変形及び変更が可能である。

#### 【 符号の説明 】

##### 【 0 0 8 1 】

|       |           |

|-------|-----------|

| 1 0   | 炭化珪素基板    |

| 1 0 a | 一方の主面     |

| 1 0 b | 他方の主面     |

| 1 1   | 第 1 の n 層 |

| 1 2   | 第 2 の n 層 |

| 1 3   | p ボディ層    |

| 1 4   | n ソース領域   |

| 1 8   | p 領域      |

| 2 0   | 絶縁膜       |

| 2 0 a | 上面        |

| 2 1   | コンタクトホール  |

| 2 1 a | 底面        |

| 2 1 b | 側面        |

| 2 5   | ゲート絶縁膜    |

| 3 0   | T i N 膜   |

| 3 0 a | 開口部       |

| 4 0   | N i 膜     |

| 4 1   | 反応前駆体層    |

| 4 1 a | オーミック電極   |

| 7 0   | 配線層       |

| 7 1   | ゲート電極     |

| 7 2   | ドレイン電極    |

| 1 2 0 | T i N 膜   |

| 1 3 0 | S i 膜     |

| 1 4 0 | N i 膜     |

| 1 4 1 | 反応前駆体層    |

| 1 4 2 | 電極層       |

10

20

30

40

50

1 4 2 a オーミック領域

1 4 2 b 第1の電極

1 4 2 c 第2の電極

1 4 2 d オーミック領域

1 5 1、1 5 2、1 5 3 レジストパターン

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図 5】

【図 6】

10

20

30

40

【図 7】

【図 8】

50

【図9】

【図10】

【図11】

【図12】

【図 1 3】

【図 1 4】

10

【図 1 5】

【図 1 6】

20

30

40

50

【図17】

【図18】

10

【図19】

【図20】

20

30

40

50

【図 2 1】

【図 2 2】

【図 2 3】

【図 2 4】

10

20

30

40

50

【図25】

【図26】

10

【図27】

【図28】

20

30

40

50

【図29】

【図30】

10

【図31】

20

30

40

50

## フロントページの続き

## (51)国際特許分類

| F I    |       |         |  |

|--------|-------|---------|--|

| H 01 L | 29/78 | 6 5 5 A |  |

| H 01 L | 29/78 | 6 5 8 F |  |

| H 01 L | 29/78 | 6 5 8 G |  |

| H 01 L | 29/78 | 6 5 8 Z |  |

## (56)参考文献

特開2013-058587(JP, A)

特開2005-276978(JP, A)

特開2018-050008(JP, A)

特開2010-103229(JP, A)

## (58)調査した分野 (Int.Cl., DB名)

|        |             |

|--------|-------------|

| H 01 L | 2 1 / 2 8   |

| H 01 L | 2 9 / 1 2   |

| H 01 L | 2 9 / 7 8   |

| H 01 L | 2 9 / 7 3 9 |

| H 01 L | 2 1 / 3 3 6 |