(10) DE 10 2018 005 216 A1 2019.02.21

(12)

## Offenlegungsschrift

(21) Aktenzeichen: 10 2018 005 216.9

(51) Int Cl.: **G06F 9/30 (2018.01)**

(22) Anmeldetag: 29.06.2018

(43) Offenlegungstag: 21.02.2019

(30) Unionspriorität:

15/640,533

01.07.2017 US

(71) Anmelder:

INTEL CORPORATION, Santa Clara, Calif., US

(74) Vertreter:

Samson & Partner Patentanwälte mbB, 80538

München, DE

(72) Erfinder:

Fleming, Kermin, Hudson, Mass., US; Glossop,

Kent, Nashua, N.H., US; Steely, Simon C. Jr.,

Hudson, N.H., US; Sury, Samantika S., Westford,

Mass., US

Prüfungsantrag gemäß § 44 PatG ist gestellt.

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen.

(54) Bezeichnung: **Prozessoren, Verfahren und Systeme für einen konfigurierbaren, räumlichen Beschleuniger mit Transaktions- und Wiederholungsmerkmalen**

100 ↘

(57) Zusammenfassung: Es werden Systeme, Verfahren und Vorrichtungen bezüglich eines konfigurierbaren räumlichen Beschleunigers beschrieben. In einer Ausführungsform weist ein Prozessor mehrere Verarbeitungselemente auf; und ein Zwischenverbindungsnetz zwischen den mehreren Verarbeitungselementen zum Empfangen einer Eingabe eines Datenflussgraphen, der mehrere Knoten umfasst, wobei der Datenflussgraph in das Zwischenverbindungsnetz und die mehreren Verarbeitungselemente zu überlagern, wobei jeder Knoten als ein Datenflussoperator in den mehreren Verarbeitungselementen repräsentiert ist, und die mehreren Verarbeitungselemente eine atomare Operation durchzuführen haben, wenn ein eingehender Operand bei den mehreren Verarbeitungselementen eingeht.

## Beschreibung

### AUSSAGE BEZÜGLICH DER STAATLICH GEFÖRDERTEN FORSCHUNG UND ENTWICKLUNG

**[0001]** Diese Erfindung wurde mit Unterstützung der Regierung unter Vertragsnummer H98230A-13-D-0124, verliehen vom Ministerium für Verteidigung, erstellt. Die Regierung besitzt gewisse Rechte auf diese Erfindung.

### TECHNISCHES GEBIET

**[0002]** Die Offenbarung betrifft allgemein Elektronik, und spezifischer betrifft eine Ausführungsform der Offenbarung einen konfigurierbaren räumlichen Beschleuniger.

### Hintergrund

**[0003]** Ein Prozessor oder Satz von Prozessoren führt Befehle aus einem Befehlssatz aus, z. B. der Befehlsatzarchitektur (ISA). Der Befehlssatz ist Teil der Rechnerarchitektur bezüglich der Programmierung und beinhaltet im Allgemeinen die nativen Datentypen, Befehle, Registerarchitektur, Adressiermodi, Speicherarchitektur, Interrupt- und Ausnahmehandhabung und externe Eingabe und Ausgabe (I/O) auf. Es sei angemerkt, dass sich der Begriff Befehl hierin auf einen Makrobefehl, z. B. einen Befehl, der dem Prozessor zur Ausführung bereitgestellt wird, oder auf einen Mikrobefehl, z. B. einen Befehl, der aus einem Prozessor-Decodierer resultiert, der Makrobefehle decodiert, beziehen kann.

### Figurenliste

**[0004]** Die vorliegende Offenbarung ist beispielhaft und nicht einschränkend in den Figuren der beigefügten Zeichnungen veranschaulicht, in denen ähnliche Bezugszeichen ähnliche Elemente angeben und in denen zeigen:

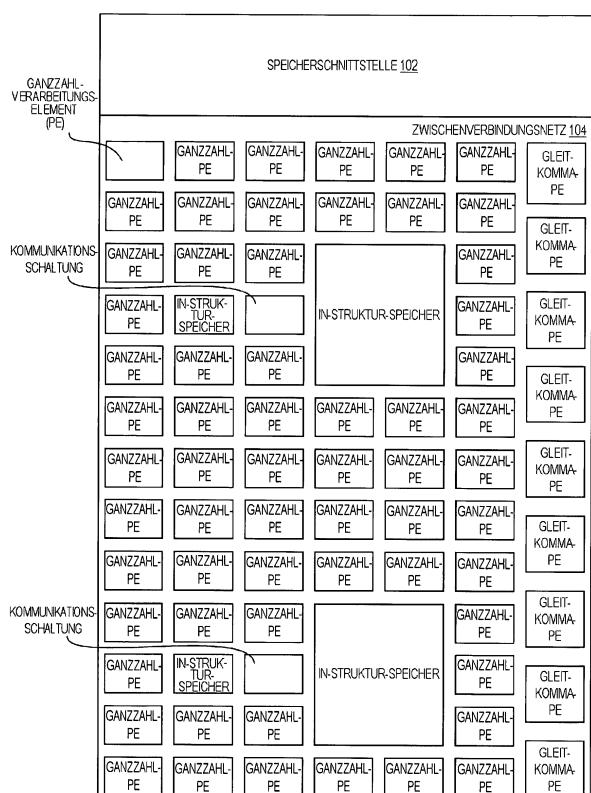

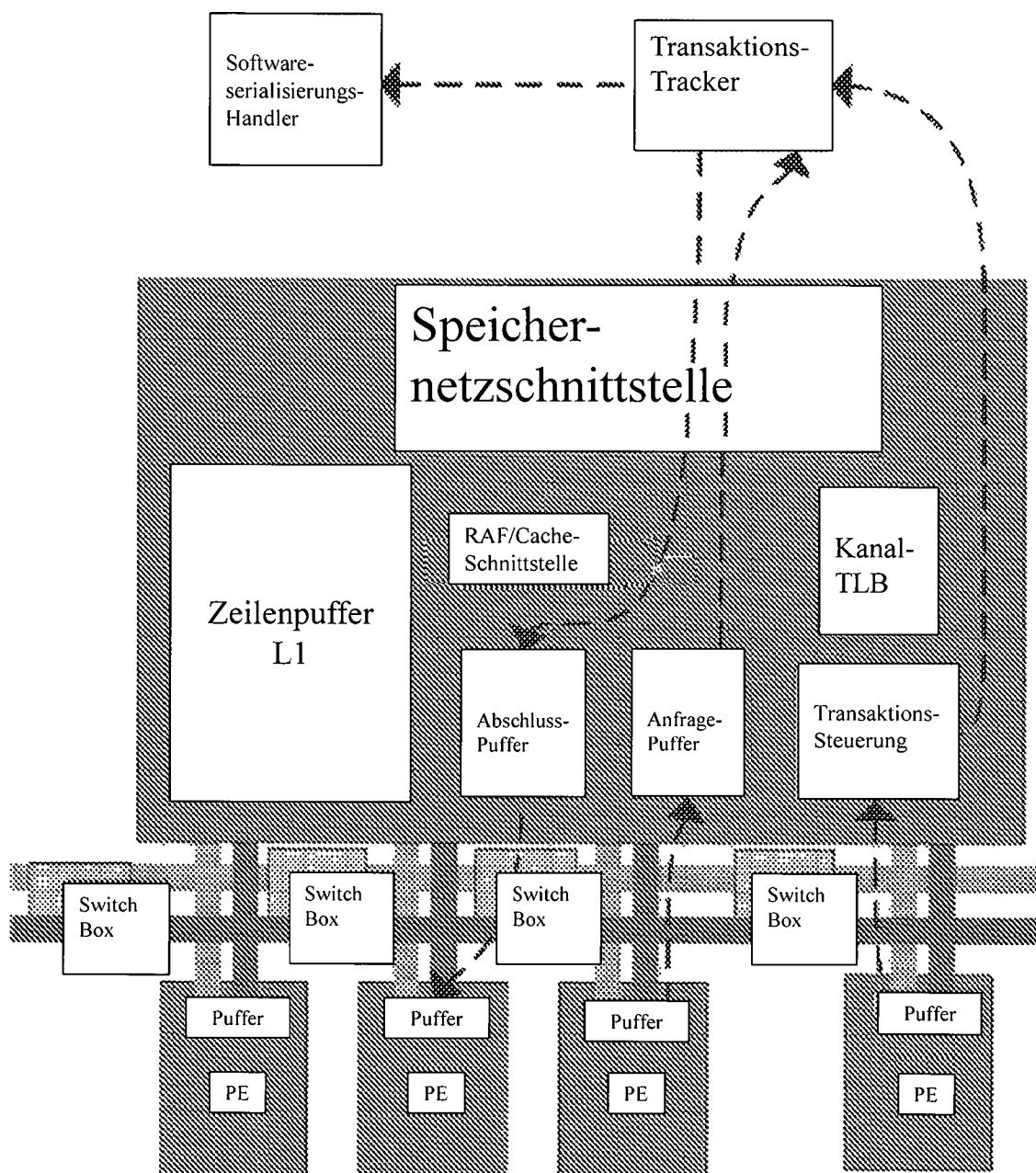

**Fig. 1** veranschaulicht eine Beschleuniger-Kachel gemäß Ausführungsformen der Offenbarung;

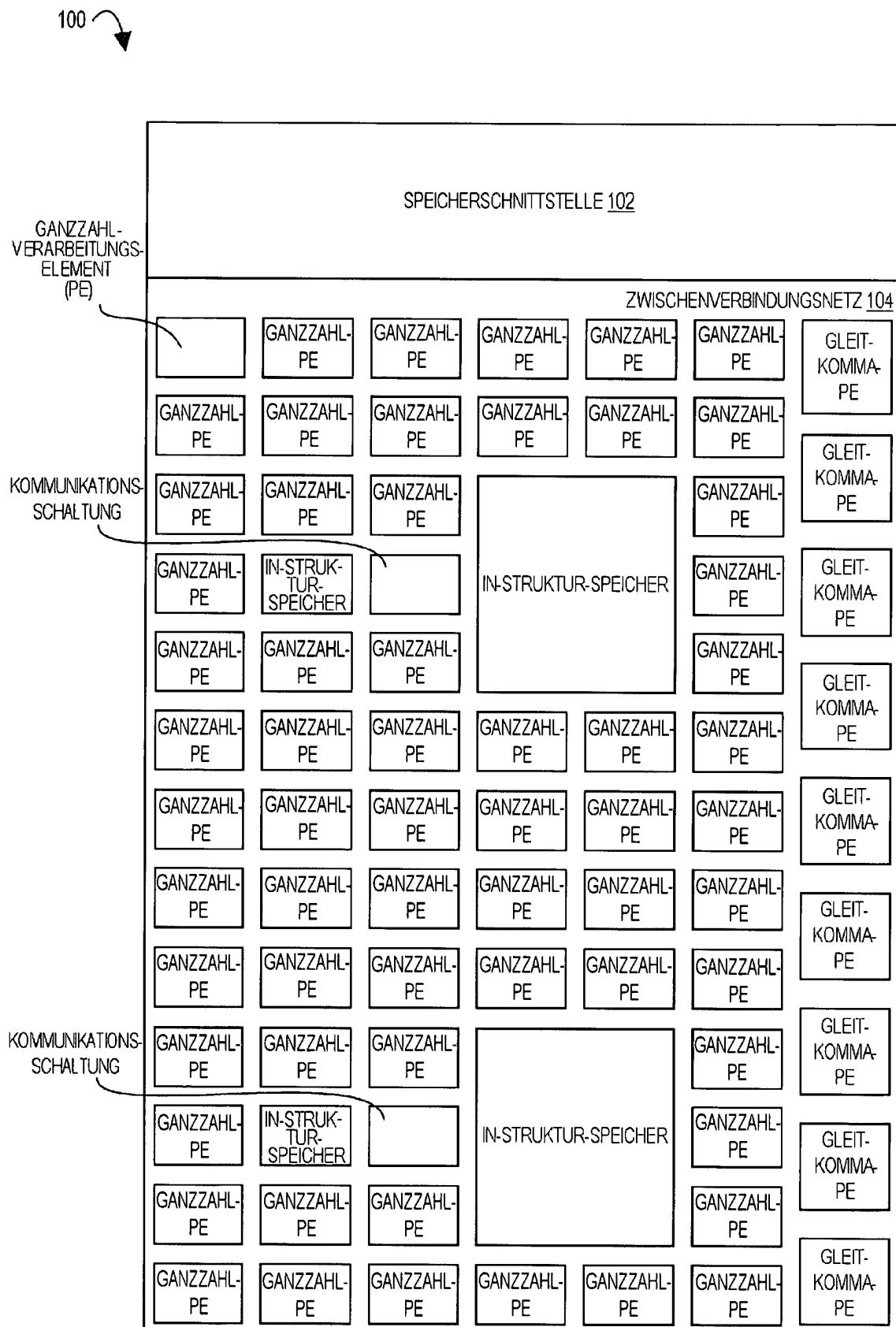

**Fig. 2** veranschaulicht einen Hardware-Prozessor, der mit einem Speicher gekoppelt ist, gemäß Ausführungsformen der Offenbarung;

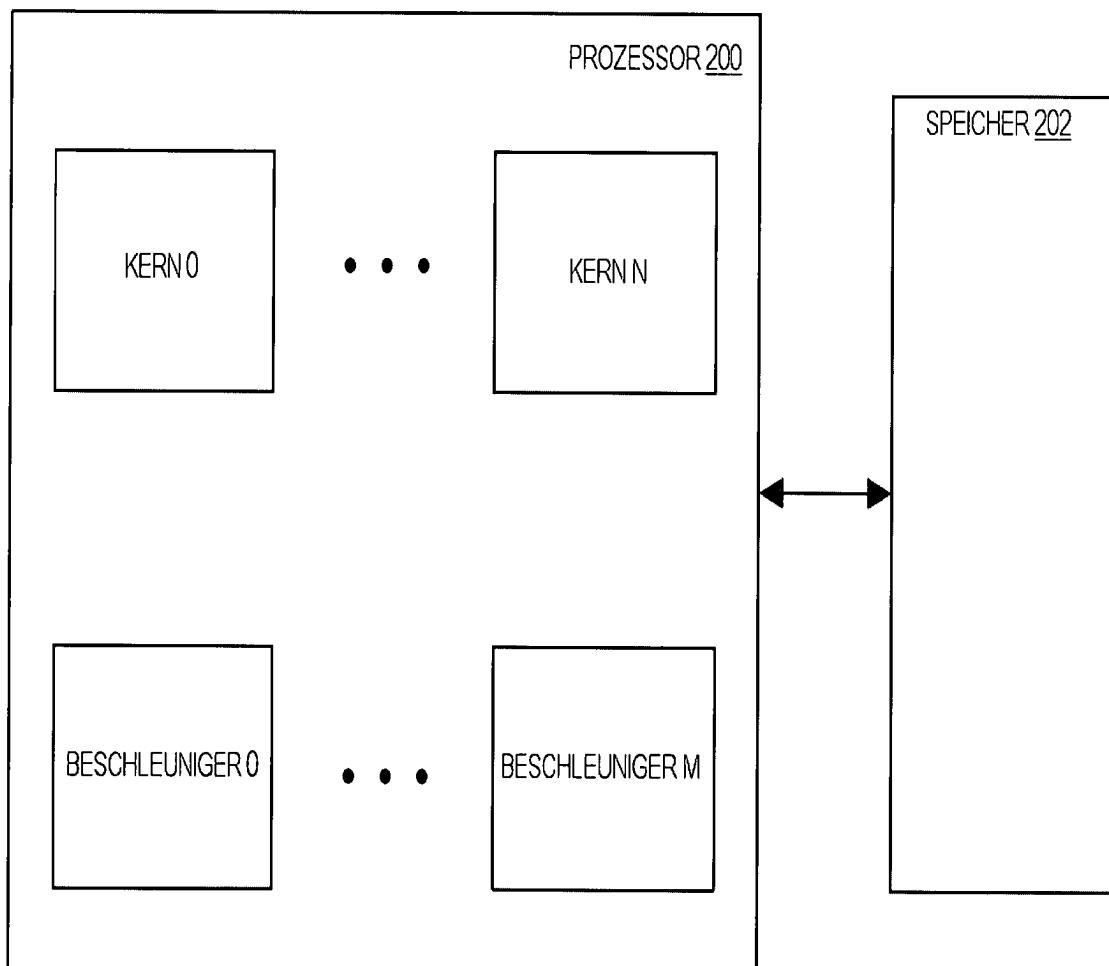

**Fig. 3A** veranschaulicht eine Programmquelle gemäß Ausführungsformen der Offenbarung;

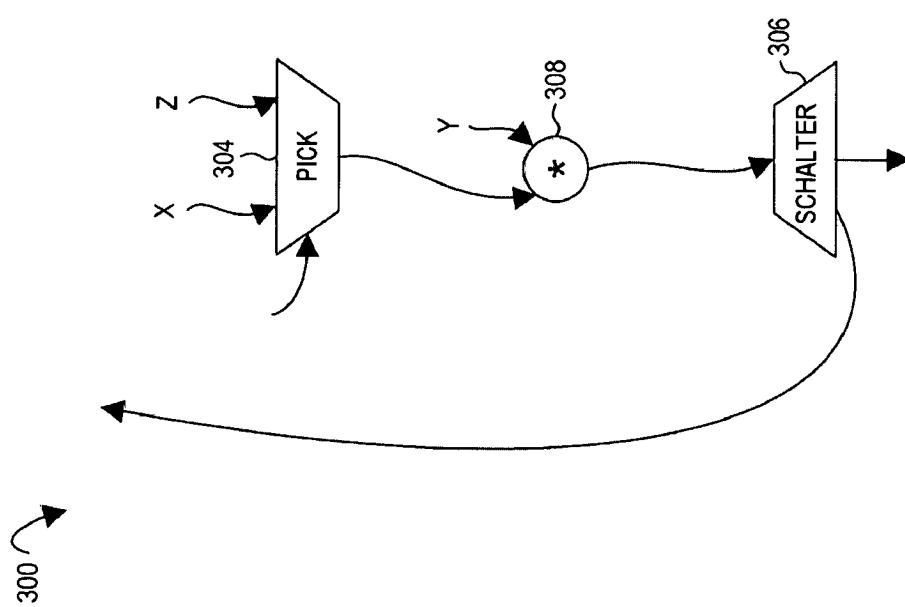

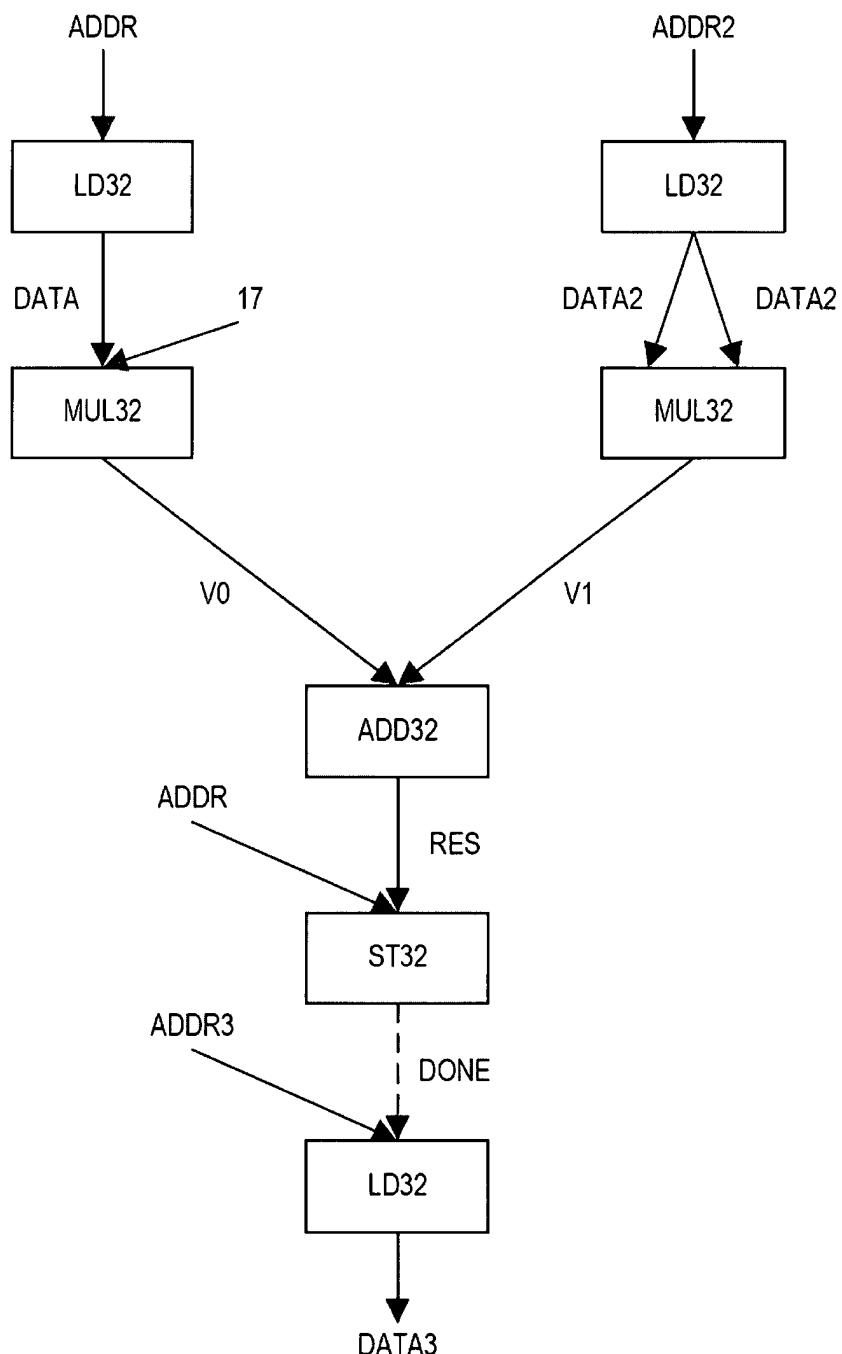

**Fig. 3B** veranschaulicht einen Datenflussgraphen für die Programmquelle aus **Fig. 3A** gemäß Ausführungsformen der Offenbarung;

**Fig. 3C** veranschaulicht einen Beschleuniger mit mehreren Verarbeitungselementen, die zum Ausführen des Datenflussgraphen aus **Fig. 3B** gemäß Ausführungsformen der Offenbarung konfiguriert ist;

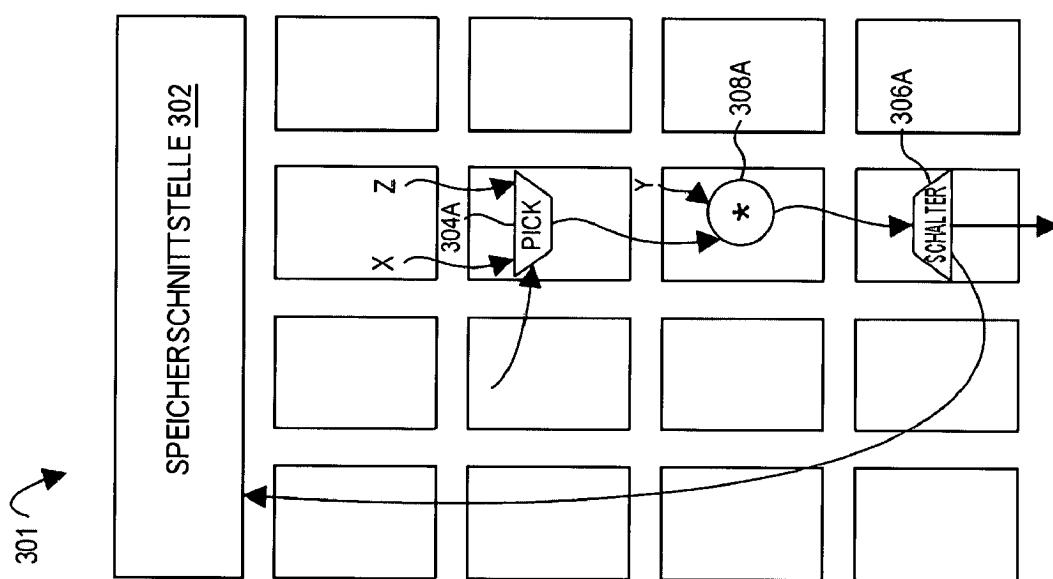

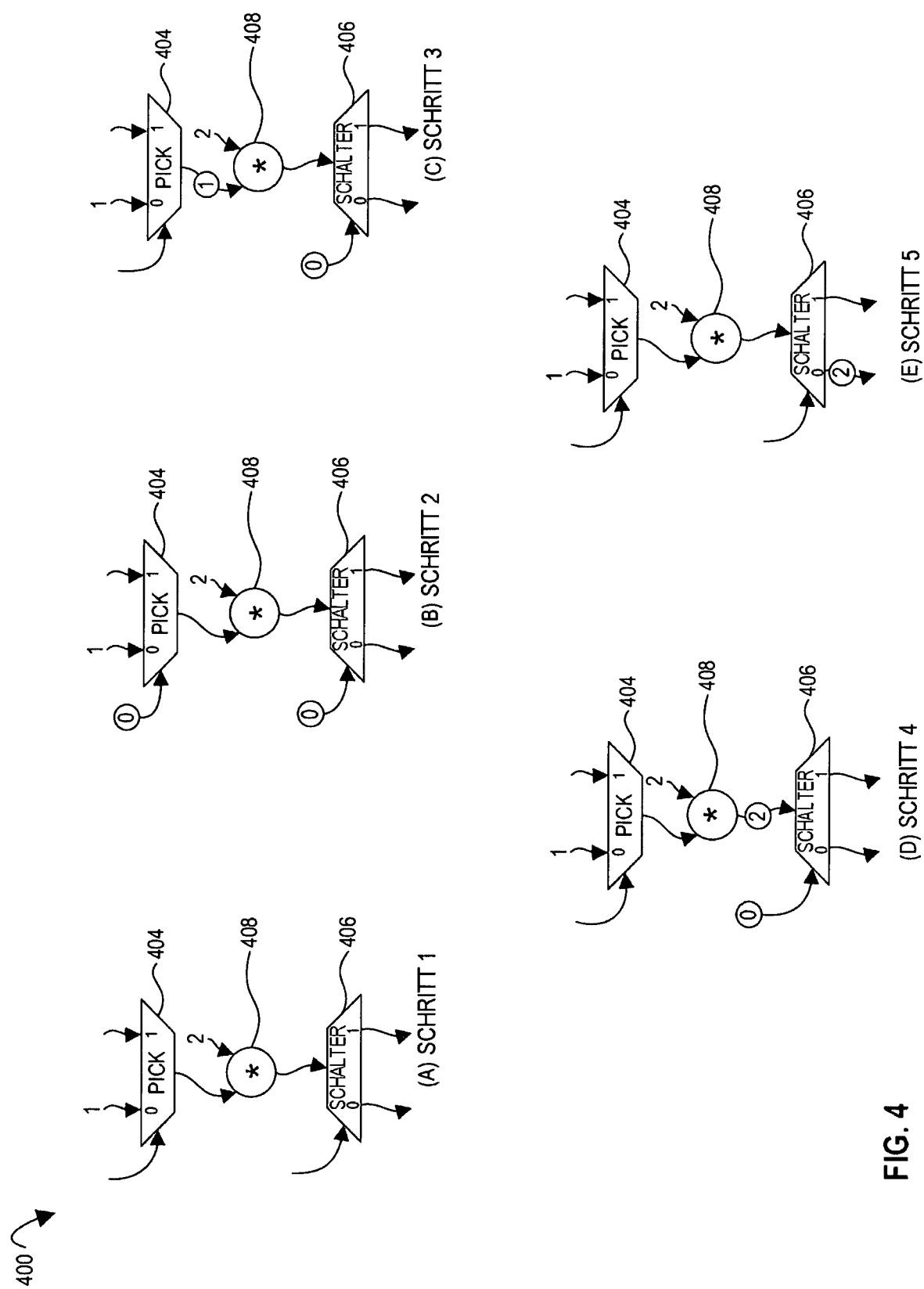

**Fig. 4** veranschaulicht eine beispielhafte Ausführung des Datenflussgraphen gemäß Ausführungsformen der Offenbarung;

**Fig. 5** veranschaulicht eine Programmquelle gemäß Ausführungsformen der Offenbarung;

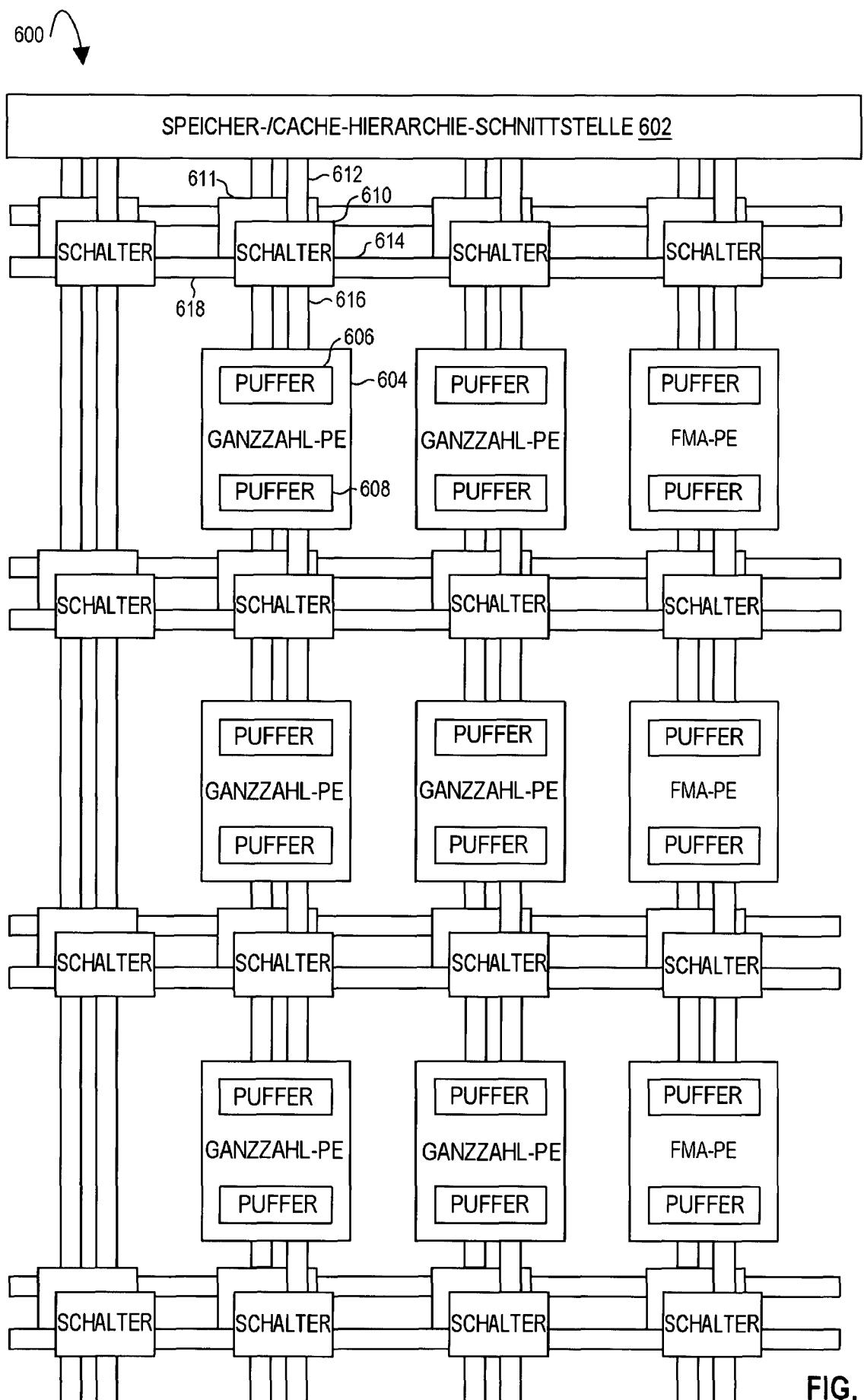

**Fig. 6** veranschaulicht eine Beschleuniger-Kachel, umfassend ein Array von Verarbeitungselementen gemäß Ausführungsformen der Offenbarung;

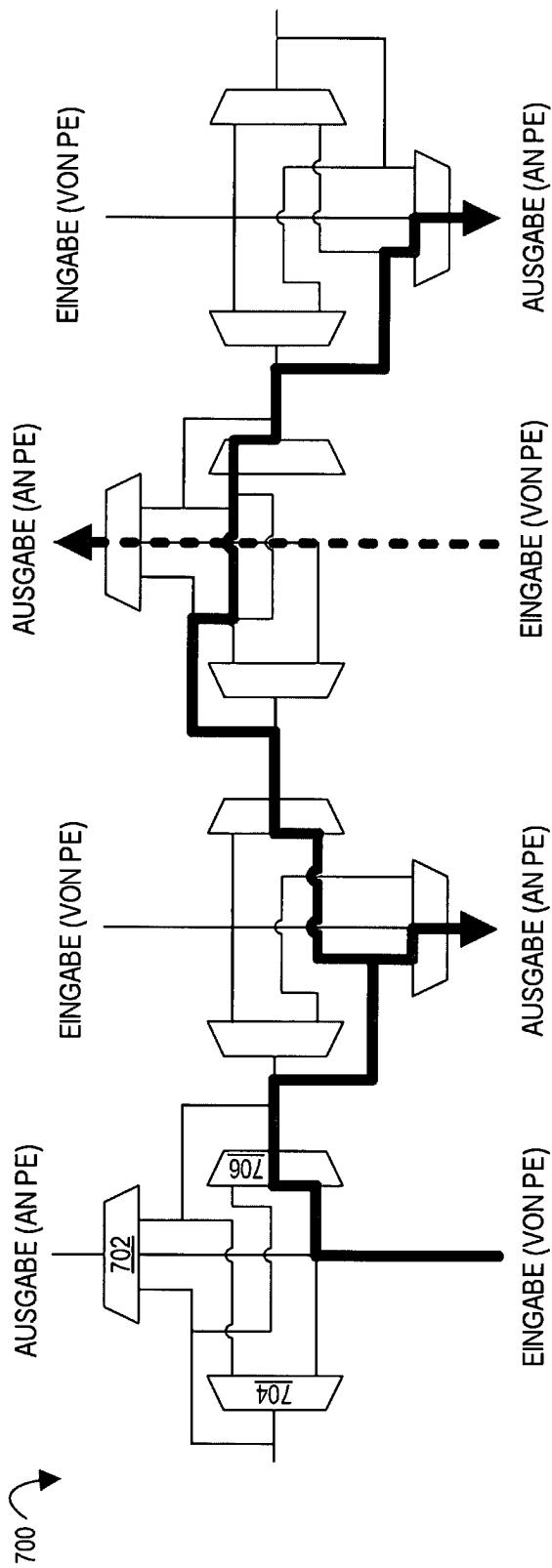

**Fig. 7A** veranschaulicht ein konfigurierbares Datenpfad-Netzwerk gemäß Ausführungsformen der Offenbarung;

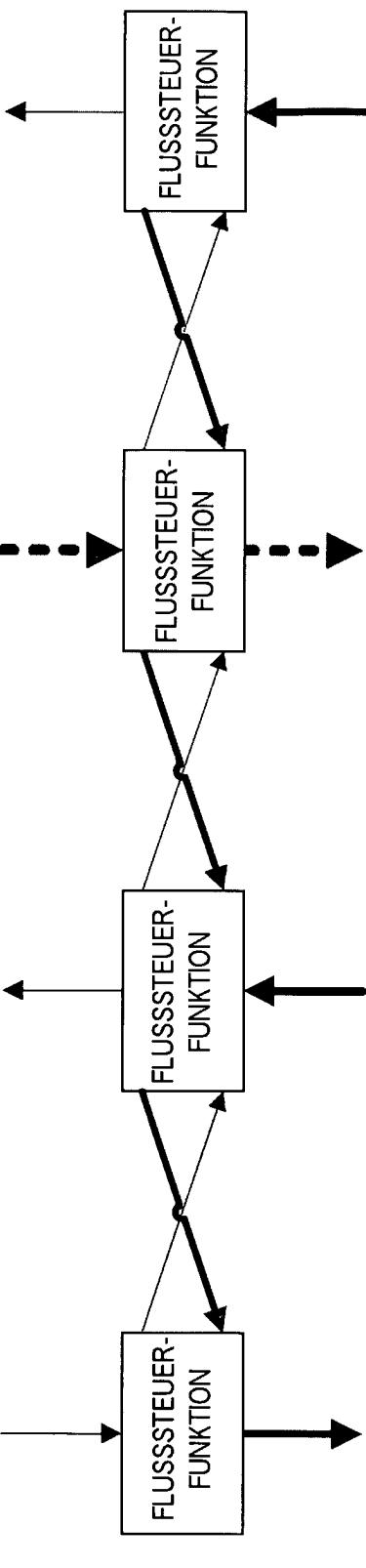

**Fig. 7B** veranschaulicht ein konfigurierbares Flusssteuerpfad-Netzwerk gemäß Ausführungsformen der Offenbarung;

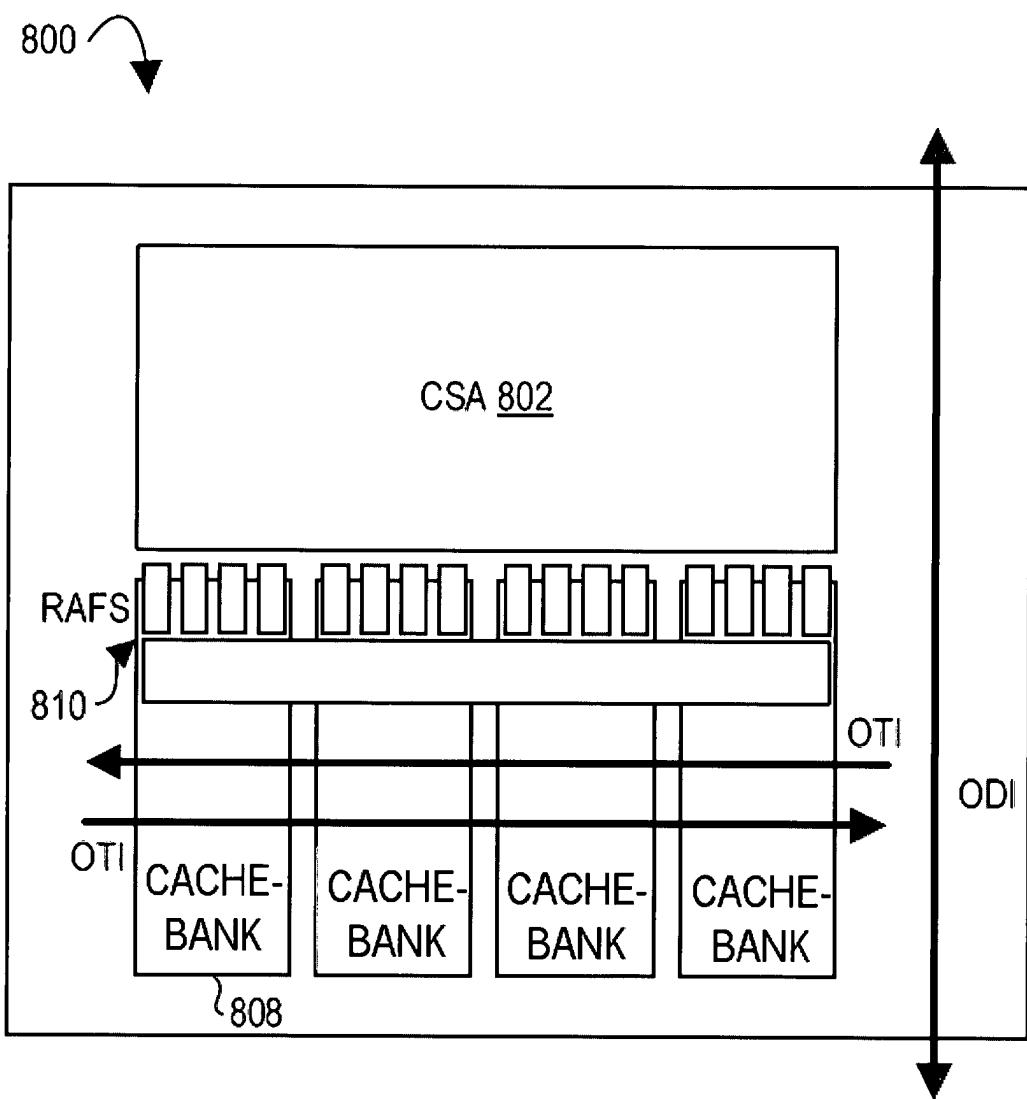

**Fig. 8** veranschaulicht eine Hardware-Prozessor-Kachel, umfassend einen Beschleuniger gemäß Ausführungsformen der Offenbarung;

**Fig. 9** veranschaulicht ein Verarbeitungselement gemäß Ausführungsformen der Offenbarung;

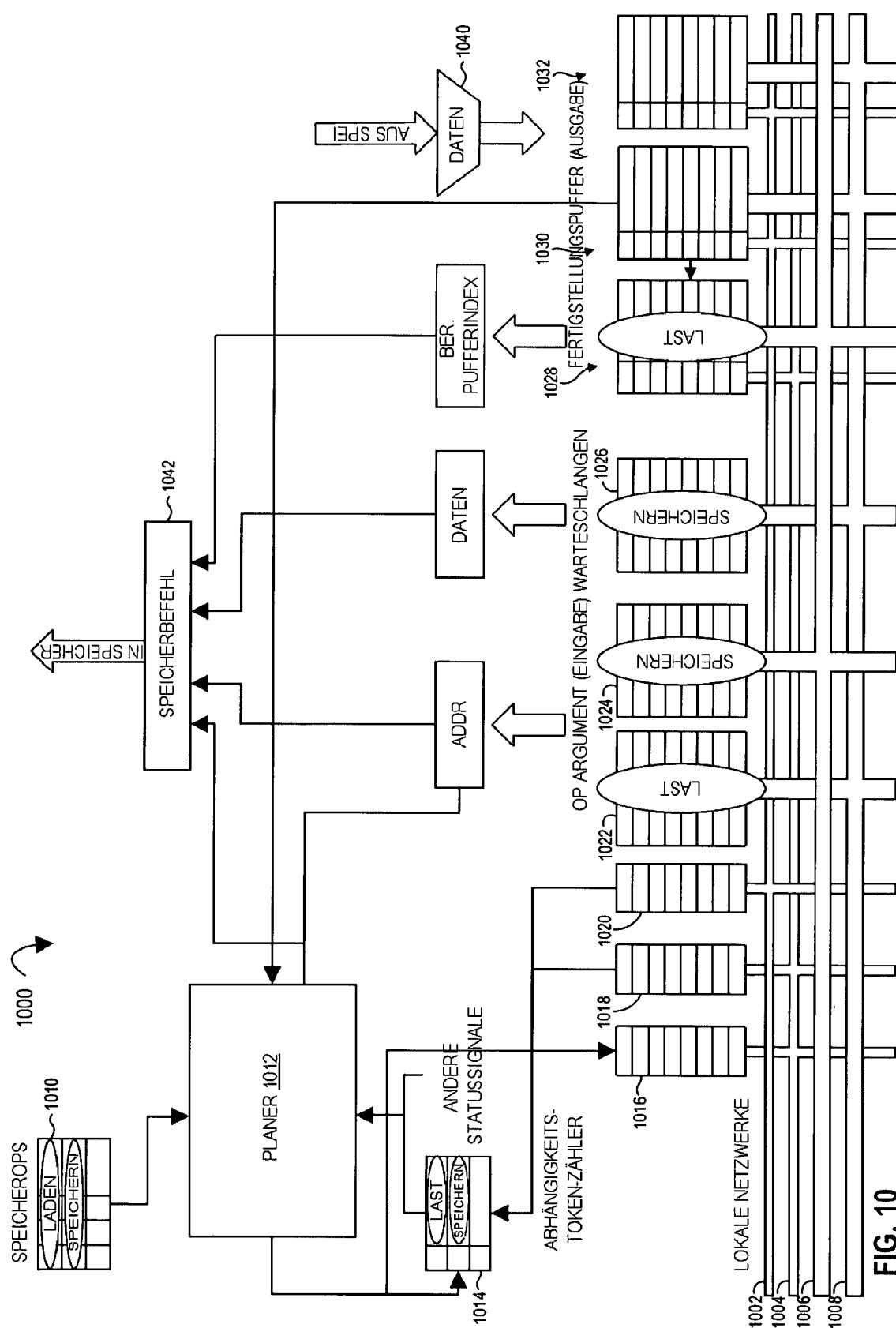

**Fig. 10** veranschaulicht eine Abfrage-Adressdatei (RAF)-Schaltung gemäß Ausführungsformen der Offenbarung;

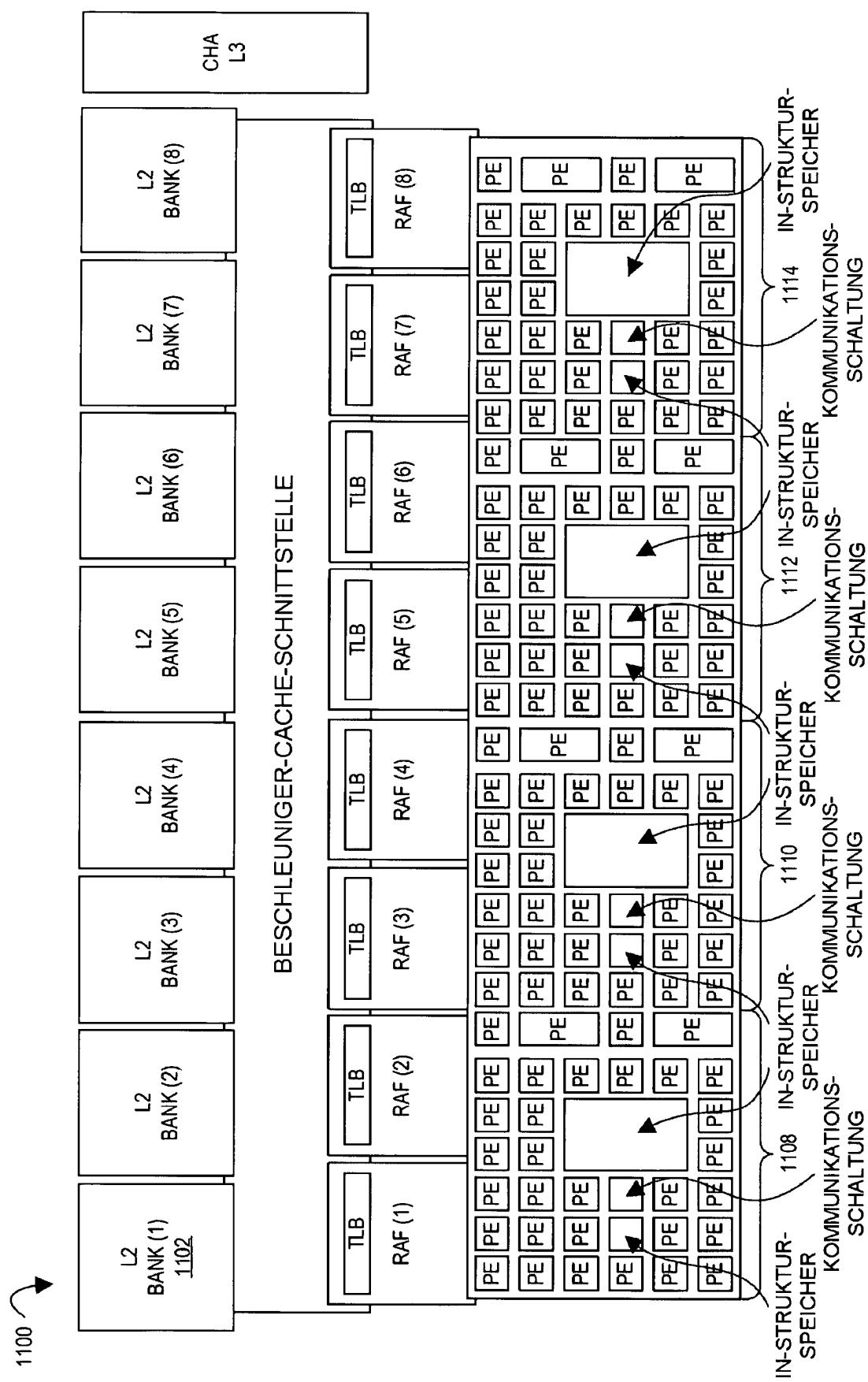

**Fig. 11A** veranschaulicht mehrere Abfrage-Adressdatei (RAF)-Schaltungen, die zwischen mehreren Beschleuniger-Kacheln und mehreren Cache-Bänken gemäß Ausführungsformen der Offenbarung gekoppelt sind;

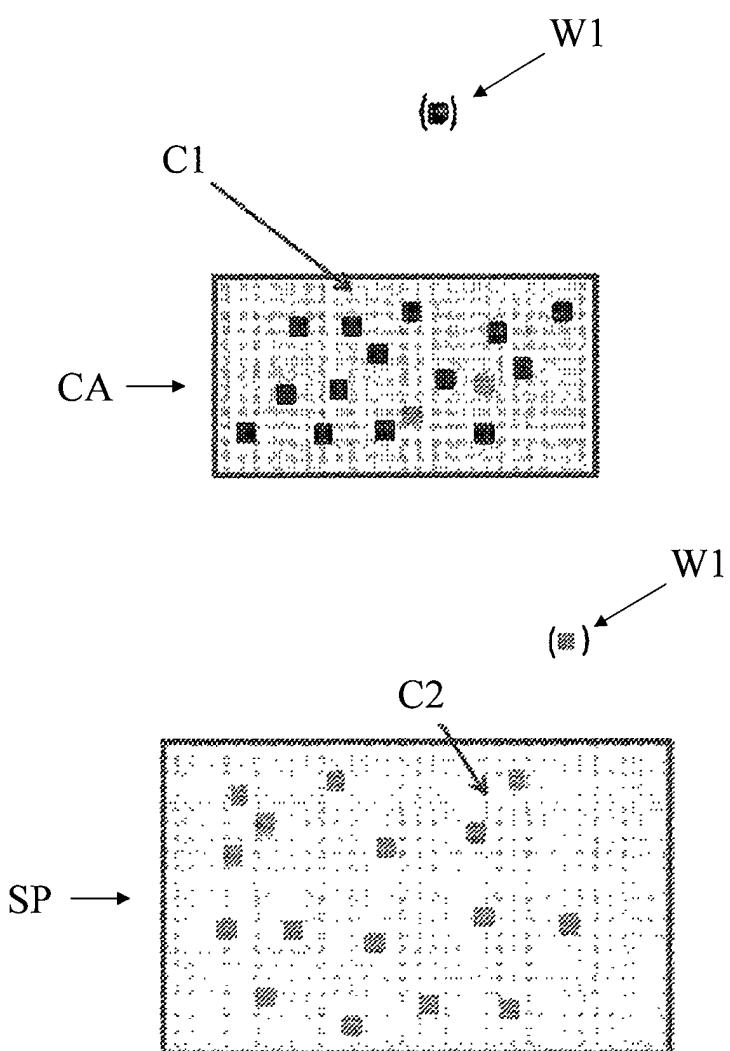

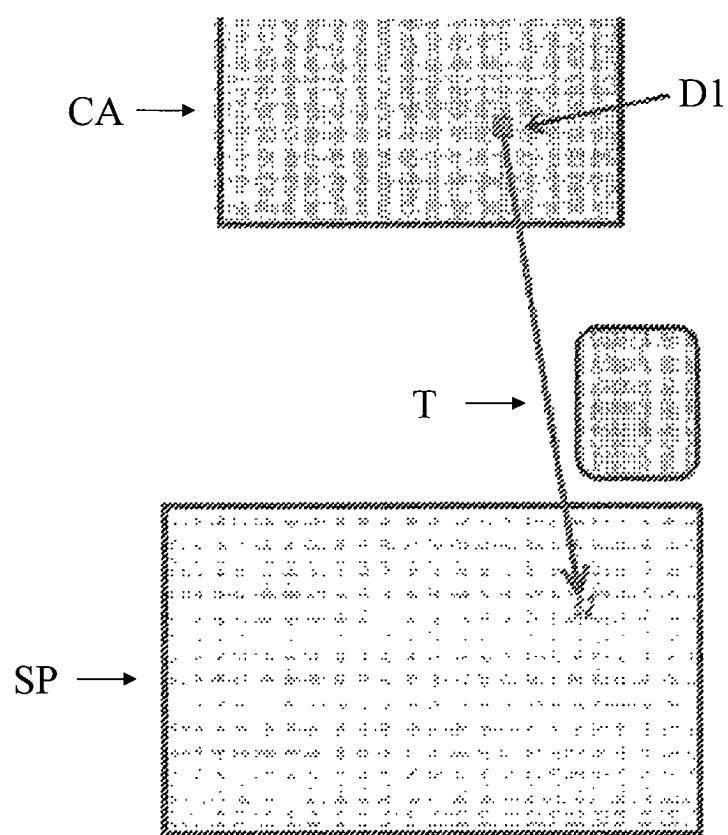

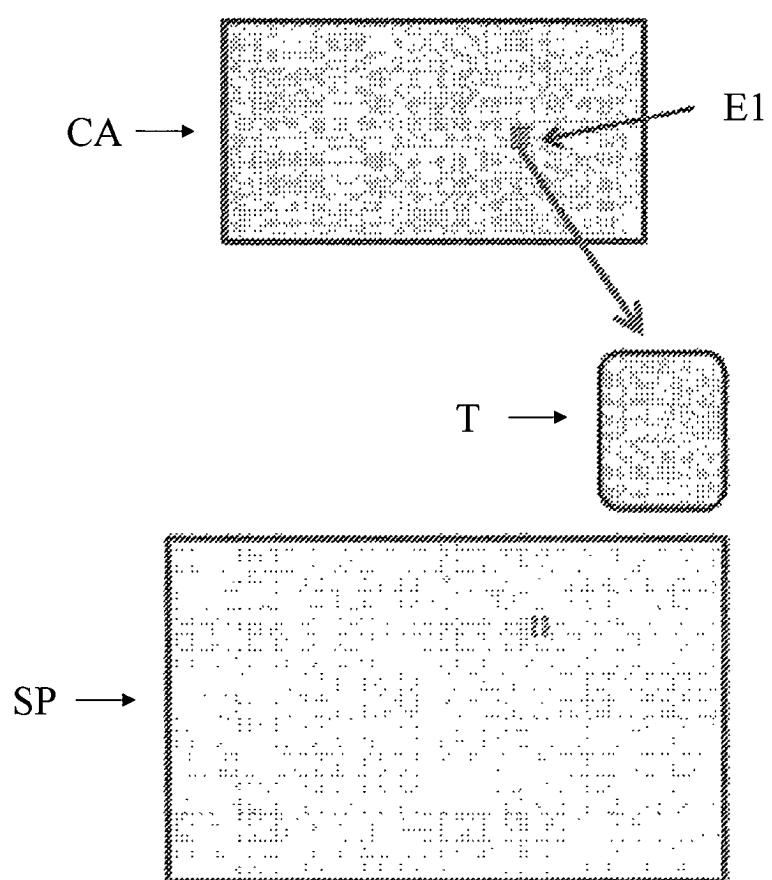

**Fig. 11B** veranschaulicht einen Transaktionsmechanismus, in dem Cache-Zeilen mit Informationen über die Quelle eines Lese- oder Schreibzugriffs markiert sind, gemäß Ausführungsformen der Offenbarung.

**Fig. 11C bis Fig. 11J** veranschaulicht eine Unterstützung für Backup und Wiederholung unter Verwendung von Epochen im Cache-/Speicheruntersystem gemäß Ausführungsformen der Offenbarung.

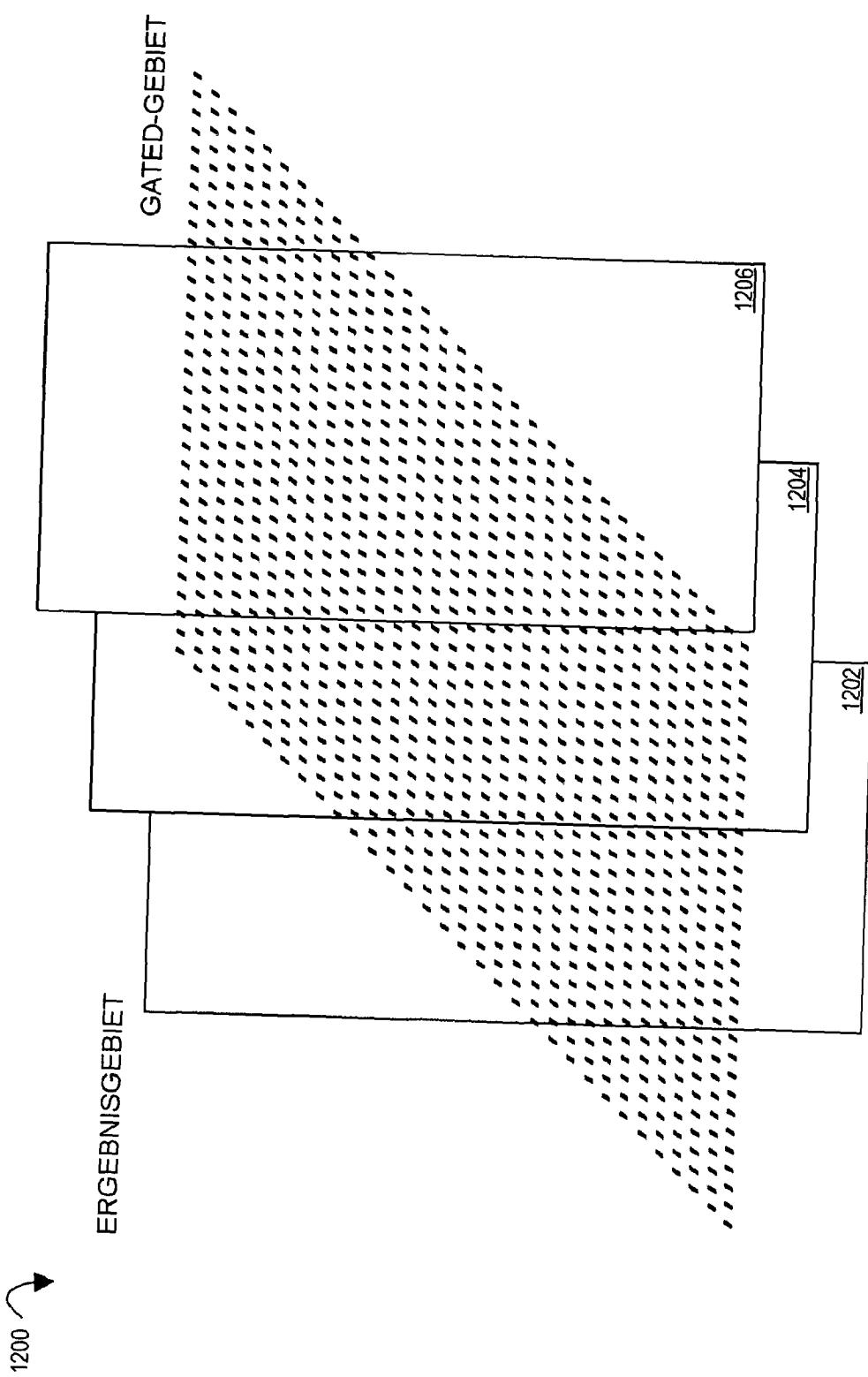

**Fig. 12** veranschaulicht einen Gleitkomma-Multiplizierer, der in drei Gebiete (Ergebnisgebiet, drei potentielle Übertraggebiete und Gebiet mit Gate) gemäß Ausführungsformen der Offenbarung unterteilt ist;

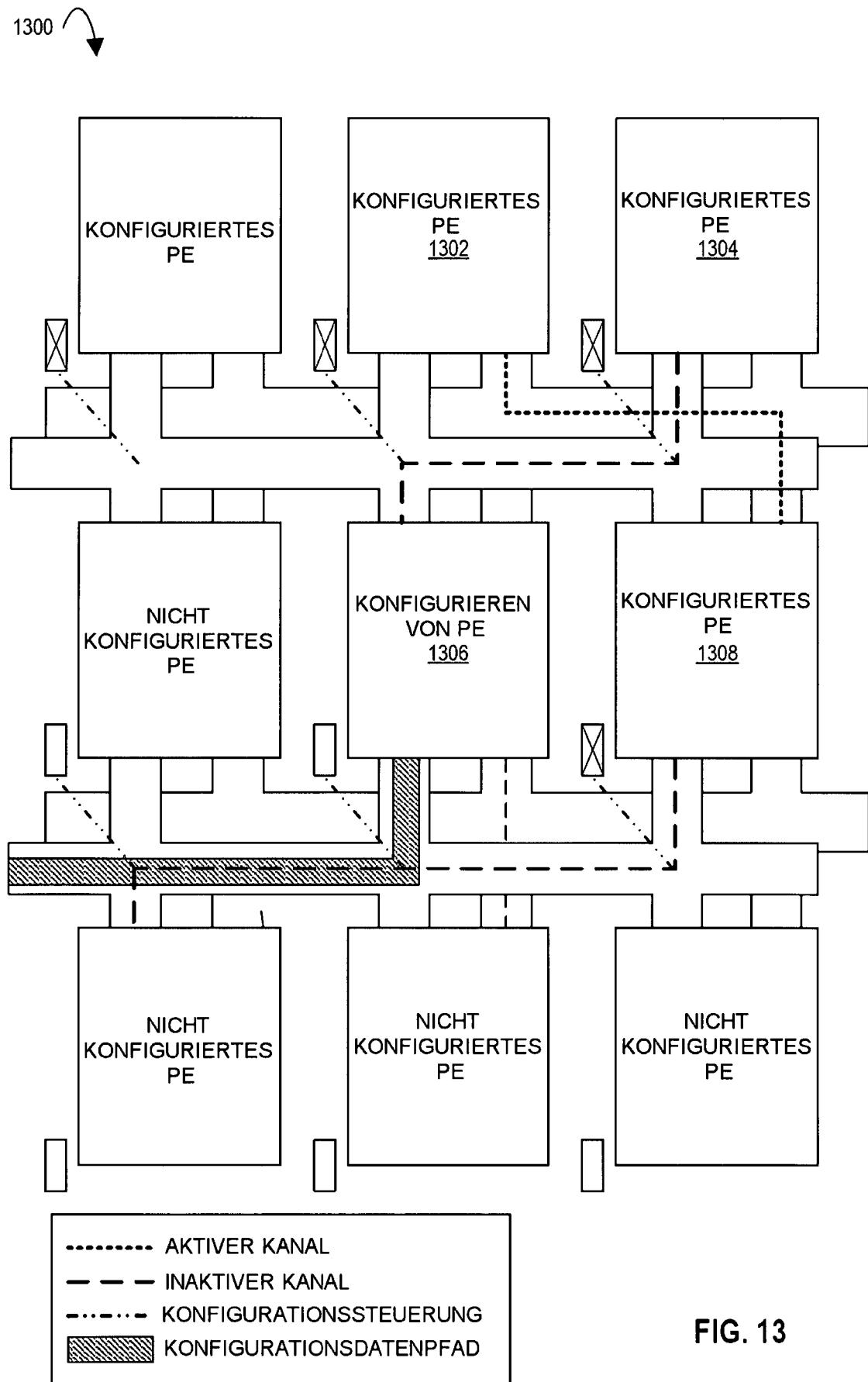

**Fig. 13** veranschaulicht eine In-Flight-Beschleunigerkonfiguration mit mehreren Verarbeitungselementen gemäß Ausführungsformen der Offenbarung;

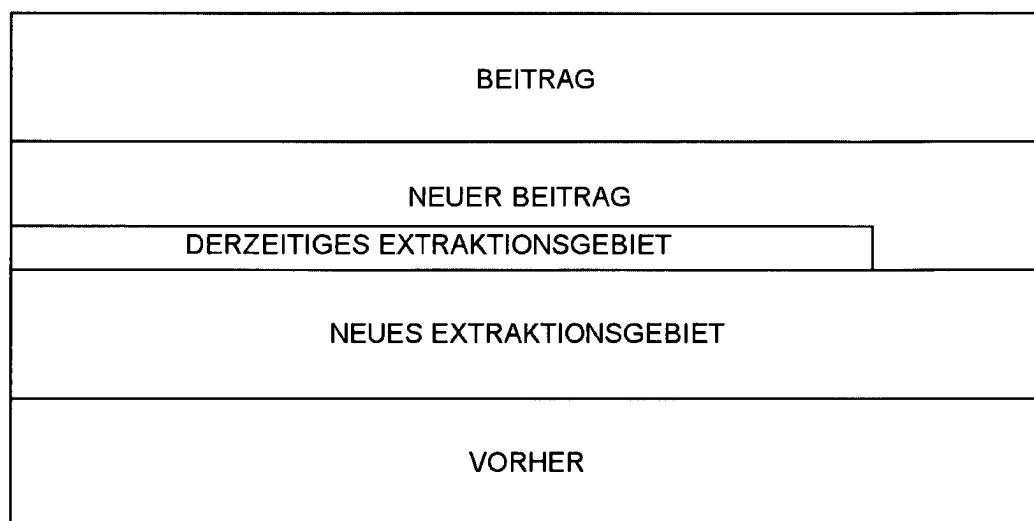

**Fig. 14** veranschaulicht einen Speicherauszug einer zeitverschachtelten In-Flight-Extraktion gemäß Ausführungsformen der Offenbarung;

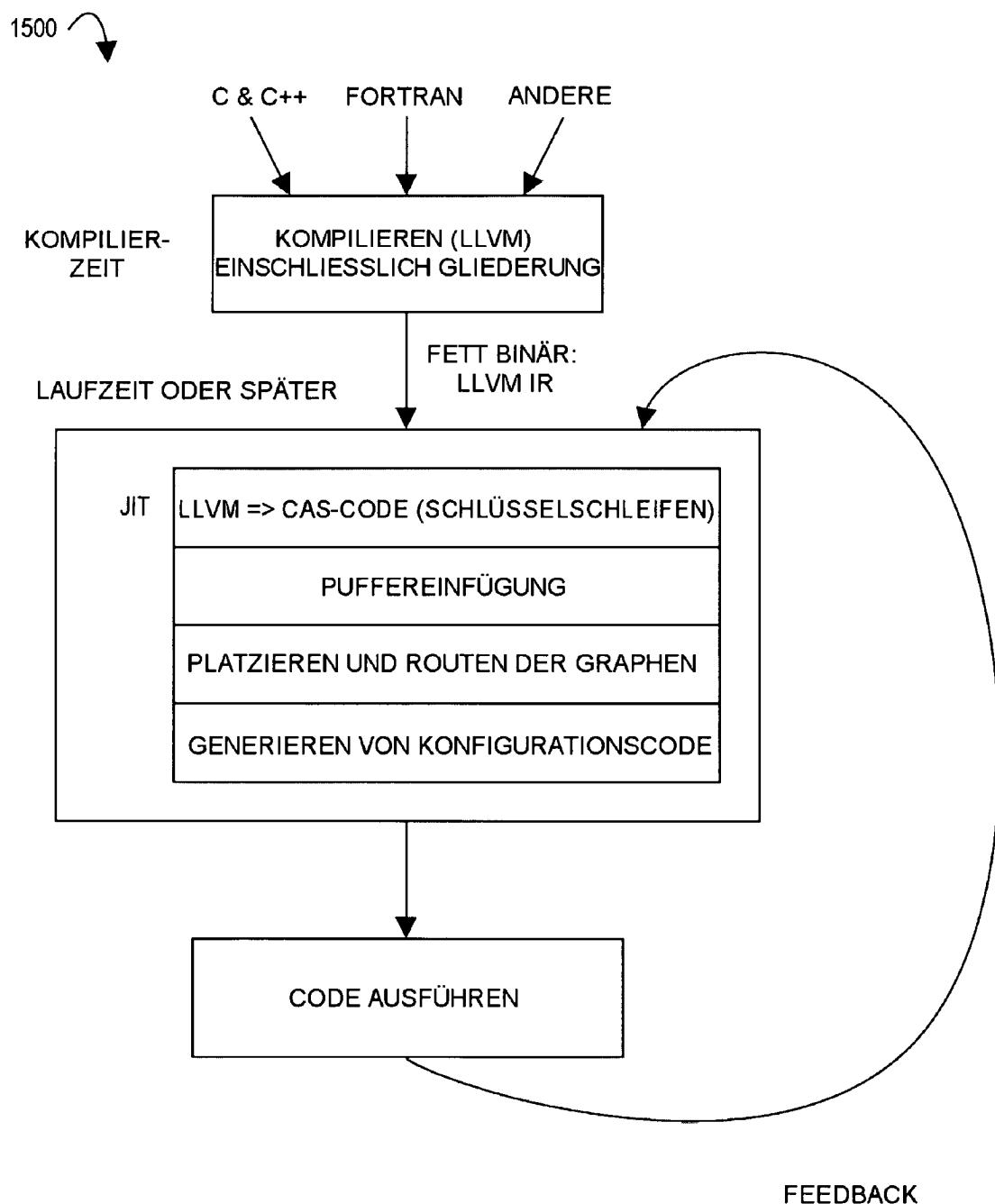

**Fig. 15** veranschaulicht eine Kompilationstoolkette für einen Beschleuniger gemäß Ausführungsformen der Offenbarung;

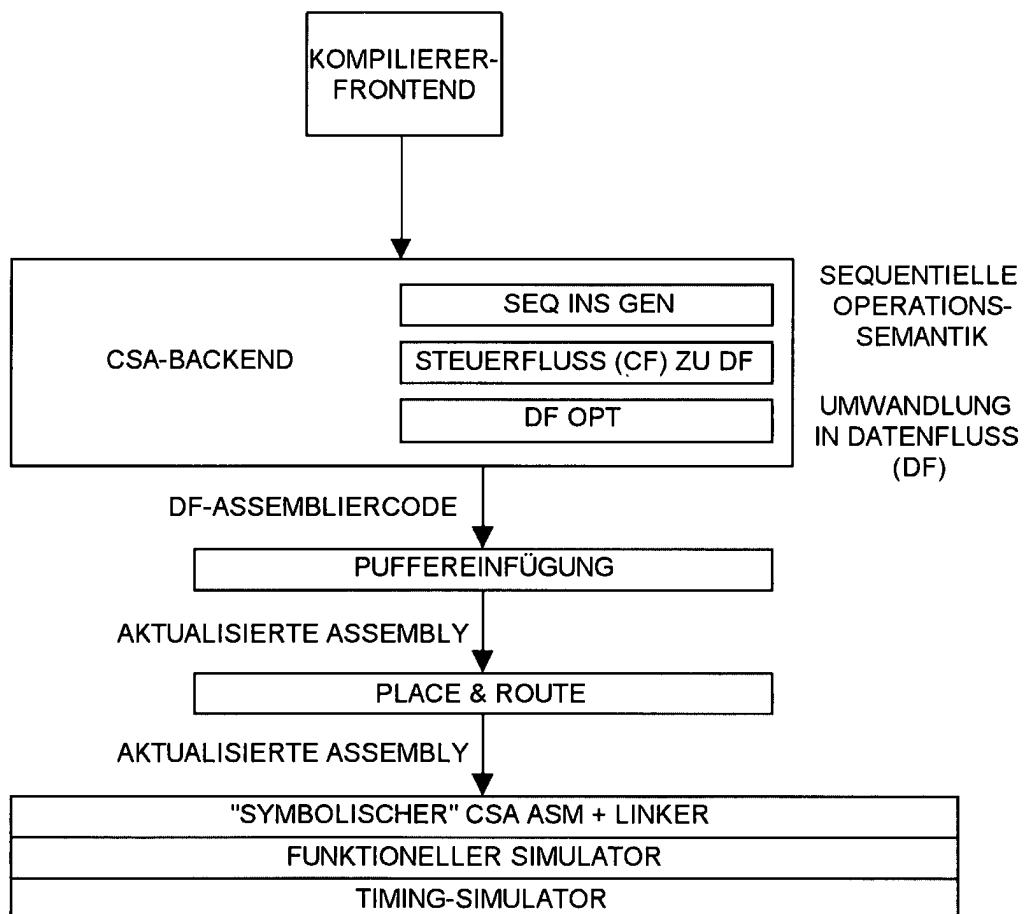

**Fig. 16** veranschaulicht einen Kompilierer für einen Beschleuniger gemäß Ausführungsformen der Offenbarung;

**Fig. 17A** veranschaulicht einen sequentiellen Assembliercode gemäß Ausführungsformen der Offenbarung;

**Fig. 17B** veranschaulicht einen Datenfluss-Assembliercode für den sequentiellen Assembliercode aus **Fig. 17A** gemäß Ausführungsformen der Offenbarung;

**Fig. 17C** veranschaulicht einen Datenflussgraph für den Datenfluss-Assembliercode aus **Fig. 17B** für einen Beschleuniger gemäß Ausführungsformen der Offenbarung;

**Fig. 18A** veranschaulicht einen C-Quellcode gemäß Ausführungsformen der Offenbarung;

**Fig. 18B** veranschaulicht einen Datenfluss-Assembliercode für den C-Quellcode aus **Fig. 18A** gemäß Ausführungsformen der Offenbarung;

**Fig. 18C** veranschaulicht einen Datenflussgraphen für den Datenfluss-Assembliercode aus **Fig. 18B** für einen Beschleuniger gemäß Ausführungsformen der Offenbarung;

**Fig. 19A** veranschaulicht einen C-Quellcode gemäß Ausführungsformen der Offenbarung;

**Fig. 19B** veranschaulicht einen Datenfluss-Assembliercode für den C-Quellcode aus **Fig. 19A** gemäß Ausführungsformen der Offenbarung;

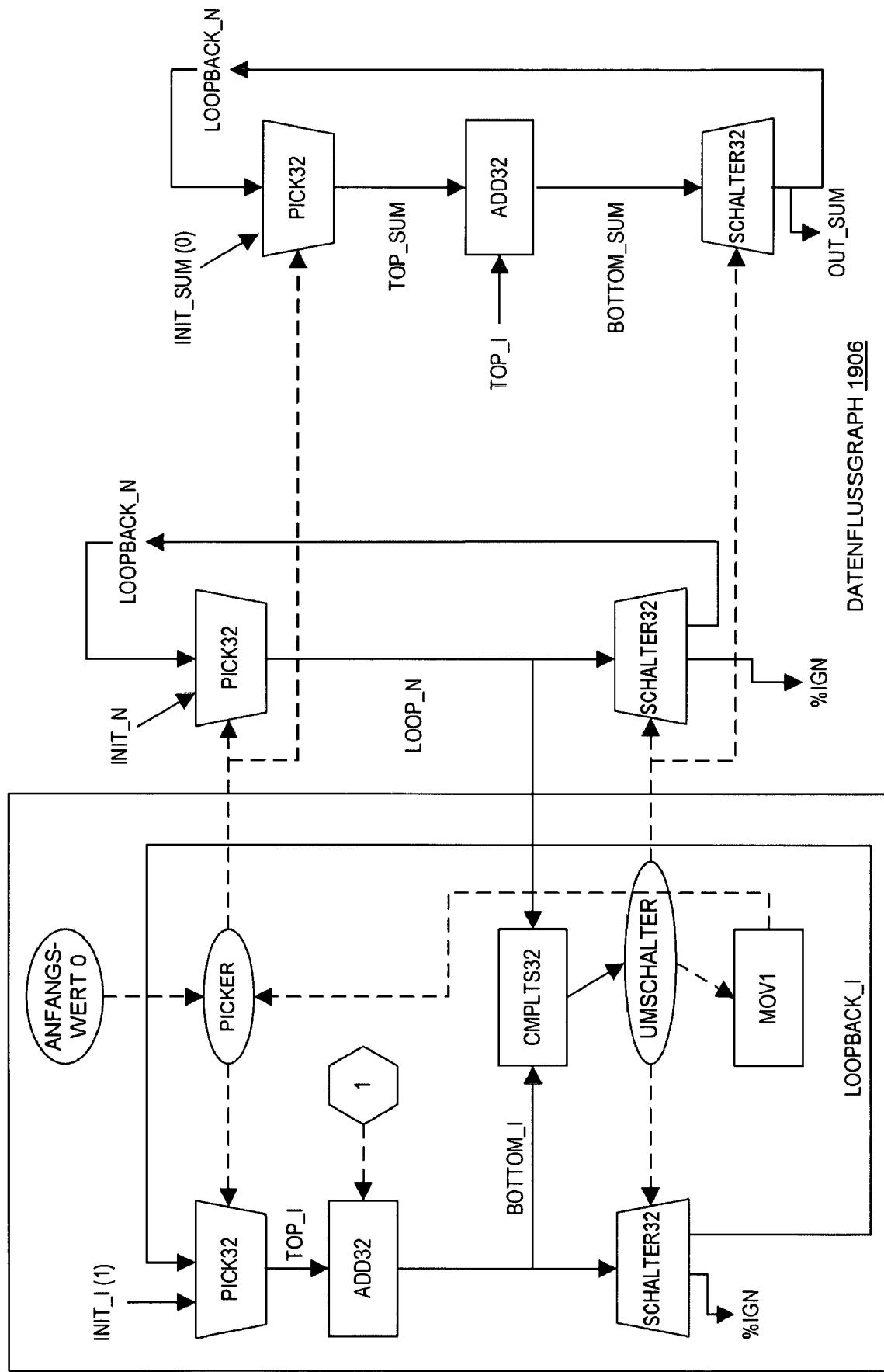

**Fig. 19C** veranschaulicht einen Datenflussgraphen für den Datenfluss-Assembliercode aus **Fig. 19B** für einen Beschleuniger gemäß Ausführungsformen der Offenbarung;

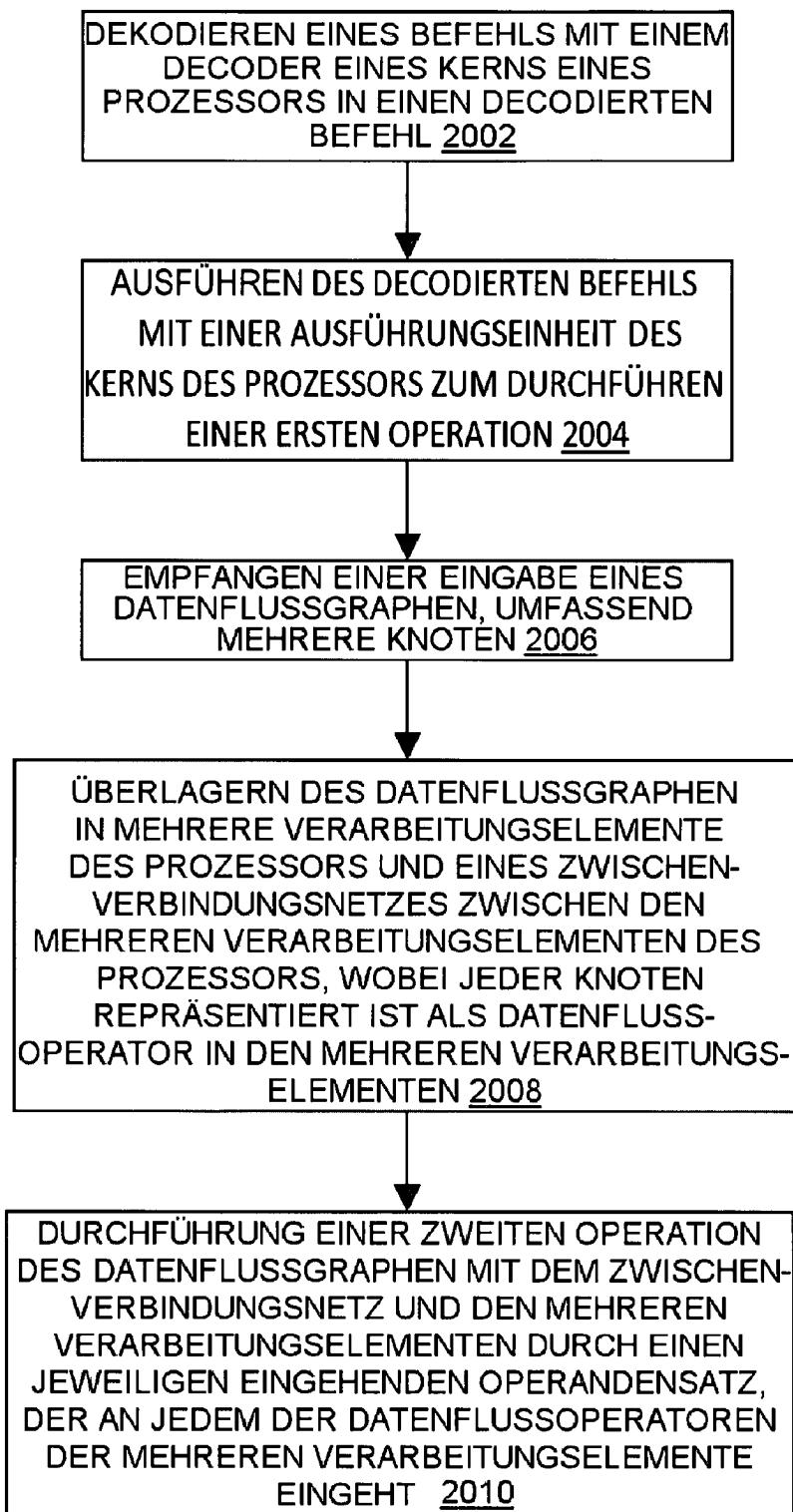

**Fig. 20A** veranschaulicht ein Flussdiagramm gemäß Ausführungsformen der Offenbarung;

**Fig. 20B** veranschaulicht ein Flussdiagramm gemäß Ausführungsformen der Offenbarung;

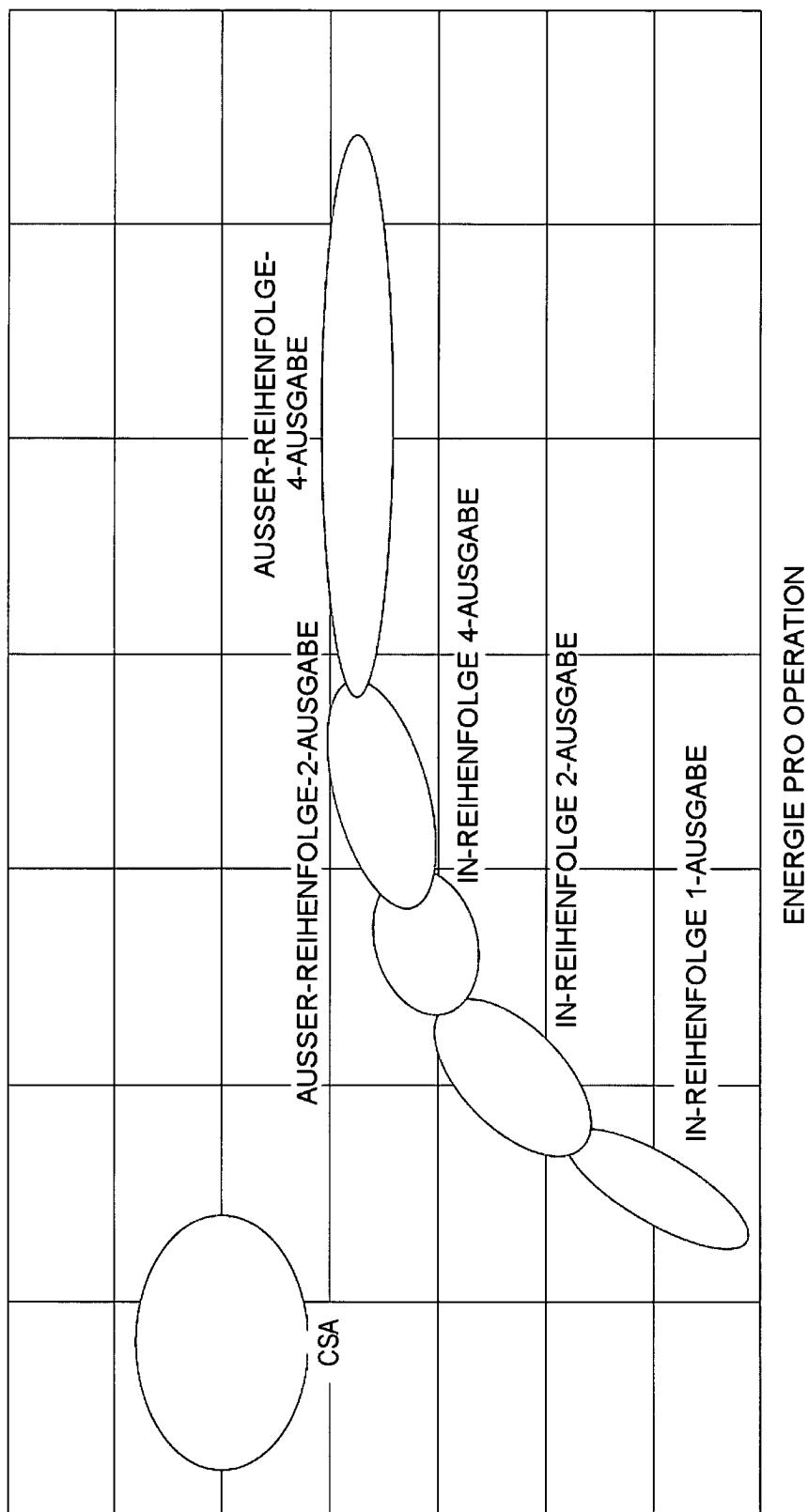

**Fig. 21** veranschaulicht einen Durchlauftypgraphen gegenüber der Energie pro Operation gemäß Ausführungsformen der Offenbarung;

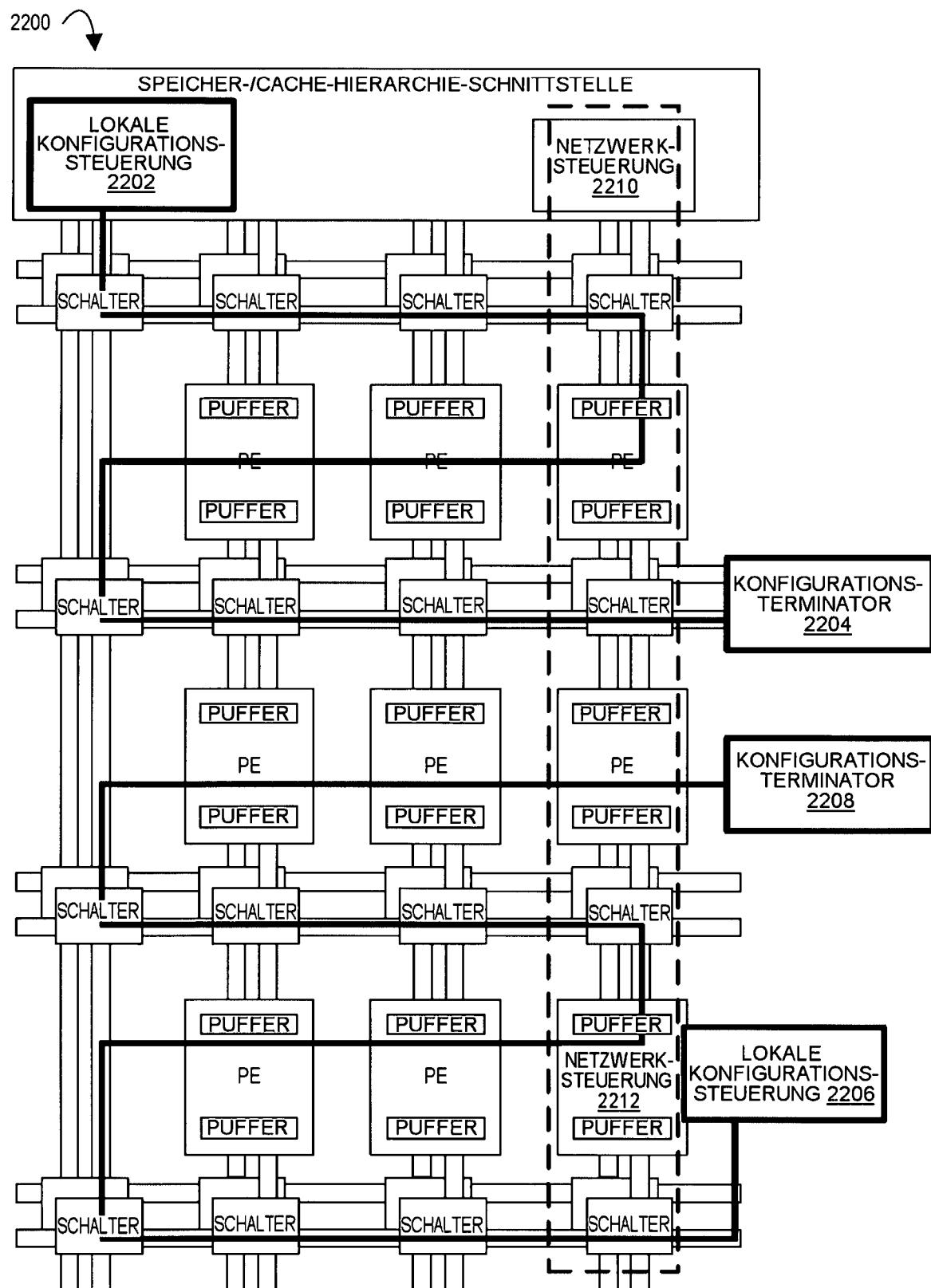

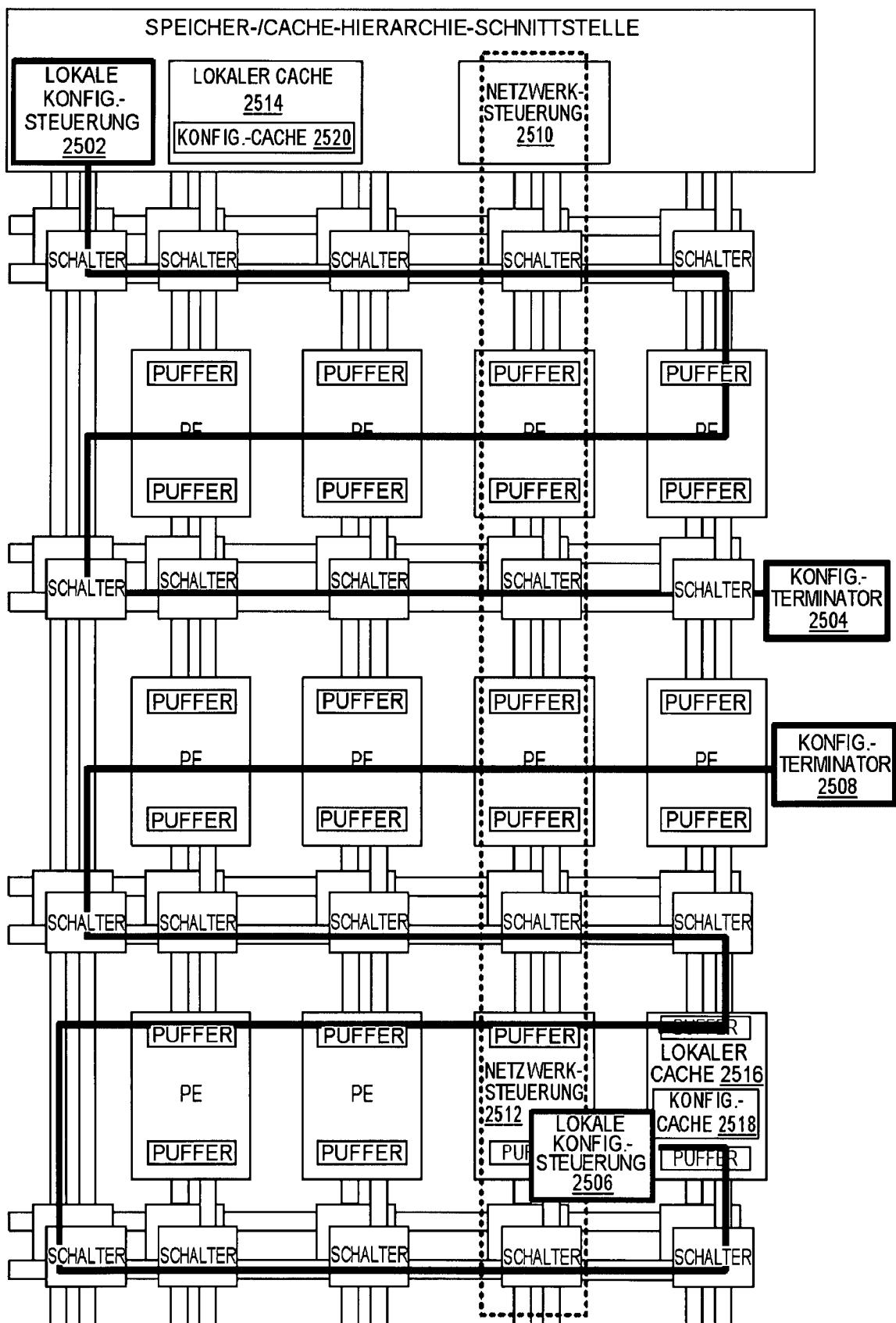

**Fig. 22** veranschaulicht eine Beschleuniger-Kachel, umfassend ein Array von Verarbeitungselementen und eine lokale Konfigurationssteuerung gemäß Ausführungsformen der Offenbarung;

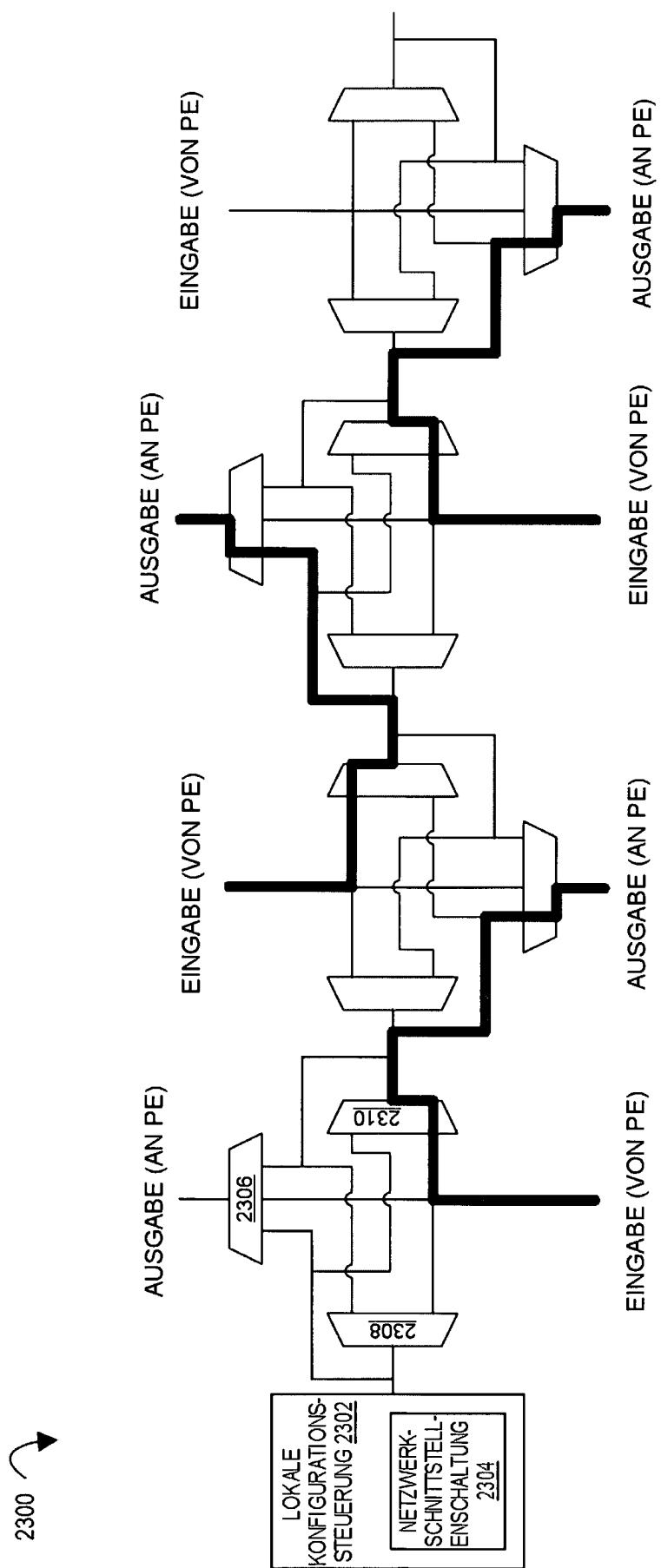

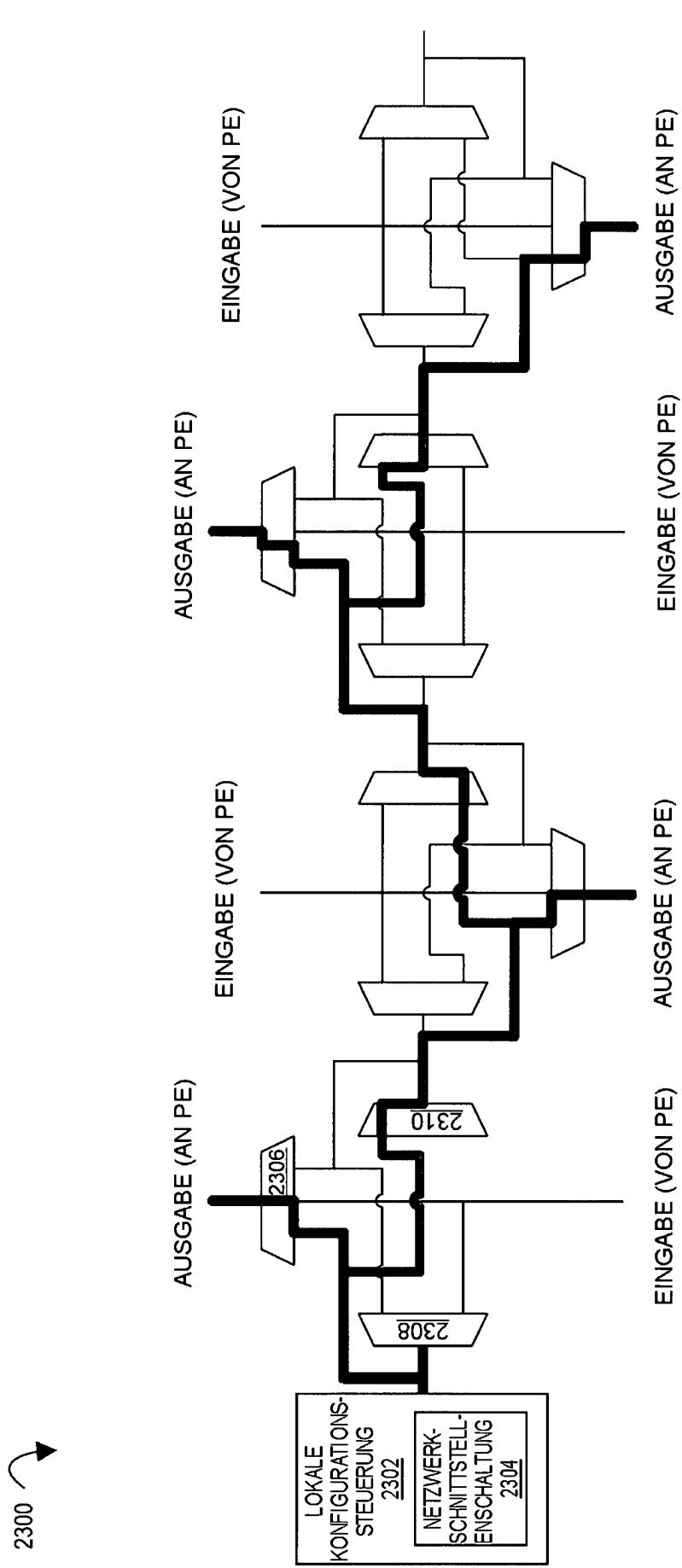

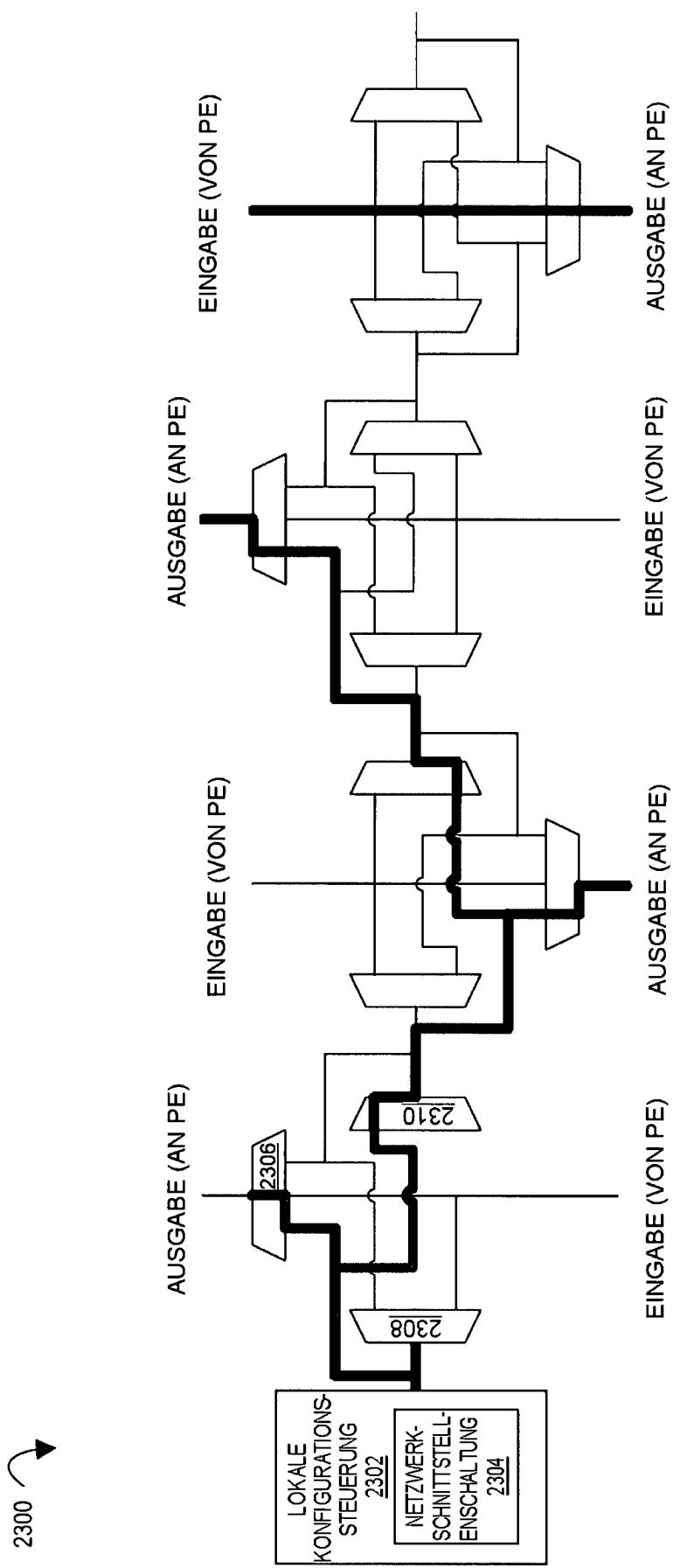

**Fig. 23A-23C** veranschaulicht eine lokale Konfigurationssteuerung, die ein Datenpfad-Netzwerk konfiguriert, gemäß Ausführungsformen der Offenbarung;

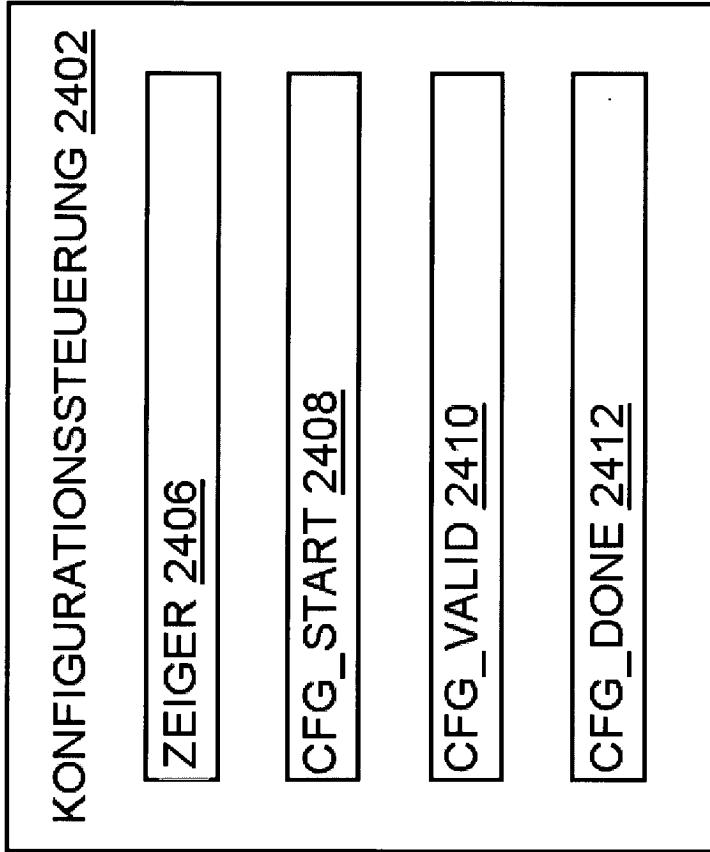

**Fig. 24** veranschaulicht eine Konfigurationssteuerung gemäß Ausführungsformen der Offenbarung;

**Fig. 25** veranschaulicht eine Beschleuniger-Kachel, umfassend ein Array von Verarbeitungselementen, ein Konfigurations-Cache und eine lokale Konfigurationssteuerung gemäß Ausführungsformen der Offenbarung;

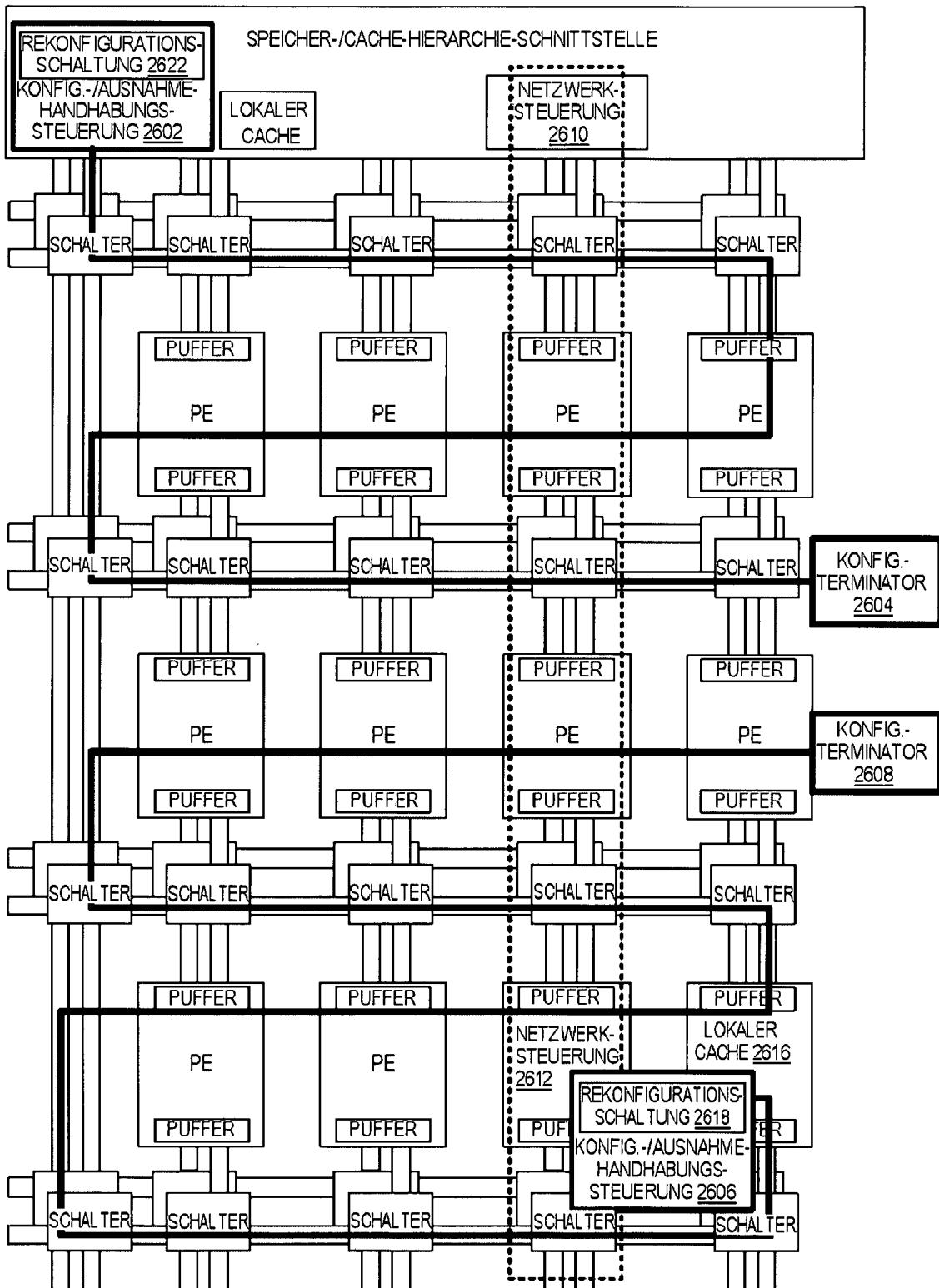

**Fig. 26** veranschaulicht eine Beschleuniger-Kachel, umfassend ein Array von Verarbeitungselementen und eine Konfigurations- und Ausnahmehandhabungssteuerung mit einer Rekonfigurationsschaltung gemäß Ausführungsformen der Offenbarung;

**Fig. 27** veranschaulicht eine Rekonfigurationsschaltung gemäß Ausführungsformen der Offenbarung;

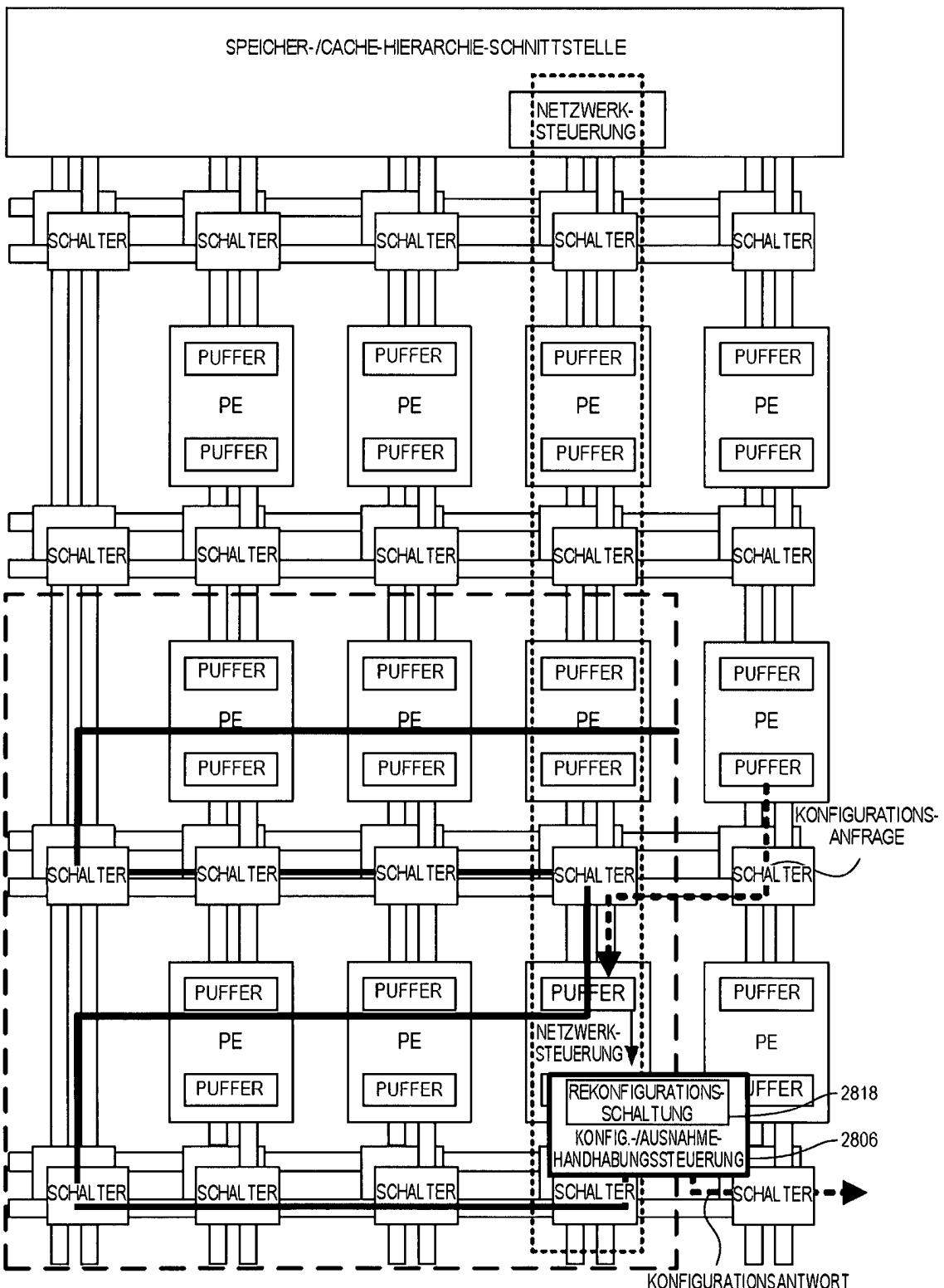

**Fig. 28** veranschaulicht eine Beschleuniger-Kachel, umfassend ein Array von Verarbeitungselementen und eine Konfigurations- und Ausnahmehandhabungssteuerung mit einer Rekonfigurationsschaltung gemäß Ausführungsformen der Offenbarung;

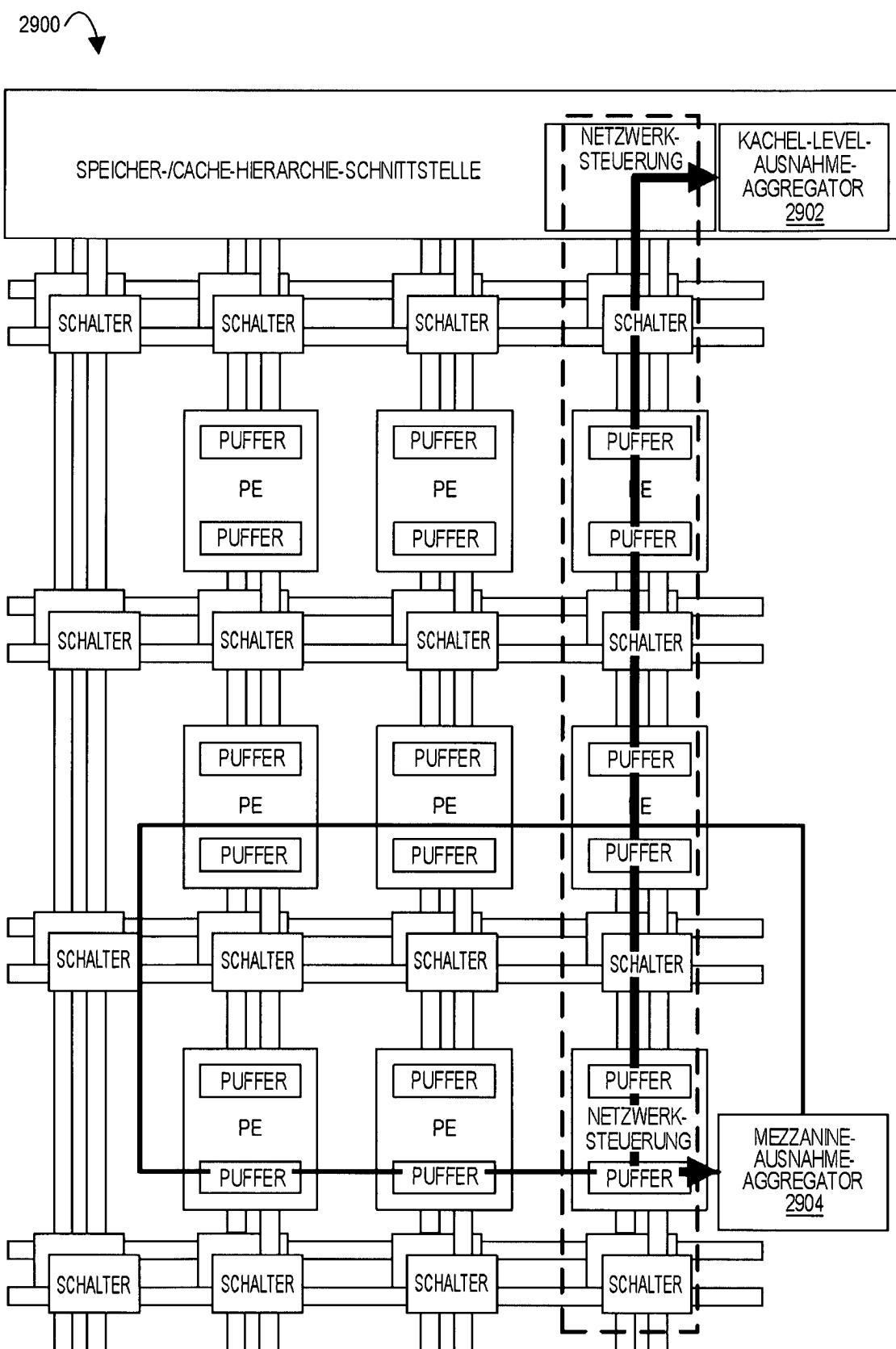

**Fig. 29** veranschaulicht eine Beschleuniger-Kachel, umfassend ein Array von Verarbeitungselementen und einen Mezzanine-Ausnahmeaggregator, der mit einem Kachel-Level-Ausnahmeaggregator gemäß Ausführungsformen der Offenbarung gekoppelt ist;

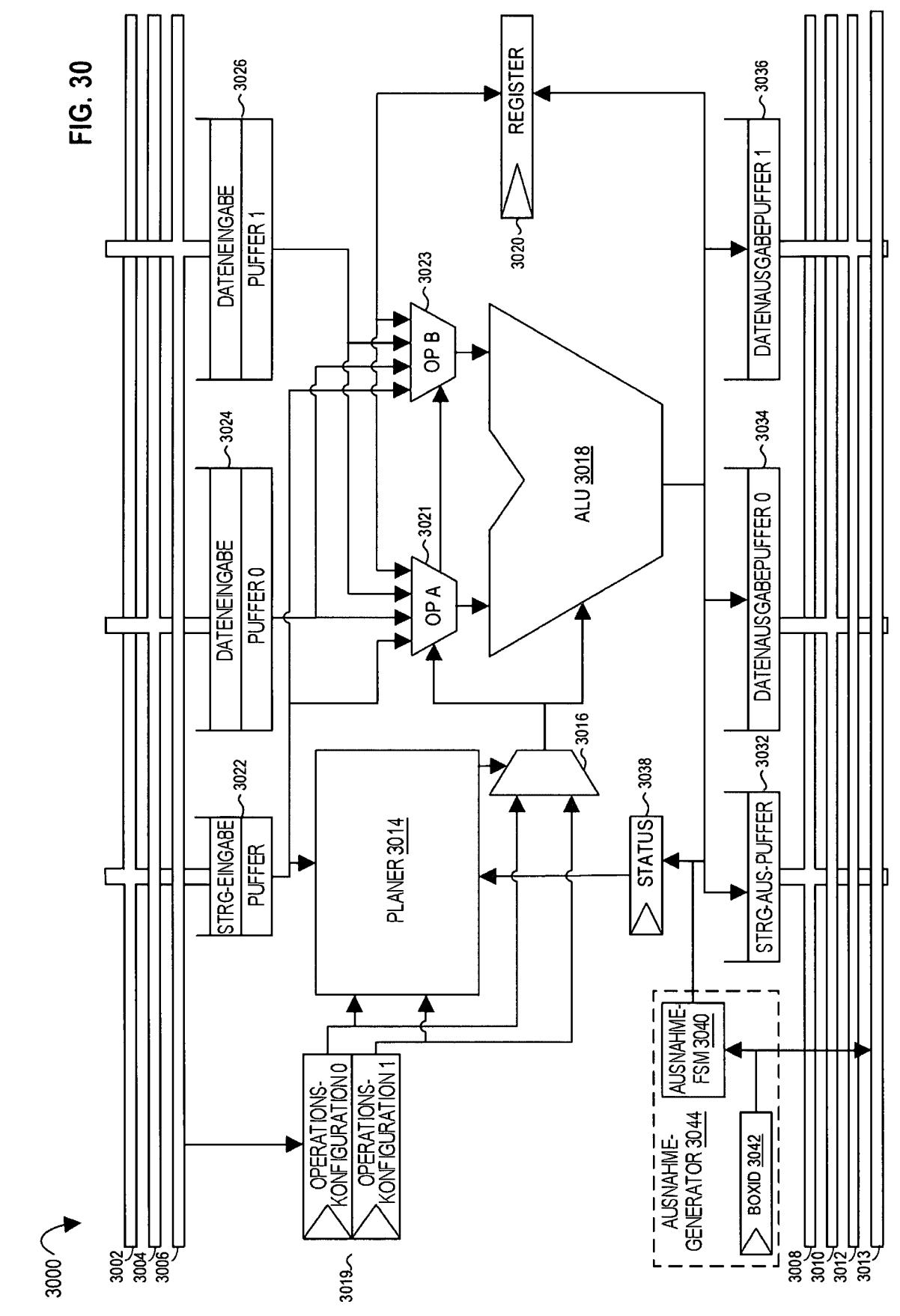

**Fig. 30** veranschaulicht ein Verarbeitungselement mit einem Ausnahmegenerator gemäß Ausführungsformen der Offenbarung;

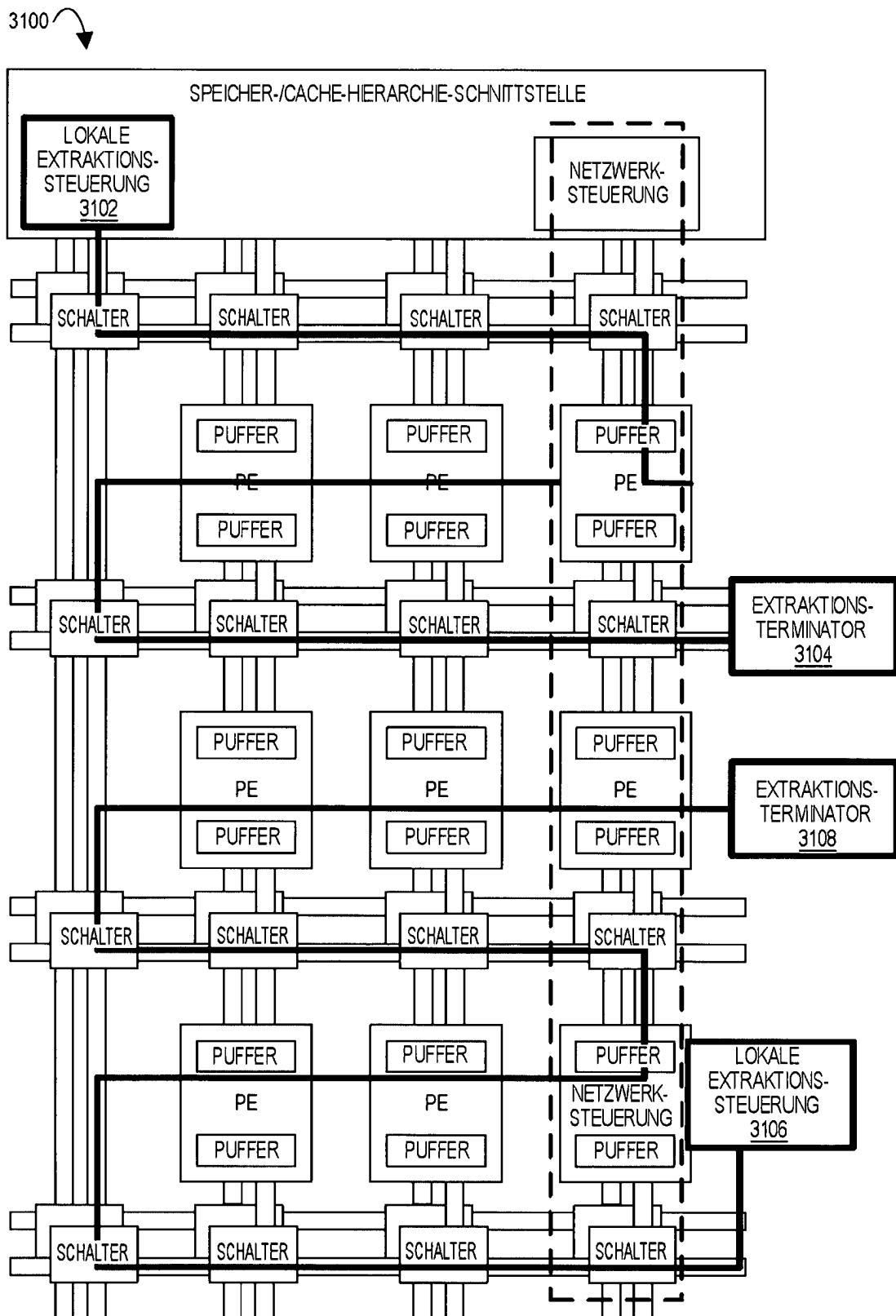

**Fig. 31** veranschaulicht eine Beschleuniger-Kachel, umfassend ein Array von Verarbeitungselementen und eine lokale Extraktionssteuerung gemäß Ausführungsformen der Offenbarung;

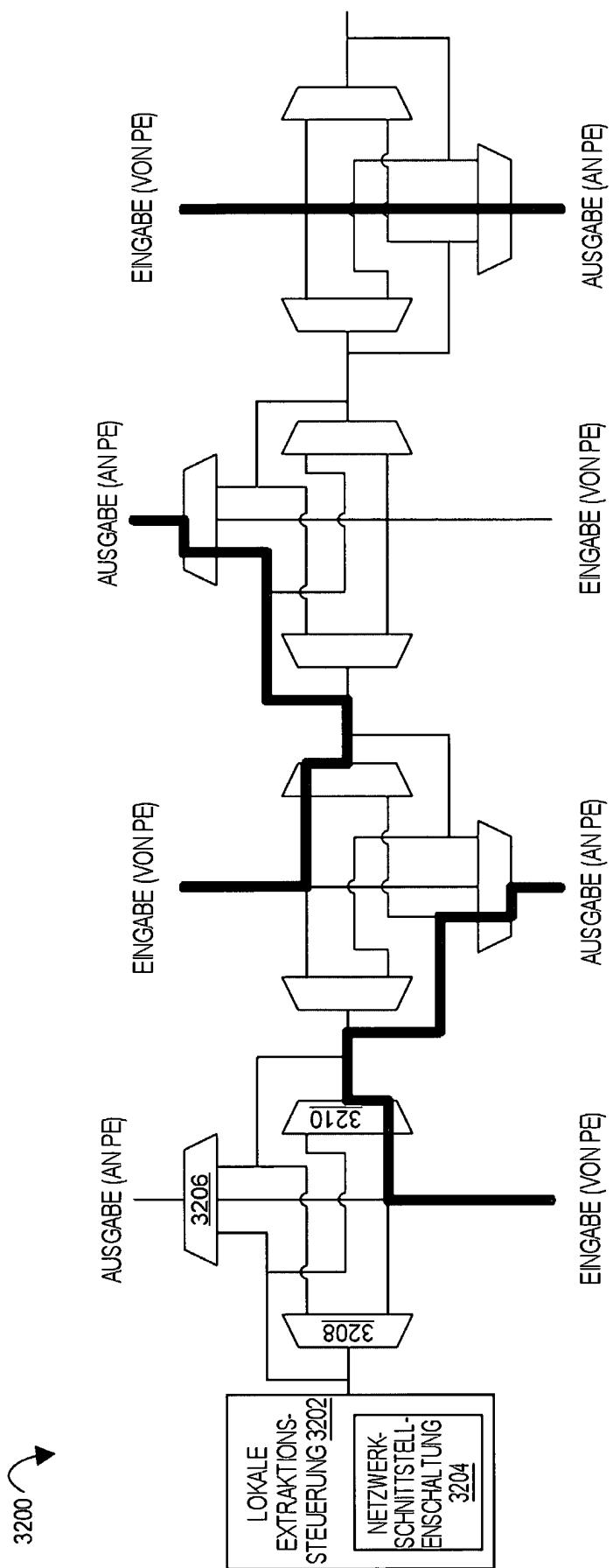

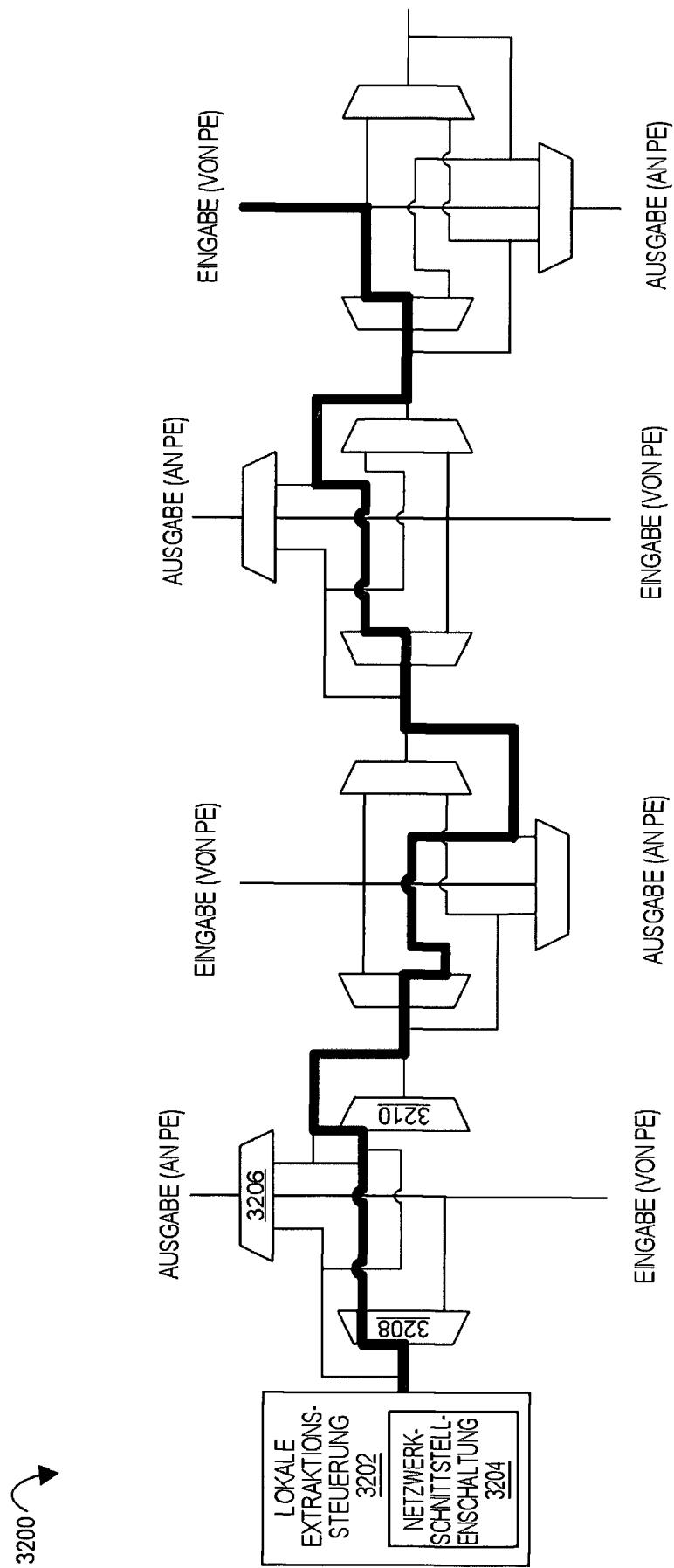

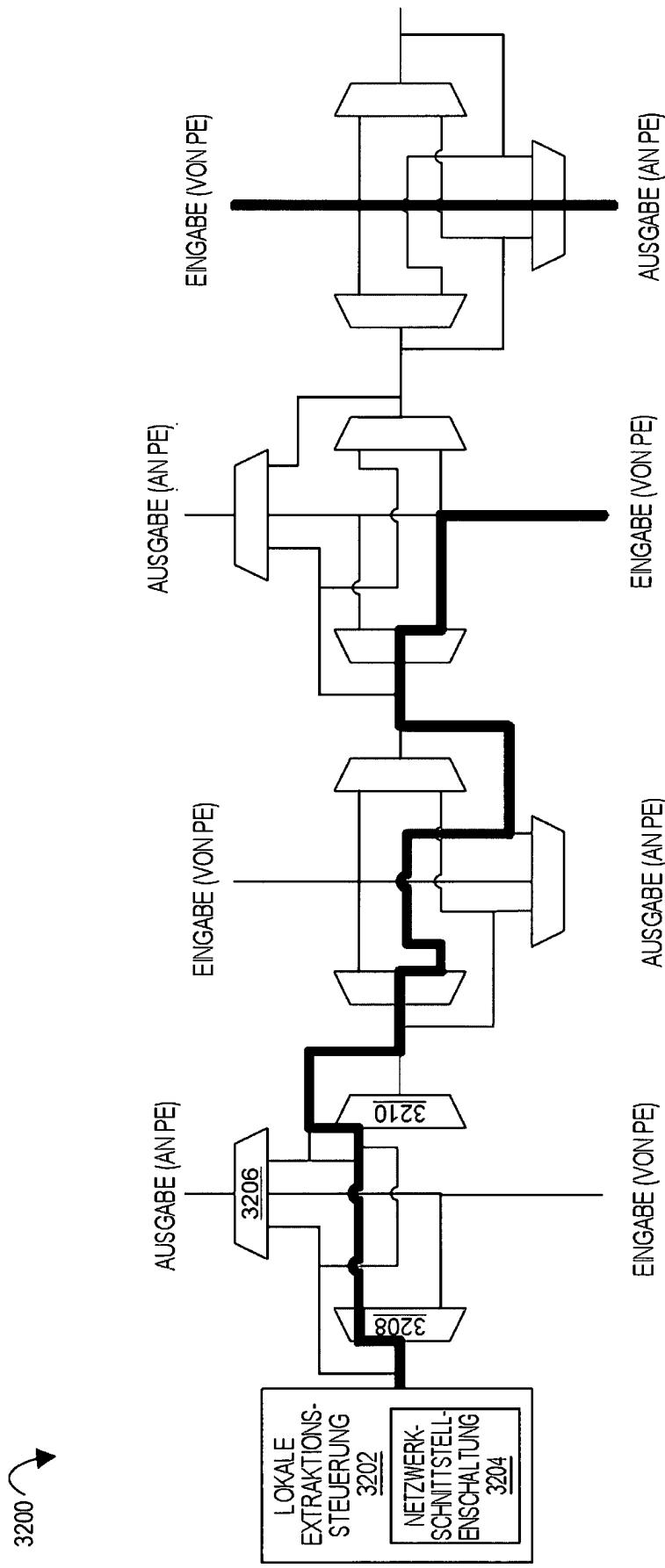

**Fig. 32A-32C** veranschaulicht eine lokale Extraktionssteuerung, die ein Datenpfad-Netzwerk konfiguriert, gemäß Ausführungsformen der Offenbarung;

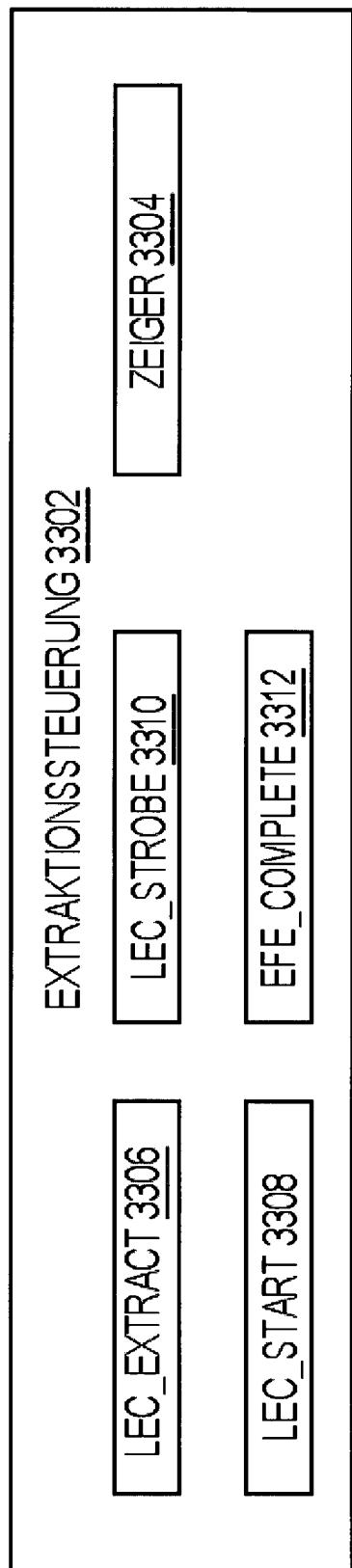

**Fig. 33** veranschaulicht eine Extraktionssteuerung gemäß Ausführungsformen der Offenbarung;

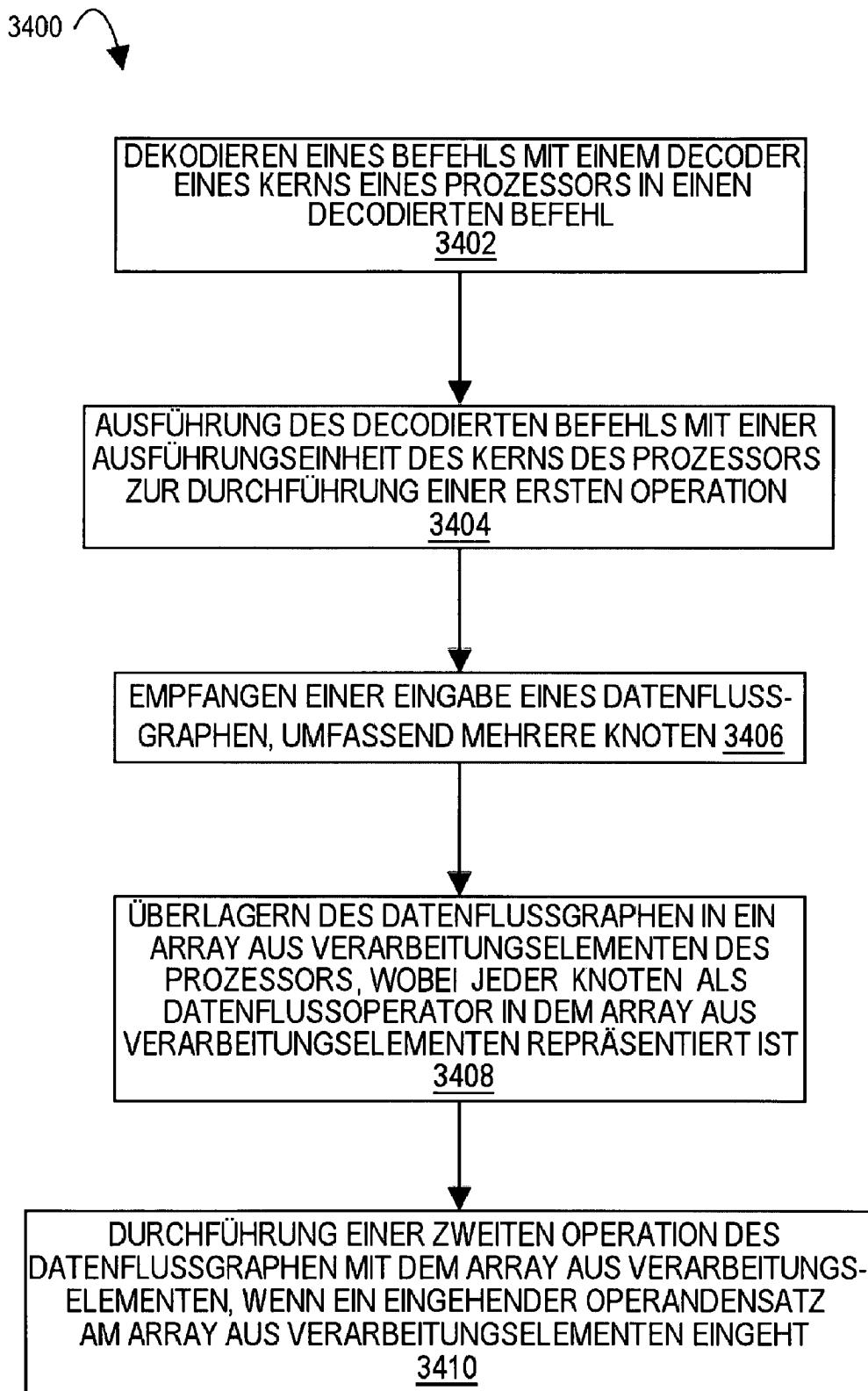

**Fig. 34** veranschaulicht ein Flussdiagramm gemäß Ausführungsformen der Offenbarung;

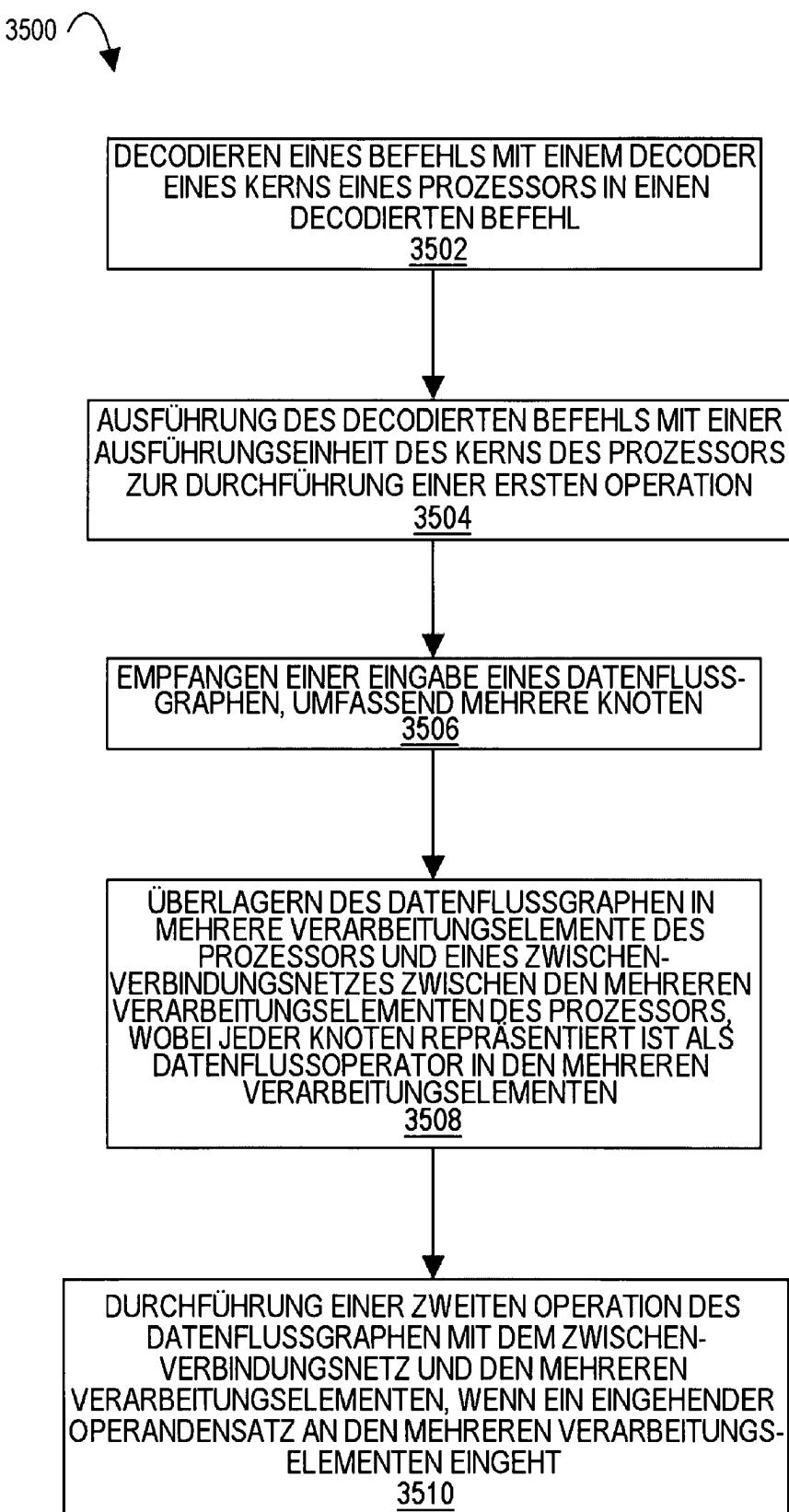

**Fig. 35** veranschaulicht ein Flussdiagramm gemäß Ausführungsformen der Offenbarung;

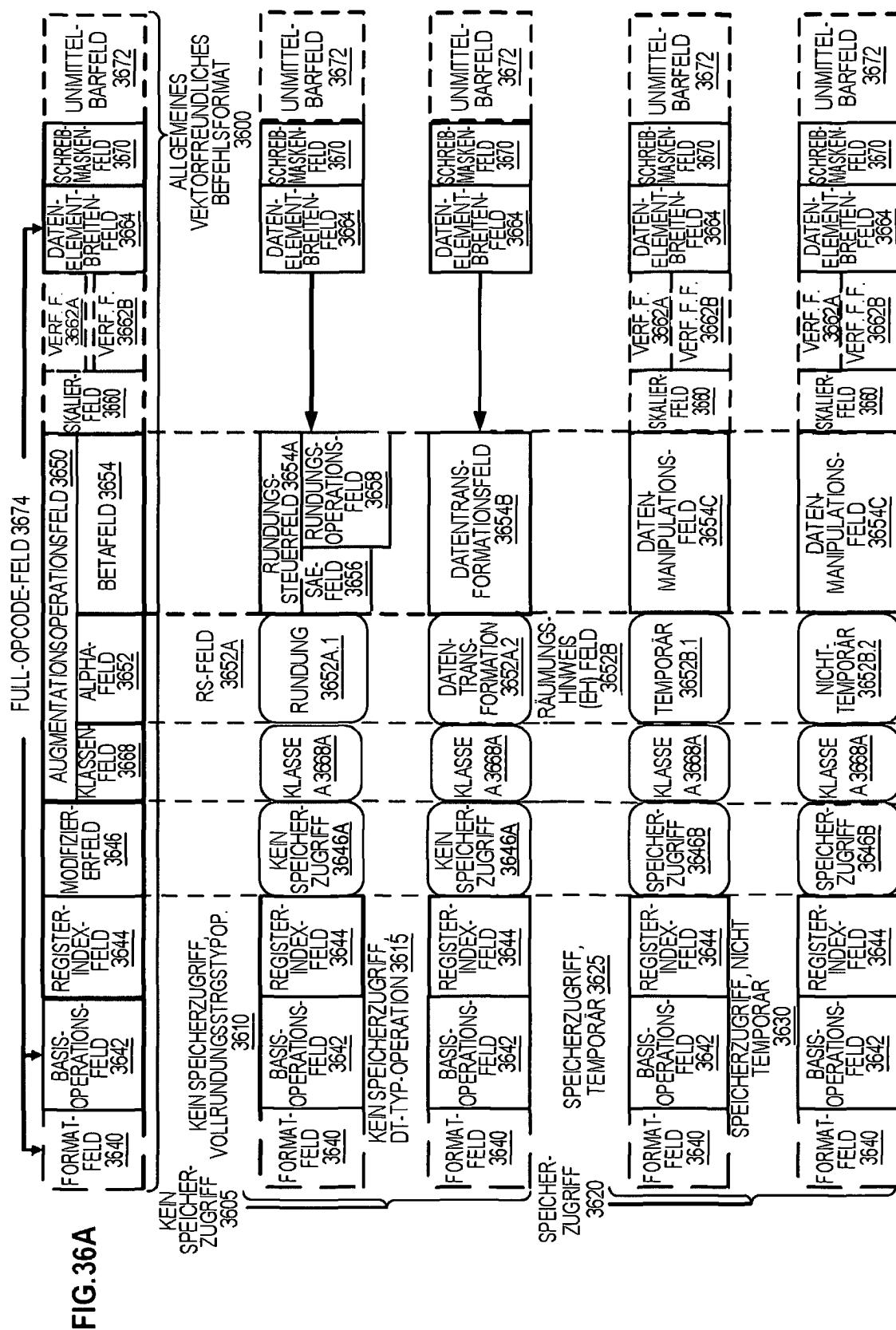

**Fig. 36A** ist ein Blockdiagramm, das ein allgemeines vektorfreundliches Befehlsformat und Klasse-A-Befehlstemplates gemäß Ausführungsformen der Offenbarung veranschaulicht;

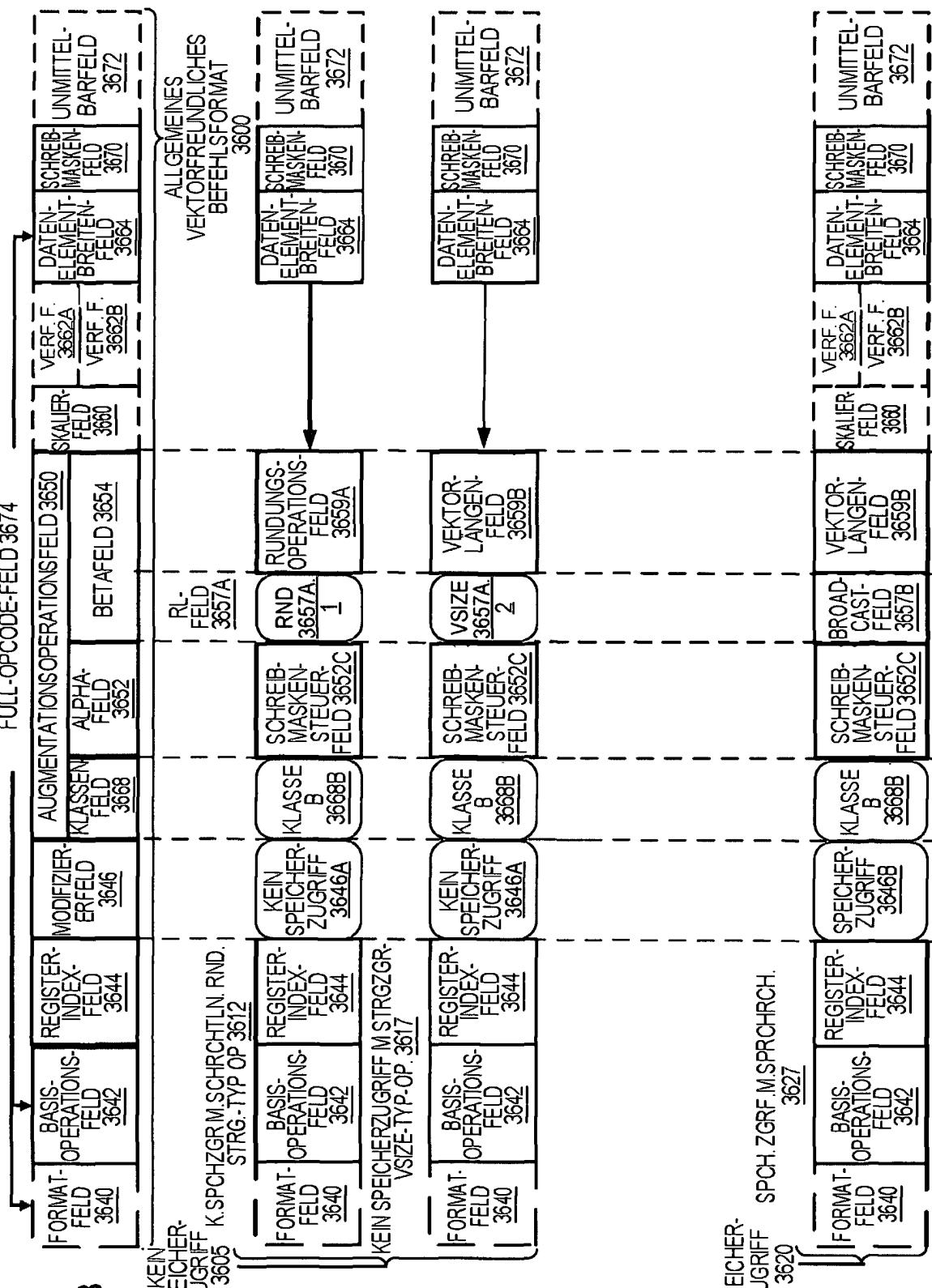

**Fig. 36B** ist ein Blockdiagramm, welches das allgemeine vektorfreundliche Befehlsformat und Klasse-B-Befehlstemplates davon gemäß Ausführungsformen der Offenbarung veranschaulicht;

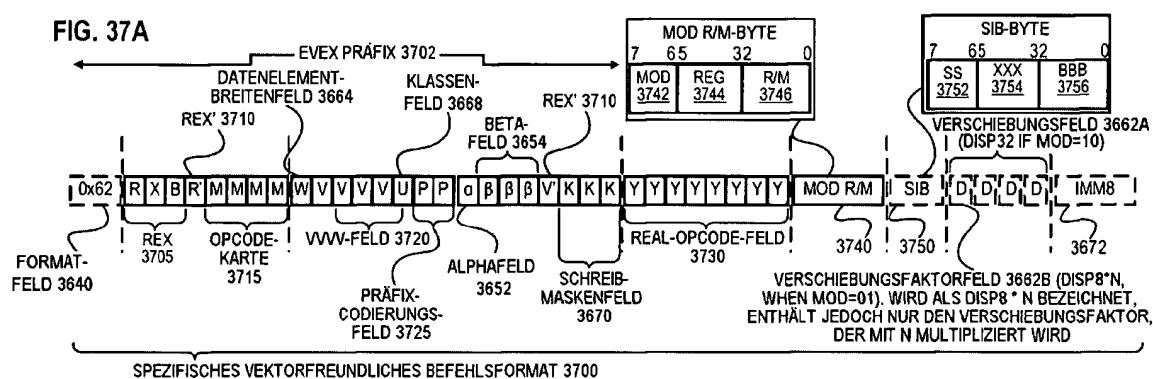

**Fig. 37A** ist ein Blockdiagramm, das Felder für die allgemeinen vektorfreundlichen Befehlsformate in **Fig. 36A** und **Fig. 36B** gemäß Ausführungsformen der Offenbarung veranschaulicht;

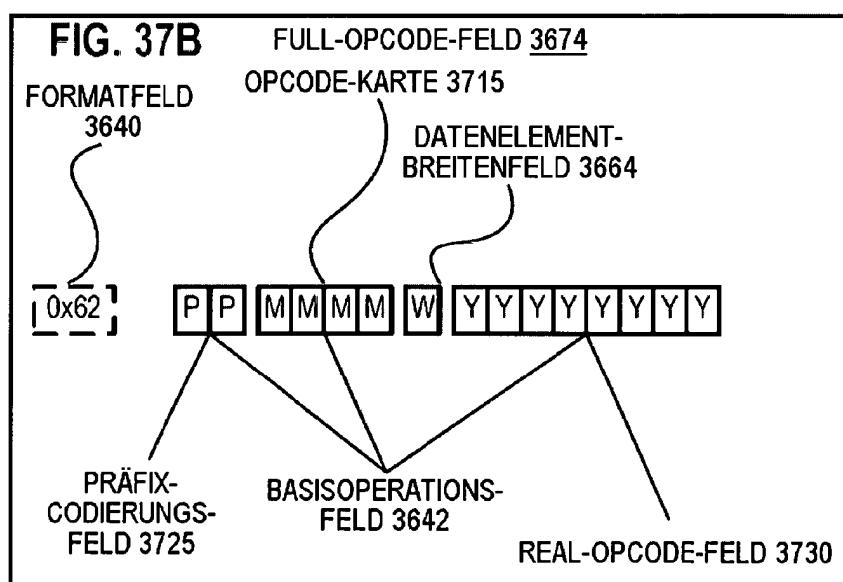

**Fig. 37B** ist ein Blockdiagramm, das die Felder des spezifischen vektorfreundlichen Befehlsformats aus **Fig. 37A** veranschaulicht, das ein Full-Opcode-Feld gemäß einer Ausführungsform der Offenbarung bildet;

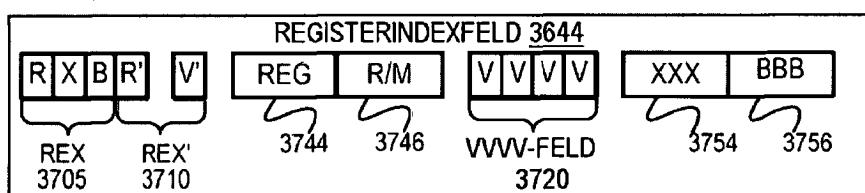

**Fig. 37C** ist ein Blockdiagramm, das die Felder des spezifischen vektorfreundlichen Befehlsformats aus **Fig. 37A** veranschaulicht, das ein Registerindex-Feld gemäß einer Ausführungsform der Offenbarung bildet;

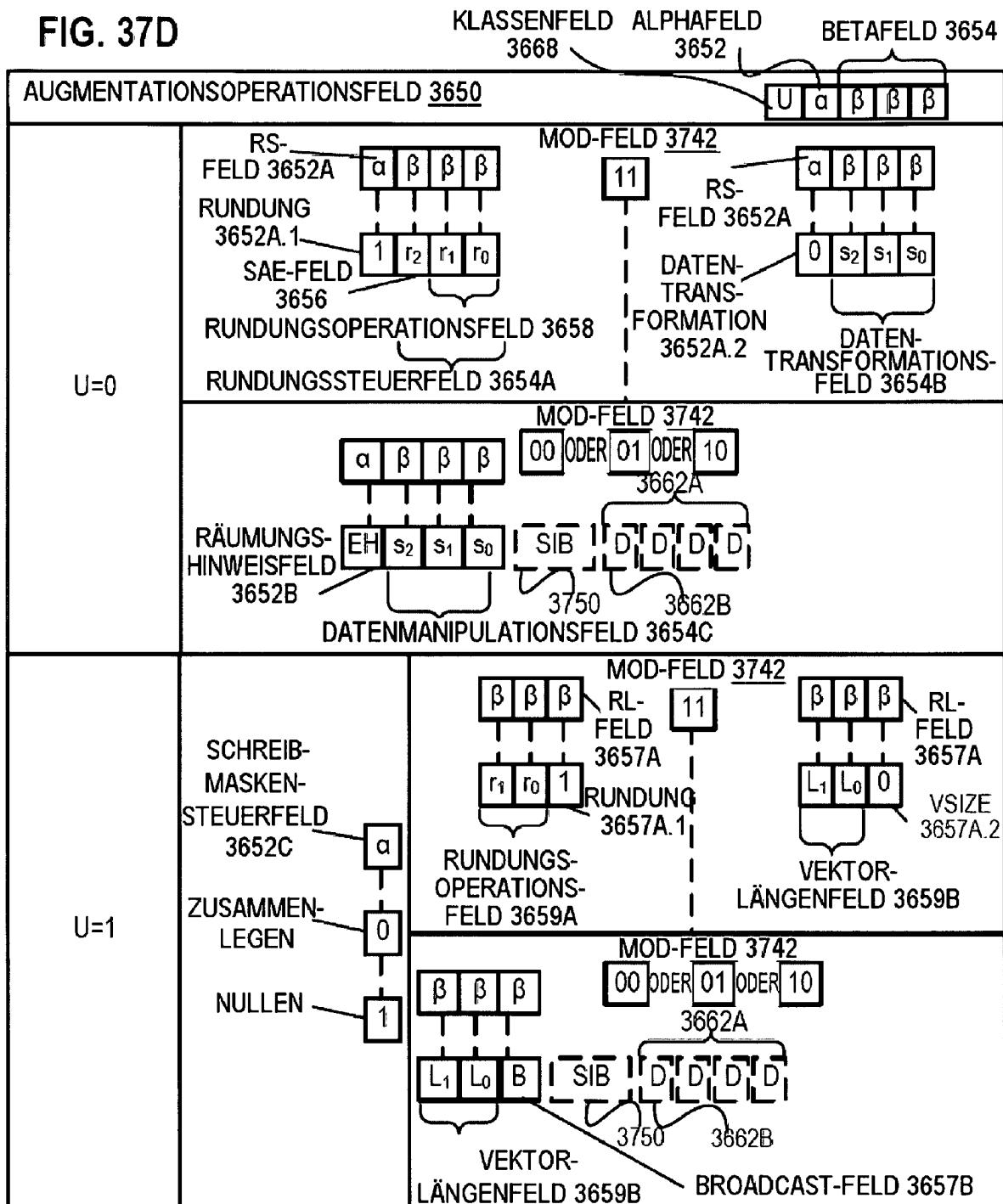

**Fig. 37D** ist ein Blockdiagramm, das die Felder des spezifischen vektorfreundlichen Befehlsformats aus **Fig. 37A** veranschaulicht, das ein Augmentationsoperationsfeld 3650 gemäß einer Ausführungsform der Offenbarung bildet;

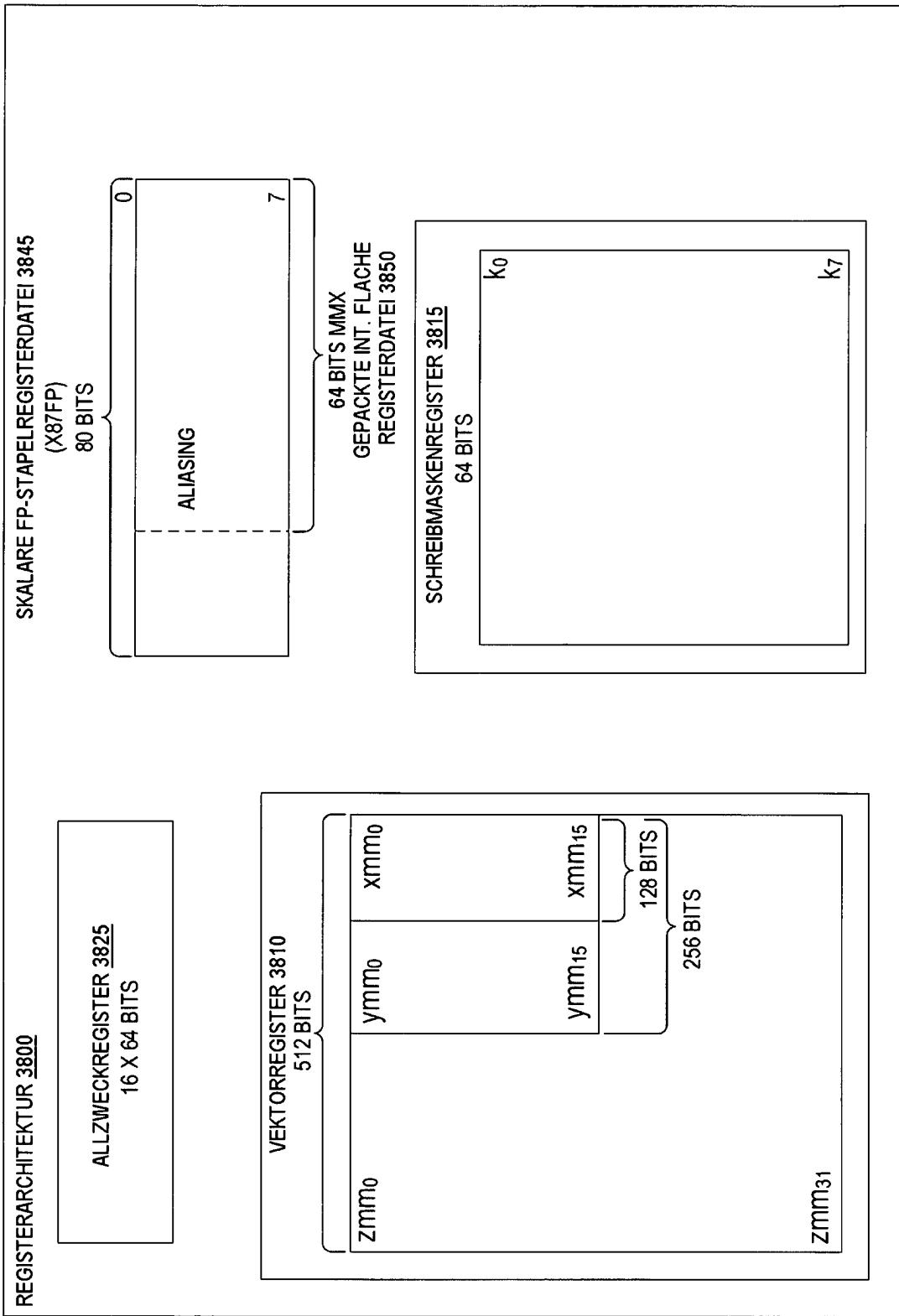

**Fig. 38** ist ein Blockdiagramm einer Registerarchitektur gemäß einer Ausführungsform der Offenbarung;

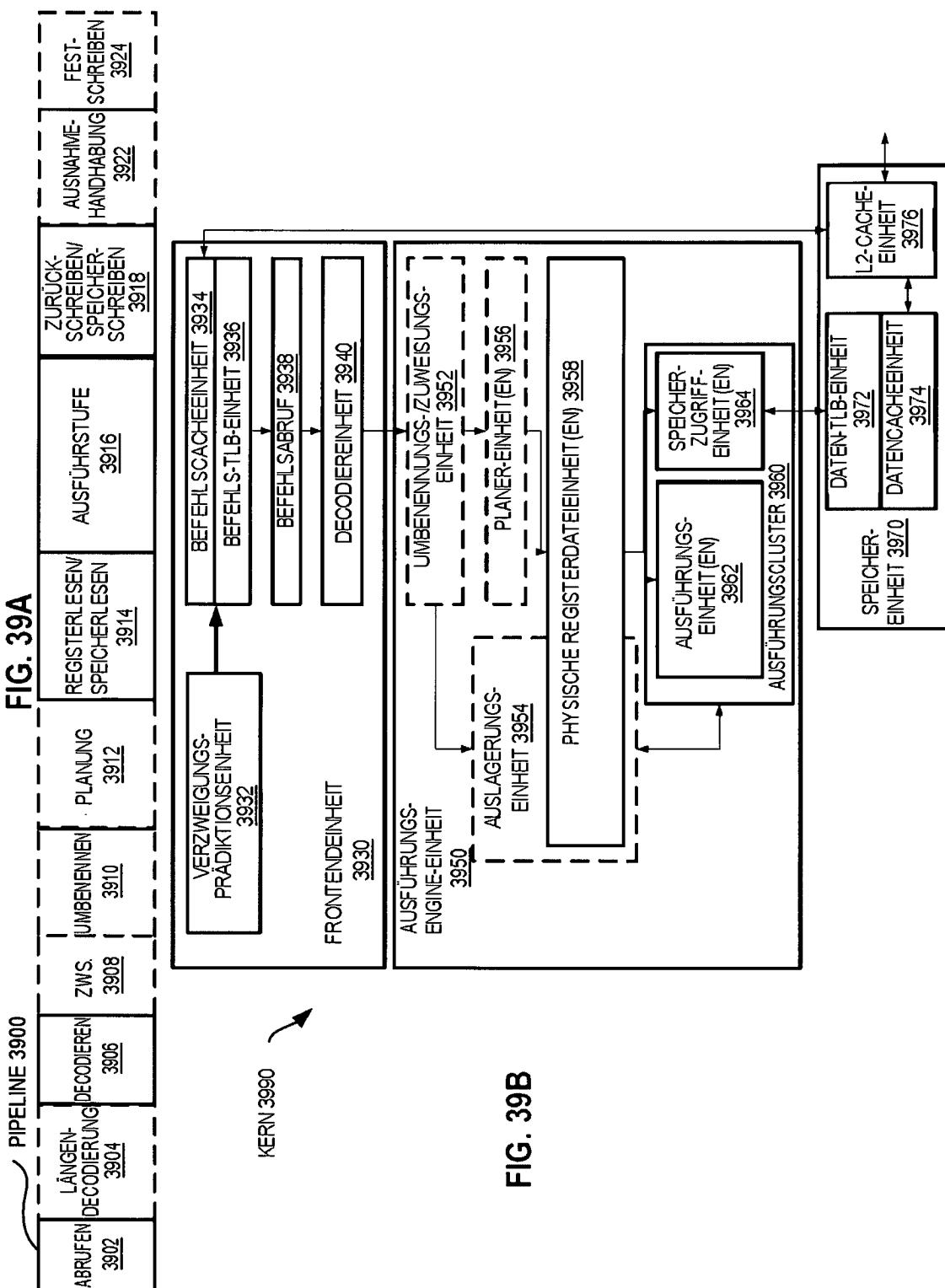

**Fig. 39A** ist ein Blockdiagramm, das sowohl eine beispielhafte In-Reihenfolge-Pipeline als auch eine beispielhafte Außer-Reihenfolge-Ausgabe/Ausführungspipeline mit Registerumbenennung gemäß Ausführungsformen der Offenbarung veranschaulicht;

**Fig. 39B** ist ein Blockdiagramm, das sowohl ein Ausführungsbeispiel eines In-Reihenfolge-Architekturkerns als auch einen beispielhaften Außer-Reihenfolge-Ausgabe/Ausführungsarchitekturkern, der in einen Prozessor aufzunehmen ist, gemäß Ausführungsformen der Offenbarung veranschaulicht;

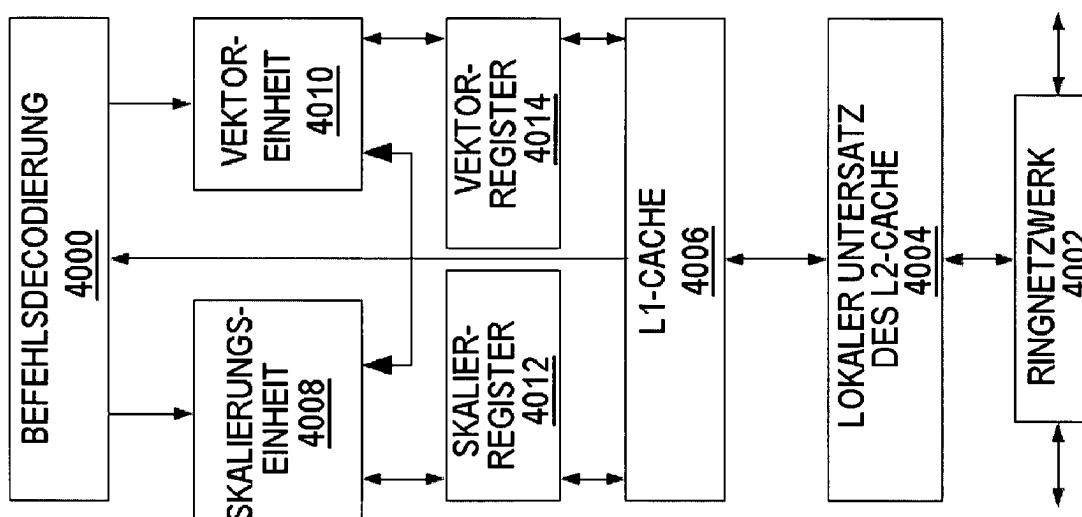

**Fig. 40A** ist ein Blockdiagramm eines einzelnen Prozessorkerns zusammen mit seiner Verbindung mit On-Die-Zwischenverbindungsnetzen und mit seinem lokalen Level 2 (L2) -Cacheuntersatz gemäß Ausführungsformen der Offenbarung;

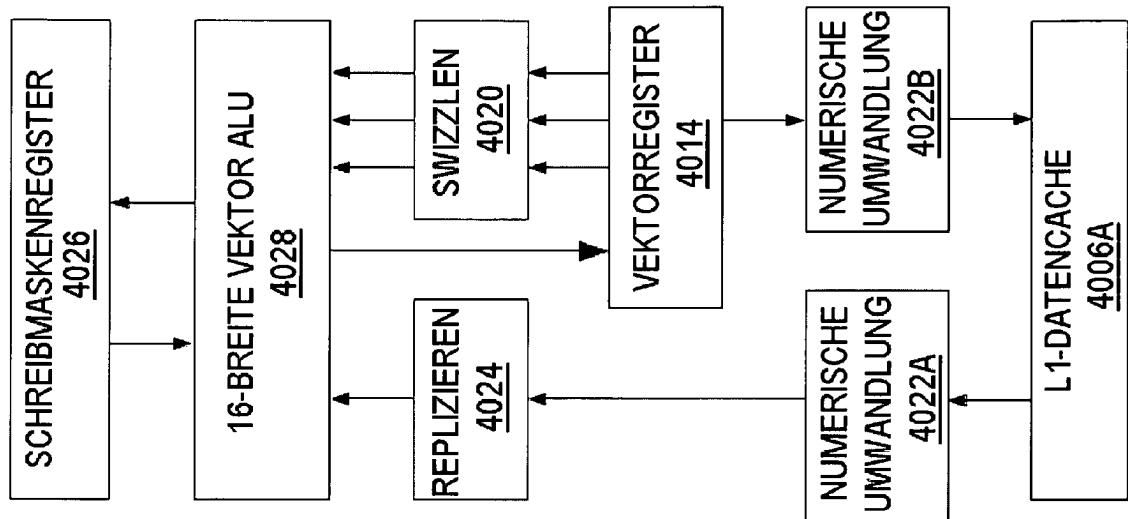

**Fig. 40B** ist eine auseinander gezogene Ansicht des Teils des Prozessorkerns aus **Fig. 40A** gemäß Ausführungsformen der Offenbarung;

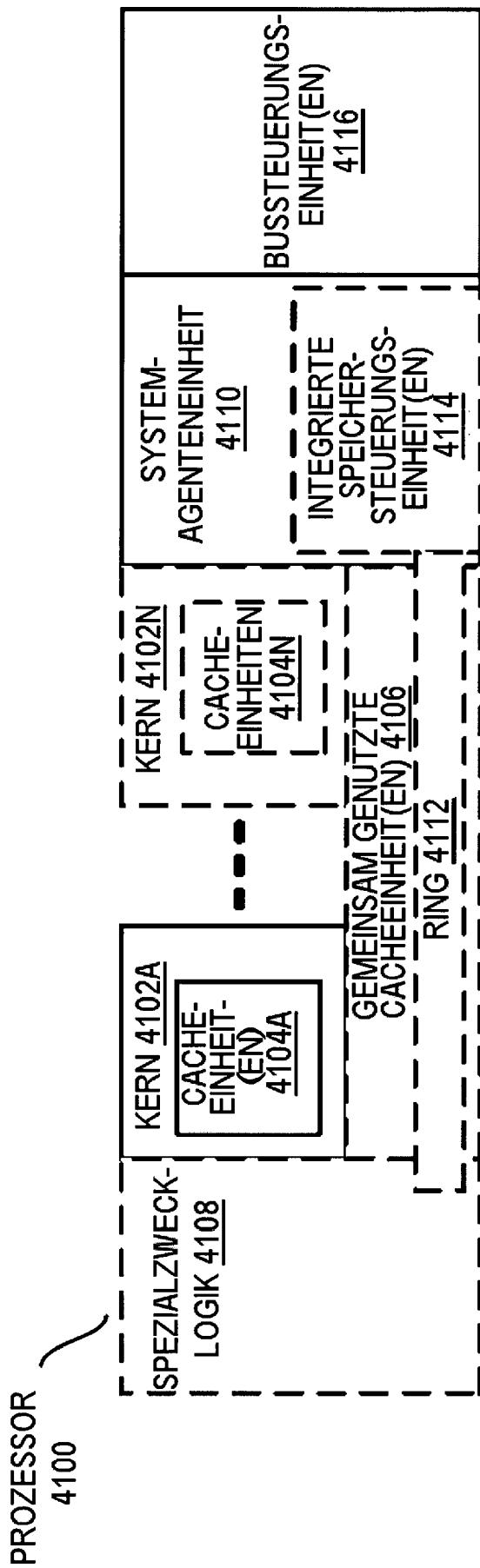

**Fig. 41** ist ein Blockdiagramm eines Prozessors, der mehr als einen Kern aufweisen kann, eine integrierte Speichersteuerung aufweisen kann und der eine integrierte Grafik gemäß Ausführungsformen der Offenbarung aufweisen kann;

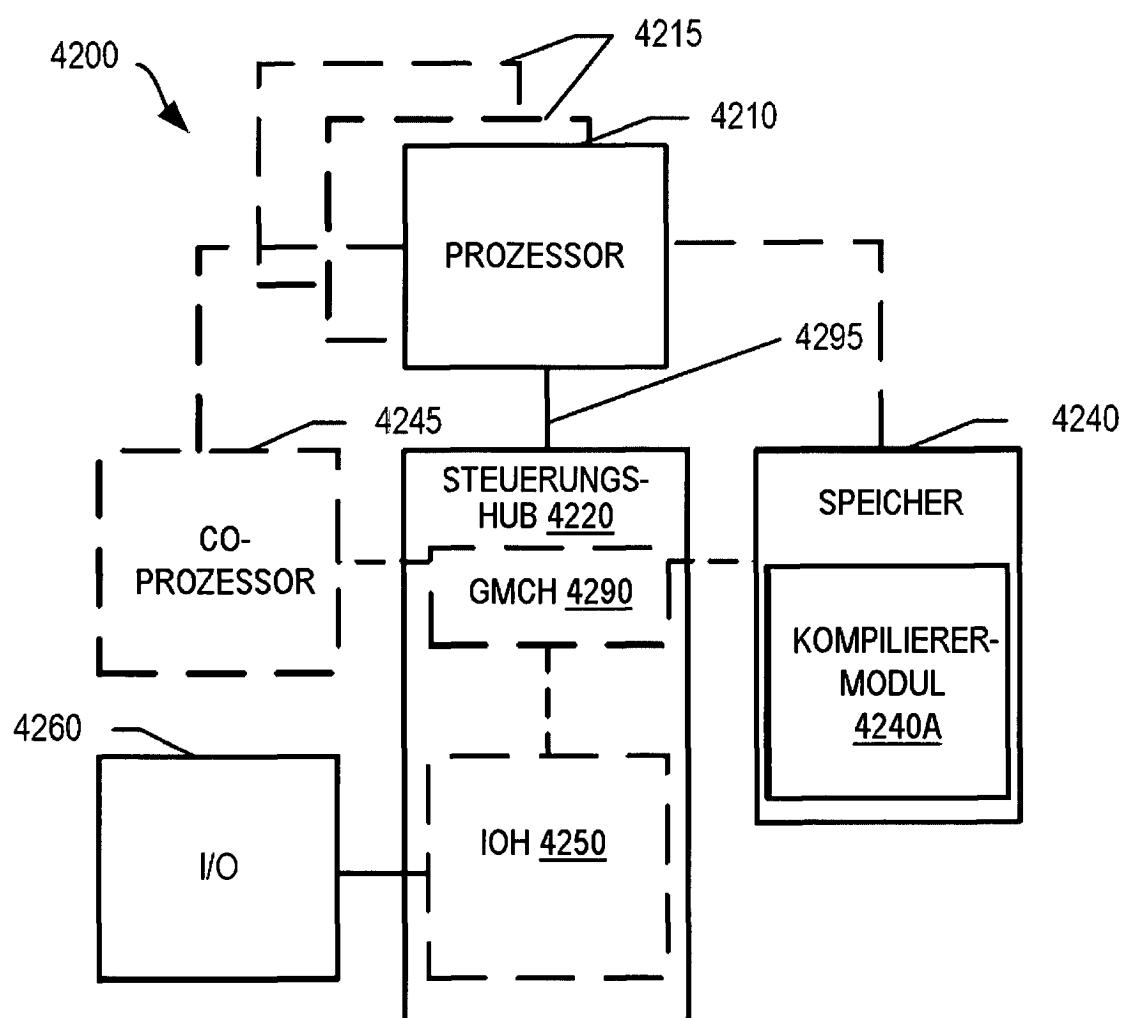

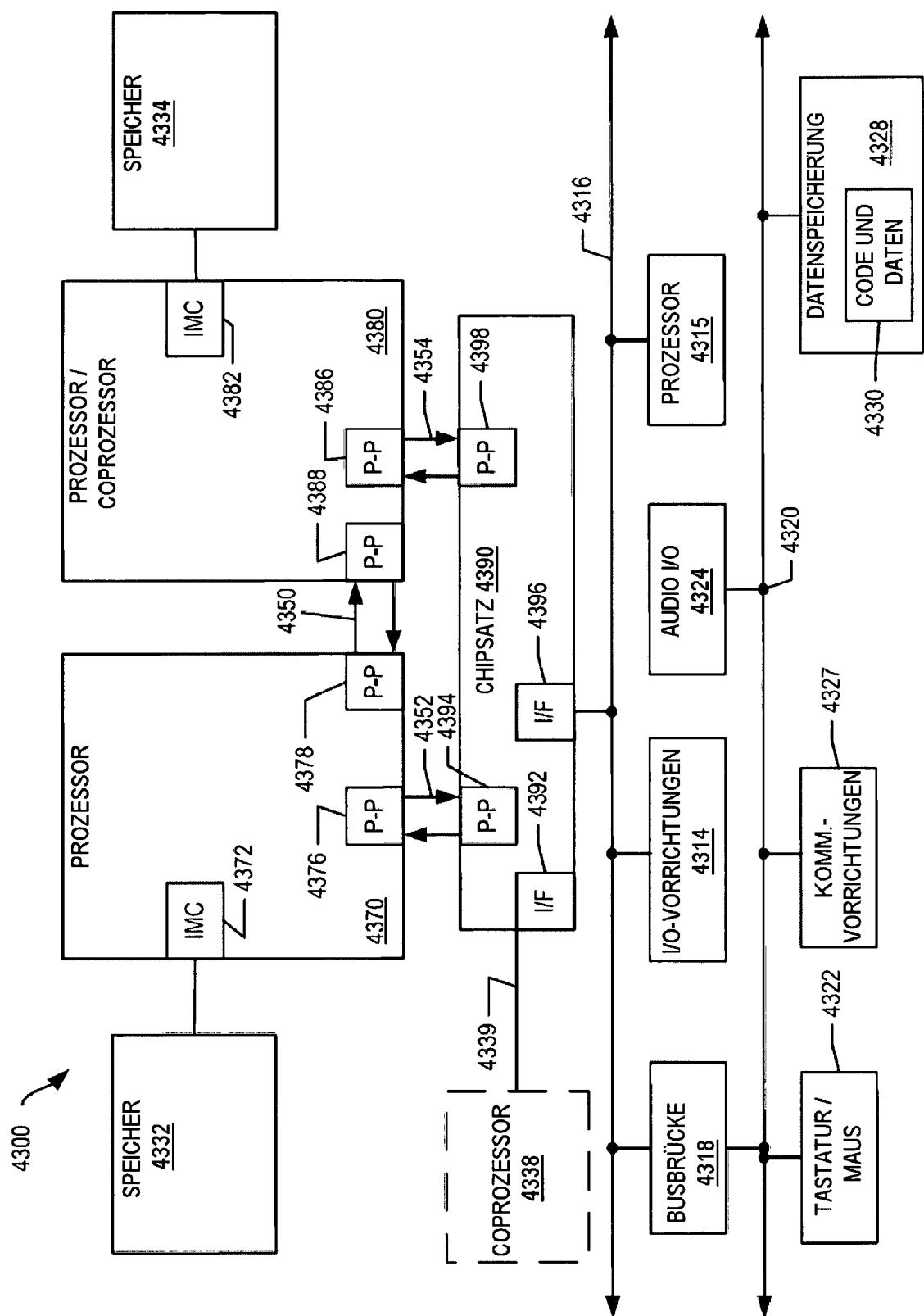

**Fig. 42** ist ein Blockdiagramm eines Systems gemäß einer Ausführungsform der vorliegenden Offenbarung;

**Fig. 43** ist ein Blockdiagramm eines spezifischeren beispielhaften Systems gemäß einer Ausführungsform der vorliegenden Offenbarung;

**Fig. 44** zeigt ein Blockdiagramm eines zweiten spezifischeren beispielhaften Systems gemäß einer Ausführungsform der vorliegenden Offenbarung;

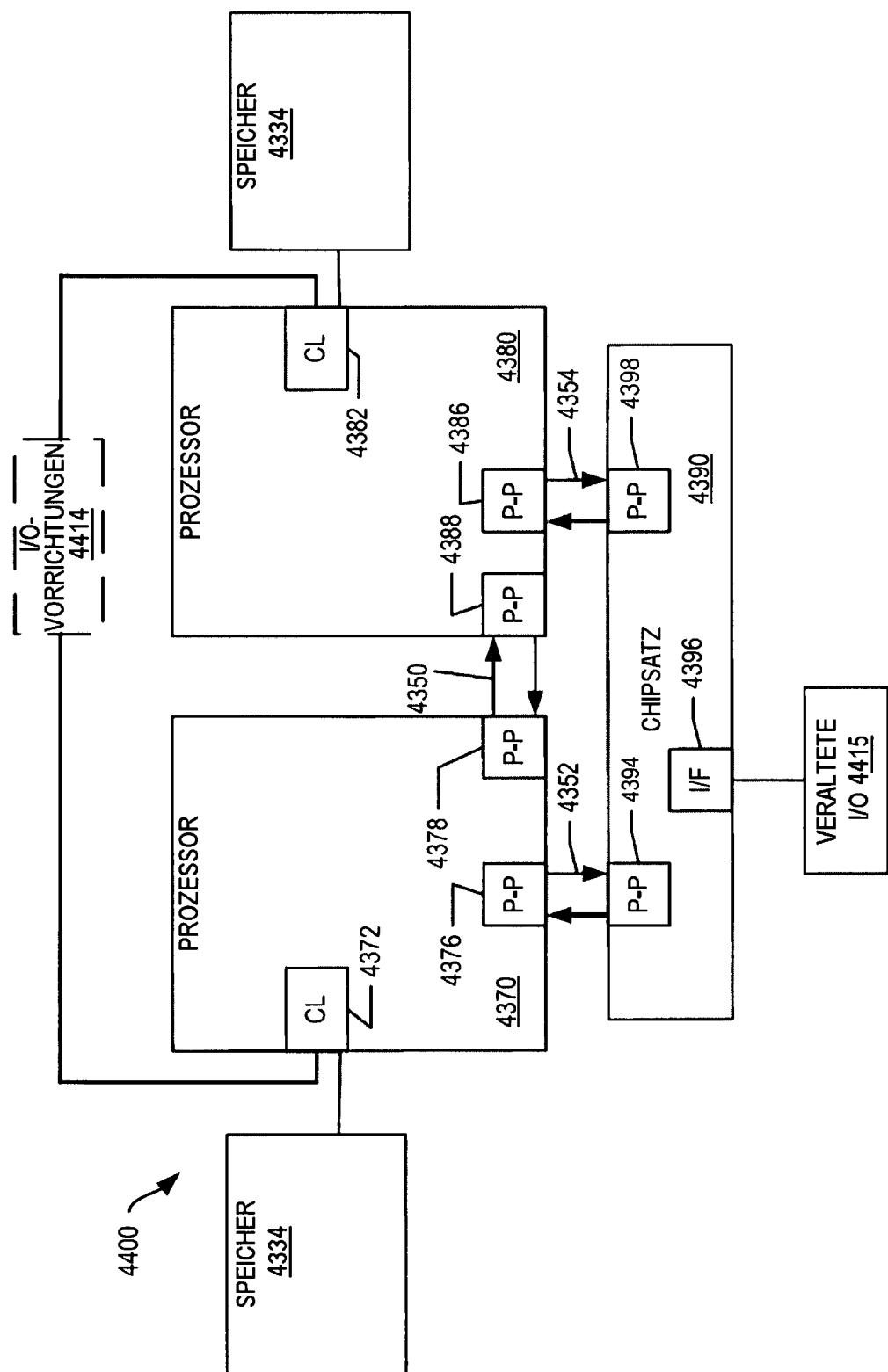

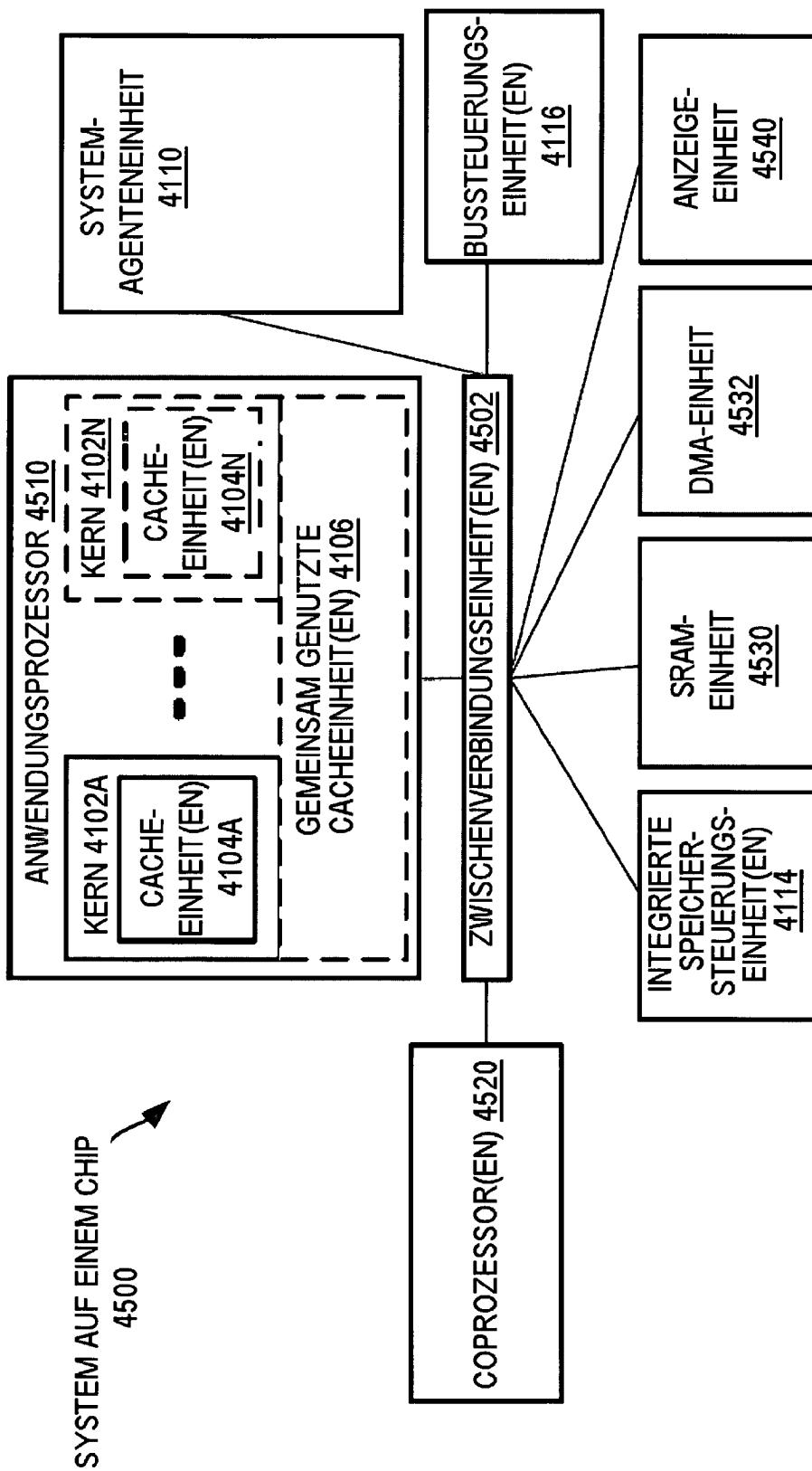

**Fig. 45** zeigt ein Blockdiagramm eines SoC (System-on-Chip) gemäß einer Ausführungsform der vorliegenden Offenbarung;

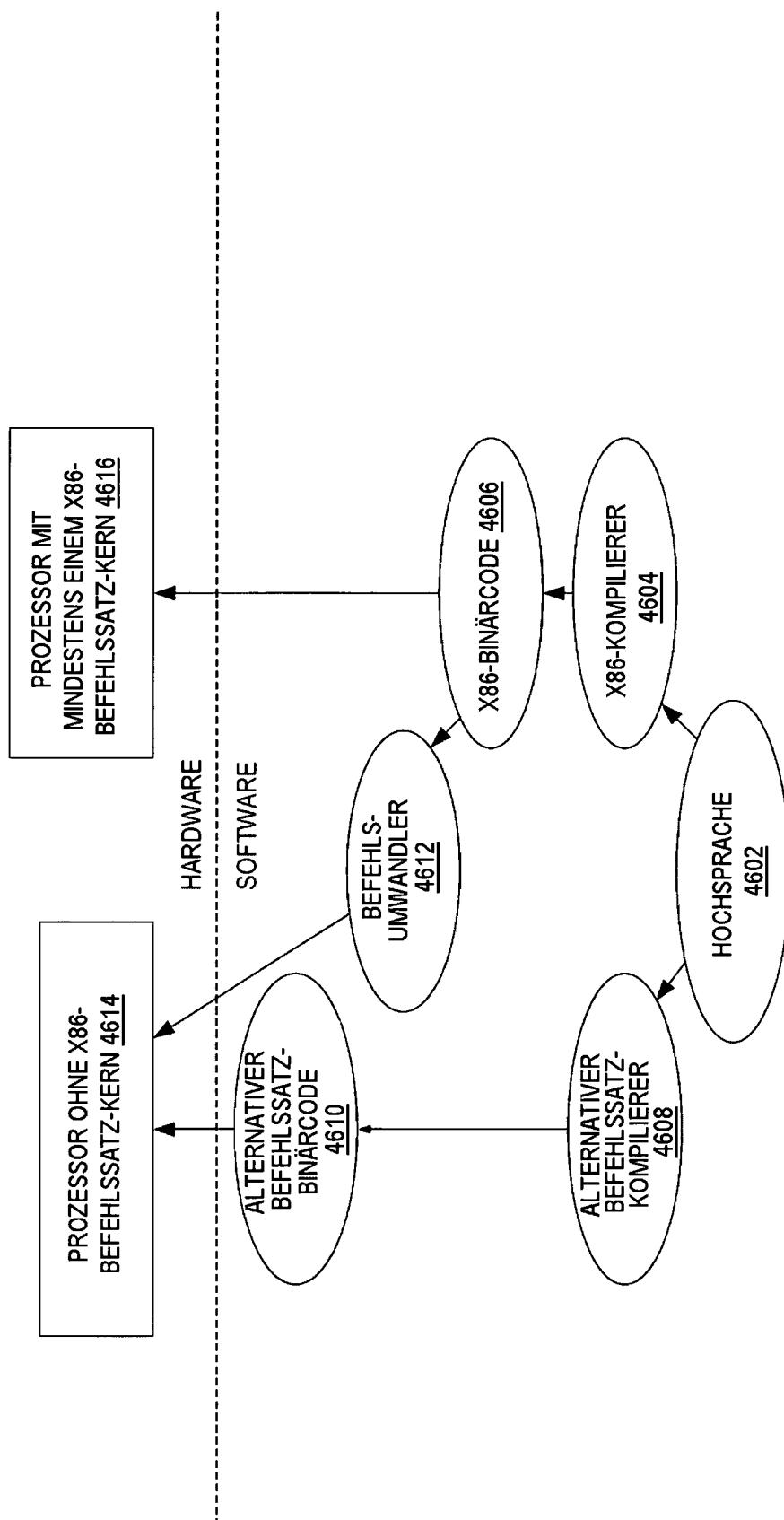

**Fig. 46** ist ein Blockdiagramm, das die Verwendung eines Softwarebefehlumwandlers zum Umwandeln von binären Befehlen in einem Quellbefehlssatz zu binären Befehlen in einem Zielbefehlssatz gemäß Ausführungsformen der Offenbarung kontrastiert.

## AUSFÜHRLICHE BESCHREIBUNG

**[0005]** In der folgenden Beschreibung sind zahlreiche spezielle Details dargelegt. Es versteht sich jedoch, dass Ausführungsformen der Offenbarung ohne diese spezifischen Details in die Praxis umgesetzt werden können. In anderen Fällen wurden hinlänglich bekannte Schaltungen, Strukturen und Techniken nicht im Detail gezeigt, um das Verständnis dieser Beschreibung nicht zu verschleiern.

**[0006]** Bezugnahmen in der Beschreibung auf „eine Ausführungsform“, „Ausführungsform“, „ein Ausführungsbeispiel“ usw. geben an, dass die beschriebene Ausführungsform ein bestimmtes Merkmal, eine bestimmte Struktur oder ein bestimmtes Charakteristikum aufweisen kann, wobei allerdings nicht jede Ausführungsform dieses bestimmte Merkmal, diese bestimmte Struktur oder dieses bestimmte Charakteristikum notwendigerweise aufweist. Darüber hinaus beziehen sich derartige Formulierungen nicht notwendigerweise auf dieselbe Ausführungsform. Wenn ein bestimmtes Merkmal, eine bestimmte Struktur oder ein bestimmtes Charakteristikum in Verbindung mit einer Ausführungsform beschrieben wird, wird außerdem angenommen, dass es im Kenntnisbereich eines Fachmannes liegt, auf ein derartiges Merkmal, eine derartige Struktur oder ein derartiges Charakteristikum in Verbindung mit anderen Ausführungsformen einzuwirken, ob es nun explizit beschrieben wurde oder nicht.

**[0007]** Ein Prozessor (z. B. mit einem oder mehreren Kernen) kann Befehle ausführen (z. B. einen Thread von Befehlen), um Daten zu bearbeiten, um beispielsweise arithmetische, logische oder andere Funktionen durchzuführen. Zum Beispiel kann Software eine Operation anfordern, und ein Hardware-Prozessor (z. B. ein Kern oder Kerne davon) kann die Operation als Reaktion auf die Anfrage durchführen. Ein nicht einschränkendes Beispiel für eine Operation ist eine Mischoperation, um mehrere Vektorelemente einzugeben und einen Vektor mit mehreren Mischelementen auszugeben. In bestimmten Ausführungsformen wird eine Vielzahl von Operationen mit der Ausführung eines einzelnen Befehls erreicht.

**[0008]** Exascale-Leistung, z. B. wie vom Ministerium für Energie definiert, kann erfordern, dass die Gleitkomma-Punktleistung auf Systemebene  $10^{18}$  Gleitkomma-Operationen pro Sekunde (exaFLOPs) oder mehr innerhalb eines vorgegebenen (z. B. 20 MW) Leistungsbudgets übersteigt. Bestimmte Ausführungsformen hierin sind auf einen konfigurierbaren räumlichen Beschleuniger (CSA - Configurable Spatial Accelerator) gerichtet, der auf Hochleistungsrechnen (HPC - High Performance Computing) abzielt. Bestimmte Ausführungsformen eines CSA zielen auf die direkte Ausführung eines Datenflussgraphen ab, um eine rechenintensive, jedoch energieeffiziente räumliche Mikroarchitektur zu erhalten, die herkömmliche Roadmap-Architekturen weit übersteigt. Im Folgenden wird eine Beschreibung der Architekturphilosophie von Ausführungsformen eines CSA und bestimmter Merkmale davon gegeben. Wie bei jeder revolutionären Architektur kann die Programmierbarkeit ein Risiko darstellen. Zur Abschwächung dieses Problems wurden Ausführungsformen der CSA-Architektur zusammen mit einer Kompilier-Toolkette ausgestaltet, die ebenfalls unten erläutert wird.

## EINLEITUNG

**[0009]** Exascale-Rechenziele können eine enorme Gleitkommaleistung auf Systemebene (z. B. 1 ExaFLOPs) innerhalb eines aggressiven Leistungsbudgets (z. B. 20 MW) erfordern. Die gleichzeitige Verbesserung der Leistung und Energieeffizienz der Programmausführung mit klassischen von Neumann-Architekturen ist jedoch schwierig geworden: Außer-Reihenfolge-Planung, simultanes Multithreading, komplexe Registerdateien und andere Strukturen stellen Leistung bereit, jedoch mit hohen Energiekosten. Bestimmte Ausführungsformen hierin erreichen gleichzeitig die Leistungs- und Energieanforderungen. Exascale-Rechenenergie-Leistungsziele können sowohl einen hohen Durchlauf als auch einen geringen Energieverbrauch pro Operation erfordern. Bestimmte Ausführungsformen hierin stellen dies bereit, indem sie eine große Anzahl von niederkomplexen, energieeffizienten Verarbeitungs- (z. B. Rechen-) Elementen bereitstellen, die den Steuerungsaufwand bisheriger Prozessorausgestaltungen weitgehend beseitigt. Geleitet von dieser Beobachtung weisen bestimmte Ausführungsformen hierin einen konfigurierbaren räumlichen Beschleuniger (CSA) auf, der z. B. ein Array aus

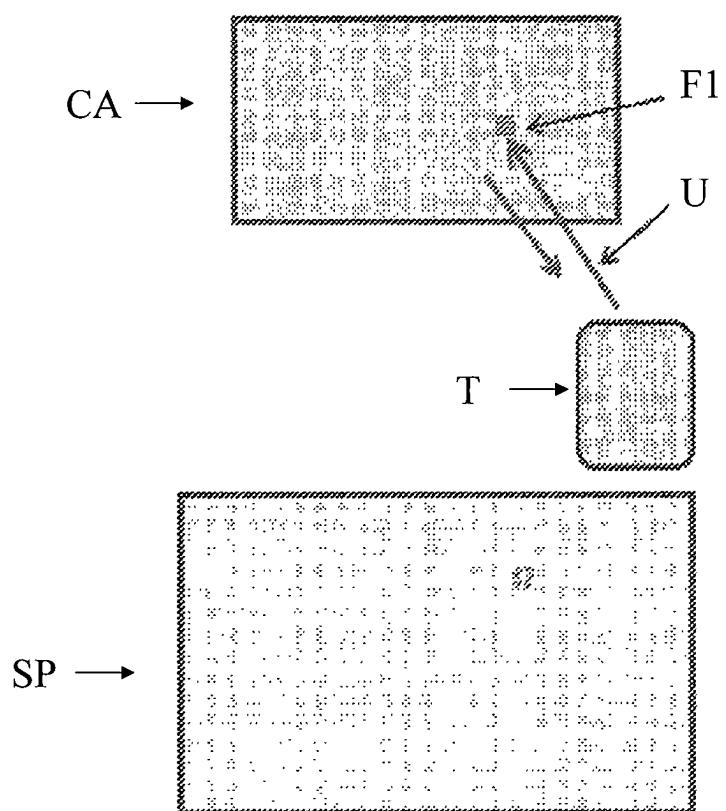

Verarbeitungselementen (PEs) umfasst, die durch einen Satz von leichtgewichtigen Gegendrucknetzwerken verbunden werden. Ein Beispiel für eine CSA-Kachel ist in **Fig. 1** dargestellt. Bestimmte Ausführungsformen von Verarbeitungselementen (z. B. Rechenelementen) sind Datenflussoperatoren, z. B. eine Vielzahl von Datenflussoperatoren, die nur Eingabedaten verarbeiten, wenn sowohl (i) die Eingabedaten beim Datenflussoperator eingegangen sind und (ii) Speicherplatz zum Speichern der Ausgabedaten verfügbar ist, weil z. B. anderenfalls keine Verarbeitung erfolgt. Bestimmte Ausführungsformen (z. B. eines Beschleunigers oder CSA) benutzen keinen getriggerten Befehl.

**[0010]** **Fig. 1** veranschaulicht eine Beschleuniger-Kachel **100** gemäß Ausführungsformen der Offenbarung. Die Beschleuniger-Kachel **100** kann ein Abschnitt einer größeren Kachel sein. Die Beschleuniger-Kachel **100** führt einen oder mehrere Datenflussgraphen aus. Ein Datenflussgraph kann sich im Allgemeinen auf eine explizit parallele Programmbeschreibung beziehen, die bei der Kompilierung von sequentiellen Codes entsteht. Bestimmte Ausführungsformen hierin (z. B. CSAs) ermöglichen, dass Datenflussgraphen direkt auf dem CSA-Array konfiguriert werden, z. B. anstatt in sequentielle Befehlsströme umgewandelt zu werden. Die Ableitung eines Datenflussgraphen aus einem sequentiellen Kompilierungsfluss ermöglicht es Ausführungsformen eines CSA, bekannte Programmiermodelle zu unterstützen und (z. B. ohne Verwendung einer Arbeitstabelle) einen existierenden Hochleistungsrechencode (HPC) direkt auszuführen. Die CSA-Verarbeitungselemente (PE) können energieeffizient sein. In **Fig. 1** kann die Speicherschnittstelle **102** mit einem Speicher (z. B. Speicher **202** in **Fig. 2**) gekoppelt sein, um es der Beschleuniger-Kachel **100** zu ermöglichen, auf Daten des Speichers (z. B. Off-Die) zuzugreifen (z. B. diese zu laden und/oder zu speichern). Die dargestellte Beschleuniger-Kachel **100** ist ein heterogenes Array, das aus verschiedenen Arten von PEs besteht, die über ein Zwischenverbindungsnetz **104** miteinander gekoppelt sind. Die Beschleuniger-Kachel **100** kann eine oder mehr ganzzählige arithmetische PEs, arithmetische Gleitkomma-PEs, Kommunikationsschaltkreise und in-Struktur-Speicher aufweisen. Die Datenflussgraphen (z. B. kompilierte Datenflussgraphen) können die Beschleuniger-Kachel **100** für die Ausführung überlagern. In einer Ausführungsform handelt es sich für einen bestimmten Datenflussgraphen jede PE nur eine oder zwei Operationen des Graphen. Das PE-Array kann heterogen sein, z. B. derart, dass kein PE die volle CSA-Datenflussarchitektur unterstützt und/oder eine oder mehrere PEs programmiert sind (z. B. benutzerdefiniert), um nur einige wenige, aber hocheffiziente Operationen durchzuführen. Bestimmte Ausführungsformen hierin ergeben somit einen Beschleuniger mit einem Array aus Verarbeitungselementen, das im Vergleich zu Roadmap-Architekturen rechenintensiv ist und dennoch eine Erhöhung der Energieeffizienz und Leistung in Bezug auf bestehende HPC-Angebote um etwa eine Größenordnung erreicht.

**[0011]** Die Leistungsanstiege können aus der parallelen Ausführung innerhalb des (z. B. dichten) CSA, wobei jede PE gleichzeitig ausführen kann, z. B. wenn Eingabedaten verfügbar sind. Die Effizienzanstiege können aus der Effizienz jedes PE resultieren, z. B. wenn jede PE-Operation (z. B. Verhalten) einmal pro Konfigurationsschritt (z. B. Mapping) fixiert wird und die Ausführung beim lokalen Eingehen von Daten am PE erfolgt, z. B. ohne Berücksichtigen einer anderen Strukturaktivität. In bestimmten Ausführungsformen ist ein PE ein Datenflussoperator (z. B. jeweils ein einzelner), z. B. ein Datenflussoperator, der nur Eingabedaten verarbeitet, wenn sowohl (i) die Eingabedaten beim Datenflussoperator eingegangen sind als auch (ii) Speicherplatz zum Speichern der Ausgabedaten verfügbar ist, weil z. B. anderenfalls keine Verarbeitung erfolgt. Diese Eigenschaften ermöglichen Ausführungsformen des CSA, paradigmaverschobene Leistungsniveaus und enorme Verbesserungen in der Energieeffizienz über eine breite Klasse bestehender Einzelstrom- und Parallelprogramme bereitzustellen, z. B. aller bei gleichzeitiger Beibehaltung vertrauter HPC-Programmiermodelle. Bestimmte Ausführungsformen eines CSA können auf HPC abzielen, sodass die Gleitkomma-Energieeffizienz extrem wichtig wird. Bestimmte Ausführungsformen des CSA liefern nicht nur überzeugende Leistungsverbesserungen und Energieeinsparungen, sie liefern diese Vorteile auch für bestehende HPC-Programme, die in Mainstream-HPC-Sprachen und für Mainstream-HPC-Frameworks geschrieben sind. Bestimmte Ausführungsformen der CSA-Architektur (z. B. unter Berücksichtigung der Kompilierung) stellen mehrere Erweiterungen bei der direkten Unterstützung der von modernen Kompilierern erzeugten internen Steuerdatenflussrepräsentationen bereit. Bestimmte Ausführungsformen hierin sind direkt an einen CSA-Datenfluss-Kompilierer gerichtet, der z. B. C-, C++- und Fortran-Programmiersprachen akzeptieren kann, um auf eine CSA-Architektur abzuzielen.

**[0012]** Abschnitt 2 unten offenbart Ausführungsformen der CSA-Architektur. Insbesondere sind neuartige Ausführungsformen der Integration von Speicher innerhalb des Datenfluss-Ausführungsmodells offenbart. Abschnitt 3 taucht in die mikroarchitektonischen Details der Ausführungsformen eines CSA ein. In einer Ausführungsform ist das Hauptziel eines CSA die Unterstützung von vom Kompilierer erzeugten Programmen. Abschnitt 4 unten untersucht die Ausführungsformen einer CSA-Kompilierungstoolkette. Die Vorteile der Ausführungsformen eines CSA werden mit anderen Architekturen bei der Ausführung von kompilierten Codes in Abschnitt 5 verglichen. Schließlich wird die Leistung der Ausführungsformen einer CSA-Mikroarchitektur in

Abschnitt 6 erläutert, weitere CSA-Details werden in Abschnitt 7 erläutert und eine Zusammenfassung in Abschnitt 8 bereitgestellt.

## ARCHITEKTUR

**[0013]** Das Ziel bestimmter Ausführungsformen eines CSA ist das schnelle und effiziente Ausführen von Programmen, z. B. Programmen, die von Kompilierern erzeugt werden. Bestimmte Ausführungsformen der CSA-Architektur stellen Programmierabstraktionen bereit, die den Bedarf an Kompilierertechnologien und Programmierparadigmen unterstützen. Ausführungsformen des CSA führen Datenflussgraphen aus, z. B. eine Programmmanifestation, welche die kompilierereigene interne Repräsentation (IR) von kompilierten Programmen eng imitiert. In diesem Modell wird ein Programm als ein Datenflussgraph dargestellt, der aus Knoten (z. B. Scheitelpunkten), die aus einem Satz von architektonisch definierten Datenflussoperatoren (die z. B. sowohl Rechen- als auch Steueroperationen umschließen) und Rändern besteht, welche die Übertragung von Daten zwischen den Datenflussoperatoren repräsentieren. Die Ausführung kann durch Einfügen von Datenfluss-Token (die z. B. Datenwerte sind oder repräsentieren) in den Datenflussgraph fortsetzen. Die Token können zwischen jedem Knoten (z. B. Scheitelpunkt) fließen und umgewandelt werden und z. B. eine vollständige Berechnung bilden. Ein Probendatenflussgraph und seine Ableitung aus einem High-Level-Quellcode ist in **Fig. 3A-3C** gezeigt, und **Fig. 5** zeigt ein Beispiel der Ausführung eines Datenflussgraphen.

**[0014]** Ausführungsformen der CSA sind für die Datenflussgrahpausführung durch Bereitstellen exakt solcher Datenfluss-Graph-Ausführungsunterstützungen konfiguriert, die durch die Kompilierer erfordert werden. In einer Ausführungsform ist der CSA ein Beschleuniger (z. B. ein Beschleuniger aus **Fig. 2**), der nicht versucht, einige der notwendigen aber selten verwendeten Mechanismen zu suchen, die auf Allzweck-Verarbeitungskernen verfügbar sind (z. B. einem Kern aus **Fig. 2**), wie z. B. Systemanrufe. Daher kann der CSA in dieser Ausführungsform viele Codes ausführen, aber nicht alle Codes. Im Gegenzug erzielt der CSA signifikante Leistungs- und Energievorteile. Zum Aktivieren der Beschleunigung von Code, der in herkömmlich verwendeten sequentiellen Sprachen geschrieben ist, führen die Ausführungsformen hierin auch verschiedene neuartige Architekturmerkmale zum Unterstützen des Kompilierers ein. Eine besondere Neuheit ist die CSA-Speicherbehandlung, ein Gegenstand, der zuvor ignoriert oder nur dürftig angegangen wurde. Ausführungsformen des CSA sind auch eindeutig bei der Verwendung von Datenflussoperatoren, z. B. im Gegensatz zu Nachschlagetabellen (LUT), als ihre fundamentale Architekturschnittstelle.

**[0015]** **Fig. 2** veranschaulicht einen Hardware-Prozessor **200**, der mit einem Speicher **202** gemäß Ausführungsformen der Offenbarung gekoppelt (z. B. damit verbunden) ist. In einer Ausführungsform sind der Hardware-Prozessor **200** und der Speicher **202** ein Rechnersystem **201**. In bestimmten Ausführungsformen sind einer oder mehrere der Beschleuniger ein CSA gemäß dieser Offenbarung. In bestimmten Ausführungsformen sind einer oder mehrere der Kerne in einem Prozessor die hierin offenbarten Kerne. Der Hardware-Prozessor **200** (z. B. jeder Kern davon) kann einen Hardware-Decodierer (z. B. Decodiereinheit) und eine Hardware-Ausführungseinheit aufweisen. Der Hardware-Prozessor **200** kann Register aufweisen. Es sei angemerkt, dass die Figuren hierin ggf. nicht alle Datenkommunikationskopplungen (z. B. Verbindungen) darstellen. Ein Durchschnittsfachmann wird zu schätzen wissen, dass dies gewisse Details in den Figuren nicht verschleiert. Es sei darauf hingewiesen, dass ein Doppelpfeil in den Figuren keine Zweiwegekommunikation erfordert, z. B. kann er eine Einwegekommunikation (z. B. zu oder von dieser Komponente oder Vorrichtung) angeben. Jede oder alle Kombinationen von Kommunikationspfaden können in bestimmten Ausführungsformen hierin verwendet werden. Der dargestellte Hardware-Prozessor **200** weist mehrere Kerne (O bis N, wobei N 1 oder mehr sein kann) und Hardware-Beschleuniger (O bis M, wobei M 1 oder mehr sein kann) gemäß Ausführungsformen der Offenbarung auf. Der Hardware-Prozessor **200** (z. B. der/die Beschleuniger und/oder Kern(e) davon) können mit dem Speicher **202** (z. B. Datenspeichervorrichtung) gekoppelt sein. Der Hardware-Decodierer (z. B. des Kerns) kann einen (z. B. einzelnen) Befehl (z. B. Makrobefehl) empfangen und den Befehl decodieren, z. B. in Mikrobefehle und/oder Mikrooperationen. Die Hardware-Ausführungseinheit (z. B. des Kerns) kann den decodierten Befehl (z. B. Makrobefehl) zum Durchführen einer Operation oder Operationen ausführen. Mit erneuter Bezugnahme auf die Ausführungsformen des CSA werden als nächstes die Datenflussoperatoren erläutert.

### Datenflussoperatoren

**[0016]** Die wichtigste Architekturschnittstelle der Ausführungsformen des Beschleunigers (z. B. CSA) ist der Datenflussoperator, z. B. als eine direkte Repräsentation eines Knotens in einem Datenflussgraphen. Aus einer betrieblichen Perspektive verhalten sich die Datenflussoperatoren in einer Streaming- oder datenangesteuerten Weise. Die Datenflussoperatoren können ausführen, sobald ihre eingehenden Operanden verfügbar werden. Die CSA-Datenflussausführung kann (z. B. nur) von einem stark lokalisierten Status abhängig

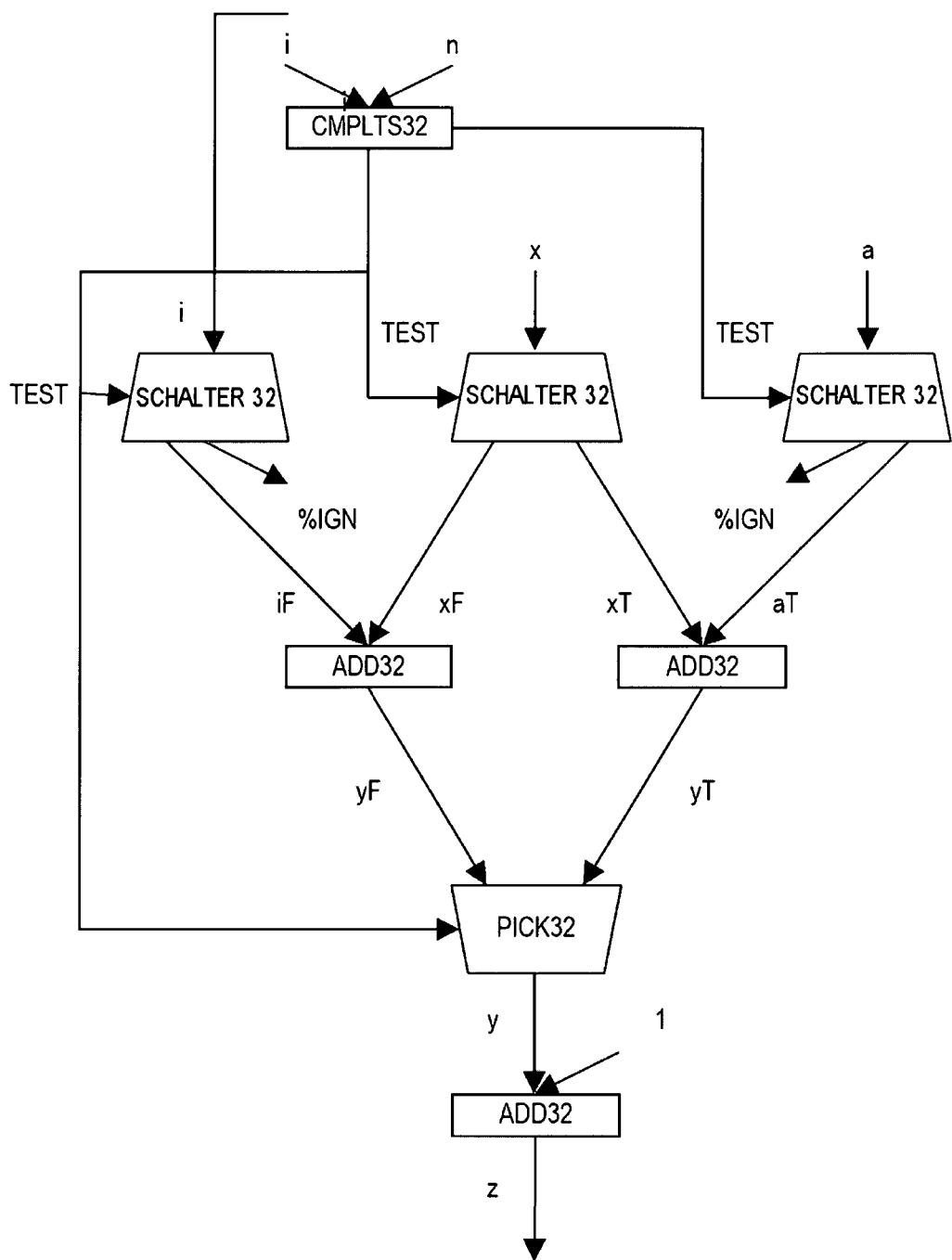

sein, der z. B. in einer hoch skalierbaren Architektur mit einem verteilten, asynchronen Ausführungsmodell resultiert. Die Datenflussoperatoren können arithmetische Datenflussoperatoren aufweisen, z. B. eine oder mehrere von Gleitkomma-Addition und - Multiplikation, Integer-Addition, Subtraktion und Multiplikation, verschiedene Vergleichsformen, logische Operatoren und Verschiebung. Die Ausführungsformen des CSA können auch einen reichen Satz an Steueroperatoren aufweisen, welche die Verwaltung der Datenfluss-Token in dem Programmgraphen stützen. Beispiele davon weisen einen „Pick-“ Operator auf, der z. B. zwei oder mehr logische Eingabekanäle zu einem einzelnen Ausgabekanal multiplext, sowie einen „Schalt-“ Operator, der z. B. als ein Kanal-Demultiplexer arbeitet (der z. B. einen einzelnen Kanal aus zwei oder mehreren logischen Eingabekanälen ausgibt). Diese Operatoren können einem Kompilierer ermöglichen, Steuerparadigmen wie bedingte Ausdrücke zu implementieren. Bestimmte Ausführungsformen eines CSA können einen begrenzten Datenflussoperatorsatz (z. B. für eine relativ kleine Anzahl an Operationen) aufweisen, um dichte und energieeffiziente PE-Mikroarchitekturen zu ergeben. Bestimmte Ausführungsformen können Datenflussoperatoren für komplexe Operationen aufweisen, die in HPC-Code gewöhnlich sind. Die CSA-Datenflussoperator-Architektur ist für einsatzspezifische Erweiterungen stark anpassungsfähig. Zum Beispiel können komplexere mathematische Datenflussoperatoren, z. B. trigonometrische Funktionen, in bestimmten Ausführungsformen zum Beschleunigen bestimmter mathematikintensiver HPC-Arbeitslasten einschließen. Auf ähnliche Weise kann eine neuralnetzwerkabgestimmte Erweiterung Datenflussoperatoren für eine vektorisierte niederpräzise Arithmetik einschließen.

**[0017]** Fig. 3A veranschaulicht eine Programmquelle gemäß Ausführungsformen der Offenbarung. Der Programmquellcode weist eine Multiplikationsfunktion (func) auf. Fig. 3B veranschaulicht ein Datenflussschaubild 300 für die Programmquelle aus Fig. 3A gemäß Ausführungsformen der Offenbarung. Der Datenflussgraph 300 weist einen Pick-Knoten 304, Switch-Knoten 306 und Multiplikationsknoten 308 auf. Ein Puffer kann wahlweise entlang eines oder mehrerer Kommunikationspfade aufgenommen sein. Der dargestellte Datenflussgraph 300 kann eine Operation der Auswahl der Eingabe X mit Pick-Knoten 304 durchführen, X mit Y multiplizieren (z. B. Multiplikationsknoten 308) und dann das Ergebnis von der übrigen Ausgabe des Switch-Knotens 306 ausgeben. Fig. 3C veranschaulicht einen Beschleuniger (z. B. CSA) mit mehreren Verarbeitungselementen 301, der zum Ausführen des Datenflussgraphen aus Fig. 3B gemäß Ausführungsformen der Offenbarung 301 konfiguriert ist; Insbesondere ist der Datenflussgraph 300 in das Array der Verarbeitungselemente 301 überlagert (z. B. und die (z. B. Zwischenverbindungs-)Netzwerk(e) dazwischen), z. B. sodass jeder Knoten des Datenflussgraphen 300 als ein Datenflussoperator in dem Array aus Verarbeitungselementen 301 repräsentiert ist. In einer Ausführungsform dienen eines oder mehrere der Verarbeitungselemente in dem Array von Verarbeitungselementen 301 zum Zugriff auf den Speicher durch die Speicherschnittstelle 302). In einer Ausführungsform entspricht der Pick-Knoten 304 des Datenflussgraphen 300 somit dem Pick-Operator 304A (wird z. B. davon repräsentiert), der Switch-Knoten 306 des Datenflussgraphen 300 entspricht also dem Schalt-Operator 306A (wird z. B. davon repräsentiert) und der Multiplizierer-Knoten 308 des Datenflussgraphen 300 entspricht also dem Multiplizierer-Operator 308A (wird z. B. dadurch repräsentiert). Ein weiteres Verarbeitungselement und/oder ein Flusssteuerpfad-Netzwerk können die Steuersignale (z. B. Steuer-Token) an den Pick-Operator 304A und den Schalt-Operator 306A bereitstellen, um die Operation in Fig. 3A durchzuführen. In einer Ausführungsform ist das Array von Verarbeitungselementen 301 zum Ausführen des Datenflussgraphen 300 aus Fig. 3B vor Start der Ausführung konfiguriert. In einer Ausführungsform führt der Kompilierer die Umwandlung von Fig. 3A bis Fig. 3B durch. In einer Ausführungsformbettet die Eingabe der Datenflussgraph-Knoten in das Array aus Verarbeitungselementen den Datenflussgraph logisch in das Array aus Verarbeitungselementen ein, z. B. wie weiter unten besprochen, sodass der Eingabe-/Ausgabepfad zum Erzeugen des gewünschten Ergebnisses konfiguriert ist.

#### Latenzinsensitive Kanäle

**[0018]** Kommunikationsbögen sind die zweite Hauptkomponente des Datenflussgraphen. Bestimmte Ausführungsformen eines CSA beschreiben diese Bögen als latenzinsensitive Kanäle, z. B. in-Reihenfolge, Gegendruck- (die z. B. keine Ausgabe erzeugen oder senden, bis ein Platz zum Speichern der Ausgabe vorhanden ist), Point-to-Point-Kommunikationskanäle. Wie bei den Datenflussoperatoren sind die latenzinsensitiven Kanäle fundamental asynchron und geben die Freiheit, viele Typen von Netzwerken zum Implementieren der Kanäle eines bestimmten Graphen zusammenzustellen. Latenzinsensitive Kanäle können willkürlich lange Latenzen aufweisen und die CSA-Architektur weiterhin gewissenhaft implementieren. In bestimmten Ausführungsformen ist es jedoch ein großer Anreiz bezüglich der Leistung und Energie, die Latenzen so klein wie möglich zu machen. Abschnitt 3.2 hierin offenbart eine Netzwerk-Mikroarchitektur, in der die Datenflussgraph-Kanäle zeitverschachtelt mit nicht mehr als einem Latenzyklus implementiert sind. Ausführungsformen von latenzinsensitiven Kanälen stellen eine kritische Abstraktionsschicht bereit, die mit der CSA-Architektur zum Bereitstellen einer Anzahl von Laufzeitdiensten an den Anwendungsprogrammierer genutzt werden können.

Ein CSA kann beispielsweise die Latenzinsensitiven Kanäle bei der Implementierung der CSA-Konfiguration (dem Laden eines Programms auf ein CSA-Array) nutzen.

**[0019]** **Fig. 4** veranschaulicht eine beispielhafte Ausführung des Datenflussgraphen **400** gemäß Ausführungsformen der Offenbarung. Bei Schritt 1 können Eingabewerte (z. B. 1 für X in **Fig. 3B** und **Fig. 2** für Y in **Fig. 3B**) in den Datenflussgraph **400** geladen werden, um eine  $1 \times 2$ -Multiplikationsoperation durchzuführen. Einer oder mehrere Dateneingabewerte können in der Operation (z. B. 1 für X und 2 für Y in Bezug auf **Fig. 3B**) statisch (z. B. konstant) sein oder während der Operation aktualisiert werden. Bei Schritt 2 geben ein Verarbeitungselement (z. B. auf einem Flusssteuerpfad-Netzwerk) oder andere Schaltungsausgaben eine Null in die Steuereingabe (z. B. Mux-Steuersignal) von Pick-Knoten **404** (z. B. um eine eins von Port „0“ zu seiner Ausgabe zu beschaffen) und gibt eine Null zur Steuereingabe (z. B. Mux-Steuersignal) von Switch-Knoten **406** aus (z. B. zum Bereitstellen seiner Eingabe aus Port „0“ zu einem Ziel (z. B. einem nachgeschalteten Verarbeitungselement). Bei Schritt 3 wird der Datenwert 1 vom Pick-Knoten **404** (und z. B. sein Steuersignal „0“ am Pick-Knoten **404** verbraucht) an den Multiplizierer-Knoten **408** ausgegeben, um mit dem Datenwert von 2 bei Schritt 4 multipliziert zu werden. Bei Schritt 4 erreicht die Ausgabe des Multiplizierer-Knotens **408** den Switch-Knoten **406**, was z. B. den Switch-Knoten **406** veranlasst, ein Steuersignal „0“ zu verbrauchen, um den Wert von 2 von Port „2“ von Switch-Knoten **406** bei Schritt 5 auszugeben. Die Operation ist dann abgeschlossen. Ein CSA kann daher dementsprechend programmiert werden, damit ein entsprechender Datenflussoperator für jeden Knoten die Operation in **Fig. 4** durchführt. Obwohl die Ausführung in diesem Beispiel serialisiert ist, können im Prinzip alle Datenfluss-Operationen parallel ausgeführt werden. Die Schritte werden in **Fig. 4** verwendet, um die Datenflussausführung von jeder physischen mikroarchitektonischen Manifestation zu differenzieren. In einer Ausführungsform hat ein nachgeschaltetes Verarbeitungselement ein Signal an den Schalter **406** zu senden (oder kein Bereit-Signal zu senden) (z. B. auf einem Flusssteuerpfad-Netzwerk), um die Ausgabe von Schalter **406** aufzuhalten, z. B. bis das nachgeschaltete Verarbeitungselement für die Ausgabe bereit ist (z. B. Speicherplatz aufweist).

### Speicher

**[0020]** Datenfluss-Architekturen konzentrieren sich im Allgemeinen auf die Kommunikation und Datenmanipulation und beachten dem Status weniger Beachtung. Das Aktivieren von echter Software, insbesondere Programmen, die in sequentiellen veralteten Sprachen geschrieben sind, erfordert eine bedeutende Beachtung der Schnittstelle mit dem Speicher. Bestimmte Ausführungsformen eines CSA verwenden Architektur-speicheroperationen als ihre primäre Schnittstelle zur (z. B. großen) statusbehafteten Speicherung. Aus der Perspektive des Datenflussgraphen ähneln die Speicheroperationen anderen Datenfluss-Operationen, mit der Ausnahme, dass sie den Nebeneffekt der Aktualisierung eines gemeinsam genutzten Speichers aufweisen. Insbesondere haben Speicheroperationen von bestimmten Ausführungsformen hierin die gleiche Semantik wie jeder andere Datenflussoperator, z. B. werden „ausgeführt“, wenn ihre Operanden, z. B. eine Adresse, verfügbar ist und nach einiger Latenz eine Antwort erzeugt wird. Bestimmte Ausführungsformen hierin entkoppeln die Operandeneingabe explizit und resultieren in einer Ausgabe, sodass die Speicheroperatoren natürlich zeitverschachtelt sind und das Potenzial aufweisen, viele simultan ausstehende Anforderungen zu erzeugen, welche diese z. B. ausgezeichnet für die Latenz- und Bandbreitencharakteristika eines Speicheruntersystems geeignet machen. Ausführungsformen eines CSA stellen grundlegende Speicheroperationen wie Last bereit, die einen Adressenkanal nimmt und einen Antwortkanal mit den Werten, die den Adressen entsprechen, und einen Speicher füllt. Ausführungsformen eines CSA können auch erweiterte Operationen wie speicherinterne Atomik- und Konsistenz-Operatoren bereitstellen. Diese Operationen können eine ähnliche Semantik wie ihre von-Neumann-Gegenstücke aufweisen. Ausführungsformen eines CSA können vorhandene Programme beschleunigen, die unter Verwendung sequentieller Sprachen wie C- und Fortran beschrieben werden. Eine Folge der Unterstützung dieser Sprachmodelle ist das Adressieren der Programmspeicherreihenfolge, z. B. der seriellen Anordnung von Speicheroperationen, die typischerweise durch diese Sprachen vorgeschrieben sind.

**[0021]** **Fig. 5** veranschaulicht eine Programmquelle (z. B. C-Code) 500 gemäß Ausführungsformen der Offenbarung. Gemäß der Speichersemantik der C-Programmiersprache ist die Speicherkopie (memcpy) zu serialisieren. Memcpy kann jedoch mit einer Ausführungsform des CSA parallelisiert werden, wenn die Arrays A und B bekanntmaßen unverbunden sind. **Fig. 5** veranschaulicht ferner das Problem der Programmreihenfolge. Allgemein können Komplizierter nicht nachweisen, dass Array A anders als Array B ist, z. B. entweder für den gleichen Wert des Index oder einen anderen Wert des Index über den Schleifenkörpern. Dies ist als Zeiger- oder Speicher-Aliasing bekannt. Da Komplizierter einen statisch korrekten Code erzeugen müssen, werden sie gewöhnlich zur Serialisierung der Speicherzugriffe gezwungen. Typischerweise verwenden Komplizierter, die auf sequentielle von-Neumann-Architekturen abzielen, die Befehlsreihenfolge als natürliches Mittel zum Durchsetzen der Programmreihenfolge. Ausführungsformen des CSA besitzen jedoch keine Vorstellung

von Befehlen oder befehlsbasierter Programmreihenfolge, wie durch einen Programmzähler definiert. In bestimmten Ausführungsformen sind eingehende Abhängigkeits-Token, die z. B. keine architektonisch sichtbare Information enthalten, wie alle anderen Datenfluss-Token und die Speicheroperationen können nicht ausgeführt werden, bis sie einen Abhängigkeits-Token empfangen haben. In bestimmten Ausführungsformen erzeugen die Speicheroperationen einen ausgehenden Abhängigkeits-Token, sobald ihre Operation für alle logisch nachfolgenden abhängigen Speicheroperationen sichtbar ist. In bestimmten Ausführungsformen gleichen die Abhängigkeits-Token anderen Datenfluss-Token in einem Datenflussgraph. Da Speicheroperationen z. B. in bedingten Kontexten auftreten, können die Abhängigkeits-Token auch unter Verwendung von Steueroperatoren manipuliert werden, wie in Abschnitt 2.1 beschrieben, z. B. wie alle anderen Token. Abhängigkeits-Token können den Effekt der Serialisierung von Speicherzugriffen haben, z. B. dem Kompliler eine Einrichtung zum architektonischen Definieren der Reihenfolge von Speicherzugriffen bereitstellen.

### Laufzeitdienste

**[0022]** Ein Hauptpunkt für die Berücksichtigung der Architektur von Ausführungsformen des CSA beinhaltet die tatsächliche Ausführung von Programmen auf Benutzerebene, es kann aber auch wünschenswert sein, verschiedene Mechanismen zu unterstützen, die diese Ausführung stärken. Zu den wichtigsten zählen Konfiguration (bei der ein Datenflussgraph in den CSA geladen wird), Extraktion (bei welcher der Status eines ausführenden Graphen in den Speicher verschoben wird) und Ausnahmen (in denen mathematische, weiche und andere Arten von Fehlern in der Struktur erkannt und behandelt werden, möglicherweise durch eine externe Entität). Abschnitt 3.6 unten erläutert die Eigenschaften einer latenzinsensitiven Datenflussarchitektur einer Ausführungsform eines CSA, um effiziente, stark zeitverschachtelte Implementierungen dieser Funktionen zu ergeben. Vom Konzept her kann die Konfiguration den Status eines Datenflussgraphen in die Zwischenverbindungs- und Verarbeitungselemente (z. B. Struktur) laden, z. B. im Allgemeinen von dem Speicher. Während dieses Schrittes können alle Strukturen im CSA mit einem neuen Datenflussgraphen geladen werden und alle Datenfluss-Token in diesem Graphen, z. B. als Folge einer Kontextumschaltung, leben. Die latenzinsensitive Semantik eines CSA kann eine verteilte, asynchrone Initialisierung der Struktur ermöglichen, z. B. kann sie die Ausführung unmittelbar beginnen, sobald die PEs konfiguriert sind. Unkonfigurierte PEs können ihre Kanäle gegendrücken, bis sie konfiguriert werden, z. B. Kommunikationen zwischen konfigurierten und unkonfigurierten Elementen verhindern. Die CSA-Konfiguration kann in einen privilegierten Status und Status auf Benutzerebene partitioniert werden. Eine solche Zwei-Level-Partitionierung kann der primären Konfiguration der Struktur ermöglichen, ohne Aufrufen des Betriebssystems zu erfolgen. Während einer Extraktionsausführungsform wird eine logische Sicht des Datenflussgraphen erfasst und in den Speicher festgeschrieben, z. B. durch Aufnehmen aller Live-Steuer- und Datenfluss-Token und Zustand in dem Graphen.

**[0023]** Die Extraktion kann auch eine Rolle bei der Bereitstellung von Zuverlässigkeitsgarantien durch die Schaffung von Strukturprüfunkten spielen. Ausnahmen in einem CSA können allgemein durch die gleichen Ereignisse verursacht werden, die Ausnahmen in Prozessoren bewirken, wie z. B. illegale Operatorargumente oder RAS-Ereignisse (RAS - Reliability (Zuverlässigkeit), Availability (Verfügbarkeit) und Serviceability (Betriebsfähigkeit)). In bestimmten Ausführungsformen werden Ausnahmen auf dem Level der Datenflussoperatoren erfasst, wie z. B. durch Prüfen von Argumentwerten oder durch modulare arithmetische Schemata. Nach dem Detektieren einer Ausnahme kann ein Datenflussoperator (z. B. eine Schaltung) halten und eine Ausnahmenachricht emittieren, die z. B. sowohl einen Operationsidentifikator als auch einige Details über die Natur des Problems, das aufgetreten ist, enthält. In einer Ausführungsform bleibt der Datenflussoperator angehalten, bis er rekonfiguriert wurde. Die Ausnahmenachricht kann dann einem zugeordneten Prozessor (z. B. Kern) zur Wartung kommuniziert werden, die z. B. das Extrahieren des Graphen zur Softwareanalyse einschließen kann.

### Kachel-Level-Architektur

**[0024]** Ausführungsformen der CSA-Computerarchitekturen (z. B. auf HPC und Datencenter abzielende Verwendungen) sind nebeneinander angeordnet. **Fig. 6** und **Fig. 8** zeigen den Kachel-Level-Einsatz eines CSA. **Fig. 8** zeigt eine Voll-Kachel-Implementierung eines CSA, die z. B. ein Beschleuniger eines Prozessors mit einem Kern sein kann. Ein Hauptvorteil dieser Architektur kann reduziertes Ausgestaltungsrisiko sein, sodass der CSA und der Kern z. B. bei der Herstellung vollständig entkoppelt sind. Zusätzlich zu der Ermöglichung einer besseren Komponentenwiederverwendung kann dies der Ausgestaltung der Komponenten wie dem CSA-Cache ermöglichen, nur den CSA zu berücksichtigen, statt z. B. die strikteren Latenzanforderungen des Kerns zu integrieren. Schließlich können separate Kacheln die Integration des CSA mit kleinen oder großen Kernen ermöglichen. Eine Ausführungsform des CSA erfasst die meisten vektorparallelen Arbeitslasten, sodass die meisten vektorartigen Arbeitslasten direkt auf dem CSA laufen, aber in bestimmten Ausführungsformen können die vektorartigen Befehle in dem Kern eingeschlossen sein, z. B. zum Unterstützen von veralteten Binariäten.

## MIKROARCHITEKTUR

**[0025]** In einer Ausführungsform ist das Ziel der CSA-Mikroarchitektur das Bereitstellen einer hochqualitativen Implementierung jedes Datenflussoperators, der durch die CSA-Architektur spezifiziert wird. Ausführungsformen der CSA-Mikroarchitektur sehen vor, dass jedes Verarbeitungselement der Mikroarchitektur ungefähr einem Knoten (z. B. einer Entität) in dem Architekturdatenflussgraphen entspricht. In bestimmten Ausführungsformen führt dies zu Mikroarchitekturelementen, die nicht nur kompakt sind, was zu einem dichten Berechnungsarray führt, sondern auch energieeffizient, zum Beispiel, wenn Verarbeitungselemente (PEs) sowohl einfach als auch stark ungemultiplex sind, z. B. Ausführen eines einzelnen Datenflussoperators für eine Konfiguration (z. B. Programmierung) des CSA ausführen. Um den Energie- und Implementierungsbereich weiter zu reduzieren, kann ein CSA einen konfigurierbaren, heterogenen Strukturstil aufweisen, in dem jedes PE davon nur einen Untersatz von Datenflussoperatoren implementiert. Peripherie und unterstützende Teilsysteme, wie z. B. der CSA-Cache, können bereitgestellt werden, um die verteilte Parallelität zu unterstützen, die in der Haupt-CSA-Verarbeitungsstruktur selbst vorherrscht. Die Implementierung von CSA-Mikroarchitekturen kann Datenfluss- und latenzinsensitive Kommunikationsabstraktionen verwenden, die in der Architektur vorhanden sind. In bestimmten Ausführungsformen gibt es (z. B. im Wesentlichen) eine Eins-zu-Eins-Entsprechung zwischen Knoten in dem komplizierter erzeugten Graphen und den Datenflussoperatoren (z. B. Datenflussoperator-Rechenelementen) in einem CSA.

**[0026]** Es folgt eine Erläuterung eines beispielhaften CSA, gefolgt von einer detaillierteren Erläuterung der Mikroarchitektur. Bestimmte Ausführungsformen hierin stellen einen CSA bereit, der eine einfache Kompilierung ermöglicht, z. B. im Gegensatz zu bestehenden FPGA-Kompilierern, die einen kleinen Untersatz einer Programmiersprache (z. B. C oder C++) handhaben und viele Stunden benötigen, um selbst kleine Programme zu kompilieren.

**[0027]** Bestimmte Ausführungsformen einer CSA-Architektur erlauben heterogene grobkörnige Operationen, wie Gleitkomma mit doppelter Genauigkeit. Programme können in weniger grobkörnigen Operationen ausgedrückt werden, z. B. so, dass der offizielle Kompilierer schneller läuft als herkömmliche räumliche Kompilierer. Bestimmte Ausführungsformen beinhalten eine Struktur mit neuen Verarbeitungselementen, um sequentielle Konzepte wie programmgeordnete Speicherzugriffe zu unterstützen. Bestimmte Ausführungsformen implementieren Hardware, um grobkörnige datenflussartige Kommunikationskanäle zu unterstützen. Dieses Kommunikationsmodell ist abstrakt und kommt der vom Kompilierer verwendeten Steuerdatenflussrepräsentation sehr nahe. Bestimmte Ausführungsformen hierin beinhalten eine Netzwerkimplementierung, die Einzelzyklus-Latenzzeitkommunikationen unterstützt, z. B. Benutzen (z. B. kleiner) PEs, die einzelne Steuerdatenflussoperationen unterstützen. In bestimmten Ausführungsformen verbessert dies nicht nur die Energieeffizienz und Leistung, sondern vereinfacht auch die Kompilierung, da der Kompilierer eine Eins-zu-eins-Abbildung zwischen High-Level-Datenflusskonstrukten und der Struktur vornimmt. Bestimmte Ausführungsformen hierin vereinfachen somit die Aufgabe des Kompilierens existierender (z. B. C-, C++- oder Fortran-) Programme zu einem CSA (z. B. Struktur).

**[0028]** Die Energieeffizienz kann ein Hauptanliegen moderner Rechensysteme sein. Bestimmte Ausführungsformen hierin stellen ein neues Schema von energieeffizienten räumlichen Architekturen bereit. In bestimmten Ausführungsformen bilden diese Architekturen eine Struktur mit einer einzigartigen Zusammensetzung aus einer heterogenen Mischung aus kleinen, energieeffizienten, datenflussorientierten Verarbeitungselementen (PEs) mit einem leichtgewichtigen leitungsvermittelten Kommunikationsnetzwerk (z. B. Interconnect), z. B. mit einer gehärteten Unterstützung der Flussteuerung. Aufgrund der Energivorteile davon kann die Kombination dieser zwei Komponenten einen räumlichen Beschleuniger (z. B. als Teil eines Rechners) bilden, der zum Ausführen von komplizierteren parallelen Programmen in einer extrem energieeffizienten Weise geeignet ist. Da diese Struktur heterogen ist, können bestimmte Ausführungsformen an unterschiedliche Anwendungsdomänen durch Einführen neuer domänspezifischer PEs angepasst werden. Eine Struktur für die Hochleistungsberechnung könnte z. B. einige Anpassungen für doppelte Genauigkeit, fusioniertes Multiply-Add, enthalten, während eine Struktur, die auf tiefe neuronale Netzwerke abzielt, Gleitkomma-Operationen mit niedriger Genauigkeit beinhalten könnte.

**[0029]** Eine Ausführungsform eines räumlichen Architekturschemas, wie es z. B. in **Fig. 6** veranschaulicht ist, ist die Zusammensetzung von leichtgewichtigen Verarbeitungselementen (PE), die durch ein Inter-PE-Netzwerk verbunden sind. Im Allgemeinen können PEs Datenflussoperatoren umfassen, wo z. B., sobald alle Eingabeoperanden bei dem Datenflussoperator eingegangen sind, einige Operationen (z. B. Mikrobefehl oder Mikrobefehlssatz) ausgeführt werden, und die Ergebnisse an nachgeschaltete Operatoren weitergeleitet werden.

Steuerung, Planung und Datenspeicherung können daher unter den PEs verteilt sein, z. B. durch Entfernen des Aufwands der zentralisierten Strukturen, die klassische Prozessoren dominieren.

**[0030]** Programme können in Datenflussgraphen umgewandelt werden, die auf die Architektur abgebildet werden, indem PEs und Netzwerk konfiguriert werden, um den Steuerdatenflussgraphen des Programms auszudrücken. Kommunikationskanäle können flussgesteuert und vollständig gegengedrückt sein, z. B. sodass die PEs anhalten, wenn entweder die Quellkommunikationskanäle keine Daten aufweisen oder die Zielkommunikationskanäle voll sind. In einer Ausführungsform fließen Daten zur Laufzeit durch die PEs und Kanäle, die zum Implementieren der Operation konfiguriert wurden (z. B. ein beschleunigter Algorithmus). Zum Beispiel können Daten aus dem Speicher durch die Struktur eingestreamt werden und dann zurück in den Speicher gehen.

**[0031]** Ausführungsformen einer solchen Architektur können eine bemerkenswerte Leistungseffizienz gegenüber herkömmlichen Mehrkernprozessoren erreichen: die Rechenleistung (z. B. in Form von PEs) kann einfacher, energieeffizienter und umfangreicher sein als in größeren Kernen, und die Kommunikation kann direkt und meist kurzstreckig sein, z. B. im Gegensatz zum Auftreten über ein breites Vollchip-Netzwerk wie in typischen Mehrkernprozessoren. Da Ausführungsformen der Architektur des Weiteren extrem parallel sind, ist eine Anzahl von leistungsfähigen Optimierungen auf Schaltungs- und Geräteebene möglich, ohne den Durchsatz ernsthaft zu beeinträchtigen, z. B. Geräte mit niedrigem Verlust und niedriger Betriebsspannung. Diese Lower-Level-Optimierungen können gegenüber herkömmlichen Kernen noch größere Leistungsvorteile bringen. Die Kombination aus Effizienz auf Architektur-, Schaltungs- und Geräte-Level dieser Ausführungsformen ist zwingend. Ausführungsformen dieser Architektur können größere aktive Bereiche ermöglichen, während gleichzeitig die Transistordichte weiter steigt.

**[0032]** Ausführungsformen hierin bieten eine einzigartige Kombination aus Datenflussunterstützung und Leistungsvermittlung, um die Struktur kleiner, energieeffizienter zu machen und eine höhere Aggregatleistung gegenüber vorherigen Architekturen bereitzustellen. FPGAs sind im Allgemeinen auf eine feinkörnige Bitmanipulation abgestimmt, während Ausführungsformen hierin auf Gleitkomma-Operationen mit doppelter Genauigkeit in HPC-Anwendungen abgestimmt sind. Bestimmte Ausführungsformen hierin können einen FPGA zusätzlich zu einem CSA gemäß dieser Offenbarung aufweisen.

**[0033]** Bestimmte Ausführungsformen hierin kombinieren ein leichtgewichtiges Netzwerk mit energieeffizienten Datenflussverarbeitungselementen zum Bilden einer energieeffizienten HPC-Struktur mit hohem Durchsatz und geringer Latenz. Dieses Netzwerk mit geringer Latenz kann den Bau von Verarbeitungselementen mit weniger Funktionen ermöglichen, zum Beispiel nur einen oder zwei Befehle und ggf. ein sichtbares Architekturregister, weil es effizient ist, mehrere PE gemeinsam zu gruppieren, um ein vollständiges Programm zu bilden.

**[0034]** Bezuglich eines Prozessorkerns können CSA-Ausführungsformen hierin mehr Rechendichte und Energieeffizienz bereitstellen. Wenn zum Beispiel PEs sehr klein sind (z. B. verglichen mit einem Kern), kann der CSA viel mehr Operationen durchführen und hat viel mehr Rechenparallelität als ein Kern, z. B. womöglich etwa das 16-fache der Anzahl der FMAs einer Vektorverarbeitungseinheit (VPU - Vector Processing Unit). Zum Nutzen aller dieser Rechenelemente ist die Energie pro Operation in bestimmten Ausführungsformen sehr gering.

**[0035]** Die Energievorteile unserer Ausführungsformen dieser Datenflussarchitektur sind zahlreich. Parallelität ist in Datenflussgraphen explizit und Ausführungsformen der CSA-Architektur verbrauchen keine oder nur minimale Energie zur Extraktion davon, z. B. im Gegensatz zu Außer-Reihenfolge-Prozessoren, die jedes Mal, wenn ein Befehl ausgeführt wird, die Parallelität neu erkennen müssen. Da jedes PE in einer Ausführungsform für eine einzelne Operation verantwortlich ist, können die Registerdateien und Port-Zählungen klein sein, z. B. oft nur eins, und verbrauchen daher weniger Energie als ihre Gegenstücke im Kern. Bestimmte CSAs weisen viele PEs auf, von denen jedes Live-Programmwerte enthält, die den Gesamteffekt einer riesigen Registerdatei in einer traditionellen Architektur ergeben, was die Speicherzugriffe drastisch reduziert. In Ausführungsformen, bei denen der Speicher vom Mehrfachporttyp und verteilt ist, kann ein CSA viel mehr anstehende Speicheranforderungen erfüllen und mehr Bandbreite als ein Kern nutzen. Diese Vorteile können kombiniert werden, um einen Energiepegel pro Watt zu ergeben, der nur einen kleinen Prozentsatz der Kosten der bloßen arithmetischen Schaltung darstellt. Zum Beispiel kann im Falle einer Integer-Multiplikation ein CSA nicht mehr als 25% mehr Energie als die zugrundeliegende Multiplikationsschaltung verbrauchen. In Bezug auf eine Ausführungsform eines Kerns verbraucht eine Integeroperation in dieser CSA-Struktur weniger als 1/30 der Energie pro Integeroperation.

**[0036]** Aus einer Programmierperspektive ergibt die anwendungsspezifische Formbarkeit von Ausführungsformen der CSA-Architektur wichtige Vorteile gegenüber einer Vektorverarbeitungseinheit (VPU). Bei traditionellen, unflexiblen Architekturen müssen die Anzahl funktionaler Einheiten, wie Gleitdivision, oder die verschiedenen transzendentalen mathematischen Funktionen zum Ausgestaltungszeitpunkt basierend auf einem erwarteten Anwendungsfall gewählt werden. In Ausführungsformen der CSA-Architektur können solche Funktionen basierend auf den Anforderungen jeder Anwendung (z. B. durch einen Benutzer und nicht einen Hersteller) in der Struktur konfiguriert werden. Der Anwendungsdurchsatz kann dadurch weiter gesteigert werden. Gleichzeitig verbessert sich die Rechendichte von Ausführungsformen des CSA, indem die Verhärtung solcher Funktionen vermieden wird und stattdessen mehr Instanzen primitiver Funktionen wie Gleitmultiplikation vorgesehen werden. Diese Vorteile können bei HPC-Arbeitslasten von Bedeutung sein, von denen einige 75% der Gleitkomma-Ausführung in transzendentalen Funktionen verbrauchen.

**[0037]** Bestimmte Ausführungsformen des CSA stellen einen bedeutenden Fortschritt als eine datenflussorientierte räumliche Architektur dar, weil z. B. die PEs dieser Offenbarung kleiner, aber auch energieeffizienter sein können. Diese Verbesserungen können sich direkt aus der Kombination von datenflussorientierten PEs mit einer leichtgewichtigen, leitungsvermittelten Zwischenverbindung ergeben, die zum Beispiel im Gegensatz zu einem paketvermittelten Netzwerk eine Einzelzykluslatenz aufweist (z. B. mit einer 300% höheren Latenz an einem Minimum). Bestimmte Ausführungsformen der PEs unterstützen die 32-Bit- oder 64-Bit-Operation. Bestimmte Ausführungsformen hierin erlauben die Einführung neuer anwendungsspezifischer PEs, z. B. für Maschinenlernen oder Sicherheit, und sind keine rein homogene Kombination. Bestimmte Ausführungsformen hierin kombinieren leichtgewichtige datenflussorientierte Verarbeitungselemente mit einem leichtgewichtigen Niederlatenznetzwerk zum Bilden einer energieeffizienten Rechenstruktur.

**[0038]** Damit bestimmte räumliche Architekturen erfolgreich sind, müssen Programmierer sie mit relativ geringem Aufwand konfigurieren, z. B. sie gegenüber sequentiellen Kernen eine signifikante Energie- und Leistungsüberlegenheit erhalten. Bestimmte Ausführungsformen hierin stellen einen CSA (z. B. räumliche Struktur) bereit, der leicht programmiert werden kann (z. B. durch einen Kompilierer), energieeffizient und hochparallel ist. Bestimmte Ausführungsformen hierin stellen ein Netzwerk (z. B. Zwischenverbindungsnetz) bereit, dass diese drei Ziele erreicht. Aus einer Programmierbarkeitsperspektive stellen bestimmte Ausführungsformen des Netzwerks flussgesteuerte Kanäle bereit, die z. B. dem Steuerdatenflussgraphen (CDFG - Control-Dataflow Graph)-Modell der Ausführung entsprechen, das in Kompilierern verwendet wird. Bestimmte Netzwerkausführungsformen benutzen zweckgebundene leitungsvermittelte Verknüpfungen, so dass die Programmleistung sowohl von einem Menschen als auch einem Kompilierer leichter zu verstehen ist, weil die Leistung vorhersehbar ist. Bestimmte Netzwerkausführungsformen bieten sowohl hohe Bandbreite als auch niedrige Latenz. Bestimmte Netzwerkausführungsformen (z. B. statische leitungsvermittelte) stellen eine Latenz von 0 bis 1 Zyklus bereit (z. B. je nach der Übertragungsstrecke). Bestimmte Ausführungsformen stellen eine hohe Bandbreite durch paralleles Verlegen verschiedener Netzwerke bereit, z. B. in Low-Level-Metallen. Bestimmte Netzwerkausführungsformen kommunizieren in Low-Level-Metallen und über kurze Strecken und sind somit sehr energieeffizient.

**[0039]** Bestimmte Ausführungsformen von Netzwerken weisen eine Architekturunterstützung für die Durchflusssteuerung auf. Zum Beispiel können in räumlichen Beschleunigern, die aus kleinen Verarbeitungselementen (PEs) bestehen, die Kommunikationslatenz und die Bandbreite für die Gesamtprogrammleistung bedeutend sein. Bestimmte Ausführungsformen hierin stellen ein leichtgewichtiges leitungsvermitteltes Netzwerk bereit, das die Kommunikation zwischen PEs in räumlichen Verarbeitungsarrays, wie dem in **Fig. 6** gezeigten räumlichen Array, und den mikroarchitektonischen Steuermerkmalen, die notwendig sind, um dieses Netzwerk zu unterstützen, erleichtert. Bestimmte Ausführungsformen eines Netzwerks ermöglichen die Konstruktion von flussgesteuerten Punkt-zu-Punkt-Kommunikationskanälen, welche die Kommunikation der datenflussorientierten Verarbeitungselemente (PEs) unterstützen. Zusätzlich zu den Punkt-zu-Punkt-Kommunikationen können bestimmte Netzwerke hierin auch Multicast-Kommunikationen unterstützen. Die Kommunikationskanäle können durch statisches Konfigurieren des Netzwerks zum Bilden virtueller Schaltungen zwischen den PEs gebildet werden. Schaltungsumschalttechniken hierin können die Kommunikationslatenz verringern und die Netzwerkpufferung entsprechend minimieren, was zum Beispiel sowohl zu einer hohen Leistungsfähigkeit als auch zu einer hohen Energieeffizienz führt. In bestimmten Ausführungsformen eines Netzwerks kann die Inter-PE-Latenz so niedrig wie ein Null-Zyklus sein, was bedeutet, dass das nachgeschaltete PE mit Daten im Zyklus arbeiten kann, nachdem es erzeugt wurde. Zum Erhalten einer noch höheren Bandbreite und zum Zulassen von mehr Programmen kann eine Vielzahl von Netzwerken parallel angeordnet sein, wie z. B. in **Fig. 6** gezeigt.

**[0040]** Räumliche Architekturen, wie die in **Fig. 6** gezeigte, können die Zusammensetzung von leichtgewichtigen Verarbeitungselementen sein, die durch ein Inter-PE-Netzwerk verbunden sind. Programme, die als Da-

tenflussgraphen angesehen werden, können auf der Architektur durch Konfigurieren der PEs und des Netzwerks abgebildet werden. Im Allgemeinen können PEs als Datenflussoperatoren konfiguriert sein und, sobald alle Eingabeoperanden am PE eingehen, kann dann eine Operation erfolgen und das Ergebnis an die gewünschten nachgeschalteten PEs weitergeleitet werden. PEs können über zweckgebundene virtuelle Schaltungen kommunizieren, die durch statistisches Konfigurieren eines leitungsvermittelten Kommunikationsnetzwerks gebildet werden. Diese virtuellen Schaltungen können flussgesteuert und vollständig gegengedrückt sein, z. B. so, dass die PEs anhalten, wenn entweder die Quelle keine Daten aufweist oder der Zielspeicherplatz voll ist. Bei Laufzeit können Daten durch die PEs fließen und den abgebildeten Algorithmus implementieren. Zum Beispiel können Daten aus dem Speicher durch die Struktur eingestreamt werden und dann zurück in den Speicher gehen. Ausführungsformen dieser Architektur können eine bemerkenswerte Leistungseffizienz im Vergleich zu herkömmlichen Mehrkernprozessoren erreichen: wenn zum Beispiel eine Berechnung in der Form von PEs einfacher und zahlreicher ist als größere Kerne und die Kommunikation direkt ist, z. B. im Gegensatz zu einer Erweiterung des Speichersystems.

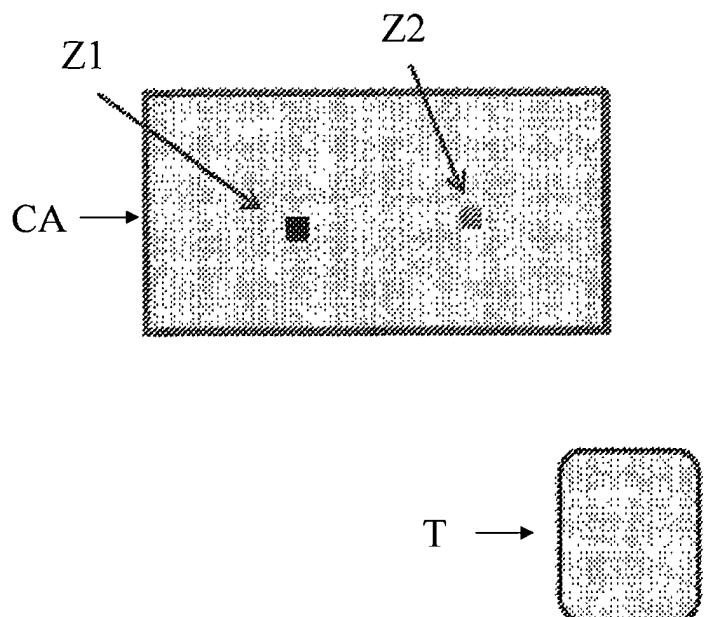

**[0041]** Fig. 6 veranschaulicht eine Beschleuniger-Kachel 600, umfassend ein Array von Verarbeitungselementen (PEs) gemäß Ausführungsformen der Offenbarung. Das Zwischenverbindungsnetz ist als leitungsvermittelte, statisch konfigurierte Kommunikationskanäle dargestellt. Zum Beispiel eine Gruppe von Kanälen, die durch einen Schalter miteinander verbunden sind (z. B. Schalter 610 in einem ersten Netzwerk und Schalter 611 in einem zweiten Netzwerk). Das erste Netzwerk und das zweite Netzwerk können getrennt oder zusammengekoppelt sein. Der Schalter 610 kann z. B. einen oder mehrere der vier Datenpfade (612, 614, 616, 618) zusammenkoppeln, z. B. wie zum Durchführen einer Operation gemäß einem Datenflussgraphen konfiguriert. In einer Ausführungsform kann die Anzahl von Datenpfaden jede beliebige Vielzahl sein. Das Verarbeitungselement (z. B. Verarbeitungselement 604) kann wie hierin offenbart sein, zum Beispiel, wie in Fig. 9A. Die Beschleuniger-Kachel 600 weist eine Speicher-/Cache-Hierarchieschnittstelle 602 auf, z. B. zum Verbinden der Beschleuniger-Kachel 600 mit einem Speicher und/oder Cache. Ein Datenpfad (z. B. 618) kann sich zu einer anderen Kachel erstrecken oder enden, z. B. am Rand einer Kachel. Ein Verarbeitungselement kann einen Eingabepuffer (z. B. Puffer 606) und einen Ausgabepuffer (z. B. Puffer 608) aufweisen.

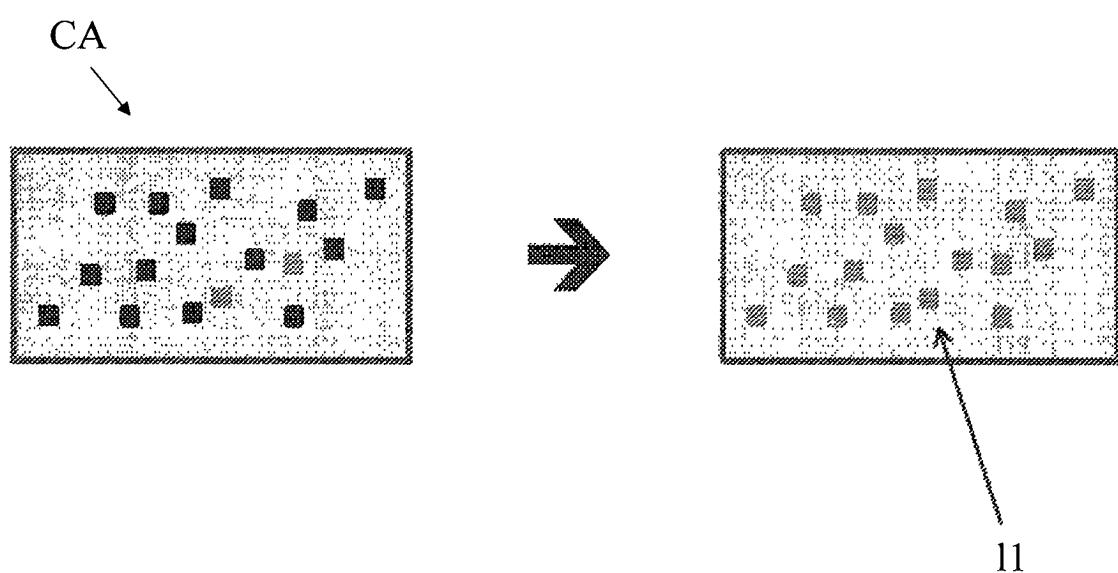

**[0042]** Die Operationen können basierend auf der Verfügbarkeit ihrer Eingaben und dem Status des PE ausgeführt werden. Ein PE kann Operanden aus den Eingabekanälen erhalten und die Ergebnisse in Ausgabekanäle schreiben, auch wenn ein interner Registerstatus ebenfalls verwendet werden kann. Bestimmte Ausführungsformen hierin beinhalten ein konfigurierbares datenflussfreundliches PE. Fig. 9 zeigt ein detailliertes Blockdiagramm eines solchen PE: dem Integer-PE. Dieses PE besteht aus verschiedenen I/O-Puffern, einer ALU, einem Speicherregister, einigen Befehlsregistern und einem Planer. Jeden Zyklus kann der Planer einen Befehl für die Ausführung basierend auf der Verfügbarkeit der Eingabe- und Ausgabepuffer und dem Status des PE auswählen. Das Ergebnis der Operation kann dann entweder in einen Ausgabepuffer oder ein Register (z. B. lokal oder PE) geschrieben werden. Die Daten, die in einen Ausgabepuffer geschrieben werden, können zu einem nachgeschalteten PE zur weiteren Verarbeitung transportiert werden. Dieser PE-Stil kann extrem energieeffizient sein, z. B. weil statt Daten aus einer komplexen Mehrportregisterdatei zu lesen, ein PE die Daten aus einem Register liest. Auf ähnliche Weise können die Befehle direkt in einem Register gespeichert werden, anstelle in einem virtuellen Befehls-Cache.

**[0043]** Befehlsregister können während eines speziellen Konfigurationsschrittes eingestellt werden. Während dieses Schritts können Hilfssteuerdrähte und Zustand zusätzlich zum inter-PE-Netzwerk zum Streamen in der Konfiguration über die verschiedenen PEs, welche die Struktur umfassen, verwendet werden. Als Ergebnis der Parallelität können bestimmte Ausführungsformen eines solchen Netzwerks eine schnelle Rekonfiguration bereitstellen, z. B. kann ein kachelgroßes Netzwerk in weniger als etwa 10 Mikrosekunden konfiguriert sein.

**[0044]** Fig. 9 repräsentiert eine Beispielkonfiguration eines Verarbeitungselements, in dem z. B. alle Architekturelemente minimal bemessen sind. In anderen Ausführungsformen ist jede der Komponenten eines Verarbeitungselements unabhängig bemessen, um neue PEs zu erzeugen. Zum Handhaben komplizierterer Programme kann z. B. eine größere Anzahl von Befehlen eingefügt werden, die durch ein PE ausführbar sind. Eine zweite Dimension der Konfigurierbarkeit ist abhängig von der PE-Arithmetik-Logik-Einheit (ALU). In Fig. 9 ist ein Integer-PE dargestellt, das Addition, Subtraktion und verschiedene logische Operationen unterstützen kann. Andere Arten von PEs können durch Ersetzen unterschiedlicher Arten von Funktionseinheiten in dem PE geschaffen werden. Ein Integer-Multiplikations-PE kann beispielsweise keine Register, einen Einzelbefehl und einen einzigen Ausgabepuffer aufweisen. Bestimmte Ausführungsformen eines PE zerlegen eine fusionierte Multiplikationsaddition (FMA) in separate, aber eng gekoppelte, Gleitkomma-Multiplikations- und Gleitkomma-Additionseinheiten zum Verbessern der Unterstützung von Multiply-Add-Schwerarbeitslasten. PEs werden nachstehend erläutert.

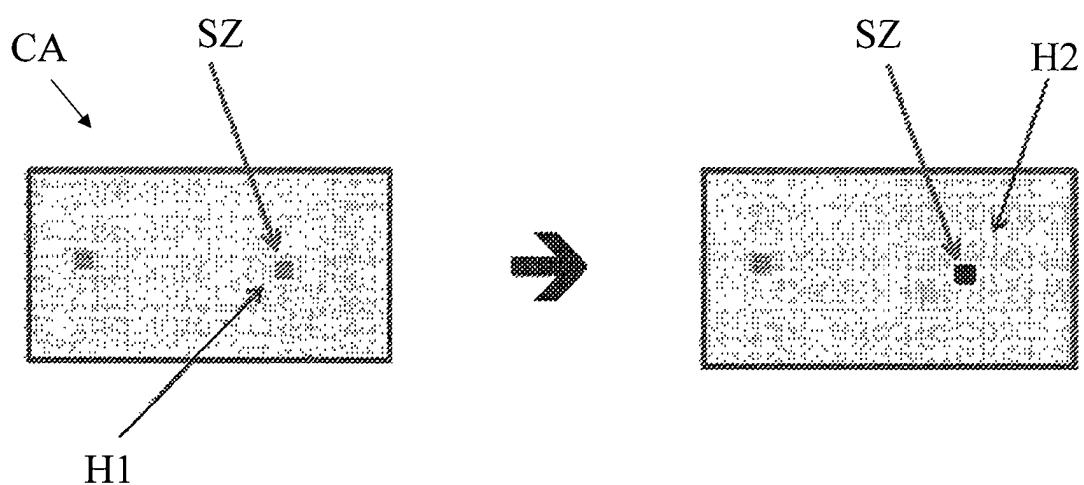

**[0045]** Fig. 7A veranschaulicht ein konfigurierbares Datenpfad-Netzwerk 700 (z. B. von Netzwerk eins oder Netzwerk zwei, die in Bezug auf Fig. 6 erläutert wurden) gemäß Ausführungsformen der Offenbarung. Das Netzwerk 700 weist mehrere Multiplexer (z. B. Multiplexer 702, 704, 706) auf, die konfiguriert werden können (z. B. über zugehörige Steuersignale), um einen oder mehrere Datenpfade (z. B. von PEs) miteinander zu verbinden. Fig. 7B veranschaulicht ein konfigurierbares Flusssteuerpfad-Netzwerk 701 (z. B. Netzwerk eins oder Netzwerk zwei, die in Bezug auf Fig. 6 erläutert wurden) gemäß Ausführungsformen der Offenbarung. Ein Netzwerk kann ein leichtgewichtiges PE-PE-Netzwerk sein. Bestimmte Ausführungsformen eines Netzwerks können als ein Satz von zusammenfügbarer Grundelementen zum Bau von verteilten, Punkt-zu-Punkt-Datenkanälen gedacht sein. Fig. 7A zeigt ein Netzwerk, das zwei aktivierte Kanäle aufweist, die fette schwarze Linie und die gepunktete schwarze Linie. Der Kanal der fetten schwarzen Linie ist Multicast, z. B. wird eine einzelne Eingabe an zwei Ausgaben gesendet. Es sei angemerkt, dass sich die Kanäle an einigen Punkten innerhalb eines einzelnen Netzwerks schneiden können, selbst wenn zweckgebundene leitungsvermittelte Pfade zwischen den Kanalendpunkten gebildet werden. Des Weiteren stellt diese Kreuzung keine strukturelle Gefahr zwischen den zwei Kanälen dar, sodass jeder unabhängig und bei voller Bandbreite arbeitet.

**[0046]** Das Implementieren von verteilten Datenkanälen kann zwei Pfade aufweisen, wie in Fig. 7A bis Fig. 7B veranschaulicht. Die Vorwärtsverbindung, oder Datenpfad, trägt Daten von einem Erzeuger zu einem Verbraucher. Multiplexer können zum Lenken von Daten und Validieren von Bits von dem Erzeuger zu dem Verbraucher konfiguriert sein, z. B. wie in Fig. 7A. Im Fall von Multicast werden die Daten zu einer Vielzahl von Verbraucherendpunkten gelenkt. Der zweite Teil dieser Ausführungsform eines Netzwerks ist die Flusssteuerung oder der Gegendruckpfad, der in Gegenrichtung des Vorwärtsdatenpfads fließt, z. B. wie in Fig. 7B. Die Verbraucherendpunkte können geltend gemacht werden, wenn sie zum Annehmen neuer Daten bereit sind. Diese Signale können dann zurück zum Erzeuger unter Verwendung der konfigurierbaren logischen Konjunktionen gelenkt werden, die als Flusssteuerungsfunktion in Fig. 7B gekennzeichnet sind (z. B. Rückfluss). In einer Ausführungsform kann jede Flusssteuerungsfunktionsschaltung mehrere Schalter (z. B. Muxes) aufweisen, wie z. B. ähnlich denen aus Fig. 7A. Der Flusssteuerpfad kann zurückkehrende Steuerdaten von dem Verbraucher an den Erzeuger handhaben. Konjunktionen können Multicast ermöglichen, wobei z. B. jeder Verbraucher Daten empfangen kann, bevor der Erzeuger voraussetzt, dass diese empfangen wurden. In einer Ausführungsform ist ein PE ein PE, das einen Datenflussoperator wie seine Architekturnchnittstelle aufweist. Zusätzlich oder alternativ kann in einer Ausführungsform ein PE eine Art von PE (z. B. in der Struktur) sein, z. B. ein PE, das eine Befehlszweiger-, Triggerbefehl- oder Zustandsmaschinen-Architekturnchnittstelle aufweist, aber nicht darauf beschränkt ist.

**[0047]** Das Netzwerk kann statisch konfiguriert sein, z. B. zusätzlich zu PEs, die statisch konfiguriert sind. Während des Konfigurationsschrittes können Konfigurationsbits an jeder Netzwerkkomponente eingestellt werden. Diese Bits steuern z. B. die Muxauswahl und die Flusssteuerfunktionen. Ein Netzwerk kann mehrere Netzwerke umfassen, z. B. ein Datenpfad-Netzwerk und ein Flusssteuerungsnetzwerk. Eine Netzwerk oder mehrere Netzwerke können Pfade unterschiedlicher Breiten benutzen (z. B. einer ersten Breite und einer engeren oder breiteren Breite). In einer Ausführungsform weist ein Datenpfad-Netzwerk eine breitere (z. B. Bittransport) Breite auf als die Breite eines Flusssteuerpfad-Netzwerks. In einer Ausführungsform weist jedes von einem ersten Netzwerk und einem zweiten Netzwerk sein eigenes Datenpfad-Netzwerk und Flusssteuerpfad-Netzwerk auf, z. B. Datenpfad-Netzwerk A und Flusssteuerpfad-Netzwerk A und ein breiteres Datenpfad-Netzwerk B und ein Flusssteuerpfad-Netzwerk B.

**[0048]** Bestimmte Ausführungsformen eines Netzwerks sind pufferlos und die Daten müssen sich zwischen dem Erzeuger und Verbraucher in einem Einzelzyklus bewegen. Bestimmte Ausführungsformen eines Netzwerks sind ungebunden, das heißt, das Netzwerk überspannt die gesamte Struktur. In einer Ausführungsform kommuniziert ein PE mit einem anderen PE in einem Einzelzyklus. In einer Ausführungsform können zum Verbessern der Routingbandbreite mehrere Netzwerke parallel zwischen die Reihen der PE gelegt werden.

**[0049]** Bezuglich der FPGAs haben bestimmte Ausführungsformen von Netzwerken hierin drei Vorteile: Bereich, Frequenz und Programmausdruck. Bestimmte Ausführungsformen von Netzwerken arbeiten grobkörnig, was z. B. die Anzahl an Konfigurationsbits reduziert und dadurch den Netzwerkbereich. Bestimmte Ausführungsformen von Netzwerken erhalten die Bereichsreduktion durch Implementieren der Steuerlogik direkt im Schaltkreis (z. B. Silicium). Bestimmte Ausführungsformen gehärteter Netzwerkimplementierungen genießen gegenüber FPGA auch einen Frequenzvorteil. Aufgrund eines Bereichs- und Frequenzvorteils kann ein Leistungsvorteil vorhanden sein, wenn eine geringere Spannung als Durchsatzparität verwendet wird. Schließlich stellen bestimmte Ausführungsformen von Netzwerken bessere High-Level-Semantiken als FPGA-Drähte bereit, insbesondere in Bezug auf die variable Zeitsteuerung, weshalb solche bestimmten Ausführungsformen leichter durch die Kompilierer anzuzielen sind. Bestimmte Ausführungsformen von Netzwerken hierin können

als ein Satz von zusammensetzbaren Grundelementen zum Bau von verteilten, Punkt-zu-Punkt-Datenkanälen gedacht sein.

**[0050]** In bestimmten Ausführungsformen kann eine Multicast-Quelle ihre Daten erst dann geltend machen, wenn ein Bereit-Signal von jeder Senke empfangen wurde. Daher können ein zusätzliches Konjunktions- und Steuerbit in dem Multicastfall benutzt werden.

**[0051]** Wie bestimmte PEs kann das Netzwerk statistisch konfiguriert sein. Während dieses Schrittes werden Konfigurationsbits an jeder Netzwerkkomponente eingestellt. Diese Bits steuern z. B. die Muxauswahl und die Flusssteuerungsfunktion. Der Vorwärtspfad unseres Netzwerks erfordert, dass einige Bits ihre Muxe schwingen. In dem in **Fig. 7A** gezeigten Beispiel werden vier Bits pro Hop erfordert: die Ost- und West-Muxe benutzen jeweils ein Bit, während die südlich gebundenen Muxe zwei Bits benutzen. In dieser Ausführungsform können vier Bits für den Datenpfad benutzt werden, es können aber 7 Bits für die Flusssteuerungsfunktion benutzt werden (z. B. in dem Flusssteuerpfad-Netzwerk). Andere Ausführungsformen können mehr Bits benutzen, z. B., wenn ein CSA ferner eine Nord-Süd-Richtung benutzt. Die Flusssteuerungsfunktion kann ein Steuerbit für jede Richtung benutzen, aus welcher die Flusssteuerung kommen kann. Dies kann das Einstellen der Sensitivität der Flusssteuerungsfunktion statisch ermöglichen. Die Tabelle 1 unten fasst die Boolesche Algebra-Implementierung der Flusssteuerungsfunktion für das Netzwerk in **Fig. 7B** zusammen, wobei die Konfigurationsbits in Großbuchstaben aufgeführt sind. In diesem Beispiel werden sieben Bits benutzt.

Tabelle 1 Flussimplementierung

|              |                                                                                                                      |

|--------------|----------------------------------------------------------------------------------------------------------------------|

| readyToEast  | (EAST_WEST_SENSITIVE+readyFromWest) * (EAST_SOUTH_SENSITIVE+readyFromSouth)                                          |

| readyToWest  | (WEST_EAST_SENSITIVE+readyFromEast) * (WEST_SOUTH_SENSITIVE+readyFromSouth)                                          |

| readyToNorth | (NORTH_WEST_SENSITIVE+readyFromWest) * (NORTH_EAST_SENSITIVE+readyFromEast) * (NORTH_SOUTH_SENSITIVE+readyFromSouth) |

**[0052]** Für die dritte Flusssteuerungsbox von links in **Fig. 7B** sind EAST\_WEST\_SENSITIVE (ost-west-sensitiv) und NORTH\_SOUTH\_SENSITIVE (nord-süd-sensitiv) als Satz dargestellt, um die Flusssteuerung für Kanäle in fetter Linie bzw. gestrichelter Linie zu implementieren.

**[0053]** **Fig. 8** veranschaulicht eine Hardware-Prozessor-Kachel, 800 umfassend einen Beschleuniger **802** gemäß Ausführungsformen der Offenbarung. Der Beschleuniger **802** kann ein CSA gemäß dieser Offenbarung sein. Die Kachel **800** weist mehrere Cache-Bänke (z. B. Cache-Bank **808**) auf. Abfrageadressdatei (RAF)-Schaltungen **810** können aufgenommen sein, z. B. wie unten in Abschnitt 3.2 erläutert. ODI kann sich auf eine On-Die-Zwischenverbindung beziehen, z. B. eine Zwischenverbindung, die sich über den gesamten Chip erstreckt, der alle Kacheln miteinander verbindet. OTI kann sich auf eine On-Tile-Zwischenverbindung beziehen, die sich z. B. über eine Kachel erstreckt, die z. B. die Cache-Bänke auf der Kachel miteinander verbindet.

#### Verarbeitungselemente

**[0054]** In bestimmten Ausführungsformen weist ein CSA ein Array aus heterogenen PEs auf, in denen die Struktur aus verschiedenen Typen von PEs zusammengesetzt ist, von denen jedes nur einen Untersatz von Datenflussoperatoren implementiert. Rein beispielhaft zeigt **Fig. 9** eine provisionale Implementierung eines PE, das einen breiten Satz von Integer- und Steueroperationen implementieren kann. Andere PEs, einschließlich solcher, die eine Gleitkomma-Addition, Gleitkomma-Multiplikation, Pufferung und bestimmte Steueroperationen aufweisen, können einen ähnlichen Implementierungsstil aufweisen, z. B. mit der angemessenen (Datenflussoperator)-Schaltung, welche die ALU ersetzt. PEs (z. B. Datenflussoperatoren) eines CSA können vor dem Beginn der Ausführung zum Implementieren einer bestimmten Datenfluss-Operation von einem der Sätze, die das PE unterstützt, konfiguriert (z. B. programmiert) werden. Eine Konfiguration kann eines oder zwei Steuerwörter umfassen, die einen Opcode spezifizieren, der die ALU steuert, die verschiedenen Multiplexer innerhalb des PE lenkt und den Datenfluss in die PE-Kanäle hinein und aus diesen heraus betätigt. Die Datenflussoperatoren können durch Mikrocodieren dieser Konfigurationsbits implementiert werden. Das dargestellte Integer-PE **900** in **Fig. 9** ist als Einzelstufen-Logik-Pipeline, die von oben nach unten fließt, organisiert. Daten treten von einem eines Satzes lokaler Netzwerke ein, in denen sie in einem Eingabepuffer zur nachfolgenden Operation registriert werden. Jedes PE kann eine Anzahl von breiten, datenausgerichteten und schmalen, steuerungsausgerichteten Kanälen unterstützen. Die Anzahl der vorgesehenen Kanäle kann basierend auf der

PE-Funktionalität variieren, jedoch weist eine Ausführungsform eines ganzzahlorientierten PE 2 breite und 1-2 schmale Eingabe- und Ausgabekanäle auf. Obwohl das Integer-PE als eine Einzelzyklus-Pipeline implementiert ist, können andere Wahlen für das Pipelinennetz benutzt werden. Multiplikations-PEs können z. B. eine Mehrzahl von Pipelinestufen aufweisen.