(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2019년06월27일

(11) 등록번호 10-1993869

(24) 등록일자 2019년06월21일

- (51) 국제특허분류(Int. Cl.)

*H04J 11/00* (2006.01) *H04W 56/00* (2009.01)

- (52) CPC특허분류

*H04J 11/0073* (2013.01)

*H04W 56/001* (2013.01)

- (21) 출원번호 10-2018-7019304(분할)

- (22) 출원일자(국제) 2014년11월03일

심사청구일자 2018년07월05일

- (85) 번역문제출일자 2018년07월05일

- (65) 공개번호 10-2018-0080373

- (43) 공개일자 2018년07월11일

- (62) 원출원 특허 10-2016-7013926

원출원일자(국제) 2014년11월03일

심사청구일자 2016년05월25일

- (86) 국제출원번호 PCT/US2014/063726

- (87) 국제공개번호 WO 2015/066632

국제공개일자 2015년05월07일

- (30) 우선권주장

61/898,973 2013년11월01일 미국(US)

14/530,322 2014년10월31일 미국(US)

- (56) 선행기술조사문헌

3gpp R1-072321\*

3gpp R1-134883\*

Draft Report of 3GPP TSG RAN WG1 #74bis

v0.2.0

([http://www.3gpp.org/ftp/tsg\\_ran/WG1\\_RL1/TSGR1\\_74b/Report/](http://www.3gpp.org/ftp/tsg_ran/WG1_RL1/TSGR1_74b/Report/)) (2013.10.15.)\*

3GPP TS 36.211 v.8.8.0 (2009.09.29.)\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 22 항

심사관 : 노상민

(54) 발명의 명칭 동기 신호 송신 시스템 및 방법

**(57) 요 약**

장치대장치(device-to-device, D2D) 통신 방법은, 동기 소스가, eNodeB(Evolved NodeB)에 의해 보내지는 주 동기 신호(primary synchronization signal, PSS) 및 장치대장치 통신 장치(블록 305)에 의해 보내지는 기준 상향 링크(uplink, UL) 신호와 서로 다른 주 장치대장치 동기 신호를 생성하는 단계; 그리고 동기 소스가, 단일 캐리

(뒷면에 계속)

**대 표 도** - 도3

어 주파수 분할 다중 접속(single carrier frequency division multiple access, SC-FDMA) 과형(블록 315)으로

주 장치대장치 동기 신호를 송신하는 단계를 포함한다.

(52) CPC특허분류

*H04J 2011/0096* (2013.01)

*H04J 2211/005* (2013.01)

(72) 발명자

**리 치앙**

중국 베이징 로드 젠카이청 넘버 1 빌딩 세컨드 룸

1-102

**포포비 브라니슬라브**

스웨덴 에스이-164 40 키스타 박스 54 스카홀츠가

탄 9-11 4 플로어 3

---

**베르그렌 프레드릭**

스웨덴 에스이-164 4 키스타 박스 54 스카홀츠가탄

9-11 4 플로어 3

## 명세서

### 청구범위

#### 청구항 1

장치대장치(device-to-device) 통신 방법으로서,

동기 소스(synchronization source)가 제1 시퀀스에 따라서 동기 시퀀스를 생성하는 단계 - 상기 제1 시퀀스의 제1 루트 인덱스는 주 동기 신호(primary synchronization signal, PSS)를 생성하기 위해 사용되는 제2 시퀀스의 제2 루트 인덱스와 서로 다름 - ;

동기 소스가, 중심 대칭인 주 장치대장치 동기 신호를 만들어 내기 위해서 상기 동기 시퀀스를 서브캐리어에 매핑하는 단계; 및

상기 동기 소스가, 상기 주 장치대장치 동기 신호를 단일 캐리어 주파수 분할 다중 접속(single carrier frequency division multiple access, SC-FDMA) 과형으로 송신하는 단계

를 포함하고,

상기 주 장치대장치 동기 신호의 N개의 샘플은  $s[k] = -s[N-k]$ ,  $k = 1, \dots, N-1$ 에 따라서 중심 대칭이고, 여기서 N은 정수 값이며,

상기 제1 시퀀스의 제1 루트 인덱스는 장치대장치 동작 대역폭에 기초하여 선택되는,

장치대장치 통신 방법.

#### 청구항 2

제1항에 있어서,

상기 제1 시퀀스는 제1 천공(punctured) 자도프-추(Zadoff-Chu, ZC) 시퀀스를 포함하고, 상기 제2 시퀀스는 제2 천공 ZC 시퀀스를 포함하는, 장치대장치 통신 방법.

#### 청구항 3

제1항 또는 제2항에 있어서,

상기 동기 신호가  $s_u(t) = \sum_{k=-N/2}^{N/2-1} H_u[k] \cdot e^{j2\pi(k+\delta)\Delta f t}$ ,  $0 \leq t < \frac{1}{\Delta f} = N \cdot T_s$ 에 따라서 생성되고, 상기 동기

시퀀스가  $H_u[k]$ 의 최대 N개의 계수에 매핑되며, 여기서  $T_s$ 는 샘플링 주기(period)이고,  $\Delta f$ 는 서브캐리어 간 격(spacing)이고, u는 상기 제1 루트 인덱스이며,  $N = 1/T_s \Delta f$ , 그리고  $\delta = 1/2$ , 장치대장치 통신 방법.

#### 청구항 4

제3항에 있어서,

상기 동기 시퀀스는 아래와 같이 표현할 수 있고,

$$d_u(n) = \begin{cases} e^{-j\frac{\pi m(n+1)}{63}} & n = 0, 1, \dots, 30 \\ e^{-j\frac{\pi u(n+1)(n+2)}{63}} & n = 31, 32, \dots, 61 \end{cases}$$

상기 동기 시퀀스는 아래에 따라서 매핑되며,

$$H_u[k] = d_u(n), \quad n=0, \dots, 61,$$

$$K=n-31,$$

여기서  $u$ 는 상기 제1 루트 인덱스인, 장치대장치 통신 방법.

### 청구항 5

제1항 또는 제2항에 있어서,

상기 제1 루트 인덱스가 상기 동기 소스의 식별자(identifier)에 추가로 기초하여 선택되는, 장치대장치 통신 방법.

### 청구항 6

장치대장치(device-to-device) 통신 장치의 동작 방법으로서,

상기 장치대장치 통신 장치가, 단일 캐리어 주파수 분할 다중 접속(single carrier frequency division multiple access, SC-FDMA) 과정으로 송신되는 주 장치대장치 동기 신호를 수신하는 단계 - 상기 주 장치대장치 동기 신호는 제1 시퀀스에 따라서 생성된 동기 시퀀스를 서브캐리어에 매핑하는 것에 의해 생성되고, 상기 제1 시퀀스의 제1 루트 인덱스는 주 동기 신호(primary synchronization signal, PSS)를 생성하기 위해 사용되는 제2 시퀀스의 제2 루트 인덱스와 서로 다르며, 상기 주 장치대장치 동기 신호는 중심 대칭이고, 상기 주 장치대장치 동기 신호의  $N$ 개의 샘플은  $s[k] = -s[N-k]$ ,  $k = 1, \dots, N-1$ 에 따라서 중심 대칭이고, 여기서  $N$ 은 정수 값이며, 상기 제1 시퀀스의 제1 루트 인덱스는 장치대장치 동작 대역폭에 기초하여 선택됨 - ;

상기 장치대장치 통신 장치가, 상기 주 장치대장치 동기 신호를 탐지하는 단계; 및

상기 장치대장치 통신 장치가, 상기 주 장치대장치 동기 신호에 따라서 동기화하는 단계

를 포함하는, 장치대장치 통신 장치의 동작 방법.

### 청구항 7

제6항에 있어서,

상기 제1 시퀀스는 제1 천공(punctured) 자도프-추(Zadoff-Chu, ZC) 시퀀스를 포함하고, 상기 제2 시퀀스는 제2 천공 ZC 시퀀스를 포함하는, 장치대장치 통신 장치의 동작 방법.

### 청구항 8

제6항 또는 제7항에 있어서,

상기 동기 신호가  $s_u(t) = \sum_{k=-N/2}^{N/2-1} H_u[k] \cdot e^{j2\pi(k+\delta)\Delta f t}$ ,  $0 \leq t < \frac{1}{\Delta f} = N \cdot T_s$ 에 따라서 생성되고, 상기 동기

시퀀스가  $H_u[k]$ 의 최대  $N$ 개의 계수에 매핑되며, 여기서  $T_s$ 는 샘플링 주기(period)이고,  $\Delta f$ 는 서브캐리어 간

격(spacing)이고,  $u$ 는 상기 제1 루트 인덱스이며,  $N = 1/T_s \Delta f$ , 그리고  $\delta = 1/2$ , 장치대장치 통신 장치의 동작 방법.

### 청구항 9

제8항에 있어서,

상기 동기 시퀀스는 아래와 같이 표현할 수 있고,

$$d_u(n) = \begin{cases} e^{-j\frac{\pi un(n+1)}{63}} & n = 0, 1, \dots, 30 \\ e^{-j\frac{\pi u(n+1)(n+2)}{63}} & n = 31, 32, \dots, 61 \end{cases}$$

상기 동기 시퀀스는 아래에 따라서 매핑되며,

$$H_u[k] = d_u(n), \quad n=0, \dots, 61,$$

$$K=n-31,$$

여기서  $u$ 는 상기 제1 루트 인덱스인, 장치대장치 통신 장치의 동작 방법.

### 청구항 10

제6항에 있어서,

상기 제1 루트 인덱스가 상기 주 장치대장치 동기 신호를 송신하는 동기 소스의 식별자(identifier)에 추가로 기초하여 선택되는, 장치대장치 통신 장치의 동작 방법.

### 청구항 11

동기 소스(synchronization source)로서,

제1 시퀀스에 따라서 동기 시퀀스를 생성하고, 중심 대칭인 주 장치대장치 동기 신호를 만들어 내기 위해서 상기 동기 시퀀스를 서브캐리어에 매핑하도록 구성된 프로세서 - 상기 제1 시퀀스의 제1 루트 인덱스는 주 동기 신호(primary synchronization signal, PSS)를 생성하기 위해 사용되는 제2 시퀀스의 제2 루트 인덱스와 서로 다름 - ; 및

상기 프로세서와 작동 가능하게 연결되고, 상기 주 장치대장치 동기 신호를 단일 캐리어 주파수 분할 다중 접속(single carrier frequency division multiple access, SC-FDMA) 과형으로 송신하도록 구성된 송신기

를 포함하고,

상기 주 장치대장치 동기 신호의  $N$ 개의 샘플은  $s[k] = -s[N-k]$ ,  $k = 1, \dots, N-1$ 에 따라서 중심 대칭이고, 여기서  $N$ 은 정수 값이며,

상기 제1 시퀀스의 제1 루트 인덱스는 장치대장치 동작 대역폭에 기초하여 선택되는,

동기 소스.

### 청구항 12

제11항에 있어서,

상기 제1 시퀀스는 제1 천공(punctured) 자도프-추(Zadoff-Chu, ZC) 시퀀스를 포함하고, 상기 제2 시퀀스는 제2 천공 ZC 시퀀스를 포함하는, 동기 소스.

### 청구항 13

제11항 또는 제12항에 있어서,

상기 동기 신호가  $s_u(t) = \sum_{k=-N/2}^{N/2-1} H_u[k] \cdot e^{j2\pi(k+\delta)\Delta f t}$ ,  $0 \leq t < \frac{1}{\Delta f} = N \cdot T_s$ 에 따라서 생성되고, 상기 동기 시퀀스가  $H_u[k]$ 의 최대  $N$ 개의 계수에 매핑되며, 여기서  $T_s$ 는 샘플링 주기(period)이고,  $\Delta f$ 는 서브캐리어 간

격(spacing)이고,  $u$ 는 상기 제1 루트 인덱스이며,  $N = 1/T_s \Delta f$ , 그리고  $\delta = 1/2$ 인, 동기 소스.

#### 청구항 14

제13항에 있어서,

상기 동기 시퀀스는 아래와 같이 표현할 수 있고,

$$d_u(n) = \begin{cases} e^{-j\frac{\pi m(n+1)}{63}} & n = 0, 1, \dots, 30 \\ e^{-j\frac{\pi u(n+1)(n+2)}{63}} & n = 31, 32, \dots, 61 \end{cases}$$

상기 동기 시퀀스는 아래에 따라서 매핑되며,

$$H_u[k] = d_u(n), \quad n=0, \dots, 61,$$

$$K=n-31,$$

여기서  $u$ 는 상기 제1 루트 인덱스인, 동기 소스.

#### 청구항 15

제11항 또는 제12항에 있어서,

상기 제1 루트 인덱스가 상기 동기 소스의 식별자(identifier)에 추가로 기초하여 선택되는, 동기 소스.

#### 청구항 16

장치대장치(device-to-device) 통신 장치로서,

프로세서에 작동 가능하게 연결되고, 단일 캐리어 주파수 분할 다중 접속(single carrier frequency division multiple access, SC-FDMA) 파형으로 송신되는 주 장치대장치 동기 신호를 수신하도록 구성된 수신기 - 상기 주 장치대장치 동기 신호는 제1 시퀀스에 따라서 생성된 동기 시퀀스를 서브캐리어에 매핑하는 것에 의해 생성되고, 상기 제1 시퀀스의 제1 루트 인덱스는 주 동기 신호(primary synchronization signal, PSS)를 생성하기 위해 사용되는 제2 시퀀스의 제2 루트 인덱스와 서로 다르며, 상기 주 장치대장치 동기 신호는 중심 대칭이고, 상기 주 장치대장치 동기 신호의  $N$ 개의 샘플은  $s[k] = -s[N-k]$ ,  $k = 1, \dots, N-1$ 에 따라서 중심 대칭이고, 여기서  $N$ 은 정수 값이고, 상기 제1 시퀀스의 제1 루트 인덱스는 장치대장치 동작 대역폭에 기초하여 선택됨 - ;

상기 주 장치대장치 동기 신호를 탐지하고 그리고 상기 주 장치대장치 동기 신호에 따라서 동기화하도록 구성된 프로세서

를 포함하는

장치대장치 통신 장치.

#### 청구항 17

제16항에 있어서,

상기 제1 시퀀스는 제1 천공(punctured) 자도프-추(Zadoff-Chu, ZC) 시퀀스를 포함하고, 상기 제2 시퀀스는 제2 천공 ZC 시퀀스를 포함하는, 장치대장치 통신 장치.

#### 청구항 18

제16항 또는 제17항에 있어서,

상기 동기 신호가  $s_u(t) = \sum_{k=-N/2}^{N/2-1} H_u[k] \cdot e^{j2\pi(k+\delta)\Delta f t}$ ,  $0 \leq t < \frac{1}{\Delta f} = N \cdot T_s$ 에 따라서 생성되고, 상기 동기

시퀀스가  $H_u[k]$ 의 최대 N개의 계수에 매핑되며, 여기서  $T_s$ 는 샘플링 주기(period)이고,  $\Delta f$ 는 서브캐리어 간 격(spacing)이고, u는 상기 제1 루트 인덱스이며,  $N = 1/T_s \Delta f$ , 그리고  $\delta = 1/2$ , 장치대장치 통신 장치.

### 청구항 19

제18항에 있어서,

상기 동기 시퀀스는 아래와 같이 표현할 수 있고,

$$d_u(n) = \begin{cases} e^{-j\frac{\pi am(n+1)}{63}} & n = 0, 1, \dots, 30 \\ e^{-j\frac{\pi u(n+1)(n+2)}{63}} & n = 31, 32, \dots, 61 \end{cases}$$

상기 동기 시퀀스는 아래에 따라서 매핑되며,

$$H_u[k] = d_u(n), \quad n=0, \dots, 61,$$

$$K=n-31,$$

여기서 u는 상기 제1 루트 인덱스인, 장치대장치 통신 장치.

### 청구항 20

제16항에 있어서,

상기 제1 루트 인덱스가 상기 주 장치대장치 동기 신호를 전송하는 동기 소스의 식별자(identifier)에 추가로 기초하여 선택되는, 장치대장치 통신 장치.

### 청구항 21

프로그램이 기록된 컴퓨터 판독가능한 기록 매체로서,

상기 프로그램은 실행시에 컴퓨터로 하여금 제1항 또는 제2항에 따른 방법을 수행하게 하는,

컴퓨터 판독가능한 기록 매체.

### 청구항 22

프로그램이 기록된 컴퓨터 판독가능한 기록 매체로서,

상기 프로그램은 실행시에 컴퓨터로 하여금 제6항 또는 제7항에 따른 방법을 수행하게 하는,

컴퓨터 판독가능한 기록 매체.

### 청구항 23

삭제

### 청구항 24

삭제

### 청구항 25

삭제

## 청구항 26

삭제

### 발명의 설명

#### 기술 분야

[0001]

본 발명은 무선 통신에 관한 것으로서, 특히, 동기 신호를 송신하는 시스템 및 방법에 관한 것이다.

#### 배경 기술

[0002]

장치대장치(Device-to-Device, D2D) 기술은 새로운 서비스를 제공하고, 시스템 스루풋(throughput)을 향상시키며, 더 나은 사용자 경험을 제공할 수 있기 때문에 많은 관심을 받고 있다. D2D에 대한 다양한 잠재적 사용 사례가 확인되었다.

[0003]

성공적인 D2D 통신을 보장하기 위해서, 동기(synchronization)이 매우 중요하다. D2D 송신 및 수신 사용자 장비(user equipment, UE)들은 동기 소스(들)로부터 동일한 시간 및/또는 주파수 동기를 획득해야 한다. 이러한 소스들은 D2D UE들이 시간 및/또는 주파수 동기를 얻는 것을 보장할 수 있도록 적어도 D2D 동기 신호(D2D synchronization signal, D2DSS)를 주기적으로 송신할 필요가 있다. 동기 소스는 eNodeB(evolved NodeB)로부터의 하향링크(downlink, DL) 동기 채널을 릴레이하고 있는, 기지국(base station), eNodeB(전통적인 3GPP(third generation partnership project) LTE(long term evolution) 네트워크와 같음), 또는 D2D UE일 수 있다.

### 발명의 내용

[0004]

아래는 동기 신호를 송신하는 방법 및 시스템을 제공하는 본 개시의 실시예이다.

[0005]

본 개시의 한 실시예에 따르면, 장치대장치(device-to-device) 통신 방법이 제공된다. 상기 장치대장치 통신 방법은, 동기 소스(synchronization source)가, eNodeB(evolved NodeB)로부터 보내지는 주 동기 신호(primary synchronization signal, PSS) 및 장치대장치 통신 장치로부터 보내지는 기존 상향링크(uplink, UL) 신호와 서로 다른 주 장치대장치 동기 신호를 생성하는 단계; 그리고 동기 소스가, 주 장치대장치 동기 신호를 단일 캐리어 주파수 분할 다중 접속(single carrier frequency division multiple access, SC-FDMA) 파형으로 송신하는 단계를 포함한다.

[0006]

본 개시의 다른 실시예에 따르면, 장치대장치(device-to-device) 통신 장치의 동작 방법이 제공된다. 상기 동작 방법은, 장치대장치 통신 장치가, eNodeB(evolved NodeB)로부터 보내지는 주 동기 신호(primary synchronization signal, PSS) 및 장치대장치 통신 장치로부터 보내지는 기존 상향링크(uplink, UL) 신호와 서로 다른 주 장치대장치 동기 신호를 포함하는 복수의 물리 자원 블록(physical resource block, PRB)을 수신하는 단계; 장치대장치 통신 장치가, 복수의 PRB 내에서 주 장치대장치 동기 신호를 탐지하는 단계; 그리고 장치대장치 통신 장치가, 주 장치대장치 동기 신호에 따라서 동기화하는 단계를 포함하고, 주 장치대장치 동기 신호는 단일 캐리어 주파수 분할 다중 접속(single carrier frequency division multiple access, SC-FDMA) 파형으로 송신된다.

[0007]

본 개시의 다른 실시예에 따르면, 동기 소스(synchronization source)가 제공된다. 상기 동기 소스는, eNodeB(evolved NodeB)로부터 보내지는 주 동기 신호(primary synchronization signal, PSS) 및 장치대장치 통신 장치로부터 보내지는 기존 상향링크(uplink, UL) 신호와 서로 다른 주 장치대장치 동기 신호를 생성하도록 구성된 프로세서; 그리고 주 장치대장치 동기 신호를 단일 캐리어 주파수 분할 다중 접속(single carrier frequency division multiple access, SC-FDMA) 파형으로 송신하도록 구성된, 프로세서와 동작 가능하게 연결된 송신기를 포함한다.

[0008]

본 개시의 다른 실시예에 따르면, 장치대장치(device-to-device) 통신 방법이 제공된다. 상기 장치대장치 통신

$$s_u(t) = \sum_{k=-N/2}^{N/2-1} H_u[k] \cdot e^{j2\pi(k+\delta)\Delta f t}, \quad 0 \leq t < \frac{1}{\Delta f} = N \cdot T_s$$

방법은, 동기 소스(synchronization source)가,

에 따라서 주 장치대장치 동기 신호를 생성하는 단계; 그리고 동기 소스가, 단일 캐리어 주파수 분할 다중 접속

(single carrier frequency division multiple access, SC-FDMA) 과정으로 주 장치대장치 동기 신호를 송신하는 단계를 포함하고, 주 장치대장치 동기 시퀀스가  $H[\cdot]$ 의 최대  $N$ 개의 푸리에 계수(Fourier coefficient)에 매핑되고, 여기서  $T_s$ 는 샘플링 주기(period)이고,  $\Delta f$ 는 서브캐리어 간격(spacing)이고,  $u$ 는 제1 루트 인덱스이고,  $N$ 은 정수 값이며,  $\delta = 1/2$  이다.

[0009] 실시예의 한 가지 이점은 중심 대칭 신호의 사용이 디코딩 복잡도를 단순화한다는 것이다.

### 도면의 간단한 설명

[0010] 본 개시와 그 이점에 대한 보다 완벽한 이해를 위해서, 첨부 도면과 결합된 아래 설명이 참조된다.

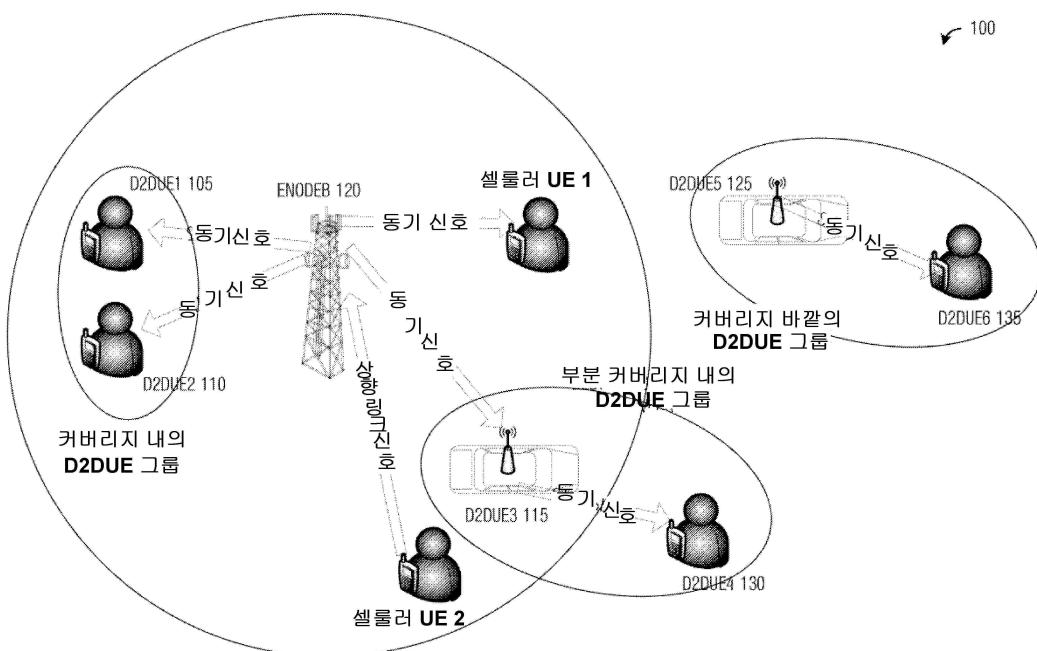

도 1은 여기 설명된 실시예에 따른 통신 시스템의 예시를 도시한다;

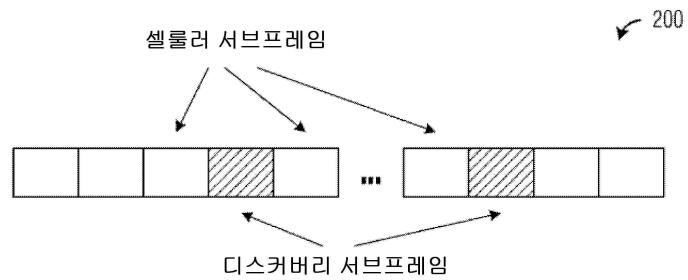

도 2는 여기 설명된 실시예에 따른 서브프레임의 예시를 도시한다;

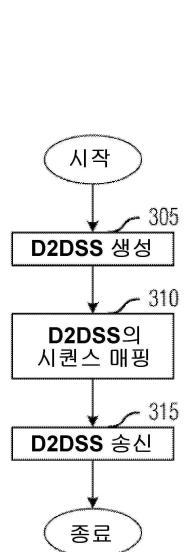

도 3은 여기 설명된 실시예에 따른 D2D UE에서 일어나는 동작의 예시의 흐름도를 도시한다;

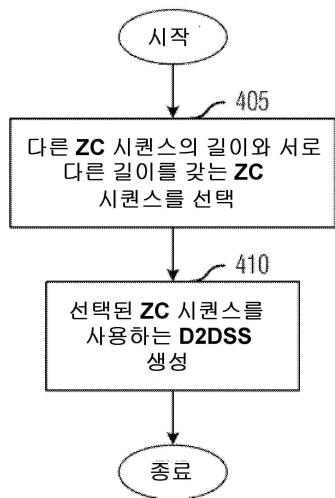

도 4는 여기 설명된 실시예에 따른 D2D UE가 D2DSS를 생성하는 경우 D2D UE에서 일어나는 동작의 예시의 흐름도를 도시한다;

도 5는 여기 설명된 실시예에 따른 D2D UE가 다른 루트 인덱스를 갖는 ZC 시퀀스에 따라서 D2DSS를 생성하는 경우 D2D UE에서 일어나는 동작의 예시의 흐름도를 도시한다;

도 6은 여기 설명된 실시예에 따른 예를 들어, 여기 설명된 장치 및 방법을 구현하기 위해 사용될 수 있는 컴퓨팅 플랫폼의 예시를 도시한다;

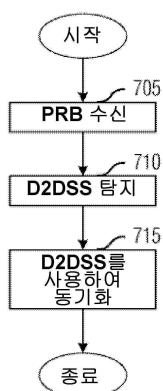

도 7은 여기 설명된 실시예에 따른 D2DSS를 사용하여 동기화하는 D2D 통신 장치에서 일어나는 동작의 예시의 흐름도를 도시한다;

도 8은 여기 설명된 실시예에 따른 통신 장치의 예시를 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0011] 현재 실시예의 동작 및 그들의 구조가 아래에서 설명된다. 인정되어야 할 것은, 하지만, 본 개시는 특정 상황에서 다양하게 구현될 수 있는, 적용 가능한 다수의 창의적인 컨셉트를 제공한다는 것이다. 설명된 특정 실시예는 단지 개시에 관한 특정 구조 및 개시를 작동시키기 위한 방법을 설명하기 위한 것에 불과하고, 본 개시의 범위를 제한하지 않는다.

[0012] 본 개시는 특정 상황에서의 실시예, 주로, D2D 통신을 용이하게 할 수 있는 동기 신호를 사용하는 통신 시스템에 관련하여 설명될 것이다. 본 개시는 3GPP(Third Generation Partnership Project), IEEE 802.11 등과 같은 표준 준수 통신 시스템, 기술적 표준, 그리고 D2D 통신을 용이하게 하기 위하여 동기 신호를 사용하는 비표준 준수 통신 시스템에 적용될 수 있다.

[0013] 도 1은 통신 시스템(100)의 실시예를 도시한다. 통신 시스템(100)은 D2D 통신을 지원하고, 따라서 D2D 시스템으로 지칭될 수 있다. D2D 시스템에서의 동기가 도 1에 강조되어 있다. 도 1에 도시된 대로, D2DUE1(105), D2DUE2(110), 그리고 D2DUE3(115)는 eNodeB(120)에 의해 보내진 주 동기 신호(primary synchronization signal, PSS) 및 보조 동기 신호(secondary synchronization signal, SSS), 또는 eNodeB(120)에 의해 보내진 다른 동기 신호들과 같은 레거시(legacy) LTE DL 동기 채널에 기반하여 시간 및/또는 주파수 동기를 얻을 수 있다. 동시에, D2DUE3(115) 및 D2DUE5(125)는 각각 D2DUE4(130) 및 D2DUE6(135)에 대해서 동기 소스(synchronization source)(즉, D2D 동기 소스)의 역할을 수행한다. eNodeB들은 또한 통상적으로 NodeB, 제어기(controller), 기지국(base station), 접속 포인트(access point), 베이스 터미널 스테이션(base terminal station) 등으로 지칭될 수 있다. 유사하게, 단말들도 또한, 통상적으로 이동 스테이션(mobile station), 모바일, 단말, 사용자, 스테이션, 가입자 등으로 지칭될 수 있다. 통신 시스템은 많은 수의 UE와 통신할 능력이 있는 복수의 eNodeB를 사용할 수 있다고 이해되지만, 오직 하나의 eNodeB 및 다수의 UE가 간략함을 위해서 도시된다.

[0014] 디스커버리(discovery)는 이웃 UE를 탐지할 능력을 포함하는 D2D 테크닉이다. 디스커버리는 eNodeB 지원(eNodeB-assisted) 디스커버리 또는 오픈 디스커버리일 수 있다. eNodeB 지원 디스커버리에서, 제1 UE는 신호

(예를 들어, 사운딩 참조 신호(sounding reference signal, SRS))를 송신하도록 지시되고, 제2 UE는 신호를 수신하여 신호 품질을 eNodeB에게 보고하도록 요구된다. eNodeB는, 보고된 신호 품질에 기반하여, ProSe가 이 두 개의 UE에 대해서 가능하게 될지 결정할 수 있다. 오픈 디스커버리에서, 임의의 UE는 다른 UE에게 자신의 존재를 알리기 위해서 비콘 신호(beacon signal)과 같은 신호를 송신할 수 있다. 명심해야 할 것은, 이 프로세스가 아이들(idle) UE를 포함할 수 있다는 것이다.

[0015] 오픈 디스커버리가 아이들 UE를 포함할 수 있음을 감안할 때, 오픈 디스커버리는 일반적으로, 매우 제한된 가용 정보로 수행될 수 있다. 특히, 아이들 UE는 일반적으로 eNodeB에 의해 방송된 정보에 의존해야 한다. 이러한 아이들 UE를 웨이크업(wake up)하고 UE에게 무선 자원 제어(radio resource control, RRC) 시그널링을 송신하는 것은 대부분의 상황에서 비용이 많이 들 수 있다. 게다가, 아이들 UE의 위치는 가깝고, 아이들 UE가 모여 있는(camping) 정확한 셀은 통신 시스템에 의해서 알려지지 않는다.

[0016] D2D 통신에서, 간섭이 상향링크(uplink, UL) 상에서 셀룰러 UE에게 덜 편파적이기 때문에, D2D는 대역폭의 UL 부분(portion)에서 발생한다고 일반적으로 가정된다. UL 상에서, 송신하는 D2D UE는 eNodeB에게 간섭을 준다. 결과적으로, D2D UE가 eNodeB로부터 합리적인 거리에 위치할수록, D2D UE에 의해 생성된 간섭은 영향을 거의 갖지 않는다. 반대로, UL 상에서, D2D 간섭은 이웃 UE에 영향을 미치고, 잠재적으로 동기 채널 및 PDCCH를 수신하는 이웃 UE의 능력이 영향을 받으며, D2D UE가 UL 상에서 송신했을 때보다 훨씬 더 큰 영향을 줄 수 있다.

[0017] D2D 통신이 UL 상에서 발생함을 감안하면, D2D 디스커버리도 UL 상에서 발생한다고 가정하는 것이 합리적이다. 오픈 디스커버리에 대해서, 주어진 개수의 서브프레임(예를 들어, 1%)이 디스커버리를 위해서 확보된다. 이 서브프레임 동안, 보통 셀룰러 통신은 전혀 없다. 오직 UE 디스커버리 신호만이 송신된다. 도 2는 서브프레임(200)의 예를 도시한다. 몇몇 서브프레임(200)은 디스커버리 서브프레임(크로스 해칭된 박스로 도시됨)으로 사용되고, 다른 서브프레임은 셀룰러 서브프레임(음영이 없는 박스로 도시됨)으로 사용된다.

[0018] 실시예에 따르면, D2D 동기 신호의 예가 제공된다. D2DSS의 설계 원칙은 하나 또는 그 이상의 아래 사항을 포함할 수 있다.

- (예를 들어, ZC 시퀀스에 기반한) 종래 PSS와 같은, 좋은 자기-상관 및 상호-상관 특성을 갖는다.

- D2D UE 및 막 커진 셀룰러 UE 간의 모호함을 유발하지 않도록 종래 PSS와 다르다.

- D2D 신호가 UL 스펙트럼/서브프레임에서 전송될 것이기 때문에, 상향링크 변조 참조 신호(demodulation reference signal, DMRS)와 같은 상향링크 신호와의 오버랩과 관련한 좋은 상호 상관 특성을 갖는다.

- D2D UE가 D2D 구성 정보(configuration information)를 신속하게 획득할 수 있게 하는, D2D 동작 파라미터를 가능한한 지시한다.

- LTE 시스템에서 PSS 및/또는 SSS가 코스(coarse)한 시간 및/또는 주파수 동기만을 제공할 수 있는 반면, D2DSS에 기반하여 파인(fine)한 시간 및/또는 주파수 동기를 가능한한 지원한다.

[0024] 추가로, 레거시 UE가 D2DSS를 탐지할 수 없을 것이기 때문에, 레거시 UE가 D2D UE(D2DSS의 소스)를 eNodeB라고 실수로 가정하는 것을 방지할 수 있도록, 하위 호환성이 보증될 수 있다. 명심해야 할 것은, 여기에 설명된 실시예는 결합될 수 있다는 것이다.

[0025] 게다가, D2DSS의 탐지는 일반적으로, 예를 들어, 수신된 신호 및 D2DSS 사이의 상관을 결정하는 것과 같이 수신기 내의 매칭되는 필터링의 몇 가지 유형을 포함한다. D2DSS의 탐지가 많은 양의 복소 값 연산의 수행을 내포하기 때문에, D2DSS가 탐지 복잡도(detection complexity)를 줄이기 위해 사용될 수 있는 신호 특성을 보이도록 D2DSS를 설계하는 것이 목적이다.

[0026] 도 3은 D2D UE에서 일어나는 동작(300) 실시예의 흐름도를 도시한다. 동작(300)은 D2D UE에서 일어나는 동작을 나타낼 수 있다.

[0027] 동작(300)은 D2D UE가 D2DSS를 생성하는 단계(블록 305)로부터 시작할 수 있다. D2D UE는 D2DSS에 대한 시퀀스를 생성할 수 있다(예를 들어, PD2DSS 및/또는 SD2DSS). D2DSS의 실시예의 세부 사항은 아래에 나타나 있다. D2D UE는 매핑된 D2DSS를 생성하기 위해서, D2DSS의 시퀀스를 매핑할 수 있다(블록 310). D2D UE는, 예를 들어, D2DSS가 중심 대칭(centrally symmetric)이 될 수 있도록 D2DSS의 시퀀스를 서브캐리어에 매핑할 수 있다. D2D UE는 매핑된 D2DSS를 송신할 수 있다(블록 315). 앞에서 논의된 대로, 매핑된 D2DSS는 UL 자원 또는 서브프레임 내에서 송신될 수 있다.

- [0028] 실시예에 따르면, D2DSS는 통신 시스템에서 사용되는 다른 ZC 시퀀스의 길이와 다른 길이를 갖는 ZC 시퀀스에 기반할 수 있다. 동기 소스는 D2D UE(D2D 그룹을 구성하는)의 그룹이 시간 및/또는 주파수 동기를 얻는 기반이 되는 D2DSS를 송신한다. D2DSS는 적어도 주 D2DSS(primary D2DSS, PD2DSS)를 포함할 수 있고, 여기서 PD2DSS는 제1 ZC 시퀀스로부터 생성되고, 제1 ZC 시퀀스의 길이는, UE에 의해 보내진 기존 UL 참조 신호(DMRS 및 SRS를 포함하는)를 생성하기 위해 사용되는 임의의 가능한 ZC 시퀀스의 길이뿐만 아니라, eNodeB에 의해 보내진 레거시 LTE PSS를 생성하기 위해 사용되는 제2 ZC 시퀀스의 길이(레거시 LTE PSS를 생성하기 위해 사용되는 ZC 시퀀스는 63 시퀀스 길이이고, ZC 시퀀스의 중앙의 원소(central element)는 62 시퀀스 길이를 만들어 내기 위해 천공(punctured)됨)와 서로 다르다.

- [0029] 제1 실시예에서, 동기 소스, eNodeB 또는 D2D UE 중 하나는, D2D UE(D2D 그룹을 구성하는)의 그룹이 시간 및/또는 주파수 동기를 얻는 기반이 되는 D2DSS를 송신한다. D2DSS는 적어도 주 D2DSS(primary D2DSS, PD2DSS)를 포함해야 하고, 여기서 PD2DSS는 제1 ZC 시퀀스로부터 생성되고, 제1 ZC 시퀀스의 길이는, 레거시 LTE PSS를 생성하기 위해 사용되는 제2 ZC 시퀀스의 길이와 서로 다르다. 다른 길이의 ZC 시퀀스의 사용은 D2D UE를 eNodeB로 오탐(false detection)하지 않도록 보증한다. 다시 말해서, PD2DSS가 PSS로 오인되지 않을 것이다. 게다가, ZC 시퀀스 길이는 UE에 의해 보내지는 기존 UL 참조 신호(DMRS 및 SRS를 포함함)를 생성하기 위해 사용되는 임의의 가능한 길이의 ZC 시퀀스와 서로 다르다.

- [0030] 더 나아가, 제1 ZC 시퀀스의 길이는 소수(prime number)이거나, 또는 제1 ZC 시퀀스의 길이의 두 번째로 작은 양의 약수가 3보다 큰 숫자이어야 한다.

- [0031] 도 4는 D2D UE가 D2DSS를 생성하는 경우 D2D UE에서 일어나는 동작(400) 실시예의 흐름도를 도시한다. 동작(400)은 D2D UE가 D2DSS를 생성하는 경우 D2D UE에서 일어나는 동작을 나타낼 수 있다.

- [0032] 동작(400)은 D2D UE가 레거시 LTE PSS를 생성하기 위해 사용되는 제2 ZC 시퀀스의 길이와 서로 다른 길이를 갖는 제1 ZC 시퀀스를 선택하는 단계로부터 시작할 수 있다(블록 405). 더 나아가, 제1 ZC 시퀀스의 길이는, UL 참조 신호(DMRS 및 SRS를 포함하는)와 같은, D2D UE에 의해 송신되는 기존 신호를 생성하기 위해 사용되는 다른 ZC 시퀀스의 길이와도 서로 다르다. 또한, 제1 ZC 시퀀스의 길이는 소수이거나, 또는 제1 ZC 시퀀스의 길이의 두 번째로 작은 양의 약수가 2보다 큰 숫자일 수 있다. D2D UE는 제1 ZC 시퀀스를 사용하여 D2DSS를 생성할 수 있다(블록 410).

- [0033] 여기에 설명된 동작(400)은 D2DSS를 생성하는 D2D UE에 초점을 맞추고 있다. 하지만, D2D UE를 위해 D2DSS를 생성하고 D2D UE에게 D2DSS를 제공하는 통신 시스템 내의 다른 엔티티(entity)에 대해서도 적용될 수 있다. 동작(400)은 통신 시스템 내의 임의의 엔티티에 의해 수행될 수 있다. 그러므로, 동작(400)을 수행하는 D2D UE에 대한 논의는 실시예의 범위 또는 사상을 제한하는 것으로 해석되어서는 안 된다.

- [0034] 상기 설명에 기반하여, D2DSS(예를 들어, PD2DSS)로 사용되는 ZC 시퀀스의 길이는, 동기 소스가 주파수 도메인의 6개의 물리 자원 블록(physical resource blocks, PRBs)(레거시 LTE PSS와 같이 72개의 서브캐리어) 내에서 PD2DSS를 송신한다는 가정 하에 도출될 수 있다. ZC 시퀀스의 길이는 아래 원칙에 기반하여 결정될 수 있다.

- 소수이거나, 또는 ZC 시퀀스의 길이의 두 번째로 작은 양의 약수가 3보다 큰 숫자이다.

- [0036] - 63(레거시 LTE PSS로 사용되는 ZC 시퀀스의 길이)이 아니다.

- [0037] - UL DMRS로 사용되는 ZC 시퀀스의 가능한 길이인, 71, 31, 또는 47이 아니다.

- [0038] 모든 원칙이 충족되는 경우, 제1 ZC 시퀀스의 길이는 61, 65, 또는 67일 수 있다. 명심해야 할 것은, 67은 72보다 크지 않고 위 원칙을 만족하는 최대 값이라는 것이고, 61은 64보다 크지 않고 위 원칙을 만족하는 최대 값이라는 것이며, 65는 두 번째로 작은 양의 약수가 5이고 위 원칙을 만족하는 값이라는 것이다. 일반적인 수신기에서, 샘플링 레이트(sampling rate)는 예를 들어, 2의 거듭제곱과 같은 특정 값만을 가질 수 있다. 설명에 도움이 되는 예시로서, 시퀀스 길이가 최대 64이면, 64개 샘플의 수신기 윈도우가 사용될 수 있고, 유사하게, 시퀀스 길이가 64보다 크고 128보다 작으면, 128 샘플의 수신기 윈도우가 사용될 수 있다. 수신기 윈도우 길이는 PD2DSS를 탐지하기 위해 필요한 복소값 연산의 수량과 관련이 있다. 61과 67을 가능한 길이 값으로 비교하면, 제1 ZC 시퀀스의 길이가 61이면, 오직 64개의 복소 샘플이 PD2DSS 마다 필요하고, 복잡도가 낮아진다. 제1 ZC 시퀀스의 길이가 67이면, 128개의 복소 샘플이 PD2DSS 마다 필요하고, 복잡도가 높아진다. 반면에, 제1 ZC 시퀀스의 길이가 67인 경우에는 낮은 상호-상관이 획득될 수 있다. 그러므로, 길이는 그것이 성능을 상당히 향상시키는지 여부가 고려되어야 한다.

[0039] 홀수 길이(예를 들어, N=61)인 ZC 시퀀스는,

$$x_u(m) = e^{-j\frac{\pi um(m+1)}{N}}, \quad 0 \leq m \leq N-1$$

[0040] [0041] 로 정의되고, u는  $0 < u \leq N-1$  인 루트 인덱스이다.

[0042] PD2DSS에 대한 후보 루트 인덱스들은 레거시 PSS와 가능한한 낮은 상호 상관을 획득하도록 선택되어야 한다. 즉, 후보 인덱스들은 {4, 7, 9, 11, 13, 15, 16, 17, 18, 19, 23, 29, 32, 38, 42, 43, 44, 45, 46, 48, 50, 52, 54, 57} 내에서 선택되어야 한다.

[0043] 동기 소스는 적어도 D2DSS를 포함할 수 있고, D2DSS는 제2 D2DSS(SD2DSS)를 포함해야 하며, SD2DSS는 제1 m-시퀀스에 의해 생성되고, SD2DSS의 길이는 eNodeB에 의해 보내지는 레거시 SSS의 길이 및/또는 제1 ZC 시퀀스의 길이와 서로 달라야 한다. 이것은 더 나은 동기를 보증하고, 송신 노드가 커버리지 바깥에 있는 경우에도 프레임 인덱스 또는 그와 동등한 것과 같은 추가 정보를 송신할 수 있도록 한다. 게다가, 시퀀스 길이 및 SD2DSS의 대역폭은 PD2DSS에 대한 것과 같거나 더 커야 한다.

[0044] 제1 ZC 시퀀스의 루트 인덱스는 아래 중 적어도 하나에 따라서 결정될 수 있다.

[0045] - SD2DSS의 대역폭이다.

[0046] - 제1 ZC 시퀀스 및/또는 제1 m-시퀀스의 루트 인덱스는 아래 측면의 적어도 하나에 따라서 결정된다.

[0047] - D2D 동작 대역폭(operating bandwidth)이다.

[0048] - 예를 들어, 소스가 D2D UE인 경우 UE-ID와 같은, 동기 소스의 아이덴티티(identity)이다.

[0049] - eNodeB 또는 D2D UE를 포함하는, 동기 소스의 유형이다.

[0050] - 동기 소스의 우선 순위(priority)이다.

[0051] - D2D UE 그룹의 아이덴티티이다.

[0052] - D2D UE 그룹의 유형이다.

[0053] - D2D UE 그룹의 우선 순위이다.

[0054] PD2DSS(위에서 언급된 모든 후보 중에서)에 대한 ZC 시퀀스의 루트 인덱스는 또한, 본 D2D 그룹의 D2D 동작 대역폭뿐만 아니라, 대응하는 SD2DSS의 위치 및/또는 대역폭과 관련된 정보를 전달할 수 있고, 여기서 후보 대역폭은 1.4MHz, 3MHz, 5MHz, 10MHz, 15MHz, 또는 20MHz (6RB, 15RB, 25RB, 50RB, 75RB, 또는 100RB, 여기서 RB는 LTE 시스템에서 정의된 자원 블록임)를 포함한다. 상기 지시의 사용 예시가 아래 표 1에 도시된다. 표 1은 PD2DSS에 대한 루트 인덱스 및 SD2DSS의 대응하는 대역폭이다.

**표 1**

| Bandwidth | Root index |

|-----------|------------|

| 6RB       | 19         |

| 15RB      | 23         |

| 25RB      | 29         |

| 50RB      | 32         |

| 75RB      | 38         |

| 100RB     | 42         |

[0055] [0056] 이 상황에서, SD2DSS의 길이 및 대역폭은 PD2DSS의 그것과 각각 서로 다를 수 있다. 명심해야 할 것은, SD2DSS의 더 큰 대역폭(PD2DSS의 그것에 비해서)은 D2D 그룹 내의 D2D UE들이 미세한(fine) 시간 및/또는 주파수 동기를 획득하는데 도움을 줄 수 있다는 것이고, LTE 통신 시스템의 PSS 및/또는 SSS의 설계 목표와 다르다는 것이다.

[0057] 한 실시예에 따르면, D2DSS는 ZC 시퀀스에 대한 다른 루트 인덱스를 갖는 ZC 시퀀스에 기반한다. 일반적으로, 하나의 시퀀스로부터 생성되지만 다른 루트 인덱스를 갖는 두 개의 시퀀스는 다른 시퀀스가 될 수 있다. 동기

소스가 주파수 도메인 내의 6개의 PRB(레거시 LTE PSS와 같이 72개의 서브캐리어) 내에서 PD2DSS를 송신한다고 가정하는 것으로부터 다른 해결책이 얻어질 수 있다. PD2DSS에 대한 제1 ZC 시퀀스는 아래 원칙에 기초하여 결정될 수 있다.

- [0058] - 소수이거나 또는 그것의 두 번째로 작은 양의 약수가 3보다 큰 숫자이다.

- [0059] - 길이는 71이고, 여기서 71은 6 PRB 전송을 위한 UL DMRS의 가능한 길이이다.

- [0060] - 루트 인덱스는 6 PRB 전송을 위한 UL DMRS에 의해 사용되는 루트 인덱스와 달라야 한다.

- [0061] - 모든 원칙이 충족되는 경우, 제1 ZC 시퀀스의 길이는 71이 될 수 있다. 제1 ZC 시퀀스의 후보 루트 인덱스는 세트 {0, 1, 8, 15, 24, 31, 40, 47, 56, 63} 내에서 선택되어야 한다.

[0062] 도 5는 D2D UE가 다른 루트 인덱스를 갖는 ZC 시퀀스에 따라서 D2DSS를 TOID성하는 경우 D2D UE에서 일어나는 동작(500) 실시예의 흐름도를 도시한다. 동작(500)은 D2D UE가 다른 루트 인덱스를 갖는 ZC 시퀀스에 따라서 D2DSS를 생성하는 경우 D2D UE에서 일어나는 동작을 나타낼 수 있다.

[0063] 동작(500)은 D2D UE가 레거시 LTE PSS를 생성하기 위해 사용되는 제2 ZC 시퀀스의 루트 인덱스와 다른 루트 인덱스를 갖는 제1 ZC 시퀀스를 선택하는 단계로부터 시작할 수 있다(블록 505). 더 나아가, 제1 ZC 시퀀스의 루트 인덱스는 또한, UL 참조 신호(DMRS 및 SRS를 포함하는)와 같이, D2D UE에 의해 송신되는 기준 신호를 생성하기 위해 사용되는 다른 ZC 시퀀스의 루트 인덱스와도 다르다. 또한, 제1 ZC 시퀀스의 길이는 UL DMRS를 생성하기 위해 사용되는 시퀀스의 길이가 될 수 있다. D2D UE는 제1 ZC 시퀀스를 사용하여 D2DSS를 생성할 수 있다.

[0064] 여기에서 설명된 동작(500)은, D2DSS를 생성하는 D2D UE에 초점을 맞추고 있다. 하지만, D2D UE를 위해 D2DSS를 생성하고 D2D UE에게 D2DSS를 제공하는 통신 시스템 내의 다른 엔티티(entity)에 대해서도 적용될 수 있다. 동작(500)은 통신 시스템 내의 임의의 엔티티에 의해 수행될 수 있다. 그러므로, 동작(500)을 수행하는 D2D UE에 대한 논의는 실시예의 범위 또는 사상을 제한하는 것으로 해석되어서는 안 된다.

[0065] 게다가, D2DSS는 또한 보조 D2DSS(secondary D2DSS, SD2DSS)를 포함할 수 있고, 여기서 SD2DSS는 m-시퀀스에 의해 생성되며, SD2DSS의 길이 및 점유된 대역폭은 eNodeB에 의해 보내지는 레거시 SSS의 그것과 다르다.

[0066] PD2DSS(위에서 언급된 모든 후보 중에서)에 대한 ZC 시퀀스의 루트 인덱스는 또한, 본 D2D 그룹의 D2D 동작 대역폭뿐만 아니라, 대응하는 SD2DSS의 위치 및/또는 대역폭의 정보를 또한 전달할 수 있고, 여기서 후보 대역폭은 1.4MHz, 3MHz, 5MHz, 10MHz, 15MHz 또는 20MHz (6RB, 15RB, 25RB, 50RB, 75RB, 100RB, 여기서 RB는 LTE 시스템에서 정의된 자원 블록임)를 포함한다. 상기 지시의 사용 예시가 아래 표 2에 도시된다. 표 2는 PD2DSS에 대한 루트 인덱스 및 SD2DSS의 대응하는 대역폭이다.

## 표 2

| Bandwidth | Root index |

|-----------|------------|

| 6RB       | 15         |

| 15RB      | 24         |

| 25RB      | 31         |

| 50RB      | 40         |

| 75RB      | 47         |

| 100RB     | 56         |

[0068] 이 상황에서, SD2DSS의 길이 및 대역폭은 PD2DSS의 그것과 각각 서로 다를 수 있다. 명심해야 할 것은, SD2DSS의 더 큰 대역폭(PD2DSS의 그것에 비해서)은 D2D 그룹 내의 D2D UE들이 미세한(fine) 시간 및/또는 주파수 동기를 획득하는데 도움을 줄 수 있다는 것이고, LTE 통신 시스템의 PSS 및/또는 SSS의 설계 목표와 다르다는 것이다. PD2DSS 신호 매핑에 관하여, PD2DSS는 주파수 도메인(푸리에) 계수의 세트의 변환으로서 획득될 수 있다. 제한 없는(non-limiting) 예시로서, 이산 시간-도메인 기저 대역 신호(base band signal)가 아래와 같이 획득되고 가정한다.

$$s_u[k] = \frac{1}{N} \sum_{n=0}^{N-1} H_u[n] W_N^{-kn}, k = 0, 1, \dots, N-1$$

[0069]

[0070] 그리고, 푸리에 주파수 계수(Fourier frequency coefficient)의 세트  $H_u[l], l = 0, 1, \dots, N - 1$ 에 대해서,  $W_N = \exp\left(-\frac{j2\pi}{N}\right), j = \sqrt{-1}$  이다.

[0071] 시퀀스  $x_u(l), 0 \leq l \leq L - 1$  where  $L \leq N$  이,  $H_u[l] = H_u[N - l], l = 1, \dots, N - 1$  와 같은 푸리에 주파수 계수의 세트에 매핑되는 경우, 신호가, 예를 들어,  $|s_u[k]| = |s_u[N - k]|, k = 1, \dots, N - 1$  와 같이 중심 대칭이 되도록 보여질 수 있다. 즉, 푸리에 계수는 DC 서브캐리어 주변에 대칭이 되도록 매핑되어야 한다. PSS는 대칭 시퀀스, 즉, 천공된 길이 63의 ZC 시퀀스로부터 획득되고,  $s_u[k] = s_u[N - k], k = 1, \dots, N - 1$  에 따라서 중심 대칭이라는 결과를 낳는다. 중심 대칭 특성은, 수신된 신호 및 PD2DSS의 상관을 수행할 때 수신기에서 복소값 연산의 양을 줄이기 위해서 사용될 수 있기 때문에 유리하다. 예를 들어, 상관 값을 결정할 때, D2DSS의 복제 샘플(replica sample)의 곱셈 연산 수행 이전에 대칭 샘플이 수신기에 추가될 수 있고, 그에 의해 복소값 연산의 양을 거의 50% 정도 줄일 수 있다. 더욱이, 복소 결례 쌍을 구성하는 두 개의 시퀀스, 즉,  $x_u(l) = x_v^*(l), 0 \leq l \leq L - 1$  가 존재하고,

신호가 중심 대칭이라면,  $s_u[k] = s_v^*[k], k = 1, \dots, N - 1$  이 된다. 이 특성은 또한, 이러한 두 신호를 병렬로 검출할 때 복소값 연산의 개수를 줄이기 위해서 수신기에서 사용될 수 있다.

[0072] 설명에 도움이 되는 예시로서, 대응하는 연속 기저 대역(continuous base band) OFDM 신호(순환 전치(cyclic prefix)를 배제하고)가 아래에 의해 생성된다(이산 푸리에 변환  $H_u[l] = H_u[N + l], l = 0, 1, \dots, N - 1$  의 주기를 사용함):

$$s_u(t) = \sum_{k=-N/2}^{N/2-1} H_u[k] \cdot e^{j2\pi k \Delta f t}, 0 \leq t < \frac{1}{\Delta f} = N \cdot T_s$$

[0073] 여기서,  $T_s$  는 샘플링 주기(sampling period),  $\Delta f$  는 서브캐리어 간격(subcarrier spacing)이며,  $N = 1/T_s \Delta f$ 이다. 동등하게,  $N$  은 OFDM 심호의 서브캐리어의 개수이다. 표기의 단순화를 위해서,  $N$  은 짹수로 가정되고, 표시는 홀수  $N$  으로 일반화될 수 있다. 종래 기술 LTE 통신 시스템에서,  $\Delta f = 15 \text{ kHz}$ 에 대해  $N = 2048$  이다. 많은 실제 OFDM 통신 시스템에서, DC 서브캐리어는 변조되지 않고, 즉,  $H_u[0] = 0$ 이며, 합계(sum)의 한계(limits) 및 인덱싱(indexing)은 적절하게 변경될 수 있다.

[0075] 한 실시예에 따르면, 중심 대칭 신호를 획득하기 위해서 PD2DSS가  $H_u[l] = H_u[N - l], l = 1, \dots, N - 1$  과 같은 푸리에 계수에 매칭된다.

[0076] 다른 설명에 도움이 되는 예시에서, 대응하는 연속 기저 대역 OFDM 신호(순환 전치를 배제하고)는 아래에 의해 생성된다(이산 푸리에 변환  $H_u[l] = H_u[N + l], l = 0, 1, \dots, N - 1$  의 주기를 사용함):

$$s_u(t) = \sum_{k=-N/2}^{N/2-1} H_u[k] \cdot e^{j2\pi(k+\delta)\Delta f t}, 0 \leq t < \frac{1}{\Delta f} = N \cdot T_s$$

[0078] 여기서,  $T_s$  는 샘플링 주기(sampling period),  $\Delta f$  는 서브캐리어 간격(subcarrier spacing)이고,  $N = 1/T_s \Delta f$  이고,  $-1 < \delta < 1$  이다. 한 실시예에 따르면, 이 신호 파형에 대한 동기 신호는  $\delta \neq 0$  일

경우 설계된다. 이러한 신호 생성의 형태는  $\delta = 1/2$  인 LTE 통신 시스템의 UL에서 사용되고 있고 여기서 DC 서브캐리어는 변조될 수 있으며, 그것은 SC-FDMA 신호 파형으로 지정된다. 오프셋  $\delta$ 는 DC 서브캐리어의 변조로 인한 수신기 내의 왜곡의 영향을 최소화하기 위해서 도입될 수 있다. 명심해야 할 것은,  $\delta = 1/2$ 이고, 푸리에 계수가 DC 서브캐리어( $k = 0$ ) 주변에서 대칭일 때, 예를 들어, 중심 대칭 신호  $s_u[k] = -s_u[N-k]$ ,  $k = 1, \dots, N-1$  가 획득된다는 것이다. 이것은 대칭 시퀀스를 이용하여 획득될 수 있고, 여기서  $L$ 은 짝수인 정수이다. 위의 파형은 DC 서브캐리어 주위의 푸리에 계수에 대칭적으로 매핑되는 시퀀스에 대해서 중앙 대칭을 획득하기 위해서 거리  $t = n \cdot T_s$ 에서 샘플링될 수 있다. 중앙 대칭은 음수 사인(negative sign)에서 PSS의 그것과 다르다. 그러나, 중앙 대칭의 이 파형은 수신기 복잡도 측면의 감소를 여전히 보유하고 있다. 연속하는 서브캐리어의 세트가 변조될 수 있고, PSS에 대해서, DC 서브캐리어는 변조되지 않은채 남아있기 때문에, 동기 시퀀스의 매핑이 PSS의 그것과 다르다는 것도 또한 실현된다. 실시예의 한 가지 유리한 점은, 단일 캐리어 주파수 분할 다중 접속(single carrier frequency division multiple access, SC-FDMA)에 기반하여 기존 송신기 및 수신기 메커니즘을 사용하여 동시에, PD2DSS를 위한 UE 내의 수신기 복잡도가 감소될 수 있다는 것이다.

[0079]

한 실시예에 따르면, 시간-도메인 대칭 PD2DSS SC-FDMA 신호가 생성된다.

[0080]

한 실시예에서,  $L$ 이 짝수인 정수값이고  $d(n) = d(L-1-n)$ 인 시퀀스  $d(n), 0 \leq n < L-1$ 은, 푸리에 계수의 세트  $H_u[l], l = 0, 1, \dots, N-1$ 에 연속적으로 매핑되고, 여기서 푸리에 스펙트럼  $s_u(t)$ 는,  $\delta \neq 0$ 이고 정수값  $k$ (예를 들어,  $k = -\frac{N}{2}, \dots, \frac{N}{2} - 1$ )의 세트에 대해, 주파수  $(k + \delta)\Delta f$ 에서 대칭으로 된다.

[0081]

실시예로서,  $\delta = 1/2$ 인 주파수  $\delta\Delta f$ 에 대응하는 푸리에 계수  $H_u[0]$ 은 주파수  $-\delta\Delta f$ 의 푸리에 계수  $H_u[-1]$ 와 동일해야 하고, 주파수  $\frac{3}{2}\Delta f$ 에 대응하는 푸리에 계수  $H_u[1]$ 은 주파수  $-\frac{3}{2}\Delta f$ 의 푸리에 계수  $H_u[-2]$ 와 동일해야 한다.

[0082]

한 실시예에서, 시퀀스  $d(n)$ 은 PD2DSS로서 사용되고, 아래 표현에 따른 주파수-도메인 자도프-추(Zadoff-Chu) 시퀀스로부터 생성된다:

$$d_u(n) = \begin{cases} e^{-j\frac{\pi m(n+1)}{63}} & n = 0, 1, \dots, 30 \\ e^{-j\frac{\pi u(n+1)(n+2)}{63}} & n = 31, 32, \dots, 61 \end{cases}$$

[0083]

길이 62인 시퀀스  $d_u(n)$ 는 아래 표현에 따라서 매핑될 수 있다:

$$H_u[k] = d(n), \quad n = 0, \dots, 61$$

$$k = n - 31$$

[0085]

시퀀스  $d(n)$ 은 길이 62의 천공된 ZC 시퀀스이고, 길이 63인 ZC 시퀀스로부터 획득된다.

- [0087] 한 실시예에 따르면, 디스커버리 시퀀스는 PSS와 동일한 위치에서 사용되지만, 레거시 UE가 eNodeB 대신에 UE와 동기화하는 것을 피하기 위해서 다른 길이 및/또는 루트 인덱스를 갖는다. 한 실시예는 PSS를 위한 위치 매핑을 제공한다. 한 실시예는 하드웨어 설계, 표준화 작업 등을 단순화하기 위하여 기존 LTE 동기 설계와 함께 동작한다. 한 실시예는 또한 레거시 UE로 하여금 D2D UE가 사용되는 네트워크에서 계속하여 동작할 수 있도록 허용한다.

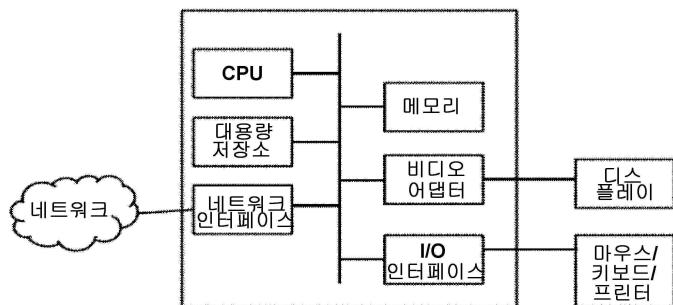

- [0088] 도 6은 여기서 설명된 장치 및 방법을 구현하기 위해 사용될 수 있는 프로세싱 시스템(600)의 블록도이다. 특정 장치가 도시도니 모든 구성요소를 사용할 수도 있고, 또는 구성요소의 서브세트 만을 사용할 수도 있으며, 통합 레벨은 장치마다 매우 다를 수 있다.

- [0089] 더 나아가, 장치는 복수의 프로세싱 유닛, 프로세서, 메모리, 송신기, 수신기, 등 다양한 구성요소의 예시를 담고 있을 수 있다. 프로세싱 시스템은 스피커, 마이크로폰, 마우스, 터치스크린, 키패드, 키보드, 프린터, 디스플레이, 기타 등등의 하나 또는 그 이상의 입력/출력 장치들이 갖춰진 프로세싱 유닛을 포함할 수 있다. 프로세싱 유닛은 중앙 처리 유닛(central processing unit, CPU), 메모리, 대용량 저장 장치, 비디오 어댑터, 그리고 버스에 연결된 I/O 인터페이스를 포함할 수 있다.

- [0090] 버스는, 메모리 버스 또는 메모리 컨트롤러(controller), 주변 버스(peripheral bus), 비디오 버스, 기타 등등을 포함하는 몇 가지 버스 아키텍처의 하나 또는 그 이상의 임의의 유형일 수 있다. CPU는 전자적 데이터 프로세서의 임의의 유형을 포함할 수 있다. 메모리는 정적 랜덤 액세스 메모리(static random access memory, SRAM), 동적 랜덤 액세스 메모리(dynamic random access memory, DRAM), 동기식 DRAM(synchronous DRAM, SDRAM), 읽기 전용 메모리(read-only memory, ROM), 그들의 조합, 기타 등등과 같은 시스템 메모리의 임의의 유형을 포함할 수 있다. 한 실시예에서, 메모리는 부트-업(boot-up)에서의 사용을 목적으로 ROM을 포함할 수 있고, 프로그램을 실행하는 동안의 사용을 목적으로 한 프로그램 및 데이터 저장소로서 DRAM을 포함할 수 있다.

- [0091] 대용량 저장 장치는 데이터, 프로그램, 다른 정보를 저장하고, 버스를 거쳐서 데이터, 프로그램, 그리고 다른 정보에 접근할 수 있도록 구성된 저장 장치의 임의의 유형을 포함할 수 있다. 대용량 저장 장치는 예를 들어, 하나 또는 그 이상의 고체 상태 드라이브(solid state drive), 하드 디스크 드라이브(hard disk drive), 마그네틱 디스크 드라이브(magnetic disk drive), 광학 디스크 드라이브(optical disk drive), 기타 등등을 포함할 수 있다.

- [0092] 비디오 어댑터 및 I/O 인터페이스는 외부의 입력 및 출력 장치를 프로세싱 유닛에 연결하는 인터페이스를 제공한다. 도시된 대로, 입력 및 출력 장치의 예시는 비디오 어댑터에 연결된 디스플레이, I/O 인터페이스에 연결된 마우스/키보드/프린터를 포함한다. 다른 장치는 프로세싱 유닛에 연결될 수 있고, 추가적인 또는 보다 소수의 인터페이스 카드가 사용될 수 있다. 예를 들어, 유니버설 직렬 버스(universal serial bus, USB)(미도시)와 같은 직렬 인터페이스가 프린터에게 인터페이스를 제공하기 위해서 사용될 수 있다.

- [0093] 프로세싱 유닛은, 이더넷(Ethernet) 케이블 등과 같은 유선 링크(wired link), 및/또는 액세스 노드 또는 다른 네트워크로 향하는 무선 링크를 포함할 수 있는 하나 또는 그 이상의 네트워크 인터페이스를 포함한다. 네트워크 인터페이스는 프로세싱 유닛이 네트워크를 거쳐서 원격의 유닛들과 통신할 수 있도록 한다. 예를 들어, 네트워크 인터페이스는 하나 또는 그 이상의 송신기/송신 안테나 및 하나 또는 그 이상의 수신기/수신 안테나를 거쳐서 무선 통신을 제공할 수 있다. 한 실시예에서, 프로세싱 유닛은 다른 프로세싱 유닛, 인터넷, 원격 저장 시설, 기타 등등과 같은 원격 장치와 통신하고 데이터 프로세싱을 위해서 로컬 영역 네트워크(local-area network) 또는 광역 네트워크(wide-area network)와 연결된다.

- [0094] 도 7은 D2DSS를 사용하여 동기화하는 D2D 통신 장치에서 일어나는 동작(700) 실시예의 흐름도를 도시한다. 동작(700)은 상기 장치가 D2DSS를 사용하여 동기화하는 경우 D2D 통신 장치에서 일어나는 동작을 나타낼 수 있다.

- [0095] 동작(700)은 D2D 통신 장치가 복수의 PRB를 수신하는 단계로부터 시작할 수 있다(블록 705). 복수의 PRB 내에 포함된 것은 PD2DSS일 수 있다. PD2DSS는 여기서 설명된 방법과 같은 기술을 사용하여 생성될 수 있다. PD2DSS는 SC-FDMA 파형에서 송신될 수 있다. 복수의 PRB는 또한 SD2DSS를 포함할 수 있다. SD2DSS는 여기서 설명된 방법과 같은 기술을 사용하여 생성될 수 있다. D2D 통신 장치는 PD2DSS를 탐지할 수 있다(710). D2D 통신 장치는 SD2DSS도 또한 탐지할 수 있다. D2D 통신 장치는 PD2DSS(그리고 잠재적으로 SD2DSS)를 사용하여 동기화할 수 있다(블록 715).

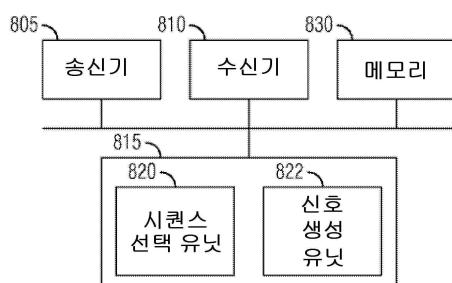

- [0096] 도 8은 통신 장치(800)의 실시예를 도시한다. 통신 장치(800)는 D2D UE와 같은 D2D 동기 소스로서 동작하는 장치의 구현일 수 있다. 통신 장치(800)는 여기서 설명된 다양한 실시예를 구현하기 위해서 사용될 수 있다. 도 8

에 도시된 대로, 송신기(805)는 패킷, D2DSS, PD2DSS, SD2DSS, 기타 등을 송신하도록 구성된다. 통신 장치(800)는 또한 패킷 등을 수신하도록 구성된 수신기(810)를 포함한다.

[0097] 시퀀스 선택 유닛(820)은 D2DSS를 얻기 위해 사용되는 시퀀스를 선택하도록 구성된다. 시퀀스 선택 유닛(820)은 ZC 시퀀스를 선택하도록 구성된다. 시퀀스 선택 유닛(820)은 DMRS, SRS 등과 같은, 통신 장치(800)의 상향링크에서 송신되는 다른 신호를 생성하기 위해 사용되는 시퀀스의 길이뿐만 아니라, LTE PSS를 생성하기 위해 사용되는 다른 ZC 시퀀스를 선택하도록 구성된다. 시퀀스 선택 유닛(820)은 DMRS, SRS 등과 같은, 통신 장치(800)의 상향링크에서 송신되는 다른 신호를 생성하기 위해 사용되는 시퀀스의 루트 인덱스뿐만 아니라, LTE PSS를 생성하기 위해 사용되는 다른 ZC 시퀀스의 루트 인덱스와도 서로 다른 ZC 시퀀스의 루트 인덱스를 선택하도록 구성된다. 신호 생성 유닛(822)은 시퀀스 선택 유닛(820)에 의해 선택된 시퀀스에 따라서, D2DSS, PD2DSS, SD2DSS 등을 생성하도록 구성된다. 메모리(830)는 시퀀스, ZC 시퀀스, 길이, 루트 인덱스, 신호, 기타 등을 저장하도록 구성된다.

[0098] 통신 장치(800)의 구성 요소는 특정 하드웨어 논리 블록(specific hardware logic blocks)으로서 구현될 수 있다. 또는, 통신 장치(800)의 구성 요소는 프로세서, 컨트롤러, 애플리케이션 특정 집적 회로, 기타 등등에서 실행하는 소프트웨어로서 구현될 수 있다. 또 다른 예로서, 통신 장치(800)의 구성 요소는 소프트웨어 및/또는 하드웨어의 조합으로서 구현될 수 있다.

[0099] 한 실시예로서, 수신기(810) 및 송신기(805)는 특정 하드웨어 블록으로서 구현될 수 있는 한편, 시퀀스 선택 유닛(820) 및 신호 생성 유닛(822)은 마이크로프로세서(microprocessor)(프로세서(815)와 같은) 또는 맞춤형 회로 또는 필드 프로그래머블 논리 어레이(field programmable logic array)의 맞춤 총족 논리 어레이에서 실행하는 소프트웨어 모듈일 수 있다. 시퀀스 선택 유닛(820) 및 신호 생성 유닛(822)는 메모리(830)에 저장된 모듈일 수 있다.

[0100] 비록 본 기재 및 그것의 유리한 점이 상세하게 설명되었지만, 다양한 변경, 치환 및 대체가, 부수된 클레임에 의해 정의된 대로의 개시 범위 및 사상에서 벗어나지 않고 만들어질 수 있다는 점이 이해되어야 한다.

## 도면

### 도면1

도면2

도면3

## 도면4

✓ 400

## 도면5

✓ 500

## 도면6

600 ↘

## 도면7

700 ↘

## 도면8

800 ↘