(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4671470号

(P4671470)

(45) 発行日 平成23年4月20日(2011.4.20)

(24) 登録日 平成23年1月28日(2011.1.28)

(51) Int.Cl.

F 1

H01L 23/12 (2006.01)

H01L 23/14 (2006.01)H01L 23/12

H01L 23/14L

R

請求項の数 30 (全 10 頁)

(21) 出願番号 特願2000-173780 (P2000-173780)

(22) 出願日 平成12年6月9日 (2000.6.9)

(65) 公開番号 特開2001-15643 (P2001-15643A)

(43) 公開日 平成13年1月19日 (2001.1.19)

審査請求日 平成16年11月25日 (2004.11.25)

(31) 優先権主張番号 09/330648

(32) 優先日 平成11年6月11日 (1999.6.11)

(33) 優先権主張国 米国(US)

(73) 特許権者 500271546

インテル・コーポレーション

INTEL CORPORATION

アメリカ合衆国 95051 カリフォルニア、サンタ・クララ、ウォルシュ・アベニュー 2625

(74) 代理人 100076222

弁理士 大橋 邦彦

(72) 発明者 ロンキアン・エル・ズウ

アメリカ合衆国 85045 アリゾナ、フェニックス、ウェスト・ミュアウッド・ドライブ 1502

最終頁に続く

(54) 【発明の名称】有機ランド・グリッド・アレイ・パッケージ、基板、有機基板、集積回路パッケージ及び回路アセンブリ

## (57) 【特許請求の範囲】

## 【請求項 1】

有機ランド・グリッド・アレイ・パッケージであって、

一対の導電性層を具備し、その各々がそれ自体を貫通している複数の脱ガス・アーバーチャーを有し、該一対の導電性層の内の一方の導電性層における前記アーバーチャーが第1方向及び第2方向の双方で他方の導電性層における前記アーバーチャーとオフセットされており、前記第1方向における隣接脱ガス・アーバーチャーの間隔が前記第2方向における隣接脱ガス・アーバーチャーの間隔の2倍とされており、

更に、前記一対の導電性層の間に配置された非導電性層と、

前記一対の導電性層の間に設けられた少なくとも2つの金属トレースとを具備し、それら金属トレースが略同一のインピーダンスを有する有機ランド・グリッド・アレイ・パッケージ。

## 【請求項 2】

前記第2方向が前記第1方向と実質的に直交している、請求項1に記載の有機ランド・グリッド・アレイ・パッケージ。

## 【請求項 3】

前記第1方向が経路指定方向である、請求項1に記載の有機ランド・グリッド・アレイ・パッケージ。

## 【請求項 4】

前記第2方向がファン-アウト方向である、請求項1に記載の有機ランド・グリッド・

アレイ・パッケージ。

**【請求項 5】**

前記一方の導電性層における前記アーチャーが前記他方の導電性層における前記アーチャーと前記第1方向で互い違いとなっている、請求項1に記載の有機ランド・グリッド・アレイ・パッケージ。

**【請求項 6】**

前記一方の導電性層における前記アーチャーが前記他方の導電性層における前記アーチャーと前記第2方向で互い違いとなっている、請求項1に記載の有機ランド・グリッド・アレイ・パッケージ。

**【請求項 7】**

更に、前記一対の導電性層の上に重ね合わされた少なくとも別の1つずつの非導電性層及び導電性層と、

該少なくとも1つの別の導電性層と前記一対の導電性層との間に設けられた少なくとも1つの別の金属トレース群とを具備する、請求項1に記載の有機ランド・グリッド・アレイ・パッケージ。

**【請求項 8】**

基板であって、

実質的に相互に積み重ねられた第1層及び第2層並びにこれら第1層及び第2層の間に挟まれた第3層を具備し、前記第1層及び前記第2層の各々が複数のアーチャーを有し、前記第1層における前記アーチャーの位置が第1方向で前記第2層における前記アーチャーの位置と互い違いとされ、前記第1層における前記アーチャーの位置が前記第1方向と実質的に直交する第2方向で前記第2層における前記アーチャーの位置と互い違いとされ、前記第1方向における隣接アーチャーの間隔が前記第2方向における隣接アーチャーの間隔の2倍とされており、

更に、前記第1層及び前記第2層の間に設けられた少なくとも2つの金属トレースを具備し、これら金属トレースが前記第1方向に沿って実質的に延在している基板。

**【請求項 9】**

前記金属トレースが前記第1方向に対する第1角度でファン-アウトしている、請求項8に記載の基板。

**【請求項 10】**

前記第1角度が $\pm 45^\circ$ である、請求項9に記載の基板。

**【請求項 11】**

前記アーチャーが脱ガス穴である、請求項8に記載の基板。

**【請求項 12】**

前記第1層及び前記第2層における前記アーチャーが格子形式に配列されている、請求項8に記載の基板。

**【請求項 13】**

前記第1方向が経路指定方向である、請求項8に記載の基板。

**【請求項 14】**

前記第1層におけるアーチャー間の間隔が前記第1方向において1000ミクロンであり、前記第1層におけるアーチャー間の間隔が前記第2方向で500ミクロンである、請求項8に記載の基板。

**【請求項 15】**

前記第2層におけるアーチャー間の間隔が前記第1方向において1000ミクロンである、請求項8に記載の基板。

**【請求項 16】**

前記第2層におけるアーチャー間の間隔が前記第2方向において500ミクロンである、請求項8に記載の基板。

**【請求項 17】**

前記第1方向で前記第1層及び前記第2層におけるアーチャー間の間隔が500ミク

10

20

30

40

50

ロンである、請求項 8 に記載の基板。

【請求項 18】

前記第2方向で前記第1層及び前記第2層におけるアーチャー間の間隔が250ミクロンである、請求項 8 に記載の基板。

【請求項 19】

有機基板であって、

少なくとも2つの重ね合わせ層としての頂部層及び底部層及びその間に設けられた第3の層を具備し、該頂部層及び底部層がそれら各々に形成された複数の脱ガス穴を含む脱ガス穴構造とされている有機基板において、

前記脱ガス穴が前記頂部層及び前記底部層の間で互い違いとなっている脱ガス穴格子を形成し、それら脱ガス穴が所定のピッチ間隔で前記頂部層及び前記底部層の間に交互に配置され、それら脱ガス穴が第1方向と該第1方向に実質的に直交する第2方向とで交互に配置され、前記第1方向における隣接脱ガス穴の間隔が前記第2方向における隣接脱ガス穴の間隔の2倍とされている有機基板。 10

【請求項 20】

集積回路パッケージであって、

シリコン・ダイと、

前記シリコン・ダイに搭載された有機ランド・グリッド・アレイとから成る集積回路パッケージにおいて、

前記有機ランド・グリッド・アレイが

20

頂部層及び底部層を具備し、これら頂部層及び底部層の各々がそれ自身において複数のアーチャーを有し、前記頂部層及び前記底部層の前記アーチャーが第1方向において互い違いとされ、且つ該第1方向に実質的に直交する第2方向において互い違いとされ、前記第1方向における隣接アーチャーの間隔が前記第2方向における隣接アーチャーの間隔の2倍とされており、

更に、前記頂部層及び前記底部層の間に設けられた一対の金属トレースを具備し、これら金属とレースが前記第1方向に沿って実質的に延在している集積回路パッケージ。

【請求項 21】

前記金属トレースが前記第1方向に対する第1角度でファンアウトしている、請求項 20 30 に記載の集積回路パッケージ。

【請求項 22】

前記第1角度が±45°である、請求項 21 に記載の集積回路パッケージ。

【請求項 23】

前記アーチャーが脱ガス穴である、請求項 20 に記載の集積回路パッケージ。

【請求項 24】

前記第1層及び前記第2層における前記アーチャーが格子形式で配列されている、請求項 20 に記載の集積回路パッケージ。

【請求項 25】

前記第1方向が経路指定方向であり、この経路指定方向における隣接アーチャーの間隔が前記第1方向と実質的に直交する前記第2方向における隣接アーチャーの間隔の2倍である、請求項 20 に記載の集積回路パッケージ。 40

【請求項 26】

前記第1層におけるアーチャー間の間隔が前記第1方向において1000ミクロンであり、前記第2層におけるアーチャー間の間隔が前記第1方向において1000ミクロンである、請求項 20 に記載の集積回路パッケージ。

【請求項 27】

前記第1層におけるアーチャー間の間隔が前記第2方向において500ミクロンであり、前記第2層におけるアーチャー間の間隔が前記第2方向において500ミクロンである、請求項 20 に記載の集積回路パッケージ。 50

## 【請求項 28】

前記第1方向で前記第1層及び前記第2層におけるアパーチャー間の間隔が500ミクロンである、請求項20に記載の集積回路パッケージ。

## 【請求項 29】

前記第2方向で前記第1層及び前記第2層におけるアパーチャー間の間隔が250ミクロンである、請求項20に記載の集積回路パッケージ。

## 【請求項 30】

回路アセンブリであって、

マイクロプロセッサと、

基板とより成り、

10

前記基板は実質的少なくとも2つの重ね合わせ層としての頂部層及び底部層及びその間に設けられた第3の層を具備し、前記第1層及び前記第2層の各々が複数のアパーチャーを有し、前記第1層及び前記第2層における前記アパーチャーの位置が第1方向で互い違いとされ、且つ前記第1方向と実質的に直交する第2方向で互い違いとされ、前記第1方向における隣接アパーチャーの間隔が前記第2方向における隣接アパーチャーの間隔の2倍とされており、

前記基板は、更に、前記第1層及び前記第2層の間に設けられた一対の金属トレースを具備し、これら金属トレースが前記第1方向に沿って実質的に延在し、

更に、複数の取付け領域を有するマザーボードとより成り、前記基板が前記マザーボード上に取り付け可能となっている回路アセンブリ。

20

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は一般的にはコンピュータ・ボード及びチップ・パッケージングに関し、より詳細には有機ランド・グリッド・アレイ（O L G A）設計及び製造に関する。

## 【0002】

## 【従来の技術】

高性能半導体チップに必要される入力／出力（I／O）速度及び該I／Oの総数は劇的に増大されてきたので、相互接続ライン数の増大の要望がチップ・パッケージにおける低いライン・インピーダンス変動と共に増大されてきており。こうした要望に対処するため、製造業者は幾つかの導体層が誘電体層によって分離されている多層パッケージを使用してきた。

30

## 【0003】

プリント回路基板（P C B）及び集積回路（I C）の製造において、しばしばシリコン・チップ（ダイ）がマザーボードに接続される。ダイのマザーボードへのこうした接続はパッケージとして知られる。ダイは有機ランド・グリッド・アレイ（O L G A）と云われる基板の一片にフリップ取り付けされ得る。このO L G Aは、典型的には、プリント回路基板の製造において共通して使用されているF R 4材のコアから形成される。

## 【0004】

O L G A ボードの2つの側面には、典型的には、一連の重ね合わせ層が誘電体材及び導電性材の交互層から形成されている。パターンは、当業界では公知であるのでここではこれ以上説明しない湿式エッティング等の様々なエッティング・プロセスを介して金属或は導電体の層内に構築され得る。バイアと云われる穴又はホールを介してのメッキは金属から成る様々な層間の相互接続を作るために使用される。これら層及びバイアを用いて、相互接続の幾つかの層は構築され得る。

40

## 【0005】

O L G A パッケージング技術において、入力／出力機能はそうした層間の金属トレースを用いて達成される。こうしたトレースは典型的にはグループ分けされる。各トレースはその幾何形状及びO L G A 上での配置によって作り出されるインピーダンスを有する。製造技術及び材料要件によって、O L G A パッケージは適切な動作を可能とするために金属層

50

内に形成される多数の脱ガス穴を必要とする。脱ガス穴はガスが蒸発又は気化して、泡がパッケージ内に形成されないようにしている。

【0006】

トレースは脱ガス穴の上若しくは下に経路指定され得るか、脱ガス穴回りに経路指定され得るか、或は、それらの組合せとなり得る。トレースはOLGA上の同一箇所にはないで、それらトレースはインピーダンス変動或は不釣り合いを有する。OLGAトレースのインピーダンス変動は2つの分離した源、即ち、製造変動及び設計変動から引き起こされる。製造変動及び設計変動は、全体的なインピーダンスの変動或は不釣り合いを生ずるよう静的に付加される。

【0007】

製造変動は、トレース幅、トレース厚み、誘電体厚み、並びに、誘電体の誘電率の変動を含むトレースの幾何形状変動から生ずる。設計変動はパッケージ設計から導入される。トレースがOLGA内に走らされると、それらトレースは経路指定された方向及びファン-アウト方向を有する。トレースはダイからそのパッケージまで経路指定されなければならない。トレースが経路指定されると、そのトレースの方向は経路指定方向と云われる。ファン-アウト方向はその経路指定方向から典型的には45°であり、+45°か或は-45°かの何れかである。

【0008】

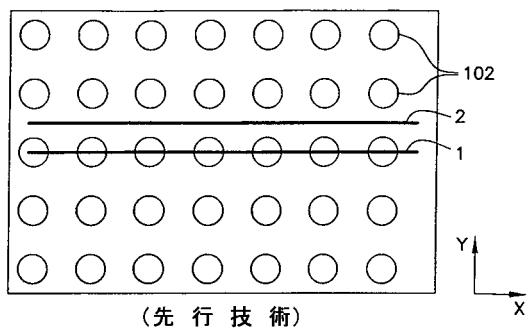

典型的な脱ガス穴のパターンは、図1に示されるように、2つの層間を垂直方向に整合された脱ガス穴から成るグリッド様（格子状）アレイを有する。図1において、上部層（頂部層）及び底部層における脱ガス穴102はx方向及びy方向で正確に整合されている。トレース1及びトレース2等のトレースが図1に示されるような脱ガス穴整合方式と共に使用されると、トレース1は、トレース2と比較して、当該トレース1の上下双方における導電性層からの金属をより少なく有する。トレース1及び2の上下における金属量の相違は、これらトレースがファン-アウト方向へ走らされるときまで継続する。図1の脱ガス穴パターンは、それだけで約20%程度である設計インピーダンス変動に到ることになる。

【0009】

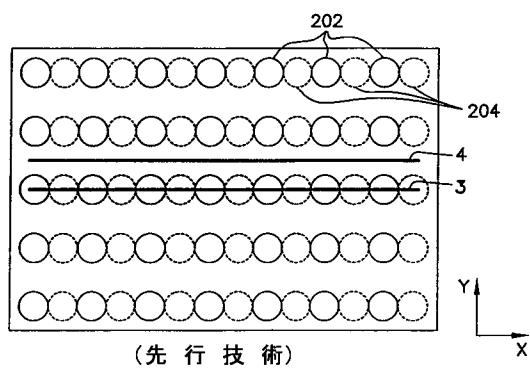

図2に示される別の脱ガス穴パターンは、次の層における脱ガス穴204から互い違いに配置された脱ガス穴202のグリッド様アレイを有する。図2における脱ガス穴は層間でx方向に互い違いに配置されている。脱ガス穴間の距離はピッチとして知られている。図2における各種層の脱ガス穴はx方向に半ピッチだけ互い違いに配置されている。トレース3及びトレース4等のトレースが図2に示されるような脱ガス穴整合方式と共に使用されると、トレース3は、トレース4と比較して、当該トレース3の上下双方における導電性層からの金属をより少なく有する。これらトレース上下における金属量に関する変動は、脱ガス穴の互い違い配置のために、x方向から45°の角度でのファン-アウト状態で低下させられる。更に重要な設計インピーダンス変動は図2における脱ガス穴パターンに伴って提供される。

【0010】

【発明が解決しようとする課題】

上述した理由や、本明細書を読んで理解した当業者には明らかとなるような下述の他の理由のため、OLGAパッケージにおける設計変動を減ずる脱ガス穴パターンの要望が当業界にある。

【0011】

【課題を解決するための手段】

OLGAパッケージは、一対の導電性層であり、各層がそれ自体を貫通する多数の脱ガス・アーチャーを有して、前記層の前記アーチャーが第1方向及び第2方向の双方で互い違いに配置させられていることから成る一対の導電性層と、導電性層間に配置された非導電性層と、前記導電性層対間の一対の金属トレースであり、該トレースが略同一インピーダンスを有することから成る一対の金属トレースとを備えている。

10

20

30

40

50

## 【0012】

## 【発明の実施の形態】

本実施例の以下の詳細な説明において、本明細書の一部を形成すると共に、本発明が実施され得る例示目的の特定実施例が示されている添付図面が参照される。理解して頂きたいことは、他の実施例が利用され得て、本発明の範囲から逸脱すること無しに、構造的変更が為され得ることである。

## 【0013】

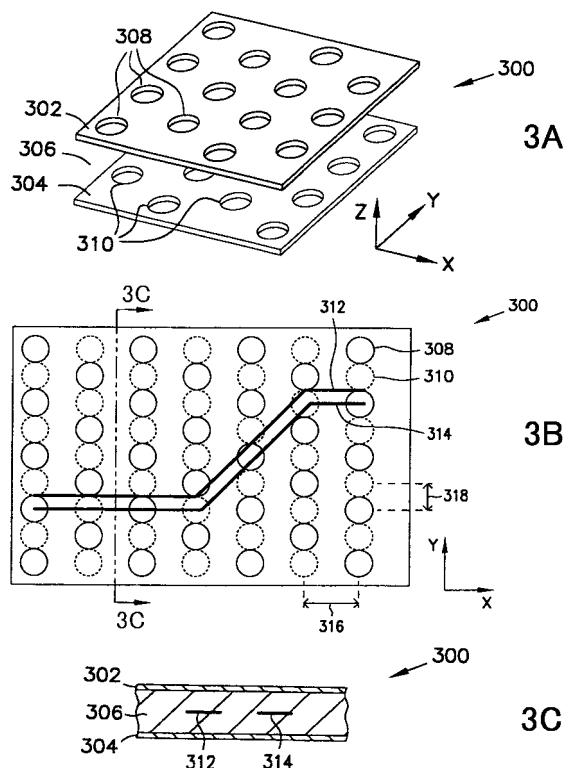

図3Aは、本発明の一実施例300に係る脱ガス穴形態を示している。実施例300は、(図3C)誘電体層306を挟み込んでいる少なくとも2つの重ね合わせ金属層302及び304を有するOLGAを備える。金属層302及び304の各々は、それぞれ、複数のアパー チャー又は穴308及び310をその中に有する。金属層302及び304は垂直方向に整合されると、それら層は積み重ねられ、実施例300は図3Aで参照されるようにx方向及びy方向の双方において互い違いに配置されている層302における脱ガス穴308と層304における脱ガス穴310とを有する。x及びyが選択されているが、任意の座標系が本発明の範囲から逸脱すること無しに使用され得る。

10

## 【0014】

図3Bにも示される一実施例において、脱ガス穴は格子パターン状に配列されおり、一方方向における格子定数と、他の実質的に直交する方向における第2の格子定数とを有する格子パターンを形成している層302及び304における脱ガス穴を具備している。説明の簡略化の目的で、格子パターンはx方向における第1格子定数とy方向における第2格子定数とを具備して図3に示されている。この実施例において、脱ガス穴格子パターンは層302から層304までx方向及びy方向の双方において互い違いに脱ガス穴を有している。言い換えれば、上方から見られる脱ガス穴格子パターンにおいて、即ち積み重ねられた層302及び304を見下ろした場合、x方向及びy方向の双方において層302の脱ガス穴308が層304の脱ガス穴310と交互配置又は互い違い配置となっている。

20

## 【0015】

各脱ガス穴308或は310は、x及びy座標における位置をz座標位置と共に有している。そのz方向は図3Aで最も明示されている。各層における全ての脱ガス穴のz座標は同一である。層302における全ての脱ガス穴308のz座標は層304における全ての脱ガス穴310のz座標とは異なるが、層302における全ての脱ガス穴308に対して同一である。図3Bから明らかなように、実施例300において、各脱ガス穴はx方向及びy方向において異なる層における脱ガス穴と隣接し且つ異なるz座標を有する。脱ガス穴は、層302から層304までx方向及びy方向の双方においてz座標が互い違いとなっている。実施例300における各脱ガス穴は、x, y, z座標の唯一の組を有する。

30

## 【0016】

一実施例において、第1格子定数、即ちx方向における格子定数は脱ガス穴308及び310の径の2倍のピッチ又は間隔316を有する。この実施例において、第2格子定数、即ちy方向における格子定数は脱ガス穴308及び310の径に等しいピッチ318を有する。別の実施例において、第1格子定数は500ミクロンであり、第2格子定数は250ミクロンである。この実施例において脱ガス穴の径は250ミクロンである。それ故に、層302或は層304の何れかにおける隣接脱ガス穴間の最小間隔は約500ミクロンである。

40

## 【0017】

上述したトレースは、典型的には、グループ分けさせられる。トレース312及び314は図3B及び図3Cに示されている。しかしながら理解して頂きたいことは、3つ以上のトレースをグループ分けでき、そうした付加的なトレースは本発明の範囲内にあることである。各トレースは第1の経路指定方向を走って、第2のファン-アウト方向へファンアウトされ得る。典型的には、ファン-アウトは経路指定方向から+45°或は-45°の角度で行われている。上述したように、それぞれのトレースの上下における層からの金属量が異なる別個のそれらトレースは不釣り合いなインピーダンスを有することになる。図

50

3 の実施例で示された脱ガス穴の互い違いピッチ形態によって、金属層 302 及び 304 の間に経路指定されたトレース 312 或は 314 等の信号トレースは、それらの各トレース路における各層から概略で同一数の脱ガス穴を有することになる。更に、トレース 312 或は 314 等の各信号トレースは該当トレースの上下における金属量をも有し、その金属量が、同様に経路指定された他方のトレースの上下における金属の量とより緊密に一致している。

【0018】

図 3 に示されるトレース形態において、トレース 312 及びトレース 314 は最も不利な可能性があるトレース・ラインを走る位置決め、即ち、それらトレース間で最も大きなインピーダンス変動を有するトレース・ライン対を作り出すように走る位置決めとされている。図から理解して頂けるように、トレース 314 は、その経路指定された方向を走る際に、各層における脱ガス穴の中心をそれら脱ガス穴の略中心で横切っている。他方、トレース 312 はその経路指定された方向を走っているが、各層における脱ガス穴のエッジを横切っている。この最も不利な場合のシナリオでは、設計考慮によってのインピーダンス変動は異なる脱ガス穴形態の設計によるインピーダンス変動を凌いで著しく低減され得る。

10

【0019】

もし図 3 の形態でのトレースに対する主要経路指定方向が実質的に x 方向であれば、x 方向に経路指定されたトレースはその y 座標に関して何等制約を受けない。換言すれば、x 方向に経路指定されたトレースはその y 座標位置と云う点において自由に上下に移動させることができる。もし多重信号ラインが x 方向に沿って密に経路指定されたならば、脱ガス穴形態は浪費スペースの量を低減することになる。

20

【0020】

図 3 に示される本実施例の設計変動によるインピーダンスの低減は、経路指定方向から 45° のファン-アウト方向においてよりいっそう顕著となる。これは図 3A で判明され得る。トレースが x 方向に経路指定されて、該 x 方向から 45° でファンアウトさせられると、それらトレースは当該トレースの上下双方における脱ガス穴を横切る。トレースがその経路指定方向から、+ 或は - の何れであろうが、概略で 45° で走っていれば、脱ガス穴を横切ることになる。図面から見ることができるように、各トレース 312 及び 314 は概略で同一数の脱ガス穴を横切り、そして概略同一の脱ガス穴面積を覆っている。換言すれば、各トレース 312 及び 314 は、ファン-アウト方向に走っている際、該当トレースの上下の金属量の変動が相当より少なくなる。これは設計考慮によってインピーダンスを更に低減する。

30

【0021】

設計要因による最も不利な場合のインピーダンス変動は実施例 300 に示される脱ガス穴形態によって著しく低減される。トレース上下における金属量の大きな変動を削除することは、設計要因によるインピーダンスを低減する。トレースは実施例 300 の脱ガス穴形態による配置を強要するより少ない気遣いで経路指定が為され得る。

【0022】

図 4 は、本発明の集積回路 400 のブロック構成図を図示している。この集積回路 400 は入力信号或は制御信号を受信する。こうした信号は内部回路 404 による処理のために O L G A パッケージ 402 に結合可能である。O L G A 402 は図 3 に関して上述されたように配列され得る。この集積回路は任意のタイプの集積回路であることが可能であり、プロセッサ、メモリ、メモリ・コントローラ、或は、特定用途向け集積回路 ( A S I C ) を含むが、それらに限定されることはない。

40

【0023】

図 5 は本発明の回路パッケージ実施例 500 を示している。実施例 500 において、シリコン・ダイ 502 の接続はマザーボード 504 の O L G A 部に為されている。一実施例において、シリコン・ダイはボード上にフリップ取り付けされている。O L G A は図 3 に関して上述されたように配列され得る。また別の実施例において、図 3 に関して上述された

50

O L G A はマザーボード上のソケットに取り付け可能となる。そうした回路パッケージは当業者には公知なプロセッサ或は他の電子コンポーネントをも含むことができる。

【 0 0 2 4 】

他の実施例において、本発明のO L G A パッケージは、チップ・セット及びプロセッサ・パッケージング等々に対してのような形態で使用可能である。O L G A パッケージング技術を用いての任意のプロセッサ製品は本発明の実施例の内の1つを具現化できる。

【 0 0 2 5 】

理解して頂きたいことは、以上の説明は例示的目的のものであり、制限的ではないことである。数多くの他の実施例は、以上の説明を読んで理解した当業者には明らかとなるであろう。それ故に本発明の範囲は、添付の特許請求の範囲をそうした請求項が付与される均等物の全範囲と共に参照して決定されるべきである。

10

【図面の簡単な説明】

【図1】図1は、先行技術に係る脱ガス穴形態の上面図である。

【図2】図2は、別の先行技術に係る脱ガス穴形態の上面図である。

【図3】図3 Aは本発明の一実施例に係る脱ガス穴形態の斜視図であり、図3 Bは図3 Aに示される実施例の上面図であり、図3 Cは図3 Bに示される実施例の3 C - 3 C線で切断された場合の断面図である。

【図4】図4は、本発明の一実施例に係る集積回路のプロック構成図である。

【図5】図5は、本発明のパッケージ実施例の側面図である。

【符号の説明】

20

3 0 0 脱ガス穴形態

3 0 2 , 3 0 4 金属層

3 0 8 , 3 1 0 脱ガス穴（脱ガス・アパー・チャーチー）

3 1 6 , 3 1 8 ピッチ又は間隔

3 1 2 , 3 1 4 トレース

4 0 0 集積回路

4 0 2 O L G A パッケージ

4 0 4 内部回路

5 0 0 回路パッケージ

5 0 2 シリコン・ダイ

30

5 0 4 マザーボード

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 ヒューオン・ティー・ド

アメリカ合衆国 85257 アリゾナ、スコットデイル、イースト・ベレビュウ・ストリート

7007

審査官 宮本 靖史

(56)参考文献 実開平03-097973(JP, U)

特開平06-085106(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H01L 23/14