(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5110766号

(P5110766)

(45) 発行日 平成24年12月26日(2012.12.26)

(24) 登録日 平成24年10月19日(2012.10.19)

(51) Int.Cl.

F 1

|             |           |             |      |

|-------------|-----------|-------------|------|

| HO1L 21/02  | (2006.01) | HO1L 27/12  | B    |

| HO1L 27/12  | (2006.01) | HO1L 29/78  | 627D |

| HO1L 21/336 | (2006.01) | HO1L 21/20  |      |

| HO1L 29/786 | (2006.01) | HO1L 21/302 | 201A |

| HO1L 21/20  | (2006.01) | HO1L 29/78  | 613Z |

請求項の数 7 (全 29 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2004-362339 (P2004-362339)  |

| (22) 出願日     | 平成16年12月15日 (2004.12.15)      |

| (65) 公開番号    | 特開2005-203762 (P2005-203762A) |

| (43) 公開日     | 平成17年7月28日 (2005.7.28)        |

| 審査請求日        | 平成19年12月4日 (2007.12.4)        |

| (31) 優先権主張番号 | 特願2003-417317 (P2003-417317)  |

| (32) 優先日     | 平成15年12月15日 (2003.12.15)      |

| (33) 優先権主張国  | 日本国 (JP)                      |

前置審査

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 小森 美帆<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 佐藤 由里香<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内  |

| (72) 発明者  | 細木 和江<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】薄膜集積回路装置の作製方法及び非接触型薄膜集積回路装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

基板上に剥離層を形成し、

前記剥離層上に下地膜を形成し、

前記下地膜上に複数の薄膜集積回路を形成し、

前記薄膜集積回路上に絶縁膜を形成し、

前記絶縁膜上にコンタクトホールを介して薄膜集積回路と接続する配線を形成し、

前記配線上に保護膜を形成することで前記薄膜集積回路と前記配線を有する薄膜集積回路装置を複数形成し、

前記複数の薄膜集積回路装置の境界に溝を形成し、

前記複数の薄膜集積回路装置の上方である前記保護膜に、複数の突起部を有するジグの当該突起部を、前記薄膜集積回路装置毎に接着し、

前記溝にフッ化ハロゲンを含む気体又は液体を導入し、前記剥離層を除去することによって、前記複数の薄膜集積回路装置を分離し、

前記複数の薄膜集積回路装置に接着されたジグを取り外すことを特徴とする薄膜集積回路装置の作製方法。

## 【請求項2】

請求項1において、

前記ジグの接着は、UV光によって接着力が低下又は喪失する接着剤を用いて行なうこととを特徴とする薄膜集積回路装置の作製方法。

10

20

**【請求項 3】**

請求項 1 又は 2 において、

前記剥離層は、シリコンを主成分として含むことを特徴とする薄膜集積回路装置の作製方法。

**【請求項 4】**

請求項 1 乃至 3 のいずれか一項において、

前記下地膜は、酸化珪素、窒化珪素、窒素を含む酸化珪素のいずれかを含むことを特徴とする薄膜集積回路装置の作製方法。

**【請求項 5】**

請求項 1 乃至 4 のいずれか一項において、

前記溝はダイヤモンドスクライビング又はレーザースクライビングによって形成されることを特徴とする薄膜集積回路装置の作製方法。

**【請求項 6】**

請求項 1 乃至 5 のいずれか一項において、

前記基板は、ガラス基板又は石英基板であることを特徴とする薄膜集積回路装置の作製方法。

**【請求項 7】**

請求項 1 乃至 6 のいずれか一項において、

前記フッ化ハロゲンは、 $\text{ClF}_3$  (三フッ化塩素) であることを特徴とする薄膜集積回路装置の作製方法。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、メモリやマイクロプロセッサ（中央演算部、CPU）などを有し、紙のように薄くフレキシブルな薄膜集積回路を搭載した薄膜集積回路の作製方法、該薄膜集積回路及びアンテナからなり、主として人間、動植物、商品、紙幣等を識別するためのカード、タグ、ラベル等に利用される非接触型薄膜集積回路装置、及びその作製方法に関する。

**【背景技術】****【0002】**

近年、食品業界、製造業界等のあらゆる産業界において、商品の安全性や管理体制の強化を求める声が高まっており、それに伴い商品に関する情報量が増加しつつある。しかしながら、現状の商品情報は、主にバーコードの十数桁の数字により提供される製造国、メーカー、商品番号等の情報程度であり、情報量が非常に少なかった。またバーコードを利用した場合、一つ一つを手作業で行うため読み取りに時間を要していた。そこで、バーコードシステムに代わり、RFID (Radio Frequency Identification) と呼ばれる、電磁波を利用して非接触ICタグによる自動認識技術が注目されている。

**【0003】**

また、動植物の安全性（例えば、原産地、伝染病の感染の有無等）を確保するために、動植物の体内に直接ICチップを埋め込み、体外の情報読み取り装置（リーダ）によって動植物に関する情報を取得、管理するという体制が普及しつつある。

**【0004】**

また、近年、一人当たりが携帯するカード数が増加しており、中でも電磁界を利用して通信を行う非接触型のICカードが、電子乗車券や電子マネーといった形態で普及しつつある。また、凶悪犯罪や行方不明といった事件が増加する中、特に幼児、児童、老人や旅行者等の個々人の居場所を常時的確に把握し、事故に巻き込まれる可能性を減らすべく、個々人を認識することができるID (Identification) カード等が普及しつつある。

**【0005】**

また、紙幣、硬貨、有価証券、チケット等の偽造や盗難が行われた際に、複製や悪用を防止するために、それらの内部にICチップを埋め込んでおくという技術が普及しつつあ

る（以上、非特許文献1参照）。

【非特許文献1】日経エレクトロニクス 日経BP社 2002.11.18発行 p. 67 - 76

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0006】

しかしながら、非接触型や接触型のICチップが普及するにつれて、莫大な数の人間、動植物、商品、紙幣等に利用可能なICチップを、大量に極めて低成本で製造する必要がある。例えば、商品や紙幣等に付されるICチップは、1個当たり1円～数円、望ましくは1円を切るコストで製造する必要があり、低成本で大量生産が可能なICチップの構造、プロセスの実現が求められている。10

##### 【0007】

現状では、ICチップを製造するにあたり、シリコンウェハ上に複数の薄膜集積回路を形成し、該シリコンウェハを研磨除去（バックグラインドと呼ばれる。）することにより薄膜集積回路を分離する方法が用いられている。しかし、シリコンウェハは高価であるにも拘わらず、それをすべて研磨除去してしまうことから、製造コストの増加は回避できなかつた。また、シリコンウェハからなる集積回路は厚いため、商品容器自体に搭載する場合、表面に凹凸が生じ、デザイン選択の幅に限界があった。

##### 【0008】

また、基板を研磨除去しない方法として、複数の薄膜集積回路が形成された基板にストレスを与え、基板を物理的に剥離する方法があるが、この方法だと、基板上に形成された薄膜の応力の分布等により、基板が完全に剥離されない可能性があった。20

##### 【0009】

本発明は、このような状況に鑑みて成されたものであり、低成本で大量生産が可能で、かつ、従来のシリコンウェハと異なり、非常に膜厚の薄い薄膜集積回路、及び該薄膜集積回路を用いた薄膜集積回路装置又はICチップの構造、プロセスを提供することを目的としている。

##### 【課題を解決するための手段】

##### 【0010】

(1) 本発明に係る薄膜集積回路の作製方法は、基板上に剥離層を形成し、前記剥離層上に下地膜を介して複数の薄膜集積回路を形成し、前記複数の薄膜集積回路の境界に溝を形成し、前記溝にハロゲン化フッ素を含む気体又は液体を導入し、前記剥離層を除去することによって、前記複数の薄膜集積回路を分離することを特徴としている。30

##### 【0011】

ここで、剥離層（ピールオフ・レイヤー）は、基板と薄膜集積回路の間に設けられる層であり、後に該剥離層を除去することにより、基板と薄膜集積回路を分離することができる。剥離層としては、非晶質シリコン、多結晶シリコン、単結晶シリコン、セミアモルファスシリコン（SAS）（微結晶シリコンともいう。）等、シリコン（Si）を主成分とする層を用いることができる。ClF<sub>3</sub>（三フッ化塩素）等のハロゲン化フッ素は、シリコンを選択的にエッチングするという特性があるため、剥離層としてシリコン（Si）を主成分とする層を用いることにより、ClF<sub>3</sub>を含む気体又は液体によって前記剥離層を容易に除去することができる。40

##### 【0012】

また、下地膜は、剥離層と薄膜集積回路の間に設けられるものであり、ClF<sub>3</sub>等のハロゲン化フッ素によるエッチングから、薄膜集積回路を保護する役割を有するものである。ここで、ClF<sub>3</sub>等のハロゲン化フッ素は、珪素を選択的にエッチングするという特性がある反面、酸化珪素（SiO<sub>x</sub>）、窒化珪素（SiN<sub>x</sub>）、窒素を含む酸化珪素（SiO<sub>x</sub>N<sub>y</sub>（x > y））、酸素を含む窒化珪素（SiN<sub>x</sub>O<sub>y</sub>（x > y））はほとんどエッチングされない。したがって、時間の経過とともに剥離層はエッチングされてゆくが、酸化珪素、窒化珪素、窒素を含む酸化珪素、酸素を含む窒化珪素からなる下地膜はほとんど工50

ツチングされないため、薄膜集積回路への損傷を防止することができる。

【0013】

なお、 $C_1F_3$ 等のハロゲン化フッ素によってエッチングされる材料を剥離層として用い、一方、エッチングされない材料を下地膜として用いるという条件に従うならば、剥離層及び下地膜の組合せは、上記材料に限定されるものではなく、適宜選択することができる。

【0014】

また、エッチングに用いるガスとしては、上記 $C_1F_3$ 等に窒素を混合したガスを用いてもよい。また、 $C_1F_3$ は、反応空間の温度によっては液体の場合もあり（沸点11.75）、その際にはウェットエッチングを採用することもできる。なお、 $C_1F_3$ は、塩素を200以上でフッ素と反応させることにより、 $C_1_2(g) + 3F_2(g) \rightarrow C_1F_3(g)$ の過程を経て生成することができる。なお、上記剥離層をエッチングし、上記下地膜をエッチングしないようなエッチャントであれば、 $C_1F_3$ に限定されるものではなく、またハロゲン化フッ素に限定されるものでもない。

10

【0015】

また、薄膜集積回路の境界をなす溝の形成は、ダイシング、スクライビング又はマスクを利用したエッチング等によって行うことができる。ダイシングの場合には、ダイシング装置（ダイサー； dicer）を用いるブレードダイシング法が一般的である。ブレード（blade）とは、ダイヤモンド砥粒を埋め込んだ砥石で、その幅は約30~50 μmであり、このブレードを高速回転させることにより、薄膜集積回路を分離する。また、スクライビングの場合には、ダイヤモンドスクライビング法とレーザースクライビング法等がある。また、エッチングの場合には、露光、現像工程によりマスクパターンを形成し、ドライエッチング、ウェットエッチング等により素子分離を行うことができる。ドライエッチングにおいては、大気圧プラズマ法を用いてもよい。

20

【0016】

また、基板としては、ガラス基板、石英基板、アルミナなど絶縁物質で形成される基板、シリコンウエハ基板、後工程の処理温度に耐え得る耐熱性を有するプラスチック基板等を用いることができる。この場合、酸化珪素（ $SiO_x$ ）、窒化珪素（ $SiN_x$ ）、窒素を含む酸化珪素（ $SiO_xNy$ ）（ $x > y$ ）、酸素を含む窒化珪素（ $SiNxOy$ ）（ $x > y$ ）等、基板側から不純物などの拡散を防止するための下地絶縁膜を形成しておいてよい。また、ステンレスなどの金属または半導体基板などの表面に酸化シリコンや窒化シリコンなどの絶縁膜を形成した基板なども用いることができる。

30

【0017】

また、本発明を用いて一旦薄膜集積回路を形成した後に、剥離された使用済みの基板を再利用してもよい。再利用する場合、上記ダイシングやスクライビング等において、基板に傷が生成されないように制御するのが望ましいが、傷が生成された場合には、有機樹脂や無機膜を塗布法や液滴吐出法（インクジェット法等）によって形成し、平坦化処理を行っても良い。

【0018】

なお、薄膜集積回路をハロゲン化フッ素等によるエッチングから保護するために、薄膜集積回路上に減圧CVD法等により保護膜を形成しておくのが望ましい。特に、ハロゲン化フッ素ガスを加熱してエッチングを行う場合には、前記保護膜として耐熱性有機樹脂や、耐熱性無機膜を用いるのが望ましい。耐熱性有機樹脂の代表的なものとして、シリコンと酸素との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料、若しくは置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも一種を有する材料があり、所謂シロキサン系樹脂などとも呼ばれる。以後、耐熱性有機樹脂という場合には、シロキサン系樹脂も含むものとする。

40

【0019】

（2）本発明に係る薄膜集積回路の作製方法は、基板上に剥離層を形成し、前記剥離層上に下地膜を介して複数の薄膜集積回路を形成し、前記複数の薄膜集積回路の境界に溝を形

50

成し、前記複数の薄膜集積回路の上方に、ジグを接着し、前記溝にハロゲン化フッ素を含む気体又は液体を導入し、前記剥離層を除去することによって、前記複数の薄膜集積回路を分離し、前記複数の薄膜集積回路に接着されたジグを取り外すことを特徴としている。

#### 【0020】

ここで、ジグ（治具）とは、剥離層を除去した後に薄膜集積回路装置がバラバラに分離しないように、一時的に薄膜集積回路装置を固定するための支持基板を指す。ジグは、複数の薄膜集積回路装置が水平方向若しくは高さ方向に集積されてできた素子毎に形成される。ジグの形状としては、後にハロゲン化フッ素を含む気体又は液体の導入を容易にするために、突起部を設けた櫛状の構造とするのが望ましいが、平坦なジグを用いても構わない。また、ジグとしては、ハロゲン化フッ素によって冒されない酸化珪素を主成分とするガラス基板、石英基板、ステンレス（SUS）基板等を用いることができるが、ハロゲン化フッ素によって冒されない材料であれば、これらに限定されるものではない。また、ジグと薄膜集積回路装置との間には、仮接着するための接着剤が設けられている。

10

#### 【0021】

ここで、接着剤としては、UV光照射によって接着力（粘着力）が低下又は喪失する材料を用いることができる。あるいは、スリーエム・イノベイティブ・プロパティズ・カンパニー（3M）社製のポストトイット（登録商標）製品や、ムーア・ビジネス・フォームス・インコーポレイテッド社製ノートスティックス（登録商標）製品等に用いられる再剥離再接着可能な接着剤を用いても構わない。例えば、特開2001-30403、特許2992092、特開平6-299127に記載された、アクリル系粘着剤、合成ゴム系粘着剤、天然ゴム系粘着剤等を用いることができる。勿論、ジグを簡単に取り外すことができる材料であれば、これらに限定されるものではない。

20

#### 【0022】

その余の構成については、上記（1）で述べた本発明に準ずる。

#### 【0023】

（3）本発明に係る非接触型薄膜集積回路装置の作製方法は、基板上に剥離層を形成し、前記剥離層上に下地膜を介して複数の薄膜集積回路を形成し、前記薄膜集積回路上に耐熱性有機樹脂を形成し、前記複数の薄膜集積回路の境界に溝を形成し、前記溝にハロゲン化フッ素を含む気体又は液体を導入し、前記剥離層を除去することによって、前記複数の薄膜集積回路を分離し、前記分離された薄膜集積回路の上方又は下方にアンテナを形成することを特徴としている。

30

#### 【0024】

ここでいう薄膜集積回路装置とは、人間、動植物、自他の商品、紙幣等を識別、又はそれらに関する情報を蓄積する機能等を有するものであるが、本明細書ではIDチップ（IDentification Chip）、IDF（ID Flexible）チップ、ICチップ、又は単に半導体装置と呼ぶことがある。中でも、電磁界を利用して、薄膜集積回路装置に内蔵された送受信部（アンテナ、アンテナ回路）を介して、外部の読み込み／書き込み装置（リーダ／ライタ）と、通信を行うものを非接触型薄膜集積回路装置、または無線チップという。薄膜集積回路装置とリーダ／ライタ間で通信を行うことにより、薄膜集積回路装置が内蔵された商品等に関する情報の認識、更新、管理等を行うことができる。

40

#### 【0025】

また、アンテナとは、リーダ／ライタと通信、すなわち電波のやりとりを行うためのものであり、薄膜集積回路等の集積回路と接続されている。アンテナは、TFT等の薄膜集積回路工程の前後、あるいは、工程内において形成しても良いし、別途形成した後に、薄膜集積回路と接続しても良い。工程内において形成する場合には、例えば、TFTのゲート電極と同時に形成することができる。なお、アンテナには、図7等に示すコイル状（渦巻き状）や、図11等に示す閉ループ状がある。

#### 【0026】

また、アンテナを別途形成する場合には、アンテナが形成された基体で、薄膜集積回路の一部又は全部を包装するように形成することができる。この際、異方性導電材料や、公

50

知のポンディング法等を用いて、アンテナと薄膜集積回路とを接続すればよい。

#### 【0027】

なお、薄膜集積回路装置に内蔵されるTFT等の薄膜集積回路を作製する際には、剥離層を除去した後に薄膜集積回路装置がバラバラに分離しないように、一時的に薄膜集積回路装置を固定するためのジグを設けておくのが望ましい。ジグを設けるには、上記(2)で述べた方法を用いればよい。また、薄膜集積回路装置に内蔵される薄膜集積回路のその余の作製方法については、上記(1)、(2)で述べた方法を用いればよい。

#### 【0028】

(4) 本発明に係る非接触型薄膜集積回路装置は、基板上に下地膜を介して形成された薄膜集積回路と、前記薄膜集積回路上に形成された耐熱性を有する絶縁膜と、前記薄膜集積回路の上方又は下方に形成されたアンテナを有することを特徴としている。10

#### 【0029】

ここでは、耐熱性を有する絶縁膜としては、シリコンと酸素との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料、若しくは置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも一種を有する材料、すなわちシロキサン系樹脂等の耐熱性有機樹脂や、耐熱性の無機材料を用いることができる。

#### 【0030】

また、アンテナとは、リーダ/ライタと通信、すなわち電波のやりとりを行うためのものであり、薄膜集積回路等の集積回路と接続されている。アンテナに用いられる材料としては、Ag、Au、Al、Cu、Zn、Sn、Ni、Cr、Fe、Co若しくはTi、又はそれらを含む合金を用いることができるが、これらに限定されるものではない。また、アンテナを別途形成する場合には、アンテナが形成された基体で、薄膜集積回路の一部又は全部を包装するように形成することができる。この場合、基体として、プラスチックのように、可撓性を有する、すなわちフレキシブルな材料を用いるのが望ましい。20

#### 【0031】

また、本発明に係る非接触型薄膜集積回路装置は、IDタグ、IDカード、様々な商品、紙幣、硬貨等に組み込むことができる。ここで、薄膜集積回路装置を硬貨に組み込む場合には、硬貨の構成要素の一部がアンテナの機能を兼ねるようにしてもよい。この際、アンテナ又は前記硬貨を構成する材料としては、Ag、Au、Al、Cu、Zn、Sn、Ni、Cr、Fe、Co若しくはTi、又はそれらを含む合金を用いることができるが、これらに限定されるものではない。30

#### 【0032】

なお、本発明における基板、下地膜等の構成は、上記(1)乃至(3)の記載に基づいて適宜用いればよい。

#### 【発明の効果】

#### 【0033】

従来は、シリコンウェハ上に複数の薄膜集積回路を形成し、該シリコンウェハを研磨除去することにより薄膜集積回路を分離する方法が用いられていた。一方、本発明は、複数の薄膜集積回路が形成された基板から該薄膜集積回路を素子分離する際に、ハロゲン化フッ素を用いた化学的方法を採用することにより、シリコンウェハよりも低コストのガラス基板等を用いることができる。これにより、低コストで薄膜集積回路装置等に用いられる薄膜集積回路を作製することができる。また、シリコンウェハとほぼ同じコストの石英基板等を用いた場合であっても、本発明を用いた場合には、基板を再利用することもできるので、低コストで薄膜集積回路装置等に用いられる薄膜集積回路を作製することができる。40

#### 【0034】

また、シリコンウェハで作製されたICのように、クラックや研磨痕の原因となるバックグラインド処理を行う必要がない。また、素子の厚さのバラツキも、ICを構成する各膜の成膜時におけるばらつきに依存することになるので、大きくても数百nm程度に抑えることができる。したがって、バックグラインド処理による数~数十μmのばらつきと比50

べて飛躍的に小さく抑えることができる。

**【0035】**

また、複数の薄膜集積回路が形成された基板にストレスを与え、基板を物理的に剥離する物理的方法と比較しても、本発明は、複数の薄膜集積回路が形成された基板から該薄膜集積回路を素子分離する際に、ハロゲン化フッ素を用いた化学的方法を採用しているため、素子分離を確実に行うことができる。

**【0036】**

また、薄膜集積回路を覆って、下地膜や耐熱性を有する絶縁膜（保護膜）を形成することにより、ハロゲン化フッ素を用いた基板剥離工程において、薄膜集積回路を保護することができ、安定した特性を有する薄膜集積回路を形成することができる。

10

**【0037】**

また、ハロゲン化フッ素を用いた基板剥離工程において、薄膜集積回路装置毎に、ジグを仮接着しておくことにより、剥離層を除去した後に各薄膜集積回路装置がバラバラに分離してしまうのを防止することができる。この際、仮接着剤として、UV光照射によって接着力（粘着力）が低下又は喪失する材料を用いることにより、基板剥離後、ジグを薄膜集積回路装置から容易に取り外すことができる。

**【0038】**

以上から、本発明を用いることにより、薄膜集積回路装置に用いられる薄膜集積回路、ひいては薄膜集積回路装置や、それを用いた商品等を、低コストで大量に高歩留まり、高スループットで作製することができる。

20

**【発明を実施するための最良の形態】**

**【0039】**

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更することができる。従って、本実施の形態の記載内容に限定して解釈されるものではない。また、各図面において共通の部分は同じ符号を付して詳しい説明を省略する。

**【0040】**

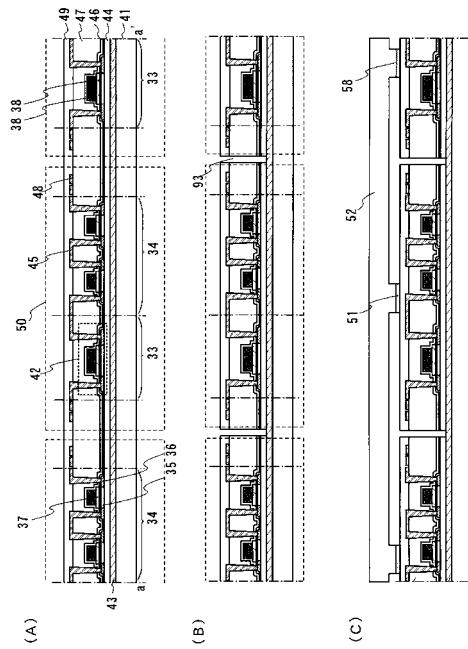

**(実施形態1)**

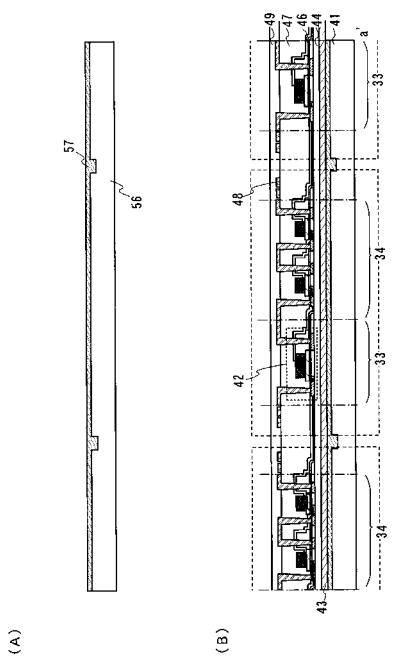

本発明を用いた薄膜集積回路装置及びその作製方法について、図1(A)～図1(C)、図2(A)～図2(C)、図3(A)、図3(B)、図12を用いて説明する。まず、基板41上に、剥離層43を形成する。ここでは、石英基板上に、500nmの膜厚のa-Si膜（非晶質シリコン膜）をスパッタ法により形成した。なお、基板としては、石英基板の他にも、ガラス基板、アルミナなど絶縁物質で形成される基板、シリコンウエハ基板、後工程の処理温度に耐え得る耐熱性を有するプラスチック基板等を用いることができる。この場合、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、窒素を含む酸化珪素(SiO<sub>x</sub>N<sub>y</sub>)( $x > y$ )、酸素を含む窒化珪素(SiN<sub>x</sub>O<sub>y</sub>)( $x > y$ )等、基板側から不純物などの拡散を防止するための下地絶縁膜を形成しておいてもよい。また、ステンレスなどの金属または半導体基板などの表面に酸化シリコンや窒化シリコンなどの絶縁膜を形成した基板なども用いることができる。

30

**【0041】**

また、剥離層43としては、非晶質シリコンの他に、多結晶シリコン、単結晶シリコン、セミアモルファスシリコン(SAS、微結晶シリコンともいう。)等、シリコンを主成分とする層を用いることができる。これらの剥離層43は、スパッタ法の他にも、プラズマCVD法等によって形成しても良い。また、剥離層43は500nmよりも薄く形成しても良い。

40

**【0042】**

次に、剥離層43上に、下地膜44を形成する。ここでは、100nm(1000)の膜厚の酸化珪素膜をスパッタ法によって形成した。なお、下地膜44は、CF<sub>3</sub>等のハロゲン化フッ素によるエッチングから、薄膜集積回路を保護する役割を有するものであ

50

り、この機能を有するものであれば、他の材料を用いてもよい。例えば、窒化珪素、窒素を含む酸化珪素、酸素を含む窒化珪素等を用いることができる。または、上記材料からなる膜を積層して下地膜44を形成しても良い。また、スパッタ法に限らず、プラズマCVD法等によって形成しても良い。

#### 【0043】

次に、下地膜44上に薄膜集積回路42、例えば薄膜トランジスタ(TFT)、有機TFT、薄膜ダイオード等を形成する。図1(A)に示す薄膜集積回路42は、下地膜44上に、チャネル形成領域35、不純物領域36、ゲート絶縁膜37及びゲート電極38が形成されている。本実施の形態では、トップゲート構造としたが、ボトムゲート構造(逆スタガ構造)としてもよい。また、薄膜トランジスタの代わりに有機TFTや薄膜ダイオードを用いてもよい。これらの薄膜集積回路が薄膜集積回路装置のCPUやメモリ等を構成する。TFTを用いたCPUやメモリ等の薄膜集積回路の作製方法の具体例については、後述する。なお、薄膜集積回路装置は、図18等に示すように、電源回路、入出力回路、論理回路、CPU、メモリ等からなるが、ここでは、TFTを用いたCPU33と、メモリ34のみを図示した。

#### 【0044】

次に、薄膜集積回路42を保護するために、第1の層間絶縁膜46を形成する。ここでは、窒化珪素膜をプラズマCVD法によって形成したが、これに限定されるものではない。さらに、第2の層間絶縁膜47を形成する。これは、薄膜集積回路を平坦化するものであり、ポリイミド、アクリル、ポリアミドや、シロキサン等の耐熱性有機樹脂を、スピニコート法、ディップ法、スプレー法、液滴吐出法等によって形成することができる。また、無機材料を用いてもよく、その際には、PSG(リンガラス)、BPSG(リンボロンガラス)、アルミナ膜等を用いることができる。

#### 【0045】

次に、レジストをマスクとしてコンタクトホールをエッチング開孔し、薄膜集積回路同士を接続する配線45及びアンテナ48を形成した。導電材料としては、Ag、Au、Al、Cu、Zn、Sn、Ni、Cr、Fe、Co若しくはTi、又はそれらを含む合金を用いることができるが、これらに限定されるものではない。また、配線とアンテナで材料が異なっていても良い。なお、配線45及びアンテナ48は、展性、延性に富む金属材料を有するように形成し、更に好ましくは膜厚を厚くして変形による応力に耐えるようにするのが望ましい。

#### 【0046】

また、配線及びアンテナの形成方法としては、スパッタ法によって全面成膜した後、レジストマスクを用いてパターニングを行ってもよいし、液滴吐出法によってノズルから選択的に形成しても良い。なお、ここでいう液滴吐出法には、インクジェット法のみならず、オフセット印刷法やスクリーン印刷等も含まれる。

#### 【0047】

また、薄膜集積回路装置を内蔵する商品が、導電材料を含む場合には、それと同様の導電材料を用いて、アンテナ又は配線を形成しても良い。例えば、硬貨の材料を用いて硬貨の内部にアンテナを形成することができる。この場合、例えば、10円玉に薄膜集積回路装置を埋め込む場合には、銅、亜鉛、スズの合金からなるアンテナを形成すると良い。

#### 【0048】

次に、アンテナ上に、保護膜49を形成する。保護膜49としては、 DLC(ダイヤモンドライカーボン)或いは窒化炭素(CN)等の炭素を有する膜、又は窒化珪素膜或いは酸素を含む窒化珪素膜等を用いることができる。あるいは、ポリイミド、アクリル、ポリアミドや、シロキサン等の耐熱性有機樹脂を用いることができる。また、無機材料を用いてもよく、その際には、PSG(リンガラス)、BPSG(リンボロンガラス)、アルミナ膜等を用いることができる。また、エポキシ樹脂を用いることもできる。なお、これらの絶縁膜を積層させて、保護膜49を形成しても良い。

#### 【0049】

10

20

30

40

50

なお、ここでは、薄膜集積回路上に、第1の層間絶縁膜46、第2の層間絶縁膜47、保護膜49の3つの絶縁膜を形成したが、それらの材料は、互いに入れ替えて用いることができる。また、第1及び第2の層間絶縁膜46及び47を兼ねて、一層の層間絶縁膜としてもよい。いずれにしても、これらの絶縁膜に用いられる材料としては、後のC<sub>1</sub>F<sub>3</sub>(三フッ化塩素)等のハロゲン化フッ素によるエッチングによって冒されず、かつ耐熱性がある材料を用いるのが望ましい(図1(A))。

#### 【0050】

なお、層間絶縁膜46及び47や保護膜49としては、弾性の高い有機材料を用いるのが望ましい。これにより、変形時の応力は、有機材料を有する層間絶縁膜や保護膜に集中し、主にこれらの膜が変形するので、薄膜トランジスタへかかる応力が低減される。また変形が生じる場合に、最も応力が負荷される箇所(エッジ、角)が、半導体膜のエッジではなく下地膜のエッジとなるため、半導体膜のエッジや界面で生じる応力集中を抑えることができる。

#### 【0051】

次に、薄膜集積回路装置50の境界領域に、ダイシングによって溝93を形成する(図1(B))。この際、ダイシング装置(ダイサー;dicer)を用いるブレードダイシング法を用いるのが一般的である。ブレード(blade)とは、ダイヤモンド砥粒を埋め込んだ砥石で、その幅は約30~50μmであり、このブレードを高速回転させることにより、薄膜集積回路装置を分離する。また、ダイシングに必要なエリアをストリートと呼ぶが、この幅は、素子への損傷を考慮し、80~150μmとしておくのが望ましい。

#### 【0052】

なお、ダイシングの他にも、スクライビング又はマスクを利用したエッチング等によって行うことができる。スクライビングの場合には、ダイヤモンドスクライビング法とレーザースクライビング法等がある。また、エッチングの場合には、露光、現像工程によりマスクパターンを形成し、ドライエッチング、ウエットエッチング等により素子分離を行うことができる。ドライエッチングにおいては、大気圧プラズマ法を用いてもよい。

#### 【0053】

なお、溝を形成する場合、溝の深さは、少なくとも剥離層の表面が露出する程度とすればよく、基板41が繰り返し利用できるように、基板に傷が付かないように上記ダイシング等を適宜制御するのが望ましい。

#### 【0054】

次に、突起部58を有するジグ(支持基板)52を、仮接着剤51を介して、薄膜集積回路装置50毎に取り付ける。ここで、ジグ(治具)とは、剥離層を除去した後に薄膜集積回路装置がバラバラに分離しないように、一時的に薄膜集積回路装置を固定する役割を有する。ジグの形状としては、図1(C)のように、後にハロゲン化フッ素を含む気体又は液体の導入を容易にするために、突起部58を設けた櫛状の構造とするのが望ましいが、図4(C)のように平坦なジグを用いても構わない。突起部を有するジグ(治具、支持基板)を用いる場合には、基板をパターニングして用いればよい。また、ジグとしては、ハロゲン化フッ素によって冒されない酸化珪素を主成分とするガラス基板、石英基板、ステンレス(SUS)基板等を用いることができるが、ハロゲン化フッ素によって冒されない材料であれば、これらに限定されるものではない。また、ジグと薄膜集積回路との間に40は、仮接着するための接着剤が設けられている。

#### 【0055】

ここで、接着剤としては、UV光照射によって接着力(粘着力)が低下又は喪失する材料を用いることができる。ここでは、日東電工社製UV照射剥離テープを用いた。これ以外にも、例えば、前述した特開2001-30403、特許2992092、特開平6-299127に記載された、アクリル系粘着剤、合成ゴム系粘着剤、天然ゴム系粘着剤等を用いることができる。勿論、ジグを簡単に取り外すことができる材料であれば、これらに限定されるものではない。

#### 【0056】

10

20

30

40

50

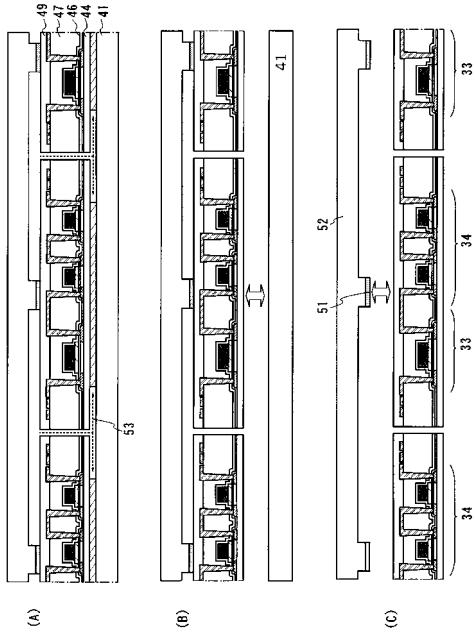

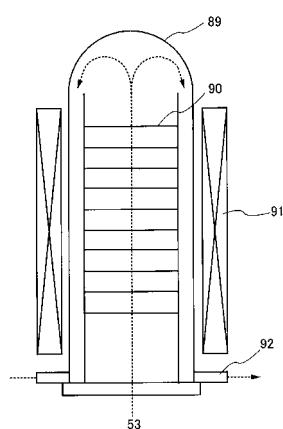

次に、溝93にハロゲン化フッ素ガスを導入することにより、剥離層43であるa-Si膜をエッチング除去した(図2(A))。ここで用いた減圧CVD装置(図12)は、反応空間であるベルジャー89内に、ClF<sub>3</sub>ガス等のハロゲン化フッ素ガス53が導入され、ガスが基板90に行き渡る仕組みになっている。また、ベルジャー89の外部にはヒーター91が設けられ、残余ガスは、排気管92から排出される。ここでは、図12に示すような減圧CVD装置を用い、ガス: ClF<sub>3</sub>、温度: 350°C、流量: 300 sccm、気圧: 6 Torr、時間: 3 hの条件でa-Si膜のエッチング除去を行ったが、この条件に限定されるものではない。また、ClF<sub>3</sub>ガスに窒素を混ぜたガスを用いてもよい。両者の流量比は適宜設定することができる。

## 【0057】

10

ここで、ClF<sub>3</sub>等のハロゲン化フッ素は、シリコンを選択的にエッチングするという特性がある反面、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiNx)、窒素を含む酸化珪素(SiO<sub>x</sub>Ny(x>y))、酸素を含む窒化珪素(SiN<sub>x</sub>Oy(x>y))はほとんどエッチングされない。したがって、時間の経過とともに剥離層43はエッチングされ、最終的に基板41を剥離することができる(図2(B))。一方、酸化珪素、窒化珪素、窒素を含む酸化珪素、酸素を含む窒化珪素等や、耐熱性樹脂からなる下地膜や、層間絶縁膜、保護膜はほとんどエッチングされないため、薄膜集積回路への損傷を防止することができる。なお、剥離した基板41は勿論再利用することができ、コスト削減に繋がる。

## 【0058】

20

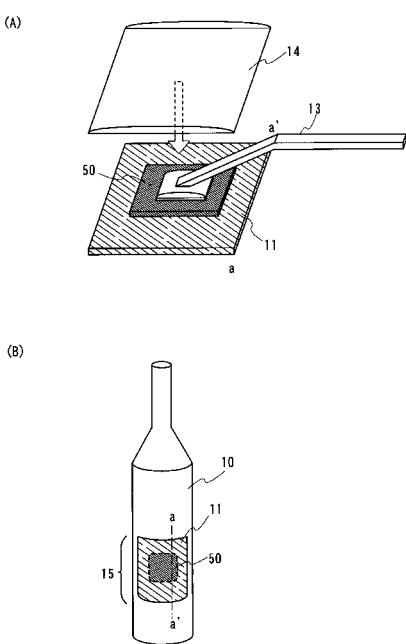

次に、UV光照射を行うことにより、仮接着剤51の粘着力を低下又は喪失させ、ジグ52と、薄膜集積回路装置とを分離することにより、薄膜集積回路装置を大量に作製することができる。なお、ジグは、コスト削減のため、再利用するのが望ましい。

## 【0059】

上記方法によって作製された薄膜集積回路装置50は、小型真空ピンセット13等により、搬送し、所望の製品に備え付けることができる。図3(A)、図3(B)は、商品10に貼付されるIDラベル15の作製方法を示したものである。ラベル11に薄膜集積回路装置50を小型真空ピンセット13により貼り付け、接着剤14で封止し、IDラベル15が完成する。さらに、商品10にIDラベル15を付して、リーダ/ライタ等によって情報を認識、更新、管理しうる商品が完成する。

## 【0060】

30

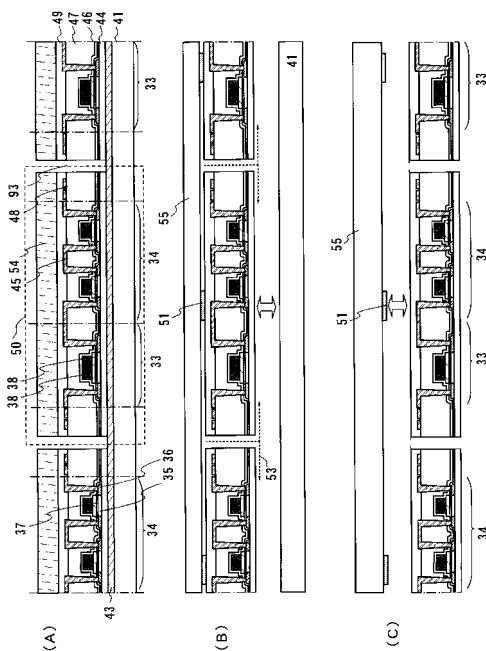

## (実施形態2)

本実施形態では、溝93を形成するにあたり、ドライエッチング法を用いる場合について、図4(A)~(C)を用いて説明する。実施形態1の記載に基づいて、図1(A)に示す保護膜49形成までを行う。その後、現像、露光工程を経て、基板上にレジスト54を形成し、レジスト54をマスクとして、ドライエッチングにより溝93を形成し、素子分離を行う(図4(A))。ここでは、プラズマエッチングを採用し、エッチング用ガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>もしくはCCl<sub>4</sub>などを代表とする塩素系ガス、CF<sub>4</sub>、SF<sub>6</sub>、NF<sub>3</sub>、CHF<sub>3</sub>などを代表とするフッ素系ガス、あるいはO<sub>2</sub>を用いたが、これらに限定されるものではない。なお、該エッチングは、大気圧プラズマを利用して行うこともできる。この際、エッチングガスとしては、CF<sub>4</sub>とO<sub>2</sub>の混合ガスを用いるのがよい。また、ガス種の異なるエッチングを複数回行うことによって溝93を形成しても良い。

40

## 【0061】

次に、仮接着剤51を介して、ジグ55を薄膜集積回路装置50に取り付け、ClF<sub>3</sub>等のハロゲン化フッ素によって、剥離層43を除去し、最終的に基板41を剥離した(図4(B))。剥離層43除去の具体的な方法は、実施形態1と同様である。なお、ジグ55として、ここでは、突起部を特に設けていない基板を用いたが、勿論、突起部を有した基板を用いてもよい。

## 【0062】

次に、UV光照射を行うことにより、仮接着剤51の粘着力を低下又は喪失させ、ジグ

50

55と、薄膜集積回路装置50とを分離する(図4(C))。これにより、薄膜集積回路装置50を大量に作製することができる。上記方法によって作製された薄膜集積回路装置50は、小型真空ピンセット等により、搬送し、所望の製品に備え付けることができる。

#### 【0063】

##### (実施形態3)

本実施形態では、ダイシング等によって溝93を形成する際に、基板41に傷が付いた場合、その基板を再利用する場合について図5(A)、図5(B)、図6(A)～図6(C)を用いて説明する。

#### 【0064】

まず、図5(A)に示すように、使用済み基板56上に平坦化膜57を形成する。平坦化膜としては、ポリイミド、アクリル、ポリアミドや、シロキサン等の耐熱性樹脂を、スピニコート法、ディップ法、スプレー法、液滴吐出法等によって形成することができる。後工程の熱処理を考慮すれば、シロキサン等の耐熱性樹脂を用いることが望ましい。また、無機材料を用いてもよく、その際には、PSG(リンガラス)、BPSG(リンボロンガラス)、アルミナ膜等を用いることができる。その後、実施形態1又は2に基づいて薄膜集積回路を作製、分離して所望の製品に備え付けることができる。

#### 【0065】

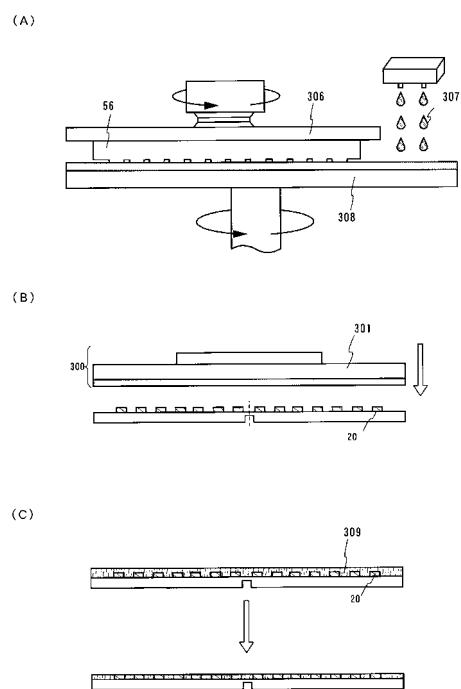

他の方法として、図6(A)～図6(C)に示すように、CMP(機械的化学的研磨)法、プレス法、エッチバック法等により、基板表面を平坦化する方法がある。CMP法(図6(A))の場合には、使用済み基板56の傷が微細である場合に特に有効である。CMP法は、研磨用パッド308内にスラリー(307)と呼ばれる研磨溶剤を供給し、ウェハキャリア306の回転とプラテンと呼ばれる回転台の回転による加圧と、研磨用パッドの研磨によって平坦化を行うものである。基板は、ガラス基板のように絶縁体であるので、スラリー307としては、アルカリ性のコロイド状シリカを混ぜたものが主に用いられる。また、プレス法(図6(B))の場合には、ヒーター301等の加熱機構を備えた装置300によってプレスを行うのがよい。また、エッチバック法(図6(C))では、絶縁膜309を平坦に形成した後に、エッチングを行って、平坦化するものである。その後、実施形態1又は2に基づいて薄膜集積回路装置を作製、分離して所望の製品に備え付けることができる。

#### 【0066】

##### (実施形態4)

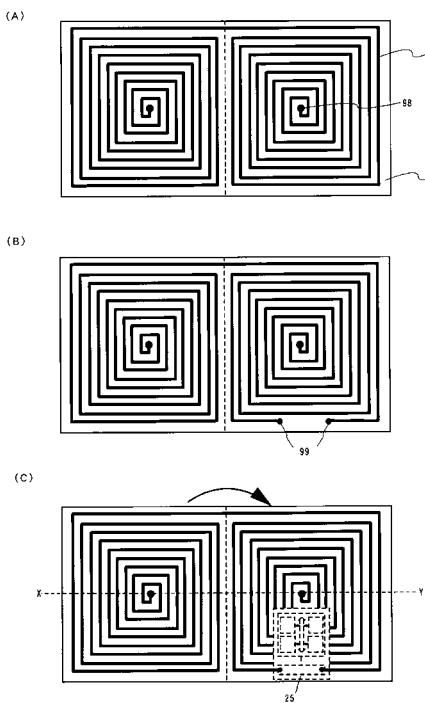

上記実施形態では、薄膜集積回路の作製工程において、アンテナを形成したが、本実施形態では、基板上に作製されたアンテナと、複数の薄膜集積回路からなる集積回路を別々に作製し、その後両者を接続する方法について、図7(A)～図7(C)、図8(A)～図8(E)、図9(A)、図9(B)、図10(A)、図10(B)、図18を用いて説明する。

#### 【0067】

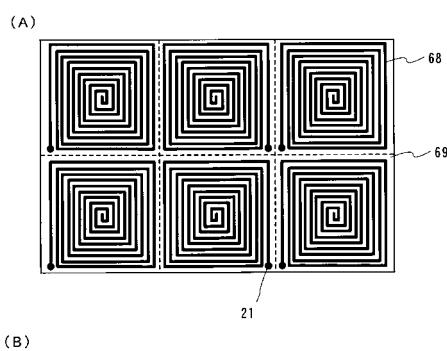

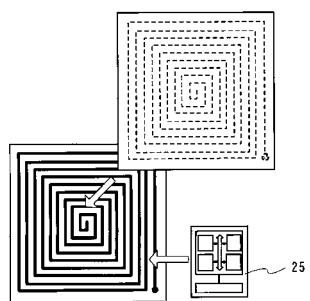

第1の方法は、図7(A)に示すように、折り曲げ可能なフレキシブル基板69上に、アンテナ68を形成し、別途形成した集積回路25を図7(B)に示すアンテナの接続部99と接続した後に、フレキシブル基板69を図7(C)に示すように半分に折りたたみ、封止して薄膜集積回路装置を作製するというものである。ここで、アンテナ68は、スピッタ法等によって形成した後にパターニング形成しても良いし、液滴吐出法を用い、導電材料を含む組成物を選択的に吐出した後に、該組成物を乾燥、焼成することにより形成しても良い。

#### 【0068】

なお、アンテナを形成した後に、図6(A)～図6(C)に示す、CMP法、プレス法、エッチバック法等により、平坦性を向上させても良い。CMP法の場合には、アンテナは導電性材料からなるので、スラリーとしては、酸性溶液にアルミナの微粉末を混ぜたものを用いるのがよい。また、プレス法の場合には、ヒーター301等の加熱機構を備えた装置によってプレスを行うのがよい。また、エッチバック法では、絶縁膜309を平坦に

10

20

30

40

50

形成した後に、エッティングを行って、平坦化するものである。なお、これらの平坦化処理工程は、薄膜集積回路の作製工程において用いることもできる。

#### 【0069】

アンテナには、アンテナ同士を接続する接続部98や、アンテナと集積回路を接続する接続部99を、アンテナ形成時に形成しておいても良い。また、集積回路との接続部99は、アンテナを形成した後に、アンテナの一部を切断することによって形成しても良い。なお、集積回路とアンテナとの接続は、異方性導電膜や、公知のボンディング法等を用いて行うことができる。また、アンテナの形状は、折り畳んだときに対称でコイル状であれば、図7(A)～図7(C)に示す形状に限定されない。

#### 【0070】

アンテナ基板に挟まれる集積回路25は、図18に示すように、電源回路26、入出力回路27、論理回路28、メモリ29、CPU30等に、リーダ/ライタ136との電波のやりとりを行うアンテナ回路が接続された構成を有している。

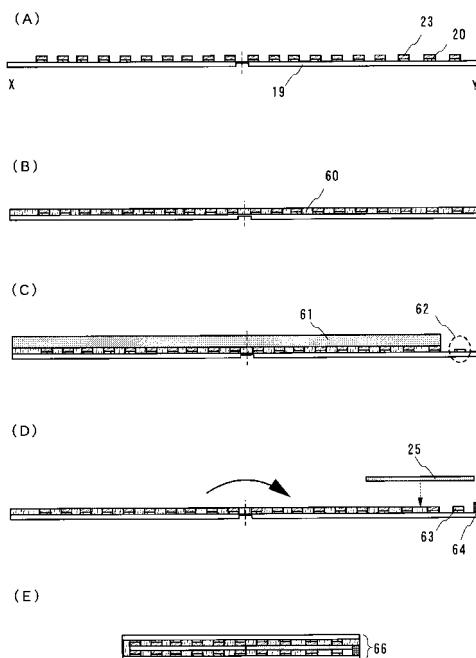

#### 【0071】

なお、図8(A)～図8(E)は、図7(C)のX-Y断面から見たアンテナ基板折り畳みの状態を示した図である。ここでは、アンテナ20をパターニング形成する際に用いたレジスト23をアッシング等によって除去してしまわずに、残存させた(図8(A))。さらに、平坦化膜60をスピンドル法、ディップ法、スプレー法、液滴吐出法等によつて形成し、平坦化を行った(図8(B))。さらに、集積回路25(ICチップ)との接続部を確保するために、レジスト61をマスクとして、エッティング又はアッシングを行い、コンタクト部62を形成した(図8(C))。さらに、異方性導電膜63を介して集積回路25を形成し、シール剤64を介して、アンテナが形成されたフレキシブル基板19を折り畳み(図8(D))、薄膜集積回路装置66を完成させた(図8(E))。この際、対向するアンテナ同士の間に配線等を設けてアンテナ同士を接続しても良い。ここで、レジスト23や平坦化膜60は、基板を折り畳んだ際に、アンテナや集積回路を保護するクッションの役割を果たす。なお、レジスト23や平坦化膜60は、一方又は両方を省略することもできる。

#### 【0072】

第2の方法は、図9(A)、図9(B)に示すように、基板69上にアンテナ68を複数形成しておき、基板69をダイシング等によって切り出し、アンテナ基板の間に集積回路25を挟む方法である。ここで、接続部21は、アンテナ同士を接続するために用いてもよいし、集積回路とアンテナとを接続するのに用いてもよい。また、接続部21は、アンテナの他の箇所に形成しても良い。なお、基板同士を貼り合わせる際に、アライメントマーカーを設ける必要があるが、該接続部21をマーカーとしても良い。

#### 【0073】

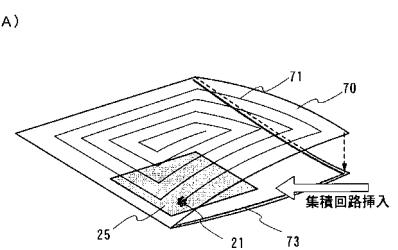

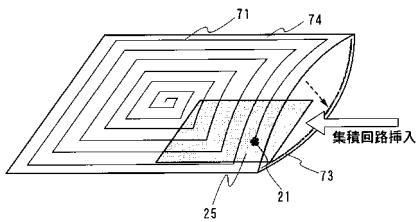

第3の方法は、図10(A)、図10(B)に示すように、二方が閉じられた食品を包装するラップ状のフレキシブル基板70や(図10(A))、三方が閉じられた封筒状のフレキシブル基板74に(図10(B))、アンテナ71を両面に形成しておき、その間に集積回路25(ICチップ)を挿入し、接着剤73で封止するという方法である。接続部21は開孔されており、アンテナ同士、又はアンテナと集積回路が接続することができる。ICチップは小型真空ピンセット等で設置すればよい。なお、アンテナは、これらの基板の内側に形成しておいても良い。

#### 【0074】

以上、本実施形態で述べた薄膜集積回路装置の作製方法は、特に、アンテナ基板と、集積回路(ICチップ)とを別々の製造者が作製し、中間生成品(部品)として流通させる場合に適した方法である。

#### 【0075】

##### (実施形態5)

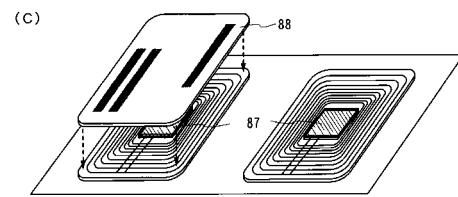

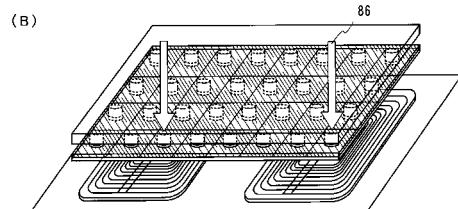

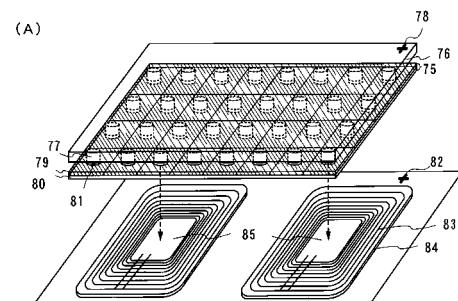

本実施形態では、図11(A)～図11(C)を参照して、素子基板75に仮接着したジグ76を取り外さずに、直接、商品84等に接着する方法について説明する。まず、実

10

20

30

40

50

施形態 1 ~ 3 に基づいて、素子基板 75 を形成し、仮接着剤 81 を介してジグ 76 を取り付ける。ジグ 76 としては、図 11 (A)、図 11 (B) に示すように、突起部 77 を有するものを用いた。仮接着剤としては、ここでは、UV 光照射によって粘着力が低下又は喪失する材料を用いる。また、素子への損傷を防ぐために、有機材料又は無機材料からなる層間膜 79 を設けている。そして、ClF<sub>3</sub> 等のハロゲン化フッ素によるエッチングにより、素子分離を行う。

#### 【0076】

次に、ジグ 76 に素子が仮接着された状態で搬送し、ID カード等の商品 84 が設置されたステージとのアライメントを行う。この際、図 11 (A) に示すように、ジグや、ステージに設けられたアライメントマーカー 78、82 を利用することもできるし、図示しないが、商品 84 に形成されたマーカーを利用することもできる。商品 84 内の薄膜集積回路装置が形成される部分には、予め接着剤 85 が形成されており、ジグを制御することにより、所望の素子を商品の所望の箇所に貼り付ける (図 11 (A))。

10

#### 【0077】

次に、商品 84 に貼り付けたい素子に、マスクを介して UV 光 86 を選択的に照射し、仮接着剤 81 の粘着力を低下又は喪失させることにより、ジグと素子とを分離する (図 11 (B))。これにより、所望の素子 (集積回路 87) を商品の所望の箇所に形成することができる。素子形成後、カバー 88 等により、素子部をカバーする (図 11 (C))。なお、ここでは、商品 84 の内部にアンテナ 83 が形成された場合を示したが、素子部にアンテナを形成しておいても良い。

20

#### 【0078】

本実施形態に示した本発明を用いることにより、ClF<sub>3</sub> 等のハロゲン化フッ素によるエッチングにより素子分離を行った際、素子がバラバラに分離することなく、所望の素子を所望の箇所に形成することができる。

#### 【実施例 1】

#### 【0079】

本実施例では、図 13 (A) ~ 図 13 (E)、図 14 (A) ~ 図 14 (E) を参照して、薄膜集積回路装置の集積回路部の具体的な作製方法について説明する。ここでは、簡単のため、n チャネル型 TFT と p チャネル型 TFT を用いた CPU とメモリの作製方法について説明する。

30

#### 【0080】

まず、基板 41 上に、剥離層 43 と、下地膜 44 を形成する (図 13 (A))。これらの材料や作製方法は、実施形態 1 ~ 実施形態 5 に述べたものを採用することができる。

#### 【0081】

次に、下地膜 44 上に、島状半導体膜 100 を形成する。島状半導体膜 100 は、アモルファス半導体、結晶性半導体、又はセミアモルファス半導体で形成する。いずれも、シリコン、シリコン・ゲルマニウム (SiGe) 等を主成分とする半導体膜を用いることができる。

#### 【0082】

本実施例では、70 nm の膜厚のアモルファスシリコンを形成し、さらにその表面を、シリコンの結晶化を促進する触媒元素、例えばニッケルを含む溶液で処理した後、500 ~ 750 °C の熱結晶化工程によって結晶性シリコン膜を得、さらにレーザー結晶化を行つて結晶性の改善を施した。また、成膜方法としては、プラズマ CVD 法、スパッタ法、LPCVD 法などを用いても良いし、結晶化方法としては、レーザー結晶化法、熱結晶化法、他の触媒元素 (Fe, Ru, Rh, Pd, Os, Ir, Pt, Cu, Au 等) を用いた熱結晶化、あるいはそれらを交互に複数回行っても良い。

40

#### 【0083】

また、非晶質構造を有する半導体膜の結晶化処理としては、連続発振のレーザーを用いても良く、結晶化に際し大粒径の結晶を得るために、連続発振が可能な固体レーザーを用い、基本波の第 2 高調波 ~ 第 4 高調波を適用するのが好ましい。代表的には、Nd : Y

50

V O<sub>4</sub>レーザー（基本波1064nm）の第2高調波（532nm）や第3高調波（355nm）を適用すればよい。連続発振のレーザーを用いる場合には、出力10Wの連続発振のYVO<sub>4</sub>レーザーから射出されたレーザー光を非線形光学素子により高調波に変換する。また、共振器の中にYVO<sub>4</sub>結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または橍円形状のレーザー光に成形して、被処理体に照射する。このときのエネルギー密度は0.01~100MW/cm<sup>2</sup>程度、好ましくは0.1~10MW/cm<sup>2</sup>が必要である。そして、10~2000cm/s程度の速度でレーザー光に対して相対的に半導体膜を移動させて照射すればよい。

## 【0084】

10

上記の方法によって結晶性シリコン膜を得た後、半導体膜上に酸化シリコン膜を介して、触媒元素をゲッタリングするためのアモルファスシリコン膜を成膜し、500~750の熱処理によってゲッタリング処理を行った。さらに、TFT素子としての閾値を制御するために、結晶性シリコン膜に対し、10<sup>13</sup>/cm<sup>2</sup>オーダーのドーズ量のホウ素イオンを注入した。その後、レジストをマスクとしてエッチングを行うことにより、島状半導体膜100を形成した。

## 【0085】

なお、結晶性半導体膜を形成するにあたっては、ジシラン(Si<sub>2</sub>H<sub>6</sub>)とフッ化ゲルマニウム(GeF<sub>4</sub>)の原料ガスとして、LPCVD(減圧CVD)法によって、多結晶半導体膜を直接形成することによっても、結晶性半導体膜を得ることができる。ガス流量比は、Si<sub>2</sub>H<sub>6</sub>/GeF<sub>4</sub>=20/0.9、成膜温度は400~500、キャリアガスとしてHe又はArを用いたが、これに限定されるものではない。

20

## 【0086】

次に、島状半導体膜100上にゲート絶縁膜102を形成する(図13(B))。ゲート絶縁膜102はプラズマCVD法又はスパッタリング法などの薄膜形成法を用い、窒化珪素、酸化珪素、酸素を含む窒化珪素又は窒素を含む酸化珪素を含む膜を、単層で、又は積層させて形成することが好ましい。積層する場合には、例えば、基板側から酸化珪素膜、窒化珪素膜、酸化珪素膜の3層構造とするのがよい。

## 【0087】

30

次に、ゲート電極103を形成する(図13(C))。本実施例では、30nmの膜厚のTaN(窒化タンタル)と、370nmの膜厚のW(タンゲステン)をスパッタ法により積層形成した後に、レジスト104をマスクとしてエッチングを行うことにより、ゲート電極103を形成した。ここで、レジストマスクの代わりに、酸化珪素等のマスクを用いてもよい。この場合、酸化珪素、窒素を含む酸化珪素等のマスク(ハードマスクと呼ばれる。)をパターニング形成工程が加わるが、エッチング時におけるマスクの膜減りがレジストよりも少ないため、所望の幅のゲート電極103を形成することができる。勿論、ゲート電極103の材料、構造、作製方法は、これに限定されるものではなく、適宜選択することができる。例えば、レジスト104を用いずに、液滴吐出法を用いて選択的にゲート電極103を形成しても良い。

## 【0088】

40

なお、ゲート電極103を形成するための導電材料としては、導電膜の機能に応じて種々の材料を選択することができるが、代表的なものとして、銀(Ag)、銅(Cu)、金(Au)、ニッケル(Ni)、白金(Pt)、クロム(Cr)、スズ(Sn)、パラジウム(Pd)、イリジウム(Ir)、ロジウム(Rh)、ルテニウム(Ru)、レニウム(Re)、タンゲステン(W)、アルミニウム(Al)、タンタル(Ta)、インジウム(In)、テルル(Te)、モリブデン(Mo)、カドミウム(Cd)、亜鉛(Zn)、鉄(Fe)、チタン(Ti)、シリコン(Si)、ゲルマニウム(Ge)、ジルコニウム(Zr)、バリウム(Ba)、アンチモン鉛、酸化スズ・アンチモン、フッ素ドープ酸化亜鉛、炭素、グラファイト、グラッシャーカーボン、リチウム、ベリリウム、ナトリウム、マグネシウム、カリウム、カルシウム、スカンジウム、マンガン、ジルコニウム、ガリウム

50

、ニオブ、ナトリウム - カリウム合金、マグネシウム / 銅混合物、マグネシウム / 銀混合物、マグネシウム / アルミニウム混合物、マグネシウム / インジウム混合物、アルミニウム / 酸化アルミニウム混合物、リチウム / アルミニウム混合物等、ハロゲン化銀の微粒子等、又は分散性ナノ粒子、あるいは、透明導電膜として用いられる酸化インジウムスズ (ITO : Indium Tin Oxide) 、酸化珪素を含む酸化インジウムスズ (酸化珪素を含むインジウム錫酸化物ともいう、以下、本明細書では「ITSO : indium tin silicon oxide」という。) 、酸化亜鉛 (ZnO : Zinc Oxide) 、ガリウムを添加した酸化亜鉛 (GZO) 、酸化インジウムに 2 ~ 20 % の酸化亜鉛を混合した酸化インジウム亜鉛 (IZO : Indium Zinc Oxide) 、有機インジウム、有機スズ、窒化チタン等を適宜採用することができる。

10

#### 【0089】

なお、ゲート電極 103 をエッティング形成する際のエッティングガスとしては、CF<sub>4</sub>、Cl<sub>2</sub> 及び O<sub>2</sub> の混合ガスや Cl<sub>2</sub> ガスを用いたが、これに限定されるものではない。

#### 【0090】

次に、p チャネル型 TFT 109, 111 となる部分をレジスト 118 で覆い、ゲート電極 103 をマスクとして、n チャネル型 TFT 108, 110 の島状半導体膜に、第 1 の不純物導入工程として n 型を付与する不純物元素 119 (代表的には P (リン) 又は As (砒素)) を低濃度に導入する (図 13 (D))。第 1 の不純物導入の条件は、ドーズ量 :  $1 \times 10^{13} \sim 6 \times 10^{13}$  / cm<sup>2</sup>、加速電圧 : 50 ~ 70 keV としたが、これに限定されるものではない。この第 1 の不純物導入によって、ゲート絶縁膜 102 を介してスルードープがなされ、一対の低濃度不純物領域 120 が形成される。なお、第 1 の不純物導入は、p チャネル型 TFT 領域をレジストで覆わずに、全面に行っても良い。

20

#### 【0091】

次に、レジスト 118 をアッシング等により除去した後、n チャネル型 TFT 領域を覆うレジスト 121 を新たに形成し、ゲート電極をマスクとして、p チャネル型 TFT 109, 111 の島状半導体膜に、第 2 の不純物導入工程として p 型を付与する不純物元素 122 (代表的には B (ホウ素)) を高濃度に導入する (図 13 (E))。第 2 の不純物導入の条件は、ドーズ量 :  $1 \times 10^{16} \sim 3 \times 10^{16}$  / cm<sup>2</sup>、加速電圧 : 20 ~ 40 keV として行う。この第 2 の不純物導入によって、ゲート絶縁膜 102 を介してスルードープがなされ、一対の p 型の高濃度不純物領域 123 が形成される。

30

#### 【0092】

次に、レジスト 121 をアッシング等により除去した後、基板表面に、絶縁膜 105 を形成した (図 14 (A))。ここでは、膜厚 100 nm の窒素を含む酸化珪素 (SiON) 膜と、膜厚 200 nm の酸化膜の 2 層構造とした。ここでは、SiON 膜は、プラズマ CVD 法で形成し、酸化膜としては、酸化珪素膜を減圧 CVD 法で形成した。その後、図示しないが、基板の TFT が形成された側をレジストで覆い、基板の裏面に形成された絶縁膜をエッティング除去した (裏面処理)。

#### 【0093】

次に、レジストを残したまま、エッチバック法により、レジスト及び絶縁膜 105 をエッティング除去し、サイドウォール (側壁) 106 を自己整合的 (セルフアライン) に形成した (図 14 (B))。エッティングガスとしては、CHF<sub>3</sub> と He の混合ガスを用いた。なお、サイドウォールを形成する工程は、これらに限定されるものではない。

40

#### 【0094】

次に、p チャネル型 TFT 領域を覆うレジスト 124 を新たに形成し、ゲート電極 103 及びサイドウォール 106 をマスクとして、第 3 の不純物導入工程として、n 型を付与する不純物元素 125 (代表的には P 又は As) を高濃度に導入する (図 14 (C))。第 3 の不純物導入の条件は、ドーズ量 :  $1 \times 10^{13} \sim 5 \times 10^{15}$  / cm<sup>2</sup>、加速電圧 : 60 ~ 100 keV として行う。この第 3 の不純物導入によって、ゲート絶縁膜 102 を介してスルードープがなされ、一対の n 型の高濃度不純物領域 126 が形成される。

#### 【0095】

50

なお、図示しないが、レジスト124をアッシング等により除去した後、不純物領域の熱活性化を行っても良い。例えば、50nmの窒素を含む酸化珪素膜を成膜した後、550、4時間、窒素雰囲気下において、加熱処理を行えばよい。また、水素を含む窒化珪素膜(SiNx膜)を、100nmの膜厚に形成した後、410、1時間、窒素雰囲気下において、加熱処理を行うことにより、結晶性半導体膜の欠陥を改善することができる。これは、例えば、結晶性シリコン中に存在するダンギリングボンドを終端させるものであり、水素化処理工程などと呼ばれる。さらに、この後、TFTを保護するキャップ絶縁膜として、膜厚600nmのSiON膜を形成する。なお、水素化処理工程は、該SiON膜形成後に行っても良い。この場合、窒化珪素膜の上に窒素を含む酸化珪素膜を順次成膜した絶縁膜は連続成膜することができる。このように、TFT上には、基板側から、窒素を含む酸化珪素膜、窒化珪素膜、窒素を含む酸化珪素膜を順次積層した3層の絶縁膜が形成されることになるが、その構造や材料はこれらに限定されるものではない。また、これらの絶縁膜は、TFTを保護する機能をも有しているため、できるだけ形成しておくのが望ましい。

10

#### 【0096】

次に、TFT上に、層間絶縁膜107を形成する。層間絶縁膜107として、ポリイミド、アクリル、ポリアミドや、シロキサン等の耐熱性有機樹脂を用いることができる。形成方法としては、その材料に応じて、スピンドルコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を採用することができる。また、無機材料を用いてもよく、その際には、PSG(リンガラス)、BPSG(リンボロンガラス)、アルミナ膜等を用いることができる。なお、これらの絶縁膜を積層させて、層間絶縁膜107を形成しても良い。

20

#### 【0097】

次に、レジストを形成した後、エッチングによりコンタクトホールを開孔し、配線128及びアンテナ48を形成する(図14(D))。コンタクトホール開孔時のエッチングに用いられるガスは、CHF<sub>3</sub>とHeの混合ガスを用いたが、これに限定されるものではない。

#### 【0098】

また、配線128とアンテナ48は同一材料を用いて同時に形成しても良いし、別々に形成しても良い。ここでは、TFTと接続される配線128は、基板側から、Ti、TiN、Al-Si、TiN、Tiを順次積層した5層構造とし、スパッタ法によって形成した後、パターニング形成した。

30

#### 【0099】

なお、A1層において、Siを混入させることにより、配線パターニング時のレジストペークにおけるヒロックの発生を防止することができる。また、Siの代わりに、0.5%程度のCuを混入させても良い。また、TiやTiNでAl-Si層をサンドイッチすることにより、耐ヒロック性がさらに向上する。なお、パターニング時には、窒素を含む酸化珪素(SiON)等からなる上記ハードマスクを用いるのが望ましい。なお、配線の材料や、形成方法はこれらに限定されるものではなく、前述したゲート電極に用いられる材料を採用しても良い。また、アンテナ48を形成する際には、上記実施の形態に示した、種々の材料、方法を用いることができる。配線とアンテナは、同時に形成しても良いし、一方を先に形成した後に、他方が乗り上げるように形成しても良い。

40

#### 【0100】

次に、配線及びアンテナ上に、保護膜49を形成し、CPU33及びメモリ34が完成する(図14(E))。保護膜49としては、 DLC(ダイヤモンドライクカーボン)あるいは窒化炭素(CN)等の炭素を有する膜、又は窒化珪素膜或いは酸素を含む窒化珪素膜等を用いることができる。形成方法としては、プラズマCVD法や、大気圧プラズマ等を用いることができる。

#### 【0101】

あるいは、ポリイミド、アクリル、ポリアミド、レジスト又はベンゾシクロブテン等の感光性又は非感光性の有機材料や、シロキサン等の耐熱性有機樹脂、を用いることができる。形成方法としては、その材料に応じて、スピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーラー、カーテンコーラー、ナイフコーラー等を採用することができる。あるいは、塗布法により得られるSOG膜（例えば、アルキル基を含むSiO<sub>x</sub>膜）を用いることもできる。また、無機材料を用いてもよく、その際には、酸化珪素、窒化珪素、窒素を含む酸化珪素、酸素を含む窒化珪素、PSG（リンガラス）、BPSG（リンボロンガラス）、アルミナ膜等を用いることができる。なお、これらの絶縁膜を積層させて、保護膜49を形成しても良い。

10

#### 【0102】

その後、本実施例によって作製された複数のTFTは、上記実施の形態に示す要領でICチップ毎に分離され、商品等に組み込むことができる。なお、本実施例では、トップゲート構造としたが、ボトムゲート構造（逆スタガ構造）としてもよい。

#### 【実施例2】

#### 【0103】

本実施例では、実施例1のプロセスにおいて、高温ポリシリコン（HPS）を採用した場合について説明する。一般に、ガラス基板の耐熱温度（約600℃）以上の結晶化プロセスを含む半導体プロセスを、高温プロセスと呼ぶ。

#### 【0104】

半導体膜を形成した後に、Ni、Fe、Ru、Rh、Pd、Os、Ir、Pt、Cu、Au等の上記触媒を添加し、LPCVD炉において加熱処理を行う。約700℃以上で、半導体膜中に結晶核が発生し、結晶化が進行する。

20

#### 【0105】

その後、島状半導体膜を形成した後、LPCVDによって、ゲート絶縁膜を形成する。例えば、シラン系ガスにN<sub>2</sub>やO<sub>2</sub>を混合させたガスを用い、900℃以上の高温で、酸化膜を形成する。

#### 【0106】

次に、リン等のn型不純物を含むポリシリコン（p-Si）を150nmの膜厚で成膜することにより、ゲート電極を形成する。さらに、W-Si（タンゲステンシリサイド）を150nmの膜厚で成膜してもよい。形成方法は、スパッタ法、CVD法等を適宜採用することができる。その後のドーピング工程は、実施例1と同様に形成することができる。

30

#### 【0107】

不純物導入工程の後、950℃、30分の熱活性化を行い、不純物領域を活性化させる。さらに、BPSG（リンボロンガラス）を用いてリフローを行い、レジストを用いたエッチバック法により、平坦化を行う。さらに、350℃の水素化アニールを行い、プラズマダメージを回復させる。

#### 【0108】

その他の工程は、実施例1と同様に行うことができる。なお、本実施例では、トップゲート構造としたが、ボトムゲート構造（逆スタガ構造）としてもよい。なお、本実施例は、他の実施形態、実施例と自由に組み合わせることができる。

40

#### 【実施例3】

#### 【0109】

本実施例では、実施例1のプロセスにおいて、島状半導体膜100として、セミアモルファスシリコン（SAS）を採用した場合について説明する。SASは、珪化物気体をグロー放電分解することにより得ることができる。代表的な珪化物気体としては、SiH<sub>4</sub>であり、その他にもSi<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>などを用いることができる。この珪化物気体を水素、水素とヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して用いることでSASの形成

50

を容易なものとすることができます。希釈率は10倍～1000倍の範囲で珪化物気体を希釈することが好ましい。勿論、グロー放電分解による被膜の反応生成は減圧下で行うが、圧力は概略0.1Pa～133Paの範囲で行えば良い。グロー放電を形成するための電力は1MHz～120MHz、好ましくは13MHz～60MHzの高周波電力を供給すれば良い。基板加熱温度は300度以下が好ましく、100～200度の基板加熱温度が推奨される。

#### 【0110】

また、珪化物気体中に、CH<sub>4</sub>、C<sub>2</sub>H<sub>6</sub>などの炭化物気体、GeH<sub>4</sub>、GeF<sub>4</sub>などのゲルマニウム化気体を混入させて、エネルギー bandwidth幅を1.5～2.4eV、若しくは0.9～1.1eVに調節しても良い。

10

#### 【0111】

また、SASは、価電子制御を目的とした不純物元素を意図的に添加しないときに弱いn型の電気伝導性を示す。これは、アモルファス半導体を成膜するときよりも高い電力のグロー放電を行うため酸素が半導体膜中に混入しやすいためである。そこで、TFTのチャネル形成領域を設ける第1の半導体膜に対しては、p型を付与する不純物元素を、この成膜と同時に、或いは成膜後に添加することで、しきい値制御をすることが可能となる。p型を付与する不純物元素としては、代表的には硼素であり、B<sub>2</sub>H<sub>6</sub>、BF<sub>3</sub>などの不純物気体を1ppm～1000ppmの割合で珪化物気体に混入させると良い。例えば、p型を付与する不純物元素としてボロンを用いる場合、該ボロンの濃度を $1 \times 10^{14} \sim 6 \times 10^{16}$ atoms/cm<sup>3</sup>とすると良い。なお、上記SASでチャネル形成領域を構成することにより $1 \sim 10 \text{ cm}^2/\text{V} \cdot \text{sec}$ の電界効果移動度を得ることができる。なお、本実施例は、他の実施形態、実施例と自由に組み合わせることができる。

20

#### 【実施例4】

#### 【0112】

本実施例では、図15(A)～図15(C)を用いて、実施例1に示した集積回路部の構造とは異なる構造について説明する。

#### 【0113】

図15(A)は、CPU33とメモリ34のアンテナ112をゲート電極103と同一層(同一レイヤー)に形成する例を示している。すなわち、ゲート電極103の材料を用いて、ゲート電極103形成と同時に所望の形状にエッチングしたり、印刷法により導電ペースト(具体的にはAg、Au、Cu、Alペースト)を用いて形成したり、ゲート絶縁膜に凹部を形成しアンテナ材料を流し込んで形成することができる。

30

#### 【0114】

図15(B)は、層間膜115上にアンテナ114及び保護膜116を形成する場合に、上部配線113によって、アンテナとTFTとを接続する例を示している。上部配線113の材料としては、実施例1に示した導電材料から適宜採用することができる。このように、高さ方向に配線を形成することにより、素子の微細化を図ることができる。

#### 【0115】

図15(C)は、CPU33、メモリ34等の薄膜集積回路を積層させた構造を示している。この場合、各薄膜トランジスタ117上に形成されている層間膜115は、すべて弾性の高い有機材料を有するように形成するのが望ましい。例えば、ポリイミド、アクリル、ポリアミド、レジスト又はベンゾシクロブテン等の感光性又は非感光性の有機材料や、シロキサン等の耐熱性有機樹脂、を用いることができる。形成方法としては、その材料に応じて、スピンドルコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を採用することができる。これにより、変形時の応力は、有機材料を有する層間絶縁膜や保護膜に集中し、主にこれらの膜が変形するので、薄膜トランジスタへかかる応力が低減される。なお、本実施例は、他の実施形態、実施例と自由に組み合わせることができる。

40

#### 【実施例5】

50

**【0116】**

本実施例では、図16～図18を参照して、本発明に係る薄膜集積回路装置（IDラベル）を搭載した商品の管理方法及び情報や商品の流れについて説明する。なお本実施の例では、IDラベルは非接触型である場合で説明する。

**【0117】**

図16に示すように、製造者からの商品出荷前又は販売者による商品陳列前に商品管理に必要な情報をホストコンピュータに入力する。例えば、IDラベル15が搭載された複数の商品10（又はそれらが梱包された箱、段ボール等）を、ベルトコンベアのような搬送手段22によって、リーダ／ライタ16にくぐらせ、リーダ／ライタアンテナ17から出された電波18をIDラベル15が受け取り、IDラベル15のアンテナから戻ってきた電波によって、コンピュータ137へ商品に関する情報を入力させる。このとき、コンピュータに直接リーダ／ライタを接続しておくこともできる。10

**【0118】**

IDラベル15に記録される多量の商品に関する情報は即座にコンピュータ137へ入力することができる。そしてコンピュータは、商品に関する情報を処理する機能を有するソフトを備えている。もちろんハードで情報処理を行ってもよい。その結果、従来のようにバーコードを一つずつ読み取る作業と比較して、情報処理に費やす時間、労力やミスが低減され、商品管理への負担が軽減される。

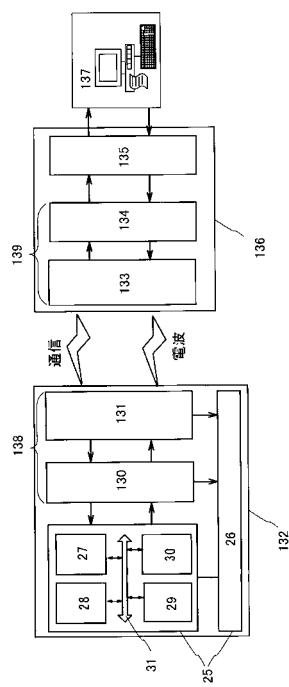

**【0119】**

ここで、非接触型薄膜集積回路装置を用いた通信原理を、図18を参照して簡単に説明する。非接触型薄膜集積回路装置を有する商品等を、リーダ／ライタ136にかざすことにより、非接触型薄膜集積回路装置132内のアンテナ回路138が、リーダ／ライタ136のアンテナ回路139から発信される電波を受信し、電源回路26において、共振作用により起電力が発生（電磁誘導等）する。そして、非接触型薄膜集積回路装置132内の薄膜集積回路25（ICチップ）が起動し、チップ内の情報を信号化した後、カード側のアンテナ回路から信号を発信する。該信号をリーダ／ライタ136のアンテナ回路139でキャッチし、コントローラ135を介してデータ処理を行うホストコンピュータ137へ送信される。なお、ホストコンピュータがリーダ／ライタ手段を有していても構わない。また、ICチップのアンテナ回路部は、RF（無線）インターフェース130と、非接触インターフェース131とを、リーダ／ライタのアンテナ回路部は非接触インターフェース133と、インターフェース回路134とを有しているが、この構成に限定されるものではない。2030

**【0120】**

メモリ29にはROM（Read Only Memory）、RAM（Random Access Memory）、PROM、EPROM又はEEPROM（Electrically Erasable and Programmable Read Only Memory）、FRAM（登録商標）（FeRAM；Ferroelectric Random Access Memory）等が利用される。PROMやEPROMの場合はカードを発行する時以外は書き込みができないが、EEPROMは書き換えが可能である。これらメモリは、用途に応じて選択すればよい。40

**【0121】**

電源回路26は、例えばダイオードと、容量とを有する構成であればよく、アンテナが受信する交流周波を直流に変換する機能を有している。

**【0122】**

非接触型のICの特徴は、コイル状に巻かれたアンテナの電磁誘導作用（電磁誘導方式）、相互誘導作用（電磁結合方式）又は静電気による誘導作用（静電結合方式）により電力が供給される点である。このアンテナの巻き数を制御することにより、受信する周波数の高さを選ぶことができる。

**【0123】**

なお、図示しないが、暗号処理専用のコプロセッサと呼ばれる演算装置をCPUに接続

50

しても良い。これにより、決済等のアプリケーションを行う際に必要となる暗号処理を行うことができる。

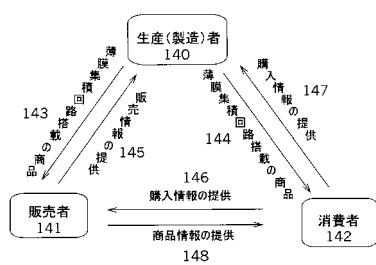

#### 【0124】

また、生産（製造）者140、販売者141、及び消費者142間の情報や商品の流れを図17に示す。生産（製造）者140は販売者（小売業者、卸業者等）141又は消費者142に薄膜集積回路装置搭載の商品143、144を提供する。そして販売者141は、例えば消費者142の精算時に料金情報、商品の売れ個数や購入時間等の販売情報145を生産（製造）者140に提供することができる。一方消費者142は、個人情報等の購入情報146、147を提供することができる。例えば、薄膜集積回路装置搭載のクレジットカード、又は個人のリーダ等により購入情報を販売者141や生産（製造）者140へネットを介して提供できる。また、販売者141は、薄膜集積回路装置により、消費者に商品情報148を提供し、販売者141は消費者142から購入情報を得ることができる。このような販売情報や購入情報等は、貴重な情報であり、今後の販売戦略に役立つ。10

#### 【0125】

各種情報を提供する手段としては、薄膜集積回路装置から販売者141や消費者142の有するリーダが読み取った情報をコンピュータやネットワークを介して、その情報を生産（製造）者140、販売者141又は消費者142に開示する方法がある。以上のような、多種多様な情報が薄膜集積回路装置を介して必要な者へ提供することができ、本発明に係る薄膜集積回路装置は商品取引又は商品管理上でも有用である。20

#### 【実施例6】

#### 【0126】

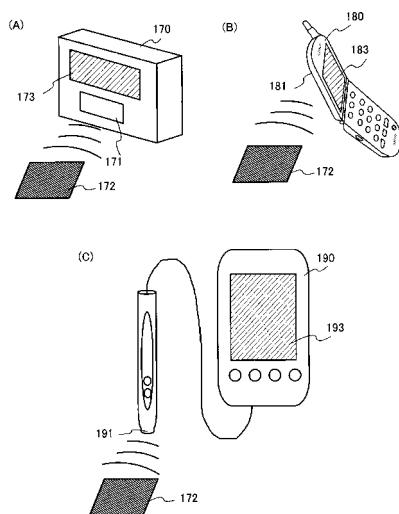

本実施例では、図19（A）～図19（C）を参照して、本発明に係る薄膜集積回路装置（IDラベル）搭載の商品において、情報を読み取る方法について説明する。なお本実施の形態では、IDラベルは非接触型である場合で説明する。

#### 【0127】

図19（A）に示すようなリーダ／ライタ本体170のセンサー部171に、IDラベルが搭載された商品172をかざす。そして表示部173には、商品の原材料や原産地、生産（製造）工程ごとの検査結果や流通過程の履歴等が表示され、更に商品の説明等の商品に関する情報を表示させる。もちろんリーダ／ライタに表示部を必ず設ける必要はなく、別に設けられてもよい。このようなリーダ／ライタは商品が陳列されている棚に設置しておけばよい。30

#### 【0128】

また図19（B）に示すように、個人が所有する携帯情報端末、例えば携帯電話機本体180に、リーダ機能を搭載させ、本体の一部に設けられたセンサー部181にIDラベルが搭載された商品172をかざし、表示部183に情報を表示させる。すると同様に、商品に関する情報が表示される。もちろんリーダ／ライタに表示部を必ず設ける必要はなく、別に設けられてもよい。

#### 【0129】

また図19（C）に示すように、個人が所有する携帯可能なリーダ本体190と接続されているセンサー部191にIDラベルが搭載された商品172をかざし、表示部193に情報を掲載させる。すると同様に、商品に関する情報が表示される。もちろんリーダ／ライタに表示部を必ず設ける必要はなく、別に設けられてもよい。40

#### 【0130】

本実施例では非接触型のリーダ／ライタについて説明したが、接触型であっても表示部に情報を表示させればよい。また非接触型又は接触型の薄膜集積回路装置が搭載される商品自体に表示部を設け、情報を表示させても構わない。

#### 【0131】

このように、従来の無線タグ等により提供される情報と比べて、消費者は商品に関する豊富な情報を自由に入手することができる。勿論、薄膜集積回路装置により商品管理を素50

早く正確に行うことができる。

【0132】

なお、本発明に係る非接触型の薄膜集積回路は、カードリーダ／ライタとの距離が2m以下である遠隔型、70cm以下である近傍型、10cm以下である近接型、数cmである密着型とすることができます、生産、製造現場での作業を考えると近傍型又は密着型が好ましい。

【0133】

周波数は、遠隔型ではマイクロ波、2.45GHz、近傍型及び近接型では、13.56MHz、密着型では4.91MHz、125kHzが一般的に使用されているが、周波数を高め波長を短くすることによりアンテナの巻き数を小さくできる。

10

【0134】

また非接触型薄膜集積回路は接触型薄膜集積回路と比較すると、リーダ／ライタに接触せず、非接触で電源供給及び情報通信を行うため、破損せず、高い耐久性を有し、静電気等によるエラーの心配がない。更にはリーダ／ライタ自体の構成は複雑にならならず、薄膜集積回路をリーダ／ライタにかざせばよいので、取り扱いが容易である。

【実施例7】

【0135】

本実施例では、図20、図21を参照して、本発明に係る薄膜集積回路、又は非接触型薄膜集積回路装置（無線チップ、IDラベル）を搭載した商品の一例について説明する。

20

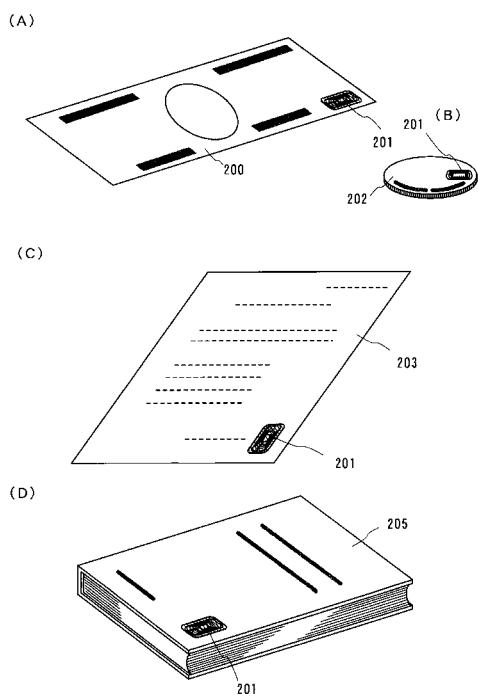

【0136】

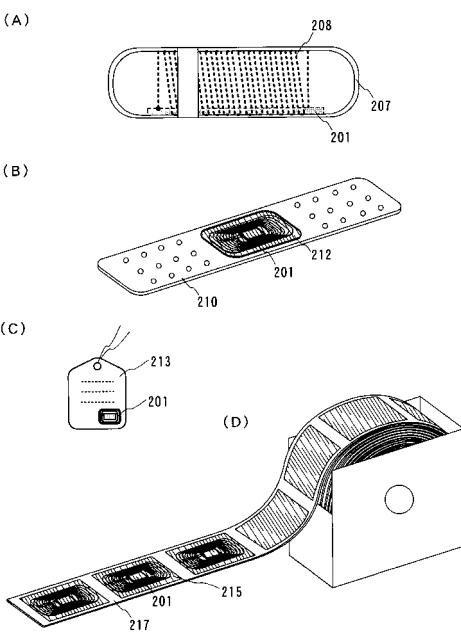

図20（A）は、薄膜集積回路装置201を内蔵した紙幣200であり、他に証券、チケット、T/C（トラベラーズチェック）等であってもよい。図20（B）は、薄膜集積回路装置201を内蔵した硬貨202であり他にメダルであってもよい。図20（C）は、薄膜集積回路装置201を内蔵した住民票、戸籍謄本等の書類203を示している。図20（D）は、薄膜集積回路装置201をブックカバーに内蔵した書籍205を示している。

【0137】

本発明に係る非接触型又は接触型の薄膜集積回路は非常に薄いため、上記紙幣、コイン、書類、書籍等の物品に薄膜集積回路を搭載しても、機能、デザイン性を損ねることがない。更に非接触型薄膜集積回路の場合、アンテナとICとを一体形成でき、曲面を有する商品に直接転写することが容易になる。

30

【0138】

図21（A）は、薄膜集積回路装置201を内蔵したカプセル207を示している。カプセル207の内部には、コイル状のアンテナ208が形成されており、外部のリーダ／ライタによって通信を行うことができる。例えば、人間や動物に、カプセル207を服用させることにより、その人間や動物の健康状態等の情報を即座に入手することができる。

【0139】

図21（B）は、薄膜集積回路装置201を内蔵した絆創膏210を示している。ガーゼとなるカバー212の裏側に薄膜集積回路装置201を設けることで通常の絆創膏として使用できる。このように、様々な医療器具等にも、本発明を用いることができる。

40

【0140】

図21（C）は、薄膜集積回路装置201を内蔵したIDタグ213を示している。IDタグ213を商品に備え付けることにより、商品管理が容易になる。例えば、商品が盗難された場合に、商品の経路を辿ることによって、その犯人を迅速に把握することができる。このように、IDタグを備えることにより、所謂トレーサビリティ（traceability；複雑化した製造、流通の各段階で問題が生じた場合に、経路を遡ることによって、その原因を迅速に把握できる態勢を整えること。）に優れた商品を流通させることができる。

【0141】

図21（D）は、ラベル台紙217に貼られた薄膜集積回路装置201を内蔵したIDラベル215を示している。IDラベル上には、その商品や役務に関する情報（商品名、

50

ブランド、商標、商標権者、販売者、製造者等)が記されており、一方、内蔵されている薄膜集積回路装置には、その商品(又は商品の種類)固有のIDナンバーが付されており、偽造や、商標権、特許権等の知的財産権侵害、不正競争等の不法行為を容易に把握することができる。また、薄膜集積回路装置内には、商品の容器やラベルに明記しきれない多大な情報、例えば、商品の产地、販売地、品質、原材料、効能、用途、数量、形状、価格、生産方法、使用方法、生産時期、使用時期、賞味期限、取扱説明、商品に関する知的財産情報等を入力しておくことができ、取引者や消費者は、簡易ナリーダによって、それらの情報にアクセスすることができる。また、生産者側からは容易に書換え、消去等も可能であるが、取引者、消費者側からは書換え、消去等ができない仕組みになっている。

## 【0142】

10

また、図示しないが、人体、動物に有害でない金属や有機材料等を用いた薄膜集積回路装置を作製し、食品等に混入させ、食事状況を管理することも可能である。

## 【0143】

上述した商品以外にも、あらゆる商品に、本発明に係る薄膜集積回路、非接触型薄膜集積回路装置を利用することができる。

## 【実施例8】

## 【0144】

20

上記実施形態又は実施例では、主に非接触型薄膜集積回路装置について説明したが、本発明に係る薄膜集積回路は、勿論、接触型薄膜集積回路装置にも採用することができる。例えば、磁気ストライプ型や、ICモジュール接点型のチップとすることができる。接触型ICの場合はアンテナを設けない構成とすればよい。また、これらの磁気ストライプ型又はICモジュール接点型の薄膜集積回路装置と、非接触型薄膜集積回路装置とを組み合わせた構造としても良い。

## 【産業上の利用可能性】

## 【0145】

30

本発明に係る薄膜集積回路の作製方法、非接触型薄膜集積回路装置並びにその作製方法は、従来のシリコンウエハを用いて作製するICチップの作製方法に比べ、製造コストを大幅に削減することができる。本発明を用いることにより、薄膜集積回路装置に用いられる薄膜集積回路、非接触型薄膜集積回路装置や、それを用いた商品等を、低成本で大量に高歩留まり、高スループットで作製することができる。また、本発明に係る薄膜集積回路の作製方法は、接触型、非接触型薄膜集積回路装置のいずれにも採用することができ、その利用範囲は極めて広い。

## 【図面の簡単な説明】

## 【0146】

【図1】図1は本発明を用いた薄膜集積回路装置の作製工程図である。

【図2】図2は本発明を用いた薄膜集積回路装置の作製工程図である。

【図3】図3は本発明に係る薄膜集積回路装置を商品に貼付する方法を説明する図である。

【図4】図4は本発明を用いた薄膜集積回路装置の作製工程図である。

【図5】図5は使用済み基板を再利用する場合を説明する図である。

40

【図6】図6は平坦化処理を説明する図である。

【図7】図7は本発明を用いた薄膜集積回路装置の作製工程図(折りたたみアンテナ)である。

【図8】図8は本発明を用いた薄膜集積回路装置の作製工程図(折りたたみアンテナ)である。

【図9】図9は本発明を用いた薄膜集積回路装置の作製工程図(サンドイッチ構造)である。

【図10】図10は本発明を用いた薄膜集積回路装置の作製工程図(ラップ、封筒構造)である。

【図11】図11は本発明を用いたIDカードの作製工程図(選択的UV光照射)である

50

。

- 【図12】図12は本発明に用いる減圧CVD装置の概略図である。

- 【図13】図13は本発明に係るCPU、メモリの作製工程図である。

- 【図14】図14は本発明に係るCPU、メモリの作製工程図である。

- 【図15】図15は本発明に係るCPU、メモリの作製工程図である。

- 【図16】図16は本発明に係る非接触型薄膜集積回路装置を搭載した商品情報のリーディング、ライティングを示す図である。

- 【図17】図17は生産者(製造者)、販売者、消費者との関係を示す図である。

- 【図18】図18は本発明に係る非接触型薄膜集積回路装置の原理を説明する図である。

- 【図19】図19はリーダ／ライタの一例を説明する図である。 10

- 【図20】図20は本発明に係る薄膜集積回路装置を有する商品の一例を説明する図である。

- 【図21】図21は本発明に係る薄膜集積回路装置を有する商品の一例を説明する図である。

- 【符号の説明】

- 【0147】

- 43：剥離層

- 44：下地膜

- 42、25、87：薄膜集積回路

- 48、68、20、112：アンテナ 20

- 50、66、201：薄膜集積回路装置

- 51、81：仮接着剤

- 52、55、76：ジグ(支持基板)

- 15：IDラベル

- 49、116：保護膜

- 10：商品

- 16、136：リーダ／ライタ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

(B)

【図10】

(B)

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/302 (2006.01) G 06 K 19/00 K

G 06 K 19/077 (2006.01)

(72)発明者 萩田 香

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 萩原 周治

(56)参考文献 特開2003-203898 (JP, A)

特開2001-272923 (JP, A)

特表2003-504867 (JP, A)

特開平11-312811 (JP, A)

特開2003-077909 (JP, A)

特開2003-142666 (JP, A)

特開2000-020665 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 27/12

H 01 L 21/02

H 01 L 21/20

H 01 L 21/302

H 01 L 21/3065

H 01 L 21/336

H 01 L 29/786

G 06 K 19/00 - 19/18