(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5830023号

(P5830023)

(45) 発行日 平成27年12月9日(2015.12.9)

(24) 登録日 平成27年10月30日(2015.10.30)

|                         |                      |

|-------------------------|----------------------|

| (51) Int.Cl.            | F 1                  |

| HO 1 L 21/336 (2006.01) | HO 1 L 29/78 3 O 1 D |

| HO 1 L 29/78 (2006.01)  | HO 1 L 29/44 Y       |

| HO 1 L 29/41 (2006.01)  | HO 1 L 29/44 L       |

請求項の数 17 (全 17 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2012-537202 (P2012-537202)  |

| (86) (22) 出願日 | 平成22年11月2日 (2010.11.2)        |

| (65) 公表番号     | 特表2013-514632 (P2013-514632A) |

| (43) 公表日      | 平成25年4月25日 (2013.4.25)        |

| (86) 国際出願番号   | PCT/US2010/055181             |

| (87) 国際公開番号   | W02011/054009                 |

| (87) 国際公開日    | 平成23年5月5日 (2011.5.5)          |

| 審査請求日         | 平成25年10月24日 (2013.10.24)      |

| (31) 優先権主張番号  | 61/257,362                    |

| (32) 優先日      | 平成21年11月2日 (2009.11.2)        |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 12/917,172                    |

| (32) 優先日      | 平成22年11月1日 (2010.11.1)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                       |

|-----------|---------------------------------------------------------------------------------------|

| (73) 特許権者 | 503346049<br>ヴィシェイーシリコニックス<br>アメリカ合衆国 カリフォルニア州 95<br>054 サンタ・クララ ロウレルウッド<br>・ロード 2201 |

| (74) 代理人  | 100109634<br>弁理士 鮎谷 威志                                                                |

| (72) 発明者  | カイル テリル<br>アメリカ合衆国、カリフォルニア州 95<br>050、サンタ クララ市、ロンドンベリー<br>ドライブ 3385                   |

| 審査官       | 市川 武宜                                                                                 |

最終頁に続く

(54) 【発明の名称】半導体素子

## (57) 【特許請求の範囲】

## 【請求項 1】

高ドープ基板層上に成長されるエピタキシャル層であって、前記高ドープ基板層及び前記エピタキシャル層の双方は第1の伝導度型であるエピタキシャル層と；

前記エピタキシャル層内の第2の伝導度型のソース領域と；

前記エピタキシャル層内の前記第2の伝導度型のドレイン領域と；

前記ドレイン領域に対するドレイン接点であって、逆バイアス接合及びMOSFET(金属酸化物半導体電界効果トランジスタ)チャンネルにより前記エピタキシャル層及び高ドープ基板層が前記ドレイン接点から隔離されているドレイン接点と；

金属が充填された導電性のトレーナー状のフィードスルー要素であって、前記フィードスルーエлементは、前記エピタキシャル層を通過し、前記高ドープ基板層及び前記ソース領域と接触しているフィードスルーエлементと；

前記フィードスルーエлементに物理的に接触しており且つ前記ソース領域より上にあるゲートシールドであって、前記フィードスルーエлементの上部は前記フィードスルーエлементの下部より幅が広く、これにより前記上部と下部とが突出する突起が形成され、前記ゲートシールドは前記突起において前記フィードスルーエлементと接触しているゲートシールドと；

前記フィードスルーエLEMENT中の前記金属の表面より上にある酸化物層と；

前記酸化物層の上にあるドープガラス層と

を具備した半導体素子。

## 【請求項 2】

10

20

前記ゲートシールドは前記ソース領域にも接触している請求項 1 に記載の半導体素子。

**【請求項 3】**

前記ゲートシールドはポリシリコンを含んでいる請求項 1 に記載の半導体素子。

**【請求項 4】**

前記金属はタングステンを含んでいる請求項 1 乃至 3 の何れかに記載の半導体素子。

**【請求項 5】**

前記フィードスルーエлементはバリア層を形成するコンフォーマルコーティングを含んでいる請求項 1 乃至 4 の何れかに記載の半導体素子。

**【請求項 6】**

前記コンフォーマルコーティングは窒化チタンを含んでいる請求項 5 に記載の半導体素子。

10

**【請求項 7】**

前記半導体素子はフリップチップを含んでいる請求項 1 乃至 6 の何れか 1 項に記載の半導体素子。

**【請求項 8】**

前記半導体素子は横方向拡散金属酸化物半導体 (LDMOS) 素子を含んでいる請求項 1 乃至 7 の何れか 1 項に記載の半導体素子。

**【請求項 9】**

高ドープ基板層上に成長されるエピタキシャル層であって、前記高ドープ基板層及び前記エピタキシャル層の双方は第 1 の伝導度型であるエピタキシャル層と；

20

前記エピタキシャル層内の第 2 の伝導度型のソース領域と；

前記エピタキシャル層内の前記第 2 の伝導度型のドレイン領域と；

金属層に連結されたドレイン接点であって、逆バイアス接合及びMOSFET (金属酸化物半導体電界効果トランジスタ) チャンネルにより前記エピタキシャル層及び高ドープ基板層が前記ドレイン接点から隔離されているドレイン接点と；

金属が充填された導電性のトレンチ状のフィードスルーエлементであって、前記フィードスルーエлементは、前記エピタキシャル層を通過し、前記高ドープ基板層と接触し、少なくとも 1 つの介在層によって前記フィードスルーエлементが前記金属層から隔離され、前記ドレイン接点及び前記フィードスルーエLEMENTが前記エピタキシャル層によって分離されているフィードスルーエLEMENTと；

30

ゲート構造であって、前記高ドープ基板層、前記ドレイン接点、前記エピタキシャル層及び前記フィードスルーエLEMENTは、前記ゲート構造に電位が付加される電気的経路を含んでいるゲート構造と；

前記フィードスルーエLEMENTに物理的に接触しており且つ前記ソース領域より上にあるゲートシールドであって、前記フィードスルーエLEMENTの上部は前記フィードスルーエLEMENTの下部より幅が広く、これにより前記上部と下部とが突出する突起が形成され、前記ゲートシールドは前記突起において前記フィードスルーエLEMENTと接触しているゲートシールドと；

前記フィードスルーエLEMENT中の前記金属の表面より上にある酸化物層と；

前記酸化物層の上にあるドープガラス層と

を具備した半導体素子。

40

**【請求項 10】**

前記ゲートシールドは前記ソース領域にも接触している請求項 9 に記載の半導体素子。

**【請求項 11】**

前記ゲートシールドはポリシリコンを含み、前記金属はタングステンを含んでいる請求項 9 又は 10 に記載の半導体素子。

**【請求項 12】**

前記フィードスルーエLEMENTはバリア層を形成するコンフォーマルコーティングを含んでいる請求項 9 乃至 11 の何れか 1 項に記載の半導体素子。

**【請求項 13】**

前記半導体素子はフリップチップを含んでいる請求項 9 乃至 12 の何れか 1 項に記載の

50

半導体素子。

【請求項 1 4】

前記半導体素子は横方向拡散金属酸化物半導体（LDMOS）素子を含んでいる請求項9乃至13の何れか1項に記載の半導体素子。

【請求項 1 5】

半導体素子の作製方法であって、

高ドープ基板層上に成長されたエピタキシャル層内においてソース領域及びドレイン領域を形成することであって、前記ソース領域及びドレイン領域の双方は第2の伝導度型であり、前記高ドープ基板層及びエピタキシャル層の双方は第1の伝導度型であることと；

金属が充填された導電性のトレンチ状のフィードスルー要素を形成することであって、前記フィードスルー要素は、前記エピタキシャル層を通過し、前記高ドープ基板層及び前記ソース領域と接触していることと；

前記フィードスルー要素に物理的に接觸しており且つ前記ソース領域より上にあるゲートシールドを形成することであって、前記フィードスルー要素の上部は前記フィードスルー要素の下部より幅が広く、これにより前記上部と下部とが出会う突起が形成され、前記ゲートシールドは前記突起において前記フィードスルー要素と接觸していることと；

前記フィードスルー要素中の前記金属の表面より上に酸化物層を形成すると共に前記酸化物層の上にドープガラス層を形成することと

を含んだ方法。

【請求項 1 6】

前記フィードスルー要素を形成することは、

前記エピタキシャル層内においてトレンチを前記高ドープ基板層内に延びるように形成することと、

前記トレンチをバリア層でコーティングすることと、

前記トレンチを前記金属で充填することと、

をさらに含んでいる請求項15に記載の方法。

【請求項 1 7】

前記半導体素子は、フリップチップ及び横方向拡散金属酸化物半導体（LDMOS）素子からなる群から選択される請求項15又は16に記載の方法。

10

20

30

【発明の詳細な説明】

【技術分野】

【0001】

本出願は、米国仮特許出願（シリアル番号61/257,362号、K.Terrill 1、出願日：2009年11月2日、名称：「Transistor Structure with Feed-Through Source-to-Substrate Contact」）及び米国非仮特許出願（シリアル番号：12/917,172号、K.Terrill 1、出願日：2010年11月1日、名称：Transistor Structure with Feed-Through Source-to-Substrate Contact」）に対する優先権を主張する。同文献双方全体をここで参考のため援用する。

40

【0002】

本教示による実施形態は、一般に半導体素子に関する。

【背景技術】

【0003】

DC-DC電源において、制御MOSFET（金属酸化物半導体電界効果トランジスタ）を最適化するには、導通損失及びスイッチング損失の両方を最小化する必要がある。従来、低抵抗即ち低導通損失に起因して、平面DMOS（拡散MOS）素子又はトレンチDMOS（拡散MOS）素子がスイッチング用途に用いられている。これらのMOSFET

50

構造においては、ウエハの基板を通じてドレイン接点を利用している。これらの構造の場合、低抵抗ではあるものの、低スイッチング損失に関して不十分である。LDMOS（横方向拡散MOS）素子は、高周波数において極めて低いスイッチング損失が必要となるRF（無線周波数）用途において、従来から用いられている。LDMOS素子が平面DMOS素子又はトレンチDMOS素子に匹敵する抵抗を達成できれば、DMOS素子のスイッチング損失は低いため、変換効率が高くなる。

#### 【0004】

より低い抵抗を得るためにには、LDMOSセルピッチを低減するための技術が必要となる。制御MOSFET及び同期MOSFET双方を単一パッケージ内にパッケージングする場合、前記制御MOSFETをドレイン接点と共にダイ上部に配置し、前記ソース接点をダイの下部に配置することが望ましい。パッケージフットプリント低減のために、前記制御MOSFETを前記同期MOSFET上にスタックすることが可能である。10

#### 【0005】

従来のRF LDMOSパワートランジスタにおいては、LDMOSのドレイン接点をダイ上部に設けるために、ソース接点をダイ下部に設ける必要がある。そのため、n+表面ソース領域とp+基板との間に接点が必要となる。ここで重要なのは、この接点による占有面積を小さくすることである。なぜならば、このような占有面積の低減により、セルピッチが小さくなり、その結果前記MOSFETの所与の領域における全抵抗が低減するからである。また、前記接点を極低抵抗にすることで、前記MOSFETの抵抗に有意に貢献できるようにすることも重要である。加えて、前記ソース電極へ接続されたゲートシールドを設けることで、素子のゲート領域及びドレイン領域間の電界を低減することも重要である。良好な高周波数性能を得るためにには、ゲートシールド抵抗を低くする必要がある。これは、前記ゲートシールドを局所的にソースへと接続した場合に達成することができる。別個のパワーMOSFETにおいて、前記ゲートシールドを金属製にすることはできない。なぜならばプロセス内において得られる金属層は1層のみであり、また、この金属層は、ドレイン接続及びゲートルーティングに用いられるからである。そのため、前記ゲートシールドは、前記金属の下側に設けられた導体で構成される。このようなシールドに用いられる導体は、高ドープポリシリコンである。なぜならば、高ドープポリシリコンは形成するのが容易であり且つ安定しているからである。20

#### 【0006】

ソース - 基板接続の形成における従来の試みにおいては、n+ソースからp+シンカーへのバディング接点が用いられている。この技術の場合、必要な面積が過大である。また、この技術の場合、基板への接触のためにメタライゼーションを用いていないため、抵抗が高くなる。別の技術においては、トレンチを基板までエッチングして、シリサイド及びアルミニウム金属を用いてソースを前記基板へと接続する。この技術の場合も、必要な面積が過大である。なぜならば、アルミニウムボイディングを回避するために、トレンチを極めて急傾斜なプロファイルにする必要があるからである。接点の形成において、トレンチをエッチングし、n+ソースをp+基板へと接続する際に用いられるメタライゼーションを施すことができる。なぜならばこのようなプロセスにより抵抗が低下するからである。しかし、メタライゼーションにおいてp+基板に到達するには、狭い開口部を通過する必要がある。40

#### 【発明の概要】

#### 【0007】

本教示による実施形態は、上述した問題に対する解決法を提供する。一実施形態において、LDMOS構造は、ソースを基板及びゲートシールドに接続させ、その際、このような接点のためにより小さい面積が用いられる。一実施形態において、前記ゲートシールドは、高ドープポリシリコンを用いて構築され、ドレインメタライゼーションから隔離される。前記プロセスは、単一の金属層のみを必要とする。一実施形態において、前記ゲートシールド、n+ソース、及びp+基板を接触させるタングステンフィードスルーが用いられ50

る。前記フィードスルーは、比較的狭い幅を有する。前記比較的狭い幅は、高アスペクト比で、深いトレンチ中に化学蒸着（CVD）チタン（Ti）、窒化チタン（TiN）及びタンゲステン（W）プラグ処理を充填するための向上したプロセス能力に起因する。

#### 【0008】

実施形態は、LDMOS（横方向拡散金属酸化物半導体）構造を含む。この構造では、前記ソースを基板及び前記ゲートシールドへと接続させ、その際、このような接点のためにより小さい面積が用いられる。前記構造は、導電性基板層と、ソースと、ドレイン接点とを含む。前記ドレイン接点は、少なくとも1つの介在層により、前記基板層から分離される。導電性のトレンチ状のフィードスルー要素が前記介在層を通過し、前記基板及び前記ソースと接触して、前記ドレイン接点及び前記基板層を電気的に接続させる。

10

#### 【0009】

本文書は、一般に、フィードスルー型ソース・基板接点を用いたトランジスタ構造についての教示を主に含んでいる。当業者であれば、多様な図面中に例示される以下の詳細な説明を読了すれば、上記及び他の目的及び利点を認識することができるであろう。

#### 【図面の簡単な説明】

#### 【0010】

添付の図面は、本明細書において採用され且つ本明細書の一部をなす。添付の図面は、実施形態を示す。添付の図面を本記載と共に参照すれば、本教示の原理の理解の一助となる。図面及び本明細書中、類似の参照符号は類似の要素を指す。

20

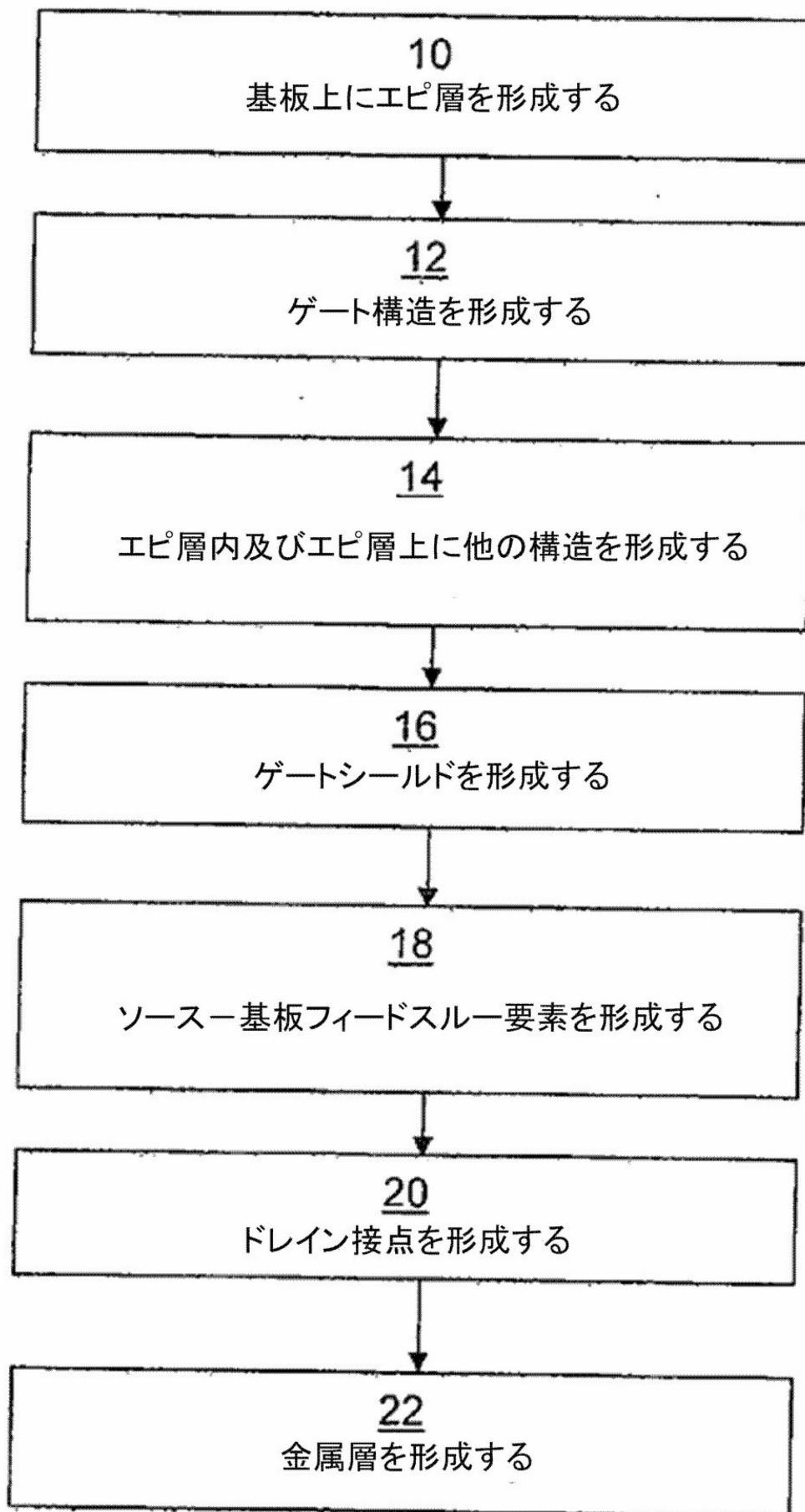

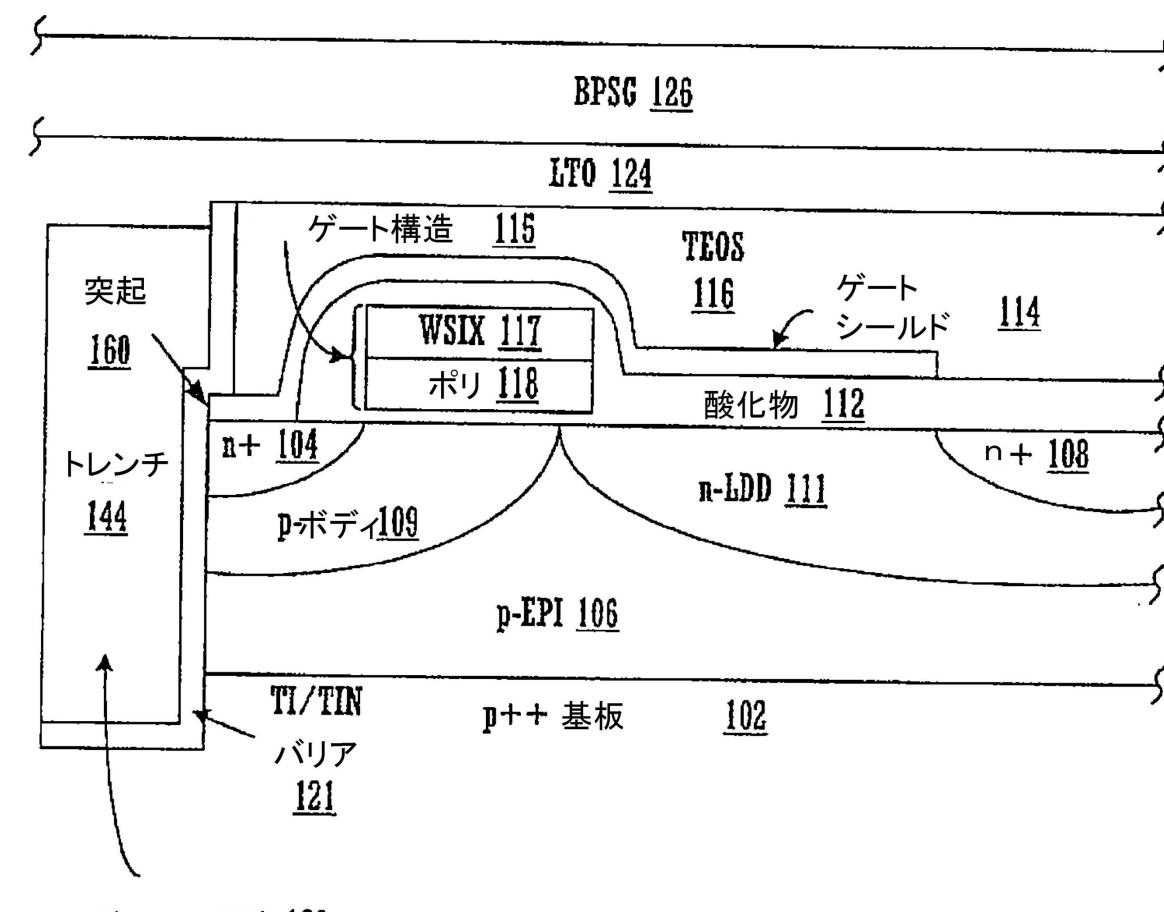

【図1】図1は、実施形態に係る半導体素子を作製する方法の一例のフローチャートである。

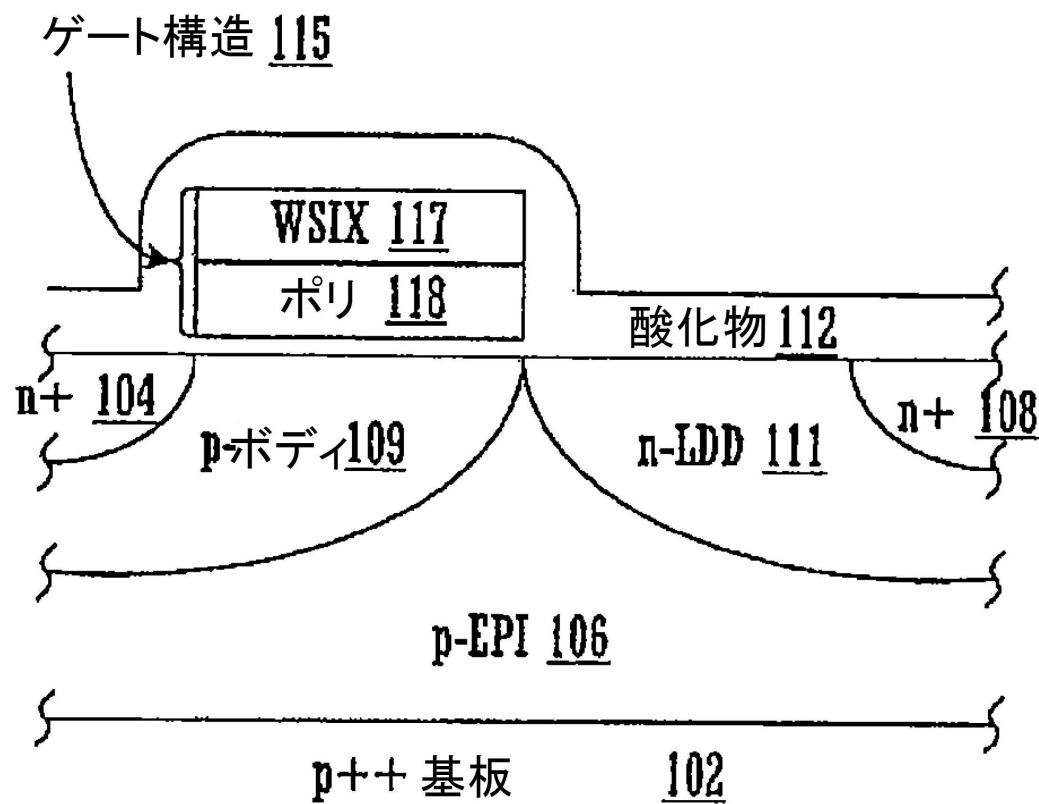

【図2】図2は、実施形態に係る種々の作製段階における半導体素子の要素の断面図である。

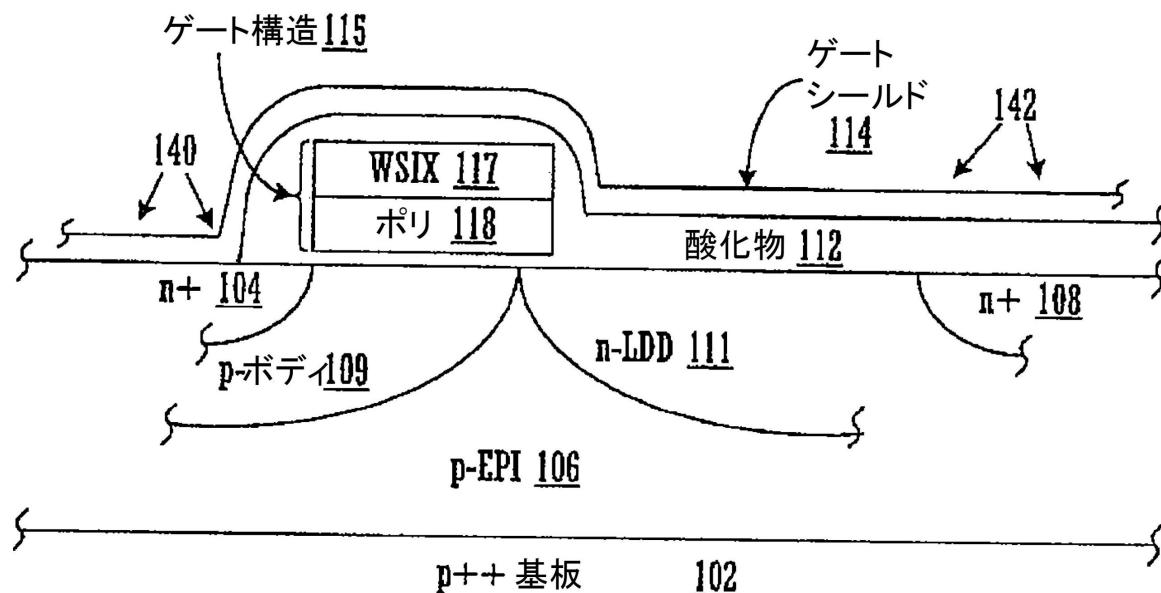

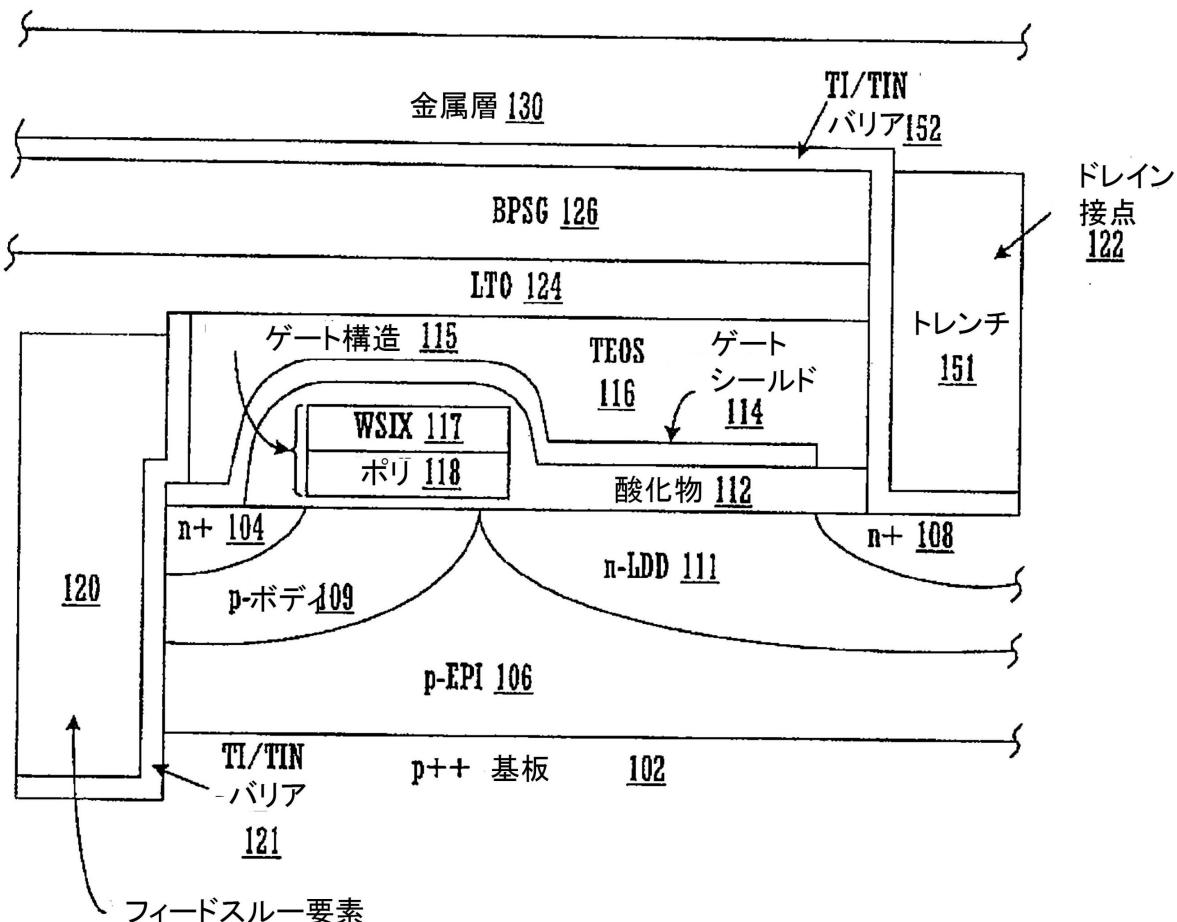

【図3】図3は、実施形態に係る種々の作製段階における半導体素子の要素の断面図である。

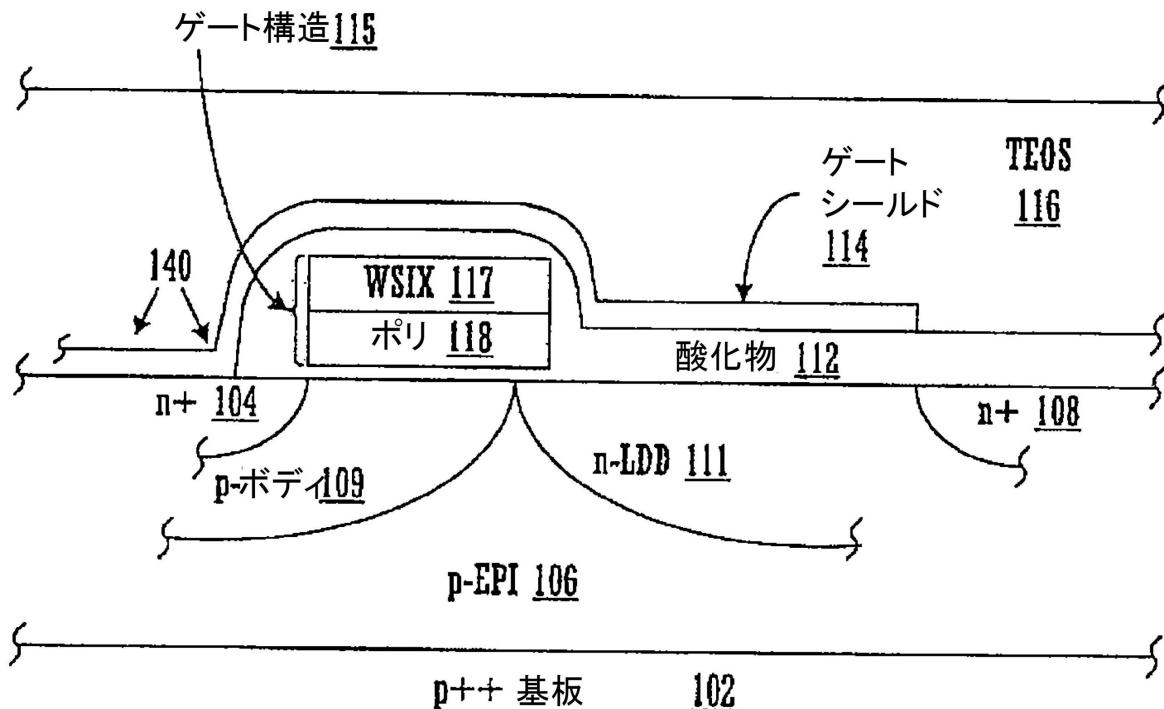

【図4】図4は、実施形態に係る種々の作製段階における半導体素子の要素の断面図である。

【図5】図5は、実施形態に係る種々の作製段階における半導体素子の要素の断面図である。

30

【図6】図6は、実施形態に係る種々の作製段階における半導体素子の要素の断面図である。

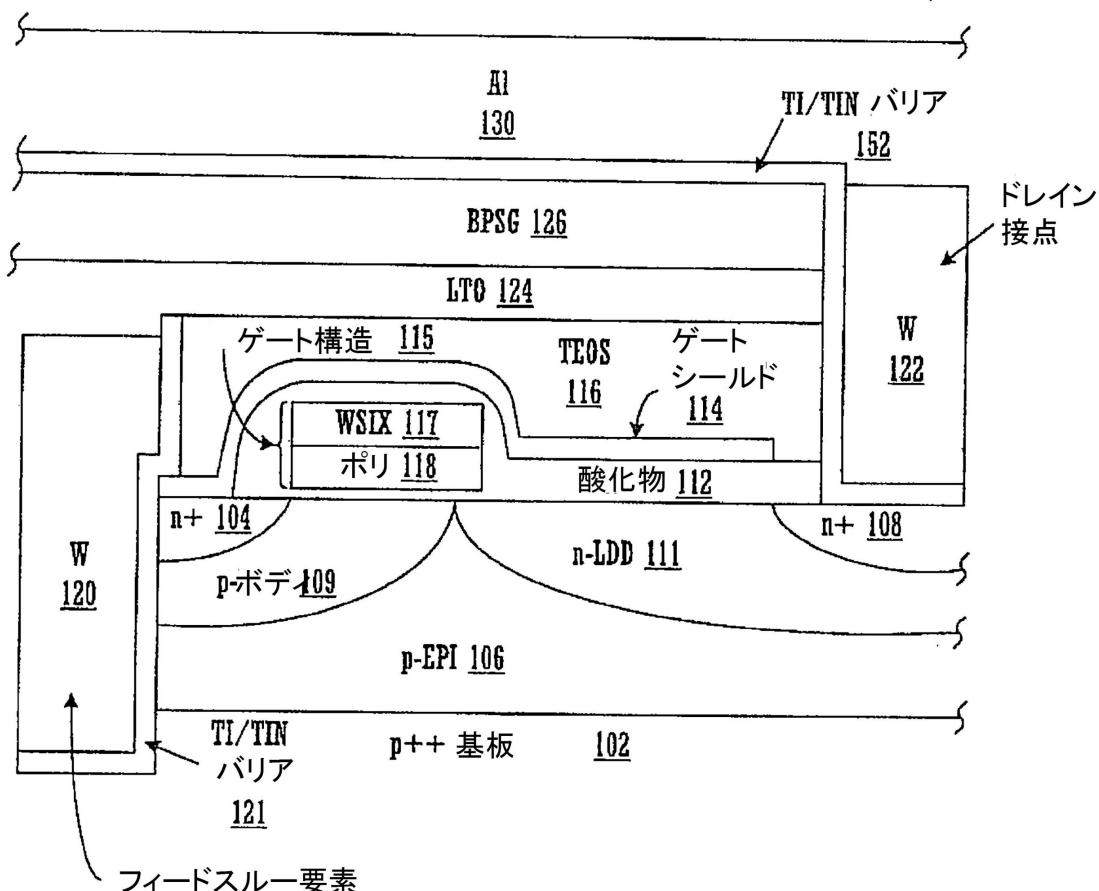

【図7】図7は、実施形態に係る半導体素子の要素を示す断面図である。

#### 【発明を実施するための形態】

#### 【0011】

以下、実施形態について詳述する。本教示について実施形態と共に説明していくが、本教示はこれらの実施形態に限定されないことが理解されるべきである。即ち、本発明は、代替物、改变物及び均等物を網羅することを意図する。このような代替物、改变物及び均等物は、添付の特許請求の範囲に従って解釈されるような本発明の範囲内に含まれ得る。

#### 【0012】

以下の詳細な説明において、深い理解のために、多数の特定の詳細について説明する。しかし、当業者にとって、これらの特定の詳細又はその均等物無しで本教示を実行することが可能である。他の場合において、本発明の側面を不要に曖昧にしないようにするために、周知の方法、手順、要素及び回路についての詳述を控える。

40

#### 【0013】

以下の詳細な説明のうち一部についての説明において、半導体素子の作製のための動作工程について、手順、論理ブロック、処理、及び他の記号表示を用いる。これらの記載及び表示は、半導体素子作製分野の当業者が動作の実質的内容を他の当業者に最も効果的に伝達するために用いられる手段である。本出願において、手順、論理ブロック、プロセッサなどは、工程又は命令の首尾一貫したシーケンスとして考えられる。これらの工程は、

50

物理的量の物理的操作を必要とするものである。しかし、上記及び類似の用語は、適切な物理的量と関連付けられるべきものであり、ひとえに便宜上の理由でこれらの量に付与されたものであることが念頭におかれるべきである。詳細に明記無き限りまた以下の議論から明らかでない限り、本出願全体において、「形成する」、「実行する」、「生成する」、「堆積する」、「エッティングする」などの用語を用いた記載は、半導体素子作製の動作及びプロセスを指すことが理解される。

#### 【0014】

本明細書中用いられる「n」という文字はn型ドーパントを指し、「p」という文字はp型ドーパントを指す。正符号「+」又は負符号「-」は、相対的に高いドーパント濃度又は相対的に低いドーパント濃度を指す。10

#### 【0015】

本明細書中で用いられる「チャンネル」という用語は、受容されている意味合いで用いられる。即ち、電界効果トランジスタ(FET)内のチャンネルにおいて、電流はソース接続からドレイン接続へと移動する。チャンネルは、n型半導体材料又はp型半導体材料のいずれかによって構成され得る。そのため、FETは、nチャンネル素子又はpチャンネル素子として指定される。

#### 【0016】

nチャンネル素子の文脈において説明するが、実施形態はこれに限定されない。即ち、本明細書中に記載される機能を、pチャンネル素子において用いることが可能である。即ち、n型ドーパント及び材料をp型ドーパント及び材料と置換することにより、当該記載をそのままpチャンネル素子に当てはめることが可能であり、またその逆も成立する。20

#### 【0017】

まず、実施形態に従って素子を作製するプロセスについて説明する。特定の工程を開示するが、このような工程はあくまで一例である。即ち、実施形態は、記載の工程以外の種々の工程又は変更例の実行にも良好に適合する。図面は縮尺通りに記載されておらず、構造及びこれらの構造を形成する多様な層の一部のみを図示している場合もある。さらに、本明細書中に記載のプロセス及び工程と共に、作製プロセス及び工程が行われる場合がある。即ち、本明細書中に図示及び記載される工程の前、最中及び/又は後において、複数のプロセス工程が存在し得る。重要なことは、実施形態が、これらの他の(恐らくは従来の)プロセス及び工程と共に(当該プロセス及び工程を大きく混乱させることなく)実行することが可能であることである。一般的に、実施形態を従来の素子又はプロセスの一部の代替として(周辺構造、プロセス及び工程に有意な影響を与えることなく)用いることが可能である。30

#### 【0018】

図1のブロック10及び図2を参照して、p型エピタキシャル(エピ)層106を高ドープ(例えばp++)基板102上に成長させる。その後、さらなるp型注入(図示せず)を実行することで、エピ濃度を選択的に向上させることができる。犠牲酸化物層(図示せず)を成長させて剥離することができ、その後、(層112の一部を形成する)ゲート酸化物層を成長させることができる。その後、ゲート構造115の形成の準備段階として、ドープポリシリコン及びWSi<sub>x</sub>(タンゲステンシリサイド)を前記ゲート酸化物上に堆積させることができる。40

#### 【0019】

図1のブロック12において、再度図2を参照して、ゲート構造115を形成する。より詳細には、一実施形態において、フォトリソグラフィックプロセスを用いて、ゲート構造115を形成させる予定の領域上にフォトレジスト(図示せず)を選択的に堆積させることができる。プラズマエッチ工程を用いて、前記領域から前記WSi<sub>x</sub>及びドープポリシリコンを除去することができ、これにより、ゲート構造115が形成される。ゲート構造115は、WSi<sub>x</sub>層117及びポリシリコン層118双方を含む。

#### 【0020】

図1のブロック14において、再度図2を参照して、エピ層106上且つエピ層10650

内に他の構造を形成する。より詳細には、一実施形態において、別のフォトリソグラフィックプロセスを用いて、p型ボディ領域109を形成する予定の領域の外部の全領域内にフォトレジスト(図示せず)を選択的に堆積させることができる。その後、垂直注入及び角度付き注入の組み合わせを用いて、ボディ領域109を形成することができる。

#### 【0021】

ウエハ洗浄後、注入アニール又はボディドライブを行うことができる。熱酸化技術又は酸化物スペーサ形成技術のいずれかを用いて、酸化物層(層112の一部)をゲート構造115の側部上に形成する。フォトリソグラフィックプロセスを用いて、n-LDD(低ドープドレイン)領域111を形成する予定の領域の外部の領域内にフォトレジスト(図示せず)を選択的に堆積させることができる。その後、注入を用いて、拡張ドレインLD領域111を形成することができる。

10

#### 【0022】

フォトリソグラフィックプロセスを用いて、n+ソース領域104及びn+ドレイン領域108を形成する予定である領域の外部の全領域内にフォトレジスト(図示せず)を選択的に堆積することができる。その後、ヒ素注入を用いて、ソース領域104及びドレイン領域108を形成することができる。前記ウエハを洗浄後、ソース注入アニールを行うことができる。

#### 【0023】

その後、プラズマ又はTEOS(オルトケイ酸テトラエチル)酸化物を堆積及びアニールすることで、ゲートシールド酸化物層112を完成させることができる。

20

#### 【0024】

図1のブロック16において、再度図3を参照して、ゲートシールド114を形成する。より詳細には、一実施形態において、フォトリソグラフィックプロセスを用いて、n+ソース接点領域140に対するゲートシールドを除く領域内にフォトレジスト(図示せず)を選択的に堆積することができる。その後、ゲートシールド酸化物層112を領域140内においてエッティング除去することで、下側のソース領域104を露出させる。希釈HF(フッ化水素酸)最終前処理を用いて前記ウエハを洗浄した後、ゲートシールド114を酸化物層112の残り部分上及びソース領域104上に堆積させることができる。意義深いことに、ゲートシールド114は、下側のソース領域104と接触する。一実施形態において、ゲートシールド114は、ドープポリシリコンを用いて形成される。

30

#### 【0025】

図3を参照して、フォトリソグラフィックプロセスを用いて、領域142を除くゲートシールド114上にフォトレジスト(図示せず)を選択的に堆積することができる。その後、プラズマエッチ工程を用いて、図4に示すようにフォトレジストによって被覆されている領域の外側の領域142中のゲートシールド材料を除去することができる。ウエハ洗浄後、比較的肉厚のTEOS層116を堆積させた後にエッチバックすることで、図4に示すようにゲートシールド114を露出させることなく平面を形成することができる。

#### 【0026】

図1のブロック18において、図5を参照して、ソース-基板フィードスルー要素120を形成する。より詳細には、一実施形態において、フォトリソグラフィックプロセスを用いて、前記ソース-基板フィードスルー接点を形成する予定の領域の外側の領域内にフォトレジスト(図示せず)を選択的に堆積させることができる。2工程プラズマエッチを用いることができ、前記フィードスルー接点のためのトレンチ144をエッティングすることができる。まず、プラズマ酸化物エッチを用いて、エピ層106上のTEOS層116をエッティングすることができる。その後、プラズマシリコンエッチを用いて、エピ層106を通じてトレンチ144をp+基板102内へと延びるように形成することができる。ウエハ洗浄後、希釈HF最終前処理を用いて、トレンチ144の上部を下部よりも幅広にし、これによりゲートシールド114がフィードスルー要素120と出合う点160において突起(ledge)が形成される。チタン(Ti)層及び窒化チタン(TiN)層のコンフォーマルコーティングをトレンチ144の側部及び下部に堆積させることができ、その

40

後高速熱アニールを行ってチタンシリサイド接点を形成することができる。

#### 【0027】

その後、CVDタングステン(W)層をトレンチ144内に堆積させることで、フィードスルーポリマー要素120を形成することができる。タングステン層は、前記トレンチを完全に充填できるような十分な厚さを有する。その後、前記タングステンに対してエッチングを行って、露出したTi層及びTiN層を(前記タングステンのエッティング無しに)除去することができる。突起160により、金属と隣接シリコンとの間の接触が向上し、接点抵抗が低下する。

#### 【0028】

低温酸化物(LTO)層124及びホウ素-リン-ケイ酸ガラス(BPSG)層126をフィードスルーポリマー要素120及びTEOS層116の上面上に堆積させ、その後アニーリングすることで、これらの材料を安定化させることができる。

10

#### 【0029】

図1のブロック20において、さらに図6を参照して、ドレイン接点122を形成する。より詳細には、一実施形態において、フォトリソグラフィックプロセスを用いて、前記ドレイン接点領域の外側の領域内にフォトレジスト(図示せず)を選択的に堆積させることができる。プラズマ酸化物エッチを用いて、酸化物(TEOS層116)をエッティング除去し、トレンチ151を形成することができる。ウエハ洗浄後、希釈HF最終前処理を用いて、Ti層及びTiN層の堆積によりバリア層152を形成する。バリア層152は、トレンチ151の内側を覆っており、BPSG126の表面上方に延びている。高速熱アニールを用いて、チタンシリサイド接点を形成することができる。CVDタングステン層の堆積は、トレンチ151の完全充填及びドレイン接点122の形成を得る位の十分な厚さになるまで行うことができる。その後、前記タングステンをエッチバックすることで前記タングステンを平坦化することができ、これにより、前記タングステンはドレイン接点122の内側のみにおいて残留する。ゲート接点(図示せず)も、類似の方法で形成することができる。

20

#### 【0030】

図1のブロック22において、金属層130を形成する。より詳細には、一実施形態において、チタン層(図示せず)及び肉厚のアルミニウム層を堆積することができる。フォトリソグラフィックプロセスを用いて、フォトレジスト(図示せず)を前記メタライゼーション領域上に選択的に堆積させることができ、プラズマエッチを用いて、前記領域の外側のアルミニウム層及びチタン層を除去することができる。

30

#### 【0031】

上記したプロセスの結果、例えば図7に示すようなLDMOS構造が形成される。図7は、本発明の実施形態による半導体素子100の一部を示す断面図である。素子100は、フリップチップとして構成することができる。

#### 【0032】

素子100は、導電性(例えばp++)基板層102を含む。フリップチップ実施形態において、基板層102に隣接するバックメタル層(図示せず)が設けられ得る。図7の配向を考慮すると、前記バックメタル層は、基板層102の下側に来る。前記素子は、エピ層106も含む。このエピ層は、n+ソース領域104、n+ドレイン領域108、p+ボディ領域109及びn-LDD領域111を含む。エピ層106は、さらなる構造、層又は領域(図7中図示せず)を含み得る。逆バイアス型接合及びMOSFETチャンネルにより、基板層102及びエピ層106がドレイン接点122から隔離される。

40

#### 【0033】

酸化物層112は、ゲート115を含む下側領域からゲートシールド114を隔離する。この下側領域は、第1の(例えばWSix)層117及び第2の(例えばポリシリコン)層118を含む。ゲートシールド114も、ドレイン接点122から隔離される。しかし、前記ゲートシールドは、ソース領域104と接触する。ゲートシールド114も、フィードスルーポリマー要素120と接触する。フィードスルーポリマー要素120も、ソース領域104及

50

び基板 102 と接触する。

**【0034】**

バリア層 121（例えば Ti / TiN）は、フィードスルーエлемент 120 の内部を覆っている。第 1 の（例えば LTO）層 124 及び第 2 の（例えば BPSG）層 126 により、フィードスルーエлемент 120 がアルミニウム層 130 から隔離される。

**【0035】**

従来の素子と比較して、フィードスルーエлемент 120 が消費する領域及び堆積が実質的に低下する。よって、各セルのサイズ低減が可能となり、これにより、素子 100 をモバイル／ハンドヘルドデバイス（例えば携帯電話及びスマートフォン）において用いる場合の重要な考慮事項であるセル密度の増加及び／又は素子サイズの低下が可能となる。さらに、フィードスルーエLEMENT 120 の作製を従来のシンカーよりも迅速に行うことが可能であるため、製造時間の短縮及びスループット増加が可能となり、これによりコスト低減が可能となる。

**【0036】**

一実施形態において、フィードスルーエLEMENT 120 は、タンゲステン製である。なぜならばタンゲステンの熱係数はドープシリコンの熱係数よりもシリコンの熱係数により適合しており、また、タンゲステンはドープシリコンよりも本来的に低抵抗であるからである。

**【0037】**

素子 100 は、電位をゲート構造 115 へと付加して回路を完成させることにより、作動させることができる。この回路は、ソース接点（図示せず）、ソース金属及びドレイン金属、エピ層 106、基板層 102、ドレイン接点 122 及びフィードスルーエLEMENT 120 中の構造を含む。

**【0038】**

要約すると、実施形態により得られる LD MOS 構造により、前記ソースが基板及びゲートシールドへと接続され、この際、このような接点のためにより小さな面積が用いられる。前記ゲートシールドは、高ドープポリシリコンを用いて構築可能であり、ドレインメタライゼーションから隔離することが可能となる。フィードスルーエLEMENT（例えばタンゲステンフィードスルーエLEMENT）が、前記ゲートシールド、n+ ソース、及び p++ 基板と接触する。これらのフィードスルーエLEMENT は、比較的狭い幅を有する。その結果、セルのサイズ即ち素子のサイズを低減することが可能となり、セル密度の増加が可能となる。

**【0039】**

特定の本発明の実施形態についての上記記載は、例示及び説明の目的のためのものであり、網羅的なものを意図しておらず、本発明を開示の形態そのものに限定することも意図していない。よって、上記教示内容に鑑みれば、多くの改変例及び変更例が可能である。実施形態は、本発明の原理及びその実際的用途を説明するために選択及び記載されたものであり、これにより、当業者が本発明及び多様な実施形態を最良に利用することが可能となり、特定の用途に適した多様な改変例が企図される。本発明の範囲は、本明細書に添付される特許請求の範囲及びその均等物によって規定されることが意図される。本明細書中記載される全ての要素、部品及び工程が、好適に含まれる。当業者であれば理解するようになら、これらの要素、部品及び工程のうち任意のものを他の要素、部品及び工程と置換することも可能であるし、あるいは、これらの要素、部品及び工程を省略することも可能であることが理解される。

**【0040】**

**コンセプト**

本文書は、少なくとも以下のコンセプトを開示する。

**【0041】**

**コンセプト 1.**

高ドープ基板層上に成長されるエピタキシャル層であって、前記高ドープ基板層及び前記エピタキシャル層の双方は第 1 の伝導度型であるエピタキシャル層と；

前記エピタキシャル層内の第 2 の伝導度型のソース領域と；

10

20

30

40

50

前記エピタキシャル層内の前記第2の伝導度型のドレイン領域と；

前記ドレイン領域に対するドレイン接点であって、逆バイアス接合及びMOSFET(金属酸化物半導体電界効果トランジスタ)チャンネルにより前記エピタキシャル及び基板層が前記ドレイン接点から隔離されているドレイン接点と；

導電性のトレンチ状のフィードスルー要素であって、前記フィードスルー要素は、前記エピタキシャル層を通過し、前記基板層及び前記ソース領域と接触し、前記フィードスルーエлементは、前記ドレイン接点と前記基板層とを電気的に接続するように動作可能であるフィードスルーエlementと

を具備した半導体素子。

コンセプト2.

10

前記フィードスルーエlementと接続するゲートシールドを更に具備したコンセプト1の半導体素子。

コンセプト3.

前記ゲートシールドも前記ソース領域に接触しているコンセプト2の半導体素子。

コンセプト4.

前記ゲートシールドはポリシリコンを含んでいるコンセプト2の半導体素子。

コンセプト5.

前記フィードスルーエlementはタンゲステンを含んでいるコンセプト1の半導体素子。

コンセプト6.

前記フィードスルーエlementはバリア層を形成するコンフォーマルコーティングを含んでいるコンセプト1の半導体素子。

20

コンセプト7.

前記コンフォーマルコーティングは窒化チタンを含んでいるコンセプト6の半導体素子。

コンセプト8.

前記素子はフリップチップを含んでいるコンセプト1の半導体素子。

コンセプト9.

前記素子は横方向拡散金属酸化物半導体(LDMOS)素子を含んでいるコンセプト1の半導体素子。

コンセプト10.

30

高ドープ基板層上に成長されるエピタキシャル層であって、前記高ドープ基板層及び前記エピタキシャル層の双方は第1の伝導度型であるエピタキシャル層と；

前記エピタキシャル層内の第2の伝導度型のソース領域と；

前記エピタキシャル層内の前記第2の伝導度型のドレイン領域と；

金属層に連結されたドレイン接点であって、逆バイアス接合及びMOSFET(金属酸化物半導体電界効果トランジスタ)チャンネルにより前記エピタキシャル及び基板層が前記ドレイン接点から隔離されているドレイン接点と；

導電性のトレンチ状のフィードスルーエlementであって、前記フィードスルーエlementは、前記エピタキシャル層を通過し、前記基板層と接触し、少なくとも1つの介在層によって前記フィードスルーエlementが前記金属層から隔離され、前記ドレイン接点及び前記フィードスルーエlementが前記エピタキシャル層によって分離されているフィードスルーエlementと；

40

ゲート構造であって、前記ゲート構造に電位が付加されると電気的経路が形成され、前記電気経路は、前記基板層、前記ドレイン接点、前記エピタキシャル層及び前記フィードスルーエlementを含んでいるゲート構造と

を具備した半導体素子。

コンセプト11.

前記フィードスルーエlementと接続するゲートシールドを更に具備したコンセプト10の半導体素子。

コンセプト12.

前記ゲートシールドも前記ソース領域に接続しているコンセプト11の半導体素子。

コンセプト13.

50

前記ゲートシールドはポリシリコンを含み、前記フィードスルー要素はタングステンを含んでいるコンセプト11の半導体素子。

コンセプト14.

前記フィードスルー要素はバリア層を形成するコンフォーマルコーティングを含んでいるコンセプト10の半導体素子。

コンセプト15.

前記素子はフリップチップを含んでいるコンセプト10の半導体素子。

コンセプト16.

前記素子は横方向拡散金属酸化物半導体(LDMOS)素子を含んでいるコンセプト10の半導体素子。

10

コンセプト17.

半導体素子の作製方法であって、

高ドープ基板層上に成長されたピタキシャル層内においてソース領域及びドレイン領域を形成することであって、前記ソース領域及びドレイン領域の双方は第2の伝導度型であり、前記高ドープ基板層及びピタキシャル層の双方は第1の伝導度型であること；

ドレイン接点を形成することであって、逆バイアス接合及びMOSFET(金属酸化物半導体電界効果トランジスタ)チャンネルにより前記エピタキシャル及び基板層が前記ドレイン接点から隔離されること；

導電性のトレンチ状のフィードスルー要素を形成することであって、前記フィードスルーエピタキシャル層を通過し、前記基板層及び前記ソース領域と接触し、前記ドレイン接点と前記基板層とを電気的に接続するように動作可能であることとを含んだ方法。

20

コンセプト18.

ゲートシールドを形成することをさらに含み、前記ゲートシールドは前記フィードスルーエピタキシャル層を通過し、前記基板層及び前記ソース領域と接続するコンセプト17の方法。

コンセプト19.

前記フィードスルーエピタキシャル層を形成することは、

前記介在層内においてトレンチを前記基板層内に延びるように形成することと、

前記トレンチをバリア層でコーティングすることと、

前記トレンチを導電性材料で充填することと、

30

をさらに含んでいるコンセプト17の方法。

コンセプト20.

前記素子は、フリップチップ及び横方向拡散金属酸化物半導体(LDMOS)素子からなる群から選択されるコンセプト17の方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

100

---

フロントページの続き

(56)参考文献 米国特許出願公開第2007/0034942(US,A1)

特開2001-244476(JP,A)

特開2002-368121(JP,A)

米国特許出願公開第2003/0218209(US,A1)

米国特許出願公開第2005/0280085(US,A1)

米国特許出願公開第2007/0020863(US,A1)

特開2006-278832(JP,A)

米国特許第07576388(US,B1)

特開2006-286953(JP,A)

特開2007-287813(JP,A)

特開2006-086398(JP,A)

特開2009-124002(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/41

H01L 29/78