(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6267207号

(P6267207)

(45) 発行日 平成30年1月24日(2018.1.24)

(24) 登録日 平成30年1月5日(2018.1.5)

(51) Int.Cl.

H04L 9/10 (2006.01)

F 1

H04L 9/00 621 A

請求項の数 16 (全 24 頁)

(21) 出願番号 特願2015-534947 (P2015-534947)

(86) (22) 出願日 平成25年9月10日 (2013.9.10)

(65) 公表番号 特表2015-532549 (P2015-532549A)

(43) 公表日 平成27年11月9日 (2015.11.9)

(86) 國際出願番号 PCT/EP2013/068746

(87) 國際公開番号 WO2014/053286

(87) 國際公開日 平成26年4月10日 (2014.4.10)

審査請求日 平成28年8月29日 (2016.8.29)

(31) 優先権主張番号 12187213.9

(32) 優先日 平成24年10月4日 (2012.10.4)

(33) 優先権主張国 歐州特許庁 (EP)

(31) 優先権主張番号 12194713.9

(32) 優先日 平成24年11月29日 (2012.11.29)

(33) 優先権主張国 歐州特許庁 (EP)

(73) 特許権者 510273499

イントリンシック・イー・ティー・ペー・ペー

オランダ国、エン・エルー 5656・アー

・エー・アントホーフエン、ハイ・テツ

ク・キヤンパス・9

(74) 代理人 110001173

特許業務法人川口國際特許事務所

(72) 発明者 フアン・デル・スライス、エリック

オランダ国、3582・フェー・イクス・

ユトレヒト、イナ・ブーディエルーバッケ

ルホフ・88

(72) 発明者 フアン・フルスト、マールテン

オランダ国、5061・アー・ペー・オーリ

ステルウェイク、ベルケンラーン・9

最終頁に続く

(54) 【発明の名称】物理的クローン不能関数として使用されるメモリから暗号化キーを生成するためのシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

暗号化キーを生成するための電子システム(100、200)であって、電子システムが、

物理的クローン不能関数として使用されるメモリ(110)であって、メモリは書き込み可能で、揮発性であり、メモリに電源投入したたびに、メモリはメモリの少なくとも部分的にランダムな物理的特性に応じたメモリコンテンツに確定するように構成されており、メモリはメモリインターフェース(120)を通してアクセス可能であるメモリと、

メモリが確定したメモリコンテンツから暗号化キーを導出するように構成されたキー導出ユニット(150、230)とを備え、

暗号化キーを生成するための電子システムがさらに、

メモリインターフェースを通してメモリ、およびキー導出ユニットに接続されたメモリ読み出しユニット(220)を備え、メモリ読み出しユニットが

スクランブルされた順序でメモリインターフェースを介してメモリコンテンツを取り出すためのアドレススクランブラー(140)と、

メモリを暗号化するための暗号化ユニット(240)であって、メモリインターフェースからスクランブルされた順序でメモリコンテンツを受信し、受信したメモリコンテンツを暗号化し、暗号化されたメモリコンテンツをメモリに書き戻すように構成されている暗号化ユニット(240)と、

メモリを復号するための復号ユニット(250)であって、メモリインターフェースか

ら事前に定義されたさらなる順序で暗号化されたメモリコンテンツを受信し、受信した暗号化されたメモリコンテンツを復号して事前に定義されたさらなる順序でメモリコンテンツを取得するように構成されている復号ユニット(250)と

を備える、電子システム。

**【請求項2】**

不揮発性のヘルパーデータメモリ(285)を備え、ヘルパーデータメモリ(285)が、物理的クローン不能関数として使用されるメモリのために構築されたヘルパーデータを記憶し、さらに、

訂正可能なビットストリングを確立するためのコンバイナ(280)を備え、訂正可能なビットストリングはエラー訂正コードの訂正可能な近傍にあり、コンバイナ(280)が、ヘルパーデータメモリからヘルパーデータを取り出して、取り出したヘルパーデータと、メモリ読み出しユニットからされた事前に定義されたさらなる順序でメモリが確定したメモリコンテンツとを組み合わせるように構成され、さらに、

エラー訂正アルゴリズムを使用して訂正可能なビットストリングからエラー訂正コードのコードワードを確立するように構成されたエラーコレクタ(290)を備える、請求項1に記載の電子システム。

**【請求項3】**

暗号化ユニットが暗号化されたメモリコンテンツをスクランブルされた順序でメモリに書き戻すように構成され、それによって、メモリコンテンツを暗号化されたメモリコンテンツで上書きする、請求項1または2に記載の電子システム。

**【請求項4】**

スクランブルされた順序が、読み出しユニットの各電源投入後に少なくとも部分的にランダムに生成されるシードから導出される、請求項1から3のいずれか一項に記載の電子システム。

**【請求項5】**

読み出しユニットが新しいシードを取得するためにシードに適用されるように構成された暗号化一方向性関数を備え、アドレススクランブラーが新しくスクランブルされた順序でメモリインタフェースを介してメモリコンテンツの再フェッチのための新しいシードから新しくスクランブルされた順序を導出するように構成された、請求項4に記載の電子システム。

**【請求項6】**

読み出しユニットが、さらなるメモリに電源投入したたびに、第2のメモリがノイズのあるメモリコンテンツに確定するように構成されたさらなる揮発性メモリを備え、シードが、第2のメモリが確定したメモリコンテンツから導出される、請求項4および5のいずれか一項に記載の電子システム。

**【請求項7】**

難読化ユニットを備え、難読化ユニットがメモリへいくつか追加で難読化アクセスするように構成され、難読化アクセスがメモリからの光子放出とメモリが電源投入時に確定したメモリコンテンツ間の相関を低減化するように構成された、請求項1から6のいずれか一項に記載の電子システム。

**【請求項8】**

難読化ユニットがメモリのメモリ位置への難読化アクセスを行うように構成され、難読化アクセスが、暗号化ユニットが暗号化されたメモリコンテンツをメモリ位置に書き戻した後に行われる、請求項7に記載の電子システム。

**【請求項9】**

物理的クローン不能関数として使用されるメモリがS R A Mメモリである、請求項1から8のいずれか一項に記載の電子システム。

**【請求項10】**

物理的クローン不能関数として使用されるメモリが揮発性F P G Aメモリである、請求項1から9のいずれか一項に記載の電子システム。

10

20

30

40

50

## 【請求項 1 1】

請求項 1 から 1 0 のいずれか一項に記載の暗号化キーを生成するための電子システムを含む集積回路。

## 【請求項 1 2】

集積回路がスマートカード、A S S P、D S P、アプリケーションプロセッサ、S I M、およびN F Cチップのいずれか一つである、請求項 1 から 1 1 のいずれか一項に記載の暗号化キーを生成するための電子システムを含む集積回路。

## 【請求項 1 3】

暗号化キーを生成するための電子システム ( 1 0 0 、 2 0 0 )において、事前に定義されたさらなる順序でメモリを安全に読み出すための電子メモリ読み出しユニットであって、システムが、

物理的クローン不能関数として使用されるメモリ ( 1 1 0 )であって、メモリは書き込み可能で、揮発性であり、メモリに電源投入したたびに、メモリはメモリの少なくとも部分的にランダムな物理的特性に応じたメモリコンテンツに確定するように構成されており、メモリはメモリインタフェース ( 1 2 0 ) を通してアクセス可能であるメモリと、

メモリが確定したメモリコンテンツから暗号化キーを導出するように構成されたキー導出ユニット ( 1 5 0 、 2 3 0 )とを備え、電子メモリ読み出しユニットはメモリインタフェースを通してメモリ、およびキー導出ユニットに接続可能であり、電子メモリ読み出しユニットが、

スクランブルされた順序でメモリインタフェースを介してメモリコンテンツを取り出すように構成されたアドレススクランブラーと、

メモリを暗号化するための暗号化ユニットとを備え、暗号化ユニットが、メモリインタフェースからスクランブルされた順序でメモリコンテンツを受信し、受信したメモリコンテンツを暗号化し、暗号化されたメモリコンテンツをメモリに書き戻すように構成され、電子メモリ読み出しユニットがさらに、

メモリを復号するための復号ユニットを備え、復号ユニットが、メモリインタフェースから事前に定義されたさらなる順序で暗号化されたメモリコンテンツを受信し、受信した暗号化されたメモリコンテンツを復号して事前に定義されたさらなる順序でメモリコンテンツを取得するように構成された、電子メモリ読み出しユニット。

## 【請求項 1 4】

暗号化キーを生成するための方法 ( 4 0 0 )であって、方法が、

物理的クローン不能関数として使用されるメモリの電源投入するステップ ( 4 1 0 ) を含み、メモリが書き込み可能で揮発性であり、方法がさらに、

メモリが、メモリの少なくとも部分的にランダムな物理的特性に応じたメモリコンテンツに確定できるようにするステップ ( 4 2 0 )、

スクランブルされた順序でメモリインタフェースを介してメモリコンテンツを取り出すステップ ( 4 3 0 )、および

メモリが確定したメモリコンテンツから暗号化キーを導出するステップ ( 4 8 0 ) を含み、

メモリの暗号化が、

メモリインタフェースからスクランブルされた順序でメモリコンテンツを受信するステップ ( 4 3 0 )、

受信したメモリコンテンツを暗号化するステップ ( 4 4 0 )、および

暗号化されたメモリコンテンツをメモリに書き戻すステップ ( 4 5 0 )によって行われること、

メモリの復号が、

メモリインタフェースから事前に定義されたさらなる順序で暗号化されたメモリコンテンツを受信するステップ ( 4 6 0 )、および

事前に定義されたさらなる順序でメモリコンテンツを取得するために受信した暗号化されたメモリコンテンツを復号するステップ ( 4 7 0 )によって行われることを含む方法。

10

20

30

40

50

**【請求項 15】**

コンピュータプログラムがコンピュータで実行される時に、請求項14に記載のすべてのステップを行うように適合されたコンピュータプログラムコード手段を含む、コンピュータプログラム。

**【請求項 16】**

コンピュータ読み取り可能媒体上で具現化される、請求項15に記載のコンピュータプログラム。

**【発明の詳細な説明】****【技術分野】****【0001】**

10

本発明は、暗号化キーを生成するための電子システムに関するもので、本システムは物理的クローン不能関数として使用されるメモリであって、本メモリは書き込み可能で、揮発性であり、メモリに電源投入したたびに、メモリがメモリの少なくとも部分的にランダムな物理的特性に応じたメモリコンテンツに確定するように構成されており、本メモリはメモリインターフェースを通してアクセス可能であるメモリ、およびメモリが確定したメモリコンテンツから暗号化キーを導出するように構成されたキー導出ユニットを備えている。

**【背景技術】****【0002】**

物理的クローン不能関数（PUF）は、安全なメモリへのキー、識別子などの保存を含む、多くの形の安全な識別情報の利点となる代替物であることが証明されている。

20

**【0003】**

物理的クローン不能関数は、製造上の変動を利用してデジタル識別子を導出する。こうして、デジタル識別子は物理的な媒体と関係されている。物理的クローン不能関数はランダムプロセスの変動に応じて異なるので、PUFを作成するのは容易であるが、特定の事前に定義された識別子を生み出すPUFを作成することは、不可能でないにしても非常に困難である。製造上の変動は、メモリ素子の様々な物理的特性という結果になる。例えば、物理的特性には、すなわち、ドーピング濃度、酸化膜厚、チャネル長、（例えば、金属層の）構造上の幅、寄生（例えば、抵抗、静電容量）などが含まれる。デジタル回路設計が何度も製造される時、これらの物理的特性はわずかに変化し、同時にそのため、I C 素子の動作、例えば、メモリ素子などが一部の状態で様々に動作するようになる。例えば、起動時の動作は、物理的特性の製造上の変動で決定される。

30

**【0004】**

PUFの便利な選択は、揮発性メモリ、具体的には、フリップフロップベースのメモリ、より具体的には、スタティックランダムアクセスメモリ（SRAM）である。そのようなメモリは評価が容易で、製造コストが低価である。SRAMベースのPUFは、SRAM PUFと呼ばれている。SRAMは、電源投入後に、オンビットとオフビットのランダムパターンで満たされる。パターンは、SRAMが次回、電源投入される場合にそれ自身を正確に繰り返さない可能性があるが、そのような2つのパターン間の相違は通常、当該状態でのビットの半数をかなり下回るものである。同じSRAMのメモリ電源投入コンテンツ間の相違は通常、異なるSRAMのメモリ電源投入コンテンツ間の相違よりもかなりわずかなものである。

40

**【0005】**

PUFは、同じチャレンジが2度評価される時、正確に同じ結果を生み出さない可能性があるので、ファジィエクストラクタとも呼ばれる、いわゆるヘルパーデータアルゴリズムが使用され、導出される場合には必ず、キーが同じになることが確保され得る。ノイズの多い測定値から再現可能な値を構築するためにヘルパーデータを使用する1つのやり方が、例えば、WO 2006 / 129242「ヘルパーデータシステムでのテンプレートの更新（Template Renewal in Helper Data Systems）」などで記述されている。

50

## 【0006】

特定のSRAM PUFでのPUFの一適用例は、電子回路で暗号化キーを導出することである。電子回路には通常、集積回路（IC）および／またはプログラム可能論理が含まれる。

## 【0007】

PUFの1つの利点は、それらが耐タンパ特性を生来所持していることである。PUFがないと、暗号化キーは攻撃者により、キーが従来保存されている不揮発性メモリに対する物理的攻撃を展開することによって回復され得る。例えば、攻撃者はメモリを開き、当該コンテンツを綿密に調べ得る。PUFの使用によって、このタイプの攻撃はかなり困難になる。その理由は、PUFを開いても通常、それが妨害されること、つまり動的コンテンツのSRAMの綿密な調査は、埋め込み不揮発性メモリの綿密な調査よりも非常に困難であることである。したがって、攻撃者が自分の綿密な調査から習得する情報は、暗号化キーの作成に使用されたインタラクションに関係がないものである。これによって、攻撃者が物理的攻撃を使用してキーを見つけることはより困難になる。

10

## 【0008】

あいにく、侵入性の物理的攻撃は、攻撃者がPUFの内部の状態の少なくとも一部の情報を取得し得る攻撃ベクトルのみではない。いわゆるサイドチャネルでも情報がリークされ得る。サイドチャネルとは、システム内部で発生する物理的現象に関連したシステムの情報ソースで、システム外部から観察され得、少なくともある程度、意図された、観察可能な、出入力動作だけではなく、システムの内部の動作および／または状態に相關した情報を明らかにするものである。

20

## 【0009】

電力消費、時間消費、および電磁放射は、暗号化システムに関連するサイドチャネルの例である。例えば、システムが暗号化キーを使用する間にモニタされる暗号化システムの電力消費は、ある程度、キーに相關され得る。暗号化キーを内密に保つことが最も重要なので、当該キーに相關された情報が少しでもリークすることは問題である。

## 【0010】

「物理システムに応じて暗号化キーを確立するためのシステム（System for establishing a cryptographic key depending on a physical system）」と題する、WO2010/100015として公開された、WO2010/051631では、PUFからのキーの導出のエラー訂正部分の間、すなわち、ヘルパーデータアルゴリズムの実行の間に発生するサイドチャネルのリークを低減化するための解決策が開示されている。エラー訂正是サイドチャネルのリークを回避するためにとりわけ重要な段階で、その理由は、それが非線形相關を導入している、機密データを複数回、処理しているからである。その上、エラー訂正がソフトウェアに実装されている場合、リークは増加する。

30

## 【先行技術文献】

## 【特許文献】

## 【0011】

【特許文献1】国際公開第2006/129242号

40

【特許文献2】国際公開第2010/100015号

【特許文献3】国際公開第2010/051631号

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0012】

エラー訂正の間に発生し得るサイドチャネルのリークが対処されると、サイドチャネルのリークのより小さなソースが残るということが判明している。これらのより小さなソースはより精巧な測定を必要とし、測定に成功しても、比較的わずかな機密情報のみを提供するが、それにもかかわらず、秘密キーの導出間に発生し得るサイドチャネルの他のソースに対処したいという要望がある。

50

## 【0013】

S R A M P U F などのメモリベースの P U F の電力消費が測定される時、1つのサイドチャネルがメモリの読み出しプロセス間に発生する。例えば、P U F の制御ブロックがメモリインターフェースを通じて接続されるメモリの起動の値（電源投入時のメモリコンテンツ）を読み出す間である。メモリインターフェースの電力消費は転送されるデータワードのハミング重みに依存する。S R A M メモリコンテンツの読み出しによって、電力または電磁解析またさらに光子放出攻撃を通じて読まれるデータバイトのハミング重みの情報がリークし得る。

## 【0014】

ハミング重みと電力消費の間が完全に対応していると想定する場合、8ビット幅のメモリインターフェースのデータリークは、理論上、バイトごとに 2 . 54 ビット位、すなわち、30%に上ることになる。実際のところ、対応関係は完全よりかなり少なく、したがって情報のリークは非常にわずかであるが、メモリベースの P U F のメモリインターフェースにおいてサイドチャネルのリークを低減化する必要がある。理論上、ビットあたりの最大リークは、メモリインターフェースがより広くなるにつれ急速に低下する。例えば、ビットあたりの理論上のリークは、メモリインターフェースが 16 ビットに増大する場合には、ほとんど半減される。しかし、メモリインターフェースがよりコスト高になり、より電力を消費すると、一部の環境では使用できなくなる。

10

## 【0015】

光子放出攻撃は、集積回路で状態が変わる時に放出され得る数個の光子により形成される光サイドチャネルを利用する。

20

## 【課題を解決するための手段】

## 【0016】

暗号化キーを生成するための電子システムが提供されている。本システムは物理的クローン不能関数として使用されるメモリであって、本メモリは書き込み可能で、揮発性であり、メモリに電源投入したたびに、メモリがメモリの少なくとも部分的にランダムな物理的特性に応じたメモリコンテンツに確定するように構成されており、本メモリはメモリインターフェースを通してアクセス可能であるメモリ、およびメモリが確定したメモリコンテンツから暗号化キーを導出するように構成されたキー導出ユニットを備えている。

## 【0017】

30

暗号化キーを生成するための電子システムはさらに、メモリインターフェースを通してメモリに、そしてキー導出ユニットに接続されたメモリ読み出しユニットを備え、本メモリ読み出しユニットはスクランブルされた順序でメモリインターフェースによりメモリコンテンツを取り出すためのアドレススクランブラーを備えている。

## 【0018】

メモリコンテンツはスクランブルされた順序でメモリインターフェースを介し転送されるので、サイドチャネルのリークが低減化される。データワード自体のハミング重みはなおりークされるが、ハミング重みとメモリコンテンツの特定のデータワード間の対応関係、それは失う。メモリコンテンツがメモリコンテンツを構成する個々のデータワードのサイズに比べると大きい場合、サイドチャネルのリークでの低減化も大きくなる。これは、この場合、測定されたハミング重みが属し得る可能性のある多くのデータワードがあるからである。これがとりわけ都合の良いのは、潜在的リークはデータワードが小さい場合（8ビット以下）にはより大きくなるからである。1024ビットのメモリコンテンツ以上にに対するサイドチャネルのリークは無視できると推定される。

40

## 【0019】

ハミング重みに依存する電力の相違からリークされる情報量を低減化することを試みる多くの潜在的な対応策は不適当であることに留意されたい。例えば、いわゆる定重み符号は対応策として提案されている。定重み符号では、すべての機密データは、通常、データワードのビットサイズの半分に等しい、固定されたハミング重みを有するデータワードに符号化される。この対応策はハミング重みに依存する電力の相違を低減化するが、たとえ

50

ば安全なメモリにキーを記憶する場合、メモリベースの PUF には不適当である。メモリコンテンツを決定する物理的な特性がランダムなので、すなわち、メモリコンテンツの符号化の特定のタイプを定めることができない。

#### 【 0 0 2 0 】

暗号化キーを生成するための電子システムは、スマートカードなどのモバイルコンピューティングデバイス、携帯電話などのモバイル通信デバイス、タブレットなどに含まれ得る。メモリコンテンツから導出されたキーは、システムがキーの所持を有すると判定するチャレンジ応答プロトコルで使用され得る。キーは、例えば、暗号化記憶装置または通信において、機密性保護のために使用され得る。導出されたキーは対称キーであり得るが、例えば、非対称キーを見つけるためのシードとしてキーを使用することによって、非対称の公開／秘密キーのペアであってもよい。

10

#### 【 0 0 2 1 】

暗号化キーを生成するための電子システムは、集積回路に含まれ得る。例えば、集積回路は ASSP、すなわち、広範囲な市場に適用可能な特定の機能を実装する特殊な集積回路であり得る。ASSPは、例えば、オーディオ／ビデオコーデックの実装に使用される。暗号化キーを使用する暗号化関数をサポートするASSPの安全性は、本明細書に記述されている暗号化キーを生成するための電子システムで暗号化キーを生成することによって改善される。

#### 【 0 0 2 2 】

例えば、集積回路はDSPとし得る。これによって、例えば、PUF生成されたキーまたはそれから導出されたものによる暗号化を使用するアプリケーションを改善し、例えば、ストリーミングコンテンツを保護すると同時に、キーを安全に保持する。

20

#### 【 0 0 2 3 】

PUF生成されたキーは認証および／または安全な通信チャネルの確立のための信頼のルートとして使用され得る。後者は、例えば、暗号化キーを生成するための電子システムを備えるNFCチップにとって重要になり得る。

#### 【 0 0 2 4 】

メモリは物理的クローン不能関数として使用される。メモリは、2つの安定状態に構成され得る、複数のバイナリ記憶素子を備え得る。起動時、各バイナリ記憶素子は2つの安定状態の1つに確定する。どちらの状態に確定するかは、記憶素子の精密な製造、例えば、ドーピングレベルにより大半が決まるが、素子が確定する状態はさらに、偶然変動にも影響される。例えば、メモリは複数のフリップフロップ、特に、Dタイプのフリップフロップを備え得るもので、特に、メモリはSRAMメモリであり得る。メモリの電源投入コンテンツは、ノイズおよび振動の影響を受けやすい。一部のFPGAのものは、物理的クローン不能関数として使用されるメモリとして使用され得る初期化されていないSRAMロックを備えている。

30

#### 【 0 0 2 5 】

メモリインタフェースはアドレスチャネルおよびデータチャネルを備え得る。メモリへのスクランブルされたアクセスは、例えば、メモリアドレスがアドレスチャネルに置かれる前に、メモリアドレスを暗号化するなどのスクランブルによって達成され得る。その場合、異なるキーを選択すると、異なるスクランブル順序が取得され得る。好適には、スクランブル順序が攻撃者に知られず、すなわち、秘密であり、より好適には、スクランブル順序がデバイスで一意であり、例えば、製造時に選択されており、より好適には、スクランブル順序がシステム自体で頻繁に変更され、さらにより好適には、スクランブル順序がメモリ読み出しユニットの起動時に少なくとも一部がランダムに決定されることである。

40

#### 【 0 0 2 6 】

電力解析、電磁解析、および光子放出攻撃では通常、優れた信号対雑音比を得るために多くの繰り返された測定（追跡）を必要とする。そして統計的解析がその繰り返された測定に対して行われる。読み出し順序をランダム化し、またさらに定期的に読み出し順序を変更することによって、この解析が妨害される。

50

## 【0027】

キー導出ユニットは、メモリが確定したメモリコンテンツから暗号化キーを導出するように構成されている。導入ユニットはメモリコンテンツからノイズを除去する。例えば、これは不揮発性ヘルパーデータメモリで、物理的クローン不能関数として使用されるメモリのために構築されたヘルパーデータを記憶するヘルパーデータメモリ、訂正可能なビットストリングを確立するためのコンバイナで、本訂正可能なビットストリングがエラー訂正コードの訂正可能な近傍にあり、ヘルパーデータメモリからヘルパーデータを取り出し、メモリが確定したメモリコンテンツと取り出されたヘルパーデータを組み合わせるよう構成されたコンバイナ、およびエラー訂正アルゴリズムを使用して訂正可能なビットストリングからエラー訂正コードのコードワードを確立するように構成されたエラーコレクタを備えている。

10

## 【0028】

ヘルパーデータはメモリの1つの特定な物理的具体化に対して構築される。その理由は、様々なメモリチップのメモリの起動コンテンツは異なり過ぎているからである。メモリコンテンツがスクランブルされた順序で取得される場合、ヘルパーデータはスクランブルされた同じ順序で適用され得るか、またはスクランブルされたメモリコンテンツがスクランブル解除される。ハイブリッド解決策が可能である。例えば、スクランブルは、すなわち、スクランブル順序の逆転である並べ替えを行い、同時に、固定した事前に定義された順序が適用されることによって除去される。事前に定義された順序は、攻撃者には秘密であり得る。例えば、システムは製造中に事前に定義された順序で構成され得る。事前に定義された順序は、デバイスごとに異なるものであり得る。

20

## 【0029】

メモリ読み出しユニットは、メモリを安全に読み出すように構成されている。スクランブルされた順序でメモリインタフェースによりメモリコンテンツを取り出すために、アドレススクランブルアダプタが使用され得る。メモリの暗号化は、コンテンツが定められ得ないので、PUFの保護には直接的には適していない。順序を変更すること、すなわち、並べ替えることによってデータの難読化を示すスクランブルのことを言及しており、これはデータ自身の、すなわち暗号化を通じての変更によるデータの難読化とは異なるものである。

## 【0030】

PUFからの暗号化キーの再構築の場合、PUFデータは、特に事前に定義された順序で、ヘルパーデータと組み合わされていなければならない。PUFの制御ブロックの設計では、ヘルパーデータが線形順序で読み出され得る場合に、より効率的である。特に、ヘルパーデータがランダムアクセスの外部アドレスバス提供していないが、データがブロック単位ベースで読み出される必要があり、何百から何千のビットの通常のブロックサイズを伴うメモリである場合である。例えば、ヘルパーデータメモリフラッシュメモリの場合、ヘルパーデータを異なる順序で読み出すことは非効率である。ヘルパーデータが線形的に読み出されうる場合、これは利点となるはずである。一実施形態では、ヘルパーデータがブロックごとに読まれ、各ブロックは線形的に読まれる。同時に、メモリインタフェースを介して受信された後、メモリコンテンツのスクランブル解除を回避することも利点となる。

30

## 【0031】

このことは、メモリ読み出しユニットに暗号化および復号ユニットを有することによって、達成され得る。暗号化ユニットは、メモリを暗号化するように構成され、本暗号化ユニットはメモリインタフェースからメモリがスクランブルされた順序で確定したメモリコンテンツを受信し、受信したメモリコンテンツを暗号化し、暗号化されたメモリコンテンツをメモリに書き戻すように構成されている。復号ユニットは、メモリを復号するように構成され、メモリインタフェースから事前に定義された順序で暗号化されたメモリコンテンツを受信し、受信した暗号化されたメモリコンテンツを復号して事前に定義された順序でメモリが確定したメモリコンテンツを取得するように構成されている。

## 【0032】

40

50

これによって、2つの段階で、メモリ電源投入データなど、事前に符号化され得ないデータの安全な読み出しが提供される。第1の段階で、安全性はスクランブル（並べ替え）により達成され、第2の段階で、安全性は暗号化により達成される。第1の段階では、ランダムアクセスを提供しないが、第2の段階で、メモリは望む任意の順序、特に、ヘルパーデータと組み合わせるために必要とされる順序でアクセスされ得る。後者は線形であり得るが、さらに追加の難読化のために何らかの他の事前に定義された順序にもし得る。後者の場合、ヘルパーデータは、同じ事前に定義された順序で S R A M データに対して準備された。ヘルパーデータの観点からすれば、S R A M データが読み出される順序は、当該順序が、ヘルパーデータが準備された時と同じである限り、問題ではない。

## 【0033】

10

暗号化では、データの各ブロックを一時キーで暗号化し得る。一時キーは、システム内部で導出され得る。例えば、一時キーは、おそらく P U F 制御ブロックの内部である、第2の P U F から導出され得、第2の P U F は読み出される順序がバラバラなものおよび／または暗号化に対してランダム性を提供する。一実施形態では、暗号化されデータブロックは、直ちに S R A M に書き戻される。一実施形態では、暗号化ユニットは、スクランブルされた順序で暗号化コンテンツデータを書き戻し、それによって、メモリコンテンツを暗号化されたメモリコンテンツで上書きする。

## 【0034】

スクランブルされた読み出しあり暗号化された書き戻しは、ヘルパーデータが処理される前に行われる準備ステップである。暗号化キーが構築される必要がある時、すべての S R A M P U F データが順々に読み出され、ヘルパーデータとの排他的論理和をとられる前に暗号化される。

20

## 【0035】

事前に定義された順序で書き込み可能メモリを安全に読み出すための電子メモリ読み出しづニットは特に利点となる。発明者らは、読み出しづニットが他の書き込み可能メモリの安全な読み出しのためにも同様に使用され得ることを理解している。こうして、安全で、保護されたサイドチャネル、読み出しを必要とし、何らかの理由で、事前に符号化または暗号化、つまり、ハミング重みの平衡コードで暗号化または符号化され得ないすべてのメモリは安全に読まれ得る。メモリは書き込み可能であることが好適である。その理由は、ツーパス方法が可能だからである。メモリは、例えば、揮発性でありうる（例えば P U F として使う）、または不揮発性でありうる（例えばデータ転送のために）。

30

## 【0036】

一実施形態では、読み出しづニットは、P U F として使用されるメモリとは異なり、さらなるメモリに電源投入したたびに、第2のメモリがノイズのあるメモリコンテンツに確定するように構成されたさらなる揮発性メモリを備え、該シードは第2のメモリが確定したメモリコンテンツから導出される。

## 【0037】

メモリの読み出しを繰り返すことが必要な場合がある。例えば、一部の実施形態では、P U F として使用されるメモリは、P U F 制御ブロックの電源、あるいは特に、メモリ読み出しづニットから独立して、再度電源投入され得る。例えば、このことは、暗号化キーを再度導出するために行われ得、これによって、キーが使用されると直ぐに削除されることが可能になる。しかし、ランダム性が新しい値を作成するための電源投入に依存する P U F 、例えば、メモリベースの P U F から取得される場合、P U F は新しいスクランブル順序を提供しない。このことは、新しいシードを取得するためにシードに適用されるように構成された暗号化一方向性関数を備える読み出しづニットによって回避され、アドレススクランブラーは電源投入しなくとも、新しくスクランブルされた順序でメモリインタフェースによりメモリコンテンツの再フェッチのための新しいシードから新しくスクランブルされた順序を導出するように構成される。例えば、メモリ読み出しづニットは、P U F として使用されたメモリが再度電源投入されたという信号を受信するように構成され得る。信号を受信すると、一方向性関数が適用され、新しいシードおよび／または暗号化キー

40

50

が導出される。

【0038】

さらなる PUF、または第2のPUFがPUF制御ブロックおよび/またはメモリ読み出しユニット内部にあることは好適であり、したがって、これは別個のSRAM PUFであり得る。第2のPUFは、SRAM PUFの測定のために読み出される必要のあるメモリアドレスのランダムな並べ替えを作成するために使用され得るランダムシードを生成するために使用され得る。例えば、ハッシュ関数などの調整アルゴリズムは、PUF応答からランダムシードを計算するために使用され得る。

【0039】

第2のPUFもIPブロックに容易に統合され得る標準的な構成部品から構成されることが好適である。DFF PUFはこの状態のための良い選択である。Dフリップフロップの起動値は十分にランダムである。一方向性関数は、AES、DES、SHAなどの、暗号ブロックであり得る。

【0040】

本発明の一態様は、暗号化キーを生成するための方法である。本方法は物理的クローン不能関数として使用されるメモリであって、本メモリは書き込み可能で、揮発性であるメモリの電源投入、メモリがメモリの少なくとも部分的にランダムな物理的特性に応じたメモリコンテンツに確定し、スクランブルされた順序でメモリインタフェースによりメモリコンテンツを取り出すことを可能にすること、メモリが確定したメモリコンテンツから暗号化キーを導出することを含んでいる。

【0041】

本方法の一実施形態は、メモリインタフェースから、メモリがスクランブルされた順序で確定したメモリコンテンツを受信し、受信したメモリコンテンツを暗号化し、暗号化したメモリコンテンツをメモリに書き戻すことによってメモリを暗号化すること、および事前に定義された順序で暗号化されたメモリコンテンツをメモリインタフェースから受信することでメモリを復号すること、メモリが事前に定義された順序で確定したメモリコンテンツを取得するために受信した暗号化されたメモリコンテンツを復号することを含んでいる。

【0042】

本発明による一方は、コンピュータ実装方法としてコンピュータで、または専用ハードウェアで、または両方の組み合わせで実施され得る。本発明による方法の実行可能コードは、コンピュータプログラム製品に格納され得る。コンピュータプログラム製品の例には、メモリデバイス、光学式記憶装置、集積回路、サーバ、オンラインソフトウェアなどが含まれる。コンピュータプログラム製品が、前記プログラム製品がコンピュータで実行される時に、本発明による方法を行うためにコンピュータ読み取り可能媒体に格納された非一時的プログラムコード手段を含んでいることは好適である。

【0043】

一好適な実施形態では、コンピュータプログラムは、コンピュータプログラムがコンピュータで実行される時に本発明による方法のすべてのステップを行うように適合されたコンピュータプログラムコード手段を含んでいる。コンピュータプログラムがコンピュータ読み取り可能媒体で具現化されることは好適である。

【0044】

本発明のこれらおよび他の態様は、これ以後に記述される実施形態を参照する時に明らかになり、解明されるであろう。各図面は次のとおりである。

【図面の簡単な説明】

【0045】

【図1a】暗号化キーを生成するための電子システムを例示するブロック図である。

【図1b】図1aのシステムで使用されるキー導出ユニットを例示するブロック図である。

【図2】暗号化キーを生成するための電子システムを例示するブロック図である。

10

20

30

40

50

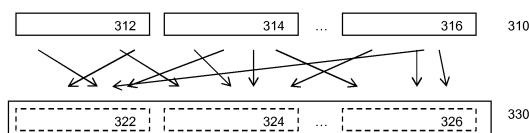

- 【図3a】スクランブルを保持するコードワード境界を例示するブロック図である。

【図3b】スクランブルを保持する非コードワード境界を例示するブロック図である。

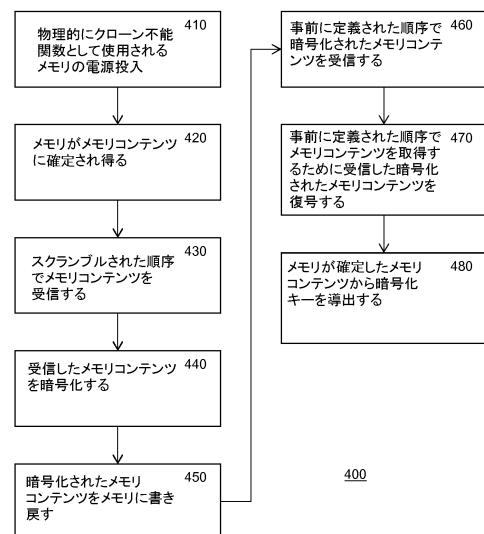

【図4】暗号化キーを生成するための方法を例示する流れ図である。

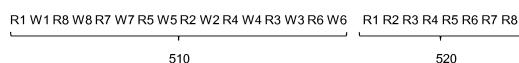

【図5a】メモリのスクランブルおよび暗号化のための可能性を例示している図である。

【図5b】メモリのスクランブルおよび暗号化のための可能性を例示している図である。

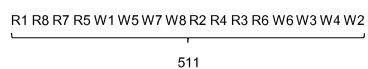

【図5c】メモリのスクランブルおよび暗号化のための可能性を例示している図である。

【図5d】メモリのスクランブルおよび暗号化のための可能性を例示している図である。

## 【発明を実施するための形態】

## 【0046】

異なる図面で同じ参照番号を有する要素は同じ構造的特徴および同じ機能、または同じ信号を有していることに留意していただきたい。そのような要素の機能および／または構造が説明されている箇所では、詳細な説明で、それを繰り返して説明する必要性はない。

10

## 【0047】

ブロック図の参照番号のリスト

|     |                        |    |

|-----|------------------------|----|

| 100 | 暗号化キーを生成するための電子システム    | 20 |

| 110 | 物理的クローン不能関数として使用されるメモリ |    |

| 112 | メモリの位置                 |    |

| 114 | メモリの位置                 |    |

| 116 | メモリの位置                 |    |

| 120 | メモリインターフェース            |    |

| 122 | データチャネル                |    |

| 124 | アドレスチャネル               |    |

| 130 | PUF制御ブロック              |    |

| 140 | アドレススクランブラー            |    |

| 150 | キー導出ユニット               |    |

| 152 | バッファ                   |    |

| 154 | 並べ替え装置                 |    |

| 156 | エラー訂正論理                |    |

| 200 | 暗号化キーを生成するための電子システム    | 30 |

| 210 | PUF制御ブロック              |    |

| 220 | メモリ読み出しユニット            |    |

| 230 | キー導出ユニット               |    |

| 240 | 暗号化ユニット                |    |

| 250 | 復号ユニット                 |    |

| 255 | アドレス生成器                |    |

| 260 | さらなるメモリ                |    |

| 265 | ランダムキーおよびシード導出ユニット     |    |

| 270 | バッファ                   |    |

| 280 | コンバイナ                  | 40 |

| 285 | ヘルパーデータメモリ             |    |

| 290 | エラー訂正器                 |    |

| 295 | キー導出関数ユニット             |    |

| 310 | メモリコンテンツ               |    |

| 312 | コードワードサイズ調整メモリチャンク     |    |

| 314 | コードワードサイズ調整メモリチャンク     |    |

| 316 | コードワードサイズ調整メモリチャンク     |    |

| 320 | スクランブルされたメモリアクセス       |    |

| 322 | コードワードサイズ調整メモリチャンク     |    |

| 324 | コードワードサイズ調整メモリチャンク     |    |

| 326 | コードワードサイズ調整メモリチャンク     | 50 |

3 3 0 スクランブルされたメモリアクセス

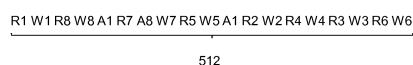

5 1 0 暗号化段階

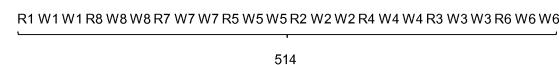

5 1 1 暗号化段階

5 1 2 暗号化段階

5 1 4 暗号化段階

5 2 0 復号段階

【 0 0 4 8 】

本発明は多くの異なる形の実施形態で可能であるが、図面で示しているとおり、本明細書では、1つ以上の特定な実施形態を詳細に説明することにしており、そのため、本開示は本発明の原理の例示として考慮されるべきであり、示され、記述される特定の実施形態に本発明を制限する意図はないことを理解していただきたい。 10

【 0 0 4 9 】

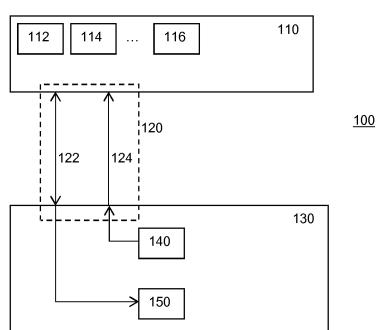

図1aおよび図1bは、暗号化キーを生成するための電子システム100をブロック図として例示している。

【 0 0 5 0 】

システム100は、物理的クローン不能関数( PUF )として使用されるメモリ110を備えている。メモリは書き込み可能および揮発性の種類からできている。その上、メモリは、メモリの各電源投入時に、メモリがメモリの少なくとも部分的にランダムな物理的特性に応じたメモリコンテンツに確定するという特性を有している。物理環境的変動は通常、製造中のわずかなプロセス変動により引き起こされる。 20

【 0 0 5 1 】

メモリが確定するメモリコンテンツはそのような物理的特性に応じて異なるので、メモリコンテンツはメモリの特定の具体化の識別となる。つまり、同じ設計の2つのメモリ110は、メモリを識別するために十分異なるメモリコンテンツを起動時に示す。例えば、メモリ110はフリップフロップに基づき得、特に、メモリ110はSRAMであり得る。

【 0 0 5 2 】

メモリ110は、電源投入時のコンテンツがPUFとして使用されるメモリ位置のシーケンスを備えている。メモリ位置はアクセス可能で、つまり、対応するメモリアドレスのシーケンスを通して、読み取りまたは書き込みアクセスが可能である。メモリ位置のシーケンスの3つが112、114、および116で示されている。 30

【 0 0 5 3 】

システム100はPUF制御ブロック130を備えている。PUF制御ブロック130は、メモリ110が暗号化キーを作成するために起動時に確定するメモリコンテンツを処理するように構成されている。未処理の状態では、メモリコンテンツはキーとして直接使用できない。電源投入時のメモリ110のメモリコンテンツは、物理的特性だけではなく、メモリコンテンツはさらにノイズにも影響される。その上、温度、メモリに対する機械的ストレスなど、環境の物理的変動の影響もある。メモリコンテンツは、ノイズの影響を受けやすいので、暗号化キーとして直接使用することはできない。さらに、単一ビットのエントロピーが低過ぎる場合もある。PUF制御ブロック130は、エラー訂正および任意選択でキーの導出によってこれらに対応する。エラー訂正などは、キー導出関数150によって行われ、これは制御ブロック130に含まれている。 40

【 0 0 5 4 】

PUF制御ブロック130は、メモリインターフェース120を通じてメモリ110に接続されている。メモリインターフェース120は、例えば、データ回線などのデータチャネル122、および例えば、アドレス線などのアドレスチャネル124を備えている。メモリインターフェース120はさらに、制御線なども備えている。

【 0 0 5 5 】

メモリインターフェースの使用には、これが潜在的サイドチャネルであるという欠点がある。データチャネル122により通信されるワードのハミング重みはシステム100の電 50

力消費を観察することによって決定され得、同時に、ワードはデータチャネル 122 により転送される。例えば、データチャネル 122 が 8 ビット幅の場合、各ワードは情報の 1 ~ 2 ビットのオーダーでリークしうる。そのようなリークには、システム全体の安全性が含まれる。

#### 【0056】

スクランブルされた順序でメモリインタフェースによりメモリコンテンツを取り出すために、制御ブロック 130 はアドレススクランブラー 140 を備えている。アドレススクランブラー 140 が（疑似）ランダムな並べ替えを実施することは好適である。例えば、アドレススクランブラー 140 は、スクランブルされた順序でメモリアドレスのシーケンスを生成する。アドレススクランブラー 140 を実装する都合の良いやり方は、適切にサイズ調整された暗号化関数によってメモリアドレスのシーケンスを暗号化することによるものである。都合の良いことに、メモリ 110 のサイズは 2 の累乗なので、ビットの整数値によって 1 対 1 でアドレス指定され得る。この場合、ブロック暗号が使用され、ビットの整数値に等しいブロック幅を有し得る。そのようなブロック暗号は、ファイステル構造を使用して構築され得る。ファイステル構造は不均衡になり得るので、例えば、いわゆるソープシャッフル (Thorps shuffle) が使用され得る。任意のアドレス指定スキームまたは任意のサイズを有するメモリ 110 では一般により多くが、いわゆるフォーマット保持暗号化を使用して収容され得る。フォーマット保持暗号化は、アドレスのシーケンスをそれ自体に全単射的にマッピングする。

#### 【0057】

暗号化が使用される時、アドレススクランブラー 140 は、任意の順序、たとえば線形的にアドレスのシーケンスを生成し、シーケンスを暗号化し得る。スクランブルされた順序でアドレスのシーケンスを生成する代替のやり方が使用され得る。例えば、アドレススクランブラー 140 は、スクランブルされた順序でメモリアドレスのシーケンスを作成するように構成された、フィードバックシフトレジスタ、例えば、線形フィードバックシフトレジスタを備え得る。

#### 【0058】

メモリ 110 が確定したメモリコンテンツがスクランブルされた順序で取り出される。

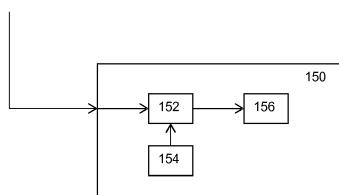

#### 【0059】

図 1a、図 1b の実施形態では、キー導出ユニット 150 はスクランブルされた順序でメモリコンテンツを受信する。図 1b では、メモリコンテンツを処理する特定のやり方を示している。

#### 【0060】

キー導出関数 150 は、バッファ 152、並べ替え装置 154、およびエラー訂正論理 156 を備えている。

#### 【0061】

バッファ 152 は、メモリ 110 から、例えば、メモリ読み出しユニット（図 1a では個別に図示されていない）から受信したメモリコンテンツをバッファリングする。並べ替え装置 154 はアドレススクランブラー 140 により適用される逆転並べ替えを行う。並べ替え装置 154 は、メモリ 110 で作成されたものと同じ順序でメモリコンテンツをバッファ 152 で作成し得る。しかし、並べ替え装置 154 は、事前に定義された順序を表す並べ替えとスクランブルされた並べ替えの逆転との関数合成を行うことによって、事前に定義された任意の順序でメモリコンテンツをバッファ 152 で作成し得る。並べ替え装置 154 は、正しいスクランブル解除動作を取得するために、スクランブラー 140 に接続されるか、またさらに統合され得る。逆転並べ替えの結果がエラー訂正論理 156 に渡される。エラー訂正論理 156 はヘルパーデータと組み合わされることによってノイズを訂正し、任意選択で、キー導出関数 (KDF) を結果に適用し、例えば、結果は暗号化ハッシュ関数でハッシュされ得るはずである。PUF として使用されるメモリのメモリコンテンツのノイズの訂正是それ自体知られているキー導出関数ではなく、メモリ読み出しユニットとともにバッファ 152 および並べ替え装置 154 を含み得る。

10

20

30

40

50

## 【0062】

メモリコンテンツはスクランブルされた形でメモリインタフェースを介してのみ移動するので、依然、ハミング重みを示すが、ハミング重みが対応するワードがもはや不明なので、リークされる情報はかなり少なくなる。

## 【0063】

このことはかなりの利点であるが、図1a、図1bの実施形態には、いくつかの欠点がある。まず第1に、これには、並べ替え装置154によって、行われるスクランブル解除動作が必要である。これは、とりわけ、所定の位置で行われる必要のある場合、比較的コストのかかる動作である。

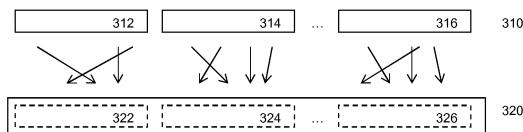

## 【0064】

エラー訂正論理156が単一のコードワードを使用する場合には、バッファ152は、所定の位置ではないスクランブル解除を使用するために、メモリ110のサイズの2倍であるはずである。これは比較的コストがかかる。しかし、より小さいコードワードの訂正是リソースの効率をより増大させるので、エラー訂正では複数のコードワードを使用することが好適である。この場合、スクランブル動作は、コードワードの境界を考慮するように構成され得るが、例えば、より大きなバッファの使用または本明細書で記述される他の解決策の使用という他のオプションもある。図3aは、スクランブル動作を例示している。

## 【0065】

メモリコンテンツ310はコードワードサイズのメモリチャネルに分割される。図3aはそのような3つのチャネル312、314、316を示している。チャネルのそれぞれは、他のチャネルから独立してエラー訂正され得る。320では、メモリの同じ部分が図示されているが、メモリアクセスがスクランブルされている。矢印は、元のアドレスに対応したスクランブルされたアドレスを指している。このマッピングはコードワード境界を考慮していることに留意されたい。つまり、メモリアドレスのシーケンスは一連のメモリアドレスの複数のコードシーケンスを含み、アドレススクランブラー140は、1つの複数のコードシーケンスが異なるシーケンスのアドレスによってインターりーブされることなく、共に生成されるようにアドレスのシーケンスを生成する。そのようなアドレスのスクランブルによってサイドチャネルのリークの防止はより少なくなるが、著しい改善がある。図3bは、コードワード境界を考慮しないスクランブルされたメモリアクセス330を示している。このようなスクランブル関数では、リークをより防止できるが、図1のキー導出関数によって収容するのは（不可能ではないが）より困難である。図2に関連して以下で記述するシステムでは、2つのパスシステムを使用して、必ずしもコードワード境界を考慮する必要のない、スクランブルされたメモリアクセス330などのスクランブルされたメモリアクセスを処理できる。

## 【0066】

並べ替え装置154を使用する代わりに、スクランブルをヘルパーデータと組み合わせの間に考慮に入れることも可能である。この場合、キー導出ユニット150は、バッファ152から、およびヘルパーデータメモリから（図1bではどちらも図示していない）読むコンバイナを含み得る。このアプローチではさらに、ヘルパーデータメモリは通常、不揮発性メモリで、通常、ブロック単位で読み出され、そのため、ヘルパーデータのランダムアクセスではよく、高い性能上のペナルティがつくという欠点がある。

## 【0067】

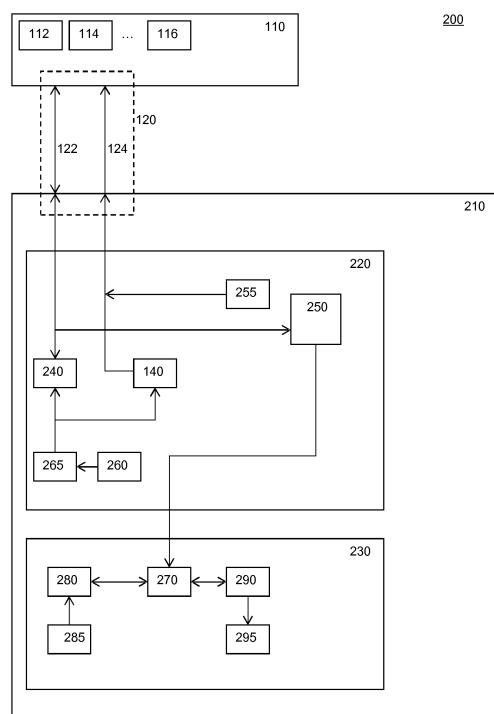

図2は、暗号化キーを生成するための改善された電子システム200を例示している。図4は、バリエーションが可能であるが、システム200を使用して行い得る暗号化キーを生成するための方法を流れ図で例示している。

## 【0068】

システム100と同様に、システム200は、メモリインタフェース120を通して、PUF制御ブロック210に接続されたPUFとして使用されるメモリ110を備えている。PUF制御ブロックは、メモリ読み出しユニット220およびキー導出ユニット23

10

20

30

40

50

0を備えている。

#### 【0069】

メモリ読み出しユニット220は、事前に定義された順序で安全にメモリ110を読み出すように構成されている。事前に定義された順序は、後続のキー導出のために何が都合が良いかによって決められる。通常、事前に定義された順序は自然な線形順序であるが、任意の順序が可能である。例えば、難読化が増大している場合、ランダムであるが、固定された事前に定義された順序も選択され得、ヘルパーデータは、当該ランダムであるが、固定された事前に定義された順序にしたがって並べ替えられたメモリコンテンツに対して計算され得る。ここから、事前に定義された順序は線形であるものとするが、これは変更され得ることに留意していただきたい。メモリコンテンツは、メモリ110の電源投入によって取得され（ステップ410）、メモリはメモリコンテンツに確定される（ステップ420）。確定時間はメモリにより異なるが、必要に応じて、実験的に決められ得る。確定時間は通常、電子コンピューティングデバイスで通常、行われるブート機能よりもかなり短いので、通常、メモリの読み出しユニットのソフトウェア実装のためにメモリの読み出しを遅延させる遅延素子を導入することは必要とはされない。

10

#### 【0070】

キー導出ユニット230は、メモリ110がメモリ読み出しユニット220から事前に定義された順序で確定したメモリコンテンツを受信する。一実施形態では、あるものは普通のPUF処理（エラー訂正および通常のキー導入関数）を行うように構成された、知られているキー導出ユニットを使用し得る。知られているキー導出ユニットが使用される場合には、キー導出ユニット230の観点から、これは通常のメモリコンテンツデータを受信する。こうして、システムのこの部分のみがおおまかな説明を与えられる。

20

#### 【0071】

キー導出ユニットはバッファ270を備え得る。バッファ270は単一のコードワードを保持できるほど大きい。キー導出関数は、ヘルパーデータメモリ285で記憶されたヘルパーデータとバッファのコンテンツを組み合わせるためのコンバイナ280を備え得る。組み合わせる関数は通常のビット単位の排他的論理和をとる動作であると想定する。しかし、任意の可逆なバイナリ動作が、例えば、異なるワード値の数を法として、例えば、バイトに対して256を法として使用され得る。ヘルパーデータはエラー訂正コードのコードワードとともにメモリコンテンツの事前に取得したコピーの排他的論理和をとることによって取得され得る。コードワードは秘密で、エラー訂正コードからランダムに選択されるか、または一部のキー管理スキームにしたがって選択される。動作中、コンバイナ280は秘密のコードワードに近傍にある訂正可能なビットストリングを取得するためにバッファ270で取得されるメモリコンテンツとともにヘルパーデータの排他的論理和をとる。エラー訂正器290は、再度秘密のコードワードを取得するためにエラー訂正コードに対応するエラー訂正コードアルゴリズムを適用する。必要に応じて、キー導出関数ユニットは、キー導出関数（KDF）、例えば、暗号化ハッシュ関数などを適用する。暗号化関数は、任意の暗号化の目的、例えば、認証、暗号化などに使用され得る。

30

#### 【0072】

興味深いことに、エラー訂正では、エラー訂正のためのツーパスシステムも同様に使用し得る。メモリはより小さなワードに分割され得、それは個別に、例えば、アダマールコードからコードワードへ訂正される。訂正されたより小さなコードワードは、より大きなブロックサイズエラー訂正コード、たとえばBCHコードで訂正されるより大きなワードへ組み合わされる。より大きなワードへの組み合わせはより小さなコードワードをインターリープすることが好適である。キー導出関数は、訂正されたより小さなコードワードをメモリに暗号化された形で書き戻し得る。キー導出関数は、例えば、インターリープを行うために、暗号化ユニットを使用して、メモリへのランダムアクセスを行い得る。このようにして、メモリ110はより複雑化したエラー訂正スキームのためのワーキングメモリとして使用され得、同時に引き続き、サイドチャネルのリークを低減化することができ、メモリ110が暗号化されると、暗号化および復号ユニットを通じて、ランダムアクセス

40

50

の読み取り / 書き込みアクセスをサポートする。

【 0 0 7 3 】

キー導出ユニットは対応策を使用して、必要に応じて、サイドチャネルのリークを低減化し得る。例えば、W O 2 0 1 0 / 1 0 0 0 1 5 で記述されたデバイスおよび方法が使用され得る。

【 0 0 7 4 】

メモリ読み出しユニットは、スクランブルされた順序でメモリインタフェースを介してメモリコンテンツを取り出すためのアドレススクランブラー 1 4 0 、および暗号化ユニット 2 4 0 を備えている。暗号化ユニット 2 4 0 はスクランブラー 1 4 0 によって取り出されたデータを受信し、それを暗号化する。暗号化されたデータ、すなわち、暗号化されたメモリコンテンツがメモリに書き込まれる。任意のメモリが使用され得るが、暗号化されたメモリコンテンツはメモリ 1 1 0 に書き戻されることが好適である。必要とされるメモリ量を低減化するために、メモリコンテンツは同じスクランブルされた順序で書き戻され得る。それによって、メモリコンテンツが暗号されたメモリコンテンツで上書きされ、各暗号されたメモリワードは、読み出された同じスクランブルされたアドレスに書き戻される。暗号化ユニット 2 4 0 とスクランブルユニット 1 4 0 は共に、メモリを所定の場所、しかし、スクランブルされた順序で暗号化する効果があり得る。

10

【 0 0 7 5 】

暗号化ユニット 2 4 0 はロック暗号であり得る。例えば、暗号化ユニット 2 4 0 は、電子コードブックモード ( E C B ) で動作し得る。例えば、暗号化ユニット 2 4 0 は、カウンタモード ( C T R ) 、例えば、アドレスを E C B モードで暗号化して、メモリコンテンツへの結果の排他的論理和をとり動作し得る。ロックサイズはよく非常に小さい、つまり、8、16、または 3 2 ビットなので、後者が好適である。その理由は、偶然に等しい値を有するメモリコンテンツのワード間の関係を曖昧にするからである。

20

【 0 0 7 6 】

暗号化ユニットではキーを必要とする。アドレススクランブラーでは、シード、またはアドレス暗号化が使用される場合にはキーが必要とされる。キーは固定され得るが、メモリ読み出しユニット 2 2 0 の起動時に作成されることがより好適である。キー / シードは、ランダムに、真または疑似ランダムのいずれかで作成され得る。例えば、メモリ読み出しユニット 2 2 0 は、真のランダム数発生器 ( 図示せず ) を含み得る。

30

【 0 0 7 7 】

しかし、ランダム性は通常、メモリ読み出しユニット 2 2 0 の電源投入の間にのみ必要とされることが観察されている。このことによって、図 2 で示されている別の解決策が可能になる。メモリ読み出しユニット 2 2 0 はさらなるメモリ 2 6 0 を備えている ( P U F 制御ロック 2 1 0 内でメモリ 1 1 0 とは異なるものであることが好適である ) 。また、さらなるメモリ 2 6 0 も揮発性である。さらなるメモリの各電源投入時に、第 2 のメモリはノイズのあるメモリコンテンツに確定する。さらなるメモリのコンテンツはさらに物理的特性によっても異なるが、この目的のために、メモリコンテンツのノイズが利用されることに留意されたい。ランダムキーおよびシード導出ユニット 2 6 5 は、例えば、ハッシュ関数をメモリ 2 6 0 のコンテンツに適用することによって、メモリ 2 6 5 のメモリコンテンツからキーおよび / またはシードを導出する。例えば、後でメモリ 1 1 0 のコンテンツを再読み込みするために、新しいキー / シードが必要な場合には、新しく電源投入しなくても、新しいキーおよび新しいシードは、一方向性関数を古いシードに適用することによって取得され得る。

40

【 0 0 7 8 】

メモリ読み出しユニット 2 2 0 はさらに、復号ユニット 2 5 0 およびアドレス生成器 2 5 5 を備えている。アドレス生成器 2 5 5 は、復号ユニット 2 5 0 と組み合わせられ得る。アドレス生成器 2 5 5 は、事前に定義された順序でメモリアドレスのシーケンスを作成するように構成されている。したがって、復号ユニット 2 5 0 は受信した暗号化されたメモリコンテンツを復号する。

50

## 【0079】

こうして、安全な読み出しが2つのパスで得られる。第1のパスでは、メモリが暗号化状態にある。このパスは、より少なくサイドチャネルのリークにさらされる。その理由は、メモリへのアクセスがスクランブルされた順序だからである。第2のパスでは、メモリは、事前に定義された順序など、望ましい任意の順序で読み出される。第2のパスがより安全なのは、メモリインタフェースを介して渡されるすべてのデータが暗号化されているからである。システム100を上回るシステム200の利点は、任意のスクランブル関数がコードワード境界を考慮しなくても使用され得ることで、同時に、キー導出がより小さくサイズのコードワードでも引き続き機能し得ることである。

## 【0080】

システム100および200は、例えば、半導体デバイスなどの電子デバイスとして実装され得る。システム100および200は専用ハードウェアに実装され得る。システム100および200の一部はソフトウェアとして実装され得る。後者の場合、通常、システム、たとえば、PUF制御ブロックは、デバイスで格納される適切なソフトウェアを実行するマイクロプロセッサ(図示せず)を備え、例えば、ソフトウェアはダウンロードされ、対応するメモリ、例えば、RAM(図示せず)またはフラッシュなどの不揮発性メモリに記憶され得る。

## 【0081】

図4は、暗号化キーを生成するための方法を流れ図で例示している。図4の方法は、バリエーションが可能であるが、システム200を使用して行われ得る。図4のステップ440、450、460、および470は方法のためのオプションで、例えば、システム100を使用して、省略され得る。

## 【0082】

システム200の動作は、次のとおり行われ得る。最初に、システムに電源を投入する。(ステップ410)電源投入の間、メモリ110は電源投入され、メモリコンテンツで確定され得る(ステップ420)。メモリ110のメモリコンテンツは、ノイズがあり得るが、この特定のメモリの見本である。このメモリコンテンツの読み出しが、次の2つのパスで行われる。第1のパスで、メモリコンテンツは、たとえばステップ430のスクランブラーによって、スクランブルされた順序で取り出され(ステップ430)、たとえば暗号化ユニット240による暗号化のために受信される。メモリコンテンツは暗号化され(ステップ440)、書き戻される(ステップ450)。第2のパスで、暗号化されたメモリコンテンツは、事前に定義された順序、たとえば線形シーケンス順序で、たとえばアドレス生成器255によって取り出され、復号ユニット250によって受信される(ステップ460)。暗号化されたメモリコンテンツは、メモリ110が事前に定義された順序で確定したメモリコンテンツを取り出すために復号される(ステップ470)。

## 【0083】

この点で、メモリコンテンツは、サイドチャネルのリークがない、または最低限で、メモリインタフェース120を介してメモリ110から安全に渡される。PUFの処理は、1つ以上の訂正可能なビットストリングを取得するためにメモリコンテンツとヘルパーデータを組み合わせることによって、進み得る。訂正可能なビットストリングは、エラー訂正コードの訂正可能な近傍にある。1つ以上の訂正可能なビットストリングは、エラー訂正アルゴリズムを使用してエラー訂正コードのコードワードを確立するためにエラー訂正され得る。キーは、KDFを適用することによって、確立されたコードワードから導出され得る。

## 【0084】

ステップ460および470で、メモリコンテンツは事前に定義された順序で取得される。このことは、メモリコンテンツが、特定の順序を必要とするヘルパーデータなどの、データと組み合わされる場合に望ましいものである。しかし、ステップ430、440、450、460、および470は、単なるPUFデータではなく、書き込み可能メモリから安全にすべてのデータを読み取るため、例えば、ステップ410、420、およびノマ

10

20

30

40

50

たは 480 なしで、共に使用され得る。この場合、メモリコンテンツがステップ 460 および 470 において事前に定義された順序で受信される必要は必ずしもなく、代わりに、任意の望ましいさらなる順序も可能である。例えば、さらなる順序でメモリを安全に読み出すための方法は、請求項 11 のように暗号化キーの生成のために、スクランブルされた順序でメモリインターフェースからメモリコンテンツを受信し (430)、受信したメモリコンテンツを暗号化し (440)、暗号化されたメモリコンテンツをメモリに書き戻す (450) ことによってメモリを暗号化すること、およびさらなる順序で暗号化されたメモリコンテンツをメモリインターフェースから受信し (460)、さらなる順序でメモリコンテンツを取得するために受信した暗号化されたメモリコンテンツを復号する (470) ことによってメモリを復号することを含んでいる。

10

#### 【0085】

方法 400 を実行するには多くの異なる方法が可能で、それは当業者には明らかになるであろう。例えば、ステップの順序は変更可能であり、一部のステップは並行して実行され得る。さらに、ステップの間に、他の方法ステップが挿入され得る。挿入されたステップは、本明細書で記述されているような方法の改善点を表すか、または本方法には関係しないものであり得る。例えば、ステップ 470 および 480 は、少なくとも部分的に平行して実行され得る。その上、所与のステップは、次のステップが開始される前に完全に完了しなくとも構わない。

#### 【0086】

本発明による方法はソフトウェアを使用して実行され得、これにはプロセッサシステムが方法 400 を実行できるようにするための命令が含まれる。ソフトウェアには、システムの特定のサブエンティティによって行われる当該ステップのみが含み得る。ソフトウェアは、ハードディスク、フロッピー（登録商標）、メモリなどの適切な記憶媒体に記憶され得る。ソフトウェアは、有線、または無線によって、あるいは、例えば、インターネットなどのデータネットワークを使用して送信され得る。ソフトウェアはダウンロードおよび / またはサーバ上でのリモート使用で使用可能にされ得る。

20

#### 【0087】

本発明はさらに、コンピュータプログラム、特に、本発明を実施するために適合されたキャリア上または中の特定のコンピュータプログラムに拡張していることを認識していただきたい。プログラムは、ソースコード、オブジェクトコード、ソースとオブジェクトの中間的コード、たとえば部分的にコンパイルされた形、または本発明による方法の実施での使用のために適切な他の任意の形であり得る。コンピュータプログラム製品に関連した一実施形態では、述べられた方法の少なくとも 1 つの処理ステップのそれぞれに対応するコンピュータ実行可能命令を備えている。これらの命令は、静的または動的にリンクされ得るサブルーチンに細分化および / または 1 つ以上のファイルに格納され得る。コンピュータプログラム製品に関連した別の実施形態では、述べられたシステムおよび / または製品の少なくとも 1 つの手段のそれぞれに対応するコンピュータ実行可能命令を備えている。

30

#### 【0088】

図 5a ~ 図 5d は、メモリのスクランブルおよび暗号化のための様々な可能性を例示している。簡単にするために、メモリの 8 つのメモリ位置が示されており、メモリコンテンツは少なくともこれら 8 つのメモリ位置を超えて拡張する。実際のところ、かなりより大きなメモリが使用され得る。図面では、メモリ位置は 1 から 8 の数字で示されている。メモリ位置は、例えば、8 ビットワード、または 16 ビットワードなどのワードであり得、メモリアクセスへの読み取りアクセスは「R」で示され、書き込みアクセスは「W」で、難読化アクセスは「A」で示されている。難読化アクセスは、同じメモリ位置に対する読み取り、書き込み、または読み取りと書き込みの組み合わせとし得る。時間は左から右へと増大する。

40

#### 【0089】

図 5a では、2 つの段階、暗号化段階 510 および後続の復号段階 520 が示されてい

50

る。暗号化段階の間、メモリ読み出しユニットは次を繰り返す。すなわち、メモリ位置から、すなわち、メモリアドレスから読み出して、メモリアドレスから読み出したコンテンツを暗号化し、そして同じメモリアドレスに書き戻す。メモリアドレスは、アドレススクランblerによってスクランブルされている。暗号化段階 510 の最後に、メモリがスクランブルされた順序で読み出されても、メモリコンテンツ全体が暗号化されている。図 5 a で示されている特定のスクランブルされた順序は例示的なものである。

#### 【0090】

復号段階の間、復号ユニットはさらなる順序で暗号化されたメモリコンテンツを受信した。図 5 a で使用されたさらにある順序は、自然なシーケンス順序である。通常、スクランブルされた順序は、同じデバイスの後続の電源投入が比較されると異なるが、さらなる順序は同じである。キー導出またはエラー訂正などの間に最善の性能を有するには、暗号化段階が終了後に復号段階 520 を開始するのが好適である。このことは、例えば、さらなる順序の第 1 のメモリ位置への暗号化された書き戻しが行われた後に、復号段階が当該位置の読み取りを開始し得、さらなる順序の次のメモリ位置で行われた後に、復号段階が 1 つのさらなる復号に続き得る場合には、必ずしも厳密に必要とされる訳ではない。この複雑さの増大は、難読化が追加の複雑さを犠牲にしても最大化する必要がある時にのみ、その価値があることになる。図 5 b ~ 図 5 d で、このことは行われないと想定すると、復号段階はそのため、図 5 a と同じであり、別個には示されていない。

#### 【0091】

暗号化段階がスクランブルされたメモリアドレスのシーケンスに対する読み取りおよび暗号化された書き戻しの繰り返されたサイクルを含む図 5 a の実施形態は、複数の異なるやり方に変化し得る。そのようなバリエーションは、新型の攻撃を防止するのに役立つ。

#### 【0092】

暗号化段階の間の読み取りおよび書き込みアクセスは厳密に交互である必要はない。例えば、暗号化段階は、複数のメモリコンテンツを読み取り、それらを暗号化して複数の暗号化されたメモリコンテンツを書き戻しうる。書き戻しが行われる順序は、同じか、または読み取られた順序と同じ場合も、または同じではない場合もある。暗号化された順序は、線形または再スクランブルされたものであり得る。図 5 b は暗号化段階 511 を示している。ここで、読み取りおよび書き込み動作は、この場合、それぞれ 4 つの読み取りおよび 4 つの書き込みという複数のバッチで行われる。バッチでは線形の書き戻しを使用し、第 2 のバッチはスクランブルされた書き戻しを使用する。バッチは、アドレスごとに、読み取り値とその暗号化を相關させることを難しくすることによって、5 a の場合に対して改善される。

#### 【0093】

最近、光子放出攻撃は、アクセス中に S R A M 構造のバックサイドから光子活動を記録することによって直接そのターゲット S R A M で威力が実証されている。光子放出攻撃は電子デバイスが、動作時に特定の確率で光子を放出する傾向にあるということに基づいている。光子の生成レートは、供給電圧およびトランジスタスイッチング周波数に比例する。特に、S R A M 値の読み取りも光子の放出の原因となる。I C のバックサイドを C C D でねらう時、読み取り動作を記録することによってメモリコンテンツでの情報を収集することは可能である。光子放出解析は他の暗号解読方法および / またはサイドチャネルを支援し得る。

#### 【0094】

潜在的に、光子攻撃は、例えば、各 P U F S R A M アドレスのまさに最初に読み取りを記録するために S R A M P U F を攻撃するために使用され得るはずである。S R A M の電源投入のメモリコンテンツの読み出し全部が取得される場合、このことは深刻な安全上の問題になるはずである。例えば、光子放出の記録がすべてのまさに最初の読み取りをキャプチャし、S R A M からはそれ以上何もキャプチャせず、多くの回数、測定を繰り返すようにプログラムされる場合、S R A M 開始値の信頼できるイメージが組み立てられ得るはずである。

10

20

30

40

50

## 【0095】

それ自体での読み取り順序のスクランブルは光子攻撃に対処するために十分ではない、すなわち、ランダム化では、ピクチャは、順序に関係なく、単にすべての最初の読み取りアクションの総計なので、ピクチャを変更しないためである。幸い、図5aおよび、より少ない程度、5bでの読み出しでは、電源投入時にメモリが確定したメモリコンテンツに相関された読み出しには、それほど相関がない書き戻しが散在している。これによって、光子情報の使用はかなり困難になる。このセットアップを攻撃するために、攻撃者は（最初の）読み取りアクセスを選び出すためにシャッターメカニズムを使用し得る。シャッターは読み取り中は開いた位置および書き込み中は閉じた位置で構成される。このようにして、暗号化されない読み取りの間の光子放出のみが記録される。一実施形態では、メモリ読み出しユニットは少なくとも部分的にランダムでバッチサイズを選択するように構成され、暗号化ユニットにより暗号化されたバッチサイズ数の書き戻し動作が続く、アドレススクランブラーによるバッチサイズ数の読み取り動作を行うように構成されている。例えば、バッチサイズは起動時に選択され得るが、例えば、バッチサイズは各バッチサイズが読み取られた後などに繰り返し選択され得る。少なくとも部分的なランダムがPUFの一部に応じたバッチサイズを作成することで達成され得る。例えば、バッチサイズは、1、2、3、4バイトからランダムに選択され得る。

## 【0096】

しかし、電源投入コンテンツに相関された信号をさらに低減化することが望ましい。

## 【0097】

このことは、追加のランダム化されたアクセス、例えば、各メモリ位置への書き込みおよび/または読み取りを導入することで達成され得る。書き込みは最初の値を上書きするので、すべての後続の読み取りは混乱させるような情報を放出することになる。この対応策をより効果的なものにするために、アドレスごとに追加の書き込みおよび読み取りが他のアドレスと類似した書き込みおよび読み取りに対してランダムに順序付けされる必要がある。

## 【0098】

ランダム化された順序でのSRAMに対する追加の読み取りおよび書き込みを行うことで、最初のPUFデータの読み取りと分離することが難しいより多くの光子活動が生成される。追加の書き込みに使用されるデータはランダムデータ、固定されたパターン、またさらにデバイス固有のパターンであり得、ここで、PUFの一部はデバイス固有のパターンを導出するために使用される。さらに、これら3つの組み合わせも使用され得る。この順序のランダム化は、それ自体がPUF起動時に基づくランダムシードに基づき得る。ランダム化によって、すべてのメモリ位置で最初の時の読み取りアクセスを選び出すことが困難になる。

## 【0099】

スクランブルされた読み出しおよび暗号化された書き込み準備ステップは、この攻撃を大いに阻害するために強化され得る。このことは、読み取り順序をスクランブルすることに加えて、読み出しおよび暗号化された書き戻し段階を併合することにより達成される。

## 【0100】

暗号化されたデータの追加の読み取り、例えば、各アドレスからの数回の読み取り、最初の時の読み取りと後続の、例えば、PUFで得られたランダムシードに基づく、ランダム化での暗号化されたデータ読み取りを混合するなどを追加することによって、このスケジュールはそれぞれの電源投入で異なるので、攻撃者が読み取りおよび書き込みの正確なスケジュールを予測することは不可能である。その結果、SRAM起動値の信頼できるピクチャを作成することは非常に困難である。

## 【0101】

例えば、図5cの暗号化段階512は図510と同じスクランブルされた順序を示しているが、追加の難読化アクセスが追加されている。難読化アクセスは、例えば、読み出しうニット210に含まれる、難読化ユニットによって行われる。例えば、難読化ユニット

10

20

30

40

50

は、ユニット210の残りの各読み取りおよび／または書き込みアクセスの後に難読化アクセスを挿入する機会を有し得る。図5cでは、難読化アクセスは、書き戻しが既に発生したメモリ位置にのみ行われる。

#### 【0102】

異なるタイプのアクセスも利点となる。アクセスは、追加の読み取りにし得るはずである。これは、書き込みに必要な値についての不明点を回避するので、実施がより簡単である。アクセスは、読み取り／書き込みサイクルにし得るはずである。書き込みアクセスは、光子放出の原因になる可能性がより高いので、したがって、追加の難読化をもたらす。アクセスは、読み取り／書き込み／書き込みサイクルであり得るはずで、最初の書き込みでは、ランダム値または固定された値、たとえば、すべて1、または読み取り値の反転が書き込まれ、次いで、第2の書き込みでは、読み取られた値が書き戻される。これによって、メモリ位置でのスイッチが増大し、光子放出もさらに増大する。したがって、難読化アクセスの実行には、メモリ位置、すなわちアドレス、好適には、暗号化された書き込みが既に行われたものを選択すること、および選択されたメモリアドレスへのアクセスを行うことが含まれ得る。10

#### 【0103】

アクセスはさらに、書き込みアクセスでもあり得る可能性があり、後者の場合、訂正值が書き込まれることに注意する必要がある。実施の効果と容易さとの特定の優れたトレードオフが図5dに示されている。図5dで、暗号化段階は、複数の読み取り／書き戻しサイクルからなっている。書き込みは繰り返され、暗号化された（したがって、相関されない）書き戻しの光子効果が増大する。さらに、このシナリオでは、第1の書き込みはランダム、反転、固定とされ得るはずである。あいにく、図5dでは、シャッターを使用してRi選び出すために脆弱になる規則的なパターンRiWiWiを示しており、一実施形態では、読み取り／書き込みパターンはランダムなインターリーブで強化されている。例えば、書き込み動作の数は部分的にランダムになり得、例えば、上述のとおりバッチサイズ数が選択され得るが、バッチサイズ数は、書き戻しの繰り返しの数を制御するためにのみ使用される。他のランダムインターリーブも使用され得る。20

#### 【0104】

第1のものが暗号化された書き戻しの反転である2つの書き戻しを有することは、第1の読み取りで可能な光子放出の効果を低減化する光子放出を増大させる。30

#### 【0105】

一実施形態では、難読化ユニットは、メモリのメモリ位置への難読化アクセスを行うように構成されており、難読化アクセスは暗号化ユニットが暗号化されたメモリコンテンツをメモリ位置に書き戻した後に行われる。難読化ユニットが、どのメモリ位置がアクセスに安全かを把握し得る種々のやり方がある。さらなる実施形態では、難読化アクセスは、復号ユニットがメモリ位置から暗号化されたメモリコンテンツを受信した前である。

#### 【0106】

別の実施形態では、難読化ユニットはランダムなメモリ位置から読み取りアクセスを行う。暗号化段階の間の固定された地点で、たとえば、スクランブルされた各読み取り後および各書き戻し後に、難読化ユニットは、難読化アクセス、好適には、読み取りアクセスをランダムなメモリ位置に挿入する機会を有している。難読化ユニットは、難読化ユニットが難読化アクセスを挿入する確率を示す確率値を備えている。暗号化段階の開始時点で、確率値はより低い値であるが、少なくとも暗号化段階の間に、確率値は、暗号化段階の終了時点で、確率値が高い値であるように増大する。例えば、確率値は、固定された開始値から固定された終了値に、各機会の後に線形に増大し得る。40

#### 【0107】

メモリのわずかな部分のみが暗号化される暗号化段階の最初では、追加の読み取りは攻撃者への信号を強化してしまうリスクがあるが、この段階では、読み取りの確率は低く、最後では、メモリの大部分が暗号化され、暗号化された値の読み取りの確率は高い。このスキームの利点は、どのメモリ位置が読み取りに安全か、すなわち、暗号化された値を有50

しているかを把握するための記憶処理が不要であることである。一実施形態では、確率値は、暗号化段階の最初から最後まで線形に 0 . 1 から 0 . 9 に増大する。さらなる順序でメモリを安全に読み出すための電子メモリ読み出しユニットの一実施形態では、本明細書で記述された難読化ユニットのいずれか一つを備えている。

【 0 1 0 8 】

上述の実施形態は本発明を制限するものではなく、当業者が多くの代替の実施形態を設計できることを例示していることに留意すべきである。

【 0 1 0 9 】

請求項で、括弧間に配置されたすべての参照記号は、請求項を制限するものとして解釈されるべきではない。動詞「comprise（含む、備える）」およびその活用の使用は、請求項で述べられたもの以外の要素またはステップの存在を除外するものではない。要素の前の冠詞「a」または「a n」は、そのような要素の複数の存在を除外するものではない。本発明は、いくつかの別個の要素を備えるハードウェアによって、および適切にプログラミングされたコンピュータによって実装され得る。いくつかの手段を列挙するデバイスの請求項では、これらの手段のいくつかはハードウェアのいずれかおよび同じ要素によって具現化され得る。特定の方策が相互に異なる従属請求項で列挙されているということは、これらの手段の組み合わせは単に利点のために使用され得ないことを示してはいない。

10

【図 1 a】

Figure 1a

【図 1 b】

Figure 1b

【図 2】

Figure 2

【図3a】

Figure 3a

【図3b】

Figure 3b

【図4】

Figure 4

【図5a】

Figure 5a

【図5b】

Figure 5b

【図5c】

Figure 5c

【図5d】

Figure 5d

---

フロントページの続き

審査官 中里 裕正

(56)参考文献 特表2012-509039 (JP, A)

米国特許出願公開第2008/0133629 (US, A1)

特開2003-018143 (JP, A)

特表2012-519987 (JP, A)

米国特許出願公開第2009/0113217 (US, A1)

米国特許出願公開第2012/0179952 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H04L 9/10

JSTPlus/JMEDPlus/JST7580 (JDreamIII)

IEEE Xplore