## INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

|                                                                                                                                  |  |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (51) International Patent Classification <sup>6</sup> :<br><b>H02M 3/335, H02H 7/12</b>                                          |  | A1                                                                                                                                                                                               | (11) International Publication Number: <b>WO 98/21814</b><br>(43) International Publication Date: 22 May 1998 (22.05.98)                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| (21) International Application Number: PCT/US97/21010                                                                            |  |                                                                                                                                                                                                  | (81) Designated States: AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, CA, CH, CN, CU, CZ, DE, DK, EE, ES, FI, GB, GE, GH, HU, ID, IL, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MD, MG, MK, MN, MW, MX, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, TJ, TM, TR, TT, UA, UG, UZ, VN, YU, ZW, ARIPO patent (GH, KE, LS, MW, SD, SZ, UG, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, ML, MR, NE, SN, TD, TG). |

| (22) International Filing Date: 12 November 1997 (12.11.97)                                                                      |  |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (30) Priority Data:<br>08/749,749 15 November 1996 (15.11.96) US                                                                 |  |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (71) Applicant: THOMSON CONSUMER ELECTRONICS, INC. [US/US]; 10330 North Meridian Street, Indianapolis, IN 46290-1024 (US).       |  |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (72) Inventor: WILLIAMS, Kevin, Michael; 6101 North Primrose Avenue, Indianapolis, IN 46220 (US).                                |  | Published<br><i>With international search report.</i><br><i>Before the expiration of the time limit for amending the claims and to be republished in the event of the receipt of amendments.</i> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (74) Agents: TRIPOLI, Joseph, S. et al.; GE & RCA Licensing Management Operation, Inc., P.O. Box 5312, Princeton, NJ 08543 (US). |  |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## (54) Title: FAULT CONTROL CIRCUIT FOR SWITCHED POWER SUPPLY

## (57) Abstract

A voltage source (RAW B<sup>+</sup>), a transformer (T1) and a switching controller (U1) are coupled for switched mode generation of a regulated output supply voltage. A switching circuit (R5, R6, R7, Q3, Q4, Z3, U3) responsive to an on/off signal (+23 V-RUN) turns the power supply on and off by establishing a conductive condition in a conductive path. A fault detector (42) establishes a non-conductive condition in a part of the conduction path responsive to an overload condition. A delay circuit (40) establishes a conductive condition in an auxiliary conduction path for a period of time after the power supply is turned on. The auxiliary conduction path becomes non-conductive when the fault detector establishes a conductive condition in the part of the conduction path. The part of the conduction path remains conductive absent an overload condition. A latch arrangement including the delay circuit maintains the non-conductive condition in the auxiliary conduction path until the power supply is turned off.

**FOR THE PURPOSES OF INFORMATION ONLY**

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

|           |                          |           |                                          |           |                                              |           |                          |

|-----------|--------------------------|-----------|------------------------------------------|-----------|----------------------------------------------|-----------|--------------------------|

| <b>AL</b> | Albania                  | <b>ES</b> | Spain                                    | <b>LS</b> | Lesotho                                      | <b>SI</b> | Slovenia                 |

| <b>AM</b> | Armenia                  | <b>FI</b> | Finland                                  | <b>LT</b> | Lithuania                                    | <b>SK</b> | Slovakia                 |

| <b>AT</b> | Austria                  | <b>FR</b> | France                                   | <b>LU</b> | Luxembourg                                   | <b>SN</b> | Senegal                  |

| <b>AU</b> | Australia                | <b>GA</b> | Gabon                                    | <b>LV</b> | Latvia                                       | <b>SZ</b> | Swaziland                |

| <b>AZ</b> | Azerbaijan               | <b>GB</b> | United Kingdom                           | <b>MC</b> | Monaco                                       | <b>TD</b> | Chad                     |

| <b>BA</b> | Bosnia and Herzegovina   | <b>GE</b> | Georgia                                  | <b>MD</b> | Republic of Moldova                          | <b>TG</b> | Togo                     |

| <b>BB</b> | Barbados                 | <b>GH</b> | Ghana                                    | <b>MG</b> | Madagascar                                   | <b>TJ</b> | Tajikistan               |

| <b>BE</b> | Belgium                  | <b>GN</b> | Guinea                                   | <b>MK</b> | The former Yugoslav<br>Republic of Macedonia | <b>TM</b> | Turkmenistan             |

| <b>BF</b> | Burkina Faso             | <b>GR</b> | Greece                                   | <b>ML</b> | Mali                                         | <b>TR</b> | Turkey                   |

| <b>BG</b> | Bulgaria                 | <b>HU</b> | Hungary                                  | <b>MN</b> | Mongolia                                     | <b>TT</b> | Trinidad and Tobago      |

| <b>BJ</b> | Benin                    | <b>IE</b> | Ireland                                  | <b>MR</b> | Mauritania                                   | <b>UA</b> | Ukraine                  |

| <b>BR</b> | Brazil                   | <b>IL</b> | Israel                                   | <b>MW</b> | Malawi                                       | <b>UG</b> | Uganda                   |

| <b>BY</b> | Belarus                  | <b>IS</b> | Iceland                                  | <b>MX</b> | Mexico                                       | <b>US</b> | United States of America |

| <b>CA</b> | Canada                   | <b>IT</b> | Italy                                    | <b>NE</b> | Niger                                        | <b>UZ</b> | Uzbekistan               |

| <b>CF</b> | Central African Republic | <b>JP</b> | Japan                                    | <b>NL</b> | Netherlands                                  | <b>VN</b> | Viet Nam                 |

| <b>CG</b> | Congo                    | <b>KE</b> | Kenya                                    | <b>NO</b> | Norway                                       | <b>YU</b> | Yugoslavia               |

| <b>CH</b> | Switzerland              | <b>KG</b> | Kyrgyzstan                               | <b>NZ</b> | New Zealand                                  | <b>ZW</b> | Zimbabwe                 |

| <b>CI</b> | Côte d'Ivoire            | <b>KP</b> | Democratic People's<br>Republic of Korea | <b>PL</b> | Poland                                       |           |                          |

| <b>CM</b> | Cameroon                 | <b>KR</b> | Republic of Korea                        | <b>PT</b> | Portugal                                     |           |                          |

| <b>CN</b> | China                    | <b>KZ</b> | Kazakhstan                               | <b>RO</b> | Romania                                      |           |                          |

| <b>CU</b> | Cuba                     | <b>LC</b> | Saint Lucia                              | <b>RU</b> | Russian Federation                           |           |                          |

| <b>CZ</b> | Czech Republic           | <b>LI</b> | Liechtenstein                            | <b>SD</b> | Sudan                                        |           |                          |

| <b>DE</b> | Germany                  | <b>LK</b> | Sri Lanka                                | <b>SE</b> | Sweden                                       |           |                          |

| <b>DK</b> | Denmark                  | <b>LR</b> | Liberia                                  | <b>SG</b> | Singapore                                    |           |                          |

## FAULT CONTROL CIRCUIT FOR SWITCHED POWER SUPPLY

Background

The invention relates to the field of switched mode power supplies for apparatus having a run mode and a standby mode of operation, such as a television receiver. In particular, the invention relates to the field of controlling switched power supplies in such apparatus during current overload conditions by utilizing a control circuit otherwise present for switching the power supply, for example an auxiliary power supply, on and off when changing between the run and standby modes of operation.

In a typical run/standby power supply, for example as used in television receivers, a bridge rectifier and a filter capacitor provide a raw DC voltage (called the  $B^+$  voltage, or raw  $B^+$ ), whenever the power supply is coupled to the domestic mains. Standby mode loads can be powered directly from the  $B^+$  voltage or from another voltage that is always present. Many run mode loads, however, are powered through a voltage regulating supply such as a switched mode supply, that operates only in the run mode. The run mode power supply for certain loads, such as the deflection circuits and high voltage screen loads, typically employ the flyback transformer that powers beam deflection. A separate or auxiliary power supply also can be operated as a switched mode supply and may provide a regulated  $B^+$  voltage for the flyback transformer as well as other auxiliary supply voltages.

Projection televisions, for example, have particularly demanding power needs because they have three high power cathode ray tubes (CRTs). An auxiliary power supply is useful to power the convergence amplifiers for the tubes, two such amplifiers generally being required for each CRT. These amplifiers require positive and negative polarity voltages and can dissipate substantial power.

In a switched mode supply, an input DC voltage (such as the  $B^+$  voltage in a television) is coupled to one terminal of a primary winding of a transformer and the other terminal of the primary winding is coupled to a switching device, such that current is coupled to the transformer when the switching device conducts. The switching device is alternately turned on and off during the run mode of operation, providing alternating currents in secondary windings of the transformer, which are rectified and filtered to provide run mode supply voltages.

Regulation of the output voltages is achieved by feedback control provided by, for example, a feedback winding of the transformer. The respective secondary windings are closely coupled, so that load variations on any of the secondary windings

are reflected on the feedback winding. The feedback control compares a voltage on the feedback winding with a standard or threshold voltage level, which may be provided by the switching device, and modulates the frequency and/or pulse width at which the switching circuit is turned on and off. The switching device is compensated to render 5 it insensitive to variation of the raw B<sup>+</sup> input voltage, while maintaining accurate output voltage levels as current loading varies over a nominal range of power consumption.

The switching device for a power supply as described can be an integrated circuit (IC) power supply controller from the Sanyo STK730 series. This controller 10 includes a FET power switching transistor, an error amplifier and driver, and an over-current protection circuit in a single package. When coupled into a switched mode supply and first turned on, current from the B<sup>+</sup> voltage flows to ground through the primary winding of the transformer, the FET and a current sensing resistor. Current increases until the over-current protection circuit in the controller IC is triggered, 15 whereupon the IC controller turns off its FET power transistor. Energy is transferred to the secondary windings of the transformer, where the induced AC current is rectified and charges filter capacitors. After a starting interval of several cycles, the output voltage reaches its regulated level. A threshold comparison circuit provided by the IC controller is coupled to a feedback winding of the transformer and controls the 20 timing of switching by the control IC to maintain the regulated output voltage level. Oscillation stabilizes at a frequency and duty cycle that accommodate the loads coupled to the secondary windings. Many other power supply controllers operate in a similar fashion and may be used instead of the Sanyo STK730 series.

Such an IC controller will attempt to start whenever the raw B<sup>+</sup> voltage is 25 present. Other switched circuits control switching between the standby mode and the run mode. If during the run mode of operation loading increases on the power supply outputs, the power supply will attempt to provide more current for keeping the feedback winding voltage equal to the control threshold. If a fault condition occurs, such as a current overload, the overcurrent fault protection circuit of the IC controller, 30 which normally limits current during start-up, becomes operative to limit the power coupled through the supply. The current limiting circuit shuts off the switching transistor before the feedback control senses that the feedback winding voltage is at the control threshold. As a result, the output voltages fall below nominal, to increasingly lower levels with increased current loading.

35 Assuming a complete short circuit fault condition on the output, the IC controller overload circuit promptly shuts off conduction and little power is actually

coupled through the supply. However, if there is a current overload but not a complete short circuit, substantial power is still coupled through the supply even as the output voltages drop. This is an undesirable operating condition, even a potentially dangerous operating condition.

5

### Summary

It would be advantageous to shut the auxiliary power supply down entirely when the output is overloaded, as the auxiliary power supply would be shut down in the standby mode of operation, for example, instead of allowing the controller IC to operate the auxiliary power supply in an overloaded and/or other fault condition.

10

However, some provision must be made to permit operation of the current limiting circuits in the IC controller to enable the power supply to start-up. Otherwise, the low voltage output condition which occurs during power supply start-up can be incorrectly identified by a fault detection circuit to be a low voltage condition resulting from a current overload fault condition. The auxiliary power supply would never start.

15

This problem can be solved in an elegant fashion when an auxiliary power supply is otherwise provided with a switch control for turning the auxiliary power supply on and off as the apparatus changes between the standby and run modes of operation.

20

In accordance with an inventive arrangement, such a switch control, which is advantageously coupled to a feedback control signal path, is modified so as to also be responsive to a fault condition detector, such as a low voltage and/or overcurrent detector, each of which conditions can be indicative of a fault condition, such as a short circuit.

25

In accordance with a further inventive arrangement, a delay circuit is interposed between the fault condition detector and the switch control, which becomes effective after the auxiliary power supply has been turned on. The fault condition detector is thereby prevented from disabling the auxiliary power supply for a period of time after the auxiliary power supply has been turned on, to provide an opportunity for the auxiliary power supply to establish an operating output voltage without a false indication of a fault condition.

30

In accordance with an inventive embodiment, a switched power supply, comprises: a voltage source, a transformer and a switching controller coupled for switched mode generation of an output supply voltage; a feedback circuit for regulating the switched mode operation responsive to loading on the output supply voltage; a switching circuit responsive to an on/off signal for turning the power supply

35

on and off by controlling conduction in a conduction path, the power supply being turned on by a conductive condition in the conductive path; a fault detector for controlling conduction in a part of the conduction path and establishing a non-conductive condition in the part of the conduction path responsive to an overload condition of the output supply voltage; and, a delay circuit for controlling an auxiliary conduction path bypassing the part of the conduction path controlled by the fault detector and establishing a conductive condition in the auxiliary conduction path for a period of time after the power supply is turned on.

In accordance with this embodiment, the auxiliary conduction path becomes non-conductive when the fault detector establishes a conductive condition in the part of the conduction path, the part of the conductive path remaining in the conductive condition until detection of the overload condition.

Further in accordance with this embodiment, the delay circuit also forms part of a latch arrangement which establishes a non-conductive condition in the auxiliary conduction path after the period of time. The latch arrangement maintains the non-conductive condition of the auxiliary conduction path until the power supply is turned off.

In accordance with another inventive embodiment, a switched power supply comprises: a voltage source, a transformer and a switching controller coupled for switched mode generation of an output supply voltage; a feedback circuit for regulating the switched mode operation responsive to loading on the output supply voltage; a switching circuit responsive to an on/off signal for turning the power supply on and off by controlling conduction in a conduction path, the power supply being turned on by a conductive condition in the conductive path; a fault detector for controlling conduction in a part of the conduction path and establishing a non-conductive condition in the part of the conduction path responsive to an overload condition of the output supply voltage; and, a latch arrangement having an auxiliary conduction path in parallel with the conduction path controlled by the fault detector and establishing a conductive condition in the auxiliary conduction path for a period of time after the power supply is turned on, the auxiliary conduction path becoming non-conductive when a conductive condition is established in the part of the conduction path, the latch arrangement maintaining the non-conductive condition of the auxiliary conduction path until the power supply is turned off.

In accordance with this embodiment, the part of the conductive path remains in the conductive condition until detection of the overload condition.

In each of the embodiments, the latch arrangement comprises: a capacitor; a semiconductor switch having a first junction forming the auxiliary signal path and a second junction providing a charging path for the capacitor; and, a diode providing a discharge path for the capacitor. The first and second junctions of the semiconductor switch become non-conductive when the fault detector establishes a conductive condition in the part of the conduction path, the part of the conduction path remaining in the conductive condition until detection of the overload condition.

The capacitor remains charged while the diode is reverse biased. The charged capacitor maintains the reverse bias condition in the second junction of the semiconductor. The diode becomes reverse biased after the power supply is turned off.

#### Brief Description of the Drawings

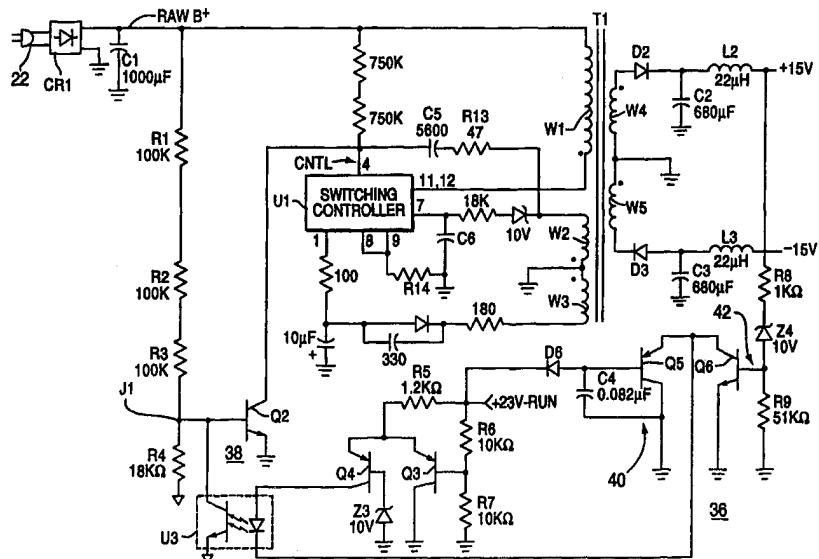

FIGURE 1 is a block diagram of an auxiliary power supply having control circuitry in accordance with inventive arrangements.

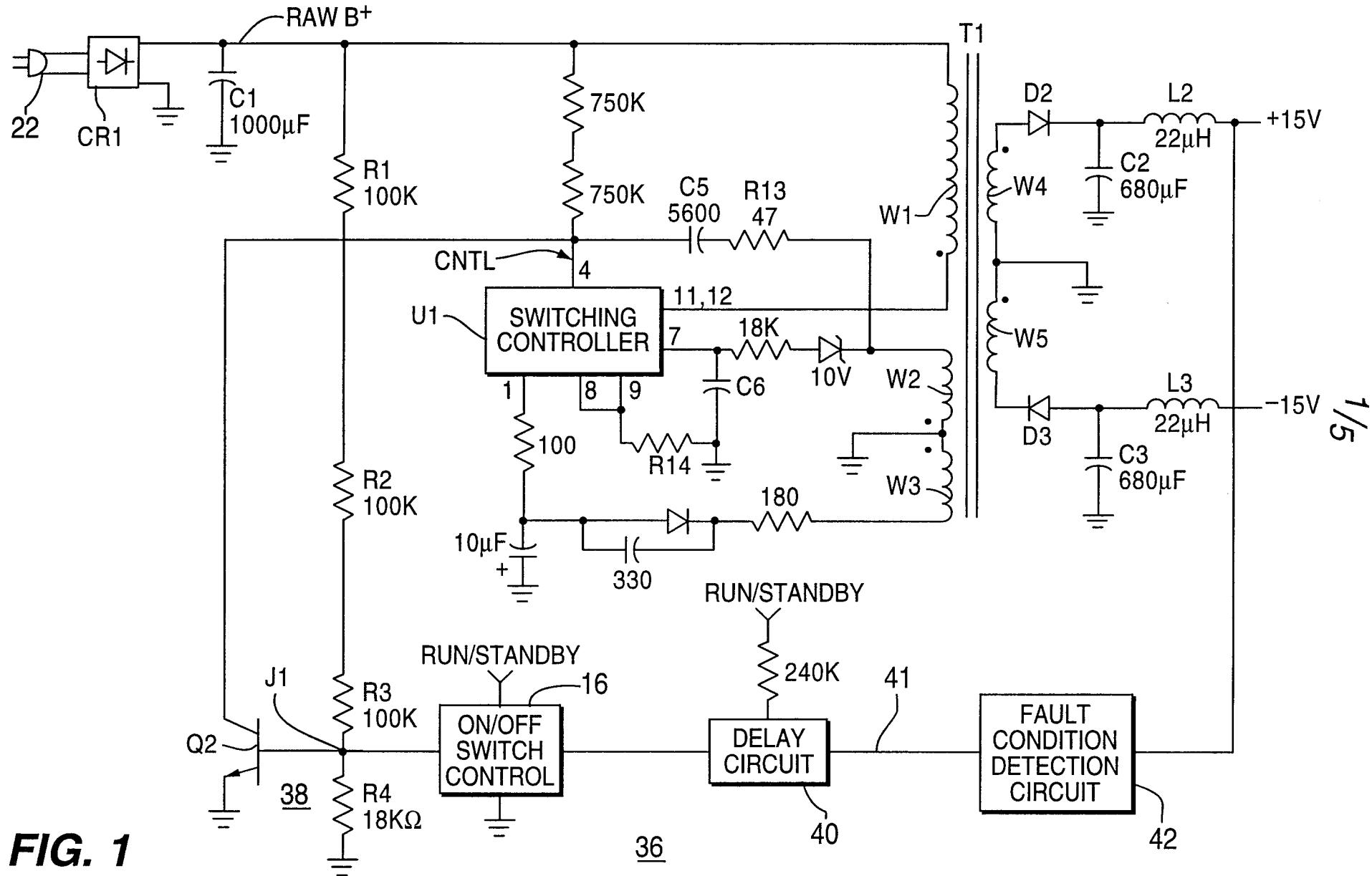

FIGURE 2 is a schematic diagram of the auxiliary power supply having control circuitry in accordance with inventive arrangements and illustrating on/off control in more detail.

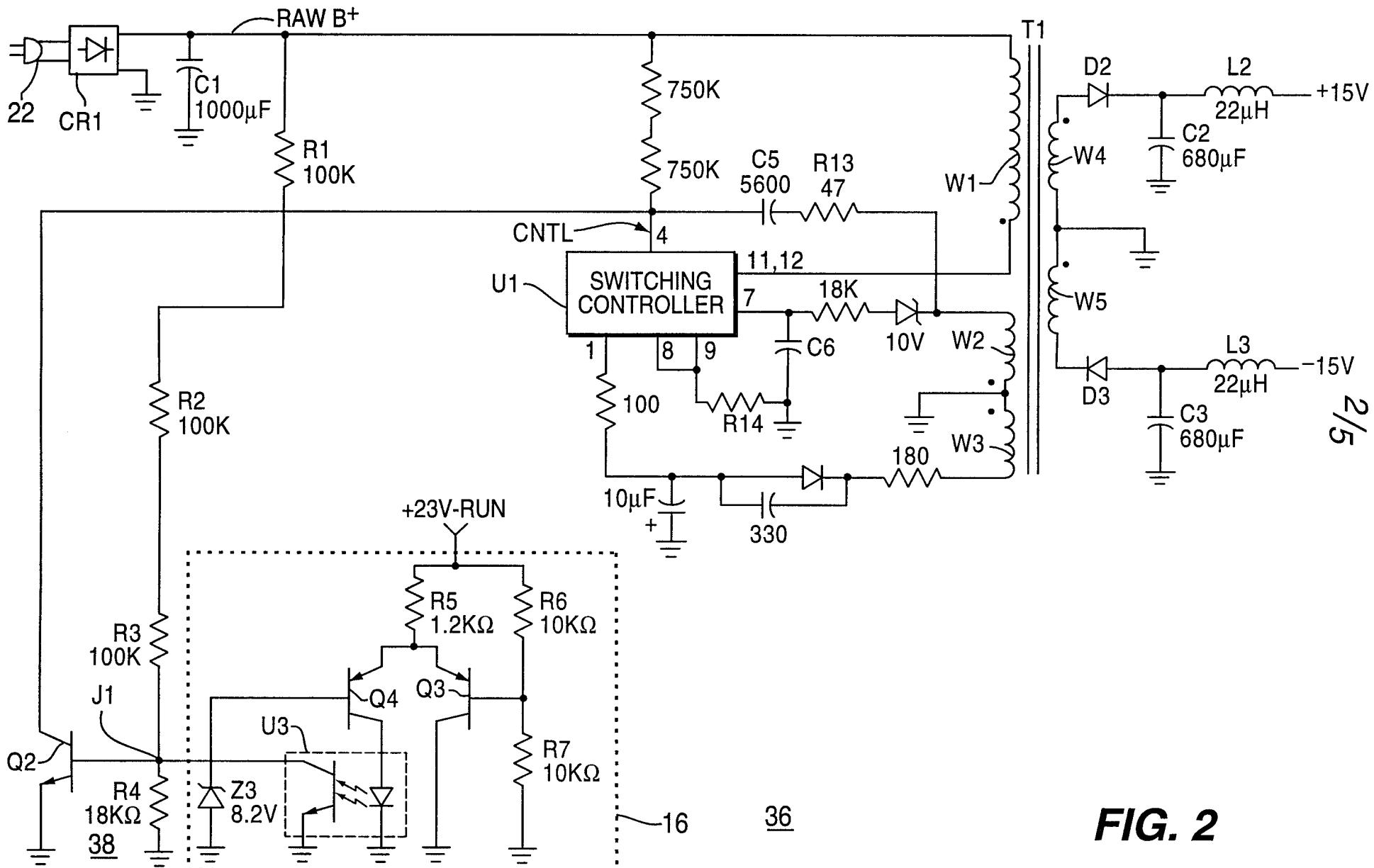

FIGURE 3 is a schematic diagram of an auxiliary power supply having control circuitry in accordance with inventive arrangements and illustrating start up and fault detection circuitry in more detail.

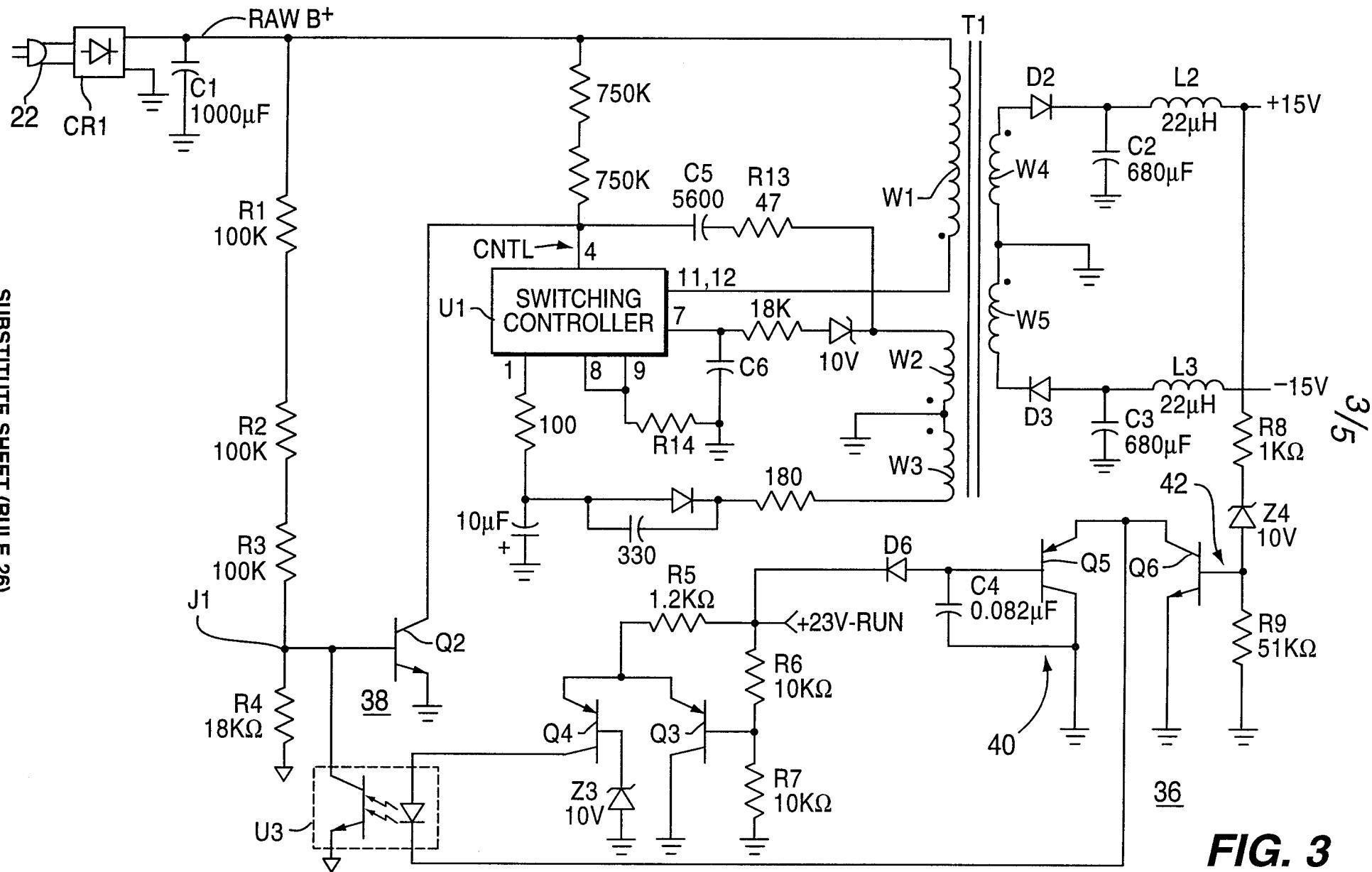

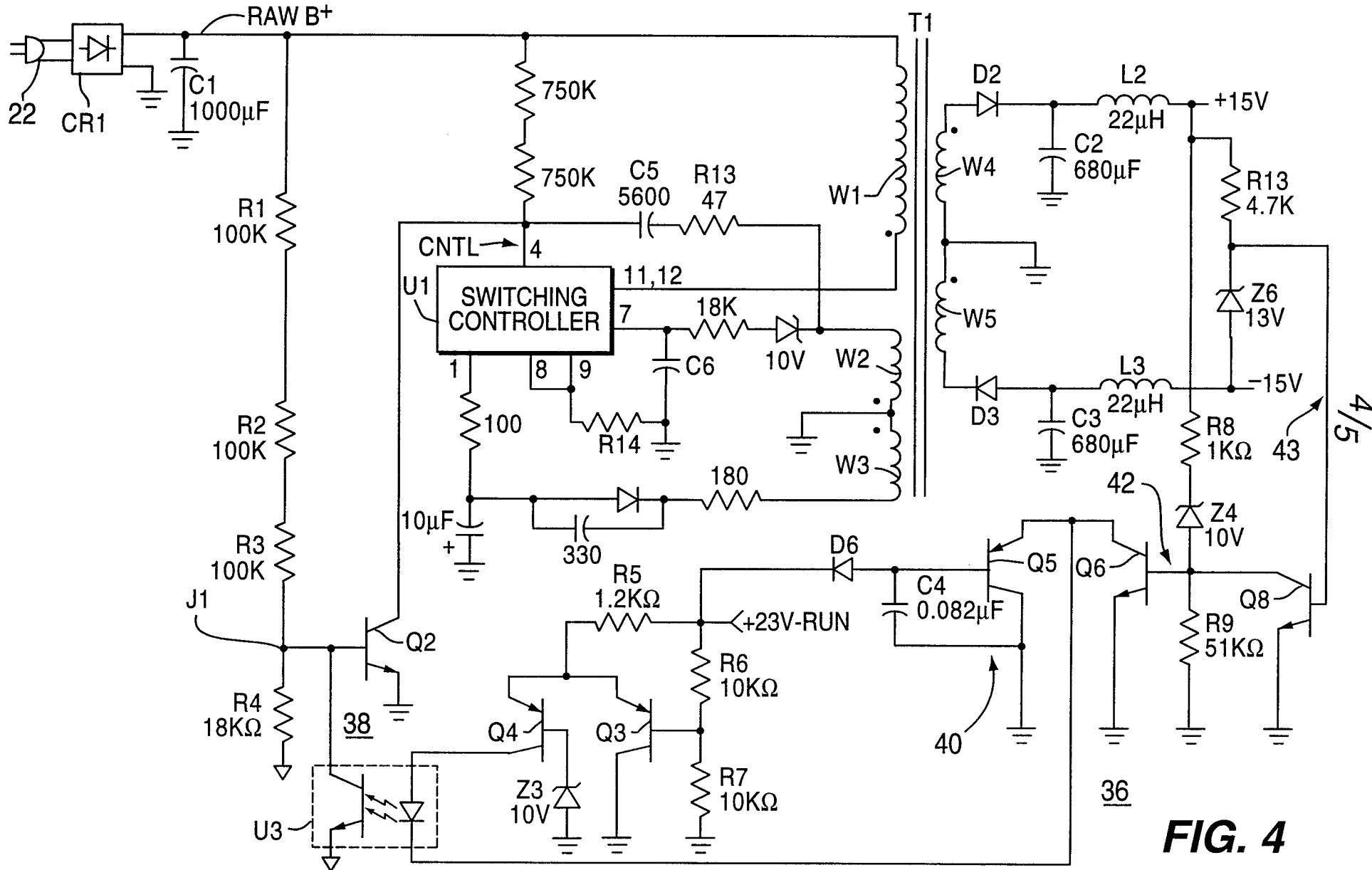

FIGURE 4 is a schematic diagram of an auxiliary power supply having a current overload detection circuit in accordance with inventive arrangements.

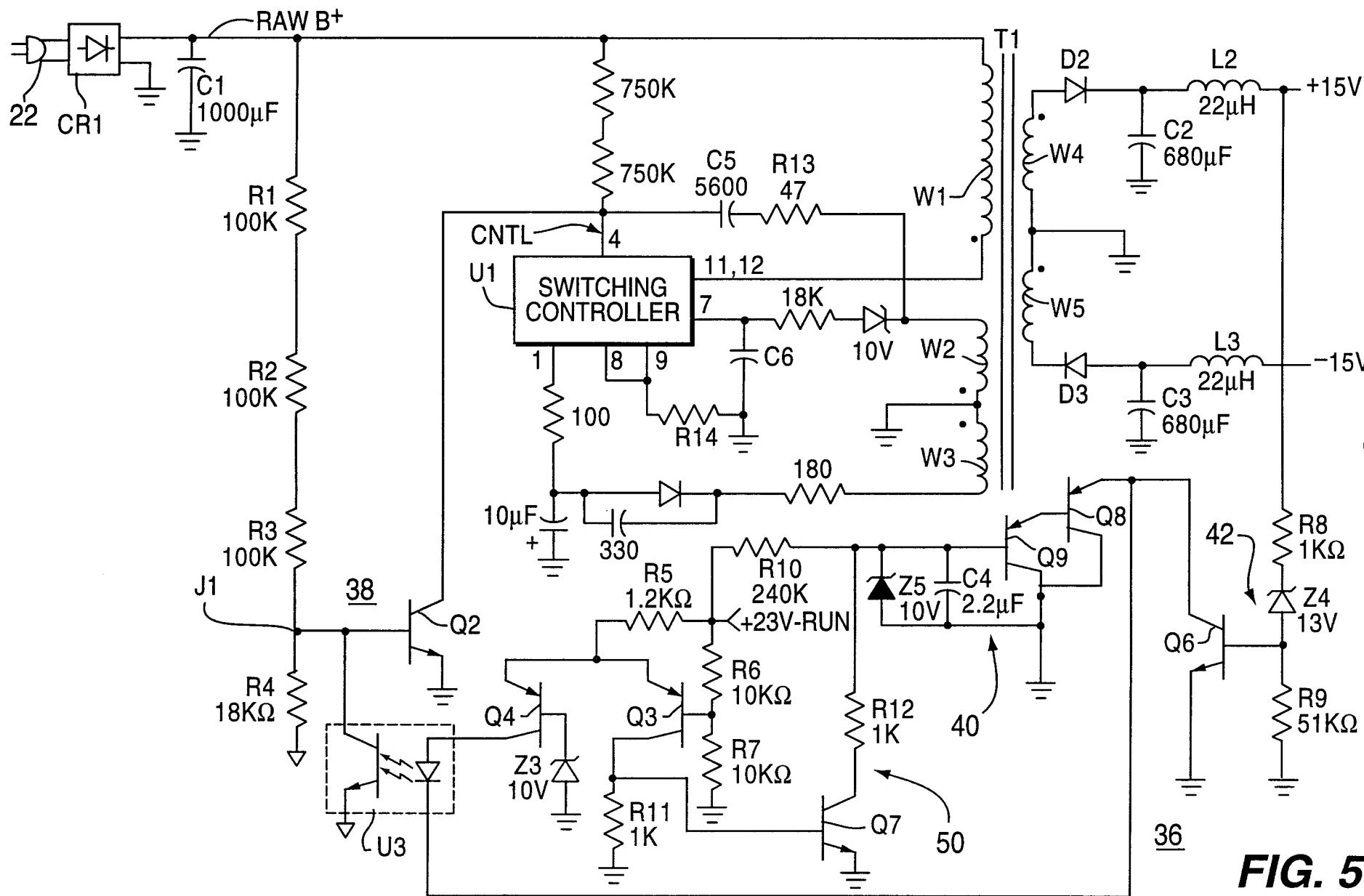

FIGURE 5 is a schematic diagram of an auxiliary power supply having a quick-reset circuit in accordance with inventive arrangements.

#### Description of the Preferred Embodiments

FIGURE 1 generally shows an inventive switched mode power supply 10 having a switching controller U1 operable periodically to apply current from a voltage input, for example a raw B<sup>+</sup> voltage, to a primary winding W1 of a transformer T1 for variably coupling power to one or more secondary windings W2, W3, W4 and W5 of transformer T1. The switching controller U1 can comprise, for example, a Sanyo STK730 series controller. Switching controller U1 conducts when a driving voltage, for example the raw B<sup>+</sup> voltage, is available on its control input CNTL at pin 4.

The raw B<sup>+</sup> input supply voltage is a direct current voltage obtained from the output of a bridge rectifier CR1 filtered by a capacitor C1. The raw B<sup>+</sup> voltage is present whenever the power supply 10 is coupled to the domestic mains 22 (i.e.,

plugged in). However, the power supply 10 only operates in a run mode, and is disabled in a quiescent or standby mode.

When power supply 10 is plugged in and is also in the run mode, the raw B<sup>+</sup> voltage is present at the control input CNTL of switching controller U1, thus enabling switching controller U1 to conduct a current through the primary winding W1 of transformer T1. The current flow through winding W1 induces a voltage across winding W2 of transformer T1, which voltage is applied to the control input CNTL through resistor R13 and capacitor C5. The polarity of winding W2 is such that the voltage induced across winding W2 keeps switching controller U1 conducting.

Switching controller U1 ceases conducting current through primary winding W1, or turns off, when the current conducted by switching controller U1 reaches a current limit threshold that is set by the combination of resistor R14 and capacitor C6. When switching controller U1 ceases conducting, the magnetic field of primary winding W1 collapses, its polarity reverses and the energy contained in primary winding W1 is transferred to windings W4 and W5, which supply power to the +15 V and -15 V, respectively, outputs.

As the energy from windings W4 and W5 becomes exhausted, their magnetic fields collapse and their polarities reverse. In accordance with the polarities of windings W2, W4 and W5, winding W2 provides a positive voltage to pin 4 of switching controller U1, thereby enabling switching controller U1 to once again conduct current through primary winding W1 until the current limit threshold of switching controller U1 has been reached and switching controller U1 ceases conducting current. Energy is then again transferred from primary winding W1 to windings W4 and W5. This process repeats for several cycles, until the operation of power supply 10 has stabilized.

Feedback winding W3 controls the duty cycle of switching controller U1 after the operation of power supply 10 has stabilized. The voltage developed across feedback winding W3 is compared with an internal reference, equal to approximately -40.5 V, developed by switching controller U1. The duty cycle of switching controller U1 is modulated such that the voltage developed across feedback winding W3 is maintained approximately equal to -40.5 V. Feedback winding W3 is coupled to the secondary windings W4 and W5 so that load changes are reflected in the voltage developed across feedback winding W3. Thus, feedback winding W3 is also used to regulate the output voltages developed by windings W4 and W5.

Normally, switching from the standby mode to the run mode or vice versa is accomplished under user control via control inputs (not shown) such as an infrared

receiver, panel switches or the like. According to an inventive aspect, additional run/standby switching circuits 36 are provided to shift the power supply 10 between the operational run mode and the non-operational standby mode. Switching controller U1 requires a large start-up current. For dependable starting and assistance in 5 developing this drive current, the run/standby switching circuits 36 include a first circuit 38 coupled between the raw B<sup>+</sup> voltage input and the control input CNTL, for providing a voltage bias to enable conduction by the switching controller whenever the raw B<sup>+</sup> voltage input is present.

In accordance with an inventive arrangement, the drive current bias provided 10 from first circuit 38 can be shunted away to reduce the available drive current to disable the switching controller U1. The drive current can be shunted to a source of reference potential, for example ground.

The run/standby switching circuits 36 further comprise a fault condition detection circuit 42 coupled to at least one of the transformer secondary windings W4 15 and W5. The circuit 42 senses a fault condition, such as current overloading on the auxiliary power supply, for example by sensing a low voltage threshold on the output coupled to the same or another secondary winding W4 or W5. The circuit 42 generates an output 41 indicative of a fault condition to disable conduction of switching controller U1 by pulling control input CNTL of switching controller U1 to 20 a ground potential, as a means for switching the auxiliary power supply off, as though the apparatus had been changed to the standby mode of operation. In order to make certain that the startup phase of the auxiliary power supply is not prevented by a false detection of a fault condition, due to initial low voltage output levels, a delay circuit 40 inhibits the effect of the output of the fault condition detection circuit 42 for 25 a sufficient period of time for the nominal output voltage levels of the auxiliary power supply to be established.

FIGURES 2-5 illustrate in detail different aspect of the inventive arrangements shown generally in FIGURE 1. The same reference numbers are used throughout the drawings to refer to the same or comparable elements. Referring to FIGURE 2, 30 switching controller U1 is coupled in series with primary winding W1 of transformer T1. Switching controller U1 alternately conducts and turns off, for transferring power to the secondary windings W4 and W5, where the resulting AC signal is rectified by diodes D2 and D3 and filtered by capacitors C2 and C3, respectively. The filtered voltages provided on windings W4 and W5 are further filtered by chokes L2 and L3, 35 respectively, to provide operational supply voltages +15 V and -15 V, respectively, for powering loads in the run mode.

The polarities of secondary windings W4 and W5 are opposite that of the primary winding W1, as shown in FIGURE 2, such that capacitors C2 and C3 are charged when switching controller U1 turns off and the energy stored in the primary winding W1 of transformer T1 is transferred to windings W4 and W5.

5 According to an inventive aspect, the power supply 10 as shown is arranged to further control the voltage at control input CNTL of switching controller U1 for controlling shifts between run and standby modes. When the device is in standby mode and switching controller U1 is not conducting periodically, the only power going into the power supply 10 is the raw B<sup>+</sup> voltage, which is present because the device

10 is coupled to domestic mains 22. It would be possible in controlling run/standby operation to couple and decouple the raw B<sup>+</sup> voltage to the switching elements of the power supply 10 using a relay or other switching device powered from a supplemental low power supply (not shown). However, according to the invention a more cost effective solution is obtained by using a signal derived in part from the raw

15 B<sup>+</sup> voltage and in part from the run mode voltages, to reduce the bias on control input CNTL to switching controller U1, namely to bring the voltage on the control input to near ground to hold switching controller U1 off until normal bias is restored.

Thus, a voltage divider comprising resistors R1, R2, R3 and R4 is coupled between the raw B<sup>+</sup> voltage and ground, and the junction J1 of the voltage divider is

20 coupled to the base of a switching transistor Q2, having its collector coupled to the control input and its emitter grounded. When the raw B<sup>+</sup> voltage is present, control input CNTL is pulled to near ground by conduction of transistor Q2. When the power supply 10 is first coupled to the mains, it is held in standby mode.

The invention is advantageously applied to an auxiliary power supply such as

25 the auxiliary supply of a television for powering run mode loads such as convergence amplifiers. For switching into the run mode, the inventive power supply senses the presence of a run mode supply voltage developed from a source other than the secondary windings of transformer T1. This run mode supply voltage is compared to a threshold level, and when the threshold level is passed, transistor Q2 is turned off,

30 permitting the bias on control input CNTL of switching controller U1 to return to normal and permit operation of the auxiliary power supply in the run mode, namely under feedback control by feedback winding W3 of transformer T1. For example, the +23 V supply that is developed by the run mode operation of the deflection and other circuits in a television can be used for this purpose.

35 Referring to FIGURE 2, a differential pair of PNP transistors Q3 and Q4 have their emitters coupled to the run mode supply voltage by resistor R5, and

differentially compare the level of the run mode supply voltage, via the voltage divider of resistors R6 and R7 on the base of transistor Q3, with a reference voltage of +8.2 V provided by Zener diode Z3 on the base of transistor Q4. When the run mode supply exceeds a level determined by the ratio of resistances in the voltage divider, transistor 5 Q4 conducts and switches on optocoupler U3. The phototransistor of optocoupler U3 grounds the base of transistor Q2, which ceases conducting, thereby permitting normal bias on control input CNTL of switching controller U1. Operation of the power supply 10 then commences in the run mode responsive to the voltages on the secondary windings W2 and W3 of transformer T1.

10 Another inventive embodiment is shown in FIGURE 3, and includes a latching circuit that has the additional function of detecting current overload conditions, when in the run mode, for switching the power supply 10 into the standby mode. Current overloading causes the output voltage level to drop below nominal, because in overcurrent conditions the overcurrent protection circuits of switching controller U1 15 turn switching controller U1 off before sufficient power has been coupled through the power supply 10 to maintain the nominal output voltage level. This method of current limiting is less than optimal for powering loads such as the digital convergence amplifiers of a projection television. For such loads, it is advantageous if the power supply 10 can be turned off when an overcurrent condition occurs, instead of 20 attempting to supply current to the loads at reduced voltage. According to the invention, this function is achieved in a manner that interfaces with the circuits controlling switching between the run and standby modes as in FIGURE 2.

In FIGURE 3, control for switching from standby to run mode is provided in part by the run mode supply voltage, such as the +23 V run supply, passing a 25 predetermined voltage as determined by the differential transistor pair Q3 and Q4, which provide current to the LED of optocoupler U3. The phototransistor of optocoupler U3 then turns off transistor Q2 and permits operation of switching controller U1. Resistors R1, R2, R3 and R4 provide bias to transistor Q2 at junction J1 from the raw B<sup>+</sup> supply voltage. In comparison to the embodiment of FIGURE 2, 30 in which the cathode of the LED in optocoupler U3 is grounded, according to FIGURE 3, the current through the LED charges a capacitor C4, through the base of a PNP transistor Q5.

Capacitor C4 provides for a delay upon first switching from the standby mode into the run mode, in which the power supply 10 can start up. When the supply 10 35 is running and the regulated voltage, in this case nominally +15 V, exceeds approximately +10 V, Zener diode Z4 conducts through resistors R8 and R9, and

10

turns on transistor Q6. The current from optocoupler U3 is then shunted to ground through transistor Q6 and capacitor C4 stops charging. Transistor Q5 is then off and capacitor C4 cannot discharge through either transistor Q5 or through diode D6, which is coupled to the +23 V run mode supply and is reverse biased.

5 In the event that the +15 V output voltage falls below the level needed to cause Zener diode Z4 to conduct, especially in the case of a current overload on secondary winding W4, transistor Q6 turns off due to insufficient base drive. With transistor Q6 off, capacitor C4 can charge from the current through optocoupler U3. When the charge on capacitor C4 reaches approximately +10 V, transistor Q5 turns off, and

10 there is no path for the current through optocoupler U3. In that case, although differential transistors Q3 and Q4 still detect the presence of the +23 V run supply, no current is conducted by the phototransistor of optocoupler U3. The raw B<sup>+</sup> supply turns on transistor Q2 due to the voltage divider formed at junction J1 by resistors R1, R2, R3 and R4. The control input CNTL of switching controller U1 is

15 pulled low. The power supply 10 shuts off, protecting the loads coupled to the outputs. Thus, unlike a power limiting solution wherein the current limiting circuits of the switching controller reduce the output voltage below nominal but continue to supply power, the inventive circuit as described switches off the power supply 10 in overcurrent conditions. This is accomplished using the run/standby circuits driven

20 from the raw B<sup>+</sup> power supply, providing a current overload protective function with a minimum of parts and complexity.

As illustrated in FIGURES 1 and 3, fault condition detection circuit 42 is utilized to detect current overload conditions on the +15 V output of power supply 10. Detection of overload conditions on the -15 V output is complicated by the fact

25 that exclusively positive-polarity biasing voltages, for example raw B<sup>+</sup>, are used in power supply 10.

An additional inventive arrangement, shown in FIGURE 4, advantageously and elegantly provides for detection of current overload conditions on the -15 V output in the absence of negative-polarity bias voltages. Detection of a current overload

30 condition on the -15 V output, when in the run mode, causes the power supply 10 to be switched into the standby mode. In FIGURE 4, the negative supply voltage overload detection circuit 43 is coupled between the +15 V and -15 V outputs of power supply 10. The Zener diode Z6 is biased between the +15 V and -15 V outputs of the power supply 10, such that the base of transistor Q8 has a bias voltage

35 that is equal to approximately -2 V when the -15 V output is nominally loaded. The Zener diode Z6 thus provides a level-shifting mechanism, or a dc offset, that enables

the -15 V output to be compared against a positive reference voltage, which in this embodiment is the turn-on voltage of the base-emitter junction of transistor Q8, for detecting a current overload condition.

If, in response to a current overload condition, the -15 V output begins to drop 5 toward a ground potential, the voltage at the base of transistor Q8 will also tend to move toward ground. Eventually, if the current overload condition persists and the -15 V output consequently reaches a predetermined threshold voltage level, the voltage at the base of transistor Q8 will become positive and will eventually become high enough, for example approximately 0.7 V, to turn on transistor Q8 to signal a 10 current overload condition. Unlike fault condition detection circuit 42, where a current overload condition is signaled by a change in the conductive state of Zener diode Z4, Zener diode Z6 remains in a conductive state when a current overload condition is signaled by transistor Q8. The desired threshold level can be selected by an appropriate choice of the breakdown voltage of Zener diode Z6.

15 When transistor Q8 turns on, current is drawn from the base of transistor Q6, thereby turning transistor Q6 off. Thus, similarly to the detection of an overcurrent condition on the +15 V output, with transistor Q6 off, capacitor C4 can charge from the current through optocoupler U3. When the charge on capacitor C4 reaches approximately +10 V, transistor Q5 turns off, and there is no path for the current 20 through optocoupler U3. In that case, although differential transistors Q3 and Q4 still detect the presence of the +23 V run supply, no current is conducted by the phototransistor of optocoupler U3. The raw B+ supply turns on transistor Q2 due to the voltage divider formed at junction J1 by resistors R1, R2, R3 and R4. The control input CNTL of switching controller U1 is pulled low. The power supply 10 25 shuts off, protecting the loads coupled to the outputs.

When the +23 V run supply voltage drops, capacitor C4 is discharged through diode D6, which otherwise would be reverse biased by the presence of the +23 V run supply. Once capacitor C4 has discharged, the power supply 10 can be restarted unless there is still an overload condition on the output that prevents development of 30 a sufficient output voltage to turn on transistor Q6 during the delay time in which the charge on capacitor C4 can rise to a sufficient voltage to turn off transistor Q5.

If capacitor C4 is not allowed enough time to fully discharge, for example if switched mode power supply 10 is shifted from the run mode to the standby mode and then back to the run mode in rapid succession, transistor Q5 will remain off. The 35 run mode output voltages will thus be prevented from coming up and attaining their nominal output voltage levels.

## 12

5 A further inventive embodiment shown in FIGURE 5 provides a quick-reset circuit 50 for rapidly discharging capacitor C4 when the +23 V run supply voltage drops. According to the invention, this function is achieved in a manner that interfaces with the circuits controlling switching between the run and standby modes as in FIGURE 2.

10 In FIGURE 5, the delay circuit 40 has a Zener diode Z5 in parallel with capacitor C4. When the +23 V run supply voltage comes up, capacitor C4 charges through resistor R10 to provide the delay time for the run mode output voltages to stabilize at approximately their nominal output voltage levels. Zener diode Z5 clamps 15 the voltage across capacitor C4 to approximately +10 V to prevent damage to the base-emitter junctions of transistors Q8 and Q9, which are arranged in a Darlington configuration.

15 Once power supply 10 is in the run mode, transistor Q4 and the diode of optocoupler U3 conduct current, in a manner similar to the embodiment shown in FIGURE 3. Unlike the embodiment in FIGURE 3, however, this current is not used 20 to charge capacitor C4. The arrangement of transistors Q8 and Q9 in a Darlington configuration results in only a minimal current flow in the base of transistor Q9. Thus, the charging rate of capacitor C4, and the delay time caused thereby, is determined exclusively by the time constant formed by resistor R10 and capacitor C4. 25 This advantageously eliminates any variation in the charging rate of capacitor C4 due to the current amplification factor, or beta, of transistor Q5 in FIGURE 3 or the Darlington arrangement of transistors Q8 and Q9 in FIGURE 5.

25 Referring to FIGURE 5, when power supply 10 is shifted into the standby mode, the +23 V run supply voltage starts to drop. As the run supply voltage drops below a level determined by the ratio of resistances in the voltage divider of resistances R6 and R7, current flow is redirected from transistor Q4 to transistor Q3. The current flowing through transistor Q3 establishes a voltage across resistor R11, which voltage biases reset transistor Q7 on. Capacitor C4 is thereby rapidly 30 discharged to ground through resistor R12 and reset transistor Q7 before the +23 V run voltage has completely decayed.

## CLAIMS:

- 1        1. A switched power supply, comprising:

- 2            a voltage source (RAW B<sup>+</sup>), a transformer (T1) and a switching controller (U1)

- 3            coupled for switched mode generation of an output supply voltage;

- 4            a feedback circuit (W3) for regulating said switched mode operation responsive

- 5            to loading on said output supply voltage;

- 6            a switching circuit (R5, R6, R7, Q3, Q4, Z3, U3) responsive to an on/off signal

- 7            for turning said power supply on and off by controlling conduction in a conduction

- 8            path, said power supply being turned on by a conductive condition in said conduction

- 9            path;

- 10           a fault detector (42) for controlling conduction in a part of said conduction

- 11          path and establishing a non-conductive condition in said part of said conduction path

- 12          responsive to an overload condition of said output supply voltage; and,

- 13           a delay circuit (40) for controlling an auxiliary conduction path bypassing said

- 14          part of said conduction path controlled by said fault detector and establishing a

- 15          conductive condition in said auxiliary conduction path for a period of time after said

- 16          power supply is turned on.

- 1        2. The switched power supply of claim 1, wherein said delay circuit (40) also

- 2          forms part of a latch arrangement which establishes a non-conductive condition in said

- 3          auxiliary conduction path after said period of time.

- 1        3. The switched power supply of claim 2, wherein said latch arrangement

- 2          maintains said non-conductive condition of said auxiliary conduction path until said

- 3          power supply is turned off.

- 1        4. The switched power supply of claim 2, wherein said latch arrangement

- 2          comprises:

- 3            a capacitor (C4);

- 4            a semiconductor switch (Q5) having a first junction forming said auxiliary

- 5            signal path and a second junction providing a charging path for said capacitor; and,

- 6            a diode (D6) providing a discharge path for said capacitor.

- 1        5. The switched power supply of claim 4, wherein said first and second

- 2          junctions of said semiconductor switch (Q5) become non-conductive when said fault

14

3 detector establishes a conductive condition in said part of said conduction path, said

4 part of said conduction path remaining in said conductive condition until detection of

5 said overload condition.

1 6. The switched power supply of claim 5, wherein said capacitor (C4)

2 remains charged while said diode is reverse biased.

1 7. The switched power supply of claim 6, wherein said charged capacitor (C4)

2 maintains a reverse bias condition in said second junction of said semiconductor switch

3 (Q5).

1 8. The switched power supply of claim 6, wherein said diode (D6) becomes

2 forward biased after said power supply is turned off.

1 9. The switched power supply of claim 1, wherein said auxiliary conduction

2 path becomes non-conductive when said fault detector (42) establishes a conductive

3 condition in said part of said conduction path, said part of said conductive path

4 remaining in said conductive condition until detection of said overload condition.

1 10. A switched power supply, comprising:

2 a voltage source (RAW B<sup>+</sup>), a transformer (T1) and a switching controller (U1)

3 coupled for switched mode generation of an output supply voltage;

4 a feedback circuit (W3) for regulating said switched mode operation responsive

5 to loading on said output supply voltage;

6 a switching circuit (R5, R6, R7, Q3, Q4, Z3, U3) responsive to an on/off signal

7 (+23 V-RUN) for turning said power supply on and off by controlling conduction in a

8 conduction path, said power supply being turned on by a conductive condition in said

9 conductive path;

10 a fault detector (42) for controlling conduction in a part of said conduction

11 path and establishing a non-conductive condition in said part of said conduction path

12 responsive to an overload condition of said output supply voltage; and,

13 a latch arrangement (C4, Q5, D6) having an auxiliary conduction path in

14 parallel with said conduction path controlled by said fault detector and establishing a

15 conductive condition in said auxiliary conduction path for a period of time after said

16 power supply is turned on, said auxiliary conduction path becoming non-conductive

17 when a conductive condition is established in said part of said conduction path, said

15

18 latch arrangement maintaining said non-conductive condition of said auxiliary

19 conduction path until said power supply is turned off.

1 11. The switched power supply of claim 10, wherein said part of said

2 conductive path remains in said conductive condition until detection of said overload

3 condition.

1 12. The switched power supply of claim 11, wherein said latch arrangement

2 comprises:

3 a capacitor (C4);

4 a semiconductor switch (Q5) having a first junction forming said auxiliary

5 signal path and a second junction providing a charging path for said capacitor; and,

6 a diode (D6) providing a discharge path for said capacitor.

1 13. The switched power supply of claim 12, wherein said first and second

2 junctions of said semiconductor switch (Q5) become non-conductive when said fault

3 detector establishes a conductive condition in said part of said conduction path, said

4 part of said conduction path remaining in said conductive condition until detection of

5 said overload condition.

1 14. The switched power supply of claim 13, wherein said charged capacitor

2 (C4) maintains a reverse bias condition in said second junction of said semiconductor

3 switch (Q5).

1 15. The switched power supply of claim 14, wherein said capacitor (C4)

2 remains charged while said diode (D6) is reverse biased.

1 16. The switched power supply of claim 15, wherein said diode (D6) becomes

2 reverse biased after said power supply is turned off.

SUBSTITUTE SHEET (RULE 26)

## **FIG. 1**

**FIG. 3**

**SUBSTITUTE SHEET (RULE 26)**

# INTERNATIONAL SEARCH REPORT

International Application No

PCT/US 97/21010

**A. CLASSIFICATION OF SUBJECT MATTER**

IPC 6 H02M3/335 H02H7/12

According to International Patent Classification(IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

IPC 6 H02M H02H H04N

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category <sup>o</sup> | Citation of document, with indication, where appropriate, of the relevant passages                                  | Relevant to claim No. |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------|

| A                     | US 4 914 560 A (OH YONG H ET AL) 3 April 1990<br>see column 4, line 49 - line 68; figure 1<br>----                  | 1,10                  |

| A                     | US 4 586 120 A (MALIK RANDHIR S ET AL) 29 April 1986<br>see the whole document<br>----                              | 1,10                  |

| A                     | US 4 323 961 A (JOSEPHSON ELLIOT) 6 April 1982<br>see column 3, line 67 - column 4, line 48;<br>figures 2,3<br>---- | 1,10                  |

| A                     | EP 0 203 444 A (SIEMENS AG) 3 December 1986<br>see abstract; figure<br>-----                                        | 1,10                  |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

<sup>o</sup> Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier document but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

"&" document member of the same patent family

1

Date of the actual completion of the international search

20 March 1998

Date of mailing of the international search report

30/03/1998

Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Authorized officer

Gentili, L

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International Application No

PCT/US 97/21010

| Patent document cited in search report | Publication date | Patent family member(s)                       | Publication date                 |

|----------------------------------------|------------------|-----------------------------------------------|----------------------------------|

| US 4914560 A                           | 03-04-90         | DE 3840406 A                                  | 08-06-89                         |

| US 4586120 A                           | 29-04-86         | NONE                                          |                                  |

| US 4323961 A                           | 06-04-82         | NONE                                          |                                  |

| EP 0203444 A                           | 03-12-86         | CA 1234210 A<br>JP 61273169 A<br>US 4736264 A | 15-03-88<br>03-12-86<br>05-04-88 |