(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6766552号

(P6766552)

(45) 発行日 令和2年10月14日 (2020.10.14)

(24) 登録日 令和2年9月23日 (2020.9.23)

(51) Int.Cl.

B 41 J 5/30 (2006.01)

G 06 F 3/12 (2006.01)

F 1

B 41 J 5/30

G 06 F 3/12 3 15

G 06 F 3/12 3 40

請求項の数 7 (全 20 頁)

(21) 出願番号 特願2016-186228 (P2016-186228)

(22) 出願日 平成28年9月23日 (2016.9.23)

(65) 公開番号 特開2018-47675 (P2018-47675A)

(43) 公開日 平成30年3月29日 (2018.3.29)

審査請求日 令和1年7月3日 (2019.7.3)

(73) 特許権者 000006747

株式会社リコー

東京都大田区中馬込1丁目3番6号

(74) 代理人 100107766

弁理士 伊東 忠重

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 田中 智憲

東京都大田区中馬込1丁目3番6号 株式会社リコー内

審査官 上田 正樹

最終頁に続く

(54) 【発明の名称】 画像形成装置、印刷システム及び画像転送用の集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

外部コントローラとインターフェースを介して接続される画像形成装置であって、前記外部コントローラから複数の色ごとの版の多値画像データと、文字や写真等の画像種や属性を識別する Tag 情報とを受信し、前記多値画像データに対し Tag 情報に応じた画像処理を行う画像転送ユニット、

記録媒体に印刷動作を行う画像形成エンジン、及び

前記外部コントローラから印刷指示を受信し、前記画像転送ユニットから取得した前記各版の画像処理後の画像データを基に、前記画像形成エンジンの印刷動作を実行するよう制御する制御部を備えており、

前記画像転送ユニットは、

第 1 のメモリと、

前記外部コントローラから前記 Tag 情報を 1 ページに 1 回受信する Tag 受信部と、受信した前記 Tag 情報に対し、データの有効領域以外に、ページを識別するためのプロセス識別子を埋め込み、前記第 1 のメモリに蓄積する Tag ライト DMA 部と、

前記複数の色ごとの版の多値画像データを受信する 夫々の タイミングで、蓄積した前記 Tag 情報を読み出し、前記プロセス識別子を抽出して、出力する Tag リード DMA 部と、

前記第 1 のメモリより読み出した前記 Tag 情報を利用して、受信した前記色ごとの版の多値画像データに対し 画像処理を行う 画像処理部と、を備え、

10

20

前記 Tag リード DMA 部では、前記 Tag 情報から抽出したプロセス識別子に対し、所定の値であるかどうかを判定することを特徴とする

画像形成装置。

【請求項 2】

前記画像転送ユニットは、

第 2 のメモリと、

前記画像処理部により画像処理された画像データに対し、データの有効領域以外にページを識別するためのプロセス識別子を埋め込み、前記第 2 のメモリに蓄積する画像ライト DMA 部と、

各版の画像処理後の画像データを前記第 2 のメモリから読み出し、前記プロセス識別子を抽出して出力する画像リード DMA 部を備え、10

前記画像リード DMA 部では、前記画像データから抽出したプロセス識別子に対し、第 2 の所定の値であるかどうかを判定することを特徴とする

請求項 1 に記載の画像形成装置。

【請求項 3】

前記 Tag リード DMA 部では、それぞれの読み出されたプロセス識別子に対し、あらかじめ設定された前記所定の値と照合し、異なっていればエラー割込みを発生させることを特徴とする

請求項 1 又は 2 に記載の画像形成装置。

【請求項 4】20

前記外部コントローラから前記複数の色ごとの版の多値画像データを受信する 2 以上の整数である n 色に対応する n 個の多値画像データ受信部を備え、

前記 Tag 受信部は、前記外部コントローラから複数の n 色の Tag 情報を 1 ページに 1 回受信し、

前記複数の n 色のうちのいずれか一色の版の多値画像データを受信するタイミングは、前記 Tag 受信部が前記 Tag 情報を受信するタイミングと同時であり、

前記 Tag ライト DMA 部は、前記受信した Tag 情報のうちの前記一色以外の ( n - 1 ) 色に対し、データの有効領域以外にページを識別するための識別子を埋め込んで、前記第 1 のメモリに蓄積させ、30

前記 Tag リード DMA 部は、前記 ( n - 1 ) 色の各版の多値画像データを受信する夫々のタイミングで、前記第 1 のメモリから蓄積した前記 Tag 情報を読み出し、前記識別子を抽出して出力することを特徴とする

請求項 1 乃至 3 のいずれか一項に記載の画像形成装置。

【請求項 5】

前記画像処理部は、前記多値画像データに対して画像処理を行って少値化する、少値化部を有することを特徴とする

請求項 1 乃至 4 のいずれか一項に記載の画像形成装置。

【請求項 6】

ユーザーから送信された印刷データを受信して描画し、多値画像データを作成する前記外部コントローラとして機能するデジタルフロントエンドと、40

前記デジタルフロントエンドとインターフェースを介して接続される請求項 1 乃至 5 のいずれか一項に記載の画像形成装置と、を備えることを特徴とする

印刷システム。

【請求項 7】

外部コントローラとインターフェースを介して接続される画像形成装置に搭載可能な、メモリと接続される画像転送用の集積回路であって、

前記外部コントローラから、文字や写真等の画像種を識別する Tag 情報を 1 ページに 1 回受信する Tag 受信部と、

受信した前記 Tag 情報に対し、データの有効領域以外にページを識別するための識別子を埋め込んで、前記メモリに蓄積させる Tag ライト DMA 部と、50

複数の色ごとの版の多値画像データを受信する夫々のタイミングで、前記メモリから蓄積した前記 Tag 情報を読み出し、前記識別子を抽出して出力する Tag リード DMA 部と、

前記メモリより読み出した前記 Tag 情報を利用して、受信した前記色ごとの版の多値画像データに対し画像処理を行う画像処理部と、を備え、

前記 Tag リード DMA 部では、読み出された識別子に対し、所定の値であるかどうかを判定することを特徴とする

画像転送用の集積回路。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は、画像形成装置、該画像形成装置を備える印刷システム及び該画像形成装置に搭載可能な画像転送用の集積回路に関する。

【背景技術】

【0002】

画像形成装置は、外部コントローラ（例えば、DFE (digital Front End) などの上位装置）からデータを送信されることが多い。プリンタエンジン（画像形成装置）側では、上位装置から送られたデータを、ページ毎に識別する必要がある。例えば、特許文献1では、エンジン側の中央演算処理部が印刷データをビットイメージに展開する際にデータに識別番号を付与する技術が提案されている。ここでは、付与データの中に入力インターフースを識別する番号が入っており、プリントエンジン側が識別番号を読み出し、印刷完了メッセージを出力することで、入力インターフェースが変わっても印刷の待ちを発生させず、プリンタエンジンの状態に関わらず、複数の上位装置からの印刷データの受信及び展開処理を行っている。

20

【0003】

また、特許文献2では、画像形成装置内部で、ページ毎に一文書として、文書識別データを蓄積させて、ページ毎に選択的に表示させる技術が提案されている。

【発明の概要】

【発明が解決しようとする課題】

30

【0004】

しかし、上記特許文献1及び特許文献2では、印刷データを、ページごとにビットイメージに変換して識別しているため、画像形成を行う機構であるメカ部の構成により、色によって画像形成のタイミングが異なる装置において、複数の色に対してデータの読み出しや展開の時間を夫々調整する、画像処理のハンドリングについては、考慮されていなかった。

【0005】

また、上位装置から画像データが転送され、色によって画像形成のタイミングが異なる装置において、メカ部での印刷速度が速くなると、画像処理のハンドリングが間に合わなくなることが懸念される。

【0006】

40

そこで、本発明は上記事情に鑑み、外部コントローラから転送される画像データを、色ごとに異なるタイミングで正確にハンドリングが実行でき、高速印刷に対応可能な、画像形成装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記課題を解決するため、本発明の一態様では、

前記外部コントローラから複数の色ごとの版の多値画像データと、文字や写真等の画像種や属性を識別する Tag 情報とを受信し、前記多値画像データに対し Tag 情報に応じた画像処理を行う画像転送ユニット、

記録媒体に印刷動作を行う画像形成エンジン、及び

50

前記外部コントローラから印刷指示を受信し、前記画像転送ユニットから取得した前記各版の画像処理後の画像データを基に、前記画像形成エンジンの印刷動作を実行させるよう制御する制御部を備えており、

前記画像転送ユニットは、

第1のメモリと、

前記外部コントローラから前記Tag情報を1ページに1回受信するTag受信部と、受信した前記Tag情報を対し、データの有効領域以外に、ページを識別するためのプロセス識別子を埋め込み、前記第1のメモリに蓄積するTagライトDMA部と、

前記複数の色ごとの版の多値画像データを受信する夫々のタイミングで、蓄積した前記Tag情報を読み出し、前記プロセス識別子を抽出して、出力するTagリードDMA部と、

前記第1のメモリより読み出した前記Tag情報を利用して、受信した前記色ごとの版の多値画像データに対し画像処理を行う画像処理部と、を備え、

前記TagリードDMA部では、前記Tag情報を抽出したプロセス識別子に対し、所定の値であるかどうかを判定することを特徴とする

画像形成装置を提供する。

#### 【発明の効果】

##### 【0008】

一態様によれば、画像形成装置において、外部コントローラから転送される画像データを、色ごとに異なるタイミングで正確にハンドリングが実行でき、高速印刷に対応することができる。

##### 【図面の簡単な説明】

##### 【0009】

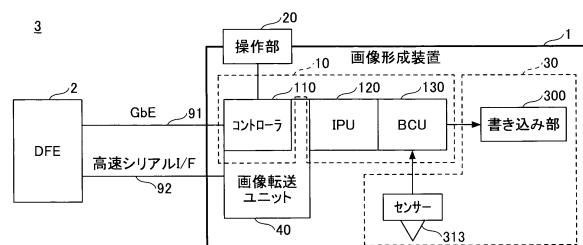

【図1】画像転送ユニットを備える画像形成装置とDFEとを含む印刷システムの構成の概略ブロック図。

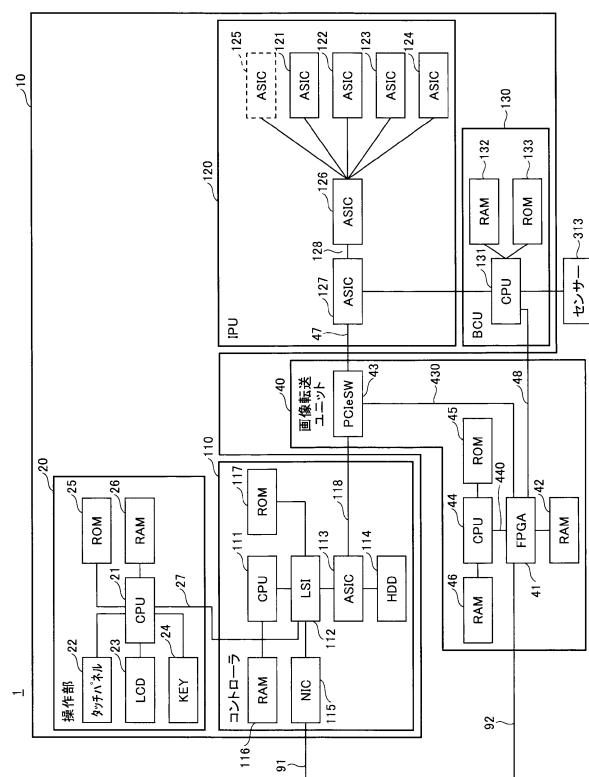

##### 【図2】図1に示す画像形成装置の制御に関する詳細ブロック図。

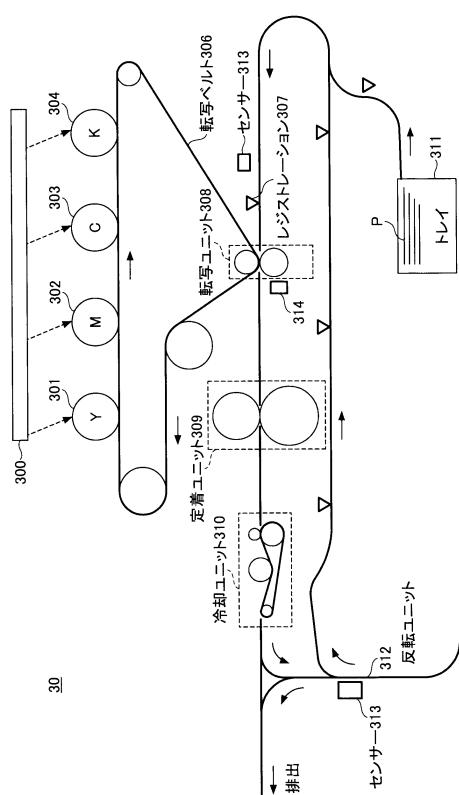

##### 【図3】図1の画像形成エンジンのメカ構成の概略図。

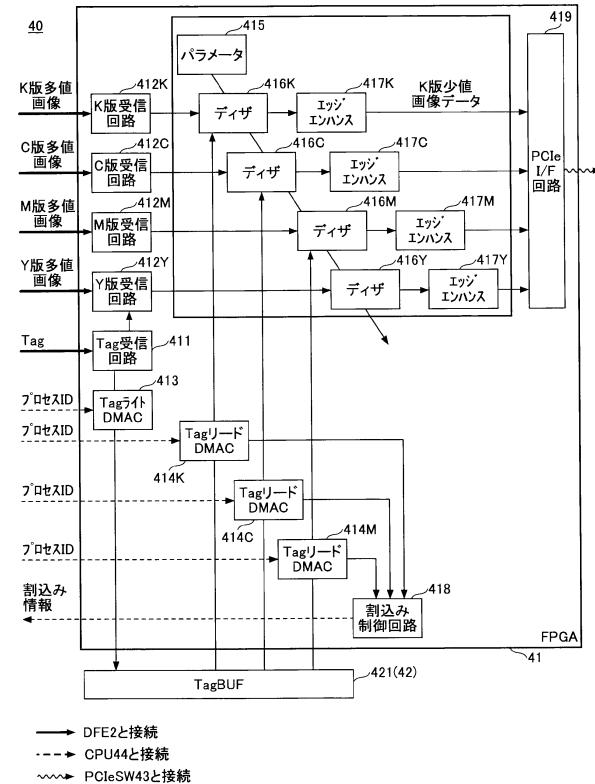

##### 【図4】本発明の第1実施形態に係る画像転送ユニットのFPGAのブロック図。

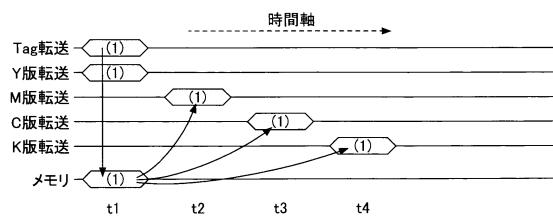

##### 【図5】1ページ印刷の際の画像転送を説明するタイミングチャート。

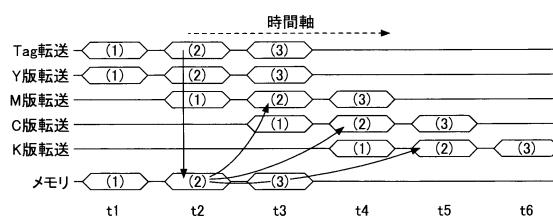

##### 【図6】3ページ印刷の際の画像転送を説明するタイミングチャート。

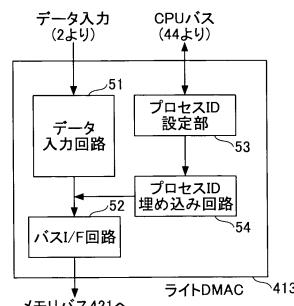

##### 【図7】図4のFPGAに含まれるTagライトDMACの内部構成図。

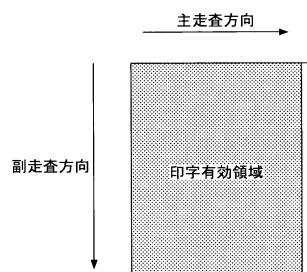

##### 【図8】主走査の後部のラインに余白を作りラスタデータを埋め込む例を示す説明図。

##### 【図9】副走査の後部のラインに余白を作りラスタデータを埋め込む例を示す説明図。

##### 【図10】図4のFPGAに含まれるTagリードDMACの内部構成図。

##### 【図11】本発明の第2実施形態に係る画像転送ユニットのFPGAのブロック図。

#### 【発明を実施するための形態】

##### 【0010】

以下、図面を参照して本発明を実施するための形態について説明する。下記、各図面において、同一構成部分には同一符号を付し、重複した説明を省略する場合がある。

##### 【0011】

#### 【システム全体】

図1は、画像転送ユニットを備える画像形成装置1と、DFE2とを含む印刷システム3の構成の概略ブロック図である。本発明の一実施形態である、画像転送ユニット40付の画像形成装置1の構成を、図1を用いて説明する。

##### 【0012】

図1に示すように、印刷システム3は、デジタルフロントエンド(DFE:Digital Front End)2と、画像形成装置(エンジン部)1とを備える。

##### 【0013】

画像形成装置1は、例えば、制御部10と、操作部20と、画像形成エンジン30と、画像転送ユニット40とを備える。詳しくは、制御部10は、コントローラ110と、画

10

20

30

40

50

像処理用ユニット( I P U : Image Processing Unit ) 1 2 0 と、ベースコントロールユニット( B C U ) 1 3 0 とを備える。画像形成エンジン3 0 は、書き込み部3 0 0 と、センサー3 1 3 等とを備える。

【 0 0 1 4 】

D F E 2 は、画像形成装置1のコントローラ1 1 0 と G b E 9 1 を介して接続され、画像形成装置1の画像転送ユニット4 0 と、高速シリアルI / F 9 2 を介して接続されている。

【 0 0 1 5 】

D F E 2 は、ユーザーから送られてきた印刷データを描画する。そして、イエロー( Y )、マゼンタ( M )、シアン( C )及びブラック( K )と、必要に応じた特色( S )の各版を1200dpi8bitで描画し、高速シリアルI / F 9 2 を通して、画像データのみを画像転送ユニット4 0 へ転送する。また、印刷のコマンド( 印刷指示 )は、 G b E 9 1 を経由して、コントローラ1 1 0 へ送る。

【 0 0 1 6 】

高速シリアルI / F 9 2 は、 D F E 2 から、画像形成装置1の画像転送ユニット4 0 へ画像データを転送するためのインターフェース( I / F )である。転送のタイミングは、画像転送ユニット4 0 で生成する。

【 0 0 1 7 】

G b E ( Giga Bit Ethernet: ギガビットイーサネット(登録商標) ) 9 1 は、 1 GBps で通信が可能な伝送媒体であり、 D F E 2 から、画像形成装置1のコントローラ1 1 0 へ、制御コマンド( 印刷指示 )を送るのに使用される。ここで、 D F E 2 と画像形成装置1とを G b E 規格で通信する(接続する)伝送媒体は、例えば、 S T P ( Shielded Twisted Pair ) ケーブル、 U T P ( Unshielded Twisted Pair ) ケーブル、光ファイバーなどである。

【 0 0 1 8 】

また、 D F E 2 は、カスタマーP C からの印刷情報を受信するための、有線L A N 、無線L A N などの通信インターフェースをさらに備えている。

【 0 0 1 9 】

画像形成装置1では、制御部1 0 のコントローラ1 1 0 は、 D F E 2 から、印刷情報とコマンドを受け取って、 B C U 1 3 0 が解釈できるコマンドに変換して、 B C U 1 3 0 へコマンドを送り、画像転送ユニット4 0 に画像引取り情報をセットして、印刷全体の制御を行う。

【 0 0 2 0 】

画像転送ユニット4 0 は、高速シリアルI / F 9 2 により D F E 2 と接続され、 D F E 2 で描画された画像データを、コントローラ1 1 0 からの指示で、 I P U 1 2 0 へ転送する。

【 0 0 2 1 】

I P U 1 2 0 は、コピーの画像処理用のユニットであり、プリンタ動作時は、画像データの転送のみを行う。

【 0 0 2 2 】

B C U 1 3 0 は、画像形成エンジン3 0 の紙搬送系などをコントロールする。

【 0 0 2 3 】

画像形成エンジン3 0 に含まれるセンサー3 1 3 は、トンボマーク情報を読み取り(検出し)、 B C U 1 3 0 において、所定のタイミングで、センサー3 1 3 が検出した位置決めトンボの画像(トンボマーク情報)を読み出す。

【 0 0 2 4 】

画像形成エンジン3 0 (書き込み部3 0 0 を含む画像形成を行う機構であるメカ部)は、図2、図3で後述するように、紙搬送機構を有し、画像を用紙に転写し、定着する機能を有しており、 B C U 1 3 0 により制御される。

10

20

30

40

50

**【 0 0 2 5 】**

また、操作部 20 は、コントローラ 110 に接続され、U I (User Interface) 機能を有する。

**【 0 0 2 6 】**

ここで、比較例として、D F E で描画されたページごとの多値の画像を、D F E 内部で、スクリーニング処理を実行して、少値化し、圧縮した後に、G b E によって、画像形成装置側のコントローラへ転送する構成も存在する。このような画像形成装置では、D F E で伸長した画像データである少値化後のデータを、画像形成装置の画像処理ユニット (I P U) に転送することが多かった。この比較例の構成だと、D F E から画像形成装置へ少値化したデータを転送することで、転送のデータ量が少なく、転送ケーブル等のコストも安価にできるが、画像形成装置 (エンジン) 側でエンジン特性を画像処理にフィードバックできなかった。10

**【 0 0 2 7 】**

例えば、図 1 に示すように、メカレイアウトの都合上、受信した画像データを処理して印字するエンジン側は印刷時の各版のデータの印字タイミングが異なる場合、D F E で少値化すると、メカの特性が反映できないため、少値化したデータを、メカの特性による夫々の色の印字のタイミングで対応付けたタイミングで、別々に送信することは難しい。

**【 0 0 2 8 】**

一方、エンジン側でエンジン特性を画像処理にフィードバックできるようにすると、少値化前の多値画像データで D F E からの受信することが必要になるが、多値画像データを送信する場合、少値化後の少値画像データに比べデータ量が多くなるということである。20

**【 0 0 2 9 】**

また、少値化前の多値画像データには、その画像の写真や文字等の属性を示す T a g 情報が対応付けられており、その T a g 情報を少値化の際に用いることが多い。これに伴い、T a g 情報を多値画像データにプラスして D F E から転送すると、画像形成装置側は画像処理がやりやすくなるが、印刷時のタイミングで D F E から画像形成装置へ、各色に対して同一の T a g 情報を版数分送ることになるので、転送データ量が増えてしまう。

**【 0 0 3 0 】**

ここで、画像形成装置における画像形成のメカ部での印刷速度の高速化に伴い、画像形成装置の制御部のみで、画像や T a g 情報を転送すると、画像やプロセス識別子の転送速度が間に合わなくなってしまうことがあった。30

**【 0 0 3 1 】**

特に、図 1 に示すように画像形成装置が印刷時の各版のデータの印字タイミングが異なる場合、適切に版の画像データ転送タイミングに合わせて読み出す必要があり、機械本体が高速になればなるほど、色ごとにタイミング画像転送を順番に行う画像ハンドリングが困難になる。

**【 0 0 3 2 】**

これに対して、上述のように本発明では、画像転送ユニット 40 は、高速の画像転送を実現するために画像形成装置 1 側に設けられている。この画像転送ユニット 40 により、コントローラ 110 と D F E 2 との転送バス (G b E 91 コントローラ 110) の他に、画像データのための転送バス (高速シリアル I / F 92 画像転送ユニット 40 I P U 120) を新たに用意することで、高速の画像転送の実現が可能になる。そのため、画像形成エンジン 30 の印刷速度が速くなっても、高速シリアル I / F での画像転送速度や G b E での転送速度が間に合わなくなるエラーを回避できる。40

**【 0 0 3 3 】**

また、本発明では画像のための転送バスが画像形成装置 1 側に設けられているため、D F E 2 側ではなく、画像処理 (スクリーニング、エッジエンハンス、補正) などを、書き込み部 300 の近くの画像形成装置 1 側へ配置することで、比較的リアルタイムなフィードバックが可能になる。ここで、画質の安定を考えて、画像転送ユニット 40 内に、画像処理部としてディザ処理回路 416 (図 4 参照) 及びエッジエンハンス回路 417 が設50

けられている。

【0034】

【制御ブロック】

図2に、図1に示す画像形成装置1の制御に関する詳細ブロック図を示す。図2では、画像形成装置1のうち、制御部10として、コントローラ110、IPU120及びベースコントロールユニット130と、画像転送ユニット40と、操作部20と、画像形成エンジン30の一部であるセンサー313を示す。書き込み部300を含む画像形成エンジン30の構成は図3とともに後述する。

【0035】

図2に示すように、画像形成装置1と、外部コントローラであるDFE2とを接続するためのインターフェースとして、PCIe92と、GbE91とが設けられている。PCIe92は、ペアツ間を接続する高速シリアルI/F92の一種であり、画像転送ユニット40と、DFE2との間で、双方向通信が可能である。また、GbE91は、GbE規格の伝送媒体であって、DFE2とコントローラ110とを接続するための専用インターフェースである。

【0036】

図2に示すコントローラ110は、CPU111、LSI112、ASIC113、HDD114、NIC115、RAM116及びROM117を備える。図2に示すコントローラ110は、RAM116に印刷情報を受信して、DFE2からのコマンドに応じて、印刷コマンド(印刷)を、PCIe118を経由してBCU130へ、転送する。

【0037】

なお、後述する第2実施形態(図11参照)の構成では、印刷コマンドの他に画像データもPCIe118を通って転送する。

【0038】

図2において、CPU(Central Processing Unit)111は、初期化プログラムをROM117から読み出して、プログラムを実行する。また、コントローラ110に搭載されるデバイスの初期化、PCIeSW43と接続されるPCIe118の初期化、FPGA41に接続されるPCIe部430の初期化、IPU120のASIC121~126のPCIe部128の初期化、ASIC127との通信について制御ができる。

【0039】

LSI(Large-Scale Integration)112は、CPU111と合わせて使う集積回路であって、PCIe、USBなどの周辺インターフェースを持つ。ASIC(application specific integrated circuit:特定用途向け集積回路)113は、接続及び転送用の専用ASICであり、IPU120と接続するためのPCIe118のインターフェースと転送のためのDMAC(Direct Memory Access Controller)などを有している。

【0040】

HDD(Hard Disk Drive)114は、プログラムやデータ、設定値などを保存する。NIC(Network Interface Card)115は、PCIe118で、LSI112に接続される、DFE2と接続するための専用インターフェースである。

【0041】

RAM(Random Access Memory)116は、CPU111が、動作するために使用するメモリであり、画像データを一時保存するためにも使われる。ROM(Read Only Memory)117は、CPU111の初期化プログラムとブートローダーを格納する。

【0042】

図2に示す画像転送ユニット40は、FPGA41、RAM(メモリ)42、PCIeSW43、CPU44、ROM45、RAM46、高速シリアルインターフェース(I/F)47、及びBCU I/F48を備えている。

【0043】

画像転送ユニット40は、PCIeSW43を介して、コントローラ110と、IPU120と接続される。

10

20

30

40

50

## 【0044】

画像転送ユニット40は、D F E 2から高速シリアルI/F92を通して、画像処理前の画像データ及びT a g情報を受信する。

## 【0045】

P C I e S W 4 3は、P C I e (118、430、47)のスイッチデバイスであって、複数のP C I eデバイスを接続するために使う。また、コントローラ110により、初期化される。

## 【0046】

C P U 4 4は、R O M 4 5のプログラムを実行することで、画像転送ユニット40の初期化を行い、B C U 1 3 0からの、コマンドにより、指示された内容を実行する。また、C P U 4 4は、コントローラ110でセットされた画像取り込み情報を基に、ページごとに開始アドレス(プロセスI D)を設定する。

10

## 【0047】

R O M 4 5は、データ転送ユニット40の制御プログラムおよびデータが格納されている。R A M 4 6は、C P U 4 4のワーク用メモリである。

## 【0048】

F P G A (Field-programmable gate array) 4 1は、プログラム可能なゲートアレイであり、高速シリアルインターフェース92を介して、D F E 2から受け取った画像データを画像処理して、少値の画像データを生成し、R A M 4 2に蓄積する。そして、I P U 1 2 0の転送要求に応じて、少値の画像データを、色版ごとに転送する。即ち、F P G A 4 1は画像転送用の集積回路である。

20

## 【0049】

ここで、F P G A 4 1の役割は、外部コントローラ(D F E 2)から、印刷1ページごとに、各版の多値画像データと、そのページの各版共通の画像種を示すT a g情報を受信して画像処理を行い、画像形成エンジン30での印刷タイミングを制御するB C U 1 3 0からの印刷要求に応じて少値データを送信することである。

## 【0050】

画像転送ユニットではT a g情報を、いったん画像転送ユニット側のメモリ(R A M 4 2)に蓄積し、各版の転送タイミングに応じて、T a g情報をメモリより読み出して各種画像処理を行っている。例えば、R A M 4 2は、図4に示すT a g専用のメモリであるT a gバッファメモリ421として機能し、画像形成エンジン30のレイアウトの違いによりドラム遅延を吸収するため、4ページ分のメモリを持っている。

30

## 【0051】

R A M(メモリ)42は、画像データ時蓄積用のメモリである。画像転送に用いる、画像処理用のデータを蓄積しておく。

## 【0052】

高速シリアルI/F92は、D F E 2から画像データを転送するための高速シリアルインターフェースである。高速シリアルI/F92で画像データを転送する転送タイミングは、F P G A 4 1によって指示される。

40

## 【0053】

B C U I/F48は、B C U 1 3 0と画像転送ユニット40間で、データのやり取りをするためのB C U用のインターフェースである。

## 【0054】

I P U(画像処理ユニット)120は、色版ごとの画像転送を受け持つ。P C I e 1 1 8、47で、コントローラ110と接続される。

## 【0055】

図2を参照して、I P U 1 2 0は、複数の色ごとの書き込み制御用のA S I C 1 2 1、122、123、124、125、制御A S I C 1 2 6、画像処理A S I C 1 2 7を備える。

## 【0056】

50

A S I C 1 2 1 は、 Y (イエロー) 色用書き込み A S I C であり、 画像補正 (台形補正) の機能を有し、 補正のパラメータは、 B C U 1 3 0 から設定される。

【 0 0 5 7 】

A S I C 1 2 2 は、 M (マゼンタ) 色用書き込み A S I C 、 A S I C 1 2 3 は、 C (シアン) 色用書き込み A S I C 、 A S I C 1 2 4 は、 K (ブラック) 色用書き込み A S I C であり、 これらの A S I C は Y 用と同様に、 画像補正 (台形補正) の機能を有し、 B C U 1 3 0 から設定される。

【 0 0 5 8 】

A S I C 1 2 5 は、 特色用書き込み A S I C であり、 オプションで、 5 色目を使うときに追加して用いられる。 また、 画像補正 (台形補正) の機能を有し、 補正のパラメータは B C U 1 3 0 から設定される。

【 0 0 5 9 】

A S I C 1 2 6 は、 書き込み制御 A S I C ( 1 2 1 ~ 1 2 5 ) を制御する A S I C である。 A S I C 1 2 7 は、 画像処理 A S I C であり、 コントローラ 1 1 0 からの画像転送を行い、 B C U 1 3 0 によって、 制御される。

【 0 0 6 0 】

B C U 1 3 0 (ベースコントロールユニット) は、 紙搬送等メカ的な制御と画像転送タイミング制御を行う。 図 2 に示す B C U 1 3 0 は C P U 1 3 1 、 R A M 1 3 2 及び R O M 1 3 3 を備えている。

【 0 0 6 1 】

R A M 1 3 2 は、 C P U 1 3 1 が、 使用するメモリであり、 R O M 1 3 3 には、 C P U 1 3 1 のプログラム / データが格納されている。 C P U 1 3 1 が、 R O M 1 3 3 のプログラムを実行することで、 I P U 1 2 0 と B C U 1 3 0 の初期化を行う。

【 0 0 6 2 】

センサー 3 1 3 は、 位置決め用トンボを読み出すための画像センサーである。 B C U 1 3 0 において、 トンボ画像が読み出し、 そのトンボ画像の座標を決定して、 画像形成の際の指標とする。

【 0 0 6 3 】

操作部 2 0 は、 U I を受け持つユニットで、 コントローラ 1 1 0 と接続される。 図 2 において、 操作部 2 0 は、 C P U 2 1 、 タッチパネル 2 2 、 L C D 2 3 、 キー入力部 2 4 、 R O M 2 5 、 R A M 2 6 及び操作部 I / F 2 7 を備える。

【 0 0 6 4 】

C P U 2 1 は、 操作部 2 0 の主制御部であり、 R O M 2 5 のプログラムから起動し、 操作部 2 0 全体の初期化が終わったら、 コントローラ 1 1 0 からのコマンド待ちになる。

【 0 0 6 5 】

タッチパネル 2 2 は、 ユーザーからの入力を検知する。 L C D ( liquid Crystal Display : 液晶ディスプレイ ) 2 3 は表示部として機能する。 キー入力部 ( K E Y ) 2 4 は、 専用ハードキーで、 ユーザーからの入力を検知する。 R O M 2 5 は、 操作部 2 0 のプログラム / データ格納用のメモリである。 R A M 2 6 は、 操作部 2 0 の C P U 2 1 のワーク用メモリである。 操作部 I / F 2 7 は、 操作部 2 0 とコントローラ 1 1 0 とを接続するインターフェースである。

【 0 0 6 6 】

【 画像形成エンジン 】

図 3 に図 1 の画像形成エンジン 3 0 のメカ構成の概略図を示す。 図 3 を用いて、 画像形成を行うメカ構成について説明する。

【 0 0 6 7 】

画像形成エンジン 3 0 において、 画像形成ユニットとして各色の感光体ユニット 3 0 1 ~ 3 0 4 、 転写ベルト 3 0 6 、 レジストレーション部 3 0 7 、 転写ユニット 3 0 8 、 定着ユニット 3 0 9 及び冷却ユニット 3 1 0 を備える。

【 0 0 6 8 】

10

20

30

40

50

また、画像形成エンジン 30において、搬送ユニットとして、給紙トレイ 311、反転ユニット 312、センサー 313 及びセンサー 314 等を備える。

【0069】

図3において、Y色感光体ユニット 301は、Y色で画像を形成するためのユニットである、M色感光体ユニット 302は、M色で画像を形成するためのユニットであり、C色感光体ユニット 303は、C色で画像を形成するためのユニットであり、K色感光体ユニット 304はK色で画像を形成するためのユニットである。

【0070】

図3では、4つの感光体ユニット 301～304において感光体のみを示しているが、夫々の感光体ユニット 301～304には、感光体の周囲に帯電装置、現像装置なども設けられている。

10

【0071】

また、4つの感光体ユニット 301～304の上方には、書き込み部（光書き込み部、露光装置）300が設けられている。

【0072】

用紙Pに画像を印刷する際、回転する感光体の表面を帯電装置によって一様に帯電させ、IPU120から転送された画像データ等に基づいて書き込み部 300が感光体の表面を露光して静電潜像を形成する。次に、内部にトナーを含む現像剤を収容する現像装置が感光体の表面の静電潜像を現像してトナー像を形成する。

20

【0073】

転写ベルト 306は、各色の感光体ユニット 301～304から、1ページ分の画像のトナー（トナー像）を載せて、用紙Pに二次転写するためのベルトである。転写ユニット 308は、転写ベルト 306から、用紙Pへトナー像を二次転写するユニットである。

【0074】

レジストレーション部 307は、タイミング合わせのために、一旦、用紙Pを停止させる場所である。レジストレーション部 307で一時停止の際、センサー（位置決めセンサー）313は、用紙Pの第一面のトンボを読み取ることができる。

【0075】

定着ユニット 309は、トナーの載った（トナー像が転写された）用紙Pを、熱と圧力で定着させるユニットである。冷却ユニット 310は、定着で温められた用紙Pを冷却するユニットである。

30

【0076】

また、搬送ユニットとして、給紙トレイ 311は、用紙Pが載置され、用紙Pが必要に応じて供給する。反転ユニット 312は、両面印刷の際に、用紙Pをスイッチバックして、用紙Pの表裏を反転させる。

【0077】

反転ユニット 312の近傍のセンサー（位置決めセンサー）313は、用紙Pの第二面のトンボを読み取ることができる。濃度センサー 314は、ローラー（転写ローラ）に転写された各色の濃度を読み取るセンサーであり、色合わせ、色位置合わせに使われる。

【0078】

40

このようなメカ構成の画像形成エンジン 30では、印刷時、トレイ 311から、用紙Pが搬送され、タイミング合わせのための位置、レジストレーション部 307で、一瞬停止する。

【0079】

そのタイミングに合わせて、IPU120は、先頭色がY色として、Y色感光体ユニット 301の感光体に絵を描くために、画像を転送する。続いて、M色感光体ユニット 302へ画像を転送し、C色感光体ユニット 303へ画像を転送し、K色感光体ユニット 304へ画像を転送する。

【0080】

これらの画像は、それぞれ色のトナーを用いて色ごとに現像され、転写ベルト 306に

50

転写される。転写は、画像の位置が合うように、タイミングを調節して、転写ベルト306に一次転写され、転写ユニット308において、用紙Pに二次転写される。

【0081】

その後、用紙Pは、定着ユニット309で、熱と圧力を付与されることで画像が定着され、冷却ユニット310で冷却される。片面印刷である場合は、用紙Pはそのまま排紙される。

【0082】

両面印刷の場合は、用紙Pは反転ユニット312に搬送され、スイッチバックして第二面が上になるようにして搬送される。両面印刷で第二面に印刷する場合も同様に、用紙Pは、レジストレーション部307で、一瞬停止し、各色の画像が載った、転写ユニット308で、転写ベルト306から、第二面へ画像が二次転写され、定着、冷却されて、排紙される。

10

【0083】

なお、図3に示す画像形成エンジンでは、給紙トレイが1つの場合について説明したが、これに限定されるものではなく、給紙トレイが複数あってもよい。また、図3では、画像形成エンジンが4つの感光体を有する場合について説明したが、感光体の数は色に対応して増減可能であり、これに限定されるものではない。

【0084】

【第1実施形態の画像転送ユニット】

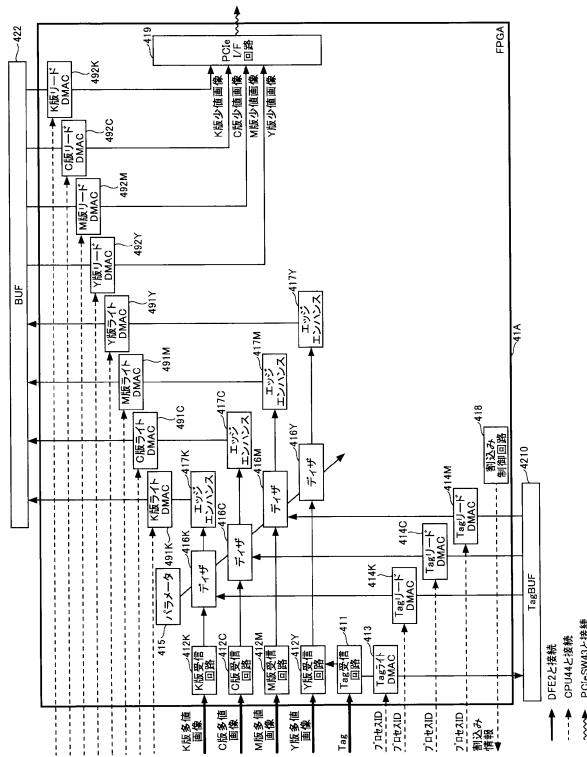

図4は、本発明の第1実施形態に係る画像転送ユニット40のFPGA41のブロック図である。図4を用いて、第1実施形態の画像転送について説明する。

20

【0085】

図4は、主に、画像転送ユニット40におけるFPGA41及びTagバッファメモリ(図中、TagBUFと示す)421を示している。Tagバッファメモリ421は、例えば図2のRAM42によって実現される。

【0086】

Tagバッファメモリ(メモリ、第1のメモリ)421は、Tag用のバッファメモリであって、Tag情報が埋め込まれた画像データを蓄積する。

【0087】

画像転送ユニット40のFPGA41は、Tag受信回路411、各色の版受信回路412Y, 412M, 412C, 412K、TagライトDMAC413、TagリードDMAC414M, 414C, 414K、パラメータ送信部415、ディザ処理回路416Y, 416M, 416C, 416K、エッジエンハンス回路417Y, 417M, 417C, 417K、割り込み制御回路418、及びPCIeI/F回路419を備える。

30

【0088】

Tag受信回路411は、DFE2から、画像種となるTagデータ(Tag情報)を受信する回路である。

【0089】

多値画像データ受信回路(多値画像データ受信部)412Yは、DFE2から、Y版の多値画像データを受信する回路である。同様に、412M, 412C, 412Kは、夫々、M版、C版、K版の多値画像データを夫々受信する受信回路である。

40

【0090】

ここで、DFE2から送られてくる画像データの転送色順は、複数の色成分(Y版/M版/C版/K版)ごとに異なり、図3に示すようなレイアウトの場合、メカレイアウトに合わせて、Tag=Y版 M版 C版 K版の順となる。なお、この色の順番は一例であって、メカレイアウトの順番に合わせて転送順を設定する。

【0091】

また、TagライトDMAC413、TagリードDMAC414M, 414C, 414Kは、CPU44と接続されるCPUバス440が接続されている。

【0092】

50

TagライトDMA413は、Tag受信回路411からのデータ(Tag情報)を受信し、メモリ42にライトするDMA回路(TagライトDMA部、Tag情報書き込み部)である。あらかじめメモリ42へアクセスする開始アドレス(プロセスID)が、画像転送ユニット240のCPU44(図2参照)にて設定される。

#### 【0093】

TagリードDMA414M, 414C, 414Kは、M版/C版/K版の多値画像の受信タイミングに合わせて起動されるDMA回路(TagリードDMA部、Tag情報読み出し部)である。詳しくは、TagリードDMA414M, 414C, 414Kが、複数の色ごとの版(M版/C版/K版)の多値画像データを受信するタイミングで、蓄積したTag情報を読み出し、識別子(開始アドレス)を抽出して出力する。

10

#### 【0094】

即ち、TagリードDMA414M, 414C, 414Kは、メモリから受信したTag情報及び画像データと、CPU44から受け取った開始アドレス(プロセスID)とを用いて、各色のデータが所望のデータであるかどうかを判別して、夫々の色ごとに異なるタイミングで画像処理へ移行させる。

#### 【0095】

ディザ処理回路(Dither: 少値化回路)416Yは、64画素×64ラインのディザマトリクスを用いて、Y版の多値画像データの画像処理(少値化)を行う回路である。同様に、416M, 416C, 416Kは、夫々、M版、C版、K版の多値画像データを画像処理する回路である。

20

#### 【0096】

パラメータ送信部415は、ディザ処理に必要なパラメータを、ディザ処理回路416Y, 416M, 416C, 416Kへ、随時供給する回路である。

#### 【0097】

エッジエンハンス回路417Yは文字画像のエッジ補正を行う回路である。同様に、417M, 417C, 417Kは、夫々、M版、C版、K版の文字画像のエッジ補正を行う回路である。

#### 【0098】

ディザ処理回路416Y～416K、パラメータ送信部415、エッジエンハンス回路417Y～417Kは、画像処理部として機能する。

30

#### 【0099】

割り込み制御回路418は、抽出されたプロセスIDとあらかじめ設定されたプロセスIDとを比較し、異なる場合に割込みを発生させる。詳細は、図10とともに後述する。

#### 【0100】

PCIeI/F回路419は、図2に示すPCIeSW43と接続されるPCIe430を制御する回路である。

#### 【0101】

このように、FPGA41では、外部コントローラであるDFE2から画像データとTag情報とを受信し、CPU44からプロセスIDを受信することで、各色のデータが所望のデータであることを判別して、色ごとに異なるタイミングで画像処理ハンドリング(画像ハンドリング)する。即ち、ドラム毎の画像形成のタイミングに適したタイミングで、画像転送処理を対応付けて実行することができる。

40

#### 【0102】

##### 〔転送タイミング〕

図4に示す画像転送ユニット40において、DFE2から送られてくる画像データの転送の様子を図5(1ページ印刷)に、3ページ印刷の様子を図6に、概略タイミングチャートとして示す。

#### 【0103】

図5に示す1ページ印刷の場合を用いて、転送のタイミングについてまず説明する。Y版と同タイミングで転送されるTagデータは、TagライトDMA413によって、

50

そのまま画像転送ユニット 40 内部のメモリである Tag バッファメモリ 421 (下記、単にメモリ 421 と示す) へ書き込まれる。それと同時に Tag データは Y 版の画像処理にも使用される。

#### 【0104】

その後時間が経過し、M 版の画像データの転送が開始されると (図 5、時刻 t2)、Tag リード DMA C414M にて、先程ライトされた Tag データのリードが開始される。リードされた Tag データは M 版の画像データと同期を合わせてリードされ、画像処理を行っていく。その後の C 版、K 版も同様に行われる。

#### 【0105】

ここでは、4 色について説明したが、色要素は、他の数であってもよい。例えば、Tag 受信部である Tag 受信回路 411 は、外部コントローラである DFE2 から複数の n 色の Tag 情報を 1 ページに 1 回受信する。この際、図 5 に示すように、複数の n 色のうちのいずれか一色の版の多値画像データを受信するタイミングは、Tag 受信回路 411 が Tag 情報を受信するタイミングと同時である。

#### 【0106】

Tag ライト DMA C413 は、受信した Tag 情報のうちの前記一色以外の (n-1) 色に対し、データの有効領域以外にページを識別するプロセス識別子を埋め込んで、メモリ 421 に蓄積させ、前記 (n-1) 色の各版の多値画像データを受信する夫々のタイミングで、メモリ 42 から蓄積した Tag 情報を読み出し、識別子を抽出して出力する。

#### 【0107】

図 6 の 3 ページ印刷のタイミングチャートでは、メカレイアウトによるが、本実施例では、2 ページ目の Y 版の転送 (2) が、M 版の 1 ページ目の転送 (1) と重なるタイミングとなる。さらに K 版の 1 ページ目では M 版の 3 ページ目と C 版の 2 ページ目と重なるタイミングとなる。一旦、メモリ 421 にライトされた Tag データは随時読み出されることになる。連続印刷になると、このような転送の重なりができるため、画像のハンドリングが複雑となる。

#### 【0108】

加えて、4 つの版が必ずあると限らず、印刷ページによっては、特定の版 (例えば Y 版) が印刷データとして存在しないこともあるため、画像ハンドリングとしては複雑度が増してしまう。

#### 【0109】

しかし、本発明では、下記制御の Tag ライト DMA C413 及び Tag リード DMA C414 を適用することで、プロセス ID を判別し、適切に画像ハンドリングを実施させる。

#### 【0110】

##### [Tag ライト DMA C]

図 7 には図 4 に示す Tag ライト DMA C413 の内部構成図を示し、以下に説明する。図 7 に示すように、Tag ライト DMA C413 は、データ入力回路 51、バス I/F 回路 52、プロセス ID 設定部 53 及びプロセス ID 埋め込み回路 54 を含む。

#### 【0111】

Tag ライト DMA C413 は、CPU44 (図 2 参照) と接続される CPU バス 440 からアクセスする開始アドレスを指定して起動される。その起動の際に、転送するプロセス ID を予め設定する。

#### 【0112】

ここで、プロセス ID は、プロセス (ページ) を実行するための識別子 (プロセス識別子、PID) であって、処理するページの固有番号 (例えば、0 から 255 の番号を繰り返し使う) を示す。

#### 【0113】

起動後は、Tag ライト DMA C413 では、データ入力回路 51 は、DFE2 からの Tag データ受信に伴い、バス I/F 回路 52 及びメモリバス 420 を介して、データを

10

20

30

40

50

メモリ 4 2 内へ随时ライトする動作を行う。その際に、プロセス ID をライトするデータの中に埋め込むことを行うのがプロセス ID 埋め込み回路 5 4 である。具体的には印字有効領域より広い範囲をメモリの書き込み対象として、その印字有効範囲外の領域にプロセス ID を埋め込み、メモリ 4 2 にライトする（書き込む）。

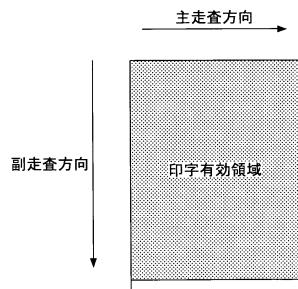

【 0 1 1 4 】

図 8 に主走査の後部のラインに余白を作りラスタデータを埋め込む例を示す。画像の転送は主走査方向にラスタ形式で行われ、そのラスタデータは副走査方向にカウントするラインと呼ばれる。そのラインの後部に余白部分を作り、その部分にプロセス ID を埋め込む。

【 0 1 1 5 】

また、図 9 に、副走査方向の後部のラインに余白を作りラスタデータを埋め込む例を示す。なお、埋め込む部分は、予め決められた余白であればどの位置であってもよい。

【 0 1 1 6 】

このように印字有効領域外にプロセス ID をデータとして埋め込むことにより、DMA 転送を指示したデータが、所望のデータなのか判別可能となり、デバッグが容易となる。

【 0 1 1 7 】

また、夫々の色ごとに異なるタイミングで画像処理へ移行させることで、色ごとに異なるタイミングで、画像ハンドリングをすることができる。

【 0 1 1 8 】

したがって、その後の画像形成において、正しいデータを、色ごとに適切なタイミングで実施できるため、画像形成エンジンで用紙 P 上に作成される画像は、ページ毎にズレのない、正確なハンドリングにより、高品質となり、高速な画像形成に対応できる。

【 0 1 1 9 】

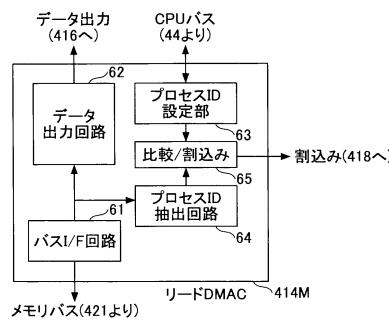

[ Tag リード DMA C ]

図 10 には図 4 で説明の Tag リード DMA C 4 1 4 の内部構成図を示し、以下に説明する。なお、図 10 では一例として Tag リード DMA C 4 1 4 M を例として説明するが、Tag リード DMA C 4 1 4 C, 4 1 4 K も同様の構成であるため、説明を省略する。

【 0 1 2 0 】

図 10 に示すように、Tag リード DMA C 4 1 4 M は、バス I / F 回路 6 1、データ出力回路 6 2、プロセス ID 設定部 6 3、プロセス ID 抽出回路 6 4 及びプロセス ID 比較 / 割込み回路 6 5 を含む。

【 0 1 2 1 】

Tag リード DMA C 4 1 4 M では、プロセス ID 設定部 6 3 が CPU バス 4 4 0 からアクセスする開始アドレスを指定して起動される。その起動の際に、転送するプロセス ID をあらかじめ設定する。

【 0 1 2 2 】

起動後、Tag リード DMA C 4 1 4 M では、バス I / F 回路 6 1 及びメモリバス 4 2 0 を介して、メモリ 4 2 から転送データをリードする（読み出す）動作を行う。読み出したリードデータの中から、Tag ライト DMA C 4 1 3 のプロセス ID の埋め込み箇所と同じ位置からプロセス ID の抽出をプロセス ID 抽出回路 6 4 にて行う。

【 0 1 2 3 】

プロセス ID 比較 / 割込み回路 6 5 では、抽出されたプロセス ID と、あらかじめ設定されたプロセス ID とを比較し、異なる場合に割込みを発生させる。割込みは FPGA 4 1 内部の割込み制御回路 4 1 8 (図 4 参照) にて処理され、CPU 4 4 に伝達される。

【 0 1 2 4 】

これによって、CPU 4 4 は異常な動作をすぐに検出することができ、高品質な画像形成装置を提供することができる。また、識別子（プロセス ID）の照合を FPGA 4 1 のハードウェア内で行うので、デバッグが容易になる。

【 0 1 2 5 】

[ 第 2 実施形態の画像転送ユニット ]

10

20

30

40

50

図11に、本発明の第2実施形態に係る画像転送ユニット40AのFPGA41Aのブロック図を示す。図11に示す本実施形態に係るFPGA41Aは、図4に示す構成要素に加えて、少値画像データ用バッファメモリ422が設けられ、FPGA41Aは、各色版の画像ライトDMA491Y, 491M, 491C, 491K、各色版の画像リードDMA492Y, 492M, 492C, 492Kをさらに備えている。

【0126】

少値画像データ用バッファメモリ(第2のバッファメモリ、メモリ)422は、画像処理後の少値画像データ用のバッファメモリであって、各色の版ごとに表面印字用としてページ2面、裏面印字用としてページ2面の計4面を有している。

【0127】

各版の画像ライトDMA491Y, 491M, 491C, 491K及び各版の画像リードDMA492Y, 492M, 492C, 492Kは、CPU44とCPUバス440を介して接続されている。

【0128】

Y版ライトDMA491Y(画像ライトDMA部)491Yは、少値化後の画像データをメモリ422にライトするDMA回路である。あらかじめ第2のメモリ422をアクセスする開始アドレスがCPU44にて設定される。画像ライトDMA491M, 491C, 491Kでの、他の色版でも同様である。

【0129】

Y版リードDMA492Y(画像リードDMA部)492Yは、印刷要求に合わせて起動されるK版データを転送するDMA回路である。あらかじめ第2のメモリ422をアクセスする開始アドレスがCPU44にて設定されている。画像リードDMA492M, 492C, 492Kでの、他の色版でも同様である。

【0130】

上述のように、本実施形態では、少値化後のデータを、一旦画像転送ユニット40Aの第2のメモリ422に蓄積する点が、図4の制御とは異なる。本実施形態では、このように一旦蓄積することで、印字のためのデータ転送速度に、DFE2からのデータ受信速度を緩和すること可能になる。

【0131】

印字側のデータ転送速度は搬送される転写紙と次の転写紙の間の時間(紙間とも呼ばれる)を含まない期間に行われるため、DFE2側の転送速度に比べて、その分だけ速くする必要がある。

【0132】

なお、各版のライトDMA491Y, 491M, 491C, 491Kの内部構成は、図7に示すTagライトDMA413と同様である。この場合、用途がTag情報と、色ごとの版の少値画像データとで異なるが、データのプロセスIDを、第2のメモリ422にライトする点で同様である。

【0133】

また、上記各版リードDMA492Y, 492M, 492C, 492Kの内部構成は、図10に示すTagリードDMA414の構成と同様である。この場合、用途が色ごとの版の多値画像データと、色ごとの版の少値画像データとで異なるが、蓄積したデータのプロセスIDを、リード時に照合するという点で同様である。

【0134】

このように、第2のメモリ422から読み出すTagデータでも、メモリアクセスの先頭アドレスをCPU44より指示して行うが、そのデータからハードウェアでライト時に埋め込んだ識別子を抽出することにより、正しいもしくは誤ったデータか判別できるため、デバッグが容易となる。

【0135】

したがって、画像転送ユニットの制御ソフトウェア作成時のデバッグにおいて、画像ハンドリングに関するミスが判別でき、設計効率が向上し、また高品質の画像形成装置の提

10

20

30

40

50

供が可能となる。

【0136】

上述のように、本発明の複数の実施形態では、画像種を示す Tag 情報、及び画像処理後の画像データに対して、蓄積時にデータの有効領域以外の部分に、処理するページの固有番号を示すプロセス ID を埋め込み、所定のタイミングでそれらのデータを読み出した際にプロセス ID を取り出し、ソフトウェアで判別できるようにした。

【0137】

これによって、DMA 転送を指示したデータが所望のデータなのか判別可能となり、デバッグが容易となる。

【0138】

なお、上記では、画像形成装置として、電子写真方式のカラープリンタの場合について説明したが、これに限定されるものではなく、例えば、光プロッタやデジタル複写装置であってもよい。あるいは、画像形成装置は、用紙にインクを吹き付けて画像を形成するインクジェットプリンタにも適用可能であってもよい。

【0139】

また、上記の画像形成装置では、画像形成の対象を用紙として説明したが、画像が形成される記録媒体は、紙に限定されるものではない。例えば、記録媒体とは、液体が少なくとも一時的に付着可能なものであって、付着して固着するもの、付着して浸透するものなどを意味する。具体例としては、用紙、記録紙、記録用紙、フィルム、布などの被記録媒体、電子基板、圧電素子などの電子部品、粉体層（粉末層）、臓器モデル、検査用セルなどの媒体であり、特に限定しない限り、液体や粉体が付着するすべてのものが含まれる。例えば、上記「対象物」の材質は、紙、糸、纖維、布帛、皮革、金属、プラスチック、ガラス、木材、セラミックスなどであり、液体が一時的でも付着可能な材質であればよい。

【0140】

以上、本発明の好ましい実施形態について詳述したが、本発明は係る特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の実施形態の要旨の範囲内において、種々の変形、変更が可能である。

【符号の説明】

【0141】

1 画像形成装置

2 DFE (外部コントローラ、デジタルフロントエンド)

10 制御部

110 コントローラ（制御部）

120 IPU（制御部）

130 BCU（制御部）

20 操作部

30 画像形成エンジン

300 書き込み部

313 センサー

40, 40A 画像転送ユニット（データ転送ユニット、DTU）

41, 41A FPGA（画像転送用の集積回路）

42 RAM

44 CPU

411 Tag 受信回路

412 (412Y, 412M, 412C, 412K) 多値画像データ受信回路（多値データ受信部）

412 Tag 受信回路（Tag 受信部）

413 Tag ライト DMA C (Tag ライト DMA 部)

414 (414M, 414C, 414K) Tag リード DMA C (Tag リード DMA 部)

10

20

30

40

50

## 4 1 5 パラメータ送信部

4 1 6 ( 4 1 6 Y , 4 1 6 M , 4 1 6 C , 4 1 6 K ) ディザ処理回路 ( 画像処理部 )

4 1 7 ( 4 1 7 Y , 4 1 7 M , 4 1 7 C , 4 1 7 K ) エッジエンハンス回路 ( 画像処理部 )

## 4 1 8 割り込み制御回路

4 1 9 P C I e I / F 回路

4 2 1 メモリ ( Tag バッファメモリ、第 1 のメモリ )

4 2 2 メモリ ( 少値画像データ用バッファメモリ、第 2 のメモリ )

4 9 1 K 版ライト D M A C ( 画像ライト D M A 部 )

4 9 2 K 版リード D M A C ( 画像リード D M A 部 )

10

P 用紙 ( 記録媒体 )

T a g T a g 情報 ( タグ )

P I D プロセス I D ( プロセス識別子、開始アドレス )

## 【先行技術文献】

## 【特許文献】

【 0 1 4 2 】

【特許文献 1 】特許第 2 8 2 8 0 1 1 号

【特許文献 2 】特許第 3 3 4 4 7 7 8 号

【 図 1 】

画像転送ユニットを備える画像形成装置と D F E を含む印刷システムの構成の概略ブロック図

【 図 2 】

図 1 に示す画像形成装置の制御に関する詳細ブロック図

【図3】

図1の画像形成エンジンのメカ構成の概略図

【図4】

本発明の第1実施形態に係る画像転送ユニットのFPGAのブロック図

【図5】

1ページ印刷の際の画像転送を説明するタイミングチャート

【図6】

3ページ印刷の際の画像転送を説明するタイミングチャート

【図7】

図4のFPGAに含まれるTagライトDMAの内部構成図

【図8】

主走査の後部のラインに余白を作りラスタデータを埋め込む例を示す説明図

【図9】

副走査の後部のラインに余白を作りラスタデータを埋め込む例を示す説明図

【図10】

図4のFPGAに含まれるTagリードDMACの内部構成図

【図11】

本発明の第2実施形態に係る画像転送ユニットのFPGAのブロック図

---

フロントページの続き

(56)参考文献 特開2017-149013(JP, A)

特開2013-223195(JP, A)

特開2012-161999(JP, A)

米国特許出願公開第2003/0193680(US, A1)

(58)調査した分野(Int.Cl. , DB名)

B 41 J 5 / 30

G 06 F 3 / 12