(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5207896号

(P5207896)

(45) 発行日 平成25年6月12日(2013.6.12)

(24) 登録日 平成25年3月1日(2013.3.1)

(51) Int.Cl.

H01L 25/065 (2006.01)

H01L 25/07 (2006.01)

H01L 25/18 (2006.01)

F 1

H01L 25/08

Z

請求項の数 10 (全 23 頁)

(21) 出願番号 特願2008-239751 (P2008-239751)

(22) 出願日 平成20年9月18日 (2008.9.18)

(65) 公開番号 特開2010-73893 (P2010-73893A)

(43) 公開日 平成22年4月2日 (2010.4.2)

審査請求日 平成23年6月30日 (2011.6.30)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者 荒井 直

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 小林 敏男

長野県長野市小島田町80番地 新光電氣

工業株式会社内

審査官 今井 拓也

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

開口部を有し、該開口部の周囲にリード部が櫛歯状に延在するように成形されたリードフレームと、

前記リードフレームの開口部に、フェイスダウンの態様で配置された第1の半導体素子と、

前記第1の半導体素子上にフェイスアップの態様で搭載され、その電極パッドがワイヤを介して前記リードフレームのリード部に接続された第2の半導体素子と、

前記第1の半導体素子及び前記リードフレームをその一面側に搭載する態様で設けられた積層配線層と、

前記積層配線層上の前記リードフレームと前記第1、第2の半導体素子及び前記ワイヤを埋め込むように形成された封止樹脂層とを備え、

前記積層配線層は、前記第1の半導体素子の電極パッド及び前記リードフレームのリード部からそれぞれひき出された配線パターンが、前記積層配線層の他面側に設けられるパッド部と電気的に繋がるようにそれぞれパターン形成された複数の配線層を含み、

前記第1の半導体素子及び前記リードフレームは、前記積層配線層の一面側において同一平面上に搭載されており、かつ、前記第1の半導体素子は、前記積層配線層の配線層と直接接続されていることを特徴とする半導体装置。

## 【請求項 2】

前記リードフレームの開口部は、前記第1の半導体素子が配置される第1の開口部と、

10

20

その周囲にリード部が櫛歯状に延在するように成形された第2の開口部とを有し、

前記第2の半導体素子は、前記第1の半導体素子より大きいサイズを有し、その周辺部分が前記第1、第2の開口部間のリードフレーム部分で支持された構造を有することを特徴とする請求項1に記載の半導体装置。

#### 【請求項3】

前記第2の半導体素子は、前記第1の半導体素子より大きいサイズを有し、その周辺部分が前記リードフレームの各リード部で支持された構造を有することを特徴とする請求項1に記載の半導体装置。 10

#### 【請求項4】

前記第1の半導体素子として複数個の半導体素子が、前記リードフレームの開口部に並設されていることを特徴とする請求項1に記載の半導体装置。

#### 【請求項5】

前記第1の半導体素子の厚さは、前記リードフレームのリード部の厚さと同じであることを特徴とする請求項1に記載の半導体装置。

#### 【請求項6】

開口部を有し、該開口部の周囲にリード部が櫛歯状に延在するように成形されたリードフレームを、フィルム状の基材に貼り付けたものを用意する工程と、

前記基材上の、前記リードフレームの開口部に対応する部分に、第1の半導体素子をフェイスダウンの態様で搭載する工程と、

前記第1の半導体素子上に第2の半導体素子をフェイスアップの態様で搭載し、さらに該第2の半導体素子の電極パッドと前記リードフレームのリード部とをワイヤにより接続する工程と、 20

前記基材上の前記リードフレームと前記第1、第2の半導体素子及び前記ワイヤを埋め込むように封止樹脂で封止する工程と、

前記基材を除去する工程と、

前記第1の半導体素子の電極パッド及び前記リードフレームのリード部からそれぞれ配線パターンをひき出し、以降、所要の数の配線層を積層する工程であって、前記配線パターンが、積層後の配線層の露出する面側に設けられるパッド部と電気的に繋がるように各配線層を積層する工程とを含むことを特徴とする半導体装置の製造方法。

#### 【請求項7】

前記リードフレームを前記基材に貼り付けたものを用意する工程において、前記リードフレームを、第1の半導体素子が配置される第1の開口部と、その周囲に前記リード部が櫛歯状に延在するように成形された第2の開口部とを有するように成形し、 30

前記第1の半導体素子上に前記第2の半導体素子を搭載し、さらに該第2の半導体素子の電極パッドと前記リードフレームのリード部とをワイヤにより接続する工程において、前記第1の半導体素子より大きいサイズを有した第2の半導体素子を、その周辺部分を前記第1、第2の開口部間のリードフレーム部分上に位置合わせして搭載することを特徴とする請求項6に記載の半導体装置の製造方法。

#### 【請求項8】

前記第1の半導体素子上に前記第2の半導体素子を搭載し、さらに該第2の半導体素子の電極パッドと前記リードフレームのリード部とをワイヤにより接続する工程において、前記第1の半導体素子より大きいサイズを有した第2の半導体素子を、その周辺部分を前記リードフレームの各リード部上に位置合わせして搭載することを特徴とする請求項6に記載の半導体装置の製造方法。 40

#### 【請求項9】

前記第1の半導体素子を搭載する工程において、前記基材上の、前記リードフレームの開口部に対応する部分に、該第1の半導体素子として複数個の半導体素子を並設することを特徴とする請求項6に記載の半導体装置の製造方法。

#### 【請求項10】

前記第1の半導体素子の厚さは、前記リードフレームのリード部の厚さと同じであるこ 50

とを特徴とする請求項 6 に記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関し、特に、複数の半導体素子が積層されて配線基板に搭載された構造を有する半導体装置及びその製造方法に関する。

【0002】

以下の記述では、「配線基板」は、半導体素子を搭載する役割を果たすことから、便宜上、「半導体パッケージ」もしくは単に「パッケージ」ともいう。

【背景技術】

10

【0003】

電子機器や電子部品装置の小型化・高機能化の要求に伴い、それに用いられる半導体装置の小型化（薄型化）、高密度化、多ピン化（多端子化）が進んでいる。このような半導体装置の一つとして、リードフレーム上に半導体素子（チップ）が搭載された構造を有したものがあり、その代表的な形態として、QFN(Quad Flat Non-Leaded package)やSOPN(Small Outline Non-Leaded package)等のリードレス・パッケージがある。

【0004】

かかるQFN等のパッケージ構造を有した半導体装置を作製する場合、その基本的なプロセスとして、リードフレームのダイパッド部に半導体素子を搭載する処理（ダイ・ボンディング、又はダイ・アタッチ）、半導体素子の電極パッドとリードフレームのリード部とをボンディングワイヤにより接続する処理（ワイヤ・ボンディング）、半導体素子等を封止樹脂により封止する処理（モールディング）、リードフレームを各パッケージ単位に分割する処理（ダイシング）などを含む。モールディングの形態としては、個々のパッケージ毎に樹脂封止を行う個別モールディングと、複数個のパッケージ単位で樹脂封止を行う一括モールディングがある。

20

【0005】

かかる従来技術に関連する技術としては、例えば、特許文献1に記載された半導体装置及びその製造方法がある。また、特許文献2に記載された半導体装置及びその製造方法、特許文献3に記載された半導体装置、特許文献4に記載された半導体装置がある。

【特許文献1】特開2006-261509号公報

30

【特許文献2】特開2008-91418号公報

【特許文献3】特開2002-83902号公報

【特許文献4】特開昭60-182731号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

QFN等のパッケージ構造を有した半導体装置のプロセスでは、銅(Cu)等の金属板をプレス加工等により所要の形状に成形してリードフレームを得るようにしているため、このリードフレームの一部に画定されるリード部（外部接続端子）の数は、リードフレームの加工技術（どれくらいのパターン幅でどれくらいの数のリード部を形成することが可能であるかの技術レベル）に依存する。

40

【0007】

つまり、現状の技術では、リードフレームのリード部（半導体装置の外部接続端子）の数がリードフレームを加工可能な範囲に制限されるといった課題があった。

【0008】

その一方で、近年のダウンサイジングの進化の中で集積度が高まることにより入出力数が増加し、より多くの外部接続端子を必要とするようになっている。特に、MPU（マイクロプロセッサユニット）等の能動的なICチップを搭載するパッケージでは、電源電流の増大も著しく、それに応じてチップに電力を供給するための外部接続端子の数も多く割り当てられ、パッケージ全体の端子数の半分以上を占めている。つまり、信号の入出力

50

用として使用できる端子は残りの半分以下に限られている。また、パッケージの小型化により、パッケージに組み込める外部接続端子の数は限られてくるため、従来のパッケージでは十分な数の外部接続端子を確保していくのは困難となっているのが現状である。

#### 【0009】

本発明は、かかる従来技術における課題に鑑み創作されたもので、高密度化等の要求に伴い外部接続端子の数を増やす必要が生じた場合でもその要求に十分応えることができる半導体装置及びその製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0010】

上述した従来技術の課題を解決するため、本発明の一形態に係る半導体装置は、開口部を有し、該開口部の周囲にリード部が櫛歯状に延在するように成形されたリードフレームと、前記リードフレームの開口部に、フェイスダウンの態様で配置された第1の半導体素子と、前記第1の半導体素子上にフェイスアップの態様で搭載され、その電極パッドがワイヤを介して前記リードフレームのリード部に接続された第2の半導体素子と、前記第1の半導体素子及び前記リードフレームをその一面側に搭載する態様で設けられた積層配線層と、前記積層配線層上の前記リードフレームと前記第1、第2の半導体素子及び前記ワイヤを埋め込むように形成された封止樹脂層とを備え、前記積層配線層は、前記第1の半導体素子の電極パッド及び前記リードフレームのリード部からそれぞれひき出された配線パターンが、前記積層配線層の他面側に設けられるパッド部と電気的に繋がるようにそれぞれパターン形成された複数の配線層を含み、前記第1の半導体素子及び前記リードフレームは、前記積層配線層の一面側において同一平面上に搭載されており、かつ、前記第1の半導体素子は、前記積層配線層の配線層と直接接続されていることを特徴とする。10 20

#### 【0011】

この形態に係る半導体装置の構成によれば、パッケージとしての役割を果たす積層配線層上でリードフレームの開口部にそれぞれフェイスダウン及びフェイスアップの態様で第1及び第2の半導体素子が積層配置され、第2の半導体素子の電極パッドとリードフレームのリード部とがワイヤを介して接続されると共に、積層配線層上で各半導体素子（ワイヤを含む）及びリードフレームを埋め込むように封止樹脂で封止されている。さらに、積層配線層を構成する各配線層は、第1の半導体素子の電極パッドとリードフレームのリード部からそれぞれひき出された配線パターンが、積層配線層の他面側（外部接続端子が接合される面側）に設けられるパッド部と電気的に繋がるようにそれぞれパターン形成されている。30

#### 【0012】

これによって、従来形のパッケージでは実現できなかったファンアウト構造のパッケージ（積層配線層）を実現することができる。従って、高密度化等の要求に伴い外部接続端子の数を増やす必要が生じた場合でも、従来のようにリードフレームを加工可能な範囲に制限されることなく、また従来形のパッケージと同じサイズで、その要求に十分応えることができる。

#### 【0013】

また、本発明の他の形態によれば、上記の形態に係る半導体装置を製造する方法が提供される。この半導体装置の製造方法は、開口部を有し、該開口部の周囲にリード部が櫛歯状に延在するように成形されたリードフレームを、フィルム状の基材に貼り付けたものを用意する工程と、前記基材上の、前記リードフレームの開口部に対応する部分に、第1の半導体素子をフェイスダウンの態様で搭載する工程と、前記第1の半導体素子上に第2の半導体素子をフェイスアップの態様で搭載し、さらに該第2の半導体素子の電極パッドと前記リードフレームのリード部とをワイヤにより接続する工程と、前記基材上の前記リードフレームと前記第1、第2の半導体素子及び前記ワイヤを埋め込むように封止樹脂で封止する工程と、前記基材を除去する工程と、前記第1の半導体素子の電極パッド及び前記リードフレームのリード部からそれぞれ配線パターンをひき出し、以降、所要の数の配線層を積層する工程であって、前記配線パターンが、積層後の配線層の露出する面側に設け40 50

られるパッド部と電気的に繋がるように各配線層を積層する工程とを含むことを特徴とする。

**【0014】**

本発明に係る半導体装置及びその製造方法の他の構成上の特徴及びそれに基づく有利な利点等については、以下に記述する発明の実施の形態を参照しながら説明する。

**【発明を実施するための最良の形態】**

**【0015】**

以下、本発明の好適な実施の形態について、添付の図面を参照しながら説明する。

**【0016】**

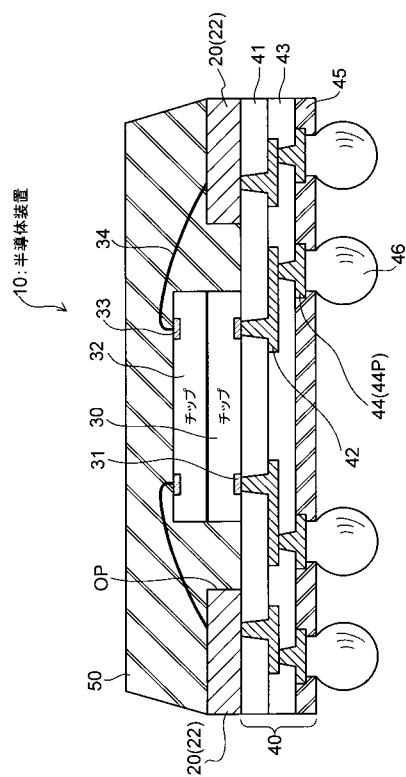

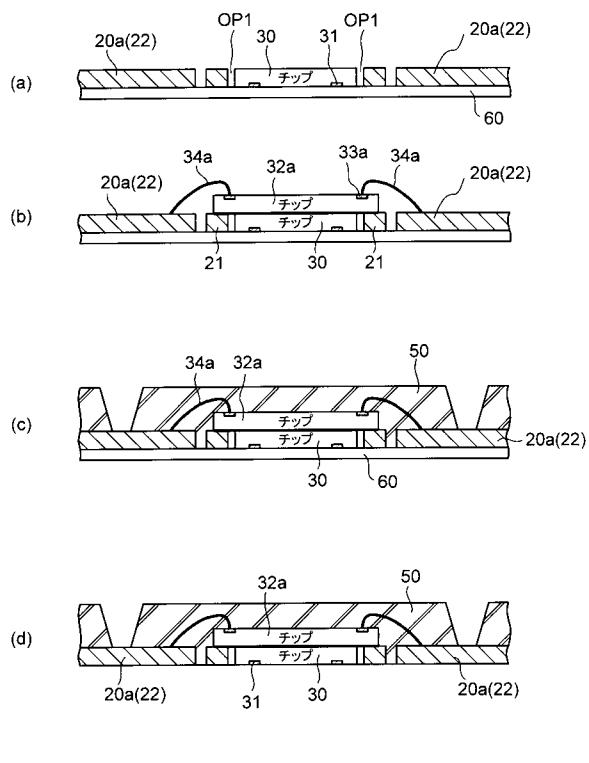

(第1の実施形態及びその変形例...図1～図6参照)

10

図1は本発明の第1の実施形態に係る半導体装置の構成を断面図の形態で示したものである。

**【0017】**

本実施形態に係る半導体装置10は、基本的には、開口部OPを備えたリードフレーム20と、このリードフレーム20の開口部OPに2段に積層配置されたICチップ(代表的にはシリコン(Si)チップ)30及び32と、各チップ30,32(直接的には下側のチップ30)及びリードフレーム20を搭載する様で設けられた積層配線層40と、この積層配線層40上で各チップ30,32及びリードフレーム20を埋め込むように形成された封止樹脂(層)50とを備えて構成されている。各チップ30,32は、後述するようにデバイスプロセスを用いてシリコンウエハに複数のデバイスが作り込まれた当該ウエハを各デバイス単位にダイシング(個片化)して得られたシリコンチップ(「ダイ」ともいう。)である。

20

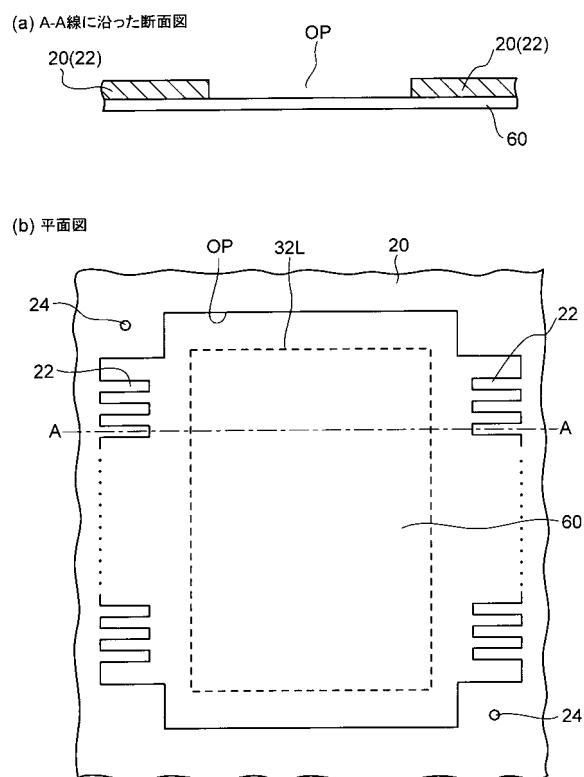

**【0018】**

リードフレーム20は、搭載される各チップ30,32の大きさ(ダイサイズ)よりも十分に大きな開口部OPを備えており、図2(b)に示すように所要の形状にパターニング形成されている。図2(b)の例では、最終的に個々の半導体装置10として分割されるべき部分に対応するリードフレーム部分のみを示しており、破線で囲んだ矩形状の部分32Lは、上側に配置されるチップ32の外形(実装エリア)を表している。リードフレーム20は、開口部OPの周囲の少なくとも一部分(図2(b)の例では左右方向に対向する2辺)において所要の数のリード部22が櫛歯状に延在するように成形されている。個々のリード部22は、ポンディングワイヤ34(図1)を介してチップ32の対応する電極パッド33に接続されるインナーリード部と、後述する外部接続端子に接続されるアウターリード部とから構成されている。また、リードフレーム20の開口部OPの周辺近傍の部分には、その対角線方向に対向する2箇所に、ダイ・アタッチの際の位置合わせ用として利用される小さな孔24が設けられている。

30

**【0019】**

このリードフレーム20は、上側に配置されるチップ32の電極パッド33を外部接続端子に接続するための中継端子としての役割の他に、本装置10(特定的には積層配線層40)の反りを防止するための補強材としても利用される。このため、リードフレーム20は、十分な機械的強度(剛性)を有した材料で熱膨張係数の小さいものから形成されているのが望ましい。例えば、銅(Cu)又はその合金(Cu-鉄(Fe)-燐(Ph)等)や、鉄(Fe)又はその合金(42%ニッケル(Ni)-Fe合金等)などを用いることができる。

40

**【0020】**

本装置10に内蔵される各チップのうち下側に配置されるチップ30は、その電極パッド(端子)31が形成されている側の面を下にしたフェイスダウンの態様で実装され、上側に配置されるチップ32は、その電極パッド(端子)33が形成されている側の面を上にしたフェイスアップの態様で実装されている。つまり、各チップ30,32は、各々の裏面を背中合わせにした状態で積層されている。

**【0021】**

50

以下の記述では、便宜上、フェイスダウンの態様で実装されるチップ30を「下側チップ」、フェイスアップの態様で実装されるチップ32を「上側チップ」ともいう。

#### 【0022】

本実施形態では、上側チップ32は、最大でも下側チップ30と同じ大きさ（ダイサイズ）のものを選定している。下側チップ30は、積層配線層40に直接搭載される形で実装されており、その電極パッド31から直接ひき出された配線パターンが積層配線層40の最上層の配線層を構成している。一方、上側チップ32の電極パッド33は、ボンディングワイヤ34を介してリードフレーム20のリード部22（インナーリード部）に接続されている。

#### 【0023】

積層配線層40は、図示のようにチップ30, 32を搭載する役割を果たすことから、機能的には配線基板（パッケージ）と同等である。この積層配線層40は、所要の数の配線層（図示の例では、配線層42, 44）がそれぞれ絶縁層41, 43を介在させて積層され、各絶縁層41, 43に形成されたビアホールに充填された導体（配線層42, 44）を構成する材料の一部分）を介して層間接続された構造を有している。積層配線層40の最上層の配線層（図示の例では配線層42）は、搭載された下側チップ30の電極パッド31から直接ひき出されている。つまり、当該電極パッド31に接続されるように配線層42がパターン形成されている。配線層42, 44の材料としては典型的に銅（Cu）が用いられ、絶縁層41, 43の材料としてはエポキシ系樹脂が用いられる。

#### 【0024】

また、積層配線層40の最下層の配線層（図示の例では配線層44）には、所要の箇所にパッド部44Pが画定されている。パッド部44Pは、リードフレーム20の開口部OP（チップ搭載エリア）の下方に対応する面だけでなくその外側エリアに対応する面にも配置されている。さらに、積層配線層40のパッド部44Pを露出させて表面を覆うように保護膜としてのソルダレジスト層45が形成されている。

#### 【0025】

このソルダレジスト層45から露出するパッド部44Pには、本装置10をマザーボード等の実装用基板に実装する際に使用されるはんだボールやピン等の外部接続端子46が接合されるので、パッド部（Cu）44P上にニッケル（Ni）めっき及び金（Au）めっきをこの順に施しておく。これは、外部接続端子46を接合したときのコンタクト性を良くするためと、パッド部44Pを構成するCuとの密着性を高め、CuがAu層中へ拡散するのを防止するためである。つまり、パッド部44PはCu / Ni / Auの3層構造となっている。

#### 【0026】

なお、図示の例ではパッド部44P上に外部接続端子46を設けているが、これは必ずしも設ける必要はない。要は、必要なときに外部接続端子を接合できるように当該パッド部44Pが露出していれば十分である。

#### 【0027】

このように積層配線層40は、搭載される下側チップ30の電極パッド31及びリードフレーム20のリード部22（このリード部22にワイヤ34を介して上側チップ32の電極パッド33が接続されている）と、マザーボード等に実装する際に用いられる外部接続端子46とを整合させる（つまり、再配線を行う）役割を果たし、図示のように、外部接続端子46のエリアがチップ搭載エリアの周囲に拡張された「ファンアウト」の形態を有している。つまり、外部接続端子46は、本装置10の実装面側の全面に亘り「グリッドアレイ」の態様で設けられている。

#### 【0028】

積層配線層40上で各チップ30, 32及びリードフレーム20を埋め込むように形成された封止樹脂（層）50は、各チップ30, 32と積層配線層40の一体的な構造を保持し、補強材として機能するリードフレーム20と協働してこの一体的な構造を固定化するためのものである。封止樹脂50の材料としては、例えば、モールド樹脂として一般に

使用されている熱硬化性エポキシ樹脂や、アンダーフィル樹脂として一般に使用されている液状エポキシ樹脂等を用いることができる。

#### 【0029】

次に、本実施形態に係る半導体装置10(図1)を製造する方法について、その製造工程の一例を示す図2～図4を参照しながら説明する。

#### 【0030】

先ず最初の工程では(図2参照)、搭載すべき下側チップ30の大きさ(ダイサイズ)に応じてそのサイズよりも十分に大きな開口部OPを備えたリードフレーム20を用意する。このリードフレーム20を構成する材料としては、上述したように十分な機械的強度を有し、さらに熱膨張係数の小さい材料であれば十分である。例えば、銅(Cu)の薄板を用意し、この金属(Cu)板をプレス加工もしくはエッティング加工により、図2(b)に示すように開口部OPの周囲の対向する2辺において所要の数のリード部22が櫛歯状に延在するように成形する。図示の例では、簡単化のために1つの開口部OP(最終的に個々の半導体装置10として分割されるべき部分に対応するリードフレーム部分)のみを示しているが、実際には複数の開口部OPがアレイ状に配列されている。10

#### 【0031】

次に、このようにして用意されたリードフレーム20を、片面に粘着剤が塗布されたフィルム状の基材(例えば、ポリイミド樹脂、ポリエステル樹脂等からなるテープ)60の粘着剤が塗布されている側の面に貼り付ける。このテープ60は、下側チップ30を規定の位置に搭載(保持)するための一時的な基材としての役割を果たす。また、テープ60は、後の段階で行うパッケージの組立て工程においてモールディングの際に封止樹脂のフレーム裏面への漏れ出し(「モールドフラッシュ」ともいう。)を防止するための部材としても利用される。20

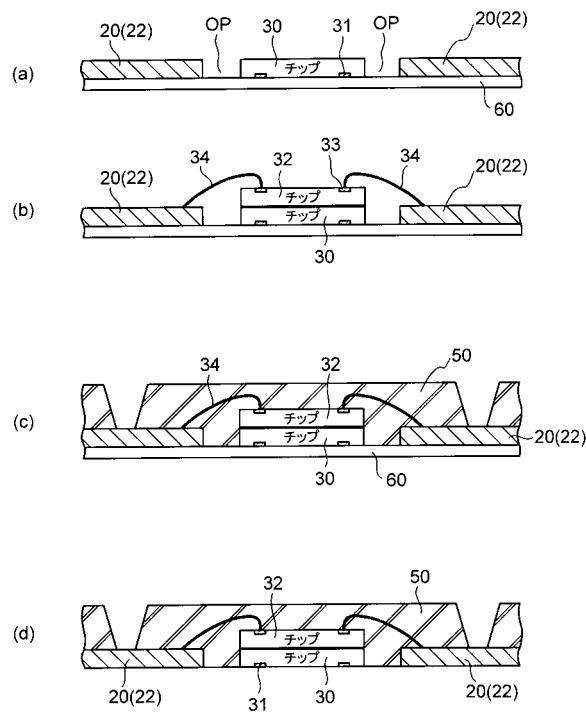

#### 【0032】

次の工程では(図3(a)参照)、リードフレーム20のテープ60が貼り付けられている側の面を下にして保持用の治具(図示せず)で保持し、あらかじめ別工程で作製しておいたシリコンチップ(下側チップ30)を、その電極パッド31が形成されている側の面を下にしたフェイスダウンの態様で、リードフレーム20の開口部OPに対応する部分のテープ60上(粘着剤が塗布されている側の面)に搭載する(ダイ・アタッチ)。本実施形態では、搭載するチップ30の厚さをリードフレーム20の厚さと同じになるよう選定している。30

#### 【0033】

例えば、12インチの大きさのシリコンウェハに対し、その一方の面側に所要のデバイスプロセスを施して複数のデバイスをアレイ状に作り込み、そのデバイスが形成されている側の面に窒化シリコン(SiN)やリンガラス(PSG)等からなるパッシベーション膜を形成し、各デバイス上に所要のパターンで形成されたアルミニウム(Al)の配線層の一部分に画定される電極パッド31に対応する部分のパッシベーション膜をレーザ等により除去し、さらにウェハを所定の厚さ(リードフレーム20の厚さと同じ厚さ)に薄く研削した後、ダイサー等により各デバイス単位に個片化することで、一方の面に電極パッド31が露出したチップ(ダイ)30を得ることができる。40

#### 【0034】

各デバイス単位に個片化する際には、そのウェハを、ダイシング用フレームに支持されたダイシング用テープ上に、ダイ・アタッチ・フィルムを介在させて、ウェハのデバイスが作り込まれている側と反対側の面を接着させて搭載し、ダイサーのブレードにより、各デバイスの領域を画定する線に沿ってウェハを切断した後、切断分割された各チップ30をピックアップする。その際、個々のチップ30にはダイ・アタッチ・フィルムが付いているが、図3(a)の例ではその図示を省略している。

#### 【0035】

下側チップ30をテープ60上の規定の位置に搭載する際には、あらかじめリードフレーム20の所定の位置に設けておいた位置合わせ用の孔24(図2(b)参照)を顕微鏡50

等で読み取り、その検出位置に従って当該チップ30を搭載する。

#### 【0036】

次の工程では(図3(b)参照)、あらかじめ別工程で作製しておいたシリコンチップ(上側チップ32)を、その電極パッド33が形成されている側の面を上にしたフェイスアップの態様で、下側チップ30上に搭載する。その際、各チップ30,32の裏面にはダイ・アタッチ・フィルムが付いているので、その粘着性を利用して各チップ30,32を背中合わせにした状態で規定の位置に保持することができる。搭載する上側チップ32は、下側チップ30の場合と同様のデバイスプロセスを用いて作製することができる。

#### 【0037】

さらに、上側チップ32の電極パッド(端子)33とリードフレーム20の対応するリード部22(インナーリード部)とをボンディングワイヤ34により電気的に接続する。これによって、上側チップ32が実装されたことになる。

#### 【0038】

次の工程では(図3(c)参照)、個別モールディングにより、テープ60上のリードフレーム20及び搭載された各チップ30,32(ワイヤ34を含む)を埋め込むように封止樹脂50で封止する。これは、特に図示はしないが、モールディング金型(1組の上型及び下型)の下型上に対象物(図3(b)の構造体)を載せ、上方から上型で挟み込むようにして、封止樹脂50を充填しながら加熱及び加圧処理することにより行われる。

#### 【0039】

封止樹脂50の材料としては、モールド樹脂として一般に使用されている熱硬化性エポキシ樹脂を用いることができる。また、その形態としては、液状の樹脂に限らず、タブレット状の樹脂や粉末状の樹脂でもよい。封止樹脂50を充填する方法としては、トランスファモールドやインジェクションモールド等の方法を用いて実施することができる。

#### 【0040】

なお、封止処理中、テープ60は、封止樹脂50のフレーム裏面への漏れ出し(モールドフラッシュ)を防止する役割を果たす。所要の封止処理を終えると、封止樹脂50で覆われた構造体(図3(c))をモールディング金型から取り出す。

#### 【0041】

次の工程では(図3(d)参照)、リードフレーム20及びチップ30,32を搭載する一時的な基材として利用したポリイミド樹脂等のテープ60(図3(c))を剥離し、除去する。この段階では、下側チップ30の電極パッド31が形成されている側の面に、剥離したテープ60に塗布されていた粘着剤の一部が残存している可能性がある。

#### 【0042】

そこで、その残存している可能性のある粘着剤を、例えば、アッシング(酸素プラズマを用いたドライエッキング)で除去する。これによって、リードフレーム20のリード部22(アウターリード部)と共に下側チップ30の電極パッド31が露出する。

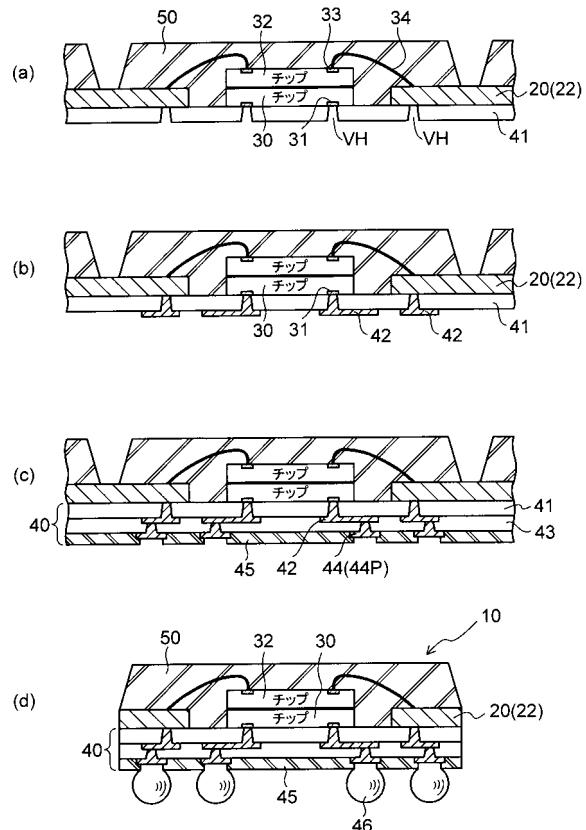

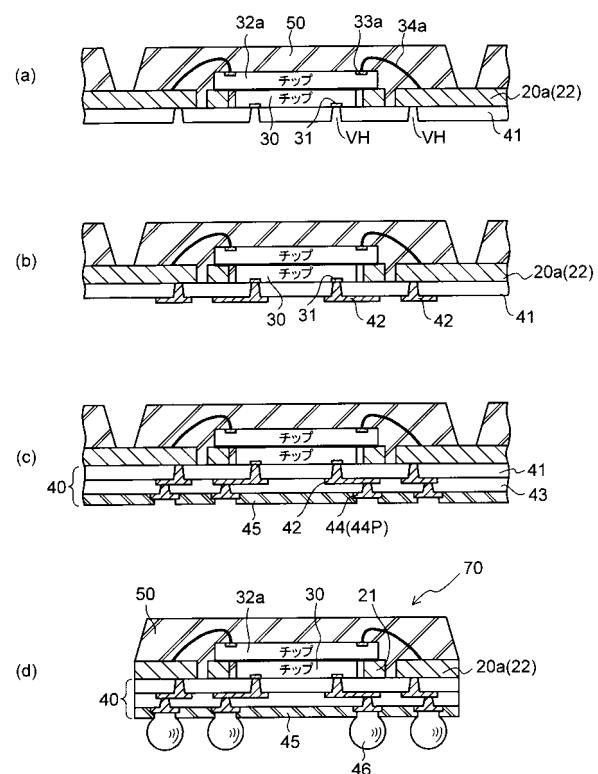

#### 【0043】

次の工程では(図4(a)参照)、下側チップ30の電極パッド31とリードフレーム20のリード部22(アウターリード部)が露出している側の面に絶縁層41を形成し、その所定の箇所に開口部VHを形成する。例えば、フォトリソグラフィにより、チップ30の電極パッド31が形成されている側の面に感光性のポリイミド樹脂を塗布し、このポリイミド樹脂のソフトベーク(プリベーク)処理を行った後、マスク(図示せず)を用いて露光及び現像(ポリイミド樹脂層のパターニング)を行い、さらにハードベーク(ポストベーク)処理を行い、図示のように所定の箇所に開口部VHを有する絶縁層(ポリイミド樹脂層)41を形成する。その際、絶縁層41のパターニングは、チップ30の電極パッド31及びリードフレーム20のリード部22の形状(配列)に従うように行う。従つて、露光及び現像を行うと、図示のようにチップ30の電極パッド31とリードフレーム20のリード部22に対応する部分のポリイミド樹脂層(絶縁層)41が除去されて、それぞれ電極パッド31及びリード部22に到達する開口部VHが形成される。

#### 【0044】

10

20

30

40

50

次の工程では(図4(b)参照)、セミアディティブ法などにより、それぞれの開口部VHを充填してチップ30の電極パッド31及びリードフレーム20のリード部22に接続される所要形状の配線層(パターン)42を形成する。具体的な一例を説明すると、以下の通りである。

#### 【0045】

先ず、絶縁層41が形成されている側の全面に、スパッタリングや無電解めっき等によりシード層を形成する。例えば、全面にクロム(Cr)又はチタン(Ti)をスパッタリングにより堆積させ(密着金属層:Cr層又はTi層)、さらにその上に銅(Cu)をスパッタリングにより堆積させることで、2層構造のシード層を形成することができる。次いで、シード層の表面(Cu層表面)の脱水ペークを行い、液状のフォトレジストを塗布して乾燥させた後、マスク(図示せず)を用いて露光及び現像(フォトレジストのパターニング)を行い、レジスト層を形成する。このフォトレジストのパターニングは、形成すべき配線パターンの形状に従うように行う。液状のフォトレジストの代わりに、感光性のドライフィルムをラミネートして、そのパターニングを行ってもよい。

10

#### 【0046】

次に、このパターニングされたレジスト層をマスクにして、シード層を給電層として利用した電解Cuめっきにより、所要の形状にCuの配線層(再配線層)42を形成する。この後、有機溶剤を含む剥離液を用いてフォトレジストを除去する。フォトレジストの代わりにドライフィルムを使用した場合には、水酸化ナトリウム(NaOH)やモノエタノールアミン系などのアルカリ性の薬液を用いてドライフィルムを剥離し、除去する。

20

#### 【0047】

さらに、ウエットエッティングにより、露出しているシード層を除去する。この場合、先ずCuを溶かすエッティング液でシード層の上層部分のCu層を除去し、次にCr又はTiを溶かすエッティング液で下層部分の密着金属層(Cr層又はTi層)を除去する。これによつて、図示のように絶縁層41が露出する。この後、所定の表面洗浄等を行う。

#### 【0048】

なお、Cuを溶かすエッティング液を用いた際に、配線層42を構成するCuも除去されてそのパターンが断線するよう見えるが、実際にはかかる不都合は生じない。その理由は、上述したようにシード層の上層部分はCuのスパッタリング等により形成されるためその膜厚はミクロンオーダー以下であるのに対し、配線層42は電解Cuめっきにより形成されるためその膜厚は少なくとも $10\mu m$ 程度であるので、シード層のCuは完全に除去されても、配線層42(Cu)についてはその表層部分のみが除去される程度であり、配線パターンが断線することはないからである。

30

#### 【0049】

次の工程では(図4(c)参照)、図4(a)及び(b)の工程で行った処理と同様の処理(ビルトアップ法)を繰り返して所要の層数となるまで、絶縁層43と配線層44を交互に積み重ねて積層する。さらに、最外層の配線層44の所要の箇所に画定されたパッド部44Pが露出するように全面を覆つてソルダレジスト層45を形成し、このソルダレジスト層45から露出しているパッド部44PにNi/Auめっきを施して、積層配線層40を形成する。

40

#### 【0050】

最後の工程では(図4(d)参照)、ダイサー等により、個々のデバイス(積み重ねられた各チップ30,32とその周囲を囲むように配置されたリードフレーム20のリード部22を含む部分)単位に分割し、さらに、ソルダレジスト層45から露出しているパッド部44P(図4(c))に、表面処理剤としてのフラックスを塗布した後、外部接続端子46として用いるはんだボールを搭載し、240~260程度の温度でリフローして固定する。その後、表面を洗浄してフラックスを除去する。

#### 【0051】

本工程では、ダイシングを行つてから個々のデバイスに外部接続端子46を接合しているが、これとは逆の順序で、各デバイスにそれぞれ外部接続端子46を接合してから個々

50

のデバイスに分割（個片化）するようにしてもよい。

#### 【0052】

以上の工程により、本実施形態の半導体装置10（図1）が製造されたことになる。

#### 【0053】

以上説明したように、第1の実施形態に係る半導体装置10（図1）及びその製造方法（図2～図4）によれば、パッケージとしての役割を果たす積層配線層40上でリードフレーム20の開口部OPにそれぞれフェイスダウン、フェイスアップの態様で半導体チップ30, 32を積層配置し、上側チップ32の電極パッド33とリードフレーム20のリード部22（インナーリード部）とをボンディングワイヤ34で接続すると共に、積層配線層40上で各チップ30, 32（ワイヤ34を含む）及びリードフレーム20を埋め込むように封止樹脂50で封止している。さらに、下側チップ30の電極パッド31とリードフレーム20のリード部22（アウターリード部）からそれぞれ配線パターンをひき出し、積層配線層40による再配線により、外部接続端子46（もしくはパッド部44P）がチップ搭載エリアの下方に対応する面だけではなくその外側エリアに対応する面にも配置されるように構成されている。10

#### 【0054】

かかる構成により、従来のパッケージでは実現できなかったファンアウト構造のパッケージ（積層配線層40）を実現することができる。従って、高密度化・多端子化の要求に伴い外部接続端子の数を増やす必要が生じた場合でも、従来のようにリードフレームを加工可能な範囲（加工技術）に制限されることなく、また従来形のものと同じパッケージサイズで、高密度化等の要求に十分応えることができる。20

#### 【0055】

また、パッケージ（積層配線層40）上に搭載したチップ30, 32の周囲を囲むように十分な機械的強度を有したリードフレーム20を配置し、各チップ30, 32と共に封止樹脂50で埋め込んで固定化しているので、パッケージ全体として剛性が高められている。これにより、例えば、本装置10をインターポーザ等に実装する際に、その隙間に充填されるアンダーフィル樹脂の熱硬化に伴いその界面に熱膨張係数の違いに応じた応力が発生した場合でも、リードフレーム20の介在によりパッケージ全体が補強されているので、パッケージが「反る」といった不都合は生じない。30

#### 【0056】

また、積層配線層40を構成する各配線層42, 44を形成するにあたり、薄膜配線ルール（ウエハレベルパッケージのプロセス）を使用できるので、配線の微細化が容易となり、層数を可及的に減らすことができる。これは、パッケージの薄型化、ひいては小型化に寄与する。

#### 【0057】

上述した実施形態に係る半導体装置10の製造方法（図2～図4）では、図4（a）の工程において絶縁層41における開口部VHの形成をフォトリソグラフィにより行う場合を例にとって説明したが、他の方法を用いて開口部VHを形成することも可能である。その方法として、例えば、炭酸ガスレーザ、エキシマレーザ等を用いることができる。ただし、チップ30の電極パッド31はアルミニウム（A1）配線の一部からなり、その上にチタン（Ti）/クロム（Cr）の導体層がスパッタリング等で形成されているため、レーザを使用した場合、そのレーザ照射によりチップ30の電極パッド（A1）31がダメージを受けるおそれがある。40

#### 【0058】

従って、これを回避するために、チップ30の電極パッド31上（Ti/Cr層上）に予め銅（Cu）等からなるバンプを形成しておく。このバンプの介在により、レーザ照射による影響が電極パッド（A1）31に直接及ぼされるのを回避することができ、絶縁層41の所定の箇所に開口部VHを形成することが可能となる。また、既にCuバンプ等が形成されているため、開口部VHを形成した後の工程（図4（b））では、シード層として形成すべき導体層は、例えば、無電解めっきによる銅（Cu）層のみで足りる。50

**【0059】**

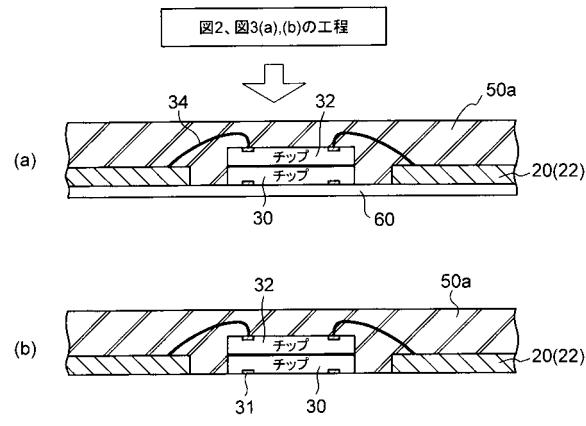

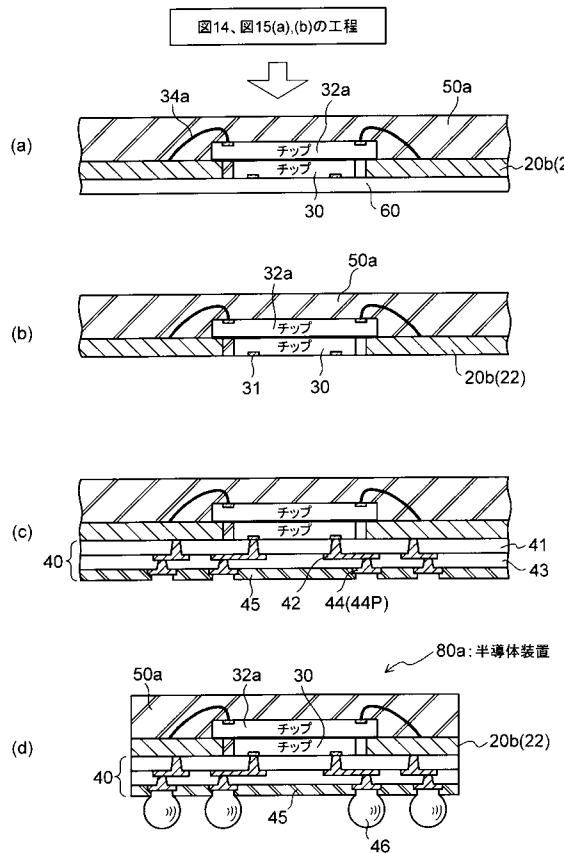

また、上述した実施形態に係る半導体装置10の製造方法では、図3(c)の工程においてテープ60上のリードフレーム20及び各チップ30,32(ワイヤ34を含む)の封止処理を個別モールディングにより行う場合を例にとって説明したが、この個別モールディングに代えて、一括モールディングにより所要の樹脂封止を行うようにしてもよい。その場合の実施形態を図5に示す。

**【0060】**

図5は、図1の半導体装置10の一変形例に係る半導体装置10aの製造工程をしたものである。

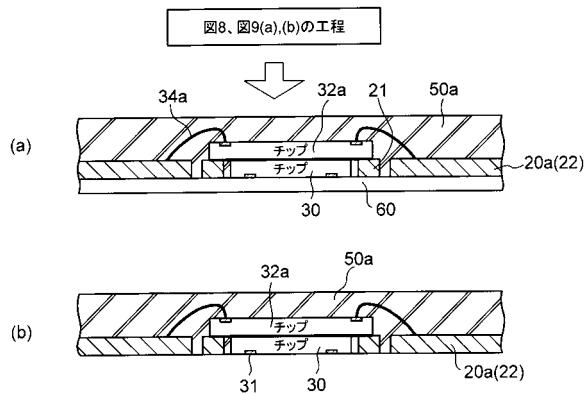

**【0061】**

先ず、上述した実施形態における図2、図3(a)及び(b)の工程と同じ工程を経た後、最初の工程では(図5(a)参照)、一括モールディングにより、複数個のパッケージ単位で、テープ60上のリードフレーム20(リード部22)及び搭載された各チップ30,32(ワイヤ34を含む)を埋め込むように封止樹脂50aで封止する。この封止処理は、図3(c)の工程で行った処理と同様にして行うことができる。所要の封止処理を終えると、封止樹脂50aで覆われた構造体(図5(a))をモールディング金型から取り出す。

**【0062】**

次の工程では(図5(b)参照)、図3(d)の工程で行った処理と同様にして、テープ60(図5(a))を剥離し、除去する。さらに、下側チップ30の電極パッド31が形成されている側の面に残存している可能性のある粘着剤(テープ60に塗布されていたもの)を、アッティング等により除去する。

**【0063】**

次の工程では(図5(c)参照)、下側チップ30の電極パッド31とリードフレーム20のリード部22(アウターリード部)が露出している側の面に、図4(a)~(c)の工程で行った処理と同様にして、積層配線層40(絶縁層41、配線層42、絶縁層43、配線層44(Ni/Auめっきを施したパッド部44P)、ソルダレジスト層45)を形成する。

**【0064】**

最後の工程では(図5(d)参照)、図4(d)の工程で行った処理と同様にして、ダイサー等により、個々のデバイス(積層された各チップ30,32とその周囲を囲むように配置されたリードフレーム20のリード部22を含む部分)単位に分割し、さらに、ソルダレジスト層45から露出しているパッド部44P(図5(c))にはんだボール(外部接続端子46)を接合する。あるいは、これとは逆の順序で、各デバイスにそれぞれ外部接続端子46を接合してから個々のデバイスに分割するようにしてもよい。

**【0065】**

以上の工程により、本実施形態の半導体装置10a(図5(d))が製造されたことになる。図示のように本実施形態の半導体装置10aは、基本的に図1の半導体装置10と同じ構成を有しており、モールディングの違い(金型の違い)に起因した構造のみ相違している。すなわち、図1の実施形態では、封止樹脂(層)50は断面的に見て台形状に形成されているのに対し、本実施形態では、封止樹脂(層)50aは断面的に見て矩形状に形成されている点で相違する。

**【0066】**

本実施形態によれば、第1の実施形態(図1~図4)で得られた効果に加え、さらに、一括モールディングにより複数個のパッケージ単位で樹脂封止を行っているので、パッケージの組立ての効率化を図ることができるというメリットがある。

**【0067】**

また、上述した第1の実施形態に係る半導体装置10(図1)の構成では、下側チップ30上に1個の上側チップ32を搭載する場合を例にとって説明したが、本発明の要旨からも明らかなように、搭載する上側チップの個数が1個に限定されることはもちろんで

10

20

30

40

50

ある。必要に応じて、積層方向のスペースが許容される範囲内で2個以上の上側チップをフェイスアップの態様で多段的に実装することも可能である。その場合の実施形態を図6に示す。

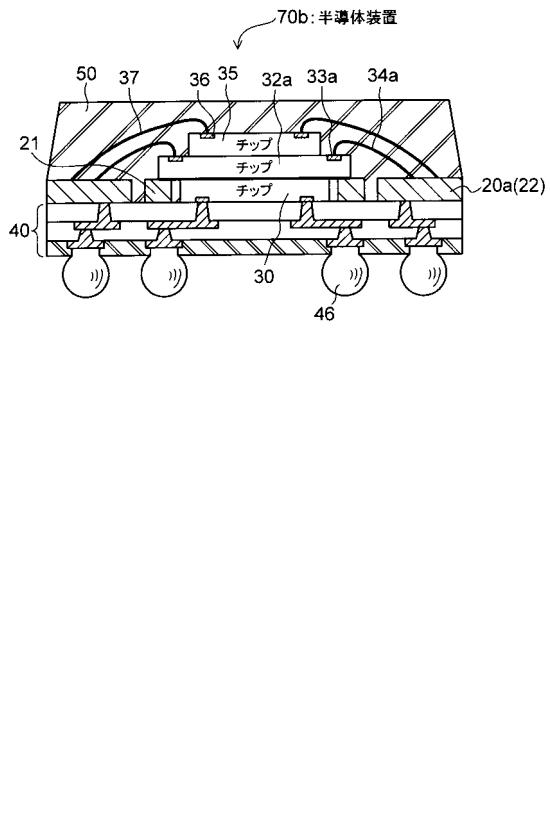

#### 【0068】

図6は、図1の半導体装置10の他の変形例に係る半導体装置10bの構成を断面図の形態で示したものである。

#### 【0069】

本実施形態に係る半導体装置10bは、図1に示した半導体装置10の構成と比べて、フェイスダウンの態様で実装された下側チップ30上に、この下側チップ30よりも大きいダイサイズを有した上側チップ32aをフェイスアップの態様で実装し、この上側チップ32aの電極パッド33aをボンディングワイヤ34aを介してリードフレーム20の一部のリード部22（インナーリード部）に接続した点、さらにこの上側チップ32a上に、この上側チップ32aよりも小さいダイサイズを有した上側チップ35をフェイスアップの態様で実装し、この上側チップ35の電極パッド36をボンディングワイヤ37を介してリードフレーム20の他のリード部22（インナーリード部）に接続した点で相違している。他の構成については、図1の半導体装置10と同じであるのでその説明は省略する。10

#### 【0070】

本実施形態の半導体装置10bは、上述した第1の実施形態に係る製造方法（図2～図4）と同様にして製造することができる。ただし、本実施形態の場合、図3（b）の工程において、上側チップ32a及び35を順次搭載したときに、上段の上側チップ35の裏面に付着しているダイ・アタッチ・フィルムの粘着性を利用して下段の上側チップ32a上で規定の位置を保持している。20

#### 【0071】

このように上側チップ32a, 35を多段的に実装することで、半導体装置10bとしての機能を更に高めることができる（高機能化）。

#### 【0072】

なお、上述した第1の実施形態及びその変形例では、上側チップ32（32a, 35）の電極パッド33（33a, 36）を外部接続端子46に接続するための中継端子として用いられるリードフレーム20のリード部22を、図2（b）に示したように開口部OPの周囲の対向する2辺にのみ設けた場合を例にとって説明したが、リード部22の配置形態がこれに限定されないことはもちろんである。例えば、開口部OPの周囲のそれぞれ対向する各2辺（=4辺）にリード部22を設けるようにしてもよい。30

#### 【0073】

このようにリード部22の数を増やすことで、更なる高密度化、ひいては多ピン化（多端子化）の要求に応えることが可能となる。

#### 【0074】

（第2の実施形態及びその変形例…図7～図12参照）

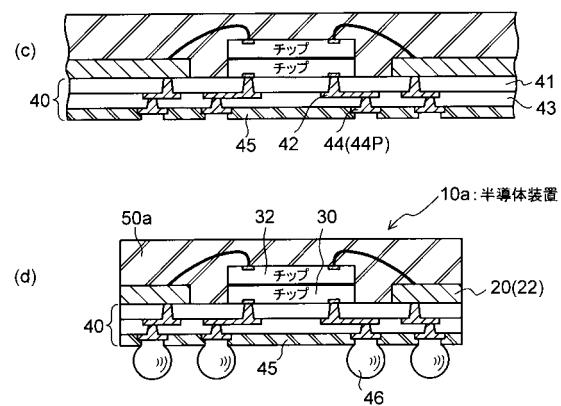

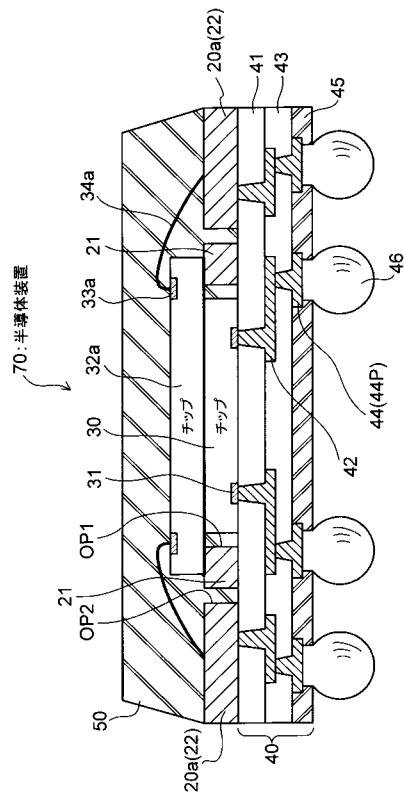

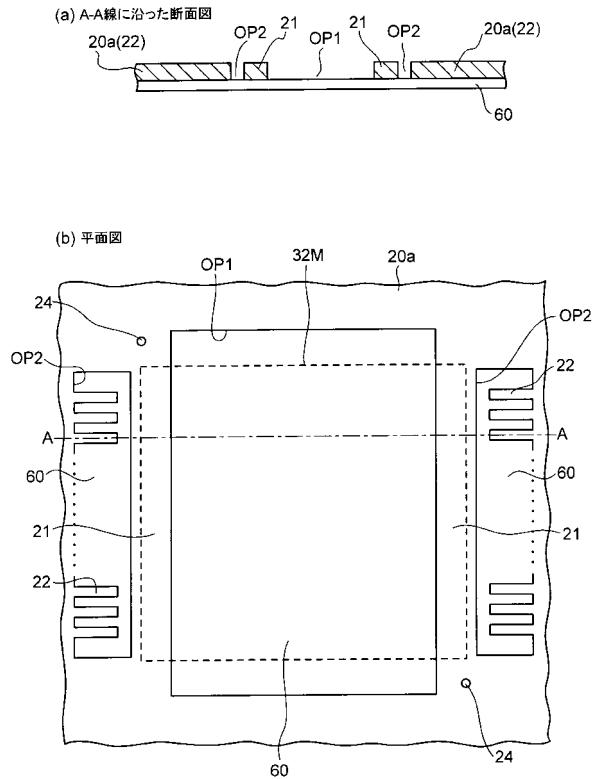

図7は本発明の第2の実施形態に係る半導体装置の構成を断面図の形態で示したものである。40

#### 【0075】

本実施形態に係る半導体装置70は、第1の実施形態に係る半導体装置10（図1）の構成と比べて、下側チップ30よりも大きいダイサイズを有した上側チップ32aを実装し、この上側チップ32aの電極パッド33aをボンディングワイヤ34aを介してリードフレーム20aのリード部22（インナーリード部）に接続した点、このリードフレーム20aに、下側チップ30が配置される開口部OP1とリード部22が画定される開口部OP2を別々に設けた点、上側チップ32aの周辺部分（下側チップ30上から突出している部分）を両開口部OP1, OP2間のリードフレーム部分（支持部21）において支持している点で相違している。他の構成については、第1の実施形態の半導体装置10と同じであるのでその説明は省略する。50

**【0076】**

本実施形態に係る半導体装置70は、一例として図8～図10に示す製造方法により製造することができる。図8～図10の各工程で行う処理は、基本的には、第1の実施形態に係る製造方法の各工程(図2～図4)で行った処理と同じである。重複的な説明を避けるため、相違する処理についてのみ以下に説明する。

**【0077】**

先ず最初の工程では(図8参照)、搭載すべき下側チップ30のダイサイズよりも大きな開口部OP1とその外側に画定される開口部OP2とを備えたリードフレーム20aを用意する。図2の工程で行った処理と同様にして、銅(Cu)の薄板を用意し、この金属(Cu)板をプレス加工もしくはエッチング加工により、図8(b)に示すように矩形状の開口部OP1が形成され、かつ、この開口部OP1の外側で左右方向に対向する2箇所の領域にそれぞれ開口部OP2が形成されると共に、各開口部OP2の周囲の外側の辺において所要の数のリード部22が櫛歯状に延在するように成形する。なお、破線で囲んだ矩形状の部分32Mは、上側チップ32aの外形(実装エリア)を表している。

10

**【0078】**

これにより、開口部OP1と各開口部OP2の間のそれぞれのリードフレーム部分は、上側チップ32aの周辺部分(実装エリア32M参照)を支持するための支持部21として規定される。このようにしてリードフレーム20aを成形した後、このリードフレーム20aをテープ60に貼り付ける。

20

**【0079】**

次の工程では(図9(a)参照)、図3(a)の工程で行った処理と同様にして、リードフレーム20aの開口部OP1に対応する部分のテープ60上(粘着剤が塗布されている側の面)に、下側チップ30を、その電極パッド31が形成されている側の面を下にしたフェイスダウンの態様で搭載する。本実施形態でも同様に、搭載するチップ30の厚さをリードフレーム20aの厚さと同じになるように選定している。

**【0080】**

次の工程では(図9(b)参照)、図3(b)の工程で行った処理と同様にして、下側チップ30上に、上側チップ32aを、その電極パッド33aが形成されている側の面上にしたフェイスアップの態様で搭載する。その際、上側チップ32aの周辺部分をリードフレーム20aの支持部21上に位置合わせし、各チップ30, 32aの裏面に付着しているダイ・アタッチ・フィルムの粘着性を利用して各チップ30, 32を規定の位置に保持する。さらに、上側チップ32aの電極パッド33aとリードフレーム20aの対応するリード部22とをボンディングワイヤ34aにより接続する。

30

**【0081】**

この後(図9(c)～図10(d)の工程)、上述した図3(c)～図4(d)の工程で行った処理と同じ処理を経て、本実施形態の半導体装置70(図7)が製造される。

**【0082】**

以上説明したように、第2の実施形態に係る半導体装置70及びその製造方法(図7～図10)によれば、その基本的な構成及びプロセスは第1の実施形態(図1～図4)の場合と同じであるので、同様の作用効果を奏することができる。

40

**【0083】**

さらにこの第2の実施形態によれば、図9(b)の工程において上側チップ32aの周辺部分(下側チップ30上から突出している部分)をリードフレーム20aの支持部21で支持しているので、その突出している部分(電極パッド33aが形成されている部分)の位置を固定化することができる。これにより、電極パッド33aとリード部22とのワイヤボンディング処理を安定に行うことができる。

**【0084】**

また、第1の実施形態の場合と同様にこの第2の実施形態においても、図9(c)の工程において行うテープ60上のリードフレーム20a及び各チップ30, 32a(ワイヤ34aを含む)の封止処理を、個別モールディングに代えて一括モールディングにより行

50

うようにしてもよい。その場合の実施形態を図 11 に示す。

**【0085】**

図 11 は、図 7 の半導体装置 70 の一変形例に係る半導体装置 70a の製造工程を示したものである。図 11 において (a) ~ (d) の各工程で行う処理については、上述した図 5 (a) ~ (d) の工程で行った処理と同じであるのでその説明は省略する。

**【0086】**

また、この第 2 の実施形態において、下側チップ 30 上に 2 個以上の上側チップを多段的に実装するようにしてもよい。その場合の実施形態を図 12 に示す。

**【0087】**

図 12 は、図 7 の半導体装置 70 の他の変形例に係る半導体装置 70b の構成を断面図の形態で示したものである。図示の半導体装置 70b は、その基本的な構成が第 1 の実施形態の変形例に係る半導体装置 10b ( 図 6 ) の構成と同じであるので、その説明は省略する。

10

**【0088】**

また、この第 2 の実施形態及びその変形例においても、上述した第 1 の実施形態の場合と同様の配置態様で、開口部 OP1 ( 図 8 参照 ) の外側で左右方向及び上下方向にそれぞれ対向する各 2 箇所 ( = 4 箇所 ) の領域にそれぞれ開口部 OP2 を形成し、各開口部 OP2 の周囲の外側の辺にそれぞれリード部 22 を設けるようにしてもよい。

**【0089】**

( 第 3 の実施形態及びその変形例 ... 図 13 ~ 図 18 参照 )

20

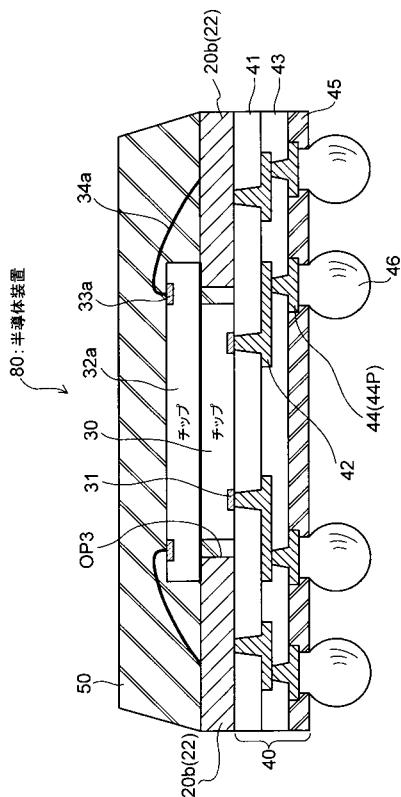

図 13 は本発明の第 3 の実施形態に係る半導体装置の構成を断面図の形態で示したものである。

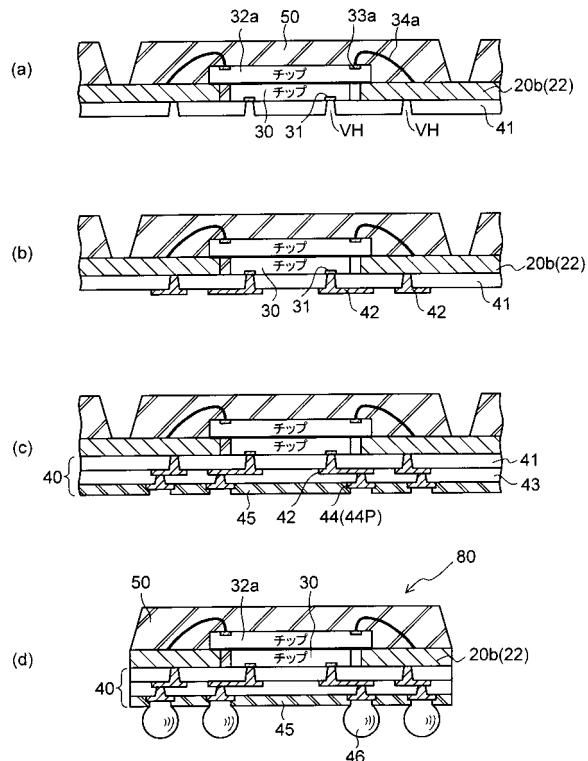

**【0090】**

本実施形態に係る半導体装置 80 は、第 1 の実施形態に係る半導体装置 10 ( 図 1 ) の構成と比べて、下側チップ 30 よりも大きいダイサイズを有した上側チップ 32a を実装し、この上側チップ 32a の電極パッド 33a をボンディングワイヤ 34a を介してリードフレーム 20b のリード部 22 ( インナーリード部 ) に接続した点、このリードフレーム 20b の開口部 OP3 の周囲に画定されるリード部 22 の少なくとも一部 ( 内側に向かう先端部 ) が、平面的に見て上側チップ 32a の周辺部分 ( 下側チップ 30 上から突出している部分 ) とオーバーラップするように成形されている点で相違している。他の構成については、第 1 の実施形態の半導体装置 10 と同じであるのでその説明は省略する。

30

**【0091】**

本実施形態に係る半導体装置 80 は、一例として図 14 ~ 図 16 に示す製造方法により製造することができる。図 14 ~ 図 16 の各工程で行う処理は、基本的には、第 1 の実施形態に係る製造方法の各工程 ( 図 2 ~ 図 4 ) で行った処理と同じである。重複的な説明を避けるため、相違する処理についてのみ以下に説明する。

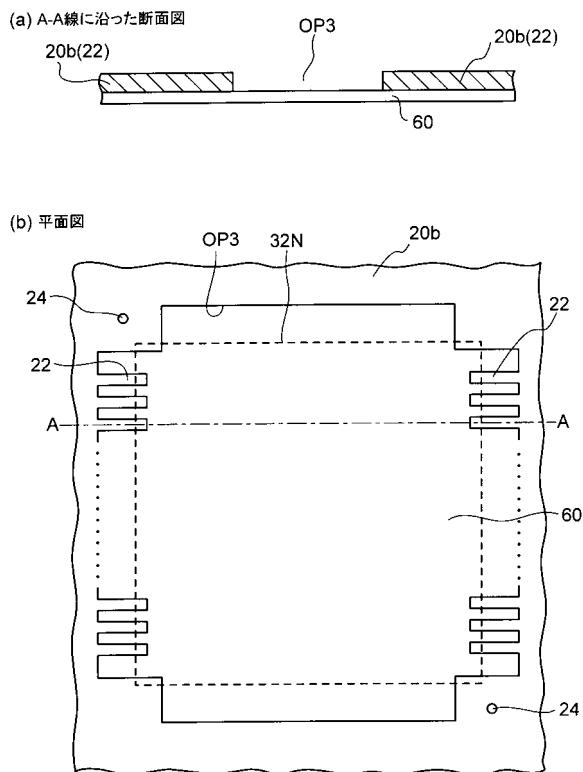

**【0092】**

先ず最初の工程では ( 図 14 参照 ) 、搭載すべき下側チップ 30 のダイサイズよりも大きな開口部 OP3 を備えたリードフレーム 20b を用意する。図 2 の工程で行った処理と同様にして、銅 ( Cu ) の薄板を用意し、この金属 ( Cu ) 板をプレス加工もしくはエッチング加工により、図 14 ( b ) に示すように開口部 OP3 の周囲の対向する 2 辺において所要の数のリード部 22 が櫛歯状に延在し、かつ、各リード部 22 の先端部が上側チップ 32a の実装エリア 32N 内に延びるように成形する。このようにしてリードフレーム 20b を成形した後、このリードフレーム 20b をテープ 60 に貼り付ける。

40

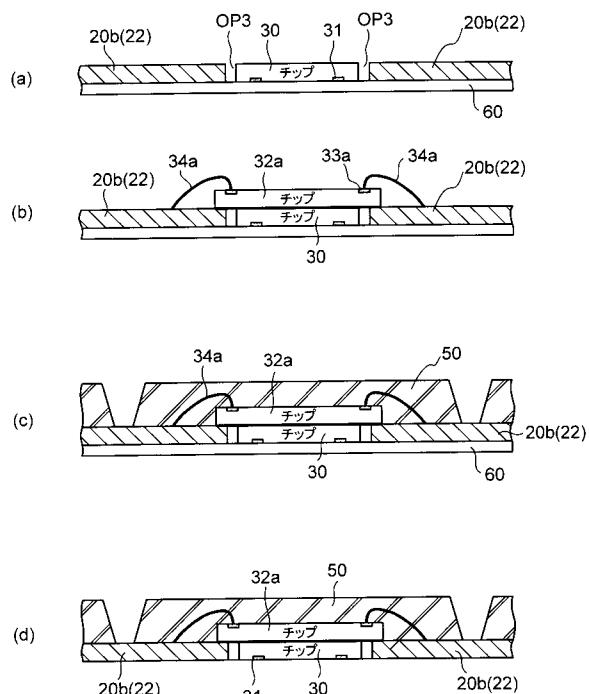

**【0093】**

次の工程では ( 図 15 ( a ) 参照 ) 、図 3 ( a ) の工程で行った処理と同様にして、リードフレーム 20b の開口部 OP3 に対応する部分のテープ 60 上 ( 粘着剤が塗布されている側の面 ) に、下側チップ 30 を、その電極パッド 31 が形成されている側の面を下にしたフェイスダウンの態様で搭載する。本実施形態でも同様に、搭載するチップ 30 の厚さをリードフレーム 20b の厚さと同じになるように選定している。

50

**【0094】**

次の工程では(図15(b)参照)、図3(b)の工程で行った処理と同様にして、下側チップ30上に、上側チップ32aを、その電極パッド33aが形成されている側の面を上にしたフェイスアップの態様で搭載する。その際、上側チップ32aの周辺部分をリードフレーム20bのリード部22の先端部上に位置合わせし、各チップ30, 32aの裏面に付着しているダイ・アタッチ・フィルムの粘着性を利用して各チップ30, 32aを規定の位置に保持する。さらに、上側チップ32aの電極パッド33aとリードフレーム20bの対応するリード部22とをボンディングワイヤ34aにより接続する。

**【0095】**

この後(図15(c)～図16(d)の工程)、上述した図3(c)～図4(d)の工程で行った処理と同じ処理を経ることで、本実施形態の半導体装置80(図13)が製造される。

10

**【0096】**

以上説明したように、第3の実施形態に係る半導体装置80及びその製造方法(図13～図16)によれば、その基本的な構成及びプロセスは第1の実施形態(図1～図4)の場合と同じであるので、同様の作用効果を奏すことができる。

**【0097】**

さらにこの第3の実施形態によれば、図15(b)の工程において上側チップ32aの周辺部分(下側チップ30上から突出している部分)をリードフレーム20bの各リード部22の先端部で支持しているので、その突出している部分(電極パッド33aが形成されている部分)の位置を固定化することができる。これにより、電極パッド33aとリード部22とのワイヤボンディング処理を安定に行うことができる。また、各リード部22の先端部は、上側チップ32aによって同じレベルに保持することができる。

20

**【0098】**

また、上述した第1、第2の実施形態の場合と同様にこの第3の実施形態においても、図15(c)の工程において、テープ60上のリードフレーム20b及び各チップ30, 32a(ワイヤ34aを含む)の封止処理を、個別モールディングに代えて一括モールディングにより行うようにしてもよい。その場合の実施形態を図17に示す。

**【0099】**

図17は、図13の半導体装置80の一変形例に係る半導体装置80aの製造工程を示したものである。図17において(a)～(d)の各工程で行う処理については、上述した図5(a)～(d)の工程で行った処理と同じであるのでその説明は省略する。

30

**【0100】**

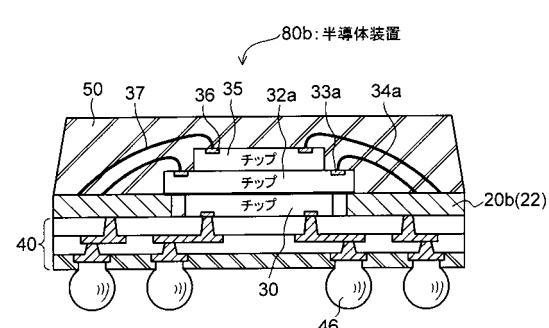

また、この第3の実施形態において、下側チップ30上に2個以上の上側チップを多段的に実装するようにしてもよい。その場合の実施形態を図18に示す。

**【0101】**

図18は、図13の半導体装置80の他の変形例に係る半導体装置80bの構成を断面図の形態で示したものである。図示の半導体装置80bは、その基本的な構成が第1の実施形態の変形例に係る半導体装置10b(図6)の構成と同じであるので、その説明は省略する。

40

**【0102】**

また、この第3の実施形態及びその変形例においても、上述した第1の実施形態の場合と同様の配置態様で、開口部OP3(図14参照)の周囲のそれぞれ対向する各2辺(=4辺)にそれぞれリード部22を設けるようにしてもよい。

**【0103】**

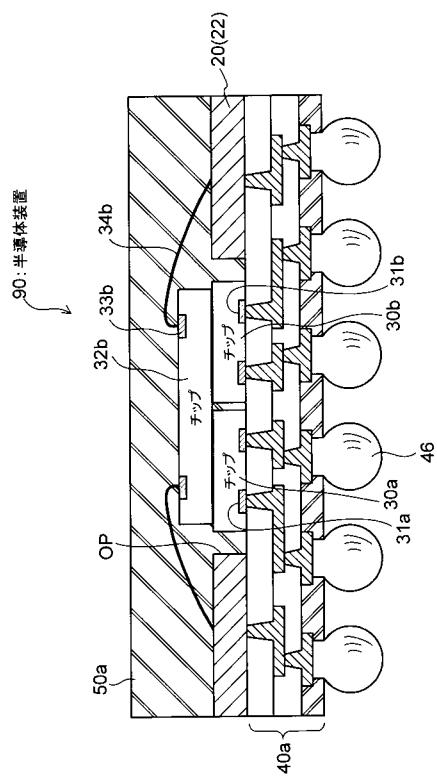

(第4の実施形態…図19参照)

図19は本発明の第4の実施形態に係る半導体装置の構成を断面図の形態で示したものである。

**【0104】**

本実施形態に係る半導体装置90は、第1の実施形態に係る半導体装置10(図1)の

50

構成と比べて、リードフレーム 20 の開口部 OP に、1 個の下側チップ 30 ( 図 1 ) に代えて複数個 ( 図示の例では 2 個 ) の下側チップ 30a 及び 30b を並列配置し、各チップ 30a, 30b の電極パッド 31a, 31b をそれぞれ積層配線層 40a の最上層の配線層に直接接続した点、さらに下側チップ 30a, 30b 上に、該下側チップよりも大きいダイサイズを有した上側チップ 32b を実装し、この上側チップ 32b の電極パッド 33b をボンディングワイヤ 34b を介してリードフレーム 20 のリード部 22 ( インナーリード部 ) に接続した点で相違している。他の構成については、図 1 の半導体装置 10 と基本的に同じであるのでその説明は省略する。

#### 【 0105 】

本実施形態の半導体装置 90 は、基本的には第 1 の実施形態に係る製造方法 ( 図 2 ~ 図 4 ) と同様にして製造することができる。ただし、本実施形態の場合、図 3 ( a ) の工程において、あらかじめ別工程で作製しておいた 2 個の半導体チップ ( 下側チップ 30a, 30b ) を、それぞれ電極パッド 31a, 31b が形成されている側の面を下にしたフェイスダウンの態様で、リードフレーム 20 の開口部 OP に対応する部分のテープ 60 上に並設 ( 搭載 ) している。さらに、図 3 ( c ) の工程で行う封止処理を、個別モールディングに代えて一括モールディングにより行っている。

10

#### 【 0106 】

本実施形態のように下側チップを複数個 ( 30a, 30b ) 実装することで、図 6 等の実施形態に示したような、上側チップ 32a, 35 を多段的に実装する場合と同様に、半導体装置 90 としての機能を更に高めることができる ( 高機能化 ) 。

20

#### 【 0107 】

なお、図 19 の実施形態では、第 1 の実施形態で使用したリードフレーム 20 ( 図 2 ) を用いた場合を例にとって説明したが、使用するリードフレームの形態がこれに限定されないことはもちろんである。第 2 の実施形態で使用したリードフレーム 20a ( 図 8 ) 、第 3 の実施形態で使用したリードフレーム 20b ( 図 14 ) に対しても、図 19 の実施形態は同様に適用することができる。

#### 【 図面の簡単な説明 】

#### 【 0108 】

【 図 1 】 本発明の第 1 の実施形態に係る半導体装置の構成を示す断面図である。

30

【 図 2 】 図 1 の半導体装置の製造工程の一例 ( その 1 ) を示す図である。

【 図 3 】 図 2 の製造工程に続く製造工程 ( その 2 ) を示す断面図である。

【 図 4 】 図 3 の製造工程に続く製造工程 ( その 3 ) を示す断面図である。

【 図 5 】 図 1 の半導体装置の一変形例に係る製造工程を示す断面図である。

【 図 6 】 図 1 の半導体装置の他の変形例に係る構成を示す断面図である。

【 図 7 】 本発明の第 2 の実施形態に係る半導体装置の構成を示す断面図である。

【 図 8 】 図 7 の半導体装置の製造工程の一例 ( その 1 ) を示す図である。

【 図 9 】 図 8 の製造工程に続く製造工程 ( その 2 ) を示す断面図である。

【 図 10 】 図 9 の製造工程に続く製造工程 ( その 3 ) を示す断面図である。

【 図 11 】 図 7 の半導体装置の一変形例に係る製造工程を示す断面図である。

【 図 12 】 図 7 の半導体装置の他の変形例に係る構成を示す断面図である。

40

【 図 13 】 本発明の第 3 の実施形態に係る半導体装置の構成を示す断面図である。

【 図 14 】 図 13 の半導体装置の製造工程の一例 ( その 1 ) を示す図である。

【 図 15 】 図 14 の製造工程に続く製造工程 ( その 2 ) を示す断面図である。

【 図 16 】 図 15 の製造工程に続く製造工程 ( その 3 ) を示す断面図である。

【 図 17 】 図 13 の半導体装置の一変形例に係る製造工程を示す断面図である。

【 図 18 】 図 13 の半導体装置の他の変形例に係る構成を示す断面図である。

【 図 19 】 本発明の第 4 の実施形態に係る半導体装置の構成を示す断面図である。

#### 【 符号の説明 】

#### 【 0109 】

10 ( a, b ), 70 ( a, b ), 80 ( a, b ), 90 ... 半導体装置、

50

- 20, 20a, 20b ... リードフレーム、

21 ... 支持部、

22 ... リード部、

30(a, b), 32(a, b), 35 ... シリコンチップ(半導体素子)、

31(a, b), 33(a, b), 36 ... 電極パッド(端子)、

32L, 32M, 32N ... 上側チップの外形(実装エリア)、

34(a, b), 37 ... ボンディングワイヤ、

40, 40a ... 積層配線層(パッケージ)、

41, 43 ... 絶縁層、

42, 44 ... 配線層(再配線層)、

44P ... (外部接続端子接合用の)パッド部、

45 ... ソルダレジスト層(保護膜)、

46 ... 外部接続端子、

50, 50a ... 封止樹脂(層)、

60 ... テープ(片面に粘着剤が塗布されたフィルム状の基材)、

OP, OP1, OP2, OP3 ... リードフレームの開口部。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(56)参考文献 特開2005-158999(JP,A)

特開2008-091418(JP,A)

特開2001-135781(JP,A)

特開2000-294722(JP,A)

特開2008-187203(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/065

H01L 25/07

H01L 25/18