(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6069617号

(P6069617)

(45) 発行日 平成29年2月1日(2017.2.1)

(24) 登録日 平成29年1月13日(2017.1.13)

(51) Int.Cl.

F 1

|                    |                  |

|--------------------|------------------|

| <b>H01L 33/32</b>  | <b>(2010.01)</b> |

| <b>H01L 21/205</b> | <b>(2006.01)</b> |

| <b>H01S 5/323</b>  | <b>(2006.01)</b> |

| <b>H01S 5/20</b>   | <b>(2006.01)</b> |

|      |        |

|------|--------|

| H01L | 33/32  |

| H01L | 21/205 |

| H01S | 5/323  |

| H01S | 5/20   |

|        |        |

|--------|--------|

| HO 1 L | 33/32  |

| HO 1 L | 21/205 |

| HO 1 S | 5/323  |

| HO 1 S | 5/20   |

|        |        |

|--------|--------|

| HO 1 L | 33/32  |

| HO 1 L | 21/205 |

| HO 1 S | 5/323  |

| HO 1 S | 5/20   |

請求項の数 6 (全 19 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2012-170932 (P2012-170932) |

| (22) 出願日     | 平成24年8月1日 (2012.8.1)         |

| (65) 公開番号    | 特開2013-46062 (P2013-46062A)  |

| (43) 公開日     | 平成25年3月4日 (2013.3.4)         |

| 審査請求日        | 平成27年8月3日 (2015.8.3)         |

| (31) 優先権主張番号 | 13/217,844                   |

| (32) 優先日     | 平成23年8月25日 (2011.8.25)       |

| (33) 優先権主張国  | 米国 (US)                      |

早期審査対象出願

前置審査

|           |                                                                                                                                                     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 502096543<br>パロ・アルト・リサーチ・センター・イン<br>コーポレーテッド<br>Palo Alto Research<br>Center Incorporated<br>アメリカ合衆国、カリフォルニア州 94<br>304、パロ・アルト、コヨーテ・ヒル・<br>ロード 3333 |

| (74) 代理人  | 100079049<br>弁理士 中島 淳                                                                                                                               |

| (74) 代理人  | 100084995<br>弁理士 加藤 和詳                                                                                                                              |

最終頁に続く

(54) 【発明の名称】窒化アルミニウム部分を除去した素子

## (57) 【特許請求の範囲】

## 【請求項 1】

発光素子の形成方法であって、

前記発光素子の第1のヘテロ構造をバルク結晶AlN基板上にエピタキシャル成長させる工程であって、前記第1のヘテロ構造は、第1の表面と、エッティング低減層と、第2の表面とを有しており、前記第1の表面は前記発光素子及び前記第2の表面のヘテロエピタキシャル成長の初期表面であり、前記第1のヘテロ構造は、格子不整合AlGaNエッティング低減層を有し、前記エッティング低減層は、前記ヘテロエピタキシャル成長の初期表面を含む、工程と、

前記第1のヘテロ構造の前記第2の表面の真上に発光層をエピタキシャル成長させる工程と、

10

前記発光層の真上に第2のヘテロ構造をエピタキシャル成長させる工程と、

前記バルク結晶AlN基板を通過する透過光の変化率を測定し、測定された前記透過光の変化率に基づいてエッティング処理を調整することにより、前記ヘテロエピタキシャル成長の初期表面の大部分に渡って前記発光素子から前記バルク結晶AlN基板を部分的に除去する工程であって、前記バルク結晶AlN基板を部分的に除去し格子不整合を緩和してエッティングされた表面を有する薄膜化されたAlN層を残す、工程と、

を含み、

前記第1のヘテロ構造における、前記ヘテロエピタキシャル成長の初期表面の約100nm以内の部分に渡って欠陥密度は $10^8 \text{ cm}^{-3}$ 未満である、

20

方法。

**【請求項 2】**

前記第1のヘテロ構造は、AlGaN、InGaN、InN、GaN、およびInAlGaNの少なくとも1つを含む、請求項1に記載の方法。

**【請求項 3】**

前記バルク結晶AlN基板を部分的に除去する工程は、エピタキシャル成長の初期表面の大部分に渡って前記バルク結晶AlN基板を除去することを含む、請求項1に記載の方法。

**【請求項 4】**

前記バルク結晶AlN基板を部分的に除去する工程は、ヘテロエピタキシャル成長の初期表面の大部分に渡って前記バルク結晶AIN基板を約 $50\text{ }\mu\text{m}$ 未満の厚さまで化学的にエッティングすることを含む、請求項1に記載の方法。 10

**【請求項 5】**

前記バルク結晶AlN基板を部分的に除去する工程は、リン酸を用いて前記バルク結晶AIN基板の窒素極性面を化学的にエッティングすることを含む、請求項1に記載の方法。

**【請求項 6】**

第1のヘテロ構造をバルク結晶AlN基板上に成長させる工程は、有機金属気相成長法、ハイドライド気相成長法、またはこれらの組み合わせにより前記第1のヘテロ構造を成長させることを含む、請求項1に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、窒化アルミニウム(AlN)部分を除去または薄膜化した素子、およびこのような素子を形成するための方法に関する。いくつかの実施形態は、発光層と第1および第2のヘテロ構造とを含む1層以上のエピタキシャル層を有する発光素子に関する。

**【背景技術】**

**【0002】**

本発明は、窒化アルミニウム(AlN)部分を除去または薄膜化した素子、およびこのような素子を形成するための方法に関する。いくつかの実施形態は、発光層と第1および第2のヘテロ構造とを含む1層以上のエピタキシャル層を有する発光素子に関する。 30

**【発明の概要】**

**【課題を解決するための手段】**

**【0003】**

第1のヘテロ構造をバルク結晶AlN基板上にエピタキシャル成長させ、次にエピタキシャル層からバルク結晶AlN基板が除去される。第1のヘテロ構造は、第1の表面と第2の表面とを有しており、第1のヘテロ構造の第1の表面は、エピタキシャル層のエピタキシャル成長の初期表面である。第1のヘテロ構造の第2の表面の真上に、発光層をエピタキシャル成長させる。発光層の真上に、第2のヘテロ構造をエピタキシャル成長させる。発光素子は、バルク結晶AlN基板を含まない。

**【0004】**

いくつかの実施形態によれば、発光素子は、第1の表面と第2の表面とを有する第1のエピタキシャル成長させたヘテロ構造と、この第1のヘテロ構造の第2の表面の真上にエピタキシャル成長させた発光層と、を含む。第2のエピタキシャル成長させたヘテロ構造を発光層を覆って成長させる。この素子は、約 $365\text{ nm}$ 未満の波長範囲の、発光層により生成された光が第1のヘテロ構造の第1の表面を通過して、この素子から射出可能であるように構成されている。第1の表面近傍の欠陥密度は、約 $10^8\text{ cm}^{-3}$ 未満である。 40

**【0005】**

いくつかの実施形態は、第1および第2のヘテロ構造間に発光層を含む発光素子に関する。バルク結晶AlN基板上に、第1のヘテロ構造をエピタキシャル成長させる。第1のヘテロ構造の真上に、発光層をエピタキシャル成長させる。発光層の真上に、第2のヘテ 50

口構造をエピタキシャル成長させる。バルク結晶AlN基板は、約50μm未満の化学的にエッティングされた厚さを有する。

#### 【0006】

いくつかの実施形態は、AlN、GaN、AlGaN、InGaN、InN、およびInAlGaNの少なくとも1つを含み、かつ、エピタキシャル成長の初期表面である第1の表面を有する1層以上のエピタキシャル層からなる物体に関する。この物体は、バルク基板を含まないが、除去処理後に残ったAlN基板残部、たとえば、約50μm未満の厚さを有する化学的にエッティングされたAlN基板残部を含んでよい。エピタキシャル成長の初期表面100nm以内の欠陥密度は、約 $10^8 \text{ cm}^{-3}$ 未満である。この物体は、約200nm以上または約365nm以上の波長の光に対して光透過性であり得る。

10

#### 【0007】

いくつかの実施形態は、素子を形成する方法に関する。バルクAlN基板上に格子不整合エピタキシャル層を成長させる。このエピタキシャル層は、初期エピタキシャル成長の表面近傍で約 $10^8 \text{ cm}^{-3}$ 未満の欠陥密度を有する。バルクAlN基板は、この基板を完全に除去するか、または化学エッティングすることによって実質的に除去されて、約50μm未満の厚さの基板残部を残す。この基板が実質的に除去された後、エピタキシャル層の格子不整合は、部分的または完全に緩和されるとともに、初期のエピタキシャル成長の表面近傍の欠陥密度は実質的に維持される。基板の実質的な除去は、エピタキシャル成長の初期表面の大部分(50%以上)に対して基板を除去する工程またはエピタキシャル成長の初期表面の大部分に対して基板残部を残す工程を含む。

20

#### 【図面の簡単な説明】

#### 【0008】

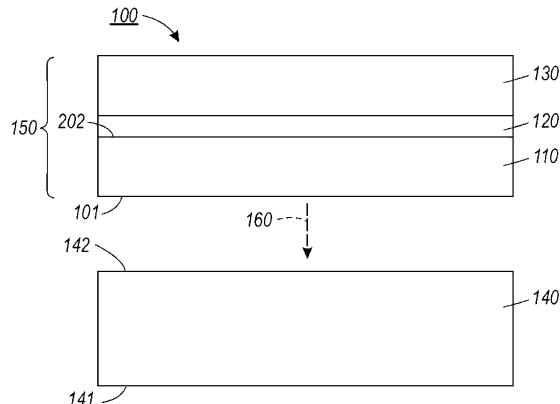

【図1】図1は、サブアセンブリを示す図である。

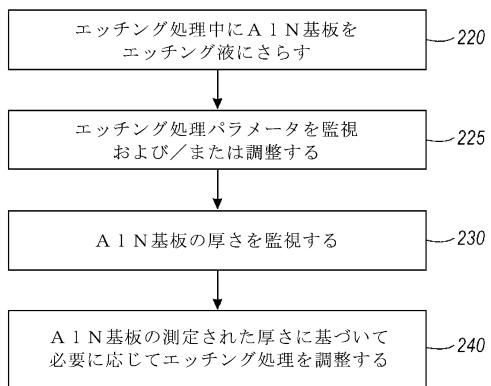

【図2】図2は、バルクAlN基板を除去する方法を示す図である。

【図3】図3は、AlN基板の厚さを測定する工程を示す流れ図である。

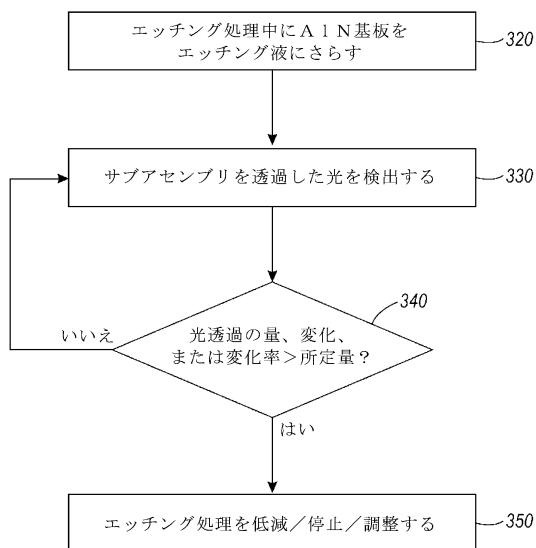

【図4】図4は、エピタキシャルな $\text{Al}_{1-x}\text{Ga}_{(1-x)}\text{N}$ 層のエッティング時間を示す図である。

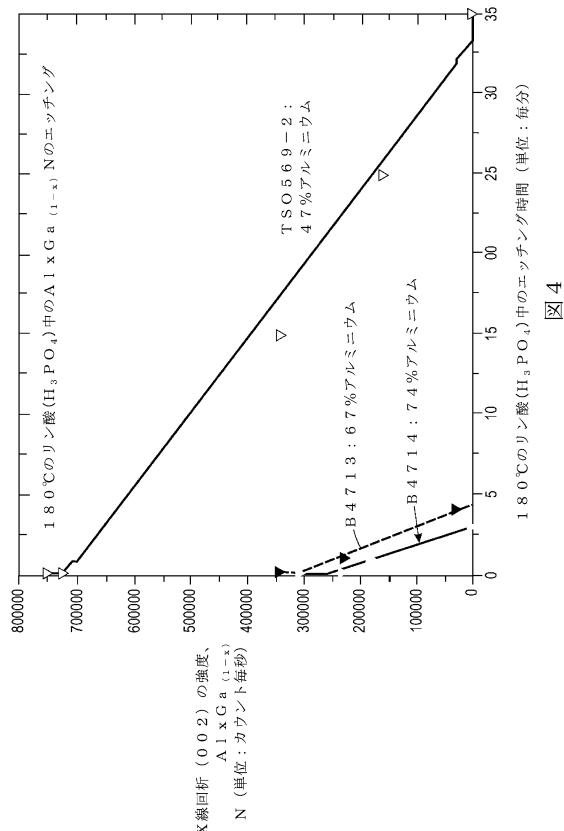

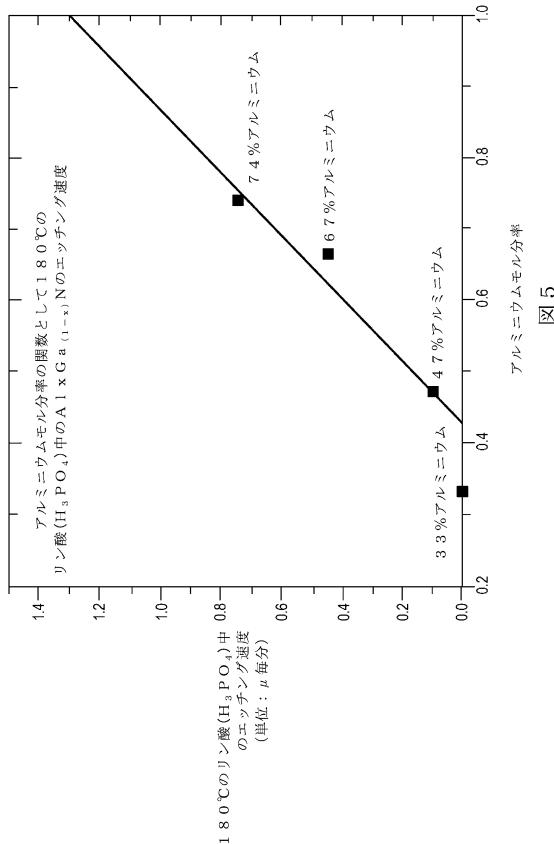

【図5】図5は、リン酸中の $\text{Al}_{1-x}\text{Ga}_{(1-x)}\text{N}$ 層のエッティング速度を示すグラフである。

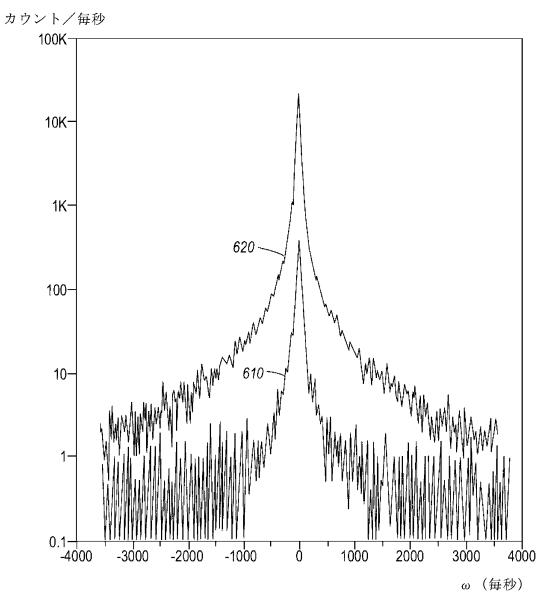

【図6】図6は、X線回折測定の一例を示す図である。

30

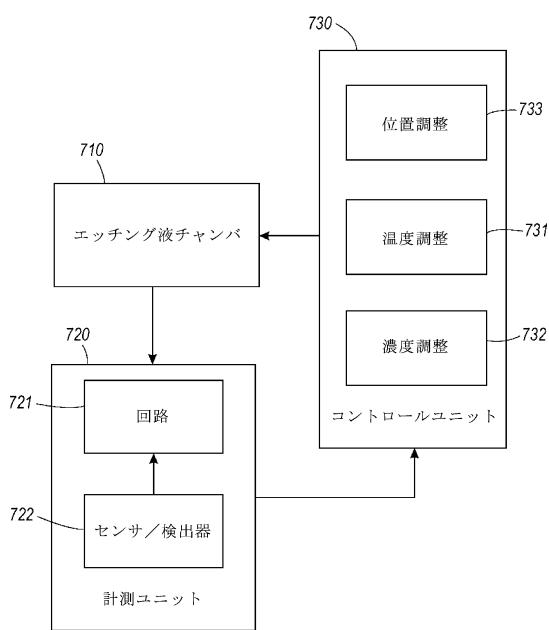

【図7】図7は、湿潤エッティングによりサブアセンブリからAlN基板を除去するために使用することができる装置を示す図である。

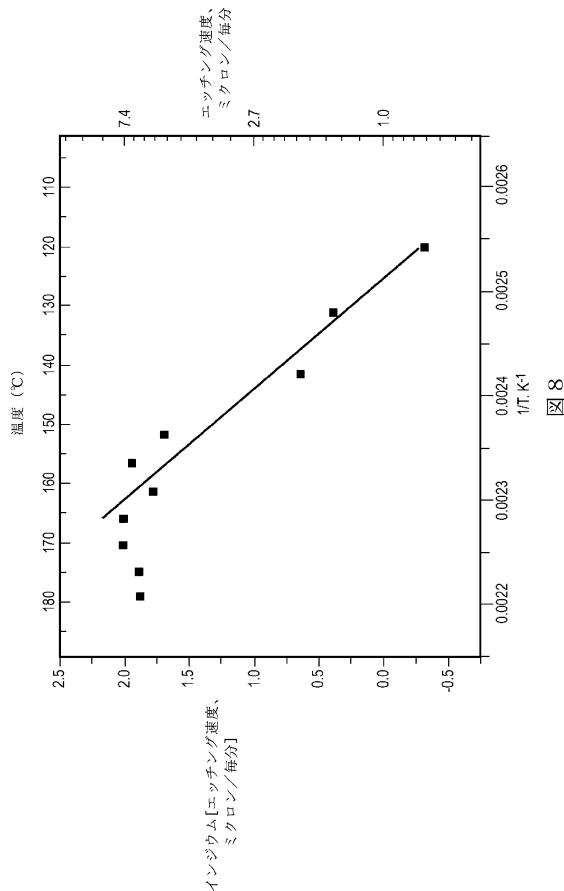

【図8】図8は、温度の関数としてバルクAlNのエッティング速度を示す図である。

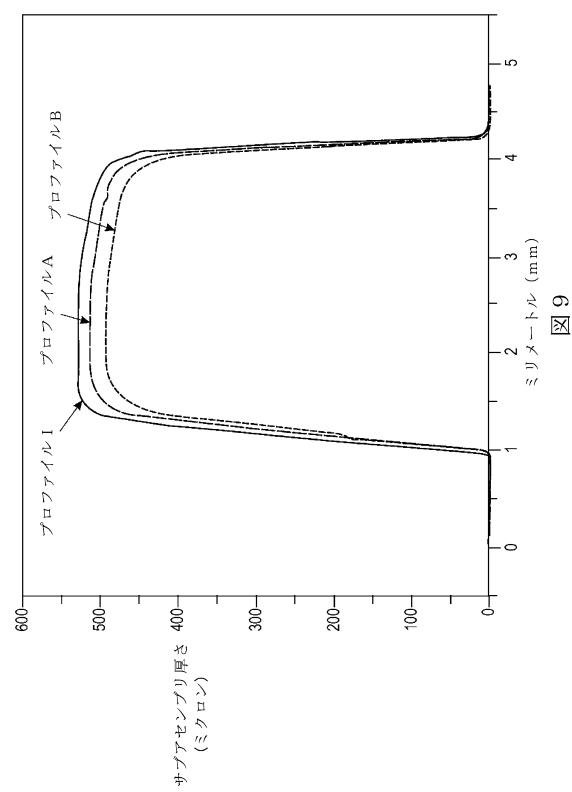

【図9】図9は、サブアセンブリのプロフィルメータの測定値を示す重畠されたグラフである。

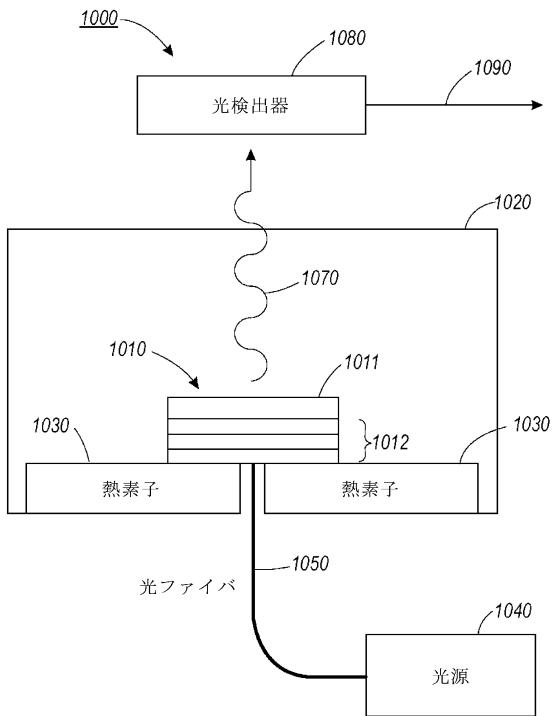

【図10】図10は、AlN基板の厚さを示す信号を生成するために光を使用する装置を示す図である。

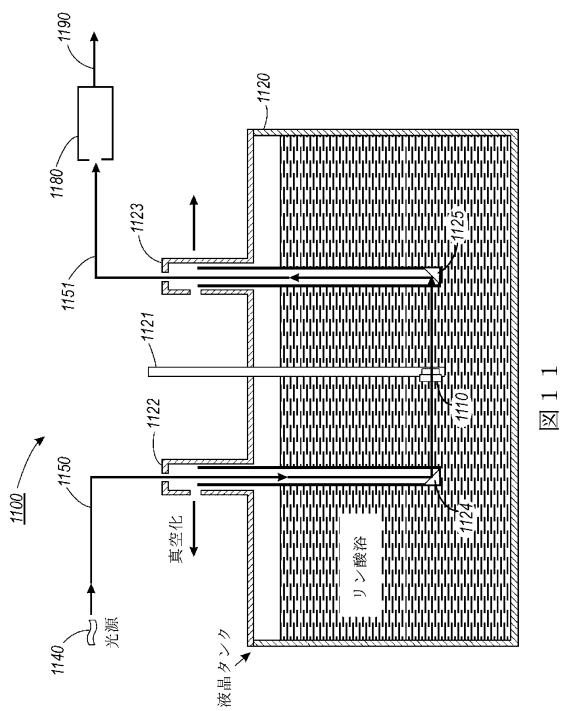

【図11】図11は、AlN基板の厚さを示す信号を生成するために光を使用する装置を示す図である。

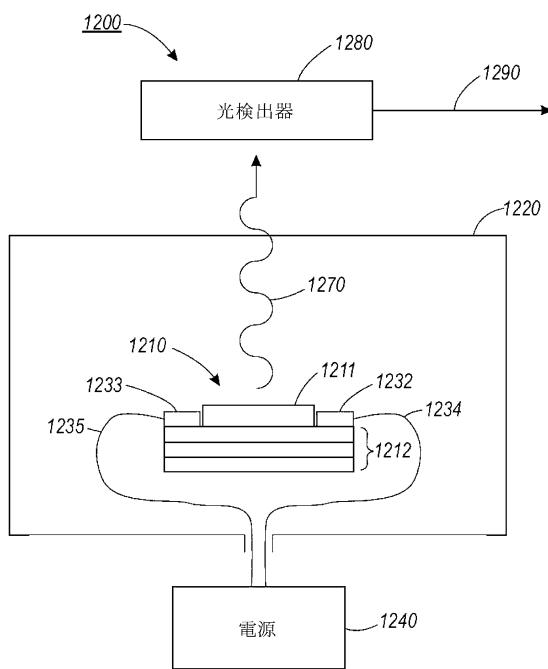

【図12】図12は、サブアセンブリによって生成される光を使用する装置を示す図である。

40

【図13】図13は、AlN層の厚さの関数としての光検出器によって生成される信号の一例を示す図である。

【図14】図14は、バルクAlN基板上に初期に成長させた紫外線(UV)発光ダイオード(LED)を示す図である。

【図15】図15は、エッティング低減層を含むLEDを示す図である。

【図16】図16は、表面で裏面コンタクトを有する垂直方向の電気的注入LEDアーキテクチャを示す図である。

【図17】図17は、レーザダイオード設計のエネルギーバリアを示す図である。

【図18】図18は、得られたエピタキシャル成長させたテンプレート/基板を形成する

50

処理を示す図である。

【図19】図19は、スタンドアロン型のエピタキシャル成長させたテンプレート／基板を形成する処理を示す図である。

【図20】図20は、界面層をエッティングすることによって基板からエピタキシャル成長させたヘテロ構造を分離した後に得られた構造を示す図である。

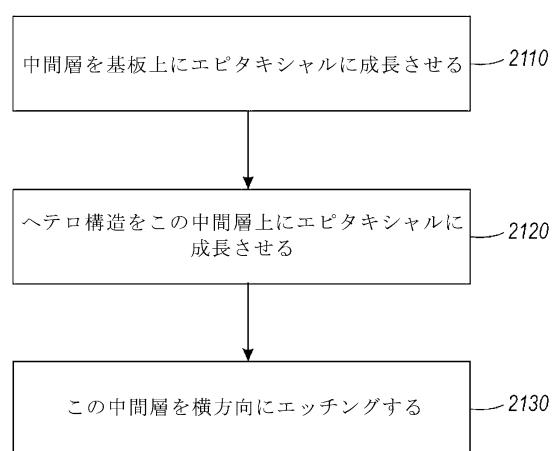

【図21】図21は、エピタキシャル成長させたヘテロ構造を形成する処理を示す図である。

#### 【発明を実施するための形態】

##### 【0009】

図1は、バルク結晶A1N基板140と、このバルクA1N基板140上に形成させたエピタキシャル層150とを最初に含むサブアセンブリ100を示す図である。図1は、いくつかのエピタキシャル層150を示しているが、サブアセンブリはこれより多いまたは少ないエピタキシャル層を含んでよいし、一部の実施においては、1層のみのエピタキシャル層を含んでもよい。A1N基板140は、第1の表面141と第2の表面142と有している。バルク結晶A1N基板は、第1および第2の表面141、142においてスライスされるインゴットとして成長させてよい。

10

##### 【0010】

場合により、エピタキシャル層150は、第1のヘテロ構造110と第2のヘテロ構造130に挟まれた1層以上の発光層120を含む。発光層120および／またはヘテロ構造110、130は、低欠陥密度でA1N上にエピタキシャル成長させることができる材料系、GaN、AlGaN、InN、InGaN、および／またはInAlGaNから形成されてよい。この例では、バルクA1N基板140の真上に、第1のヘテロ構造110をエピタキシャル成長させる。エピタキシャル層150の成長は、A1N基板140の第2の表面142上でエピタキシャル成長する第1のヘテロ構造110の第1の表面101から進行する。第1のヘテロ構造110は、欠陥低減層、ひずみ管理層、および／または電流分布層を含む多層を有してよい。次に、第1のヘテロ構造110の真上に活性領域120を成長させ、活性領域120の真上に第2のヘテロ構造130を成長させる。破線160で示すように、サブアセンブリ100の形成後、バルクA1N基板140は実質的に除去される。

20

##### 【0011】

30

バルクA1N基板は、ある波長範囲、たとえば、365nm以上の波長に対して、および／または、約200nm～約365nmのUV波長範囲において、実質的に光吸収性である。発光素子の場合、バルクA1N基板の実質的な除去によって素子の基板側（本明細書中では素子の裏面として示す）、すなわち、このバルクA1Nが実質的に除去された表面を介して光を射出することが可能となる。スタンドアロン型のエピタキシャルテンプレート／基板の場合、バルクA1N基板の実質的な除去によってエピタキシャルテンプレート／基板が約365nm以上の波長を有する光に対しておよび／または約200nm～約365nmの波長範囲の光に対して実質的に光透過性となることができる。

##### 【0012】

40

基板の実質的な除去は、エピタキシャル成長の初期表面の大部分に対して基板を除去する工程を含む。基板の実質的な除去は、たとえば、エピタキシャル成長の初期表面の大部分に対して化学的にエッティングすることにより、A1N基板を薄膜化する工程を含む。場合により、基板残部は、エッティング処理後のエピタキシャル成長の初期表面の大部分に対して残留することがある。基板残部は、約50μm～0nm（完全に除去）または約50μm未満の厚さを有する。

##### 【0013】

図2は、サブアセンブリからバルクA1N基板を除去する方法を示している。このサブアセンブリは、バルクA1N基板と、このバルクA1N基板上にエピタキシャル成長させた1層以上のエピタキシャル成長層とを含む。たとえば、この1層以上のエピタキシャル層は、発光層を有する発光素子を含むかまたは発光層を含まないエピタキシャル層を含む

50

。

#### 【0014】

バルク A 1 N 基板、たとえば、基板の窒素極性 (N 極) 面は、高温、たとえば、湿潤エッティング処理においてリン酸の沸点におけるリン酸を含むエッティング液にさらされる (220)。本明細書に記載されている LED 構造において、たとえば、図 1 に概略的に示すように、バルク A 1 N 基板の底面はエッティング液に N 極面を付与することができる。約 85 % 以上または約 87 % ~ 約 96 % の濃度範囲および 160 ~ 210 の温度範囲におけるリン酸は適切な時間内でバルク単結晶 A 1 N を溶解することができる。いくつかの構成において、使用されるリン酸は、たとえば、約 160 ~ 約 180 の温度範囲で 87 % ~ 92 % の濃度範囲を有することができる。この溶解はまた、表面の初期加水分解後に A 1 極面を付与する A 1 N 基板をエッティングするために使用することもできる。10

#### 【0015】

エッティング処理中、エッティング処理パラメータ、たとえば、リン酸の濃度および / または温度が監視され (225)、リン酸の濃度および / または温度が所定の濃度 / 温度範囲内に留まるように調整される。エッティング処理中、A 1 N 基板の厚さを監視することができる (230)。場合により、A 1 N 基板の厚さは移動位置において測定され、この厚さ測定は、エッティング処理からサブアセンブリを定期的に除去し、サブアセンブリの厚さおよび / または窒化アルミニウム基板の厚さを測定し、場合によっては測定後このサブアセンブリをエッティング処理へ戻す工程を含む。別の場合では、以下に説明するように、サブアセンブリおよび / または A 1 N 基板の厚さは原位置で測定できる。20

#### 【0016】

エッティング処理は、サブアセンブリおよび / または A 1 N 基板の測定厚さに基づき必要に応じて調整することができる (240)。エッティング処理は、エッティング速度を変化させ (エッティング速度を増減させ)、エッティング処理を開始し、および / または、基板が所定の状態に入った後、たとえば、基板がサブアセンブリから実質的に除去された後、または、基板が所定の厚さ、たとえば、約 50 mm に達した時、または基板がサブアセンブリの領域内で実質的に除去された時、エッティング処理を停止するように、調整することができる。エッティング速度は、エッティング液の濃度および / または温度を変化させることによって調整することができる。たとえば、A 1 N の厚さが所定の厚さに近づく (または基板の実質的な除去に近づく) について、エッティング速度はチャンバーに水を添加することによって遅延させてエッティング液の濃度を低下させることができる。これに代えてまたはこれに加えて、エッティング速度を遅延させるためにエッティング液の温度を下げてもよい。いくつかの実施において、エッティング処理を停止する工程は、手動または自動の除去技術のいずれかにより、エッティング液からサブアセンブリを除去して達成することができる。30

#### 【0017】

サブアセンブリおよび / または窒化アルミニウム基板の厚さ測定は、機械的、電気的、化学的、および / または光学的技術を含む様々な処理によって達成され得る。たとえば、いくつかの構成において、A 1 N 基板の厚さ測定は、電磁放射を使用する光学的技術によって達成され得る。これらの技術は、電磁放射をサブアセンブリへ方向付けるソースと、回折され、反射されおよび / またはサブアセンブリによって透過される電磁放射を検出するように構成されている検出器と、を必要とする。たとえば、サブアセンブリおよび / または A 1 N 基板の厚さは、X 線回折、偏光解析法、および / または干渉分光法などの技術を用いて測定可能である。いくつかの構成において、計測ユニットは、エッティング処理中に原位置で厚さ測定されるように配置することができる。他の構成において、厚さは、エッティング処理からサブアセンブリを除去し、測定し、このサブアセンブリをエッティング処理へ戻すことによって移動位置で測定される。40

#### 【0018】

いくつかの構成において、A 1 N 基板の厚さ測定は、サブアセンブリを透過する光を検出する工程を含む。このような測定に使用される光の波長範囲は、バルク A 1 N 基板によって実質的に吸収され、少なくともある程度エピタキシャル層によって透過される範囲の50

ものである。図3の流れ図によって示すように、最初にエッティング処理が開始された時(320)、AlN基板は相対的に厚膜であり光に対して不透明である。(あれば)AlN基板を透過した光はエッティング処理中に検出される(330)。AlN基板がエッティングによって除去されると、このAlN基板は基板を通過して光透過が可能となる位に薄膜化される。AlN基板の透過光の量、エッティング処理において以前測定した基準量に比較した場合の光透過の変化および/またはAlN基板を通過する光透過の変化率が検出でき(340)、かつ、これらをエッティング処理を調整するために用いてよい(350)。

#### 【0019】

Al<sub>x</sub>Ga<sub>(1-x)</sub>N材料(X=0~1)のエッティング速度は、アルミニウム含有量の関数として変化する。図4および図5のグラフは、各々エピタキシャル成長させたAlGaN層のエッティング時間とエッティング速度をアルミニウムのモル分率の関数として示している。各試料について、エッティングされているAlGaN層の厚さは、エッティング液化学槽から定期的に試料を取り出してX線スキャンを実行して、AlGaN層のX線信号強度を求ることにより監視された。図4は、91%濃度と180°の温度におけるリン酸(H<sub>3</sub>PO<sub>4</sub>)中でエッティングされた厚さ2.4μmのエピタキシャルなAl<sub>x</sub>Ga<sub>(1-x)</sub>N層のエッティング時間を示している。74%または67%のアルミニウムモル分率を有するAlGaNの層は5分以内で実質的に除去されたが、47%のアルミニウムモル分率を有するAlGaN層を除去するには30分以上もかかった。

#### 【0020】

図5は、91%濃度および180°の温度におけるリン酸(H<sub>3</sub>PO<sub>4</sub>)中にエピタキシャル成長させたAl<sub>x</sub>Ga<sub>(1-x)</sub>Nのエッティング速度を、アルミニウムモル分率として示すグラフである。このグラフは、アルミニウムモル分率が高くなるにつれてエッティング速度も速くなることを示している。図6は、基板の除去前(610)と基板の除去後(620)の試料サブアセンブリのX線回折測定の一例である。以下に詳細に説明するように、いくつかの実施形態において、相対的に高いモル分率のエピタキシャル成長させたAlGaNの層はバルクAlN基板を除去するための中間層として使用することができる。

#### 【0021】

図7は、湿潤エッティングによりサブアセンブリからAlN基板を除去するために使用することができる装置を示す図である。この装置はエッティング液チャンバ710を含み、このチャンバはエッティング液を含有するとともにエッティングされているサブアセンブリを保持するように構成されている。この装置は必要に応じて計測ユニット720を含み、この計測ユニットはAlN基板の厚さおよび/またはAlN基板と1層以上のエピタキシャル層との両方を含むサブアセンブリの厚さとを示す信号を生成するように構成されている。この信号はエッティング処理中に計測ユニット720によって生成され、一連の厚さ測定値を反映することが可能である。この信号はエッティング処理の1層以上の側面を調整するためにコントロールユニット730によって使用可能である。

#### 【0022】

エッティング処理の調整は、エッティング処理のさまざまな側面を調整するように配置されたコントロールユニット730の1つ以上のサブユニットによって達成可能である。たとえば、サブユニット731、732、733は、エッティング液の温度、エッティング液の濃度、および/または試料の位置を調整することができる。サブアセンブリのエッティング速度は、これらの1つ以上および/または他のパラメータを変更することによって調整することが可能である。濃度調整サブユニット732は、チャンバ710へより多くの水分を添加することによって、またはチャンバ710内の水分を減少させることによって、例えば、沸騰時に蒸発する水分を補給しないことによって、エッティング液の濃度を維持したり変更したりするように構成することができる。温度調整サブユニット731は、エッティング液を加熱および/または冷却するヒータおよびクーラの1つまたは両方を含むことが可能である。エッティング液の冷却および/またはエッティング液の濃度低下はエッティング速度を遅らせる。エッティング液の温度の上昇および/または濃度の増加はエッティング速度を

10

20

30

40

50

るポイントまで上昇させる。しかしながら、エッティング速度は A 1 N 基板表面の加水分解に依存することがあり得る。エッティング速度は、エッティング液の濃度が高くなりすぎ、エッティング液中の水量が表面の加水分解を発生させるには不十分な場合、抑制される。図 8 はバルク A 1 N のエッティング速度を温度の関数として示す。理解されるように、エッティング速度は約 85 % の濃度に対応する約 160 よりも高い温度に対しても横ばい(レベルオフ)であるように見える。この横ばいは基板の表面を加水分解するには水分が不十分であることに起因し得る。

#### 【0023】

いくつかの構成において、温度および/または濃度調整サブユニット 731、732 はエッティング液の温度および/または濃度を所定の範囲内に保つように設定される。基板の除去はエッティング溶液を監視する工程を含む。リン酸の温度が沸点に保たれる場合、沸騰時の水分の損失は A 1 N の加水分解速度を減速させ、これによりエッティング速度を低下させる。リン酸の沸点は酸の濃度に応じて変化する。たとえば、市販のリン酸は約 85 % の濃度を有し約 158 °C で沸騰する。沸騰中に水分が損失されるにつれて酸の濃度と沸騰点は上昇する。調整されたエッティング速度の場合、エッティング液の濃度および/または温度は、所定の範囲内、たとえば、約 87 % ~ 約 96 % の濃度範囲および 160 °C ~ 210 °C の温度範囲に保つことが可能である。相対的に一定した酸の濃度を保つために、損失した水分は、例えば、還流冷却器または自動ドリップシステムのいずれかにより補給することができる。

#### 【0024】

計測ユニット 720 は、センサ/検出器からの信号を処理するように構成されている適切な処理回路 721 に結合された(図 7 においてセンサ/検出器 722 として示す)1つ以上のセンサまたは検出器を含む。エッティング処理中、センサ/検出器 722 は、A 1 N 基板および/またはサブアセンブリの厚さに関連するサブアセンブリおよび/またはエッティング液の特性における変化を検出する。前述したように、計測ユニット 720 は、厚さを示す信号を生成するために様々な技術を使用することができる。これらの技術は、エッティング処理中の A 1 N 基板、サブアセンブリおよび/またはエッティング液の光学的、機械的、化学的、または電気的パラメータを感知する工程を含む。一例として、サブアセンブリの厚さの機械的な測定はプロフィルメータを使用して行われる。この例の場合、プロフィルメータの探り針(プローブ)は計測ユニットのセンサである。サブアセンブリはエッティング処理中に数回測定される。図 9 はサブアセンブリのプロフィルメータの測定値の重畠したグラフを示す。厚さプロファイル I はサブアセンブリの A 1 N 基板がエッティングされる前の起動プロファイルである。この起動プロファイル(プロファイル I)を取得した後、第 1 の期間でサブアセンブリをエッティング槽に入れ、次に除去し厚さプロファイルを再測定した。プロファイル A は、第 1 の期間においてエッティングした後のサブアセンブリの厚さを表している。プロファイル A を取得した後、第 2 の期間においてサブアセンブリをエッティングした。第 2 の期間を経た後、プロファイル B に示したように、サブアセンブリの厚さを再測定した。連続するプロファイル I、A、B は第 1 および第 2 の期間を経た後のエッティング処理の進行状況を示している。

#### 【0025】

サブアセンブリの電気的特性は、厚さを示す信号を生成するために使用可能である。たとえば、いくつかの実施形態において、センサは、サブアセンブリの表面または部分に電気接触するように構成されている電気コンタクトを含む。電気コンタクトは、1つ以上の電気的特性処理を実施するように構成されている回路に結合される。サブアセンブリの電気的特性は、抵抗/コンダクタンス測定値、静電容量測定値、電流-電圧特性、および/または他の特性の1つ以上を含み得る。サブアセンブリの厚さの薄膜化はサブアセンブリの電気的特性における検出可能な変化を生成する。

#### 【0026】

計測ユニットはサブアセンブリおよび/またはエッティング液における化学的变化を検出するように構成されている化学センサとこれらに関連する回路とを含む。化学センサは、

10

20

30

40

50

サブアセンブリの上、および／または、エッティング液槽などのエッティングチャンバ内に配置することができる。場合により、化学センサとこれらに関連する回路はエッティング槽中のイオン濃度を測定するように構成されている。この濃度は、エッティング液に溶解される状態になる A 1 N の量の関数として、エッティング処理中に変化し得る。よって、化学センサによって検出されたイオン濃度は A 1 N 基板の厚さを示す信号を生成するために使用可能である。いくつかの構成において、これは、エッティングされている表面にてイオン濃度に対する感度を高めるためにサブアセンブリの近傍、例えば、サブアセンブリの数 mm 以内に化学センサを配置するために有用であり得る。

#### 【 0 0 2 7 】

計測ユニットは基板の厚さを示す信号を生成するためにサブアセンブリを透過した光を使用することができる。これらの実施において、計測ユニットは、光をサブアセンブリへ方向付けるように配置された光源と、透過した光を検出するように配置された検出器と、を含み得る。光源は、1つ以上のランプ、LED、および／またはUV、可視光、赤外光、または広帯域光を放つレーザを含み得る。サブアセンブリへ方向付けられた光は A 1 N 基板に実質的に光学的に吸収されるがサブアセンブリのエピタキシャル層には実質的に吸収されない波長範囲を含む。たとえば、バルク A 1 N 基板と A 1 GaN エピタキシャル層とを含むサブアセンブリに対して、計測ユニットは、光源、例えば、約 200 nm ~ 約 365 nm の波長範囲で発光する LED と同範囲で光を検出する検出器とを含み得る。いくつかの構成において、光源は発光し、検出器は約 250 nm ~ 約 300 nm の波長範囲の光を検出し得る。

#### 【 0 0 2 8 】

場合により、光源はある波長範囲を有する光を出力するように構成され検出器は波長範囲にわたってサブアセンブリのスペクトル応答を特徴づけるように構成されている。スペクトル応答における変化はエッティング処理を調整するために使用することが可能である。

#### 【 0 0 2 9 】

図 10 は、厚さを示す信号を生成するために光を使用する装置 1000 を示す図である。図 10 の構成例において、バルク A 1 N 基板 1011 と A 1 N 基板 1011 上の1つ以上のエピタキシャル層 1012 とを含むサブアセンブリ 1010 はエッティング液チャンバ 1020 内に配置されている。加熱素子 1030、たとえば、ヒータおよび／またはクーラはエッティング処理中にエッティング液の温度を調整するためにチャンバ 1020 の中、その上、またはその周りに配置することができる。これに加えて、またはこれに代えて、装置 1000 は、チャンバ内のエッティング液の濃度を調整するように構成されている構造（図示しない）を含み得る。光源、たとえば、UVLED は光がサブアセンブリへ向けて方向付けられるように配置される。図 10 に示すように、光は光ファイバ 1050 を介してサブアセンブリ 1011 に向けて方向付けられる。エッティング処理に先立って、光源 1040 からの光はバルク A 1 N 基板 1011 により実質的に遮断されるが、エピタキシャル層 1012 により実質的に透過される。基板 1011 が薄膜化されるにつれて、光はサブアセンブリ 1010 を透過することが可能である。透過光 1070 は光検出器 1080 によって検出される。サブアセンブリ 1010 を透過した光 1070 に応答して、光検出器 1080 は A 1 N 基板 1011 の厚さを示す出力信号 1090 を生成する。

#### 【 0 0 3 0 】

エッティング処理中に A 1 N 基板の厚さを検出するために光を使用する装置 1100 の他の例を図 11 に示す。本実施形態の装置 1100 はリン酸槽を含む石英タンク 1120 を備えるエッティング液チャンバを含む。A 1 N 基板とこの上に形成した1つ以上のエピタキシャル層とを含むサブアセンブリ 1110 は、試料ホルダ 1121 によりタンク 1120 内に位置決めされ保持される。装置 1100 は各々が真空に結合されている2つのポート 1122、1123 を含む。この例において、ポート 1122、1123 は閉端された真空石英管を含む。光源 1140 からの光は第1のポート 1122 を介して第1の光ファイバ 1150 によって導かれ第1のミラー 1124 によってサブアセンブリ 1110 に向けて方向付けられる。サブアセンブリ 1110 を透過した光は第2のポートから第2の光フ

10

20

30

40

50

アイバ 1151 を介して第 2 のミラー 1125 によって方向付けられる。光検出器 1180 はサブアセンブリ 1110 を透過した光を検出するように配置される。検出された光に応答して、光検出器 1180 は A1N 基板の厚さを示す信号 1190 を生成する。

#### 【0031】

いくつかの実施において、サブアセンブリのエピタキシャル層は LED などの発光素子を形成し得る。これらの実施において、発光素子は A1N 基板の厚さを示す信号を生成する際に使用される光のための光源であってよい。図 12 は、A1N 基板の厚さを測定するために使用される光 1270 を生成するためにサブアセンブリ 1210 のエピタキシャル層 1212 を使用する装置 1200 を示す。装置 1200 は、図 10 に示した外部光源と光ファイバが図 12 に示した実施では使用されていないことを除いて、いくつかの点で図 10 の装置と同様である。サブアセンブリ 1210 はエッティング液チャンバ 1220 内に配置されるとともに A1N 基板 1211 上にエピタキシャル成長させる層 1212 を含む。エピタキシャル層 1212 は発光素子を形成する。装置 1200 は、発光素子 1212 と接触する電気コンタクト 1232、1233 と、これらの電気コンタクト 1232、1233 を電源 1240 に接続するリード 1234、1235 と、を含む。発光素子 1212 がリード 1234、1235 と電気コンタクト 1232、1233 を介して電源 1240 によって通電されると、発光素子 1212 は、基板が光 1270 を透過するために十分に薄膜化された時に A1N 基板を透過する光 1270 を生成する。A1N 基板 1211 がエッティングされるにつれて、この基板 1211 は增量する光 1270 を透過し、この光量は光検出器 1280 によって検出される。光検出器 1280 は A1N 基板の厚さを示す信号 1290 を生成する。

#### 【0032】

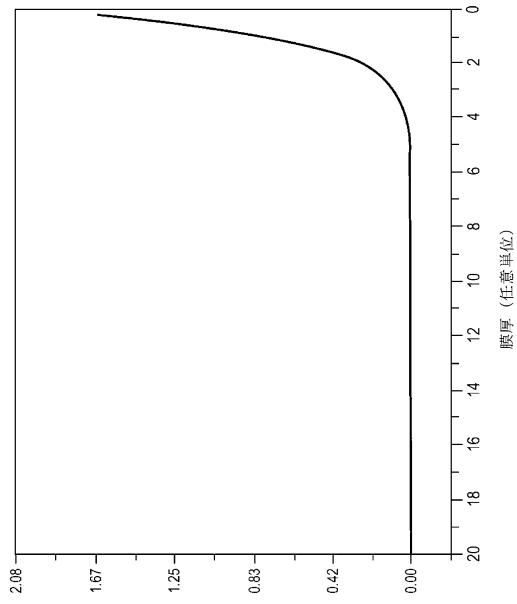

図 13 は、たとえば、A1N 基板の厚さを示す光検出器によって生成される、理想的な信号の一例を示す。最初に A1N 基板はこの A1N 基板に向けて透過される光を実質的に光学的に吸収している。エッティング処理が最初に開始されると、A1N 基板に方向付けられた光の多くが基板によって吸収されてサブアセンブリから抜け出さない。この厚さ信号は、A1N 基板の厚さが A1N 層を光が透過する位に薄膜化されるまで、公称値のままである。窒化アルミニウム基板が光を透過する位に薄膜化されると、厚さ信号は A1N が基板からエッティングされればされるほど、一層増え始める。信号の変化は A1N 基板の厚さがかなりの光量を透過する値に達した時、極めて速くなる。

#### 【0033】

場合により、計測ユニットにより生成された信号はエッティング処理を調整するために使用することができる。たとえば、コントロールユニットは急速な変化が検出されるポイントまで信号を監視し得る。その時点で、コントロールユニットはエッティング速度を変更せざるよう、たとえば、エッティング処理を遅延させたり停止させたりするよう、動作し得る。計測ユニットにより生成された信号はエッティング処理を調整するために他の情報と組み合わせて使用され得る。たとえば、計測ユニットによって生成された信号に加えて、コントロールユニットは、エッティング処理期間、エッティング処理期間にわたるチャンバ内のエッティング液の濃度、および / またはエッティング処理期間にわたるエッティング液の温度などの要因を考慮に入れる。コントロールユニットは感熱ユニット、たとえば、ヒータやクーラの動作を調整し、および / またはエッティング処理の速度を変更するためにエッティング液の濃度を調整することができる。

#### 【0034】

様々なタイプの発光素子は本明細書中に記載されているバルク A1N 基板を除去するための処理を用いて形成してよい。バルク A1N 基板の除去や薄膜化は約 200 nm ~ 約 365 nm または約 250 nm ~ 約 320 nm の波長範囲の光を放つ紫外線発光ダイオード (UVELED) と紫外線 (UV) レーザダイオードに特に有用である。これらの発光素子の形成におけるバルク A1N 基板の使用は素子構造の低欠陥エピタキシャル層の成長を可能にするが、A1N 基板は素子の基板側に向けた活性領域から放たれた光を実質的に吸収する。したがって、基板の除去は素子の基板側 (裏面) から増加した発光を可能にする。

10

20

30

40

50

いくつかの素子において、基板から活性層の反対側にある発光素子の上層（すなわち、素子の正面側にある層）は素子によって生成された光の波長で光学的に吸収している状態であり得る。したがって、これは、A1N基板の除去によって実現可能となる素子によって生成された光が基板側を通過して放たれる場合に有用である。

#### 【0035】

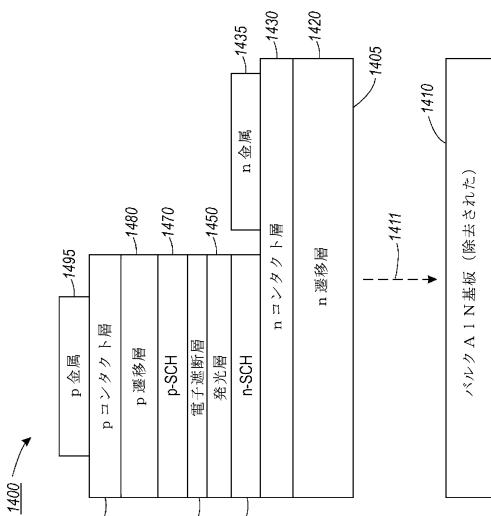

図14は、バルクA1N基板1410上に初期に成長させたUVLED1400の実施形態を示す図である。エピタキシャル層の成長は、例えば、ハイドライド気相成長法(HVPE)および/またはこれらの技術の任意の組み合わせにより、有機金属気相成長法(MOCVD)を用いて、達成される。次に、バルクA1N基板1410は、矢印1411で示されるように、除去されるかまたは薄膜化される。場合により、A1N基板1410は除去される。場合により、A1N基板1410は、たとえば、機械的な技術を用いて可能とされる厚さよりも薄く、約50μm以下の厚さまで薄膜化される。図14に示したUVLEDヘテロ構造1400は有機金属気相成長法により成長させて以下を含む：

n側のAl<sub>x</sub>Ga<sub>1-x</sub>N遷移領域1420と、

nドープされたAl<sub>0.74</sub>Ga<sub>0.26</sub>Nのnコンタクト層1430と、

n側のAl<sub>0.74</sub>Ga<sub>0.26</sub>Nの分離した閉じ込めヘテロ構造(SCH)1440と、

例えは、中心周波数=250nmで発光するように設計された、多重量子井戸(MQW)発光層1450と、

電子遮断層1460と、

p側AlGaNのSCH1470と、p型ドープAlGaN遷移領域1480と、

pドープされたGaNコンタクト層1490。

#### 【0036】

n側のAl<sub>x</sub>Ga<sub>1-x</sub>Nの遷移領域1420はA1N基板1410上に形成されたエピタキシャル成長の初期表面1405を含む。いくつかの構成において、n側遷移領域1420は、約0.90に等しいxから約0.80に等しいxまでの範囲の平均A1組成を有する一連の短周期超格子である。いくつかの構成において、遷移領域1420は、xが約100%から約74%までの範囲の線形グレード合金であってよい。nコンタクト層1430はnコンタクト1435のためのコンタクト層であり、たとえば、約1.9μm厚さであってよい。量子井戸(MQW)発光層1450は3対の6nm厚さのAl<sub>0.68</sub>Ga<sub>0.32</sub>Nバリアと2nm厚さのAl<sub>0.65</sub>Ga<sub>0.35</sub>Nウェルを含むことができる。電子遮断層(EBL)1460は約83%のアルミニウムと約20nmの厚さであってよい。p-SCH1470は約0.3から約0.74までの範囲のアルミニウム組成xを有することができる。p遷移層1480は超格子であるかまたは約0.3から約0.74までの範囲xを有する合金であってよい。pコンタクト層1490はGaNを含みかつp型金属コンタクト1495のためのコンタクト層である。記載した構造は一例にすぎない。層数、層の組成、実際のヘテロ構造の設計、および/または成長手順は大きく異なる。具体的には、これらの層はAlGaNに代えてInGaNまたはInAlGaNを形成するためにインジウムを含むことができる。

#### 【0037】

LEDをバルクA1N基板上に最初に成長させて次にこの基板を除去するかまたは薄膜化する。この処理は、たとえば、約10<sup>8</sup>cm<sup>-3</sup>または10<sup>7</sup>cm<sup>-3</sup>などの約10<sup>1</sup>~約10<sup>3</sup>cm<sup>-3</sup>の範囲において相対的に低くなるようにAlGaN遷移層のエピタキシャル成長の初期表面において欠陥密度を生成する。このように、素子はA1N基板に整合する実質的な格子によってもたらされる高品質のエピタキシャル成長を保持するが、この素子の基板側を通過する実質的な光透過を可能とすることもできる。

#### 【0038】

たとえば、バルクA1N基板上にエピタキシャル成長させる約70%~80%未満のA1モル分率を有するAlGaNのn遷移層は基板にぴったり格子整合すると思われる。このシナリオでは、AlGaNのn遷移層は低欠陥密度を有するバルク結晶A1Nの格子定

10

20

30

40

50

数にぴったり整合するように最初は不整合な状態である。AlN基板が除去されると、n遷移層の格子は緩むが、低欠陥密度は保持される。

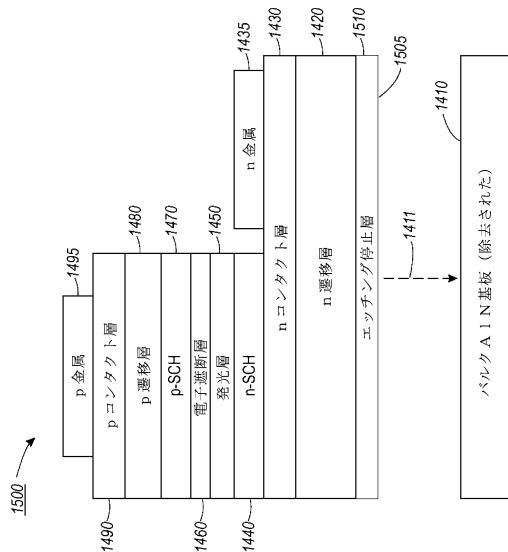

#### 【0039】

図15は、図14のLED1400にいくつかの点で類似しているLEDを示す。図15において参照符号で識別される要素は、図14におけるこれらの片われに類似している。LED1500は、このLED1500がエッチング前にAlN基板1410とAlGaN遷移層1420との間で成長させることができ可能なエッチング低減層1510（エッチング停止層ともいう）を含む点で、図14のLED1400とは異なる。この例において、エッチング低減層1510は初期のエピタキシャル表面1505を含む。エッチング低減層1510は、AlN基板をエッチングするために使用されるエッチング液に不浸透性であるかまたはエッチング液中のエッチング低減層のエッチング速度はAlN1410のエッチング速度より低速である。エッチング低減層1510は、相対的に薄層のGaN層であるかまたは約70%～約80%の範囲のアルミニウム含有量（Alモル分率）を有するAlGaN層であるかおよび／または、たとえば、エッチング低減能力を付与する他の適切な材料を含み得る。

10

#### 【0040】

約50μm未満の厚さを有する基板残部を残すための完全な除去または化学的なエッチングのいずれかによる基板の除去によってこの後の処理のために素子の裏面へのアクセスが可能となる。基板が除去された後は素子の裏面にある量の表面粗さやテクスチャリングが存在している。場合により、テクスチャリングは、この基板除去処理によって素子の裏面へ付与される。この基板除去処理は、この基板除去処理中にこの素子の裏面のテクスチャリングを付与するように構成可能である。化学エッチングから得られた表面粗さはエッチング槽温度、酸濃度、エッチング速度、および／またはウェハ裏面磨きなどの処理パラメータに依存する。適切な処理パラメータは所望される表面粗さ特性を生成するために選択することができる。いくつかのシナリオにおいて、素子の裏面は、たとえば、イオンビームまたは化学処理によって、基板除去後にテクスチャリングすることができる。テクスチャリングは光抽出を向上させることができる。いくつかのシナリオにおいて、裏面のテクスチャリングを行わずに、実質的な発光量を全内部反射によってヘテロ構造に閉じ込めることができる。裏面のテクスチャリングは放たれた光を散乱させ、全内部反射を妨げ、かつ光抽出効率を向上させる。

20

30

#### 【0041】

表面テクスチャリングは様々な湿式または乾式の処理技術によってパターン化することができる。たとえば、表面は水素化カリウム（KOH）溶液に浸漬することによりテクスチャリングすることができる。プラズマ処理技術は粗面処理するために使用することができる。たとえば、LED1400、1500の初期のエピタキシャル表面1405、1505はテクスチャリングされた表面であってよい。

#### 【0042】

裏面のテクスチャリングは、放たれた光がより短い波長でTM方向（平面に垂直な方向）へますます偏光した状態になるので、短波長のUVLEDにおいて特に重要である。これによって、光の大部分は裏面へ向けてよりもむしろ、素子の端部へ向けて伝搬しながら発光される。基板が除去されて、特性は裏面へ向けてかつ裏面を通過して放たれた光を再方向付けするようにパターン化することができる。

40

#### 【0043】

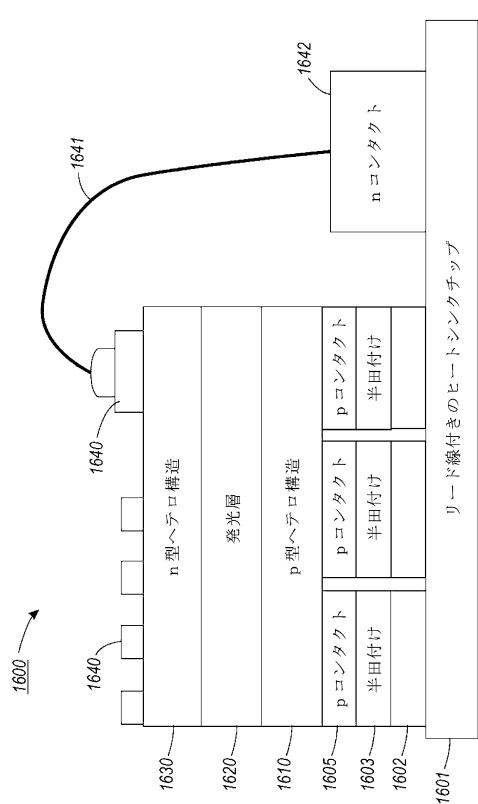

基板の除去によって垂直方向の電気的注入LEDアーキテクチャも可能になる。図16はこのような構造1600を示す。このLEDは初期エピタキシャル表面1631を含むn型のヘテロ構造1630を含む。n型のヘテロ構造の初期のエピタキシャル表面から開始して発光層1620とp型ヘテロ構造1610を連続してエピタキシャル成長させながら、LED1600をバルク結晶AlN基板（図16に図示せず）上に成長させた。エピタキシャル層1610～1630を形成した後、バルクAlN基板が除去される。

#### 【0044】

垂直方向注入 L E D 1 6 0 0 の p コンタクト 1 6 0 5 はヒートシンクチップ 1 6 0 1 のパッド 1 6 0 2 へ半田付け 1 6 0 3 される。電極 1 6 4 0 は 1 つ以上のリード 1 6 4 1 と n コンタクト 1 6 4 2 を介してヒートシンクチップ 1 6 0 1 に電気的に結合される。素子の動作中、電流は、 p コンタクト 1 6 0 5 、 p 側 ( p 型ヘテロ構造 1 6 1 0 ) 、発光層 1 6 2 0 、および n 側 ( n 型ヘテロ構造 1 6 3 0 ) を介して、外部電源 ( 図示せず ) から注入されるとともに素子 1 6 0 0 の裏面に形成された電極 1 6 4 0 にて集合される。電気的絶縁性の A 1 N 基板を除去することによって裏面コンタクト 1 6 4 0 を形成するための N 型ヘテロ構造層 1 6 3 0 へのアクセスが可能となる。

#### 【 0 0 4 5 】

図 1 6 に示した垂直方向注入構造 1 6 0 0 は、 n 型ヘテロ構造 1 6 3 0 を形成する材料 10 、たとえば、 n ドープされた A 1 G a N が大きく抵抗性を示す場合、特に有利になり得る。この状況において、 A 1 N 基板を除去しない場合、電流は、素子 1 6 0 0 の p コンタクト 1 6 0 5 と同じ側で、発光領域 1 6 2 0 に並んだ領域において、集合される ( たとえば、図 1 4 と図 1 5 の L E D 1 4 0 0 、 1 5 0 0 、 1 6 0 0 の構造を参照されたい ) 。より高い光出力パワーを得るために発光層 1 6 2 0 の面積は相対的に大きくなるように作られる。発光層の中心に注入される電流は、素子の周囲の n コンタクトに達する前に抵抗性のある n ドープされた層内により長い横方向の距離を移動する必要があるとおもわれる。この横方向の距離に沿った電流経路は大きな電圧降下を生成しつつ不均一な電流注入を生じさせることができる。 A 1 N 基板の除去はコンタクトを素子の裏面に形成することを可能にしこれにより p コンタクト 1 6 0 2 と電流収集電極 1 6 4 0 との間に直接的な電流経路とより低い電圧降下をもたらす。

#### 【 0 0 4 6 】

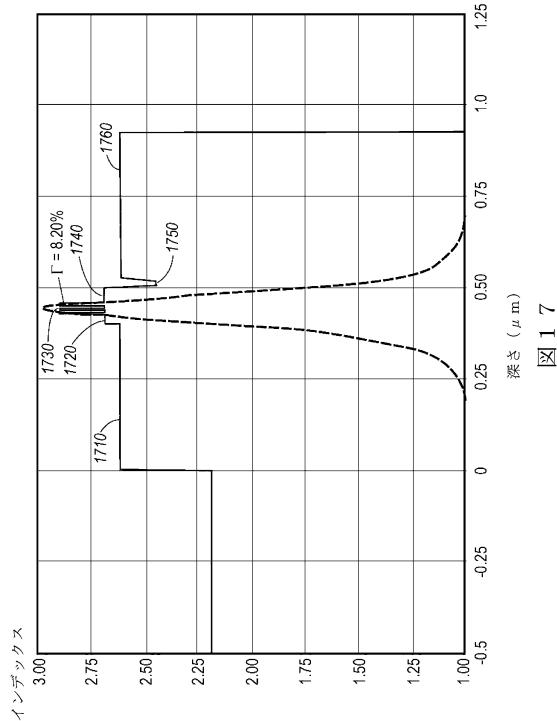

レーザダイオード ( L D ) もまた、 A 1 N 基板の除去や薄膜化を有利とすることができる。図 1 7 は関連する光学モードプロファイル ( 破線で示す ) とともに典型的なレーザーダイオード設計 ( 実線で示す ) のエネルギーバリア図 s を示す。モードの中心周波数は約 2 5 0 n m の波長に対応する。この設計において、光学モードと量子井戸 1 7 3 0 の間のオーバーラップは、 = 8 . 2 6 % で表される。 L D は、 n コンタクト 1 7 1 0 、 n S C H 1 7 2 0 、多重量子井戸 1 7 3 0 、 p S C H 1 7 4 0 、および p コンタクト 1 7 6 0 を含む。

#### 【 0 0 4 7 】

A 1 N 基板上に作られた一般的な U V レーザダイオードにおいて、何らかの電界が A 1 N 基板に浸透している場合、この A 1 N 基板がレーザ処理波長において高く光吸収するので、実質的なモーダル損失が生じる。光吸収基板は導波管材料の損失を助長しこれによりレーザ処理を達成するために必要とされる利得を増加させる。基板側のクラッド層は活性領域内に光学モードをしっかりと閉じ込めるために十分に厚くする必要がある。しかしながら、厚膜の n クラッド層は素子の抵抗性を助長する。 A 1 N 基板を除去または薄膜化することはモーダル損失を低減し設計上のフレキシビリティを高める。 A 1 N 基板の除去 / 薄膜化はまた、 L E D のケースにおいて説明した利益に類似した利益を提供する垂直方向の注入 L D 構造を可能にする。

#### 【 0 0 4 8 】

いくつかの実施形態において、基板の除去 / 薄膜化は、裏面全体を横切ってというよりむしろ裏面のいくつかの部分に於いてのみ達成される。基板は化学エッティング液から保護することができ選択領域における開口はこれらの領域のみをエッティングするためだけに形成することができる。たとえば、開口は発光層の真下の領域においてのみ形成でき、これによりバルク基板の部分はエッティング処理後に残留しこれ以降の処理のために使用可能である。

#### 【 0 0 4 9 】

いくつかの実施において、本明細書において「テンプレート / 基板」と総称されるエピタキシャル成長させた A 1 N または A 1 G a N テンプレートおよび / または基板は、スタンドアロン型コンポーネントとして製造することができる。これらのテンプレート / 基板

10

20

30

40

50

は、たとえば、ピースパートとして売られ、その後、LEDやレーザーダイオードなどのオプトエレクトロニクスデバイスとヘテロ接合トランジスタや増幅器などの電子素子とを含む数多くの種類の素子を形成するために使用することができる。エピタキシャルなテンプレートは、バルク結晶AlN基板上にエピタキシャルなAlNまたはAlGaNを成長させ次にこのAlN基板を除去または薄膜化することによって形成することができる。この技術は、AlN、AlGaN、InN、InGaN、および／またはInAlGaNなどの窒化物系材料の高品質で光学的に透明なエピタキシャル成長させたテンプレート／基板を生成することができ、これ以降の処理ステップにおけるエピタキシャル成長のためのベースとして使用することができる。エピタキシャルなテンプレート／基板は、相対的に高い成長率、たとえば、時間あたり約1μm以上で成長させて約30μm～約400μmの層を生成することができる。エピタキシャル成長させたテンプレート／基板は、有機金属気相成長法(MOCVD)により、ハイドライド気相成長法(HVPE)により、および／または、これらの技術の任意の組み合わせにより、形成される。高品質で光学的に透明なテンプレート／基板は、前述した理由からUVオプトエレクトロニクスデバイスに有用であり得る。最も一般的な配向はc平面のAlNであるが、m平面、a平面などの他の結晶配向や半極性配向も、エピタキシャル成長の開始前にAlNバルク基板を所望の配向において切断することによって得ることができます。

#### 【0050】

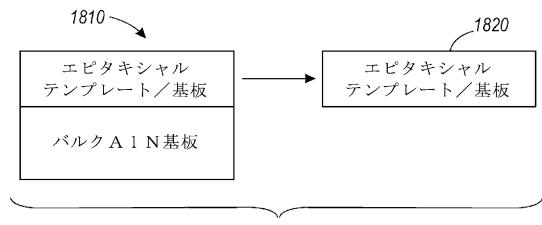

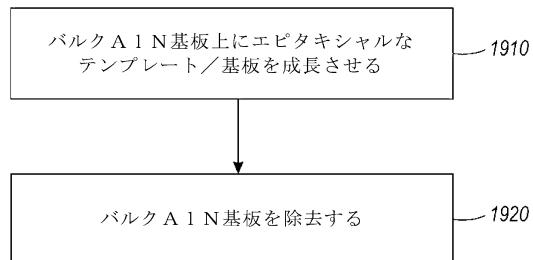

図18および図19は、スタンドアロン型のエピタキシャル成長させたテンプレート／基板を形成する処理(図19)と、これにより得られる構造(図18)と、を示す。たとえば、エピタキシャルなAlN、AlGaN、InN、InGaN、および／またはInAlGaNを含むエピタキシャル層をバルク結晶AlN基板上に成長させる(1910)。得られた構造1810を図18に示す。バルクAlN基板は、本明細書において前述した処理によって除去または薄膜化1920されて、スタンドアロン型のエピタキシャルなテンプレート／基板1820を残す。

#### 【0051】

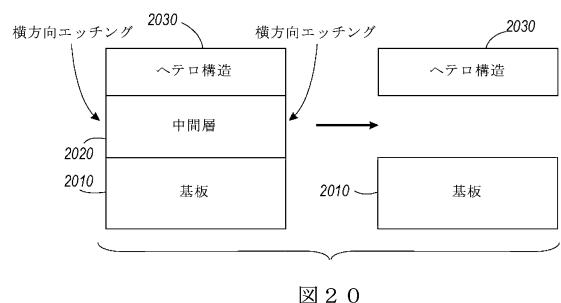

いくつかの実施において、構造、たとえば、エピタキシャルなテンプレート／基板、オプトエレクトロニクスデバイス、または他の構造またはヘテロ構造は、AlN、シリコン、サファイア、またはSiC(炭化ケイ素)などの様々な基板上に成長させた中間層上に成長させることができる。これらは中間層をエッティングすることによって基板から分離させてこれにより基板から構造を分離させることができる。図21は、中間層をエッティングすることによりその基板からスタンドアロン型のエピタキシャル成長させたヘテロ構造を形成する処理を示す。図20は、この構造の初期と最後の状態を示す。中間層2020は基板2010上にエピタキシャル成長させる(2110)。構造2030を界面層2020に成長させる(2120)。界面層2020は横方向にエッティングされ(2130)、基板2010から構造2030を分離させる。

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

【図6】

図6

【図7】

図7

【図8】

図8

【図 9】

【図 10】

【図 11】

【図 12】

【図 1 3】

図 1 3

【図 1 4】

図 1 4

【図 1 5】

図 1 5

【図 1 6】

図 1 6

【図17】

【図18】

図18

【図19】

図19

【図20】

【図21】

図21

---

フロントページの続き

(72)発明者 クリストファー・エル・チュア

アメリカ合衆国 カリフォルニア州 95123 サンノゼ キューリー・ドライブ 636

(72)発明者 ブレント・エス・クルーサー

アメリカ合衆国 カリフォルニア州 94536 フレモント コーニッシュ・ドライブ 352

15

(72)発明者 トマス・ウンデラー

アメリカ合衆国 カリフォルニア州 94301 パロ・アルト エベレット・アベニュー 71

5 アパートメント5

(72)発明者 ノーブル・エム・ジョンソン

アメリカ合衆国 カリフォルニア州 94025 メンロー・パーク オーク・グローブ・アベニ

ュー 445 ナンバー1

審査官 小濱 健太

(56)参考文献 特表2010-517298(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64