(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3716406号

(P3716406)

(45) 発行日 平成17年11月16日(2005.11.16)

(24) 登録日 平成17年9月9日(2005.9.9)

(51) Int.C1.<sup>7</sup>

F 1

H01L 21/336

H01L 29/78 29/78 29/78

H01L 29/786

H01L 29/78 29/78

H01L 29/78 626B

請求項の数 7 (全 22 頁)

(21) 出願番号 特願2000-29928 (P2000-29928)

(22) 出願日 平成12年2月8日 (2000.2.8)

(65) 公開番号 特開2001-223360 (P2001-223360A)

(43) 公開日 平成13年8月17日 (2001.8.17)

審査請求日 平成15年11月25日 (2003.11.25)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100105337

弁理士 真鍋 深

(74) 代理人 100072833

弁理士 柏谷 昭司

(74) 代理人 100075890

弁理士 渡邊 弘一

(74) 代理人 100110238

弁理士 伊藤 壽郎

(72) 発明者 原田 昭彦

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

最終頁に続く

(54) 【発明の名称】絶縁ゲート型半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

能動領域となる半導体層を基板分離用絶縁膜によって半導体基板から分離した絶縁ゲート型半導体装置において、支柱状の主ゲート電極と梁状導電体パターンからなるT字状のゲート電極を設け、前記梁状導電体パターンによって第1の導電型とは反対導電型の第2の導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨がる長さを有する第1の導電型のボディコンタクト領域を前記第2の導電型のソース領域及び第2の導電型のドレイン領域から分離するとともに、前記梁状導電体パターンの直下のゲート絶縁膜の膜厚を前記梁状導電体パターンの全長にわたって前記主ゲート電極の直下のゲート絶縁膜の膜厚より厚くしたことを特徴とする絶縁ゲート型半導体装置。

## 【請求項2】

能動領域となる半導体層を基板分離用絶縁膜によって半導体基板から分離した絶縁ゲート型半導体装置において、第1の導電型とは反対導電型の第2の導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨がる長さを有する第1の導電型のボディコンタクト領域を設けるとともに、前記第1の導電型のボディコンタクト領域と前記第2の導電型のソース領域及び第2の導電型のドレイン領域との境界に位置する第1の導電型の半導体領域の表面に設けた絶縁膜の膜厚を、前記境界の全長にわたってゲート電極の直下のゲート絶縁膜の膜厚より厚くしたことを特徴とする絶縁ゲート型半導体装置。

## 【請求項 3】

能動領域となる半導体層を基板分離用絶縁膜によって半導体基板から分離した絶縁ゲート型半導体装置において、第1の導電型とは反対導電型の第2の導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨がる長さを有する第1の導電型のボディコンタクト領域を設けるとともに、前記第1の導電型のボディコンタクト領域と、第2の導電型のソース領域及び第2の導電型のドレイン領域との境界に位置する第1の導電型の半導体領域の表面に、前記境界の全長にわたってゲート電極の直下のゲート絶縁膜の膜厚より厚い埋込絶縁膜を設けたことを特徴とする絶縁ゲート型半導体装置。

## 【請求項 4】

能動領域となる半導体層を基板分離用絶縁膜によって半導体基板から分離した絶縁ゲート型半導体装置において、支柱状の主ゲート電極と梁状導電体パターンからなる非対称なT字状のゲート電極を設けるとともに、前記梁状導電体パターンの少なくとも一部が実効的なゲート電極として機能し、且つ、第1の導電型のボディコンタクト領域と、第1の導電型とは反対導電型の第2の導電型のソース領域及び第2の導電型のドレイン領域の一方とがpn接合を形成していることを特徴とする絶縁ゲート型半導体装置。

## 【請求項 5】

能動領域となる半導体層を基板分離用絶縁膜によって半導体基板から分離した絶縁ゲート型半導体装置の製造方法において、前記第1の導電型の半導体層の表面に部分的に膜厚の異なるゲート絶縁膜を設ける工程、前記ゲート絶縁膜の厚膜部に梁状導電体パターンを設けるとともに、前記ゲート絶縁膜上に支柱状の主ゲート電極を設けてT字状のゲート電極を形成する工程、前記ゲート電極の側面にサイドウォールを形成する工程、前記主ゲート電極及び梁状導電体パターンをマスクとして不純物を導入して第1の導電型とは反対導電型の第2の導電型のソース領域及び第2の導電型のドレイン領域を形成する工程、前記梁状導電体パターンをマスクとして不純物を導入して前記第2の導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨がる長さを有する第1の導電型のボディコンタクト領域を形成する工程、及び、全面に金属膜を堆積させたのち熱処理を行うことによってシリサイド電極を形成する工程を有することを特徴とする絶縁ゲート型半導体装置の製造方法。

## 【請求項 6】

能動領域となる半導体層を基板分離用絶縁膜によって半導体基板から分離した絶縁ゲート型半導体装置の製造方法において、前記第1の導電型の半導体層の表面に部分的に膜厚の異なるゲート絶縁膜を設ける工程、前記ゲート絶縁膜の厚膜部に梁状導電体パターンを設けるとともに、前記ゲート絶縁膜上に支柱状の主ゲート電極を設けてT字状のゲート電極を形成する工程、前記ゲート電極の側面にサイドウォールを形成する工程、前記主ゲート電極及び梁状導電体パターンをマスクとして不純物を導入して第1の導電型とは反対導電型の第2の導電型のソース領域及び第2の導電型のドレイン領域を形成する工程、前記梁状導電体パターンをマスクとして不純物を導入して前記第2の導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨がる長さを有する第1の導電型のボディコンタクト領域を形成する工程、及び、前記梁状導電体パターンを除去したのち全面に金属膜を堆積させ、熱処理を行うことによってシリサイド電極を形成する工程を有することを特徴とする絶縁ゲート型半導体装置の製造方法。

## 【請求項 7】

能動領域となる半導体層を基板分離用絶縁膜によって半導体基板から分離した絶縁ゲート型半導体装置の製造方法において、前記第1の導電型の半導体層の表面に深さの異なる溝を形成し、前記溝を絶縁物によって埋め込むことによって素子分離絶縁膜と素子内分離絶縁膜を形成する工程、ゲート絶縁膜上にゲート電極を設ける工程、前記ゲート電極の側面にサイドウォールを形成する工程、前記ゲート電極及び前記素子内分離絶縁膜をマスクとして不純物を導入して第1の導電型とは反対導電型の第2の導電型のソース領域及び第2の導電型のドレイン領域を形成する工程、前記梁状導電体パターンをマスクとして不純物を導入して前記第2の導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨がる長さを有する第1の導電型のボディコンタクト領域を形成する工程、及び、前記梁状導電体パターンを除去したのち全面に金属膜を堆積させ、熱処理を行うことによってシリサイド電極を形成する工程を有することを特徴とする絶縁ゲート型半導体装置の製造方法。

10

20

30

40

50

2の導電型のドレイン領域を形成する工程、前記素子内分離絶縁膜をマスクとして不純物を導入して前記第2の導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨がる長さを有する第1の導電型のボディコンタクト領域を形成する工程、及び、全面に金属膜を堆積させ、熱処理を行うことによってシリサイド電極を形成する工程を有することを特徴とする絶縁ゲート型半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は絶縁ゲート型半導体装置及びその製造方法に関するものであり、特に、SOI (Silicon On Insulator) 基板を用いたMOSFET等の絶縁ゲート型半導体装置 (IGFET) におけるボディコンタクト領域の形成に伴う短絡、寄生容量の増加、或いは、チップサイズの増加を防止するための構成に特徴のある絶縁ゲート型半導体装置及びその製造方法に関するものである。 10

##### 【0002】

##### 【従来の技術】

従来、MOS型半導体装置においては、ゲート電極直下のチャネル領域の形成される半導体領域にキャリアが蓄積することによってしきい値電圧  $V_{th}$  やドレン電流  $I_{ds}$  が変動することがあり、半導体領域がフローティング状態となるSOI-MOS型半導体装置、特に、半導体領域が完全に空乏化しないPD (Partially Depleted) SOI-MOS型半導体装置において問題となる。 20

##### 【0003】

この様なしきい値電圧  $V_{th}$  等の変動を防止するために、チャネル領域の形成される半導体領域に対してボディコンタクトを取ることによって蓄積したキャリアを引く抜くことが行われているので、ここで、図14及び図15を参照して従来のボディコンタクト領域を設けたMOS型半導体装置を説明する。 30

##### 【0004】

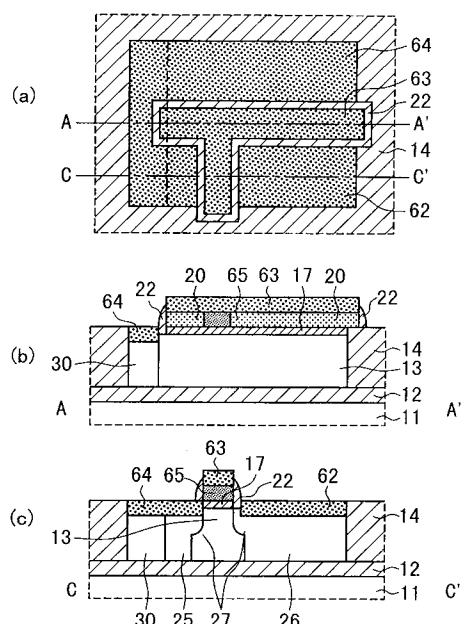

##### 図14参照

図14は、従来のMOSFETの一例を示す説明図であり、図14(a)は平面図、図14(b)は図14(a)におけるA-A'を結ぶ一点鎖線に沿った断面図であり、また、図14(c)は図14(a)におけるB-B'を結ぶ一点鎖線に沿った断面図である。 30

但し、この場合には、nチャネル型MOSFETのみを示すが、pチャネル型MOSFETにおいても導電型、したがって、用いる不純物が異なるだけで実質的には同じである。

##### 【0005】

まず、p型シリコン基板71の表面側にp型ウエル領域72を設けるとともに、LOCOS(選択酸化)法或いはSTI(Shallow Trench Isolation: シャロートレンチ分離)法を用いて素子形成領域を囲む素子分離酸化膜73を形成すると同時に、ボディコンタクト領域を分離するための素子内分離酸化膜74を形成する。 40

##### 【0006】

次いで、p型ウエル領域72の露出表面にゲート酸化膜75を形成したのち、全面にアモルファスシリコン膜等の電極用被膜を堆積させ、イオン注入等によって導電性を付与したのち、エッチングすることによってゲート電極76を形成し、次いで、ゲート電極76をマスクとしてP等のn型不純物をイオン注入することによって追い込み拡散領域77を形成する。

##### 【0007】

次いで、 $\text{SiO}_2$  膜を全面に堆積させたのち異方性エッティングを施すことによってゲート電極76の側面等にサイドウォール78を形成し、次いで、ボディコンタクト形成領域をレジストでマスクした状態で、ゲート電極76及びサイドウォール78をマスクとしてPイオンを注入することによってn型ソース領域79及びn型ドレン領域80を形成する 50

。

#### 【0008】

次いで、n型ソース領域79及びn型ドレイン領域80をレジストでマスクした状態で、ボディコンタクト形成領域にBをイオン注入することによってボディコンタクト領域81を形成し、次いで、全面にCo膜を堆積させたのち、熱処理を施すことによってシリサイド化させてシリコンが露出している領域にCoSi及びCoSi<sub>2</sub>からなるシリサイド層を形成する。

#### 【0009】

次いで、未反応のCo膜を選択的に除去したのち、再び、熱処理を施すことによってシリサイド層内のCoSiをCoSi<sub>2</sub>に変換することによってCoSi<sub>2</sub>層82～85を形成し、ボディコンタクト電極を有するMOS型半導体装置の基本構成が完成する。

10

なお、CoSi<sub>2</sub>層83はソース電極、CoSi<sub>2</sub>層84はドレイン電極、及び、CoSi<sub>2</sub>層85はボディコンタクト電極となる。

#### 【0010】

しかし、近年における半導体装置の高集積化或いは高速化の進展に伴い、素子を微細化するとともに基板との間の寄生容量を低減するために、能動素子領域を基板から絶縁分離したSOI基板を用いたMOS型半導体装置が注目を集めているが、この様なSOI-MOS型半導体装置においては能動素子領域が完全に絶縁分離されてフローティング状態になっているので、図14の場合のように、ウエル領域を介してボディコンタクト領域によってゲート電極直下の電位を制御することが不可能となる。

20

#### 【0011】

したがって、従来のSOI-MOS型半導体装置においては、ゲート電極のゲート幅方向（即ち、チャネル長方向と垂直方向）にチャネルが形成される半導体領域と同導電型の突出した島状領域を設け、この島状領域にボディコンタクト電極を設けることが提案されている（必要ならば、例えば、特開平8-125187号公報）。

#### 【0012】

しかし、この様なボディコンタクトのための突出した島状領域は素子の微細化の障害となるので、素子の微細化が進に連れて、セパレータを用いることによってソース・ドレイン領域の近傍にボディコンタクト領域を設けるとともに、自己整合的にコタクト電極を形成するためにシリサイド電極の使用が試みられているので、この様なセパレータを設けた従来のSOI-MOSFETを図15を参照して説明する。

30

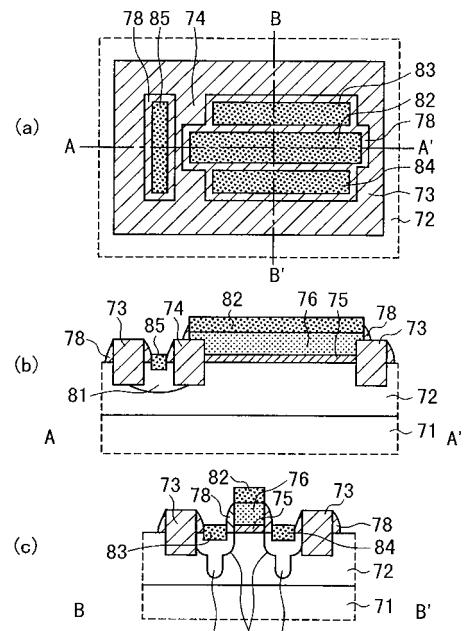

#### 【0013】

##### 図15参照

図15は、従来のSOI-MOSFETの一例を示す説明図であり、図15(a)は平面図、図15(b)は図15(a)におけるA-A'を結ぶ一点鎖線に沿った断面図であり、また、図15(c)は図15(a)におけるB-B'を結ぶ一点鎖線に沿った断面図である。

但し、この場合も、nチャネル型MOSFETのみを示すが、pチャネル型MOSFETにおいても導電型、したがって、用いる不純物が異なるだけで実質的には同じである。

#### 【0014】

まず、シリコン基板91の所定深さに酸素イオンを注入したのち熱処理を行って酸素イオン注入領域をSiO<sub>2</sub>に変換してBOX(Buried Oxide)、即ち、基板分離酸化膜92を形成し、次いで、表面にBをイオン注入することによってp型シリコン層93を形成する。

40

#### 【0015】

次いで、STI(シャロートレンチ分離)法を用いて素子形成領域を囲む素子分離酸化膜94を形成したのち、p型シリコン層93の表面にゲート絶縁膜95を形成し、次いで、全面にアモルファスシリコン膜等の電極用被膜を堆積させ、イオン注入等によって導電性を付与したのち、エッチングすることによってT字状の電極パターンを形成する

このT字状の電極パターンの支柱の部分がゲート電極96となり、梁状の部分がゲート動

作とは関係のないセパレータ 9 7 となる。

【0016】

次いで、ゲート電極 9 6 をマスクとして P 等の n 型不純物をイオン注入することによって追い込み拡散領域 9 8 を形成したのち、 SiO<sub>2</sub> 膜を全面に堆積させて異方性エッチングを施すことによってゲート電極 9 6 の側面等にサイドウォール 9 9 を形成し、次いで、ボディコンタクト形成領域をレジストでマスクした状態で、ゲート電極 9 6 、セパレータ 9 7 、及び、サイドウォール 9 9 をマスクとして P イオンを注入することによって n 型ソース領域 1 0 0 及び n 型ドレイン領域 1 0 1 を形成する。

【0017】

次いで、n 型ソース領域 1 0 0 及び n 型ドレイン領域 1 0 1 をレジストでマスクした状態で、ボディコンタクト形成領域に BF<sub>2</sub> をイオン注入することによってボディコンタクト領域 1 0 2 を形成したのち、全面に Co 膜を堆積させ、次いで、熱処理を施すことによってシリサイド化させてシリコンが露出している領域に CoSi 及び CoSi<sub>2</sub> からなるシリサイド層を形成する。

【0018】

次いで、未反応の Co 膜を選択的に除去したのち、再び、熱処理を施すことによってシリサイド層内の CoSi を CoSi<sub>2</sub> に変換することによって CoSi<sub>2</sub> 層 1 0 3 ~ 1 0 6 を形成し、ボディコンタクト電極を有する SOI - MOS 型半導体装置の基本構成が完成する。

なお、 CoSi<sub>2</sub> 層 1 0 4 はソース電極、 CoSi<sub>2</sub> 層 1 0 5 はドレイン電極、及び、 CoSi<sub>2</sub> 層 1 0 6 はボディコンタクト電極となる。

【0019】

この様な SOI - MOSFET においては、セパレータ 9 7 がイオン注入マスクの一部となるとともに、ソース・ドレイン電極となる CoSi<sub>2</sub> 層 1 0 4 , 1 0 5 電極、ボディコンタクト電極となる CoSi<sub>2</sub> 層 1 0 6 とをサイドウォール 9 9 を介して分離しているので、ボディコンタクト電極とソース・ドレイン電極とが短絡することがない。

【0020】

この場合、チャネル領域が形成される p 型シリコン層 9 3 は、ボディコンタクト領域 1 0 2 を介して所定の電位に設定されるので、 V<sub>th</sub> の変動が防止され、また、 n 型ソース領域 1 0 0 或いは n 型ドレイン領域 1 0 1 とボディコンタクト領域 1 0 2 とは p 型シリコン層 9 3 を介して接しているので、 p<sup>+</sup> / n<sup>+</sup> 接合が形成されることなく、したがって、ドレイン耐圧が低下することがない。

【0021】

【発明が解決しようとする課題】

しかし、この様なセパレータを用いた SOI - MOSFET においては、セパレータの側壁に設けたサイドウォールによってボディコンタクト電極とソース・ドレイン電極との短絡を防止しているが、サイドウォールの高さが低いとシリサイド化工程においては、サイドウォールの表面に堆積した金属膜にも Si が拡散してゆき合金化し、この部分のシリサイドを除去することができないので、このシリサイド層が介してボディコンタクト電極とソース・ドレイン電極とが短絡するという問題がある。

【0022】

また、通常の使用状態のように、トランジスタをアレイ状に配列した場合、隣接するセパレータ同士が異電位である場合、短絡を防止するために両者の間を一定の距離だけ離間させる必要があり、それによって、チップ面積が増加するという問題がある。

【0023】

さらに、セパレータの幅は、セパレータを形成する際のフォトリソグラフィー工程の重合せ精度、セパレータのエッチング工程における仕上がり寸法のバラツキ、及び、ボディコンタクト領域形成工程におけるイオン注入マスクの重ね合わせ精度等に依存するため、一つのトランジスタに占める面積はチャネル形成に機能するゲート電極と同じオーダーとなり寄生容量が増大するため、ゲート遅延が大きくなつてデバイス性能を劣化させるとい

10

20

30

40

50

う問題がある。

【0024】

したがって、本発明は、電極間の短絡を防止するとともに、セパレータ同士の短絡を防止し、また、寄生容量の増大を防止することを目的とする。

【0025】

【課題を解決するための手段】

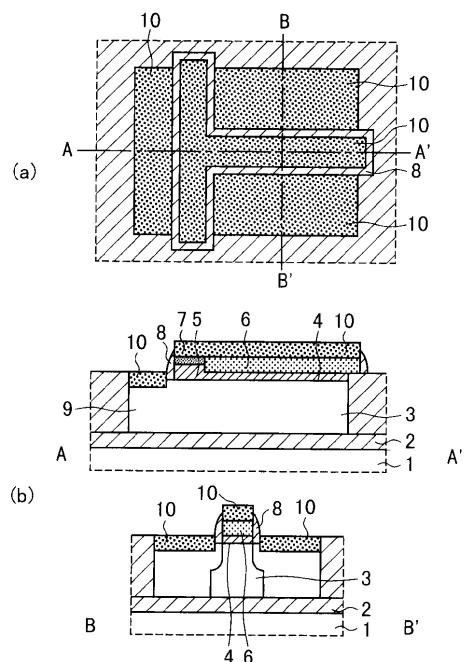

ここで、図1を参照して本発明における課題を解決するための手段を説明する。

なお、図1は、本発明の原理的構成の説明図であり、図1(a)は平面図、図1(b)は図1(a)におけるA-A'を結ぶ一点鎖線に沿った断面図であり、また、図1(c)は図1(a)におけるB-B'を結ぶ一点鎖線に沿った断面図である。

10

図1(a)乃至(b)参照

(1) 本発明は、能動領域となる半導体層3を基板分離用絶縁膜2によって半導体基板1から分離した絶縁ゲート型半導体装置において、支柱状の主ゲート電極6と梁状導電体パターン7からなるT字状のゲート電極を設け、梁状導電体パターン7によって第1の導電型とは反対導電型の第2の導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨がる長さを有する第1の導電型のボディコンタクト領域9を第2の導電型のソース領域及び第2の導電型のドレイン領域から分離するとともに、梁状導電体パターン7の直下のゲート絶縁膜の膜厚を梁状導電体パターン7の全長にわたって主ゲート電極6の直下のゲート絶縁膜4の膜厚より厚くしたことを特徴とする。

20

【0026】

この様に、梁状導電体パターン7、即ち、セパレータを有するT字状のゲート電極を設けた場合、梁状導電体パターン7の直下のゲート絶縁膜の膜厚を主ゲート電極6の直下のゲート絶縁膜4の膜厚より厚くすることによって、即ち、厚膜部5を設けることによってセパレータに起因する寄生容量が低減される。

【0027】

また、上記(1)において、ゲート電極の側壁にサイドウォール8を設けるとともに、少なくとも半導体層3の露出表面にシリサイド電極10を設けることが望ましい。

即ち、セパレータの直下はゲート絶縁膜4の厚膜部5となっているので、それに伴って主ゲート電極6の膜厚も厚くなるので、サイドウォール8の高さも高くなり、それによってシリサイド電極10が互いに接続することができるので、各シリサイド電極10間の短絡を防止することができる。

30

また、高いサイドウォール8を設けることによって隣接する素子のセパレータ間の分離はより確実になるので、短絡防止のための余分なスペースが不要になり、それによってトランジスタピッチを縮小することができる。

【0028】

(2) また、本発明は、能動領域となる半導体層3を基板分離用絶縁膜2によって半導体基板1から分離した絶縁ゲート型半導体装置において、第1の導電型とは反対導電型の第2の導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨がる長さを有する第1の導電型のボディコンタクト領域9を設けるとともに、第1の導電型のボディコンタクト領域9と第2の導電型のソース領域及び第2の導電型のドレイン領域との境界に位置する第1の導電型の半導体領域の表面に設けた絶縁膜の膜厚を、境界の全長にわたってゲート電極の直下のゲート絶縁膜4の膜厚より厚くしたことを特徴とする。

40

【0029】

この様に、一導電型のボディコンタクト領域9と逆導電型のソース・ドレイン領域との境界に位置する一導電型半導体領域の表面に設けた絶縁膜の膜厚を、ゲート電極の直下のゲート絶縁膜4の膜厚より厚くすることによって、最終的にセパレータが不要になるので、セパレータに起因する寄生容量が発生することはなく、且つ、セパレータ同士を分離するためのスペースも不要になるのでトランジスタピッチの縮小が可能になる。

50

## 【0030】

また、上記(2)において、ゲート電極の側壁にサイドウォール8を設けるとともに、少なくとも半導体層3の露出表面にシリサイド電極10を設けることが望ましい。

即ち、高いサイドウォール8を設けることによって隣接する素子のセパレータ間を確実に絶縁分離されるので余分な分離のためのスペースが不要になり、且つ、セパレータと主ゲート電極6との接続部におけるトランジスタ性能の変化を考慮する必要がなくなる。

また、一導電型のボディコンタクト領域9と逆導電型のソース・ドレイン領域との境界に位置する一導電型半導体領域の表面には厚い絶縁膜、即ち、厚膜部5が設けられているので、シリサイド電極10を形成する際に、一導電型のボディコンタクト領域9と逆導電型のソース・ドレイン領域との境界に位置する一導電型半導体領域の表面がシリサイド化される危険性が全くなくなる。10

## 【0031】

(3) また、本発明は、能動領域となる半導体層3を基板分離用絶縁膜2によって半導体基板1から分離した絶縁ゲート型半導体装置において、第1の導電型とは反対導電型の第2の導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨がる長さを有する第1の導電型のボディコンタクト領域9を設けるとともに、第1の導電型のボディコンタクト領域9と第2の導電型のソース領域及び第2の導電型のドレイン領域との境界に位置する第1の導電型の半導体領域の表面に、境界の全長にわたってゲート電極の直下のゲート絶縁膜4の膜厚より厚い埋込絶縁膜を設けたことを特徴とする。20

## 【0032】

この様に、一導電型のボディコンタクト領域9と逆導電型のソース・ドレイン領域との境界に位置する一導電型半導体領域の表面にゲート電極の直下のゲート絶縁膜4の膜厚より厚い埋込絶縁膜、即ち、素子内分離絶縁膜を設けることによって、セパレータが不要になるので、セパレータに起因する寄生容量が発生することではなく、且つ、セパレータと主ゲート電極6との接続部におけるトランジスタ性能の変化を考慮する必要がなくなる。

また、セパレータ同士を分離するためのスペースも不要になるのでトランジスタピッチの縮小が可能になる。

## 【0035】

(4) また、本発明は、能動領域となる半導体層3を基板分離用絶縁膜2によって半導体基板1から分離した絶縁ゲート型半導体装置において、支柱状の主ゲート電極6と梁状導電体パターン7からなる非対称なT字状のゲート電極を設けるとともに、梁状導電体パターン7の少なくとも一部が実効的なゲート電極として機能し、且つ、第1の導電型のボディコンタクト領域9と、第1の導電型とは反対導電型の第2の導電型のソース領域及び第2の導電型のドレイン領域の一方とがpn接合を形成していることを特徴とする。30

## 【0036】

この様に、L字状或いは非対称なT字状のゲート電極を構成する梁状導電体パターン7の少なくとも一部も実効的なゲート電極とすることによって、実効的なチャネル幅が増加するのでトランジスタ性能が向上する。

また、梁状導電体パターン7はボディコンタクト領域9を形成する際のマスクとして用いていないので、梁状導電体パターン7の幅を主ゲート電極6の幅と同じにできる。40

## 【0037】

また、本発明は、上記(4)または(5)において、ゲート電極の側壁にサイドウォール8を設けるとともに、少なくとも半導体層3の露出表面にシリサイド電極10を設けることが望ましい。

即ち、このようにシリサイド電極10を設けることによって、ボディコンタクト領域9と同電位で使用する領域に対する電極を一体に形成することができ、一方、ボディコンタクト領域9と異電位に設定する領域はサイドウォール8によって電気的に絶縁することができる。50

## 【0038】

また、本発明は、上記(1)乃至(5)のいずれかにおいて、ゲート電極の側端部の半導体層3に、追い込み拡散領域を有することを特徴とする。

即ち、追い込み拡散領域を設けることによってゲート電極の側端部にオフセット領域が形成されることが防止され、特に、サイドウォール8を設ける場合に有効になる。

## 【0039】

(5) また、本発明は、能動領域となる半導体層3を基板分離用絶縁膜2によって半導体基板1から分離した絶縁ゲート型半導体装置の製造方法において、第1の導電型の半導体層3の表面に部分的に膜厚の異なるゲート絶縁膜4を設ける工程、ゲート絶縁膜4の厚膜部5に梁状導電体パターン7を設けるとともに、ゲート絶縁膜4上に支柱状の主ゲート電極6を設けてT字状のゲート電極を形成する工程、ゲート電極の側面にサイドウォール8を形成する工程、主ゲート電極6及び梁状導電体パターン7をマスクとして不純物を導入して第1の導電型とは反対導電型の第2の導電型のソース領域及び第2の導電型のドレイン領域を形成する工程、梁状導電体パターン7をマスクとして不純物を導入して第2の導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨る長さを有する第1の導電型のボディコンタクト領域9を形成する工程、及び、全面に金属膜を堆積させたのち熱処理を行うことによってシリサイド電極10を形成する工程を有することを特徴とする。10

## 【0040】

この様に、梁状導電体パターン7、即ち、セパレータをゲート絶縁膜4の厚膜部5に設けることによって、サイドウォール8の高さを高くすることができ、それによって、シリサイド電極10がサイドウォール8上に形成されるのを防止することができ、シリサイド電極10間の短絡を防止することができる。20

## 【0041】

(6) また、本発明は、能動領域となる半導体層3を基板分離用絶縁膜2によって半導体基板1から分離した絶縁ゲート型半導体装置の製造方法において、第1の導電型の半導体層3の表面に部分的に膜厚の異なるゲート絶縁膜4を設ける工程、ゲート絶縁膜4の厚膜部5に梁状導電体パターン7を設けるとともに、ゲート絶縁膜4上に支柱状の主ゲート電極6を設けてT字状のゲート電極を形成する工程、ゲート電極の側面にサイドウォール8を形成する工程、主ゲート電極6及び梁状導電体パターン7をマスクとして不純物を導入して第1の導電型とは反対導電型の第2の導電型のソース領域及び第2の導電型のドレイン領域を形成する工程、梁状導電体パターン7をマスクとして不純物を導入して導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨る長さを有する第1の導電型のボディコンタクト領域9を形成する工程、及び、梁状導電体パターン7を除去したのち全面に金属膜を堆積させ、熱処理を行うことによってシリサイド電極10を形成する工程を有することを特徴とする。30

## 【0042】

この様に、全面にシリサイド電極10を形成するための金属膜を堆積させる前に、不純物導入マスクとなる梁状導電体パターン7、即ち、セパレータを除去することによって、セパレータによる寄生容量をなくすことができる。40

また、シリサイド化工程においては、セパレータの除去部には、厚膜部5が存在するので、金属膜の堆積工程の前の洗浄工程等において半導体層3が露出することがなく、したがって、除去部にシリサイド電極10が形成されることなくなる。

## 【0043】

(7) また、本発明は、能動領域となる半導体層3を基板分離用絶縁膜2によって半導体基板1から分離した絶縁ゲート型半導体装置の製造方法において、第1の導電型の半導体層3の表面に深さの異なる溝を形成し、溝を絶縁物によって埋め込むことによって素子分離絶縁膜と素子内分離絶縁膜を形成する工程、ゲート絶縁膜4上にゲート電極を設ける工程、ゲート電極の側面にサイドウォール8を形成する工程、ゲート電極及び素子内分離絶縁膜をマスクとして不純物を導入して第1の導電型とは反対導電型の第2の導電型のソ50

ース領域及び第2の導電型のドレイン領域を形成する工程、素子内分離絶縁膜をマスクとして不純物を導入して第2の導電型のソース領域のチャネル長方向の外側端部と第2の導電型のドレイン領域のチャネル長方向の外側端部に跨がる長さを有する第1の導電型のボディコンタクト領域9を形成する工程、及び、全面に金属膜を堆積させ、熱処理を行うことによってシリサイド電極10を形成する工程を有することを特徴とする。

#### 【0044】

この様に、ボディコンタクト領域9とソース・ドレイン領域との間を埋込絶縁物からなる素子内分離絶縁膜によって分離することによって、セパレータが不要になり、トランジスタピッチの縮小が可能になり、且つ、セパレータと主ゲート電極6との接続部におけるトランジスタ特性の変化を考慮する必要がなくなる。

10

#### 【0045】

また、本発明は、上記(6)乃至(8)のいずれかにおいて、サイドウォール8を形成する前に、不純物を導入してゲート電極の側端部に追い込み拡散領域を形成する工程を有することが望ましい。

即ち、サイドウォール8を形成する前に、追い込み拡散領域を形成することによって、サイドウォール8の直下がオフセット領域になることを防止することができる。

#### 【0046】

##### 【発明の実施の形態】

ここで、図2乃至図6を参照して本発明の第1の実施の形態のSOI-MOSFETの製造工程を説明するが、説明を簡単にするために、nチャネル型MOSFETの製造工程として説明する。

20

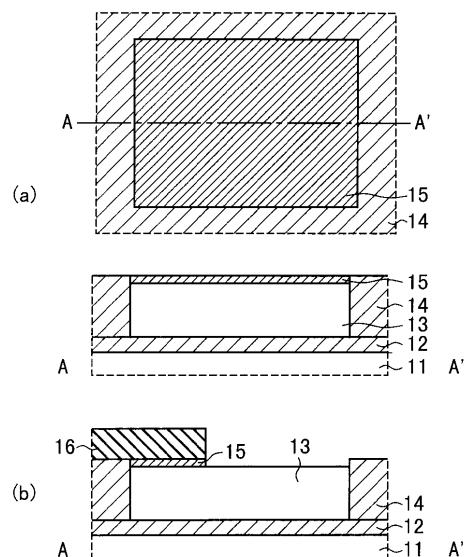

#### 図2(a)参照

図2(a)の上側の図は平面図であり、下側の図は平面図のA-A'を結ぶ一点鎖線に沿った断面図である。

まず、シリコン基板11の所定深さに酸素イオンを注入したのち熱処理を行って酸素イオン注入領域をSiO<sub>2</sub>に変換して基板分離酸化膜12を形成し、次いで、表面にBをイオン注入することによってp型シリコン層13を形成する。

次いで、STI法を用いて素子形成領域の周囲に素子分離酸化膜14を形成したのち、p型シリコン層13の表面に熱酸化によってゲート絶縁膜15を形成する。

#### 【0047】

30

#### 図2(b)参照

次いで、ボディコンタクト形成領域を覆うレジストパターン16をマスクとしてウェット・エッチングを施すことによって、ゲート絶縁膜15の露出部を除去する。

#### 【0048】

#### 図3(c)参照

次いで、レジストパターン16を除去したのち、熱酸化によって厚さが、例えば、4nmのゲート絶縁膜17を形成する。

この際、ゲート絶縁膜15の残部は、厚さが、例えば、3.5nm余分に厚い7.5nmの厚膜部18となり、ゲート絶縁膜17に膜厚差が形成される。

#### 【0049】

40

#### 図3(d)参照

なお、図3(d)の上側の図は平面図であり、下側の図は平面図のA-A'を結ぶ一点鎖線に沿った断面図である。

次いで、全面に、厚さが、例えば、180nmのアモルファスシリコン膜を堆積させたのち、Pをイオン注入し、次いで、アニールすることによってn型多結晶シリコン膜に変換したのち、T字状のレジストパターン19をマスクとしてドライ・エッチングすることによって幅が、例えば、0.18μmの支柱状のゲート電極20と、幅が、例えば、0.50μmの梁状のセパレータ21を形成する。

#### 【0050】

次いで、ウェット・エッチングを施すことによって、ゲート絶縁膜17及び厚膜部18の

50

露出部を除去して p 型シリコン層 13 の表面を露出させる。

なお、図においては、セパレータ 21 とゲート電極 20 とを異なった砂地で表現しているが、同じ n 型多結晶シリコン膜によって構成されるものである。

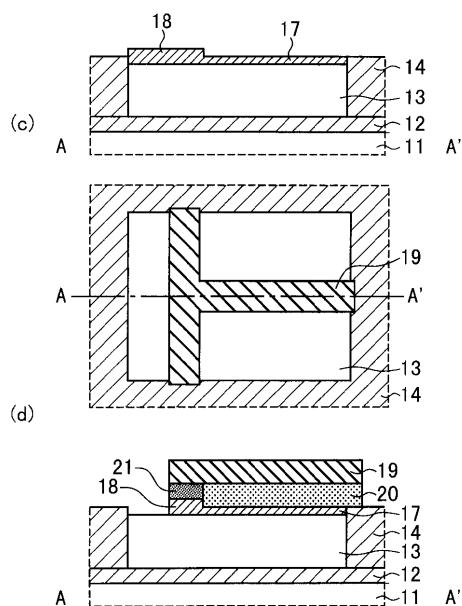

#### 【0051】

図 4 (e) 参照

なお、図 4 (e) の上側の図は平面図であり、真中の図は平面図の A - A' を結ぶ一点鎖線に沿った断面図であり、また、下側の図は平面図の B - B' を結ぶ一点鎖線に沿った断面図である。

次いで、ボディコンタクト形成領域をレジストパターン（図示せず）で被覆したのち、P<sub>i</sub> をイオン注入することによってゲート電極 20 の側端部直下に n 型の追い込み拡散領域 27 を形成する。 10

#### 【0052】

次いで、SiO<sub>2</sub> 膜を全面に堆積させたのち、異方性エッチングを施すことによってゲート電極 20 とセパレータ 21 の側面等にサイドウォール 22 を形成し、次いで、ボディコンタクト形成領域をレジストパターン 23 でマスクした状態で、ゲート電極 20、セパレータ 21、及び、サイドウォール 22 をマスクとして P<sub>i</sub> イオン 24 を注入することによって n 型ソース領域 25 及び n 型ドレイン領域 26 を形成する。

#### 【0053】

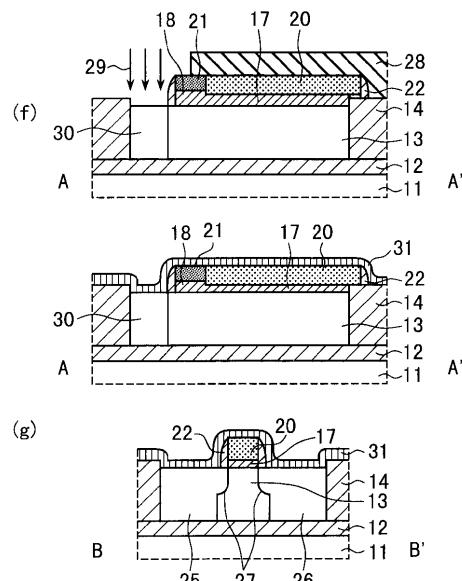

図 5 (f) 参照

次いで、レジストパターン 23 を除去したのち、n 型ソース領域 25 及び n 型ドレイン領域 26 をレジストパターン 28 でマスクした状態で、B<sub>i</sub> イオン 29 を注入することによってボディコンタクト領域 30 を形成する。 20

#### 【0054】

図 5 (g) 参照

なお、上側の図は A - A' に沿った断面図であり、下側の図は B - B' に沿った断面図である。

次いで、レジストパターン 28 を除去したのち、洗浄を行い、次いで、スパッタリング法を用いて全面に Co 膜 31 を堆積させる。

#### 【0055】

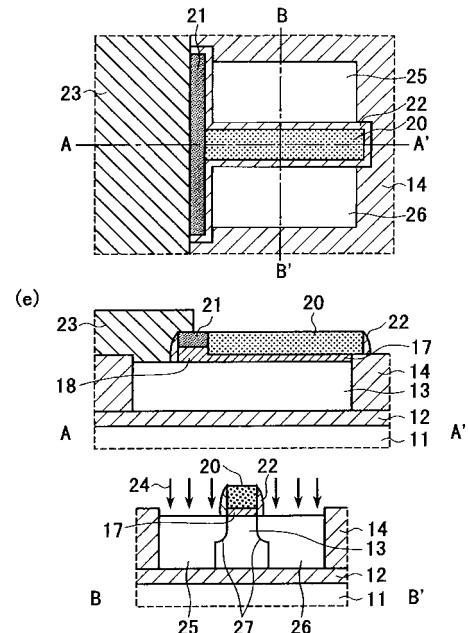

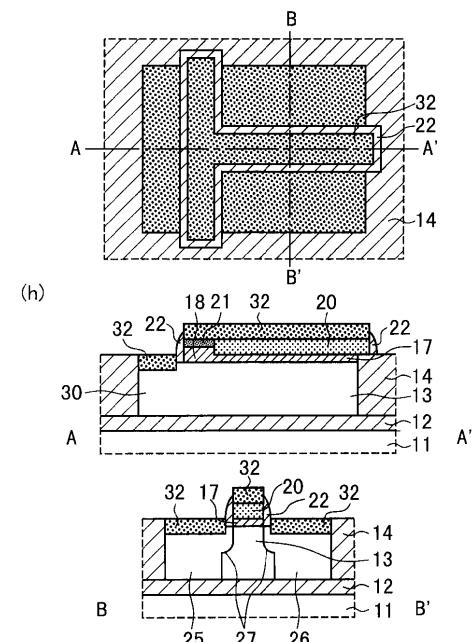

図 6 (h) 参照

なお、図 6 (h) の上側の図は平面図であり、真中の図は平面図の A - A' を結ぶ一点鎖線に沿った断面図であり、また、下側の図は平面図の B - B' を結ぶ一点鎖線に沿った断面図である。 30

次いで、N<sub>2</sub> 雰囲気中で、急速熱処理（Rapid Thermal Annealing : R T A）を施すことによって、Co 膜 31 と Si とを反応させて CoSi 層を形成したのち、H<sub>2</sub>SO<sub>4</sub> : H<sub>2</sub>O<sub>2</sub> = 3 : 1 の混合液でエッチングを行うことによって素子分離酸化膜 14 及びサイドウォール 22 等の絶縁膜の上の未反応 Co 膜を除去する。

#### 【0056】

次いで、再び、N<sub>2</sub> 雰囲気中で R T A 処理を施すことによって CoSi 層と Si とを再び反応させて、ゲート電極 20、セパレータ 21、n 型ソース領域 25、n 型ドレイン領域 26、及び、ボディコンタクト領域 30 の表面に低抵抗相の CoSi<sub>2</sub> 層 32 を形成することによって、SOI-MOSFET の基本構造が完成する。 40

#### 【0057】

この場合、セパレータ 21 の側面に形成されたサイドウォール 22 の高さは、厚膜部 18 の存在によって高くなっているので、シリサイド化反応の際に、サイドウォール 22 の表面上の Co 膜 31 がシリサイド化することなく、したがって、隣接する素子のセパレータ 21 同士がサイドウォール 22 上に形成されたシリサイド層を介して電気的に接続されることないので、素子ピッチを縮小することができる。

また、セパレータ 21 をイオン注入マスクとして作用する程度の膜厚にするために、結果的にゲート電極 20 の膜厚も厚くなるのでゲート電極 20 の側壁のサイドウォール 22 も 50

高くなるので、 $\text{CoSi}_2$  層 32 間の短絡も防止することができる。

**【0058】**

また、セパレータ 21 の直下には厚い厚膜部 18 が存在するので、セパレータ 21 に起因する寄生容量を大幅に低減することが可能になり、それによって、ゲート遅延を低減することができる。

なお、厚膜部 18 を形成するための 2 段階の工程は、周辺回路を構成する高耐圧トランジスタの形成工程と同じ工程とすることによって、工程数が増加するこがない。

**【0059】**

次に、図 7 及び図 8 を参照して、本発明の第 2 の実施の形態の SOI-MOSFET の製造工程を説明する。

10

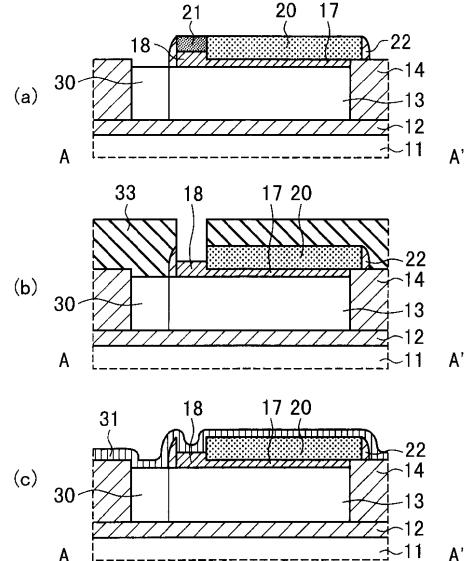

図 7 (a) 参照

まず、上記の第 1 の実施の形態と全く同様に、図 5 (f) までの工程を行ってボディコンタクト領域 30 を形成したのち、レジストパターン 28 を除去することによって、図 7 (a) の構造が得られる。

**【0060】**

図 7 (b) 参照

次いで、セパレータ 21 に対応する形状の開口部を有するレジストパターン 33 をマスクとしてドライ・エッチングを行うことによって、セパレータ 21 のみを選択的に除去する。

**【0061】**

20

図 7 (c) 参照

次いで、レジストパターン 33 を除去したのち、洗浄を行い、次いで、スパッタリング法を用いて全面に Co 膜 31 を堆積させる。

この洗浄工程において、セパレータ 21 の除去部には厚膜部 18 が存在するので、エッチングによって、除去部において  $\text{SiO}_2$  膜が除去されて p 型シリコン層が露出することがなく、この部分において p 型シリコン層 13 と Co 膜 31 とが接触することがない。

**【0062】**

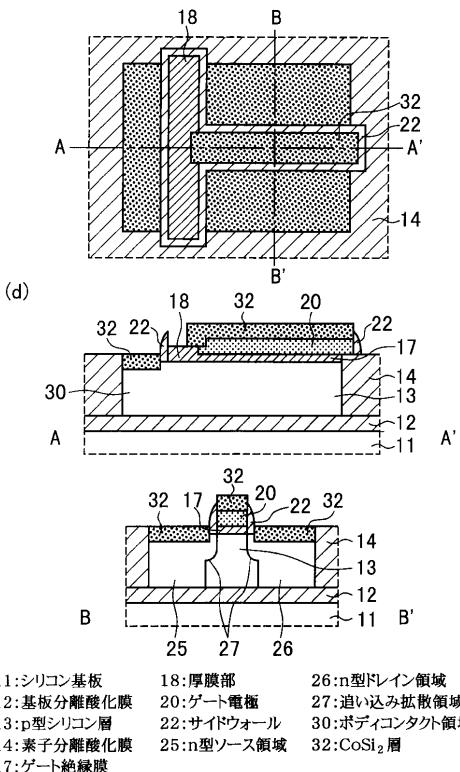

図 8 (d) 参照

なお、図 8 (d) の上側の図は平面図であり、真中の図は平面図の A-A' を結ぶ一点鎖線に沿った断面図であり、また、下側の図は平面図の B-B' を結ぶ一点鎖線に沿った断面図である。

30

次いで、 $\text{N}_2$  雰囲気中で、RTA 处理を施すことによって、Co 膜 31 と Si とを反応させて  $\text{CoSi}$  層を形成したのち、 $\text{H}_2\text{SO}_4 : \text{H}_2\text{O}_2 = 3 : 1$  の混合液でエッチングを行うことによって素子分離酸化膜 14、厚膜部 18、及び、サイドウォール 22 等の絶縁膜の上の未反応 Co 膜を除去する。

**【0063】**

次いで、再び、 $\text{N}_2$  雰囲気中で RTA 处理を施すことによって  $\text{CoSi}$  層と Si とを再び反応させて、ゲート電極 20、n 型ソース領域 25、n 型ドレイン領域 26、及び、ボディコンタクト領域 30 の表面に低抵抗相の  $\text{CoSi}_2$  層 32 を形成することによって、SOI-MOSFET の基本構造が完成する。

40

**【0064】**

この第 2 の実施の形態においては、イオン注入のためのマスクとなるセパレータ 21 をイオン注入後に除去しているので、セパレータ 21 に起因する寄生容量をなくすことができ、セパレータ 21 に起因するゲート遅延が発生するこがない。

**【0065】**

また、シリサイド化工程において、ゲート電極 20 のゲート幅方向の端部に形成された  $\text{CoSi}_2$  層 32 が多少突出したとしても、厚い厚膜部 18 上であるので、寄生容量が問題となるこがない。

**【0066】**

また、セパレータ 21 を除去しているので、ゲート電極 20 とセパレータ 21 との接続部

50

がなくなるので、接続部によるトランジスタ特性の変化を考慮する必要がなくなる。

【0067】

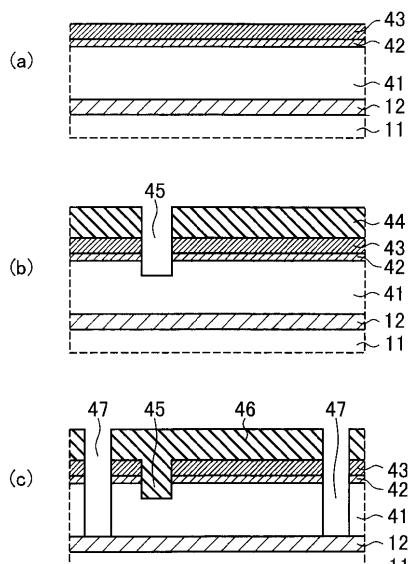

次いで、図9乃至図12を参照して、本発明の第3の実施の形態のSOI-MOSFETの製造工程を説明する。

図9(a)参照

まず、シリコン基板11の所定深さに酸素イオンを注入したのち熱処理を行って酸素イオン注入領域を $\text{SiO}_2$ に変換して基板分離酸化膜12を形成し、次いで、表面にBをイオン注入することによってp型シリコン層41を形成したのち、下地となる $\text{SiO}_2$ 膜42及び、CMP(Chemical Mechanical Polishing)工程におけるストッパーとなる $\text{SiN}$ 膜43を順次形成する。

10

【0068】

図9(b)参照

次いで、レジストパターン44をマスクとしてドライ・エッチングを施すことによって、ボディコントラクト形成領域と他の領域とを分離するためのシャロートレンチ45を形成する。

【0069】

図9(c)参照

次いで、レジストパターン44を除去したのち、新たに設けたレジストパターン46をマスクとしてドライ・エッチングを施すことによって、素子形成領域を囲む基板分離酸化膜12に達する深さの素子分離用トレンチ47を形成する。

20

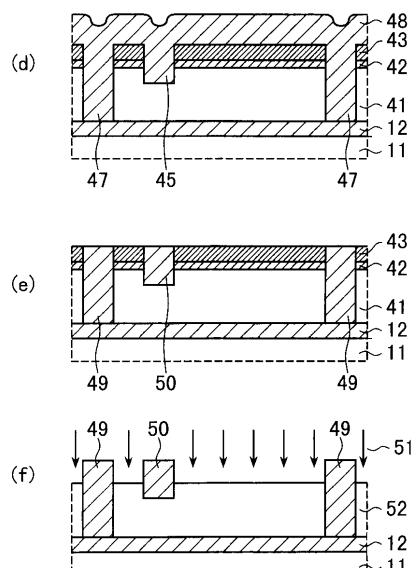

【0070】

図10(d)参照

次いで、HDP(High Density Plasma)-CVD法を用いて全面に $\text{SiO}_2$ 膜48を堆積することによって、シャロートレンチ45及び素子分離用トレンチ47を $\text{SiO}_2$ 膜48によって完全に埋め込む。

20

【0071】

図10(e)参照

次いで、CMP法によって $\text{SiO}_2$ 膜48を研磨することによって、 $\text{SiN}$ 膜43が露出するまで $\text{SiO}_2$ 膜48を除去することによって、素子分離用トレンチ47を埋め込む素子分離酸化膜49とシャロートレンチ45を埋め込む素子内分離酸化膜50を形成する。

30

【0072】

図10(f)参照

次いで、 $\text{SiN}$ 膜43及び $\text{SiO}_2$ 膜42を除去したのち、全面にBイオン51を注入することによってシリコン層41をp型シリコン層52に変換する。

【0073】

図11(g)参照

次いで、素子形成領域の表面に $\text{SiON}$ 膜からなるゲート絶縁膜53を形成する。

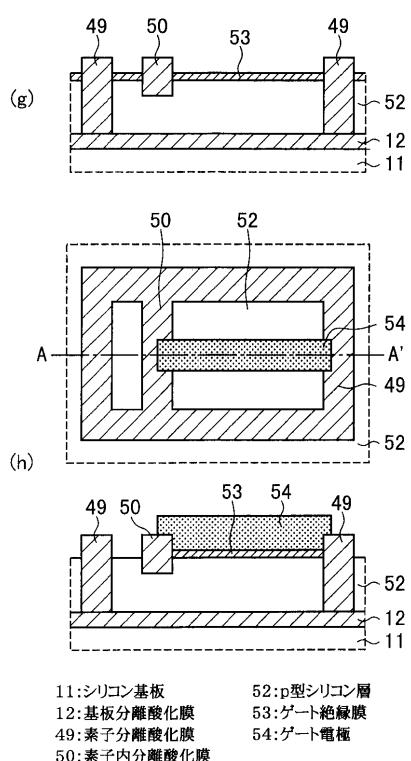

【0074】

図11(h)参照

なお、上側の図は平面図であり、下側の図は平面図のA-A'を結ぶ一点鎖線に沿った断面図である。

40

次いで、全面に、厚さが、例えば、180nmのアモルファスシリコン膜を堆積させたのち、Pをイオン注入し、次いで、アニールすることによってn型多結晶シリコン膜に変換したのち、ドライ・エッチングすることによって幅が、例えば、0.18μmのゲート電極54を形成する。

次いで、ウェット・エッチングを施すことによって、ゲート絶縁膜53の露出部を除去してp型シリコン層52の表面を露出させる。

【0075】

図12(i)参照

なお、図12(i)の上側の図は平面図であり、真中の図は平面図のA-A'を結ぶ一点鎖線に沿った断面図である。

50

鎖線に沿った断面図であり、また、下側の図は平面図の B - B' を結ぶ一点鎖線に沿った断面図である。

次いで、ボディコンタクト形成領域をレジストパターンで被覆したのち、Pをイオン注入することによってn型の追い込み拡散領域5'6'を形成する。

#### 【0076】

次いで、SiO<sub>2</sub>膜を全面に堆積させたのち、異方性エッチングを施すことによってゲート電極5'4'の側面等にサイドウォール5'5'を形成し、次いで、ボディコンタクト形成領域をレジストパターンでマスクした状態で、ゲート電極5'4'及びサイドウォール5'5'をマスクとしてPイオンを注入することによってn型ソース領域5'7'及びn型ドレイン領域5'8'を形成する。

10

#### 【0077】

次いで、レジストパターンを除去したのち、n型ソース領域5'7'及びn型ドレイン領域5'8'をレジストパターンでマスクした状態で、Bイオンを注入することによってボディコンタクト領域3'0'を形成する。

#### 【0078】

以降は上記の第1の実施の形態と全く同様な工程によって、ゲート電極5'4'、n型ソース領域5'7'、n型ドレイン領域5'8'及び、ボディコンタクト領域3'0'の表面に低抵抗相のCoSi<sub>2</sub>層3'2'を形成することによって、SOI-MOSFETの基本構造が完成する。

20

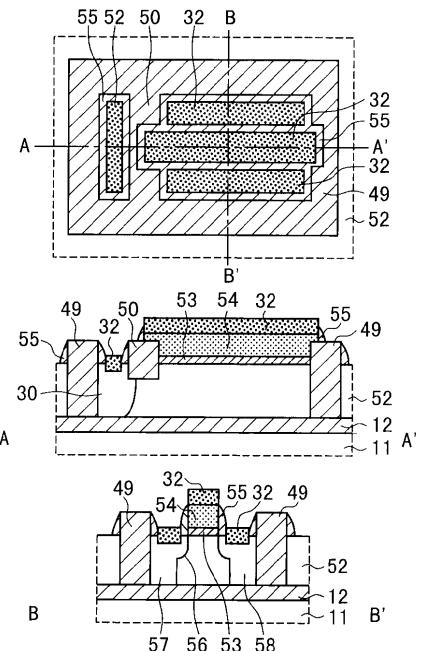

#### 【0079】

この第3の実施の形態においては、予めボディコンタクト形成領域を分離する素子内分離酸化膜5'0'を形成しており、且つ、この素子内分離酸化膜5'0'の厚さは不純物の導入を実質的に阻止する0.08μm以上の厚さであるので、セパレータが不要になり、したがって、上記の第2の実施の形態と同様にセパレータに起因する寄生容量をなくすことができ、また、素子ピッチを縮小することができる。

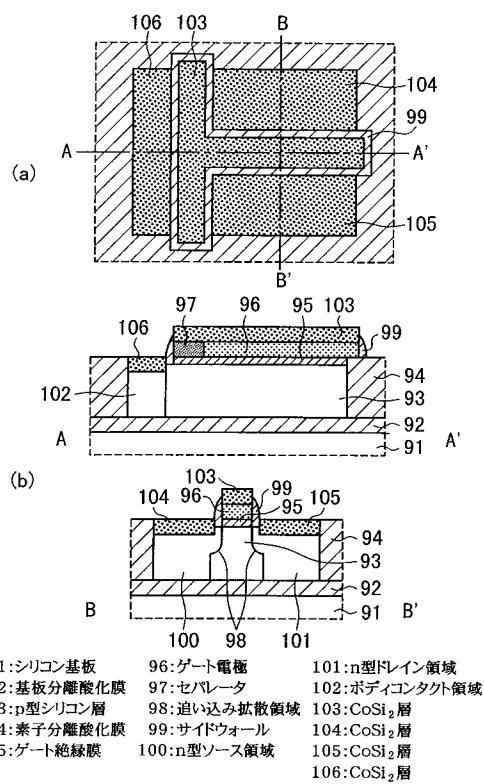

#### 【0083】

次に、図13(a)を参照して本発明の第4の実施の形態のSOI-MOSFETを説明するが、製造工程自体は、第1の実施の形態と共通する点が多いので、相違点を中心に説明する。

なお、図13(a)は平面図であり、図13(b)は図13(a)におけるA-A'を結ぶ一点鎖線に沿った断面図であり、また、図13(c)は図13(a)におけるC-C'を結ぶ一点鎖線に沿った断面図である。

30

#### 図13(a)乃至(c)参照

この第4の実施の形態のSOI-MOSFETは、n型多結晶シリコン層をパターニングする際に、ゲート電極2'0'をボディコンタクト形成領域側に若干突出させるとともに、セパレータ6'5'をドレイン領域形成側にのみ設けたものである。

#### 【0084】

そして、ソース・ドレイン領域を形成する際には、セパレータ6'5'のボディコンタクト形成領域側の近傍が露出するようにレジストパターンを設け、このレジストパターンをマスクとしてPをイオン注入することによってn型ドレイン領域2'6'を形成するとともに、セパレータ6'5'のボディコンタクト形成領域側及びセパレータ6'5'を設けない領域にn型ソース領域2'5'を形成する。

40

#### 【0085】

次いで、n型ソース領域2'5'及びn型ドレイン領域2'6'を覆うレジストパターンを設け、このレジストパターンをマスクとしてBをイオン注入することによってボディコンタクト領域3'0'を形成する。

以降は、上記の第1の実施の形態と同様なシリサイド形成工程によって、CoSi<sub>2</sub>層6'2'~6'4'を形成することによって、本発明の第4の実施の形態のSOI-MOSFETの基本構成が完成する。

なお、この場合も、p型のボディコンタクト領域3'0'とn型ソース領域2'5'とは一体の

50

$\text{CoSi}_2$  層 64 によって短絡した構造となっている。

【0086】

この第4の実施の形態においては、セパレータ65も実効的にゲート電極として機能するので、実効的なゲート幅をセパレータ65の長さ分だけ長くすることができ、それによって、トランジスタ特性を向上することができる。

【0087】

また、この場合のセパレータ65の幅は、トランジスタの動作特性を均一にするためには、ゲート電極20の幅と同じにする必要があるが、それに伴って、セパレータ65に起因するゲート容量を低減することが可能になる。

【0088】

以上、本発明の実施の形態を説明してきたが、本発明は各実施の形態に記載した構成及び条件に限られるものではなく、各種の変更が可能である。

例えば、本発明の実施の形態においては、SOI構造を酸素のイオン注入によるSIOX (Separation by Implanted Oxygen) 法によって形成しているが、基板貼り合わせ法を用いても良いものである。

【0089】

例えば、単結晶シリコン基板の表面に $\text{SiO}_2$ 膜を形成したのち、単結晶シリコン基板からなる貼り合わせ基板を $\text{SiO}_2$ 膜の表面に接着させて貼り合わせ、次いで、研削及び通常の研磨によって、単結晶シリコン基板の大部分を除去してその表面を鏡面化することによって、 $\text{SiO}_2$ 膜によって貼り合わせ基板から絶縁分離された素子形成層を設けても良いのである。

【0090】

また、上記の各実施の形態においては、素子分離絶縁膜をSTI法によって形成しているが、STI法に限られるものではなく、LOCOS(選択酸化)法等を用いても良いものであり、さらには、BOX(基板分離酸化膜)を形成する前に素子分離絶縁膜を形成しても良いものである。

【0091】

特に、基板貼り合わせ法を用いる場合には、単結晶シリコン基板に素子分離用溝形成したのち、CVD法によって全面にCVD-SiO<sub>2</sub>膜を堆積させることによって、素子分離溝を埋め込むとともに表面を平坦化し、次いで、単結晶シリコン基板からなる貼り合わせ基板をCVD-SiO<sub>2</sub>膜の表面に接着させて貼り合わせたのち、研削及び通常の研磨によって、単結晶シリコン基板の大部分を除去して、その表面を鏡面化することによって素子分離絶縁膜を設けたSOI基板を形成しても良いものである。

【0092】

また、上記の第1、第2、及び、第4の実施の形態においては、ゲート絶縁膜として熱酸化による $\text{SiO}_2$ 膜を用いているが、CVD膜でも良いものであり、さらには、 $\text{SiO}_2$ 膜に限られるものではなく、上記の第3の実施の形態と同様に $\text{SiON}$ 膜を用いても良いものであり、逆に、第3の実施の形態においてゲート絶縁膜として $\text{SiO}_2$ 膜を用いても良いものである。

【0093】

また、上記の各実施の形態においては、追い込み拡散領域を設けているが、必ずしも必須のものではなく、さらに、追い込み拡散領域の代わりにn<sup>-</sup>型のLDD(Lightly Doped Drain)領域を形成しても良いものである。

【0094】

また、上記の各実施の形態においては、シリサイド電極を形成する際に、Co膜を用いて $\text{CoSi}_2$ 層を形成しているが、 $\text{CoSi}_2$ 層に限られるものではなく、Ti膜を用いて $\text{TiSi}_2$ 層をシリサイド電極として用いても良いものである。

【0095】

また、上記の各実施の形態においては、説明を簡単にするためにnチャネル型MOSFETとして説明しているが、pチャネル型MOSFETにも同様に適当されるものであり、

特に、互いに素子分離絶縁膜によって分離されたpチャネル型MOSFETとnチャネル型MOSFETとを隣接して設け、互いのゲート電極を共通接続することによって周知のインバータを構成しても良いものである。

#### 【0096】

##### 【発明の効果】

本発明によれば、セパレータに起因する寄生容量を低減或いは消滅することができるとともに、シリサイド電極間の短絡を防止することができ、それによって、ボディコンタクト電極とドレイン電極との短絡或いは隣接するセパレータ同士の短絡を防止することができ、トランジスタピッチの縮小が可能になるので、絶縁ゲート型集積回路装置の高集積化、高速化に寄与するところが大きい。

10

##### 【図面の簡単な説明】

【図1】本発明の原理的構成の説明図である。

【図2】本発明の第1の実施の形態の途中までの製造工程の説明図である。

【図3】本発明の第1の実施の形態の図2以降の途中までの製造工程の説明図である。

【図4】本発明の第1の実施の形態の図3以降の途中までの製造工程の説明図である。

【図5】本発明の第1の実施の形態の図4以降の途中までの製造工程の説明図である。

【図6】本発明の第1の実施の形態の図5以降の製造工程の説明図である。

【図7】本発明の第2の実施の形態の途中までの製造工程の説明図である。

【図8】本発明の第2の実施の形態の図7以降の製造工程の説明図である。

【図9】本発明の第3の実施の形態の途中までの製造工程の説明図である。

20

【図10】本発明の第3の実施の形態の図9以降の途中までの製造工程の説明図である。

【図11】本発明の第3の実施の形態の図10以降の途中までの製造工程の説明図である。

。

【図12】本発明の第3の実施の形態の図11以降の製造工程の説明図である。

【図13】本発明の第4の実施の形態のSOI-MOSFETの説明図である。

【図14】従来のMOSFETの説明図である。

【図15】従来のSOI-MOSFETの説明図である。

##### 【符号の説明】

- 1 半導体基板

- 2 基板分離用絶縁膜

- 3 半導体層

- 4 ゲート絶縁膜

- 5 厚膜部

- 6 主ゲート電極

- 7 梁状導電体パターン

- 8 サイドウォール

- 9 ボディコンタクト領域

- 10 電極

- 11 シリコン基板

- 12 基板分離酸化膜

- 13 p型シリコン層

- 14 素子分離酸化膜

- 15 ゲート絶縁膜

- 16 レジストパターン

- 17 ゲート絶縁膜

- 18 厚膜部

- 19 レジストパターン

- 20 ゲート電極

- 21 セパレータ

- 22 サイドウォール

30

40

50

|     |                                     |    |

|-----|-------------------------------------|----|

| 2 3 | レジストパターン                            |    |

| 2 4 | Pイオン                                |    |

| 2 5 | n型ソース領域                             |    |

| 2 6 | n型ドレイン領域                            |    |

| 2 7 | 追い込み拡散領域                            |    |

| 2 8 | レジストパターン                            |    |

| 2 9 | Bイオン                                |    |

| 3 0 | ボディコンタクト領域                          |    |

| 3 1 | C <sub>o</sub> 膜                    |    |

| 3 2 | <u>C<sub>oSi<sub>2</sub></sub>膜</u> | 10 |

| 3 3 | レジストパターン                            |    |

| 4 1 | シリコン層                               |    |

| 4 2 | SiO <sub>2</sub> 膜                  |    |

| 4 3 | SiN膜                                |    |

| 4 4 | レジストパターン                            |    |

| 4 5 | シャロートレンチ                            |    |

| 4 6 | レジストパターン                            |    |

| 4 7 | 素子分離用トレンチ                           |    |

| 4 8 | SiO <sub>2</sub> 膜                  |    |

| 4 9 | 素子分離酸化膜                             | 20 |

| 5 0 | 素子内分離酸化膜                            |    |

| 5 1 | Bイオン                                |    |

| 5 2 | p型シリコン層                             |    |

| 5 3 | ゲート絶縁膜                              |    |

| 5 4 | ゲート電極                               |    |

| 5 5 | サイドウォール                             |    |

| 5 6 | 追い込み拡散領域                            |    |

| 5 7 | n型ソース領域                             |    |

| 5 8 | n型ドレイン領域                            |    |

| 6 2 | <u>C<sub>oSi<sub>2</sub></sub>膜</u> | 30 |

| 6 3 | C <sub>oSi<sub>2</sub></sub> 膜      |    |

| 6 4 | C <sub>oSi<sub>2</sub></sub> 膜      |    |

| 6 5 | セパレータ                               |    |

| 7 1 | p型シリコン基板                            |    |

| 7 2 | p型ウエル領域                             |    |

| 7 3 | 素子分離酸化膜                             |    |

| 7 4 | 素子内分離酸化膜                            |    |

| 7 5 | ゲート酸化膜                              |    |

| 7 6 | ゲート電極                               |    |

| 7 7 | 追い込み拡散領域                            | 40 |

| 7 8 | サイドウォール                             |    |

| 7 9 | n型ソース領域                             |    |

| 8 0 | n型ドレイン領域                            |    |

| 8 1 | ボディコンタクト領域                          |    |

| 8 2 | C <sub>oSi<sub>2</sub></sub> 膜      |    |

| 8 3 | C <sub>oSi<sub>2</sub></sub> 膜      |    |

| 8 4 | C <sub>oSi<sub>2</sub></sub> 膜      |    |

| 8 5 | C <sub>oSi<sub>2</sub></sub> 膜      |    |

| 9 1 | シリコン基板                              |    |

| 9 2 | 基板分離酸化膜                             | 50 |

9 3 p型シリコン層

9 4 素子分離酸化膜

9 5 ゲート絶縁膜

9 6 ゲート電極

9 7 セパレータ

9 8 追い込み拡散領域

9 9 サイドウォール

1 0 0 n型ソース領域

1 0 1 n型ドレイン領域

1 0 2 ボディコンタクト領域 10

1 0 3 CoSi<sub>2</sub>膜

1 0 4 CoSi<sub>2</sub>膜

1 0 5 CoSi<sub>2</sub>膜

1 0 6 CoSi<sub>2</sub>膜

【図1】

本発明の原理的構成の説明図

1:半導体基板 5:厚膜部 9:ボディコンタクト領域

2:基板分離用絶縁膜 6:主ゲート電極 10:シリサイド電極

3:半導体層 7:梁状導電体パターン

4:ゲート絶縁膜 8:サイドウォール

【図2】

本発明の第1の実施の形態の途中までの製造工程の説明図

11:シリコン基板 14:素子分離酸化膜

12:基板分離酸化膜 15:ゲート絶縁膜

13:p型シリコン層 16:レジストパターン

【図3】

本発明の第1の実施の形態の図2以降の途中までの製造工程の説明図

- |            |             |

|------------|-------------|

| 11:シリコン基板  | 18:厚膜部      |

| 12:基板分離酸化膜 | 19:レジストパターン |

| 13:p型シリコン層 | 20:ゲート電極    |

| 14:素子分離酸化膜 | 21:セバレータ    |

| 17:ゲート絶縁膜  |             |

【図4】

本発明の第1の実施の形態の図3以降の途中までの製造工程の説明図

- |            |             |             |

|------------|-------------|-------------|

| 11:シリコン基板  | 18:厚膜部      | 24:Pイオン     |

| 12:基板分離酸化膜 | 20:ゲート電極    | 25:n型ソース領域  |

| 13:p型シリコン層 | 21:セバレータ    | 26:n型ドレイン領域 |

| 14:素子分離酸化膜 | 22:サイドウォール  | 27:追い込み拡散領域 |

| 17:ゲート絶縁膜  | 23:レジストパターン |             |

【図5】

本発明の第1の実施の形態の図4以降の途中までの製造工程の説明図

- |            |            |                        |

|------------|------------|------------------------|

| 11:シリコン基板  | 18:厚膜部     | 26:n型ドレイン領域            |

| 12:基板分離酸化膜 | 20:ゲート電極   | 27:追い込み拡散領域            |

| 13:p型シリコン層 | 21:セバレータ   | 28:レジストパターン            |

| 14:素子分離酸化膜 | 22:サイドウォール | 29:Bイオン                |

| 17:ゲート絶縁膜  | 25:n型ソース領域 | 30:ボディコンタクト領域          |

|            | 31:Co膜     | 32:CoSi <sub>2</sub> 層 |

【図6】

本発明の第1の実施の形態の図5以降の製造工程の説明図

- |            |            |                        |

|------------|------------|------------------------|

| 11:シリコン基板  | 18:厚膜部     | 26:n型ドレイン領域            |

| 12:基板分離酸化膜 | 20:ゲート電極   | 27:追い込み拡散領域            |

| 13:p型シリコン層 | 21:セバレータ   | 30:ボディコンタクト領域          |

| 14:素子分離酸化膜 | 22:サイドウォール | 32:CoSi <sub>2</sub> 層 |

| 17:ゲート絶縁膜  | 25:n型ソース領域 | 33:n型ソース領域             |

【図7】

本発明の第2の実施の形態の途中までの製造工程の説明図

- |            |               |             |

|------------|---------------|-------------|

| 11:シリコン基板  | 18:厚膜部        | 31:Co膜      |

| 12:基板分離酸化膜 | 20:ゲート電極      | 33:レジストパターン |

| 13:p型シリコン層 | 21:セパレータ      |             |

| 14:素子分離酸化膜 | 22:サイドウォール    |             |

| 17:ゲート絶縁膜  | 30:ボディコンタクト領域 |             |

【図8】

本発明の第2の実施の形態の図7以降の製造工程の説明図

- |            |                        |                        |

|------------|------------------------|------------------------|

| 11:シリコン基板  | 18:厚膜部                 | 26:n型ドライン領域            |

| 12:基板分離酸化膜 | 20:ゲート電極               | 27:追い込み拡散領域            |

| 13:p型シリコン層 | 22:サイドウォール             | 30:ボディコンタクト領域          |

| 14:素子分離酸化膜 | 25:n型ソース領域             | 32:CoSi <sub>2</sub> 層 |

| 17:ゲート絶縁膜  | 32:CoSi <sub>2</sub> 層 |                        |

【図9】

本発明の第3の実施の形態の途中までの製造工程の説明図

- |                       |              |

|-----------------------|--------------|

| 11:シリコン基板             | 44:レジストパターン  |

| 12:基板分離酸化膜            | 45:シャロートレンチ  |

| 41:シリコン層              | 46:レジストパターン  |

| 42:SiO <sub>2</sub> 膜 | 47:素子分離用トレンチ |

| 43:SIN膜               |              |

【図10】

本発明の第3の実施の形態の図9以降の途中までの製造工程の説明図

- |                       |              |             |

|-----------------------|--------------|-------------|

| 11:シリコン基板             | 43:SIN膜      | 49:素子分離酸化膜  |

| 12:基板分離酸化膜            | 45:シャロートレンチ  | 50:素子内分離酸化膜 |

| 41:シリコン層              | 47:素子分離用トレンチ | 51:Bイオン     |

| 42:SiO <sub>2</sub> 膜 |              | 52:p型シリコン層  |

| 43:SIN膜               |              |             |

【図11】

本発明の第3の実施の形態の図10以降の途中までの製造工程の説明図

【図12】

本発明の第3の実施の形態の図11以降の製造工程の説明図

【図13】

本発明の第4の実施の形態のS O I -M O S F E T の説明図

【図14】

従来のM O S F E T の説明図

## 【図15】

従来のSOI-MOSFETの説明図

---

フロントページの続き

(72)発明者 秋谷 定則

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 古谷 和弘

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 渡邊 久

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

審査官 綿引 隆

(56)参考文献 特表2003-518775(JP,A)

特開平08-125187(JP,A)

特開平11-233785(JP,A)

特開平11-054758(JP,A)

特開平09-107103(JP,A)

特開昭57-027070(JP,A)

特開平10-189989(JP,A)

特開平10-284736(JP,A)

特開平11-238886(JP,A)

特開平11-204801(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H01L 29/786

H01L 21/336