(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년05월23일

(11) 등록번호 10-1623465

(24) 등록일자 2016년05월17일

- (51) 국제특허분류(Int. Cl.)

*G06F 12/10* (2016.01)

(52) CPC특허분류

*G06F 12/1036* (2013.01)

*G06F 12/1027* (2013.01)

(21) 출원번호 10-2015-7017790

(22) 출원일자(국제) 2014년01월10일

심사청구일자 2016년02월15일

(85) 번역문제출일자 2015년07월02일

(65) 공개번호 10-2015-0108361

(43) 공개일자 2015년09월25일

(86) 국제출원번호 PCT/US2014/011027

(87) 국제공개번호 WO 2014/113286

국제공개일자 2014년07월24일

(30) 우선권주장

13/741,981 2013년01월15일 미국(US)

(56) 선행기술조사문현

US5765209 B1

US4654790 B1

US20020144077 A1

(73) 특허권자

퀄컴 인코포레이티드

미국 92121-1714 캘리포니아주 샌 디에고 모어하

우스 드라이브 5775

(72) 발명자

벤쿠마한티, 수레쉬 케이.

미국 92121-1714 캘리포니아주 샌 디에고 모어하

우스 드라이브 5775

프론드케, 에리히 제이.

미국 92121-1714 캘리포니아주 샌 디에고 모어하

우스 드라이브 5775

(뒷면에 계속)

(74) 대리인

특허법의 난해드님

(74) 대리인

특허법인 남앤드남

전체 청구항 수 : 총 21 항

심사관 : 임정묵

(54) 발명의 명칭 변환 색인 버퍼(TLB)에 대한 중첩 체크

(57) 요약

장치는 변환 색인 버퍼(TLB)를 포함한다. TLB는, 엔트리 페이지에 대응하는 엔트리 페이지 크기 표시 및 엔트리 가상 어드레스를 포함하는 적어도 하나의 엔트리를 포함한다. 장치는 또한, 입력 페이지에 대응하는 입력 가상 어드레스 및 입력 페이지 크기 표시를 수신하도록 구성되는 입력 로직을 포함한다. 장치는, 엔트리 페이지 크기 표시 및 입력 페이지 크기 표시에 적어도 부분적으로 기초하여, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정하도록 구성되는 중첩 체크 로직을 더 포함한다.

대표도 - 도1

(52) CPC특허분류

G06F 2212/652 (2013.01)

(72) 발명자

코드레스쿠, 루시안

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

마옹, 쉐인 엠.

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

---

토레이, 라홀 알.

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

함단, 파디 에이.

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

## 명세서

### 청구범위

#### 청구항 1

변환 색인 버퍼의 관리 방법으로서,

변환 색인 버퍼(TLB)에서 입력 가상 어드레스 및 입력 페이지 크기 표시를 수신하는 단계 – 상기 입력 가상 어드레스 및 상기 입력 페이지 크기 표시는 입력 페이지에 대응함 –;

‘상기 TLB의 엔트리(entry)의 엔트리 페이지 크기 표시가 나타내는 엔트리 페이지 크기와 상기 입력 페이지 크기 표시가 나타내는 입력 페이지 크기 중 더 큰 것을 결정하는 단계 – 상기 TLB의 엔트리는 엔트리 페이지에 대응함 –;

상기 입력 페이지 크기와 상기 엔트리 페이지 크기 중 더 크다고 결정된 것을 제 1 선택된 페이지 크기로 선택하는 단계;

상기 제 1 선택된 페이지 크기에 기초하여, 상기 엔트리의 엔트리 가상 어드레스와 상기 입력 가상 어드레스의 제 1 마스킹(masking)된 비교를 수행하는 단계; 및

상기 제 1 마스킹된 비교를 수행한 이후에, 상기 TLB가 검사되지 않은 엔트리를 포함한다는 결정에 기초하여 상기 TLB에 의해 제 2 마스킹된 비교를 선택적으로 수행하는 단계

를 포함하는, 변환 색인 버퍼의 관리 방법.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 마스킹된 비교를 수행하는 단계는,

상기 입력 가상 어드레스와 상기 엔트리 가상 어드레스 중 마스킹되어야하는 다수의 비트들을 결정하는 단계 – 상기 다수의 비트들은 상기 제 1 선택된 페이지 크기에 기초함 –; 및

상기 입력 페이지가 상기 엔트리 페이지와 중첩하는지 여부를 결정하는 단계를 포함하는,

변환 색인 버퍼의 관리 방법.

#### 청구항 3

제 1 항에 있어서,

상기 TLB가 검사되지 않은 엔트리를 포함한다고 결정한 이후에,

상기 입력 페이지 크기와 제 2 엔트리 페이지 크기 중 더 큰 것을 식별하기 위하여, 상기 입력 페이지 크기 표시와 상기 TLB의 제 2 엔트리의 제 2 엔트리 페이지 크기 표시를 비교하는 단계 – 상기 TLB의 상기 제 2 엔트리는 제 2 엔트리 페이지에 대응함 –;

상기 입력 페이지 크기와 상기 제 2 엔트리 페이지 크기 중 더 크다고 식별된 것을 제 2 선택된 페이지 크기로서 선택하는 단계; 및

상기 입력 페이지가 상기 제 2 엔트리 페이지와 중첩하는지를 결정하기 위해, 상기 제 2 선택된 페이지 크기에 기초하여, 상기 제 2 엔트리의 제 2 엔트리 가상 어드레스와 상기 입력 가상 어드레스의 상기 제 2 마스킹된 비교를 수행하는 단계를 더 포함하고,

상기 제 2 마스킹된 비교를 수행하는 단계는, 상기 제 2 선택된 페이지 크기에 기초하여 상기 입력 가상 어드레스와 상기 제 2 엔트리 가상 어드레스 중 마스킹되어야하는 제 2 다수의 비트들을 결정하는 단계를 포함하는,

변환 색인 버퍼의 관리 방법.

#### 청구항 4

제 3 항에 있어서,

상기 제 1 선택된 페이지 크기는 상기 제 2 선택된 페이지 크기와는 상이하고,

상기 제 1 선택된 페이지 크기는 상기 입력 페이지 크기에 대응하고, 상기 제 2 선택된 페이지 크기는 상기 제 2 엔트리 페이지 크기에 대응하는,

변환 색인 버퍼의 관리 방법.

#### 청구항 5

제 3 항에 있어서,

상기 제 2 엔트리 페이지 크기 표시와 상기 입력 페이지 크기 표시를 비교하는 단계 이전에, 상기 제 2 엔트리 페이지를 상기 TLB의 검사되지 않은 엔트리로서 식별하는 단계를 더 포함하는,

변환 색인 버퍼의 관리 방법.

#### 청구항 6

장치로서,

중첩 체크 명령을 실행하도록 구성된 프로세서 –상기 중첩 체크 명령은, 입력 페이지에 대응하는 입력 가상 어드레스 및 입력 페이지 크기 표시를 포함함– 를 포함하고,

상기 프로세서는,

적어도 하나의 엔트리를 포함하는 변환 색인 버퍼(TLB) –상기 적어도 하나의 엔트리는, 엔트리 페이지에 대응하는 엔트리 페이지 크기 표시 및 엔트리 가상 어드레스를 포함함– ;

상기 입력 가상 어드레스 및 상기 입력 페이지 크기 표시를 수신하도록 구성되는 입력 로직;

중첩 체크 로직; 및

상기 중첩 체크 로직으로부터 하나 또는 그 초과의 결과들을 수신하도록 구성된 레지스터

를 포함하고,

상기 중첩 체크 로직은,

상기 입력 페이지 크기 표시가 나타내는 입력 페이지 크기와 상기 엔트리 페이지 크기 표시가 나타내는 엔트리 페이지 크기 중 더 큰 것을 결정하고;

상기 입력 페이지 크기와 상기 엔트리 페이지 크기 중 더 크다고 결정된 것을 선택된 페이지 크기로서 선택하고;

상기 선택된 페이지 크기에 기초하여 상기 중첩 체크 명령의 결과를 결정하고 –상기 결과는 상기 입력 페이지가 상기 엔트리 페이지와 중첩하는지 여부에 기초함– ; 그리고

상기 중첩 체크의 결과가 결정된 이후에, 상기 TLB가 검사되지 않은 엔트리를 포함한다는 결정에 기초하여 상기 TLB에 의해 제 2 중첩 체크의 제 2 결과를 선택적으로 결정하도록 구성되는,

장치.

#### 청구항 7

제 6 항에 있어서,

상기 적어도 하나의 엔트리는 애플리케이션 공간 식별자(ASID) 및 글로벌 표시를 더 포함하고, 상기 입력 로직은, 입력 ASID를 수신하도록 추가로 구성되고, 상기 중첩 체크 로직은,

상기 글로벌 표시가 제 1 값을 갖는 것에 대한 응답으로, 상기 ASID와 상기 입력 ASID의 비교에 기초하여 상기 입력 페이지가 상기 엔트리 페이지와 중첩하는지 여부를 결정하고; 그리고

상기 글로벌 표시가 제 2 값을 갖는 것에 대한 응답으로, 상기 ASID 및 상기 입력 ASID와는 관계 없이 상기 입력 페이지가 상기 엔트리 페이지와 중첩하는지 여부를 결정하도록 추가로 구성되는, 장치.

#### 청구항 8

제 6 항에 있어서,

상기 입력 페이지 크기 표시는 제 1 마스크 또는 상기 입력 페이지 크기에 의해 나타내지고, 상기 엔트리 페이지 크기 표시는 제 2 마스크 또는 상기 엔트리 페이지 크기에 의해 나타내지는, 장치.

#### 청구항 9

제 6 항에 있어서,

상기 적어도 하나의 엔트리는, 상기 엔트리 가상 어드레스에 맵핑되는 물리 어드레스, 애플리케이션 공간 식별자(ASID), 캐시 능력 표시, 허용 표시, 글로벌 표시 또는 이들의 임의의 조합을 포함하는, 장치.

#### 청구항 10

제 6 항에 있어서,

상기 중첩 체크 로직은 상기 프로세서에 저장된 전용 중첩 체크 로직을 포함하는, 장치.

#### 청구항 11

중첩 체크 명령의 수행 방법으로서,

프로세서에서 중첩 체크 명령을 실행하는 단계 – 상기 중첩 체크 명령은, 입력 페이지에 대응하는 입력 페이지 크기 표시 및 입력 가상 어드레스를 포함하고, 상기 중첩 체크 명령을 실행하는 단계는,

상기 입력 페이지 크기 표시가 나타내는 입력 페이지 크기와 변환 색인 버퍼(TLB)의 엔트리의 엔트리 페이지 크기 표시가 나타내는 엔트리 페이지 크기 중 더 큰 것을 결정하는 단계;

상기 입력 페이지 크기와 상기 엔트리 페이지 크기 중 더 크다고 결정된 것을 제 1 선택된 페이지 크기로 선택하는 단계;

상기 입력 페이지가 엔트리 페이지와 중첩하는지 여부를 결정하기 위해, 상기 제 1 선택된 페이지 크기에 기초하여, 상기 엔트리의 엔트리 가상 어드레스와 상기 입력 가상 어드레스의 마스킹된 비교를 수행하는 단계;

상기 마스킹된 비교를 수행하는 단계 이후에, 상기 TLB가 검사되지 않은 엔트리를 포함한다는 결정에 기초하여 상기 TLB에 의해 제 2 마스킹된 비교를 선택적으로 수행하는 단계; 및

상기 TLB가 검사되지 않은 엔트리를 포함하지 않는다는 상기 결정에 기초하고 그리고 상기 입력 페이지가 상기 엔트리 페이지와 중첩하는지 여부의 결정에 기초하여, 실행 결과를 출력하는 단계를 포함함 –; 및

상기 실행 결과에 기초하여 상기 TLB를 선택적으로 업데이트하는 단계를 포함하고,

상기 TLB를 선택적으로 업데이트하는 단계는, 중첩하지 않는다고 표시하는 상기 실행 결과에 응답하여, 상기 TLB의 제 2 엔트리에 상기 입력 페이지 크기 표시 및 상기 입력 가상 어드레스를 기록하는 단계를 포함하는,

중첩 체크 명령의 수행 방법.

#### 청구항 12

제 11 항에 있어서,

상기 실행 결과에 기초하여 상기 TLB를 선택적으로 업데이트하는 단계를 더 포함하고,

상기 TLB를 선택적으로 업데이트하는 단계는, 중첩을 표시하는 상기 실행 결과에 응답하여, 상기 TLB를 유지하는 단계를 포함하고,

상기 실행 결과는 불(Boolean) 출력을 포함하는, 중첩 체크 명령의 수행 방법.

### 청구항 13

제 11 항에 있어서,

상기 프로세서는, 상기 중첩 체크 명령을 실행하기 위한 전용 중첩 체크 로직을 포함하고,

상기 중첩 체크 명령을 실행하는 단계는, 상기 실행 결과를 상기 프로세서의 레지스터에 저장하는 단계를 더 포함하는, 중첩 체크 명령의 수행 방법.

### 청구항 14

조건부 변환 색인 베퍼 기록 명령의 수행 방법으로서,

변환 색인 베퍼(TLB)를 포함하는 프로세서에서 조건부 TLB 기록 명령을 실행하는 단계를 포함하고,

상기 TLB는, 엔트리 페이지에 대응하는 엔트리 페이지 크기 표시 및 엔트리 가상 어드레스를 갖는 제 1 엔트리를 포함하고, 상기 조건부 TLB 기록 명령은, 입력 페이지에 대응하는 입력 페이지 크기 표시 및 입력 가상 어드레스를 포함하고,

상기 조건부 TLB 기록 명령을 실행하는 단계는,

상기 입력 페이지 크기 표시가 나타내는 입력 페이지 크기와 상기 엔트리 페이지 크기 표시가 나타내는 엔트리 페이지 크기 중 더 큰 것을 결정하는 단계;

상기 입력 페이지 크기와 상기 엔트리 페이지 크기 중 더 크다고 결정된 것을 제 1 선택된 페이지 크기로 선택하는 단계;

상기 입력 페이지가 상기 엔트리 페이지와 중첩하는지 여부를 결정하기 위해, 상기 제 1 선택된 페이지 크기에 기초하여, 상기 엔트리 가상 어드레스와 상기 입력 가상 어드레스의 마스킹된 비교를 수행하는 단계;

상기 마스킹된 비교를 수행하는 단계 이후에, 상기 TLB가 검사되지 않은 엔트리를 포함한다는 결정에 기초하여 상기 TLB에 의해 제 2 마스킹된 비교를 선택적으로 수행하는 단계; 및

상기 TLB가 검사되지 않은 엔트리를 포함하지 않는다는 결정 및 상기 입력 페이지가 상기 엔트리 페이지와 중첩하지 않는다는 결정에 응답하여, 상기 TLB의 제 2 엔트리에 상기 입력 페이지 크기 표시 및 상기 입력 가상 어드레스를 기록하는 단계를 포함하는,

조건부 변환 색인 베퍼 기록 명령의 수행 방법.

### 청구항 15

제 14 항에 있어서,

상기 조건부 TLB 기록 명령을 실행하는 단계는, 상기 입력 페이지가 상기 엔트리 페이지와 중첩한다는 결정에 응답하여, 기록 실패를 나타내는 실행 결과를 출력하는 단계를 더 포함하고,

상기 실행 결과는, 상기 입력 페이지와 중첩하는 하나 또는 그 초과의 엔트리 페이지들에 대응하는 상기 TLB의 다수의 엔트리들을 식별하거나, 상기 입력 페이지와 중첩하는 특정 엔트리 페이지에 대응하는 상기 TLB의 특정 엔트리를 식별하거나, 또는 이 둘을 모두 식별하는,

조건부 변환 색인 베퍼 기록 명령의 수행 방법.

### 청구항 16

프로세서-판독가능 매체로서,

중첩 체크 명령을 포함하고,

상기 중첩 체크 명령은, 입력 페이지에 대응하는 입력 페이지 크기 표시 및 입력 가상 어드레스를 포함하고;

상기 중첩 체크 명령은, 변환 색인 베퍼(TLB)를 포함하는 프로세서에 의해,

상기 입력 페이지 크기 표시가 나타내는 입력 페이지 크기와 상기 TLB의 엔트리 페이지의 엔트리 페이지 크기 표시가 나타내는 엔트리 페이지 크기 중 더 큰 것을 결정하고;

상기 입력 페이지 크기와 상기 엔트리 페이지 크기 중 더 크다고 결정된 것을 선택된 페이지 크기로 선택하고;

상기 입력 페이지가 상기 엔트리 페이지와 중첩하는지 여부를 결정하기 위해, 상기 선택된 페이지 크기에 기초하여, 상기 엔트리의 엔트리 가상 어드레스와 상기 입력 가상 어드레스의 마스킹된 비교를 수행하고;

상기 마스킹된 비교가 수행된 이후에, 상기 TLB가 검사되지 않은 엔트리를 포함한다는 결정에 기초하여 상기 TLB에 의해 제 2 마스킹된 비교를 선택적으로 수행하고; 그리고

상기 마스킹된 비교에 부분적으로 기초하여 실행 결과를 출력하도록 실행가능한,

프로세서-판독가능 매체.

### 청구항 17

제 16 항에 있어서,

상기 실행 결과는, 상기 입력 페이지에 중첩하는 적어도 하나의 엔트리 페이지에 대응하는 상기 TLB의 적어도 하나의 엔트리를 식별하는,

프로세서-판독가능 매체.

### 청구항 18

프로세서-판독가능 매체로서,

조건부 변환 색인 베퍼(TLB) 기록 명령을 포함하고,

상기 조건부 TLB 기록 명령은, 입력 페이지에 대응하는 입력 페이지 크기 표시 및 입력 가상 어드레스를 포함하고;

상기 조건부 TLB 기록 명령은, 엔트리 페이지에 대응하는 엔트리 페이지 크기 표시 및 엔트리 가상 어드레스를 갖는 제 1 엔트리를 포함하는 TLB를 포함하는 프로세서에 의해,

상기 입력 페이지 크기 표시가 나타내는 입력 페이지 크기와 상기 엔트리 페이지 크기 표시가 나타내는 엔트리 페이지 크기 중 더 큰 것을 결정하고;

상기 입력 페이지 크기와 상기 엔트리 페이지 크기 중 더 크다고 결정된 것을 선택된 페이지 크기로 선택하고;

상기 입력 페이지가 상기 엔트리 페이지와 중첩하는지 여부를 결정하기 위해, 상기 선택된 페이지 크기에 기초하여, 상기 엔트리 가상 어드레스와 상기 입력 가상 어드레스의 마스킹된 비교를 수행하고;

상기 마스킹된 비교가 수행된 이후에, 상기 TLB가 검사되지 않은 엔트리를 포함한다는 결정에 기초하여 상기 TLB에 의해 제 2 마스킹된 비교를 선택적으로 수행하고; 그리고

상기 TLB가 검사되지 않은 엔트리를 포함하지 않는다는 결정 및 상기 입력 페이지가 상기 엔트리 페이지와 중첩하지 않는다는 결정에 응답하여, 상기 TLB의 제 2 엔트리에 상기 입력 페이지 크기 표시 및 상기 입력 가상 어드레스를 기록하도록 실행가능한,

프로세서-판독가능 매체.

### 청구항 19

제 18 항에 있어서,

상기 조건부 TLB 기록 명령은 상기 프로세서에 의해, 상기 입력 페이지가 상기 엔트리 페이지에 중첩한다는 결정에 응답하여 상기 TLB 내의 상기 엔트리 페이지를 유지하도록 추가적으로 실행가능한,

프로세서-판독가능 매체.

### 청구항 20

장치로서,

변환 색인 버퍼(TLB)에서 명령을 수신하기 위한 수단 – 상기 명령은, 입력 페이지에 대응하는 입력 가상 어드레스 및 입력 페이지 크기 표시를 포함함 – ;

상기 TLB의 엔트리 페이지의 엔트리 페이지 크기 표시와 상기 입력 페이지 크기 표시 중 더 큰 것을 결정하기 위한 수단;

상기 입력 페이지 크기 표시와 상기 엔트리 페이지 크기 표시 중 더 크다고 결정된 것을 선택된 페이지 크기 표시로 선택하기 위한 수단; 및

상기 입력 페이지가 상기 엔트리 페이지와 중첩하는지 여부를 결정하기 위해, 상기 선택된 페이지 크기 표시에 기초하여, 상기 엔트리 페이지에 대응하는 엔트리 가상 어드레스와 상기 입력 가상 어드레스의 제 1 마스킹된 비교를 수행하고, 그리고 상기 제 1 마스킹된 비교를 수행한 이후에, 상기 TLB가 검사되지 않은 엔트리를 포함한다는 결정에 기초하여 상기 TLB에 의해 제 2 마스킹된 비교를 선택적으로 수행하기 위한 수단을 포함하는, 장치.

## 청구항 21

제 20 항에 있어서,

상기 명령은 중첩 체크 명령 또는 조건부 변환 색인 버퍼(TLB) 기록 명령인,

장치.

## 발명의 설명

### 기술 분야

[0001]

[0001] 본 출원은, 2013년 1월 15일에 출원되고 발명의 명칭이 "OVERLAP CHECKING FOR A TRANSLATION LOOKASIDE BUFFER (TLB)"인 미국 가특허출원 제 13/741,981호에 대해 우선권을 주장하고, 상기 가특허출원의 내용들은 그 전체가 인용에 의해 통합된다.

[0002]

[0002] 본 개시는 일반적으로 변환 색인 버퍼들(TLB들)의 관리에 관한 것이다.

### 배경 기술

[0003]

[0003] 기술에서의 진보들은 더 작고 더 강력한 컴퓨팅 디바이스들을 초래해왔다. 예를 들어, 작고 경량이며 사용자들에 의해 쉽게 운반되는 휴대용 무선 전화들, 개인 휴대 정보 단말들(PDA들), 태블릿 컴퓨터들 및 페이징 디바이스들과 같은 무선 컴퓨팅 디바이스들을 포함하는 다양한 휴대용 개인 컴퓨팅 디바이스들이 현재 존재한다. 많은 이러한 컴퓨팅 디바이스들은, 그에 통합되는 다른 디바이스들을 포함한다. 예를 들어, 무선 전화는, 디지털 스틸 카메라, 디지털 비디오 카메라, 디지털 레코더 및 오디오 파일 플레이어를 또한 포함할 수 있다. 또한, 이러한 컴퓨팅 디바이스들은, 소프트웨어 애플리케이션들, 예를 들어, 인터넷에 액세스하기 위해 이용될 수 있는 웹 브라우저 애플리케이션, 및 스틸 또는 비디오 카메라를 활용하고 멀티미디어 재생 기능을 제공하는 멀티미디어 애플리케이션들을 포함하여, 실행 가능한 명령들을 프로세싱할 수 있다. 따라서, 이러한 디바이스들은, 통상적으로 데스크탑 컴퓨터들과 같은 더 큰 디바이스들에 의해 수행되는 기능들을 수행할 수 있다.

[0004]

[0004] 프로세서들, 예를 들어, 무선 전화들 및 다른 컴퓨팅 디바이스들의 프로세서들은 종종 하나 이상의 변환 색인 버퍼들(TLB들)을 포함한다. TLB는 가상 어드레스들과 물리 어드레스들 사이의 변환들을 캐시하기 위해 이용될 수 있다. TLB에서 특정 가상 어드레스가 발견되지 않는 경우, 그 특정 가상 어드레스에 대해 새로운 엔트리가 TLB에서 생성될 수 있고, 여기서 새로운 엔트리는 대응하는 물리 어드레스 변환을 포함한다. 이러한 엔트리를 생성하는 것은 하드웨어로 또는 소프트웨어에 의해 행해질 수 있다. 대안적으로, TLB의 기존의 엔트리는, 특정 가상 어드레스에 대한 변환 정보로 오버라이트될 수 있다. 특정 가상 어드레스가 발견되면, 즉, TLB의 엔트리에 매칭하면, TLB는 매칭하는 엔트리에 저장된 물리 어드레스를 리턴한다.

[0005]

[0005] 데이터 일관성을 유지하기 위해, TLB의 다수의 엔트리들이 입력 가상 어드레스에 매칭하는 상황들을 방지하는 것이 유용할 수 있다. 통상적으로, 이러한 의무는 TLB를 이용하는 운영 시스템에 속한다. 그러나, 프로그래밍 어려들 및 다른 조건들로 인해, 이러한 의무를 충족시키기 위해 운영 시스템에 의존하는 것은 곤란할 수 있다. 아울러, 몇몇 시스템들은 다수의 운영 시스템들(예를 들어, 하이퍼바이저와 통신하는 게스트 운영 시스템들)을 동시에 실행하고, 이것은 TLB 관리에서의 추가적인 복잡성을 도입시킬 수 있는데; 하이퍼바이저

(hypervisor)가 (소프트웨어 프로그래밍된) TLB를 프로그래밍하는 것을 담당할 수 있고, 게스트 운영 시스템은 변환들을 정의하지만, 중첩하지 않는 변환들을 생성하도록 신뢰될 수는 없다.

### 발명의 내용

[0006]

[0006] TLB에서의 프로세서-레벨(예를 들어, 하드웨어-기반) 중첩 체크가 개시된다. TLB는 소프트웨어-관리되거나 하드웨어-관리될 수 있다. 중첩 체크는, 가변 페이지 크기들을 지원하는 시스템에서 이용될 수 있는데, 이는, 가변 페이지 크기들의 이용이 중첩하는 페이지들을 가능하게 할 수 있기 때문이다. 개시된 기술은 하드웨어로 구현될 수 있기 때문에, 개시된 기술은 소프트웨어-기반 중첩 체크들보다 빠를 수 있다.

[0007]

[0007] 개시된 하드웨어-기반 중첩 체크 기술을 활용하기 위한 하나 이상의 명령들이 구현될 수 있다. 예를 들어, 중첩 체크 명령이 구현될 수 있다. 프로세서에 의해 실행되는 경우, 중첩 체크 명령은, TLB의 임의의 엔트리들이, 특정 입력 페이지와 중첩할 페이지들에 대응하는지를 나타내는 출력을 생성한다. 따라서, 중첩 체크 명령은, 입력 페이지에 대해 TLB에서 새로운 엔트리를 생성하는 것이 TLB에서 중첩하는 엔트리들을 초래할지를 결정하기 위해 이용될 수 있다. 몇몇 구현들에서, 중첩 체크 명령의 출력은, TLB의 얼마나 많은 엔트리들이 입력 페이지와 중첩하는지를 나타낼 수 있거나, 특정한 중첩하는 엔트리를 식별할 수 있다.

[0008]

[0008] 다른 예로서, 조건부 TLB 기록 명령은, 생성된 엔트리가 TLB의 임의의 기준의 엔트리들과 중첩하지 않을 것이면, 입력 페이지에 대한 TLB의 엔트리를 생성할 수 있다. 엔트리를 생성하는 것이 중첩을 초래할 것이면, 조건부 TLB 기록 명령은, 중첩 체크 명령의 출력과 유사한 출력을 생성할 수 있다.

[0009]

[0009] 특정한 실시예에서, 방법은, 입력 가상 어드레스 및 입력 페이지 크기 표시를 TLB에서 수신하는 단계를 포함한다. 입력 가상 어드레스 및 입력 페이지 크기 표시는 입력 페이지에 대응한다. 방법은 또한, TLB의 엔트리의 엔트리 페이지 크기 표시와 입력 페이지 크기 표시의 비교에 기초하여, 컴퓨팅된 페이지 크기를 결정하는 단계를 포함하고, 여기서, TLB의 엔트리는 엔트리 페이지에 대응한다. 방법은, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정하기 위해, 컴퓨팅된 페이지 크기에 기초하여, 엔트리 가상 어드레스의 마킹된 비교를 수행하는 단계를 더 포함한다.

[0010]

[0010] 다른 특정한 실시예에서, 장치는, TLB를 포함한다. TLB는, 엔트리 페이지에 대응하는 엔트리 페이지 크기 표시 및 엔트리 가상 어드레스를 포함하는 적어도 하나의 엔트리를 포함한다. 장치는 또한, 입력 페이지에 대응하는 입력 가상 어드레스 및 입력 페이지 크기 표시를 수신하도록 구성되는 입력 로직을 포함한다. 장치는, 엔트리 페이지 크기 표시 및 입력 페이지 크기 표시에 적어도 부분적으로 기초하여, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정하도록 구성되는 중첩 체크 로직을 더 포함한다.

[0011]

[0011] 다른 특정한 실시예에서, 방법은, 프로세서에서 중첩 체크 명령을 실행하는 단계를 포함한다. 중첩 체크 명령은, 입력 페이지에 대응하는 입력 페이지 크기 표시 및 입력 가상 어드레스를 포함한다. 중첩 체크 명령을 실행하는 단계는, 입력 페이지 크기 표시와 TLB의 엔트리의 엔트리 페이지 크기 표시의 비교에 기초하여, 컴퓨팅된 페이지 크기를 결정하는 단계를 포함한다. 중첩 체크 명령을 실행하는 단계는 또한, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정하기 위해, 컴퓨팅된 페이지 크기에 기초하여, 엔트리의 엔트리 가상 어드레스와 입력 가상 어드레스의 마스킹된 비교를 수행하는 단계를 포함한다. 중첩 체크 명령을 실행하는 단계는, 입력 페이지가 엔트리 페이지와 중첩하는지에 대한 결정에 기초하여, 실행 결과를 출력하는 단계를 더 포함한다.

[0012]

[0012] 다른 특정한 실시예에서, 방법은, TLB를 포함하는 프로세서에서 조건부 TLB 기록 명령을 실행하는 단계를 포함한다. TLB는, 엔트리 페이지에 대응하는 엔트리 페이지 크기 표시 및 엔트리 가상 어드레스를 갖는 제1 엔트리를 포함한다. 조건부 TLB 기록 명령은, 입력 페이지에 대응하는 입력 페이지 크기 표시 및 입력 가상 어드레스를 포함한다. 조건부 TLB 기록 명령을 실행하는 단계는, 입력 페이지 크기 표시와 엔트리 페이지 크기 표시의 비교에 기초하여, 컴퓨팅된 페이지 크기를 결정하는 단계를 포함한다. 조건부 TLB 기록 명령을 실행하는 단계는 또한, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정하기 위해, 컴퓨팅된 페이지 크기에 기초하여, 엔트리 가상 어드레스와 입력 가상 어드레스의 마스킹된 비교를 수행하는 단계를 포함한다. 조건부 TLB 기록 명령을 실행하는 단계는, 입력 페이지가 엔트리 페이지와 중첩하지 않는다는 결정에 대한 응답으로, 입력 페이지 크기 표시 및 입력 가상 어드레스를 TLB의 제2 엔트리에 기록하는 단계를 더 포함한다.

[0013]

[0013] 다른 특정한 실시예에서, 장치는 적어도 하나의 엔트리를 저장하기 위한 수단을 포함한다. 적어도 하나의 엔트리는 엔트리 페이지에 대응하는 엔트리 페이지 크기 표시 및 엔트리 가상 어드레스를 포함한다. 장치는

또한, 입력 페이지에 대응하는 입력 가상 어드레스 및 입력 페이지 크기 표시를 수신하기 위한 수단을 포함한다. 장치는, 입력 페이지 크기 표시와 엔트리 페이지 크기 표시의 비교에 기초하여, 컴퓨팅된 페이지 크기를 결정하기 위한 수단을 더 포함한다. 장치는, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정하기 위해, 컴퓨팅된 페이지 크기에 기초하여, 엔트리 가상 어드레스와 입력 가상 어드레스의 마스킹된 비교를 수행하기 위한 수단을 포함한다.

[0014] 다른 특정한 실시예에서, 비일시적 프로세서 판독가능 매체가 중첩 체크 명령을 포함한다. 중첩 체크 명령은, 입력 페이지에 대응하는 입력 페이지 크기 표시 및 입력 가상 어드레스를 포함한다. 중첩 체크 명령은, 입력 페이지 크기 표시와 TLB의 엔트리의 엔트리 페이지 크기 표시의 비교에 기초하여, 컴퓨팅된 페이지 크기를 결정하도록, TLB를 포함하는 프로세서에 의해 실행가능하다. 중첩 체크 명령은 또한, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정하기 위해, 컴퓨팅된 페이지 크기에 기초하여, 엔트리의 엔트리 가상 어드레스와 입력 가상 어드레스의 마스킹된 비교를 수행하도록 프로세서에 의해 실행가능하다. 중첩 체크 명령은, 입력 페이지가 엔트리 페이지와 중첩하는지에 대한 결정에 기초하여, 실행 결과를 출력하도록 프로세서에 의해 추가로 실행가능하다.

[0015] 다른 특정한 실시예에서, 비일시적 프로세서 판독가능 매체는 조건부 TLB 기록 명령을 포함한다. 조건부 TLB 기록 명령은 입력 페이지에 대응하는 입력 페이지 크기 표시 및 입력 가상 어드레스를 포함한다. 조건부 TLB 기록 명령은 TLB를 포함하는 프로세서에 의해 실행가능하고, TLB는, 엔트리 페이지에 대응하는 엔트리 페이지 크기 표시 및 엔트리 가상 어드레스를 갖는 제 1 엔트리를 포함한다. 조건부 TLB 기록 명령은, 입력 페이지 크기 표시와 엔트리 페이지 크기 표시의 비교에 기초하여, 컴퓨팅된 페이지 크기를 결정하도록 프로세서에 의해 실행가능하다. 조건부 TLB 기록 명령은 또한, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정하기 위해, 컴퓨팅된 페이지 크기에 기초하여, 엔트리 가상 어드레스와 입력 가상 어드레스의 마스킹된 비교를 수행하도록 프로세서에 의해 실행가능하다. 조건부 TLB 기록 명령은, 입력 페이지가 엔트리 페이지와 중첩하지 않는다는 결정에 대한 응답으로, 입력 페이지 크기 표시 및 입력 가상 어드레스를 TLB의 제 2 엔트리에 기록하도록 프로세서에 의해 추가로 실행가능하다.

[0016] 개시된 실시예들 중 적어도 하나에 의해 제공되는 하나의 특정한 이점은, TLB에서 프로세서-레벨 중첩 체크를 수행하는 능력이고, 이는, 잠재적으로 에러가 있는 제 3의 방법들(예를 들어, 운영 시스템 TLB 체크들)에 의존함이 없이, 컴퓨팅 시스템 또는 전자 디바이스에서 신뢰도 및 데이터 일관성을 증가시킬 수 있다. 본 개시의 다른 양상들, 이점들 및 특징들은, 하기 섹션들, 즉, 도면의 간단한 설명, 상세한 설명 및 청구항들을 포함하는 전체 명세서의 검토 이후 명백해질 것이다.

### 도면의 간단한 설명

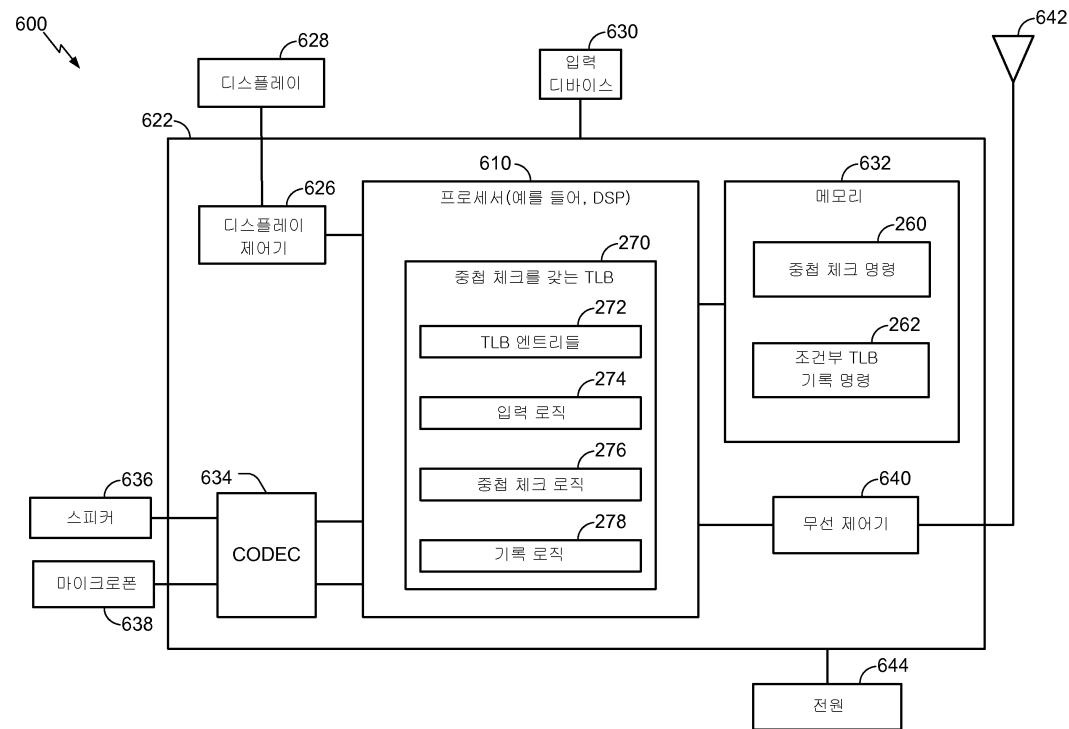

[0017] 도 1은, TLB에 대한 중첩 체크를 수행하도록 동작가능한 시스템의 특정한 실시예의 도면이다.

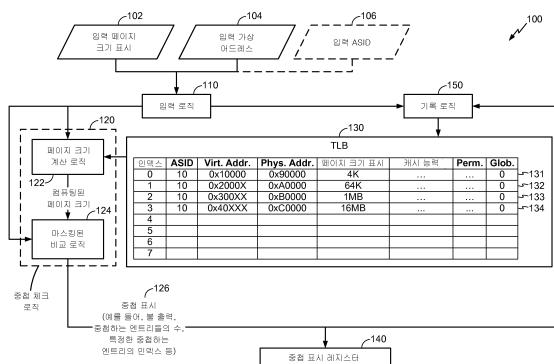

[0018] 도 2는, TLB에 대한 중첩 체크를 수행하도록 동작가능하고, 중첩 체크 명령 및 조건부 TLB 기록 명령을 실행하도록 동작가능한 프로세서를 포함하는 시스템의 특정한 실시예의 도면이다.

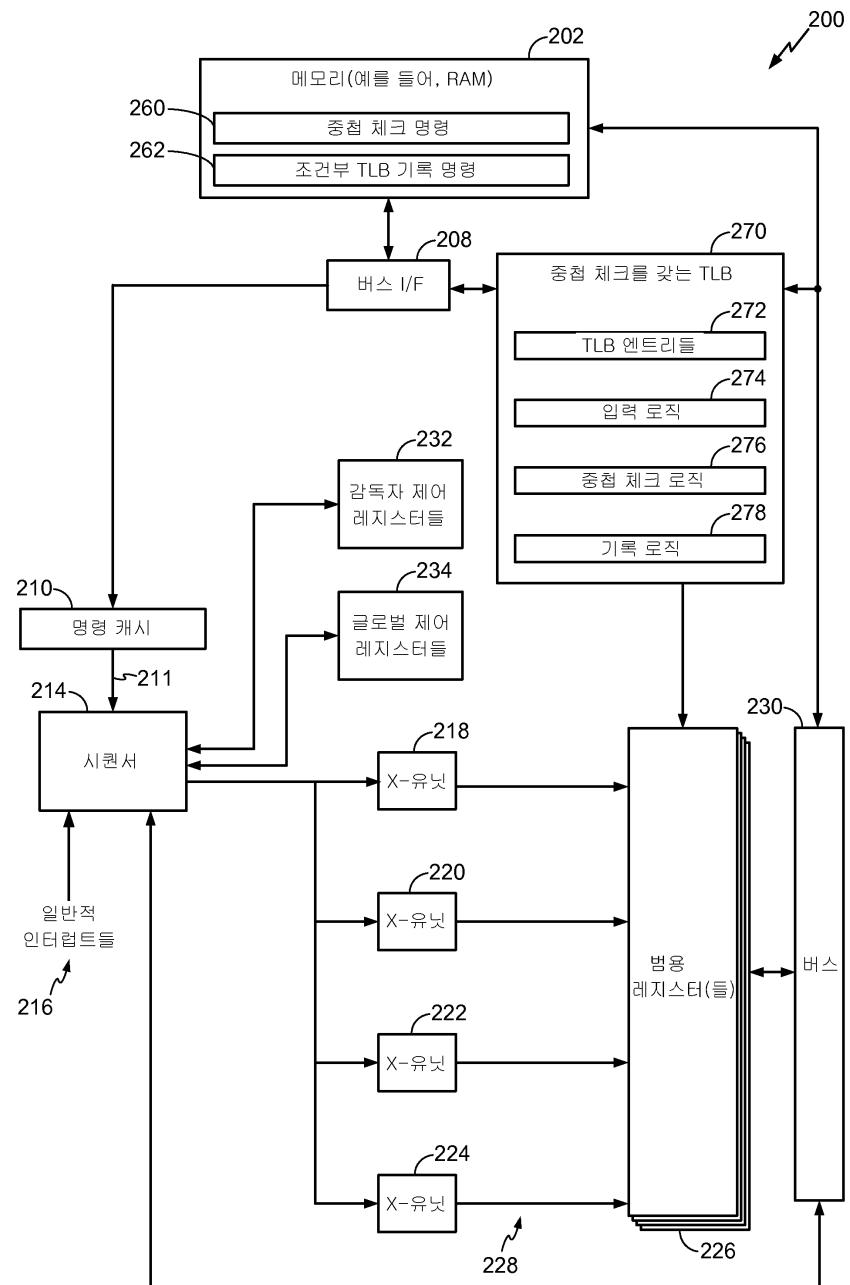

[0019] 도 3은, TLB에 대한 중첩 체크를 수행하는 방법의 특정한 실시예의 흐름도이다.

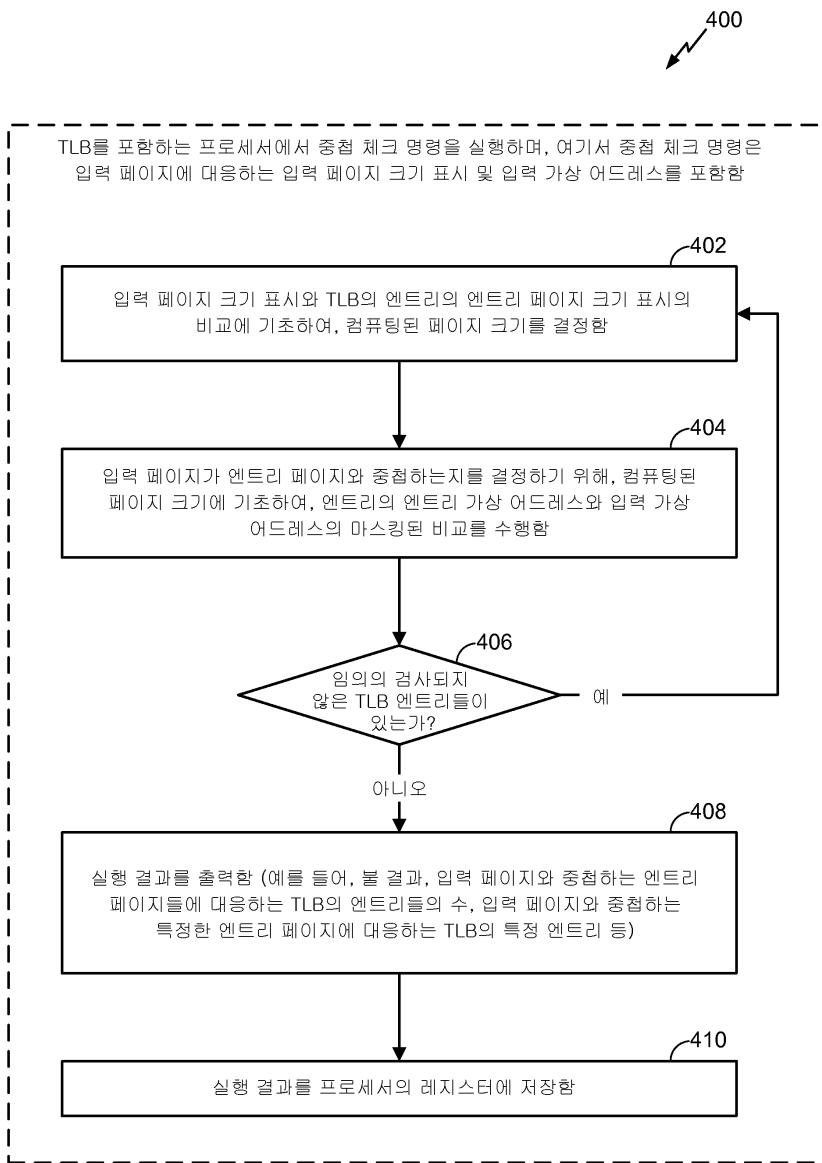

[0020] 도 4는, 중첩 체크 명령을 실행하는 방법의 특정한 실시예의 흐름도이다.

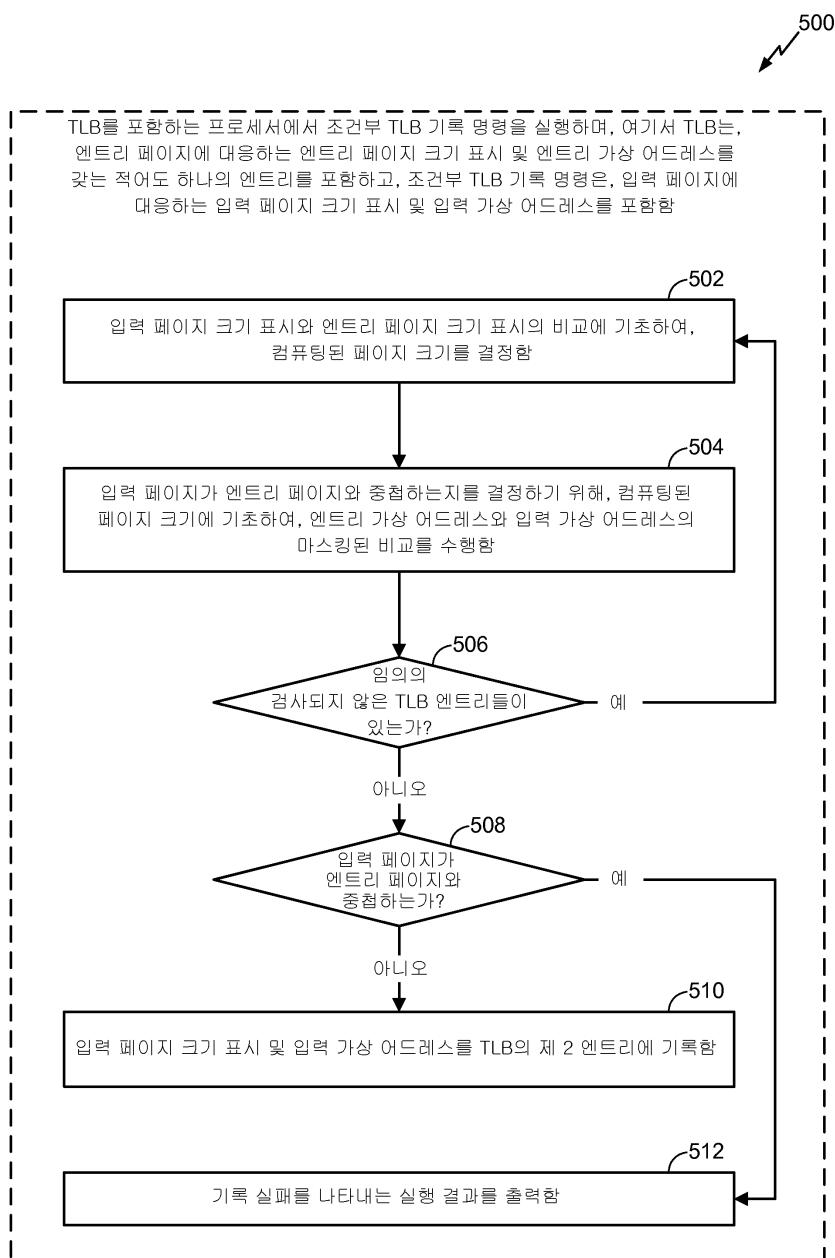

[0021] 도 5는, 조건부 TLB 기록 명령을 실행하는 방법의 특정한 실시예의 흐름도이다.

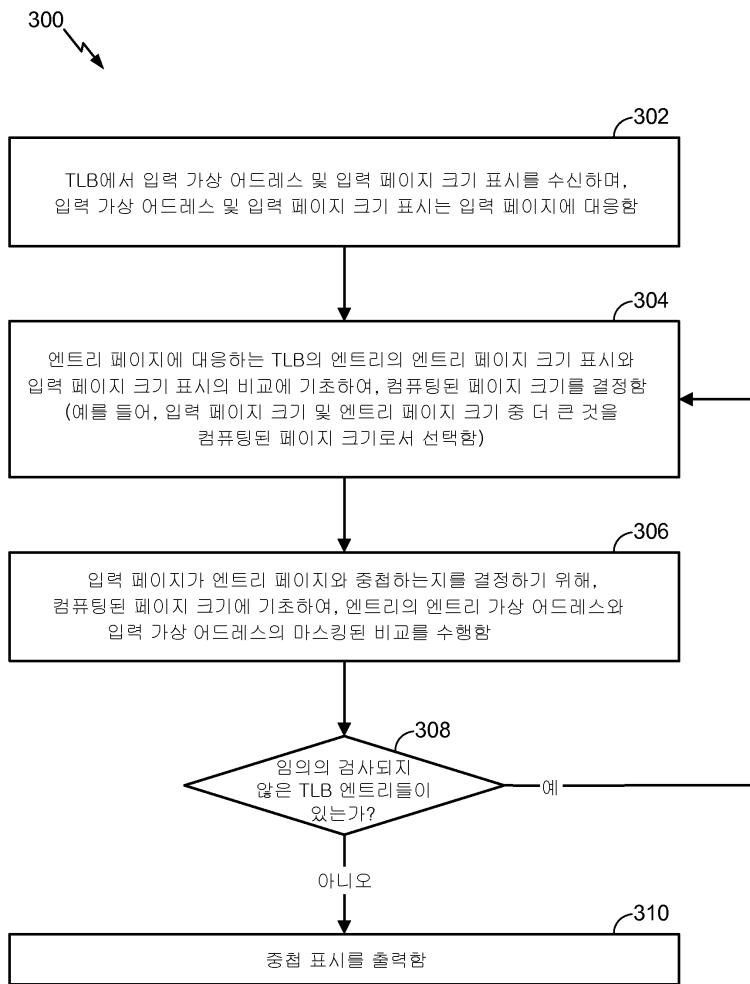

[0022] 도 6은, TLB에 대한 중첩 체크를 수행하도록 동작가능한 컴포넌트들을 포함하는 무선 디바이스의 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

[0023] 도 1은, 변환 색인 버퍼(TLB)에 대한 중첩 체크를 수행하도록 동작가능한 시스템(100)의 특정한 실시예의 도면이다. 시스템(100)은, 입력 로직(110), 중첩 체크 로직(120), 기록 로직(150) 및 중첩 표시 레지스터(140)에 커플링된 TLB(130)를 포함한다. 특정한 실시예에서, TLB(130)는 소프트웨어-관리되는 TLB이다. 대안적으로, TLB(130)는 하드웨어-관리되는 TLB일 수 있다. 예시적인 실시예에서, 도 1의 시스템(100) 및/또는 이들의 컴포넌트들은, 중앙 프로세싱 유닛(CPU) 또는 디지털 신호 프로세서(DSP)와 같은 프로세서에 포함되거나 그에 커플링될 수 있다. 예를 들어, 프로세서는, 셋탑 박스, 뮤직 플레이어, 비디오 플레이어, 엔터테인먼트 유닛, 내비게이션 디바이스, 통신 디바이스, 개인 휴대 정보 단말(PDA), 고정 위치 데이터 유닛, 컴퓨팅 디바이

스 또는 이들의 임의의 조합과 같은 전자 디바이스에 통합될 수 있다.

[0019] 특정한 실시예에서, 입력 로직(110), 중첩 체크 로직(120) 및 기록 로직(150) 중 하나 이상은 하드웨어를 이용하여(예를 들어, DSP, CPU, 제어기, 필드 프로그래머블 게이트 어레이(FPGA) 디바이스, 주문형 집적 회로(ASIC), 다른 하드웨어 디바이스 또는 이들의 임의의 조합에 의해) 구현된다. 대안적으로 또는 추가적으로, 입력 로직(110), 중첩 체크 로직(120) 및 기록 로직(150) 중 하나 이상은, 도 6을 참조하여 추가로 설명되는 바와 같이 소프트웨어(예를 들어, 프로세서에 의해 실행가능한 명령들)를 이용하여 구현될 수 있다.

[0020] TLB(130)는 하나 이상의 엔트리들을 포함할 수 있다. 도 1에서, TLB(130)는 제 1 엔트리(131), 제 2 엔트리(132), 제 3 엔트리(133) 및 제 4 엔트리(134)를 포함하고, 여기서, 엔트리들(131-134) 각각은 TLB(130)의 행에 대응한다. 각각의 엔트리(131-134)는 가상 어드레스("Virt. Addr.") 및 페이지 크기 표시("Page Size Ind.")를 포함할 수 있다. 도시된 예에서, 페이지 크기 표시는 실제 페이지 크기들(예를 들어, 4 킬로바이트(K), 64K, 1 메가바이트(MB), 16 MB 등)을 이용하여 표현된다. 대안적인 실시예에서, 페이지 크기 표시들은, 본 명세서에서 추가로 설명되는 바와 같이, 비트마스크들(또한 "마스크들"로 지칭됨)을 이용하여 표현될 수 있다.

[0021] TLB(130)의 엔트리들(131-134)은 또한, 가상 어드레스에 맵핑되는 물리 어드레스("Phys. Addr.")를 포함할 수 있다. 엔트리들(131-134)은, 애플리케이션 공간 식별자("ASID"), 캐시 능력 표시(예를 들어, 엔트리가 캐시될 수 있는지를 표시함), 허용 표시(들)("Perm.") (예를 들어, 판독 허용, 기록 허용 및/또는 사용자 허용) 및 글로벌 표시("Glob.")를 더 포함할 수 있다. TLB(130)의 각각의 엔트리는 인덱스를 가질 수 있다. 예를 들어, 제 1 엔트리(131)는 0의 인덱스를 갖고, 제 2 엔트리(132)는 1의 인덱스를 갖고, 제 3 엔트리(133)는 2의 인덱스를 갖고, 제 4 엔트리(134)는 3의 인덱스를 갖는다.

[0022] 도 1의 실시예에서, 예시의 목적으로 32-비트 어드레스 공간 및 4K의 최소 페이지 크기가 이용됨을 주목해야 한다. 따라서, TLB(130)의 가상 어드레스 및 물리 어드레스 열들에 오직 20개의 최상위 비트들(5개의 16 진수(hex) 숫자들에 대응함)만이 표현된다. 어드레스들의 12개의 최하위 비트들(3개의 hex 숫자들에 대응함)은 이용되지 않을 수 있는데, 이는, 최소 페이지 크기가 4K이고, 따라서 12개의 최하위 비트들은 (예를 들어, 공간 절약을 위해) TLB(130)에 포함되지 않을 수 있기 때문이다. 따라서, TLB(130)의 가상 어드레스는, 가상 페이지의 특정 어드레스보다는 가상 페이지 번호를 표현할 수 있다. 대안적인 실시예들에서, 상이한 크기 어드레스 공간 및 상이한 최소 페이지 크기가 이용될 수 있다.

[0023] 도 1에 도시된 바와 같이, 제 1 엔트리(131)는 가상 어드레스 0x10000에서 시작하는 4K 페이지에 대응한다. 따라서, 32-비트 어드레스 공간의 관점에서, 4K 페이지는 가상 어드레스 0x10000000 내지 0x1000FFF를 포함한다. 유사하게, 인덱스 1에서의 제 2 엔트리(132)는 가상 어드레스 0x2000X에서 시작하는 64K 페이지에 대응한다. 대문자 "X"는, 대문자 "X"에 의해 표현되는 hex 숫자에 대한 임의의 값이 64K 페이지 내에 있을 것임을 나타내기 위해 이용된다. 즉, 64K 페이지는 32-비트 가상 어드레스 범위 0x20000000 내지 0x2000FFFF에 걸쳐 있다. 인덱스 2에서의 제 3 엔트리(133)는 가상 어드레스 0x300XX에서 시작하는 1MB 페이지에 대응하고, 인덱스 3에서의 제 4 엔트리(134)는 가상 어드레스 0x40XXX에서 시작하는 16MB 페이지에 대응한다.

[0024] 동작 동안, TLB(130)는 TLB 검색들을 수신할 수 있다. 통상적으로, TLB 검색은 입력 가상 어드레스(104)를 특정할 수 있고, TLB는, (TLB에서 입력 가상 어드레스가 발견된 경우) TLB로부터 이전에 저장된 대응하는 물리 어드레스 또는 새로 생성된 맵핑에 대해 TLB에 추가된 대응하는 물리 어드레스 중 어느 하나를 리턴할 수 있다. 예시를 위해, 가상 어드레스 0x1000X에 의해 표현되는 64K 입력 페이지를 특정하는 TLB 검색을 고려한다. 본 명세서에서 사용되는 바와 같이, 용어 "입력 페이지"는 TLB 검색 또는 TLB(130) 상에서의 다른 판독/기록 동작에 의해 표현되는 메모리의 페이지를 지칭할 수 있다. 64K 입력 페이지는, 0x1000부터 0x1000F까지의 범위에 걸쳐 있을 수 있다. 따라서, 64K 입력 페이지는 TLB(130)의 제 1 엔트리(131)에 의해 표현되는 4K 엔트리 페이지와 중첩할 수 있다. 본 명세서에서 사용되는 바와 같이, 용어 "엔트리 페이지"는, TLB(130)의 엔트리에 의해 표현되는 메모리의 페이지를 지칭할 수 있다. 중첩이 존재하더라도, 입력 가상 어드레스(104)를 수신하지만 입력 페이지 크기 표시(102)를 수신하지는 않는 종래의 TLB 중첩 체크 방법들은 중첩을 검출하지 못할 수 있는데, 그 이유는, 0x1000이, 0x1000X에 의해 표현되는 임의의 값과 반드시 동일하지는 않기 때문임을 주목해야 한다. 따라서, 64K 입력 페이지에 대해 TLB(130)에서 중첩하는 엔트리가 생성될 수 있고, 이는 바람직하지 않을 수 있고, 미정의 동작 및/또는 데이터 일관성 문제들을 초래할 수 있다 (예를 들어, 이는, 후속 TLB 검색이 제 1 엔트리(131) 뿐만 아니라 새로 생성된 엔트리 둘 모두에 매칭할 수 있기 때문이다).

[0025] 설명된 중첩 체크 기술에 따르면, TLB(130)는 입력 로직(110) 및 중첩 체크 로직(120)을 포함하거나 그

에 커플링될 수 있다. TLB 검색 동안, 입력 로직(110)은 입력 가상 어드레스(104)에 추가하여 입력 페이지 크기 표시(102)를 수신할 수 있다. 예를 들어, 입력 가상 어드레스(104)는 0x1000X일 수 있고, 입력 페이지 크기 표시(102)는 64K일 수 있다. 대안적인 실시예에서, 입력 페이지 크기 표시(102)는, 본 명세서에서 추가로 설명되는 바와 같이, 마스크를 이용하여 표현될 수 있다.

[0026] [0031] 중첩 체크 로직(120)은 입력 로직(110)으로부터 입력 페이지 크기 표시(102) 및 입력 가상 어드레스(104)를 수신할 수 있고, TLB(130)의 엔트리들(131-134)을 검사하여, 엔트리들(131-134) 중 임의의 엔트리가, 입력 페이지와 중첩하는 엔트리 페이지에 대응하는지를 결정할 수 있다. 예를 들어, 중첩 체크 로직(120)은 페이지 크기 계산 로직(122) 및 마스킹된 비교 로직(124)을 포함할 수 있다. 엔트리들(131-134) 각각의 경우, 페이지 크기 계산 로직(122)은 컴퓨팅된 페이지 크기(예를 들어, 입력 페이지 크기 및 대응하는 엔트리 페이지 크기 중 더 큰 것)를 결정할 수 있다. 예를 들어, 제 1 엔트리(131)와의 중첩에 대해 체크하는 경우, 로직(122)은, 64K의 입력 페이지 크기와 4K의 엔트리 페이지 크기 중 더 큰 것인 64K의 컴퓨팅된 페이지 크기를 결정할 수 있다. 유사하게, 나머지 엔트리들(132-134)의 중첩 체크에 대한 컴퓨팅된 페이지 크기는 각각 64K, 1MB 및 16MB일 수 있다.

[0027] [0032] 마스킹된 비교 로직(124)은 컴퓨팅된 페이지 크기를 수신할 수 있고, 중첩에 대해 체크하기 위해, 컴퓨팅된 페이지 크기에 기초하여, 제 1 엔트리(131)의 가상 어드레스와 입력 가상 어드레스(104)의 마스킹된 비교를 수행할 수 있다. 예시를 위해, 제 1 엔트리(131)의 경우, 컴퓨팅된 크기가 64K이기 때문에, 마스킹된 비교로직(124)은, 입력 가상 어드레스 0x1000X 및 엔트리 가상 어드레스 0x10000의 마지막(예를 들어, 최하위) hex 숫자를 마스킹할 수 있다. 2개의 가상 어드레스들은 마지막 hex 숫자가 마스킹되는 경우 동일하기 때문에(즉, 0x1000 = 0x1000), 중첩 체크 로직(120)은, 64K 입력 페이지가 제 1 엔트리(131)에 표현된 4K 엔트리 페이지와 중첩한다고 결론지을 수 있다. 중첩 체크 로직(120)은 유사하게, TLB(130)의 나머지 엔트리들(132-134)을 검사할 수 있다. 대안적으로, 중첩 체크 로직(120)은, 중첩이 검출되면 TLB 엔트리들의 검사를 중지할 수 있다.

[0028] [0033] 중첩 체크 로직(120)은 중첩 체크의 결과를 나타내는 중첩 표시(126)를 생성할 수 있다. 예를 들어, 중첩 표시(126)는, 적어도 하나의 중첩이 검출되었는지 여부를 나타내는 불(Boolean)(예를 들어, 참/거짓) 출력일 수 있다. 다른 예로, 중첩 표시(126)는, 중첩을 초래하는 TLB(130)의 엔트리들의 수를 나타낼 수 있다. 예시를 위해, 중첩 표시(126)는, TLB(130)의 엔트리가 중첩을 초래할 때마다 중분되는 카운터일 수 있다. 또 다른 예로, 중첩 표시(126)는 특정한 중첩하는 엔트리의 인덱스를 나타낼 수 있다. 예시를 위해, TLB(130)의 엔트리가 중첩하는 경우, 중첩 표시(126)는 엔트리의 인덱스로 설정될 수 있다. 특정한 실시예에서, 중첩 표시(126)는 중첩 표시 레지스터(140)에 저장될 수 있거나 또는 프로세서 아키텍처의 예비 비트에 저장될 수 있다.

[0029] [0034] TLB(130)의 엔트리들(131-134) 중 어떠한 엔트리도 중첩을 초래하지 않는 경우, 입력 페이지에 대한 TLB(130)에서 새로운 엔트리가 생성될 수 있다. 예를 들어, 기록 로직(150)은 입력 로직(110)으로부터 입력 페이지 크기 표시(102) 및 입력 가상 어드레스(104)를 수신할 수 있고, 어떠한 중첩도 검출되지 않았음을 나타내는 중첩 표시(126)를 중첩 체크 로직(120)으로부터 수신할 수 있다. 응답으로, 기록 로직(150)은 입력 페이지에 대한 TLB(130)에서 새로운 엔트리를 생성할 수 있다. 대안적으로 TLB(130)가 "풀(full)"이면, 기록 로직(150)은, 입력 페이지에 대한 가상-대-물리 어드레스 맵핑으로, TLB(130)의 기준(예를 들어, 가장 오래된 것, 가장 최근에 이용된 것 등의) 엔트리를 오버라이트할 수 있다. 중첩이 검출되는 경우, 기록 로직(150)은 TLB(130)를 변형하는 것을 억제할 수 있다.

[0030] [0035] 도 1의 이전 설명은 TLB(130)에 저장된 입력 페이지 크기 표시(102) 및 페이지 크기 표시들에 대해 페이지 크기들(예를 들어, 4K, 64K 등)을 이용하지만, 대안적인 실시예는 페이지 크기들을 비트마스크들로 표현하는 것을 수반할 수 있음을 주목해야 한다. 이러한 실시예에서, 페이지 크기 계산 모듈(122)은 마스크들을 로직 AND함으로써 2개의 페이지 크기들 중 더 큰 것을 결정할 수 있다. 결과적으로 컴퓨팅된 마스크는, 중첩에 대해 체크하는 경우 마스킹된 비교 로직(124)에 의해 이용될 수 있다. 예시를 위해, 상기 예에서 페이지 크기들 대신에 마스크들이 이용되는 경우, 입력 가상 어드레스(104)는 0x1000X로 남지만 입력 페이지 크기 표시(102)는 64K 대신에 FFFF0일 수 있다. 제 1 엔트리(131)에 대한 페이지 크기 표시는 4K 대신에 FFFF일 수 있다. 페이지 크기 계산 로직(122)은 2개의 마스크들에 대해 로직 AND 연산을 수행하여, FFFF0의 컴퓨팅된 마스크를 생성할 수 있다(즉, FFFF AND FFFF0 = FFFF0). 마스킹된 비교 로직(124)은, 제 1 엔트리(131)의 가상 어드레스와 입력 가상 어드레스(104)를 비교하는 경우 FFFF0의 컴퓨팅된 마스크를 이용할 수 있다. FFFF0의 컴퓨팅된 마스크가 이용되는 경우, 가상 어드레스들 둘 모두의 마지막(예를 들어, 최하위) hex 숫자는 비교 전에 마스킹될 수 있어서, 동일한 긍정적인 중첩 결정을 초래한다(즉, 0x1000 = 0x1000이기 때문이다).

- [0031] [0036] 특정한 실시예에서, TLB(130)는 글로벌 표시 항목 및 ASID 항목을 각각의 엔트리(131-134)에 포함할 수 있다. 예를 들어, 도 1의 시스템(100)이 하이퍼바이저와 함께 이용되는 경우, 상이한 ASID들은 상이한 게스트(guest) 운영 시스템들에 대응할 수 있고, 가상 어드레스에 대한 확장으로서 취급될 수 있다. 예시를 위해, ASID들이 지원되는 경우, 제 1 엔트리(131)에 대한 가상 어드레스는 0x1010000일 수 있고, 상기 예에서 64K 입력 페이지에 대한 입력 가상 어드레스는 0x101000X일 수 있다. ASID들이 지원되는 경우, 입력 로직(110)은 입력 페이지 크기 표시(102) 및 입력 가상 어드레스(104)에 추가하여 입력 ASID(106)를 수신할 수 있다. TLB(130)의 특정한 엔트리의 글로벌 표시가 제 1 값(예를 들어, 1)을 갖는 경우, 중첩 체크 로직(120)은 중첩 체크 동안 입력 ASID(106) 및 엔트리 ASID를 비교할 수 있다. 글로벌 표시가 제 2 값(예를 들어, 0)을 갖는 경우, 중첩 체크 로직(120)은, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정할 때 ASID들을 무시할 수 있다(예를 들어, 마스킹하고 그리고/또는 비교를 억제할 수 있다).

- [0032] [0037] 따라서, 도 1의 시스템(100)은 TLB(130)에서의 중첩 체크를 가능하게 할 수 있어서, 컴퓨팅 시스템 또는 전자 디바이스에서 신뢰도 및 데이터 일관성을 증가시킬 수 있다. 아울러, 도 1의 시스템(100)이 이러한 중첩 체크를 프로세서 레벨에서 (예를 들어, TLB(130) 내의 또는 그에 커플링된 로직 모듈들을 이용하여) 가능하게 할 수 있기 때문에, 도 1의 시스템(100)은, 잠재적으로 에러가 있는 제 3의 방법들에 의존함이 없이 TLB 중첩 체크를 가능하게 할 수 있다. 따라서, 도 1의 시스템(100)은, 중첩하는 TLB 엔트리들을 생성하려 시도하는 운영 시스템 또는 애플리케이션으로부터 보호를 제공할 수 있다.

- [0033] [0038] 도 1의 시스템(100)은, TLB에 이미 존재하는 엔트리를 대신에 프로세서에서 "플라이트 중인(in flight)"(예를 들어, TLB 미스(miss) 큐(queue) 또는 TLB 기록 큐 내의) 데이터 및 명령들을 검사하는 중첩 체크 방법들에 대해 바람직할 수 있다. 예를 들어, 플라이트 중인 데이터/명령들을 검사하는 것은, 중첩 에러들이 고정되면 재시도 동작들을 초래할 수 있다. 또한, TLB 미스/기록 큐를 체크하는 것은 멀티스레디드 시스템에서 계산적으로 고가일 수 있다.

- [0034] [0039] 특정한 실시예에서, 하나 이상의 프로세서-실행가능 명령들은, 도 1을 참조하여 설명된 중첩 체크 동작들을 트리거링 및/또는 이용할 수 있다. 예를 들어, 중첩 체크 명령 및 조건부 TLB 기록 명령이 실행될 수 있다. 중첩 체크 명령은 입력 가상 어드레스 및 입력 페이지 크기 표시를 포함할 수 있다. 중첩 체크 명령은 (예를 들어, 임의의 엔트리가 입력 페이지와 중첩하는지를 나타내는) 불 출력을 생성할 수 있고, 입력 페이지와 중첩하는 특정 엔트리를 식별할 수 있고, 얼마나 많은 엔트리들이 입력 페이지와 중첩하는지를 식별할 수 있는 것 등이다. 몇몇 구현들에서, 출력은 프로세서의 레지스터(예를 들어, 중첩 표시 레지스터(140))에 저장될 수 있다.

- [0035] [0040] 조건부 TLB 기록 명령은 또한, 입력 페이지에 대응하는 입력 페이지 크기 표시 및 입력 가상 어드레스를 포함할 수 있다. 입력 페이지가 엔트리 페이지와 매칭하면, 조건부 TLB 기록 명령은 중첩 체크 명령의 출력과 유사한 출력을 생성할 수 있다. 어떠한 중첩도 검출되지 않으면, 조건부 TLB 기록 명령은 입력 페이지에 대한 TLB에 새로운 엔트리를 기록할 수 있거나, 입력 페이지를 반영하기 위해 TLB의 기존의 엔트리를 변형할 수 있다.

- [0036] [0041] 특정한 실시예에서, 중첩 체크 명령 및/또는 조건부 TLB 기록 명령은 단일 샘플링 사이클에서 실행될 수 있다. 예를 들어, 명령(들)은, TLB의 컨텐츠-어드레스가능 메모리(CAM) 부분에 대한 원자(atomic) 이벤트들을 표현할 수 있다.

- [0037] [0042] 도 2는, 중첩 체크 명령 및 조건부 TLB 기록 명령을 실행하도록 동작가능한 시스템(200)의 특정한 실시예의 도면이다. 시스템(200)은, 버스 인터페이스(I/F)(208)를 통해 명령 캐시(210)에 커플링될 수 있는 메모리(202)를 포함한다. 특정한 실시예에서, 시스템(200)의 전부 또는 일부는 프로세서에 통합될 수 있다. 대안적으로, 메모리(202)는 프로세서 외부에 있을 수 있다.

- [0038] [0043] 메모리(202)는 버스 인터페이스(208)를 통해 명령 캐시(210)에 명령들을 전송할 수 있다. 명령 캐시(210)는 버스(211)를 통해 시퀀서(214)에 커플링될 수 있다. 시퀀서(214)는, 인터럽트 레지스터(미도시)로부터 리트리브될 수 있는 일반적 인터럽트들(216)을 수신할 수 있다. 특정한 실시예에서, 명령 캐시(210)는, 버스(211)에 커플링될 수 있고 프로세서의 특정한 스레드들(예를 들어, 하드웨어 스레드들)과 연관될 수 있는 복수의 현재 명령 레지스터들(미도시)을 통해 시퀀서(214)에 커플링될 수 있다. 특정한 실시예에서, 프로세서는, 다수의 하드웨어 스레드들을 포함하는 인터리빙된 멀티스레디드 프로세서일 수 있다.

- [0039] [0044] 데이터 캐시가 또한 버스 인터페이스(208)를 통해 메모리(202)에 커플링될 수 있다. 특정한

실시예에서, 시스템(200)은, 중첩 체크를 포함하는 TLB(270)를 포함한다. 예를 들어, TLB(270)는, TLB 엔트리들(272)(예를 들어, 도 1의 TLB 엔트리들(131-134)), 입력 로직(274)(예를 들어, 도 1의 입력 로직(110)), 중첩 체크 로직(276)(예를 들어, 도 1의 중첩 체크 로직(120)) 및 기록 로직(278)(예를 들어, 도 1의 기록 로직(150))을 포함할 수 있다.

[0040] 특정한 실시예에서, 버스(211)는 백 이십 팔 비트(128-비트)일 수 있고, 시퀀서(214)는, 하나 이상의 명령들을 각각 포함하는 명령 패킷들을 통해 메모리(202)로부터 명령들을 리트리브하도록 구성될 수 있다. 버스(211)는 제 1 명령 실행 유닛(X-유닛)(218), 제 2 명령 실행 유닛(X-유닛)(220), 제 3 명령 실행 유닛(X-유닛)(222) 및 제 4 명령 실행 유닛(X-유닛)(224)에 커플링될 수 있다. 4개보다 더 적거나 더 많은 실행 유닛들이 존재할 수 있음을 주목해야 한다. 각각의 명령 실행 유닛(218-224)은, 로드/저장 로직 및/또는 산술-로직 유닛들(ALU들)과 같은 연산 로직을 포함할 수 있다. 각각의 명령 실행 유닛(218-224)은 버스(228)를 통해 범용 레지스터 파일(226)에 커플링될 수 있다. 범용 레지스터 파일(226)은 또한, 도시된 바와 같이, 버스(230)를 통해, 시퀀서(214), TLB(270) 및 메모리(202)에 커플링될 수 있다.

[0041] 시스템(200)은 또한, 인터럽트들(예를 들어, 일반적 인터럽트들(216))을 허용할지를 결정하고 명령들의 실행을 제어하기 위해, 시퀀서(214) 내의 제어 로직에 의해 액세스될 수 있는 비트들을 저장하는, 감독자 제어 레지스터들(232) 및 글로벌 제어 레지스터들(234)을 포함할 수 있다.

[0042] 동작 동안, 실행가능한 명령들은 메모리(202)로부터 페치(fetch)될 수 있고, 명령 캐시(210)에 저장될 수 있다. 예를 들어, 명령들은 중첩 체크 명령(260) 및/또는 조건부 TLB 기록 명령(262)을 포함할 수 있다. 실행 동안, 명령들(260-262) 각각은, 중첩 체크 동작들이 TLB(270)에서 수행되게 할 수 있다.

[0043] 예를 들어, 중첩 체크 명령(260)은 옵코드(opcode)(예를 들어, "TLBOC"), 입력 가상 어드레스, 및 입력 페이지에 대응하는 입력 페이지 크기 표시를 포함할 수 있다. ASID들이 지원되면, 중첩 체크 명령(260)은 또한 입력 ASID를 포함할 수 있다. 중첩 체크 명령(260)의 실행 동안, 입력 로직(274)은 입력 가상 어드레스, 입력 페이지 크기 표시 및 입력 ASID(존재하는 경우)를 수신할 수 있다. 중첩 체크 로직(276)은, TLB 엔트리들(272)을 검사하여, TLB 엔트리들(272) 중 임의의 엔트리가, 입력 페이지와 중첩하는 엔트리 페이지들에 대응하는지를 결정할 수 있다. 중첩 체크 로직(276)은 중첩 체크의 결과(예를 들어, 불 출력, 중첩하는 엔트리들의 수, 특정한 중첩하는 엔트리의 인덱스 등)를 나타내는 명령 실행 결과를 생성할 수 있다. 명령 실행 결과는, 저장 디바이스(예를 들어, 메모리(202) 또는 범용 레지스터 파일(226))에 저장될 수 있다. 조건부 TLB 기록 명령(262)과는 달리, 중첩 체크 명령(260)은, TLB 엔트리들(272)을 변형하지 않는 "판독-전용" 명령일 수 있음을 주목해야 한다.

[0044] 조건부 TLB 기록 명령(262)은, 옵코드(opcode)(예를 들어, "TLBCW"), 입력 가상 어드레스, 및 입력 페이지에 대응하는 입력 페이지 크기 표시를 포함할 수 있다. ASID들이 지원되면, 조건부 TLB 기록 명령(262)은 또한 입력 ASID를 포함할 수 있다. 조건부 TLB 기록 명령(262)의 실행 동안, 입력 로직(274)은 입력 가상 어드레스, 입력 페이지 크기 표시 및 입력 ASID(존재하는 경우)를 수신할 수 있다. 중첩 체크 로직(276)은, TLB 엔트리들(272)을 검사하여, TLB 엔트리들(272) 중 임의의 엔트리가, 입력 페이지와 중첩하는 엔트리 페이지들에 대응하는지를 결정할 수 있다. 적어도 하나의 엔트리 페이지가 입력 페이지와 중첩한다고 중첩 체크 로직(276)이 결정하는 경우, 중첩 체크 로직(276)은, TLB 기록 실패를 나타내는 명령 실행 결과를 출력할 수 있다. 중첩 체크 로직(276)이 중첩을 검출하지 않는 경우, 중첩 체크 로직(276)은, (예를 들어, 입력 페이지에 대한 맵핑이 메모리(202)와 같은 메모리에서 생성된 후) 입력 페이지 크기 표시, 입력 가상 어드레스, 및 입력 ASID(존재하는 경우)를 TLB 엔트리들(272) 중 하나에 기록할 수 있다.

[0045] 따라서, 도 2의 시스템(200)은, TLB 중첩 체크를 트리거링하는 하나 이상의 명령들을 포함하는 명령 세트 아키텍처(ISA)를 구현하기 위해 이용될 수 있다. 도 2의 시스템(200)은, 하드웨어-기반 TLB 중첩 체크 특징들에 대한 액세스를 프로세서 설계자들 및 애플리케이션 개발자들에게 제공할 수 있다.

[0046] 도 3은, TLB에 대한 중첩 체크를 수행하는 방법(300)의 특정한 실시예의 흐름도이다. 예시적인 실시예에서, 방법(300)은 도 1의 시스템(100) 또는 도 2의 시스템(200)에서 수행될 수 있다.

[0052] 방법(300)은, 302에서, TLB에서 입력 가상 어드레스 및 입력 페이지 크기 표시를 수신하는 단계를 포함할 수 있다. 입력 가상 어드레스 및 입력 페이지 크기 표시는 입력 페이지에 대응한다. 예를 들어, 도 1에서, 입력 로직(110)은 입력 가상 크기 표시(102) 및 입력 가상 어드레스(104)를 수신할 수 있다. 예시를 위해, 입력 페이지 크기 표시(102)는 1MB일 수 있고, 입력 가상 어드레스(104)는 0x200XX일 수 있다.

- [0048] [0053] 방법(300)은 또한, 304에서, 엔트리 페이지에 대응하는 TLB의 엔트리의 엔트리 페이지 크기 표시와 입력 페이지 크기 표시의 비교에 기초하여, 컴퓨팅된 페이지 크기를 결정하는 단계를 포함할 수 있다. 특정한 실시 예에서, 입력 페이지 크기 및 엔트리 페이지 크기 중 더 큰 것이 컴퓨팅된 페이지 크기로 선택될 수 있다. 예를 들어, 페이지 크기 계산 로직(122)은, 제 1 엔트리(131)의 경우, 컴퓨팅된 페이지 크기를, 1MB 입력 페이지 크기 및 제 1 엔트리(131)에 대한 4K 엔트리 페이지 크기 중 더 큰 것인 1MB로 결정할 수 있다.

- [0049] [0054] 방법(300)은, 306에서, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정하기 위해, 컴퓨팅된 페이지 크기에 기초하여, 엔트리의 엔트리 가상 어드레스와 입력 가상 어드레스의 마스킹된 비교를 수행하는 단계를 더 포함할 수 있다. 예를 들어, 도 1에서, 마스킹된 비교 로직(124)은, 제 1 엔트리(131)에 대해, 입력 가상 어드레스 0x200XX 및 엔트리 가상 어드레스 0x10000의 마스킹된 비교를 수행할 수 있다. 컴퓨팅된 페이지 크기가 1MB이기 때문에, 2개의 최하위(예를 들어, 최우측) 16진수 숫자들은 비교 전에 마스킹될 수 있다. 따라서, 제 1 엔트리(131)의 경우, 비교는 0x200과 0x100 사이일 수 있고, 중첩 체크 로직(120)은, 제 1 엔트리(131)에 의해 표현되는 엔트리 페이지와 입력 페이지 사이에 어떠한 중첩도 존재하지 않는다고 결정할 수 있다.

- [0050] [0055] 방법(300)은, 308에서, TLB의 임의의 검사되지 않은 엔트리들이 남아있는지를 결정하는 단계를 포함할 수 있다. 어떠한 검사되지 않은 엔트리들도 남아 있지 않으면, 방법(300)은, 310에서 중첩 표시를 출력하는 단계를 포함할 수 있다. 예를 들어, 중첩 표시는 불 출력, 중첩하는 엔트리들의 수, 특정한 중첩하는 엔트리의 인덱스 또는 몇몇 다른 중첩 표시일 수 있다. 대안적으로, 중첩이 검출되었으면, 중첩 표시가 출력될 수 있고, 중첩 표시의 부재는 어떠한 중첩도 검출되지 않았음을 나타낼 수 있다.

- [0051] [0056] TLB에 검사되지 않은 엔트리들이 여전히 존재하면, 방법(300)은 304로 리턴할 수 있다. 예를 들어, 도 1에서, 중첩 체크 로직은 TLB(130)의 나머지 엔트리들(132-134)을 검사할 수 있다. 제 2 엔트리(132)의 경우, 컴퓨팅된 페이지 크기는, 1MB 입력 페이지 크기 및 64K 엔트리 페이지 크기 중 더 큰 것인 1MB일 수 있다. 응답으로, 마스킹된 비교 로직(124)은 입력 가상 어드레스 0x200XX 및 엔트리 가상 어드레스 0x2000X의 2개의 최하위 16진수 숫자들을 마스킹할 수 있다. 결과적인 값들이 매칭하기 때문에 (즉, 0x200 = 0x200), 중첩 체크 로직(200)은 중첩(예를 들어, 제 2 엔트리(132)에 의해 표현된 엔트리 페이지가 입력 페이지를 포함하는 것)을 검출할 수 있다.

- [0052] [0057] 특정한 실시예에서, 도 3의 방법(300)은 DSP, CPU, 제어기, 필드-프로그래머블 게이트 어레이(FPGA) 디바이스, 주문형 집적 회로(ASIC), 다른 하드웨어 디바이스, 펌웨어 디바이스 또는 이들의 임의의 조합에 의해 구현될 수 있다. 일례로, 도 3의 방법(300)은, 도 6에 대해 설명된 바와 같이, 명령들을 실행하는 프로세서에 의해 수행될 수 있다.

- [0053] [0058] 도 4는, 중첩 체크 명령을 실행하는 방법(400)의 특정한 실시예의 흐름도이다. 예시적인 실시예에서, 방법(400)은 도 1의 시스템(100) 또는 도 2의 시스템(200)에서 수행될 수 있다.

- [0054] [0059] 도 4에 도시된 각각의 동작은 프로세서에서 중첩 체크 명령의 실행 동안 수행될 수 있다. 중첩 체크 명령은, 입력 페이지에 대응하는 입력 페이지 크기 표시 및 입력 가상 어드레스를 포함할 수 있다. 방법(400)은, 402에서, 입력 페이지 크기 표시와 TLB의 엔트리의 엔트리 페이지 크기 표시의 비교에 기초하여, 컴퓨팅된 페이지 크기를 결정하는 단계를 포함할 수 있다. 예를 들어, 도 2에서, 중첩 체크 명령(260)의 실행 동안, 중첩 체크 로직(276)은, 입력 페이지 크기 표시와 TLB 엔트리들(272) 중 하나의 엔트리 페이지 크기 표시의 비교에 기초하여, 컴퓨팅된 페이지 크기를 결정할 수 있다.

- [0055] [0060] 방법(400)은 또한, 404에서, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정하기 위해, 컴퓨팅된 페이지 크기에 기초하여, 엔트리의 엔트리 가상 어드레스와 입력 가상 어드레스의 마스킹된 비교를 수행하는 단계를 포함할 수 있다. 예를 들어, 도 2에서, 중첩 체크 로직(276)은 컴퓨팅된 페이지 크기에 기초하여 마스킹된 비교를 수행할 수 있다.

- [0056] [0061] 방법(400)은, 406에서, TLB의 임의의 검사되지 않은 엔트리들이 남아 있는지를 결정하는 단계를 더 포함할 수 있다. 특정한 실시예에서, TLB의 모든 엔트리들은 동시에 검사될 수 있다. TLB에 검사되지 않은 엔트리들이 여전히 존재하면, 방법(400)은 402로 리턴할 수 있다. 어떠한 검사되지 않은 엔트리들도 남아 있지 않으면, 방법(400)은 408에서 실행 결과를 출력하는 단계, 및 410에서 프로세서의 레지스터에 실행 결과를 저장하는 단계를 포함할 수 있다. 예를 들어, 도 2에서, 중첩 체크 로직(276)은 실행 결과를 범용 레지스터 파일(226)에 저장할 수 있다. 실행 결과는, 불 결과, 입력 페이지와 중첩하는 엔트리 페이지들에 대응하는 TLB의 엔트리들의 수, 입력 페이지와 중첩하는 특정 엔트리 페이지에 대응하는 TLB의 특정 엔트리 등일 수 있다. 대안적인 실

시예에서, 중첩이 식별되면, 방법(400)은 중첩 표시를 출력하고, 추가적인 TLB 엔트리들을 검사하는 것을 계속하는 대신에 종료할 수 있다. 따라서, 도 4의 방법(400)은, 입력 페이지에 대한 TLB에 새로운 엔트리를 생성하는 것이 TLB에서 중첩하는 엔트리들을 초래할지를 결정하기 위해, 중첩 체크 명령의 실행을 가능하게 할 수 있다.

[0057] [0062] 특정한 실시예에서, 도 4의 방법(400)은 DSP, CPU, 제어기, 필드-프로그래머블 게이트 어레이(FPGA) 디바이스, 주문형 집적 회로(ASIC), 다른 하드웨어 디바이스, 펌웨어 디바이스 또는 이들의 임의의 조합에 의해 구현될 수 있다. 일례로, 도 4의 방법(400)은, 도 6에 대해 설명된 바와 같이, 명령들을 실행하는 프로세서에 의해 수행될 수 있다.

[0058] [0063] 도 5는, 조건부 TLB 기록 명령을 실행하는 방법(500)의 특정한 실시예의 흐름도이다. 예시적인 실시예에서, 방법(500)은 도 1의 시스템(100) 또는 도 2의 시스템(200)에서 수행될 수 있다.

[0059] [0064] 도 5에 도시된 각각의 동작은 TLB를 포함하는 프로세서에서 조건부 TLB 기록 명령의 실행 동안 수행될 수 있다. TLB는, 엔트리 페이지에 대응하는 엔트리 페이지 크기 표시 및 엔트리 가상 어드레스를 갖는 적어도 하나의 엔트리를 포함할 수 있다. 조건부 TLB 기록 명령은, 입력 페이지에 대응하는 입력 페이지 크기 표시 및 입력 가상 어드레스를 포함할 수 있다. 방법(500)은, 502에서, 입력 페이지 크기 표시와 엔트리 페이지 크기 표시의 비교에 기초하여, 컴퓨팅된 페이지 크기를 결정하는 단계를 포함할 수 있다. 예를 들어, 도 2에서, 조건부 TLB 기록 명령(262)의 실행 동안, 중첩 체크 로직(276)은, 입력 페이지 크기 표시와 TLB 엔트리들(272) 중 하나의 엔트리 페이지 크기 표시의 비교에 기초하여, 컴퓨팅된 페이지 크기를 결정할 수 있다.

[0060] [0065] 방법(500)은 또한, 504에서, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정하기 위해, 컴퓨팅된 페이지 크기에 기초하여, 엔트리의 엔트리 가상 어드레스와 입력 가상 어드레스의 마스킹된 비교를 수행하는 단계를 포함할 수 있다. 예를 들어, 도 2에서, 중첩 체크 로직(276)은 컴퓨팅된 페이지 크기에 기초하여 마스킹된 비교를 수행할 수 있다.

[0061] [0066] 방법(500)은, 506에서, TLB의 임의의 검사되지 않은 엔트리들이 남아 있는지를 결정하는 단계를 더 포함할 수 있다. 대안적인 실시예에서, 중첩이 식별되면, 방법(500)은 중첩 표시를 출력하고, 추가적인 TLB 엔트리들을 검사하는 것을 계속하는 대신에 종료할 수 있다. TLB에 검사되지 않은 엔트리들이 여전히 존재하면, 방법(500)은 502로 리턴할 수 있다. 어떠한 검사되지 않은 엔트리들도 남아 있지 않으면, 방법(500)은, 508에서, 입력 페이지가 적어도 하나의 엔트리 페이지와 중첩하는지를 결정하는 단계를 포함할 수 있다.

[0062] [0067] 어떠한 엔트리 페이지도 입력 페이지와 중첩하지 않는 경우, 방법(500)은, 510에서, 입력 페이지 크기 표시 및 입력 가상 어드레스를 TLB의 제 2 엔트리에 기록하는 단계를 포함할 수 있다. 적어도 하나의 엔트리 페이지가 입력 페이지와 중첩하는 경우, 방법(500)은, 512에서 기록 실패를 나타내는 실행 결과를 출력하는 단계를 포함할 수 있다. 따라서, 도 5의 방법(500)은, TLB에서 중첩에 대해 체크하고, 어떠한 중첩도 검출되지 않으면 TLB에 새로운 엔트리를 생성하기 위한 단일 명령의 실행을 가능하게 할 수 있다.

[0063] [0068] 특정한 실시예에서, 도 5의 방법(500)은 DSP, CPU, 제어기, 필드-프로그래머블 게이트 어레이(FPGA) 디바이스, 주문형 집적 회로(ASIC), 다른 하드웨어 디바이스, 펌웨어 디바이스 또는 이들의 임의의 조합에 의해 구현될 수 있다. 일례로, 도 5의 방법(500)은, 도 6에 대해 설명된 바와 같이, 명령들을 실행하는 프로세서에 의해 수행될 수 있다.

[0064] [0069] 도 6을 참조하면, 전자 디바이스(600)의 블록도가 도시된다. 특정한 실시예에서, 전자 디바이스(600) 또는 이들의 컴포넌트들은, 통신 디바이스, 컴퓨팅 디바이스, 개인 휴대 정보 단말(PDA), 엔터테인먼트 유닛, 셋탑 박스, 뮤직 플레이어, 비디오 플레이어, 내비게이션 디바이스, 고정 위치 데이터 유닛 또는 이들의 임의의 조합에 포함될 수 있다.

[0065] [0070] 전자 디바이스(600)는, 메모리(632)에 커플링된 프로세서(예를 들어, DSP)(610)를 포함한다. 프로세서(610)는 멀티코어 프로세서일 수 있고 그리고/또는 다수의 하드웨어 스레드들을 포함할 수 있다. 예를 들어, 프로세서(610)는 인터리빙된 멀티스레디드 실행을 지원할 수 있다.

[0066] [0071] 도 6은, 프로세서(610) 및 디스플레이(628)에 커플링되는 디스플레이 제어기(626)를 포함한다. 코더/디코더(CODEC)(634)는 프로세서(610)에 커플링될 수 있다. 스피커(636) 및 마이크로폰(638)은 CODEC(634)에 커플링될 수 있다. 도 6은 또한, 무선 제어기(640)가 (예를 들어, 라디오 주파수(RF) 인터페이스를 통해) 프로세서(610) 및 안테나(642)에 커플링될 수 있는 것을 나타낸다.

- [0067] [0072] 메모리(632)는, 실행가능한 명령들을 포함하는 유형의(tangible) 비일시적 컴퓨터 관독가능 또는 프로세서-관독가능 저장 매체일 수 있다. 명령들은, 도 3, 4, 및 5의 방법들(300, 400 및 500)을 포함하는 본 명세서에서 설명된 다양한 기능들 및 방법들을 수행하기 위해, 프로세서(610)와 같은 프로세서에 의해 실행될 수 있다. 예를 들어, 메모리(632)는 중첩 체크 명령(260) 및 조건부 TLB 기록 명령(262)을 저장할 수 있다. 명령들(260 및 262)의 실행은 프로세서(610)의 TLB(270)에서 중첩 체크 동작들을 트리거링할 수 있다. 예를 들어, 이러한 중첩 체크 동작들은, 도 2를 참조하여 설명된 바와 같이, TLB 엔트리들(272), 입력 로직(274), 중첩 체크 로직(276) 및/또는 기록 로직(278)을 수반할 수 있다.

- [0068] [0073] 특정한 실시예에서, 프로세서(610), 디스플레이 제어기(626), 메모리(632), CODEC(634) 및 무선 제어기(640)는 시스템-인-패키지 또는 시스템-온-칩 디바이스(622)에 포함된다. 특정한 실시예에서, 입력 디바이스(630) 및 전원(644)은 시스템-온-칩 디바이스(622)에 커플링된다. 아울러, 특정한 실시예에서, 도 6에 도시된 바와 같이, 디스플레이(628), 입력 디바이스(630), 스피커(636), 마이크로폰(638), 안테나(642) 및 전원(644)은 시스템-온-칩 디바이스(622) 외부에 있다. 그러나, 디스플레이(628), 입력 디바이스(630), 스피커(636), 마이크로폰(638), 안테나(642) 및 전원(644) 각각은 인터페이스 또는 제어기와 같은, 시스템-온-칩 디바이스(622)의 컴포넌트에 커플링될 수 있다.

- [0069] [0074] 설명된 실시예들과 함께, 장치는 적어도 하나의 엔트리를 저장하기 위한 수단을 포함한다. 적어도 하나의 엔트리는, 엔트리 페이지에 대응하는 엔트리 페이지 크기 표시 및 엔트리 가상 어드레스를 포함한다. 예를 들어, 저장하기 위한 수단은 도 1의 TLB(130), 도 2의 TLB(270), 데이터를 저장하도록 구성되는 다른 디바이스 또는 모듈 또는 이들의 임의의 조합일 수 있다.

- [0070] [0075] 장치는 또한, 입력 페이지에 대응하는 입력 가상 어드레스 및 입력 페이지 크기 표시를 수신하기 위한 수단을 포함할 수 있다. 예를 들어, 수신하기 위한 수단은, 도 1의 입력 로직(110), 도 2의 입력 로직(274), 데이터를 수신하도록 구성되는 다른 디바이스 또는 모듈 또는 이들의 임의의 조합을 포함할 수 있다.

- [0071] [0076] 장치는, 입력 페이지 크기 표시와 엔트리 페이지 크기 표시의 비교에 기초하여, 컴퓨팅된 페이지 크기를 결정하기 위한 수단을 더 포함할 수 있다. 예를 들어, 결정하기 위한 수단은, 도 1의 페이지 크기 계산 로직(122), 도 2의 중첩 체크 로직(276), 페이지 크기를 컴퓨팅하도록 구성되는 다른 디바이스 또는 모듈 또는 이들의 임의의 조합을 포함할 수 있다.

- [0072] [0077] 장치는, 입력 페이지가 엔트리 페이지와 중첩하는지를 결정하기 위해, 컴퓨팅된 페이지 크기에 기초하여, 엔트리 가상 어드레스와 입력 가상 어드레스의 마스킹된 비교를 수행하기 위한 수단을 포함할 수 있다. 예를 들어, 마스킹된 비교를 수행하기 위한 수단은, 도 1의 마스킹된 비교 로직(124), 도 2의 중첩 체크 로직(276), 마스킹된 비교를 수행하도록 구성되는 다른 디바이스 또는 모듈 또는 이들의 임의의 조합을 포함할 수 있다.

- [0073] [0078] 당업자들은, 본 명세서에서 개시된 실시예들과 관련하여 설명된 로직 블록들, 구성들, 모듈들, 회로들 및 알고리즘 단계들이 전자 하드웨어, 프로세서에 의해 실행되는 컴퓨터 소프트웨어 또는 이 둘의 조합으로 구현될 수 있음을 추가로 인식할 것이다. 다양한 예시적인 컴포넌트들, 블록들, 구성들, 모듈들, 회로들 및 단계들은 이들의 기능의 관점에서 설명되었다. 이러한 기능이 하드웨어로 구현되는지, 또는 프로세서 실행가능 명령들로 구현되는지 여부는 특정 애플리케이션, 및 전체 시스템에 대해 부과된 설계 제한들에 의존한다. 당업자들은 설명된 기능을 각각의 특정 애플리케이션에 대해 다양한 방식들로 구현할 수 있지만, 이러한 구현 결정들이 본 개시의 범주를 벗어나는 것으로 해석되어서는 안 된다.

- [0074] [0079] 본 명세서에 개시된 실시예들과 관련하여 설명되는 알고리즘 또는 방법의 단계들은 직접적으로 하드웨어로, 프로세서에 의해 실행되는 소프트웨어 모듈로, 또는 이 둘의 조합으로 구현될 수 있다. 소프트웨어 모듈은 랜덤 액세스 메모리(RAM), 플래쉬 메모리, 관독 전용 메모리(ROM), 프로그래머블 관독 전용 메모리(PROM), 소거 가능한 프로그래머블 관독 전용 메모리(EPROM), 전기적으로 소거가능한 프로그래머블 관독 전용 메모리(EEPROM), 레지스터들, 하드디스크, 착탈식 디스크, 컴팩티 디스크 관독 전용 메모리(CD-ROM), 디지털 다기능 디스크(DVD) 또는 업계에 공지된 임의의 다른 형태의 비일시적 저장 매체에 상주할 수 있다. 예시적인 저장 매체는, 프로세서가 저장 매체로부터 정보를 관독하고, 저장 매체에 정보를 기록할 수 있도록 프로세서에 연결된다. 대안적으로, 저장 매체는 프로세서에 통합될 수 있다. 프로세서 및 저장 매체는 주문형 집적 회로(ASIC)에 상주할 수도 있다. ASIC은 컴퓨팅 디바이스 또는 사용자 단말에 상주할 수 있다. 대안적으로, 프로세서 및 저장 매체는 컴퓨팅 디바이스 또는 사용자 단말에서 개별 컴포넌트들로서 상주할 수 있다.

[0075]

[0080] 개시된 실시예들의 전술한 설명은 당업자가 개시된 실시예들을 이용하거나 또는 실시할 수 있도록 제공된다. 이러한 실시예들에 대한 다양한 변형들은 당업자들에게 쉽게 명백할 것이며, 본 명세서에 정의된 일반적인 원리들은 본 개시의 범주를 벗어남이 없이 다른 실시예들에 적용될 수 있다. 따라서, 본 개시는 본 명세서에 제시된 실시예들로 한정되는 것으로 의도되는 것이 아니라, 다음의 청구항들에 의해 정의되는 바와 같은 원리들 및 신규한 특징들과 일치하는 가장 넓은 범위에 부합한다.

## 도면

### 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6