(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-36211

(P2007-36211A)

(43) 公開日 平成19年2月8日(2007.2.8)

| (51) Int.C1.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>HO1L 29/739</b> (2006.01) | HO1L 29/78 | 655A        |

| <b>HO1L 29/78</b> (2006.01)  | HO1L 29/78 | 652L        |

| <b>HO1L 21/336</b> (2006.01) | HO1L 29/78 | 658F        |

| <b>HO1L 21/28</b> (2006.01)  | HO1L 21/28 | 301R        |

| <b>HO1L 29/41</b> (2006.01)  | HO1L 29/44 | L           |

審査請求 未請求 請求項の数 15 O L (全 13 頁)

|              |                              |          |                                                    |

|--------------|------------------------------|----------|----------------------------------------------------|

| (21) 出願番号    | 特願2006-169083 (P2006-169083) | (71) 出願人 | 503361248                                          |

| (22) 出願日     | 平成18年6月19日 (2006.6.19)       |          | 富士電機デバイステクノロジー株式会社                                 |

| (31) 優先権主張番号 | 特願2005-179720 (P2005-179720) |          | 東京都品川区大崎一丁目11番2号                                   |

| (32) 優先日     | 平成17年6月20日 (2005.6.20)       | (74) 代理人 | 100104190                                          |

| (33) 優先権主張国  | 日本国 (JP)                     |          | 弁理士 酒井 昭徳                                          |

|              |                              | (72) 発明者 | 風間 健一<br>東京都品川区大崎一丁目11番2号 富士<br>電機デバイステクノロジー株式会社内  |

|              |                              | (72) 発明者 | 中嶋 経宏<br>東京都品川区大崎一丁目11番2号 富士<br>電機デバイステクノロジー株式会社内  |

|              |                              | (72) 発明者 | 佐々木 弘次<br>東京都品川区大崎一丁目11番2号 富士<br>電機デバイステクノロジー株式会社内 |

最終頁に続く

(54) 【発明の名称】半導体素子の製造方法

## (57) 【要約】

【課題】アルミニウムシリコン電極のシリコン濃度および厚さを最適化することにより、素子の裏面に電極を有する90~200μmの厚さの半導体素子を高い良品率で製造すること。

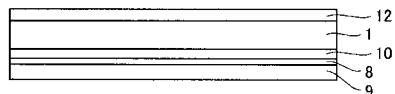

【解決手段】シリコン基板の第1の主面側に素子の表面構造を形成し、第2の主面を研削加工して基板を薄くした後、第2の主面側にバッファ層10およびコレクタ層8を形成する。その後、コレクタ層8の表面に、厚さが0.3μm以上1.0μm以下で、シリコン濃度が0.5wt%以上2wt%以下、好ましくは1wt%以下のアルミニウムシリコン膜を第1層目とするコレクタ電極9を形成する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

シリコン基板の第1の主面側に素子の表面構造を有し、かつ前記シリコン基板の第2の主面側に裏面電極を有する半導体素子を製造するにあたって、

前記裏面電極としてアルミニウムシリコン膜を前記第2の主面に接して形成することを特徴とする半導体素子の製造方法。

**【請求項 2】**

前記アルミニウムシリコン膜の表面にバッファ金属膜を形成することを特徴とする請求項1に記載の半導体素子の製造方法。

**【請求項 3】**

前記バッファ金属膜の表面に半田接合金属膜を形成し、さらに前記半田接合金属膜の表面に保護金属膜を形成することを特徴とする請求項2に記載の半導体素子の製造方法。

**【請求項 4】**

前記アルミニウムシリコン膜におけるシリコン濃度を0.5wt%以上にすることを特徴とする請求項1～3のいずれか一つに記載の半導体素子の製造方法。

**【請求項 5】**

前記アルミニウムシリコン膜の厚さを0.3μm以上にすることを特徴とする請求項1～4のいずれか一つに記載の半導体素子の製造方法。

**【請求項 6】**

前記アルミニウムシリコン膜におけるシリコン濃度を2wt%以下にすることを特徴とする請求項5に記載の半導体素子の製造方法。

**【請求項 7】**

前記アルミニウムシリコン膜におけるシリコン濃度を1wt%以下にすることを特徴とする請求項5に記載の半導体素子の製造方法。

**【請求項 8】**

前記アルミニウムシリコン膜の厚さを1.0μm以下にすることを特徴とする請求項5～7のいずれか一つに記載の半導体素子の製造方法。

**【請求項 9】**

前記アルミニウムシリコン膜を形成する前に、前記シリコン基板の厚さを50μm以上200μm以下にすることを特徴とする請求項1～8のいずれか一つに記載の半導体素子の製造方法。

**【請求項 10】**

前記バッファ金属膜をチタンまたはモリブデンで形成することを特徴とする請求項1～9のいずれか一つに記載の半導体素子の製造方法。

**【請求項 11】**

前記第1の主面と前記第2の主面の間に、前記第1の主面側から順に、第1導電型のドリフト層、第1導電型のバッファ層および第2導電型のコレクタ層を有し、かつ前記コレクタ層が前記アルミニウムシリコン膜に接する構成のフィールドトップ型の絶縁ゲート型バイポーラトランジスタを製造することを特徴とする請求項1～10のいずれか一つに記載の半導体素子の製造方法。

**【請求項 12】**

シリコン基板の第1の主面と第2の主面の間に、前記第1の主面側から順に、第1導電型のドリフト層および第2導電型のコレクタ層を有し、かつ前記コレクタ層を含む第2導電型の半導体領域が前記ドリフト層を囲み、さらに前記コレクタ層に接する裏面電極を備えた逆阻止型の絶縁ゲート型バイポーラトランジスタを構成する半導体素子を製造するにあたって、

前記裏面電極としてアルミニウムまたはアルミニウム合金からなる0.3μm以上の厚さの膜を前記コレクタ層に接して形成することを特徴とする半導体素子の製造方法。

**【請求項 13】**

シリコン基板の第1の主面と第2の主面の間に、前記第1の主面側から順に、第1導電

10

20

30

40

50

型のドリフト層および第2導電型のコレクタ層を有し、かつ前記コレクタ層を含む第2導電型の半導体領域が前記ドリフト層を囲み、さらに前記コレクタ層に接する裏面電極を備えた逆阻止型の絶縁ゲート型バイポーラトランジスタを構成する半導体素子を製造するにあたって、

前記裏面電極としてシリコンの濃度が2wt%以上のアルミニウム合金膜を前記コレクタ層に接して形成することを特徴とする半導体素子の製造方法。

【請求項14】

シリコン基板の第1の主面と第2の主面の間に、前記第1の主面側から順に、第1導電型のドリフト層、第1導電型のバッファ層および第2導電型のコレクタ層を有し、かつ前記コレクタ層に接する裏面電極を備えたフィールドストップ型の絶縁ゲート型バイポーラトランジスタを構成する半導体素子を製造するにあたって、

前記裏面電極としてアルミニウムまたはアルミニウム合金からなる0.3μm以上の厚さの膜を前記コレクタ層に接して形成することを特徴とする半導体素子の製造方法。

【請求項15】

シリコン基板の第1の主面と第2の主面の間に、前記第1の主面側から順に、第1導電型のドリフト層、第1導電型のバッファ層および第2導電型のコレクタ層を有し、かつ前記コレクタ層に接する裏面電極を備えたフィールドストップ型の絶縁ゲート型バイポーラトランジスタを構成する半導体素子を製造するにあたって、

前記裏面電極としてシリコンの濃度が2wt%以上のアルミニウム合金膜を前記コレクタ層に接して形成することを特徴とする半導体素子の製造方法。

10

20

30

40

50

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体素子の製造方法に関し、特に電力変換装置などに用いられるパワー半導体素子であって、素子の裏面に電極を有する90~200μmの厚さの半導体素子の製造方法に関する。

【背景技術】

【0002】

電力用半導体素子の一つであるIGBT(絶縁ゲート型バイポーラトランジスタ)は、MOSFET(絶縁ゲート型電界効果トランジスタ)の高速スイッチング特性および電圧駆動特性と、バイポーラトランジスタの低オン電圧特性を有するワンチップのパワー素子である。その応用範囲は、汎用インバータ、ACサーボ、無停電電源(UPS)またはスイッチング電源などの産業分野から、電子レンジ、炊飯器またはストロボなどの民生機器分野へと拡大してきている。また、新しいチップ構造を用いた、より低オン電圧のIGBTが開発されており、IGBTを用いた応用装置の低損失化や高効率化が図られてきている。

【0003】

IGBTには、パンチスルー(以下、PTとする)型、ノンパンチスルー(以下、NP型とする)型、フィールドストップ(以下、FSとする)型などの構造があり、一部の用途を除いて、nチャネル型の縦型二重拡散構造のものが主流である。従って、本明細書では、nチャネル型IGBTを例にして説明するが、pチャネル型IGBTでも同様である。

【0004】

PT型IGBTは、p<sup>+</sup>半導体基板上にn<sup>+</sup>バッファ層とn<sup>-</sup>活性層をエピタキシャル成長させたエピタキシャル基板を用いて形成される。そのため、例えば耐圧600V系の素子では、活性層の厚さは100μm程度で十分であるが、p<sup>+</sup>半導体基板の部分を含む総厚さは200~300μm程度と、厚くなる。また、エピタキシャル基板を用いるため、

コストが高くなる。

【0005】

そこで、エピタキシャル基板の代わりに、フローティングゾーン(FZ)法により作製された半導体インゴットから切り出されたFZ基板を用いることによって低コスト化を図ったNPT型やFS型のIGBTが開発されている。これらのIGBTでは、素子の裏面側に低ドーズ量の浅いp<sup>+</sup>コレクタ層(低注入p<sup>+</sup>コレクタ)が形成される。

【0006】

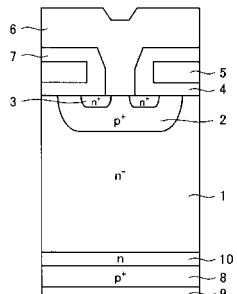

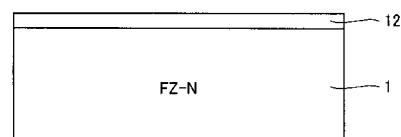

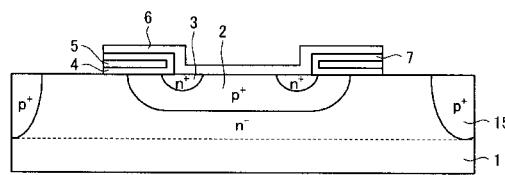

図1は、FZ基板を用いて作製されたNPT型IGBTの構成を示す断面図である。図1に示すように、例えばFZ基板よりなるn<sup>-</sup>半導体基板を活性層1とし、その表面側にp<sup>+</sup>ベース領域2、n<sup>+</sup>エミッタ領域3が選択的に形成されている。また、基板表面上には、ゲート酸化膜4を介してゲート電極5が形成されている。エミッタ電極6は、エミッタ領域3およびベース領域2に接触しているとともに、層間絶縁膜7によりゲート電極5から絶縁されている。

【0007】

基板裏面には、p<sup>+</sup>コレクタ層8およびコレクタ電極9が形成されている。NPT型の場合には、PT型の場合よりも基板の総厚さが大幅に薄くなる。そして、正孔の注入率を制御することができるので、ライフタイム制御を行わなくとも、高速スイッチングが可能である。また、エピタキシャル基板を用いずに、FZ基板を用いているので、安価である。

【0008】

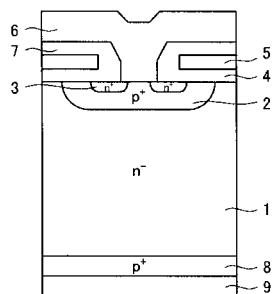

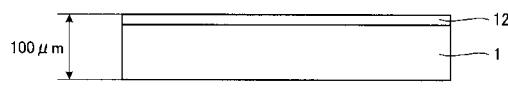

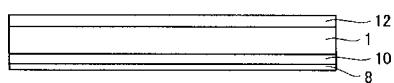

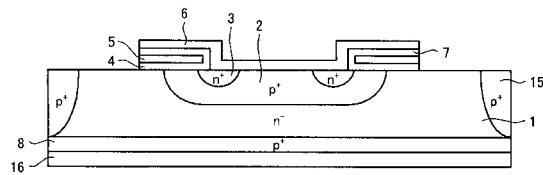

図2は、FS型IGBTの構成を示す断面図である。図2に示すように、基板表面側の素子構造は、図1に示すNPT型の素子と同じである。基板裏面側には、n<sup>-</sup>活性層1とp<sup>+</sup>コレクタ層8との間に、nバッファ層10が設けられている。FS型の場合には、FZ基板を用いることによって、基板の総厚さが100~200μmとなる。

【0009】

PT型の場合と同様に、活性層1を空乏化させるため、600V耐圧の素子では、活性層1の厚さは100μm程度である。そして、NPT型と同様に、ライフタイム制御が不要である。近時、オン電圧のより一層の低減を図るため、チップ表面に狭く深い溝を形成し、この溝の側面にMOSFETを形成したトレンチ構造と、FS型構造を組み合わせた構造のIGBTも提案されている。

【0010】

FZ基板を用いてFS型IGBTを製造するにあたっては、まず、基板表面に素子の表面構造を作製する。その後に、基板裏面のグラインドを行って基板を薄くする。ついで、その薄化した基板の裏面に2種類のイオンを注入し、活性化熱処理を行って、基板裏面側にバッファ層10とコレクタ層8を形成する。そして、コレクタ層8の表面にアルミニウム(Al)等の金属を蒸着またはスパッタしてコレクタ電極9を形成する。

【0011】

一方、マトリクスコンバータ等の用途に適したIGBTとして、逆耐圧を有するIGBT(以下、逆阻止型IGBTとする)が市場で求められている。例えばnチャネル型の逆阻止型IGBTは、通常のnチャネル型IGBTの側部に高濃度のp型分離領域を形成し、このp型分離領域をコレクタ層に接続した構成となっている。FZ基板を用いて逆阻止型IGBTを製造するにあたっては、まず、基板の表面側から不純物を選択的に拡散させて分離領域を形成する。その後に、FS型IGBTの場合と同様に、素子の表面構造の作製、基板裏面のグラインド、および基板裏面へのイオン注入と活性化熱処理を順に行い、蒸着またはスパッタによりコレクタ電極を形成する。

【0012】

FS型IGBTでは、順方向バイアスの印加時にバッファ層に強電界がかかり、逆阻止型IGBTでは、逆バイアスの印加時に素子の裏面側のPN接合部に強電界がかかる。しかし、これらの素子では、裏面側のPN接合深さが0.3μmと薄いため、裏面側の表面にわずかな傷が入ると、容易にパンチスルーやショートが発生する。素子本来の機能が損なわれてしまう。

10

20

30

40

50

。

## 【0013】

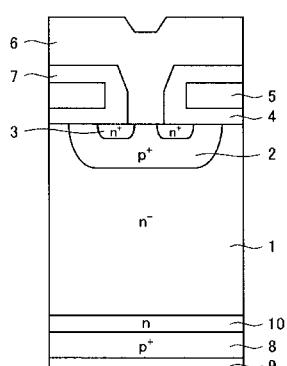

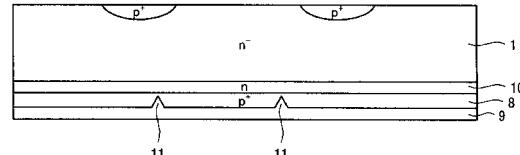

一方、コレクタ電極としてA1等の金属を蒸着またはスパッタすると、図3に示すように、コレクタ層8となるシリコン(Si)とコレクタ電極9となる金属電極との界面に、シリコン中に突出する金属のスパイク11が生じやすい。FS型IGBTにおいて、このスパイク11がバッファ層10に達すると、漏れ電流不良を引き起こす。また、逆阻止型IGBTにおいて、スパイク11がPN接合部に達すると、逆耐圧不良や逆漏れ電流不良を引き起こす。上述した薄型IGBTでは、コレクタ層の厚さが薄いため、スパイク11が生じないように基板裏面に金属電極を形成することが、不良低減を図る上で重要である。

10

## 【0014】

ところで、高周波回路に用いられるディスクリートの可変容量ダイオードにおいて、シリコン濃度が3%以上5%以下のアルミニウムシリコン(A1-Si)を用いてアノード電極を形成することにより、シリコンの拡散層へのアルミニウムスパイクを防止するようにしたものが公知である(例えば、特許文献1参照。)。この特許文献1には、高密度集積回路(LSI)では、従来、アルミニウムスパイクを防止するためにシリコン濃度が1~2重量%のアルミニウムシリコンの電極を用いていることが記載されている。

## 【0015】

【特許文献1】特開2002-343980号公報

20

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0016】

しかしながら、上記特許文献1に開示されたアルミニウムシリコン電極は、ディスクリートの可変容量ダイオードまたはLSI用に適した電極であり、IGBT等の電力用半導体素子の裏面電極においてアルミニウムスパイクが発生するのを回避するのには、適当ではない。特に、バックグラインド等により薄くされた基板の裏面に対してイオン注入を行い、基板裏面に沿って浅い不純物拡散層を形成したパワー半導体素子の場合、アルミニウムスパイクの発生を防ぐためには、アルミニウムシリコン電極のシリコン濃度を最適化する必要がある。また、バックグラインド後の基板が非常に薄いため、アルミニウムシリコン電極が厚いと基板に反りが生じ、基板が割れてしまうなどの不具合があるため、アルミニウムシリコン電極の厚さも最適化する必要がある。

30

## 【0017】

この発明は、上述した従来技術による問題点を解消するため、アルミニウムシリコン等でできた裏面電極の厚さやシリコン濃度を最適化することにより、素子の裏面に電極を有する90~200μmの厚さの半導体素子を高い良品率で製造することができる半導体素子の製造方法を提供することを目的とする。

## 【課題を解決するための手段】

## 【0018】

上述した課題を解決し、目的を達成するため、この発明にかかる半導体素子の製造方法は、以下の特徴を有する。FS型IGBTを製造する場合には、まず、シリコン基板の第1の主面側に素子の表面構造を形成する。その後、第2の主面を加工して基板を50μm以上200μm以下の厚さにしてから、第2の主面側にイオン注入等によりバッファ層とコレクタ層を形成する。その後、裏面電極となるアルミニウムシリコン膜をコレクタ層に接して形成する。

40

## 【0019】

アルミニウムシリコン膜におけるシリコン濃度は、0.5wt%以上であるのが適当である。また、アルミニウムシリコン膜の厚さは、0.3μm以上1.0μm以下であるのが適当である。アルミニウムシリコン膜の厚さがこの範囲にある場合には、アルミニウムシリコン膜におけるシリコン濃度は、2wt%以下、好ましくは1wt%以下であるのが適当である。アルミニウムシリコン膜の表面にチタン(Ti)またはモリブデン(Mo)

50

からなるバッファ金属膜を形成してもよい。また、バッファ金属膜の表面に半田接合金属膜を形成し、さらに半田接合金属膜の表面に保護金属膜を形成してもよい。

【0020】

逆阻止型IGBTを製造する場合には、裏面電極として、アルミニウムまたはアルミニウム合金からなる0.3μm以上の厚さの膜をコレクタ層に接して形成する。このときのアルミニウム合金膜のシリコン濃度は問わない。あるいは、アルミニウム合金膜が0.3μmよりも薄い場合、例えば0.1μm程度である場合には、シリコンの濃度が2wt%以上のアルミニウム合金膜をコレクタ層に接して形成することによって、裏面電極を形成してもよい。FS型IGBTの場合も同様である。この発明によれば、漏れ電流不良や逆耐圧不良や逆漏れ電流不良の原因となるアルミニウムスパイクの発生を防ぐことができる。

10

【発明の効果】

【0021】

本発明にかかる半導体素子の製造方法によれば、アルミニウムシリコン等でできた裏面電極の厚さやシリコン濃度を最適化することにより、アルミニウムスパイクの発生を防ぐことができる。従って、素子の裏面に電極を有する90~200μmの厚さの半導体素子を高い良品率で製造することができるという効果を奏する。

【発明を実施するための最良の形態】

【0022】

以下に添付図面を参照して、この発明にかかる半導体素子の製造方法の好適な実施の形態を詳細に説明する。本明細書および添付図面において、nまたはpを冠記した層や領域では、それぞれ電子または正孔が多数キャリアであることを意味する。また、nやpに付す+および-は、それぞれそれが付されていない層や領域よりも高不純物濃度および低不純物濃度であることを意味する。なお、以下の実施の形態の説明および添付図面において、同様の構成には同一の符号を付し、重複する説明を省略する。

20

【0023】

実施の形態1.

図2および図4~図8は、本発明方法を適用してFS型IGBTを製造する方法を説明するための断面図である。まず、図2および図4に示すように、活性層(ドリフト層)1となるn-FZ基板(FZ-N)の表面側に、ベース領域、エミッタ領域、ゲート酸化膜、ゲート電極、層間絶縁膜、エミッタ電極および絶縁保護膜(図2では、省略)よりなる表面側素子構造部12を形成する。

30

【0024】

ゲート酸化膜は、例えば酸化シリコン(SiO<sub>2</sub>)でできている。ゲート電極は、例えばポリシリコンでできている。層間絶縁膜は、例えばBPSGでできている。エミッタ電極は、例えばアルミニウムシリコン膜でできている。アルミニウムシリコン膜は、安定した接合性を有する低抵抗配線を実現するために、350~450程度の低温で熱処理される。絶縁保護膜は、例えばポリイミド膜でできている。

30

【0025】

ついで、図5に示すように、基板の裏面を、バックグラインド、ポリッシュまたはエッティング等(以下、これらをまとめてバックグラインド等とする)の加工方法を単独または組み合わせて研削し、基板を50μm以上200μm以下の厚さ、例えば100μmの厚さとする。なお、エッティングの場合、厳密には研削ではないが、本明細書では、基板を薄くする手段については問わないので、エッティングを含めて研削とする。

40

【0026】

ついで、図6に示すように、基板の裏面から、例えばn型イオンであるリンと、p型イオンであるボロンをイオン注入し、電気炉で350~450の熱処理(アニール)を行い、基板裏面側にバッファ層10およびコレクタ層8を形成する。その後、図7に示すように、基板の裏面、すなわちコレクタ層8の表面に、多層膜よりなるコレクタ電極(裏面電極)9の第1層目の導電膜として、アルミニウムシリコン膜を蒸着またはスパッタによ

50

り形成する。

【0027】

その際、アルミニウムシリコン膜を、そのシリコン濃度が0.5wt%以上2wt%以下、好ましくは1wt%以下となり、かつその厚さが0.3μm以上となるように形成する。ただし、アルミニウムシリコン膜が1.0μmよりも厚くなると、基板の反りが大きくなり、組み立て不良が増加するため、好ましくない。このような条件でアルミニウムシリコン膜を形成することにより、アルミニウムスパイクの発生を防ぐことができるので、組み立て時の不良発生率を低減することができる。

【0028】

アルミニウムシリコン膜の形成に続いて、チタン、ニッケルおよび金などの複数の金属を蒸着またはスパッタにより形成し、コレクタ電極9を形成する。チタン膜、ニッケル膜および金膜は、それぞれバッファ金属膜、半田接合金属膜および保護金属膜である。なお、バッファ金属膜をモリブデンで形成してもよい。

【0029】

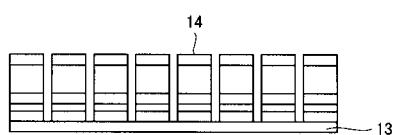

最後に、図8に示すように、コレクタ電極9側にダイシングテープ13を貼り付けてダイシングを行い、複数のチップ14に分割する。各チップ14は、そのコレクタ電極9が装置の固定部材に半田付けされ、かつエミッタ電極等の表面電極にアルミニウム電極が超音波ワイヤボンディング装置により固着されることにより、種々の装置に実装される。

【0030】

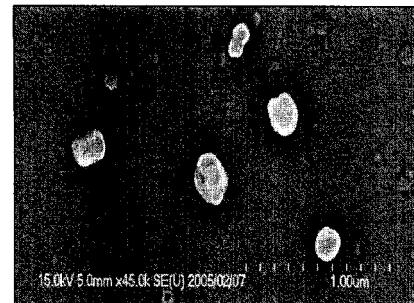

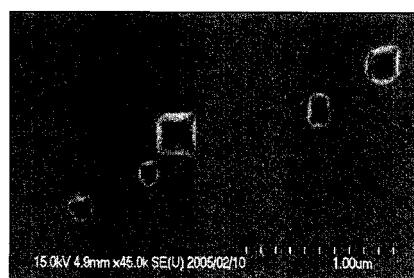

図9は、上述した厚さおよびシリコン濃度を満たすアルミニウムシリコン膜を蒸着またはスパッタによりシリコンの表面に形成した後、王水を用いてそのアルミニウムシリコン膜を剥がしてシリコン面を露出させ、その表面状態を観察した電子顕微鏡写真である。図10は、アルミニウムシリコン膜の代わりにアルミニウム膜を形成した後、王水を用いてそのアルミニウム膜を剥がしてシリコン面を露出させ、その表面状態を観察した電子顕微鏡写真である。図10では、アルミニウムスパイクによってできた傷が観察されるが、図9にはその傷が認められない。つまり、実施の形態1によれば、アルミニウムスパイクの発生を防ぐことができる。

【0031】

なお、コレクタ電極9の、コレクタ層8と接する第1層目を、0.3μm以上の厚さのアルミニウム膜とするとアルミニウムスパイクの発生を小さくすることができる。また、0.3μm以上の厚さのアルミニウム合金膜（シリコンの濃度は問わない）とするとアルミニウムスパイクの発生を防ぐかあるいは小さくすることができる。また、そのコレクタ電極9の第1層目を0.3μmよりも薄いアルミニウム合金膜とする場合、例えば0.1μm程度の厚さにする場合には、そのアルミニウム合金膜のシリコン濃度を2wt%以上にするとよい。このようにしても、アルミニウムスパイクの発生を防ぐことができる。これらについては、実施の形態2で詳述する。

【0032】

実施の形態2.

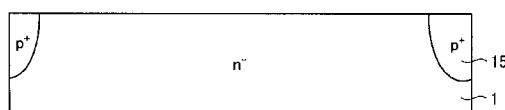

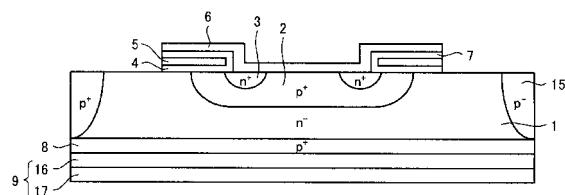

図11～図14は、本発明方法を適用して逆阻止型IGBTを製造する方法を説明するための断面図である。まず、図11に示すように、活性層（ドリフト層）1となるn-FZ基板の上から選択的にp型イオンを熱拡散させてp型の分離領域15を形成する。例えば定格1200Vの素子を製造する場合には、p型イオンを200μm程度、拡散させる。

【0033】

ついで、図12に示すように、FZ基板の、分離領域15で囲まれる領域の表面側に、ベース領域2、エミッタ領域3、ゲート酸化膜4、ゲート電極5、層間絶縁膜7、エミッタ電極6および図示省略した絶縁保護膜よりなる表面側素子構造部を形成する。ついで、バックグラインド等により基板の裏面を研削する。その際、図12に点線で示すように、分離領域15が現れるまで基板裏面を研削する。

【0034】

10

20

30

40

50

ついで、図13に示すように、基板の裏面から、p型イオンを注入し、熱処理（アニール）を行って、基板裏面側にコレクタ層8を形成する。その後、コレクタ層8の表面に、多層膜よりなるコレクタ電極（裏面電極）9の第1層目の導電膜として、蒸着またはスパッタによりアルミニウム膜16を形成する。このとき、アルミニウム膜16の厚さを0.3μm以上、例えば0.6μmの厚さに形成することによって、アルミニウムスパイクの発生を小さくすることができるので、組み立て時の不良発生率を低減することができる。

#### 【0035】

アルミニウム膜16の形成に続いて、図14に示すように、チタン、ニッケルおよび金などの複数の金属層17を蒸着またはスパッタにより形成し、コレクタ電極9を形成する。最後に、実施の形態1と同様に、ダイシングを行って複数のチップに分割する。

10

#### 【0036】

なお、コレクタ電極9の、コレクタ層8と接する第1層目を、0.3μm以上の厚さのアルミニウム合金膜（シリコンの濃度は問わない）にしても同様の効果が得られる。また、そのアルミニウム合金膜の厚さを0.3μmよりも薄くする場合、例えば0.1μm程度の厚さにする場合には、そのアルミニウム合金膜のシリコン濃度を2wt%以上にするとよい。このようにしても、アルミニウムスパイクの発生を防ぐことができる。

#### 【0037】

図15～図17は、蒸着またはスパッタによりシリコンの表面に、第1層目がアルミニウム膜である多層構造の電極を形成し、熱処理した後に、王水を用いてその電極を剥がしてシリコン面を露出させ、その表面状態を観察した電子顕微鏡写真である。図15は、アルミニウム膜の厚さが0.1μmのものであり、シリコンの表面にアルミニウムスパイクによってできた0.2μm程度の深さの傷が観察される。

20

#### 【0038】

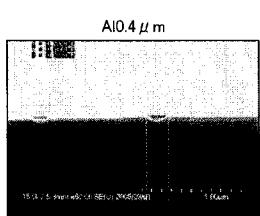

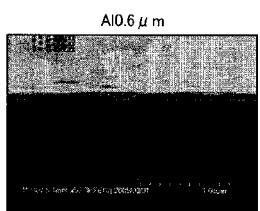

図16および図17は、それぞれアルミニウム膜の厚さが0.4μmおよび0.6μmのものであり、それぞれの断面の状態を観察した電子顕微鏡写真を図18および図19に示す。図16～図19には、アルミニウムスパイクによる傷が小さくなつたことが認められる。アルミニウム膜の厚さを0.3μmにした場合も、同様である。

20

#### 【0039】

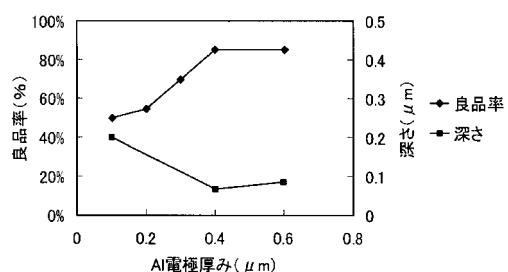

つまり、実施の形態2によれば、多層構造の電極の第1層目を0.3μm以上の厚さのアルミニウム膜にすることによって、アルミニウムスパイクの発生を防ぐことができる。図20に、アルミニウム膜の厚さとアルミニウムスパイクによる傷の深さおよび良品率との関係を調べた結果を示す。図20より、アルミニウム膜の厚さが0.3μm以上であれば、アルミニウムスパイクによる傷が、例えばコレクタ層8の厚さよりも浅くなり、良品率が向上することがわかる。

30

#### 【0040】

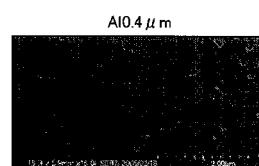

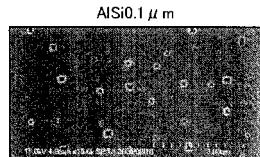

図21～図23は、スパッタによりシリコンの表面に、第1層目がアルミニウムシリコン膜である多層構造の電極を形成し、熱処理した後に、王水を用いてその電極を剥がしてシリコン面を露出させ、その表面状態を観察した電子顕微鏡写真である。図21は、アルミニウムシリコン膜の厚さが0.1μmのものであり、シリコンの表面にアルミニウムスパイクによってできた傷が観察される。

40

#### 【0041】

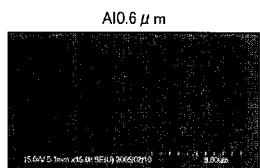

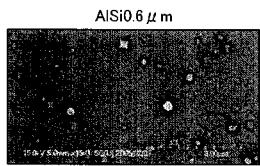

図22および図23は、それぞれアルミニウムシリコン膜の厚さが0.4μmおよび0.6μmのものであり、いずれもアルミニウムスパイクによる傷が認められない。アルミニウムシリコン膜の厚さを0.3μmにした場合も、同様である。特に、アルミニウムシリコン膜の厚さを0.4μm以上にすると、アルミニウムスパイクによる傷は皆無となる。その代わり、シリコンモジュールと呼ばれる塊が残るが、良品率に対する悪影響はない。

#### 【0042】

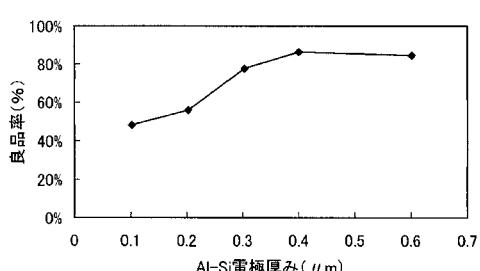

実施の形態2によれば、多層構造の電極の第1層目を0.3μm以上の厚さのアルミニウムシリコン膜にしても、アルミニウムスパイクの発生を防ぐことができる。図24に、

50

アルミニウムシリコン膜の厚さと良品率との関係を調べた結果を示す。図24より、アルミニウムシリコン膜の厚さが0.3μm以上であれば、良品率が向上することがわかる。

【0043】

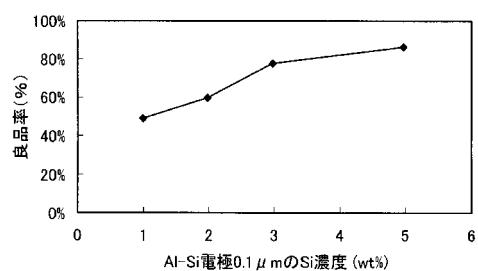

図25は、アルミニウムシリコン膜の厚さを0.1μmとし、スパッタ装置のターゲット材料を変えてアルミニウムシリコン膜のシリコン濃度を変化させたときのシリコン濃度と良品率との関係を調べた結果を示す特性図である。図25より、アルミニウムシリコン膜のシリコン濃度が2wt%以上になると良品率が向上することがわかる。つまり、実施の形態2によれば、多層構造の電極の第1層目であるアルミニウムシリコン膜が薄い場合、例えば0.3μmよりも薄い場合には、シリコン濃度を2wt%以上にすることによって、アルミニウムスパイクの発生を防ぐことができる。

10

【0044】

以上において本発明は、上述した実施の形態に限らず、種々変更可能である。例えば、各実施の形態では第1導電型をn型とし、第2導電型をp型としたが、本発明は第1導電型をp型とし、第2導電型をn型としても同様に成り立つ。

【産業上の利用可能性】

【0045】

以上のように、本発明にかかる半導体素子の製造方法は、デバイス厚の薄い半導体素子を製造するのに有用であり、特に、汎用インバータ、ACサーボ、無停電電源(UPS)またはスイッチング電源などの産業分野や、電子レンジ、炊飯器またはストロボなどの民生機器分野に用いられるIGBT等の電力用半導体素子の製造に適している。

20

【図面の簡単な説明】

【0046】

【図1】NPT型IGBTの構成を示す断面図である。

【図2】FS型IGBTの構成を示す断面図である。

【図3】金属電極からシリコン中へ伸びるスパイクを示す断面図である。

【図4】実施の形態1の製造方法を説明するためのFS型IGBTの断面図である。

【図5】実施の形態1の製造方法を説明するためのFS型IGBTの断面図である。

【図6】実施の形態1の製造方法を説明するためのFS型IGBTの断面図である。

【図7】実施の形態1の製造方法を説明するためのFS型IGBTの断面図である。

【図8】実施の形態1の製造方法を説明するためのFS型IGBTの断面図である。

【図9】アルミニウムシリコン膜を剥がした後のシリコン表面の状態を示す電子顕微鏡写真である。

【図10】アルミニウム膜を剥がした後のシリコン表面の状態を示す電子顕微鏡写真である。

【図11】実施の形態2の製造方法を説明するための逆阻止型IGBTの断面図である。

【図12】実施の形態2の製造方法を説明するための逆阻止型IGBTの断面図である。

【図13】実施の形態2の製造方法を説明するための逆阻止型IGBTの断面図である。

【図14】実施の形態2の製造方法を説明するための逆阻止型IGBTの断面図である。

【図15】アルミニウム膜を剥がした後のシリコン表面の状態を示す電子顕微鏡写真である。

30

【図16】アルミニウム膜を剥がした後のシリコン表面の状態を示す電子顕微鏡写真である。

【図17】アルミニウム膜を剥がした後のシリコン表面の状態を示す電子顕微鏡写真である。

【図18】アルミニウム膜を剥がした後のシリコン断面の状態を示す電子顕微鏡写真である。

【図19】アルミニウム膜を剥がした後のシリコン断面の状態を示す電子顕微鏡写真である。

【図20】アルミニウム膜の厚さとアルミニウムスパイクによる傷の深さおよび良品率との関係を示す特性図である。

40

50

【図21】アルミニウムシリコン膜を剥がした後のシリコン表面の状態を示す電子顕微鏡写真である。

【図22】アルミニウムシリコン膜を剥がした後のシリコン表面の状態を示す電子顕微鏡写真である。

【図23】アルミニウムシリコン膜を剥がした後のシリコン表面の状態を示す電子顕微鏡写真である。

【図24】アルミニウムシリコン膜の厚さと良品率との関係を示す特性図である。

【図25】アルミニウムシリコン膜のシリコン濃度と良品率との関係を示す特性図である。

【符号の説明】

10

【0047】

- 1 シリコン基板、ドリフト層

- 8 コレクタ層

- 9 裏面電極

- 10 バッファ層

- 12 表面側素子構造部

- 15 第2導電型の半導体領域

- 16 アルミニウム膜

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

---

フロントページの続き

(72)発明者 清水 明夫

東京都日野市富士町1番地 富士電機アドバンストテクノロジー株式会社内

(72)発明者 林 崇

東京都日野市富士町1番地 富士電機アドバンストテクノロジー株式会社内

(72)発明者 脇本 博樹

東京都日野市富士町1番地 富士電機アドバンストテクノロジー株式会社内

F ターム(参考) 4M104 BB03 BB05 BB14 BB16 BB38 DD37 FF02 GG09 GG18 HH04