(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5421254号

(P5421254)

(45) 発行日 平成26年2月19日(2014.2.19)

(24) 登録日 平成25年11月29日(2013.11.29)

|                     |                 |

|---------------------|-----------------|

| (51) Int.Cl.        | F 1             |

| H05K 3/46 (2006.01) | H05K 3/46 B     |

| H05K 3/34 (2006.01) | H05K 3/46 N     |

|                     | H05K 3/46 S     |

|                     | H05K 3/34 501 E |

請求項の数 20 (全 10 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2010-514821 (P2010-514821)  |

| (86) (22) 出願日 | 平成20年6月23日 (2008.6.23)        |

| (65) 公表番号     | 特表2010-532567 (P2010-532567A) |

| (43) 公表日      | 平成22年10月7日 (2010.10.7)        |

| (86) 国際出願番号   | PCT/US2008/007978             |

| (87) 国際公開番号   | W02009/005696                 |

| (87) 国際公開日    | 平成21年1月8日 (2009.1.8)          |

| 審査請求日         | 平成23年6月17日 (2011.6.17)        |

| (31) 優先権主張番号  | 11/824,484                    |

| (32) 優先日      | 平成19年6月29日 (2007.6.29)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                           |

|-----------|-------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504142411<br>テッセラ、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア州 95<br>134, サン・ノゼ, オーチャード・<br>パークウェイ 3025 |

| (74) 代理人  | 100099623<br>弁理士 奥山 尚一                                                                    |

| (74) 代理人  | 100096769<br>弁理士 有原 幸一                                                                    |

| (74) 代理人  | 100107319<br>弁理士 松島 鉄男                                                                    |

| (74) 代理人  | 100114591<br>弁理士 河村 英文                                                                    |

| (74) 代理人  | 100118407<br>弁理士 吉田 尚美                                                                    |

最終頁に続く

(54) 【発明の名称】 ピン・インターフェースを有する多層配線エレメント

## (57) 【特許請求の範囲】

## 【請求項 1】

相互接続エレメントのコンタクトを形成する方法であって、

(a) 導電性エレメントと該相互接続エレメントとの間に配置した誘電体層を用いて、該導電性エレメントを、多重配線層を有する前記相互接続エレメントに接合する工程と、

(b) 前記誘電体層の主表面の少なくとも一部をいくつかの導電性ピンの間に露出させて、前記導電性エレメントをパタン形成して前記導電性ピンを形成する工程と、

(c) 前記主表面の露出した前記一部から延びるいくつかの開口部を前記誘電体層に形成する工程と、

(d) 前記導電性ピンを、前記誘電体層の前記開口部を介して、前記相互接続エレメントの導電性部位と電気的に相互接続する工程と

を含んでなる方法。

## 【請求項 2】

工程(a)は、前記導電性エレメントを前記誘電体層で前記相互接続エレメントと接合することを含むものである請求項1に記載の方法。

## 【請求項 3】

前記誘電体層は、接着剤を含むものである請求項2に記載の方法。

## 【請求項 4】

工程(c)は、前記誘電体層に前記開口部の内部へと延び、前記導電性部位を前記導電性ピンと相互接続する導電性トレースを形成することを含むものである請求項2に記載の

10

20

方法。

【請求項 5】

前記導電性エレメントは、単一の金属シートを含むものである請求項 1 に記載の方法。

【請求項 6】

前記導電性エレメントは、層状金属構造体を含むものである請求項 1 に記載の方法。

【請求項 7】

前記層状金属構造体は、外側の金属層と、前記相互接続エレメントに対向する内側の金属層と、前記内側の金属層と前記外側の金属層の間に介在する第 3 の金属層とを含み、工程 ( b ) は、前記外側の金属層を前記第 3 の金属層に関して選択的にエッチングすることを更に含み、工程 ( c ) は、前記導電性部位を前記内側の金属層の 1 以上の部分と相互接続することを含むものである、請求項 6 に記載の方法。10

【請求項 8】

工程 ( c ) は、前記第 3 の金属層と前記内側の金属層に、前記導電性部位と整合した開口部を形成することを更に含むものである請求項 7 に記載の方法。

【請求項 9】

前記内側の金属層は、1 つ以上の第 1 の開口部を有し、工程 ( c ) は、前記第 3 の金属層に、前記第 1 の開口部と前記導電性部位とに整合する貫通開口部を形成することを更に含むものである請求項 7 に記載の方法。

【請求項 10】

相互接続エレメントのコンタクトを形成するための請求項 1 に記載された方法を含む、パッケージチップを形成する方法であって、20

( d ) マイクロエレクトロニクス素子のコンタクトを前記導電性ピンと電気的に相互接続する工程を更に含む方法。

【請求項 11】

相互接続エレメントのコンタクトを形成するための請求項 1 に記載された方法を含む、パッケージチップを形成する方法であって、ここで、前記導電性ピンは、前記相互接続エレメントの第 1 の表面から突出しており、当該方法は、

( d ) マイクロエレクトロニクス素子のコンタクトを、前記相互接続エレメントの前記第 1 の表面から遠隔にある第 2 の表面に露出した前記相互接続エレメントの第 2 の導電性部位と相互接続する工程を更に含む方法。30

【請求項 12】

相互接続エレメントを形成する方法であって、

複数のコンタクトパッドを有する多層基板を用意する工程であって、該多層基板は少なくとも 1 つの誘電体層によって分離された多層配線層を有し、該多層配線層は、前記多層基板の第 1 の表面に露出した複数の導電性構造体を含み、少なくとも 1 つの誘電体層または 1 つ以上の第 2 構造体は、前記第 1 の表面から離れた前記多層基板の第 2 の表面に露出している、多層基板を用意する工程と、

金属層を接合層で前記多層基板に接合する工程と、

前記金属層から、実質的に固体である複数の導電性ポストを形成する工程であって、前記ポストは、前記接合層に沿う横方向に前記ポストの最大の長さを規定する端部を有する、複数のポストを形成する工程と、40

前記接合層内に、前記多層基板のコンタクトパッドを前記複数のポストに電気的に結合させる複数の金属化ビアを形成する工程であって、該金属化ビアは、前記ポストの前記端部を超えて配置されている、形成する工程と

を含んでなる方法。

【請求項 13】

前記接合層は誘電体層を構成することを特徴とする請求項 1 2 に記載の方法。

【請求項 14】

前記誘電体層は接着剤層を構成することを特徴とする請求項 1 3 に記載の方法。

【請求項 15】

前記金属層は単一の金属シートを含むことを特徴とする請求項1\_2に記載の方法。

**【請求項 1 6】**

前記金属層は層状金属構造体を含むことを特徴とする請求項1\_2に記載の方法。

**【請求項 1 7】**

相互接続エレメントのコンタクトを形成するための請求項1\_2に記載された方法を含む、パッケージチップを形成する方法であって、

マイクロエレクトロニクス素子のコンタクトを前記複数のポストに電気的に相互接続する工程を更に含む。方法。

**【請求項 1 8】**

相互接続エレメントのコンタクトを形成するための請求項1\_2に記載された方法を含む、パッケージチップを形成する方法であって、ここで、前記複数のポストは、前記相互接続エレメントの第 1 の表面から突出しており、10

マイクロエレクトロニクス素子のコンタクトを、前記多層基板の前記第 1 の表面からは遠隔にある第 2 の表面に露出した前記多層基板の第 2 の導電性パッドと電気的に相互接続する工程を更に含む、方法。

**【請求項 1 9】**

前記ステップ (c) が、前記誘電体層に関連した前記ピンの位置によって完全に決定されない位置を有する前記開口部を形成するものである、請求項 1 に記載の方法。

**【請求項 2 0】**

前記ポストは、接合処理中に前記ポストが固体であるようにするため、接合金属の融点よりも実質的に高い融点を有する金属から形成される、請求項1\_2に記載の方法。20

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

**[関連出願の相互参照]**

本願は、2007年6月29日に出願された“MULTILAYER WIRING ELEMENT HAVING PIN INTERFACE”と題された米国特許出願第11/824,484号の利益を主張するものである。同米国特許出願の内容は、引用することにより本明細書の一部をなすものとする。

**【0 0 0 2】**

**[発明の分野]**

本発明は一般に、マイクロエレクトロニクス・デバイスを相互接続し、相互接続エレメント、特に多層配線エレメントをサポートする技術に関する。30

**【背景技術】**

**【0 0 0 3】**

フリップチップ実装技術では、マイクロエレクトロニクス・デバイスの正面またはコンタクト支持面は、チップキャリアなどの相互接続エレメントあるいは他の相互接続エレメント、例えば基板に、表を下にして実装される。デバイス上の各コンタクトは、半田付け (solder bond) によって、基板上の対応するコンタクトパッドに接合される。この際、基板またはデバイス上に半田ボールを配置し、デバイスを正面を下向きにして基板と並置し、半田を瞬時にリフローさせて接合する。フリップチップ技術は、チップ自体の面積以下の基板面積を占める、コンパクトなアセンブリを実現する。40

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0 0 0 4】**

しかしながら、熱応力はフリップチップ・アセンブリの設計に重大なチャレンジを投げかける。デバイス・コンタクトと支持基板との間の半田付けは、剛性がかなり高い。デバイスと支持基板の、稼働中の熱膨張収縮に起因する相対的なサイズの変化は、これらの剛性結合に相当なストレスを生み出し、これが半田付けの疲労破損の原因となる可能性がある。さらに、チップを基板へ取り付ける前にチップを検査することは困難であり、このため、仕上がったアセンブリの必要とされる出荷品質レベルを維持することは、特にアセン50

プリが多数のチップを含む場合には、困難である。

**【0005】**

マイクロエレクトロニクス・デバイスあたりの相互接続数が増すにつれ、相互接続の平面性の問題も増大し続ける。相互接続が互いにに関して平面にない場合、相互接続の多くは、標準的なプリント基板などの支持基板上に並置されたそれらのコンタクトパッドに電気的に接触しないという事態が起こり得る。そのため、コプレナー（coplanar）ピンを既存の多層相互接続エレメント上に設ける方法が望まれる。

**【課題を解決するための手段】**

**【0006】**

本発明は、上記課題を解決するための1つの手段として、相互接続エレメントのコンタクト（contacts）を形成する方法を提供する。本方法は、(a)導電性エレメントを、多重配線層（multiple wiring layers）を有する相互接続エレメントに接合する工程と、(b)導電性エレメントをパターン形成して導電性ピンを形成する工程と、(c)導電性ピンを相互接続エレメントの導電性部位（conductive features）と電気的に相互接続する工程とを含む。

10

**【0007】**

本発明は、上記課題を解決するためのもう1つの手段として、露出したピン・インタフェースを有する多重配線層相互接続エレメントも提供する。本エレメントは、少なくとも1つの誘電体層で分離された多重配線層を有する相互接続エレメントと、相互接続エレメントの第1の表面から離れる方向に突出する複数の導電性ピンと、前記多重配線層は相互接続エレメントの第1の表面に露出した複数の導電性部位を含んでおり、これらの導電性部位を導電性ピンと電気的に相互接続する金属トレース（metal features）とを備える。

20

**【図面の簡単な説明】**

**【0008】**

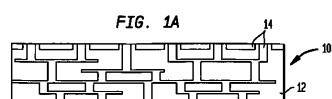

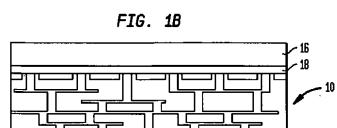

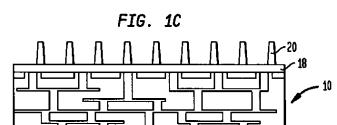

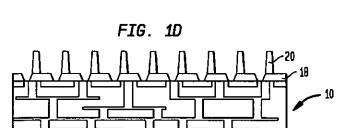

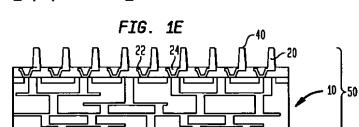

【図1A - 1E】本発明の実施の一形態による、ピン・インタフェースを有する電気相互接続エレメントを組み立てるための方法の手順を説明するための図である。

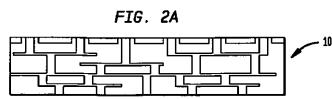

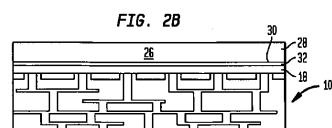

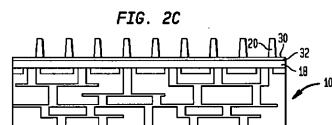

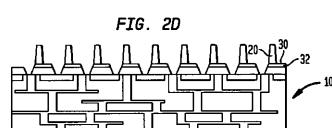

【図2A - 2E】本発明の別の実施形態による、ピン・インタフェースを有する電気相互接続エレメントを組み立てるための方法の手順を説明するための図である。

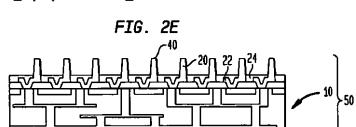

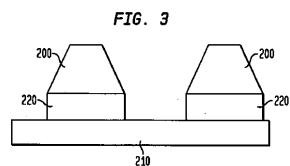

**【図3】マイクロエレクトロニクス・ピンの略側面図である。**

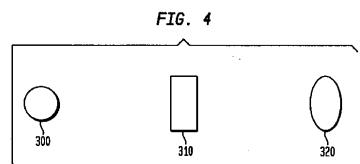

**【図4】マイクロエレクトロニクス・ピンの略上面図である。**

30

**【図5A - 5B】マイクロエレクトロニクス・ピンの略側面図である。**

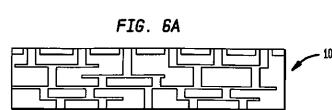

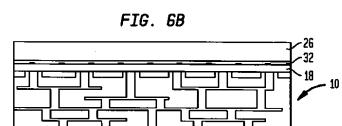

【図6A - 6E】本発明の更に別の実施形態による、ピン・インタフェースを有する電気相互接続エレメントを組み立てるための方法の手順を説明するための図である。

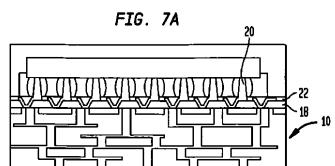

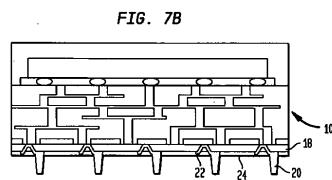

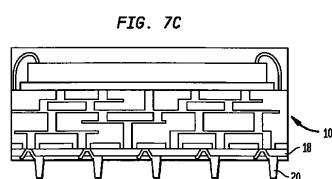

【図7A - 7C】本発明の実施の一形態によるアセンブリを他のエレクトロニクス構造体に接合した状態を示す図である。

**【発明を実施するための形態】**

**【0009】**

既存の多層相互接続エレメント上にコプレナー・ピン（coplanar pins）を形成する方法をここに開示する。図1に多層相互接続エレメント10を示す。多層相互接続エレメント10は、誘電体部分12と導電体部分14を有する。導電体部分は、配線、接合パッド、あるいは他の類似物の形態をとることがある。

40

**【0010】**

多層相互接続エレメント10は、例えばポリイミド、セラミック、FR4、BT樹脂などの誘電体を用いて单一の金属基板または多層基板から形成されることがある。多層相互接続エレメント10は、多重配線層（multiple wiring layers）などを含む相互接続エレメントでありうる。多層相互接続エレメントの製造方法を開示している米国特許第6,528,784号明細書も参照されたい。なお、同米国特許の内容は、引用することにより本明細書の一部をなすものとする。

**【0011】**

本発明の実施の一形態において、金属層16は、図1Bに示すように、多層相互接続工

50

レメント 10 上に接着剤 18 を用いてラミネート加工される。金属層 16 は、当該分野において既知の任意の適切な金属でありうる。例えば、前記金属は、銅などの任意の導電性金属でありうる。そして、金属層 16 は、図 1 C に示すように、マイクロエレクトロニクス・コンタクトまたはピンを形成するために使用することができる。

#### 【 0 0 1 2 】

マイクロエレクトロニクス・ピン 20 は、当該分野において既知の方法に従って形成することができる。例えば、マイクロエレクトロニクス・ピン 20 は、金属層 16 上のレジスト層をフォトリソグラフィーでパタン形成し、レジストパタンをエッティングによって金属層 16 に転写することによって形成することができる。

#### 【 0 0 1 3 】

接着剤層 18 がエッティング停止層として機能する場合、マイクロエレクトロニクス・ピン 20 が形成された後、マイクロエレクトロニクス・ピン 20 と多層相互接続エレメント 10 の導電体部分 14 との間に電気接続路を確立することを可能にするために、図 1 D に示すように、接着剤層 18 からいくつかの部分が取り除かれることがある。接着剤層 18 は、当該分野において既知のフォトリソグラフィー技術などを使って、選択的に除去することができる。

10

#### 【 0 0 1 4 】

次に、図 1 E に示すように、接着剤 18 から取り除かれた部分に隣接して電気接続路 (electrical connections) 22 が形成される。例えば、物理的気相成長法としても知られるスパッタリング、または化学めっきの後に、電気接続路の場所を画定するためにフォトリソグラフィーパタン形成またはレーザ穴開けが実行されることがある。電気接続路 22 が形成された後、それらは所望の厚みまで厚みを増すために電気メッキされることがある。この結果、多層相互接続エレメント 10 とマイクロエレクトロニクス・ピン 20 との間に電気接続路 22 が形成される。最後に、アセンブリ 50 が破損しないように、電気接続路 22 とマイクロエレクトロニクス・ピン 20 の下部とをカバーする保護誘電体層または保護誘電膜 24 (図 1 E ) が、多層相互接続エレメント 10 上に積層されることがある。この保護層 (あるいは保護膜) 24 は、マイクロエレクトロニクス・ピン 20 の最上面の共平面性を維持することにも関与することができる。なぜならば、保護誘電体層 24 はピン 20 を動かないように固定することに役立つので、保護誘電体層 24 はアセンブリ 50 が取り扱われる際のたわみを低減するからである。保護層 (あるいは保護膜) の材料としては、例えば半田マスクなどがある。

20

#### 【 0 0 1 5 】

本発明の別の実施形態による多層相互接続エレメント 10 を図 2 A に示す。まず図 2 B に示すように、接着剤 18 を用いて層状金属構造体 26 が多層相互接続エレメント 10 に接合される。層状金属構造体 26 は、第 1 の金属層 28 、エッティング停止層 30 および第 2 の金属層 32 を含みうる。第 1 の金属層 28 は、好ましくは、第 2 の金属層 32 よりも大きな層厚を有する。トライメタル構造が図示されているが、層状金属構造体 26 は任意数の層を含みうる。

30

#### 【 0 0 1 6 】

マイクロエレクトロニクス・ピン 20 は、図 2 C に示すように、フォトリソグラフィーパタン形成技術などを用いて、第 1 の金属層 28 から形成することができる。しかしながら、エッティング停止層はそのままの状態で残る。

40

#### 【 0 0 1 7 】

次に、図 3 以降の図面を参照しながら、マイクロエレクトロニクス・ピン 20 を形成する方法について説明する。図 3 に示すように、連続した金属配線層 210 の表面から上に突き出すように、複数の導電性ピン 200 が形成される。ピン 200 は、様々な異なるプロセスによって形成することができる。例示的なプロセスについては、米国特許第 6,884,709 号明細書のほかに、2007 年 1 月 11 日に出願された “Chip Capacitor Embedded PWB” と題された米国仮特許出願第 60/875,730 号も参照されたい。なお、同米国特許および同米国仮特許出願の内容は、引用することにより本明細書の一部を

50

なすものとする。

**【0018】**

1つの斯かるプロセスにおいて、多層金属構造体の露出した金属層は、ピン200を形成するために、フォトリソグラフィーでパタン形成されたフォトレジスト層に従ってエッチングされる。このエッチングプロセスは、多層金属構造体の内部金属層220上で停止する。内部金属層220は、露出した金属層の金属とは異なる1種類以上の金属を含み、内部金属層220は、露出した金属層をエッチングするために使用されるエッチング液によって攻撃されないような組成を有する。例えば、ピン200を形成するためにエッチングされる金属層は基本的に銅から構成されることが可能であり、連続した金属層210も基本的に銅から構成されることが可能である。そして、内部金属層220は、基本的にニッケルから構成されることが可能である。ニッケルは銅と比べて好適な選択性を有し、金属層がピン200を形成するためにエッチングされるときにニッケルが攻撃されることを避けることができる。10

**【0019】**

そして、ピン200を形成した後、露出した内部金属層220を下地の金属層210に対して選択的なプロセスによって取り除くために、異なるエッチング液が適用される。代わりに、ピン200を形成することができる別の方法は電気メッキによるものである。この方法では、ピンは、フォトレジスト層などの誘電体層内にパタン形成された開口部を通して金属をベース金属層210上にメッキすることによって形成される。20

**【0020】**

図4の上面図に示すように、ピンは、様々な異なる形状とサイズを有することができる。例えば、真上から見ると、ピンは、円形300、正方形または直方形310、または橢円形320をした形状を持つことがある。ピンが星形をしている場合、他の形状を使用する場合よりも、ピンを押し込むことがより容易に、あるいはより難しくなる可能性がある。ピン200の下地の金属層の平面からの高さは一般的に約15ミクロン(μm)と約250ミクロン(μm)の間の範囲にあり、ピンの先端部の幅は約30ミクロン(μm)以上の範囲にある。

**【0021】**

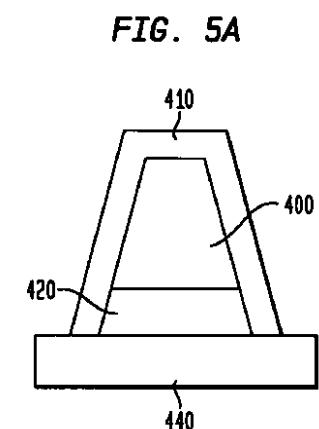

図5Aと図5Bに、ピンが採ることができる例示的な代替構造を示す。例えば、図5Aに示すように、ピン400は、ベース金属層440上に積層するエッチング停止層420に対して選択的な第1の金属層をエッチングすることによって形成され、ピン400は第2の金属層410で被覆(コーティング)される。第2の金属層は、第1の金属層と同じ金属、1種類以上の他の金属、あるいは第1の金属層に含まれる金属と別の金属との組み合わせを含みうる。ある特定の実施形態では、第2の金属層410は、腐食に強く、第2の金属層と該第2金属層と接触する別の部位(feature)の金属層との間の拡散結合の形成を促進することもできる、金などの金属を含む。別の特定の実施形態では、第2の金属層は、スズといった融点が低い金属あるいは半田といった融点が低い合金あるいは共晶混合物を含む。第2の金属層として利用可能な1種類以上の金属の追加的な例としては、ニッケル、アルミニウム、またはニッケル／金を含む。30

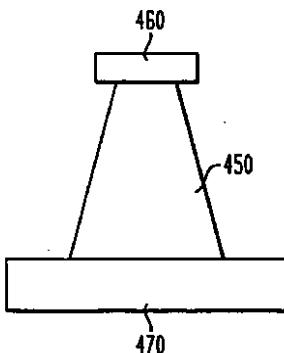

**【0022】**

図5Bに示すように、導電性ピン450の先端部のみが第2の金属層460で被覆されることがある。また、導電性ピンの本体は、エッチング停止層を介在せることなく、接着剤層470に直接接触することがある。40

**【0023】**

次に、図2Dに示すように、エッチング停止層30、第2の金属層32および接着剤層18のいくつかの部分が取り除かれることがある。エッチング停止層30、第2の金属層32および接着剤18は、必要に応じて、同時または順次に取り除くことができる。これらの層の除去のおかげで、マイクロエレクトロニクス・ピン20は、ここで述べたように、多層相互接続エレメント10の導電体部分14と電気的に接続することができる。最後に、完成した構造体の最上部に、(図1Eに関連して)既に述べたような誘電体保護層250

4が積層されることがある。

**【0024】**

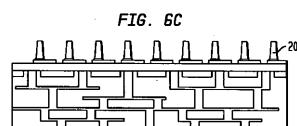

本発明の更に別の実施形態では、図6A～図6Eに示すように、層状金属構造体26が多層相互接続エレメント10に接着剤18を用いて接合されることがある。しかしながら、この工程の前に、第2の金属層32はいくつかの部分が取り除かれる。そうすることでき、層状金属構造体26が接着剤18を用いて多層相互接続エレメント10に貼り合わされるときに、一部の接着剤が、図6Bおよび図6Cに示す様に、第2の金属層32の取り除かれた部分に上に向かって入り込むことができるようになる。このように、第2の金属層32は、層状金属構造体26を多層相互接続エレメント10に貼り合わせる前に、既にパターン形成されていることがある。

10

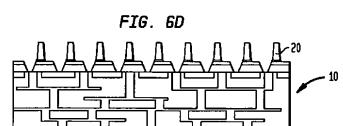

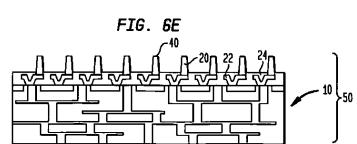

**【0025】**

その後、マイクロエレクトロニクス・ピン20が、既に述べた方法で形成される。次に、エッティング停止層30と接着剤層18のいくつかの部分が、図6Dに示すように取り除かれる。そして、マイクロエレクトロニクス・ピン22を多層相互接続エレメント10の導電体部分14と電気的に接続する電気接続路22が形成される。最後に、アセンブリ50を形成するために保護層24が積層されることがある。

**【0026】**

ここで説明した方法および構造は、LGA (land grid array) またはBGA (ball grid array) を有するチップの、図7Aに示したものとの様な露出したピン・インタフェースへのフリップチップ実装に有利である。チップは、図7Bに示すように、マイクロエレクトロニクス・ピン20の反対側でアセンブリ50に実装されることもある。さらに、本方法および構造は、図7Cに示す様に、フリップチップまたはワイヤボンド・マイクロコントラクトにも有利である。仕上がったアセンブリは回路パネルである場合がある、あるいはチップに接合した回路パネルである場合がある。さらに、仕上がったセンブリは別の回路パネルまたはチップへの相互接続に向いていると考えられる。

20

**【0027】**

本発明を特定の実施形態に関して説明してきたが、これらの実施形態は、本発明の原理と用途を単に例示するものであることが理解されるべきである。従って、本願の特許請求の範囲の請求項によって画定される本発明の精神および範囲から逸脱することなく、例示した実施形態に多数の変更を施すことができること、更に、他の構成を考案することができることが理解されるべきである。

30

**【符号の説明】**

**【0028】**

- 10 多層相互接続エレメント

- 12 誘電体部分

- 14 導電体部分

- 16 金属層

- 18 接着剤層

- 20 マイクロエレクトロニクス・ピン

- 22 電気接続路（金属トレース）

- 24 誘電体保護層

- 26 層状金属構造体

- 26 層状金属構造体

- 28 第1の金属層

- 30 エッティング停止層

- 32 第2の金属層

- 40 ピンの最上面

- 50 アセンブリ

- 200 導電性ピン

- 210 連続した金属配線層

40

50

220 内部金属層

300 円形ピン

310 直方形ピン

320 楕円形ピン

400 ピン(第1の金属層)

410 第2の金属層

420 エッチング停止層

440 ベース金属層

450 導電性ピン

460 第2の金属層

470 接着剤層

10

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図3】

【図4】

【図5A】

【図6C】

【図6D】

【図6E】

【図7A】

【図5B】

**FIG. 5B**

【図6A】

【図6B】

【図7B】

【図7C】

---

フロントページの続き

(74)代理人 100125380

弁理士 中村 綾子

(74)代理人 100125036

弁理士 深川 英里

(74)代理人 100142996

弁理士 森本 聰二

(74)代理人 100154298

弁理士 角田 恭子

(74)代理人 100156443

弁理士 松崎 隆

(74)代理人 100162330

弁理士 広瀬 幹規

(72)発明者 ハーバ , ベルガセム

アメリカ合衆国カリフォルニア州 95134 , サン・ノゼ , オーチャード・パークウェイ 302

5 , テッセラ , インコーポレイテッド気付

審査官 中田 誠二郎

(56)参考文献 特開2004-327945 (JP, A)

国際公開第2006/064111 (WO, A1)

特開平11-067823 (JP, A)

特開平11-298144 (JP, A)

特開2002-043506 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

H 05 K 3 / 46

H 05 K 3 / 34