(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4039930号

(P4039930)

(45) 発行日 平成20年1月30日(2008.1.30)

(24) 登録日 平成19年11月16日(2007.11.16)

(51) Int.Cl.

F 1

|             |               |                  |      |      |         |

|-------------|---------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/30</b>   | <b>(2006.01)</b> | G09G | 3/30 | J       |

| <b>G09G</b> | <b>3/20</b>   | <b>(2006.01)</b> | G09G | 3/20 | 6 1 1 H |

| <b>H01L</b> | <b>29/786</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 2 1 F |

| <b>H01L</b> | <b>51/50</b>  | <b>(2006.01)</b> | G09G | 3/20 | 6 2 4 B |

|             |               |                  | G09G | 3/20 | 6 4 2 A |

請求項の数 10 (全 54 頁) 最終頁に続く

(21) 出願番号

特願2002-301388 (P2002-301388)

(22) 出願日

平成14年10月16日 (2002.10.16)

(62) 分割の表示

特願2002-274680 (P2002-274680)

の分割

原出願日 平成14年9月20日 (2002.9.20)

(65) 公開番号

特開2004-54203 (P2004-54203A)

(43) 公開日

平成16年2月19日 (2004.2.19)

審査請求日 平成17年9月14日 (2005.9.14)

(31) 優先権主張番号

特願2001-290287 (P2001-290287)

(32) 優先日

平成13年9月21日 (2001.9.21)

(33) 優先権主張国

日本国 (JP)

(31) 優先権主張番号

特願2001-304643 (P2001-304643)

(32) 優先日

平成13年9月28日 (2001.9.28)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100110858

弁理士 柳瀬 瞳

(72) 発明者 木村 瞳

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 西島 篤宏

(58) 調査した分野 (Int.Cl., DB名)

G09G 3/00- 3/38

H01L 51/50

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の信号がゲートに入力される第1のトランジスタと、

第2の信号がゲートに入力される第2のトランジスタと、

第1の端子が負荷に電気的に接続された第3のトランジスタと、

ゲートが前記第3のトランジスタのゲートに電気的に接続され、第2の端子が第1の配線に電気的に接続され、第1の端子が前記第3のトランジスタの第2の端子に電気的に接続された第4のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートに電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、第2の配線、又は前記第4のトランジスタの第1の端子に電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第2の配線に電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記第4のトランジスタの第1の端子、又は前記第4のトランジスタのゲートに電気的に接続され、

前記第3のトランジスタの第1の端子および前記第4のトランジスタの第1の端子はソースである、または前記第3のトランジスタの第2の端子および前記第4のトランジスタの第2の端子はソースであることを特徴とする半導体装置。

## 【請求項 2】

10

20

請求項 1において、

前記第1の信号と前記第2の信号とは、同一配線から入力されることを特徴とする半導体装置。

**【請求項 3】**

請求項 1において、

前記第1の信号と前記第2の信号とは、異なる配線から入力されることを特徴とする半導体装置。

**【請求項 4】**

請求項 1又は請求項 2において、

前記第1のトランジスタのゲートは、第3の配線に電気的に接続されることを特徴とする半導体装置。 10

**【請求項 5】**

請求項 1又は請求項 2において、

前記第2のトランジスタのゲートは、第3の配線に電気的に接続されることを特徴とする半導体装置。

**【請求項 6】**

請求項 1又は請求項 2において、

前記第1のトランジスタのゲートは、第3の配線に電気的に接続され、且つ前記第2のトランジスタのゲートは、前記第3の配線に電気的に接続されることを特徴とする半導体装置。 20

**【請求項 7】**

請求項 1又は請求項 3において、

前記第1のトランジスタのゲートは、第3の配線に電気的に接続され、

前記第2のトランジスタのゲートは、第4の配線に電気的に接続されることを特徴とする半導体装置。

**【請求項 8】**

第1のトランジスタと、

第2のトランジスタと、

第1の端子が負荷に電気的に接続された第3のトランジスタと、

ゲートが前記第3のトランジスタのゲートに電気的に接続され、第2の端子が第1の配線に電気的に接続され、第1の端子が前記第3のトランジスタの第2の端子に電気的に接続された第4のトランジスタと、を有し、 30

前記第1のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートに電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、第2の配線、又は前記第4のトランジスタの第1の端子に電気的に接続され、

前記第1のトランジスタのゲートは、第3の配線に電気的に接続され、

前記第2のトランジスタのゲートは、前記第3の配線に電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第2の配線に電気的に接続され、 40

前記第2のトランジスタのソース又はドレインの他方は、前記第4のトランジスタの第1の端子、又は前記第4のトランジスタのゲートに電気的に接続され、

前記第3のトランジスタの第1の端子および前記第4のトランジスタの第1の端子はソースである、または前記第3のトランジスタの第2の端子および前記第4のトランジスタの第2の端子はソースであることを特徴とする半導体装置。

**【請求項 9】**

第1のトランジスタと、

第2のトランジスタと、

第1の端子が負荷に電気的に接続された第3のトランジスタと、

ゲートが前記第3のトランジスタのゲートに電気的に接続され、第2の端子が第1の配 50

線に電気的に接続され、第1の端子が前記第3のトランジスタの第2の端子に電気的に接続された第4のトランジスタと、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのゲートに電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、第2の配線、又は前記第4のトランジスタの第1の端子に電気的に接続され、

前記第1のトランジスタのゲートは、第3の配線に電気的に接続され、

前記第2のトランジスタのゲートは、第4の配線に電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第2の配線に電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記第4のトランジスタの第1の端子、又は前記第4のトランジスタのゲートに電気的に接続され、

前記第3のトランジスタの第1の端子および前記第4のトランジスタの第1の端子はソースである、または前記第3のトランジスタの第2の端子および前記第4のトランジスタの第2の端子はソースであることを特徴とする半導体装置。

#### 【請求項10】

請求項1乃至請求項9のいずれか一において、

前記負荷は、エレクトロルミネッセンス素子を有することを特徴とする半導体装置。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、半導体装置の構成に関する。本発明は特に、ガラス、プラスチック等の絶縁体上に作製される薄膜トランジスタ(以後、TFTと表記する)を有するアクティブマトリクス型半導体装置の構成に関する。また、このような半導体装置を表示部に用いた電子機器に関する。

##### 【0002】

##### 【従来の技術】

近年、エレクトロルミネッセンス(Electro Luminescence: EL)表示装置やFED(Field Emission Display)等、自発光型の表示装置の開発が活発化している。自発光型の表示装置の利点として、視認性が高く、液晶表示装置(LCD)等において必要なバックライトを必要としないために薄型化に適しているとともに、視野角にほとんど制限が無い等の点が挙げられる。

##### 【0003】

ここで、EL素子とは、電場を加えることで発生するルミネッセンスが得られる発光層を有する素子を指す。この発光層においては、一重項励起状態から基底状態に戻る際の発光(蛍光)と、三重項励起状態から基底状態に戻る際の発光(燐光)とがあるが、本発明の半導体装置は、上述したいずれの発光形態であっても良い。

##### 【0004】

EL素子は、一対の電極(陽極と陰極)間に発光層が挟まれる形で構成され、通常、積層構造をとっている。代表的には、イーストマン・コダック・カンパニーのTangらが提案した「陽極／正孔輸送層／発光層／電子輸送層／陰極」という積層構造が挙げられる。この構造は非常に発光効率が高く、現在研究が進められているEL素子の多くはこの構造が採用されている。

##### 【0005】

また、これ以外にも、陽極と陰極との間に、「正孔注入層／正孔輸送層／発光層／電子輸送層」または「正孔注入層／正孔輸送層／発光層／電子輸送層／電子注入層」の順に積層する構造がある。本発明の半導体装置に用いるEL素子の構造としては、上述の構造のいずれを採用していても良い。また、発光層に対して蛍光性色素等をドーピングしても良い。

##### 【0006】

10

20

30

40

50

本明細書においては、EL素子において、陽極と陰極との間に設けられる全ての層を総称してEL層と呼ぶ。よって、上述の正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層は、全てEL層に含まれ、陽極、EL層、および陰極で構成される発光素子をEL素子と呼ぶ。

#### 【0007】

##### 【発明が解決しようとする課題】

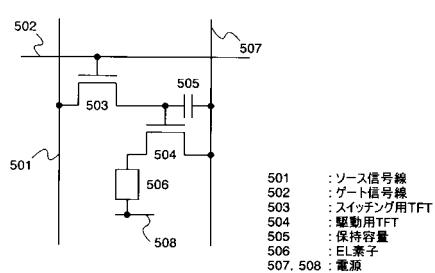

図5に、一般的な半導体装置における画素の構成を示す。なお、代表的な半導体装置として、EL表示装置を例とする。図5に示した画素は、ソース信号線501、ゲート信号線502、スイッチング用TFT503、駆動用TFT504、保持容量505、EL素子506、電源507、508を有している。

10

#### 【0008】

各部の接続関係について説明する。ここで、TFTはゲート、ソース、ドレインの3端子を有するが、ソース、ドレインに関しては、TFTの構造上、明確に区別が出来ない。よって、素子間の接続について説明する際は、ソース、ドレインのうち一方を第1の電極、他方を第2の電極と表記する。TFTのON、OFFについて、各端子の電位等について説明する際には、ソース、ドレイン等と表記する。

#### 【0009】

スイッチング用TFT503のゲート電極は、ゲート信号線502に接続され、第1の電極はソース信号線501に接続され、第2の電極は駆動用TFT504のゲート電極に接続されている。駆動用TFT504の第1の電極は、電源507に接続され、第2の電極はEL素子506の一方の電極に接続されている。EL素子506の他方の電極は、電源508に接続されている。保持容量505は、駆動用TFT504のゲート電極と第1の電極との間に接続され、駆動用TFT504のゲート・ソース間電圧を保持する。

20

#### 【0010】

ゲート信号線502の電位が変化してスイッチング用TFT503がONすると、ソース信号線501に入力されている映像信号は、駆動用TFT504のゲート電極へと入力される。入力された映像信号の電位に従って、駆動用TFT504のゲート・ソース間電圧が決定し、駆動用TFT504のソース・ドレイン間を流れる電流(以下、ドレイン電流と表記)が決定する。この電流はEL素子506に供給されて発光する。

#### 【0011】

30

ところで、多結晶シリコン(ポリシリコン 以下P-Si)で形成されたTFTは、非晶質シリコン(アモルファスシリコン 以下A-Si)で形成されたTFTよりも電界効果移動度が高く、ON電流が大きいため、半導体装置に用いるトランジスタとしてより適している。

#### 【0012】

反面、ポリシリコンで形成されたTFTは、結晶粒界における欠陥に起因して、その電気的特性にばらつきが生じやすいといった問題点を有している。

#### 【0013】

図5に示した画素において、画素を構成するTFTのしきい値やON電流等の特性が画素ごとにばらつくと、同じ映像信号を入力した場合にも、それに応じてTFTのドレイン電流の大きさが異なってくるため、EL素子506の輝度がばらつく。

40

#### 【0014】

このような問題を解決するには、TFTの特性によらず、所望の電流をEL素子に供給するようにすれば良い。このような点から、TFTの特性に左右されずにEL素子に流れる電流の大きさを制御することが出来る、様々な種類の電流書き込み型の画素が提案されてきている。

#### 【0015】

電流書き込み型とは、ソース信号線より画素に入力される映像信号が、通常はアナログもしくはデジタルの電圧情報で入力されるのに対し、電流で入力される方式を言う。この方式によると、EL素子に供給したい電流値を外部で信号電流として設定し、画素において

50

はそれに等しい電流が流れるため、TFTの特性ばらつきの影響を受けないという利点がある。

#### 【0016】

以下に、代表的な電流書き込み型の画素を数例示し、それらの構成と動作および特徴について説明する。

#### 【0017】

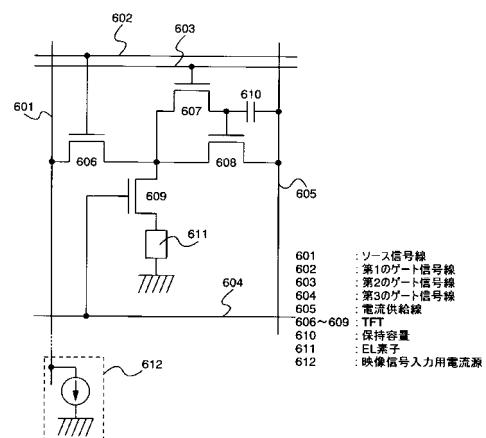

図6に第1の構成例を示す。図6の画素は、ソース信号線601、第1～第3のゲート信号線602～604、電流供給線605、TFT606～609、保持容量610、EL素子611、信号電流入力用電流源612を有する。

#### 【0018】

TFT606のゲート電極は、第1のゲート信号線602に接続され、第1の電極はソース信号線601に接続され、第2の電極は、TFT607の第1の電極、TFT608の第1の電極、およびTFT609の第1の電極に接続されている。TFT607のゲート電極は、第2のゲート信号線603に接続され、第2の電極はTFT608のゲート電極に接続されている。TFT608の第2の電極は、電流供給線605に接続されている。TFT609のゲート電極は、第3のゲート信号線604に接続され、第2の電極はEL素子611の陽極に接続されている。保持容量610はTFT608のゲート電極と入力電極との間に接続され、TFT608のゲート・ソース間電圧を保持する。電流供給線605およびEL素子611の陰極には、それぞれ所定の電位が入力され、互いに電位差を有する。

10

#### 【0019】

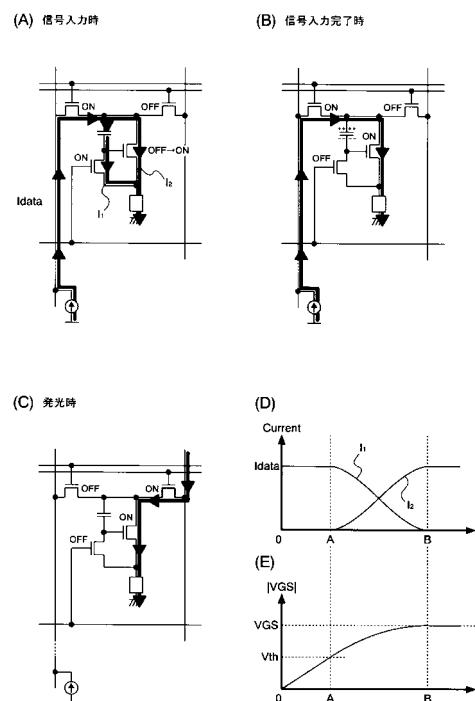

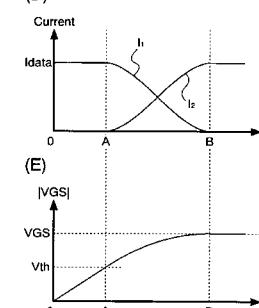

図7を用いて、信号電流の書き込みから発光までの動作について説明する。図中、各部を示す図番は、図6に準ずる。図7(A)～(C)は、電流の流れを模式的に示している。図7(D)は、信号電流の書き込み時ににおける各経路を流れる電流の関係を示しており、図7(E)は、同じく信号電流の書き込み時に、保持容量610に蓄積される電圧、つまりTFT608のゲート・ソース間電圧について示している。

20

#### 【0020】

まず、第1のゲート信号線602および第2のゲート信号線603にパルスが入力され、TFT606、607がONする。このとき、ソース信号線を流れる電流、すなわち信号電流を $I_{data}$ とする。

30

#### 【0021】

ソース信号線には、電流 $I_{data}$ が流れているので、図7(A)に示すように、画素内では、電流の経路は $I_1$ と $I_2$ とに分かれて流れる。これらの関係を図7(D)に示している。なお、 $I_{data} = I_1 + I_2$ であることは言うまでもない。

#### 【0022】

TFT606がONした瞬間には、まだ保持容量610には電荷が保持されていないため、TFT608はOFFしている。よって、 $I_2 = 0$ となり、 $I_{data} = I_1$ となる。すなわちこの間は、保持容量610における電荷の蓄積による電流のみが流れている。

#### 【0023】

その後、徐々に保持容量610に電荷が蓄積され、両電極間に電位差が生じ始める(図7(E))。両電極の電位差がVthとなると(図7(E) A点)、TFT608がONして、 $I_2$ が生ずる。先に述べたように、 $I_{data} = I_1 + I_2$ であるので、 $I_1$ は次第に減少するが、依然電流は流れしており、さらに保持容量には電荷の蓄積が行われる。

40

#### 【0024】

保持容量610においては、その両電極の電位差、つまりTFT608のゲート・ソース間電圧が所望の電圧、つまりTFT608が $I_{data}$ の電流を流すことが出来るだけの電圧(VGS)になるまで電荷の蓄積が続く。やがて電荷の蓄積が終了する(図7(E) B点)と、電流 $I_2$ は流れなくなり、さらにTFT608はそのときのVGSに見合った電流が流れ、 $I_{data} = I_2$ となる(図7(B))。以上で信号の書き込み動作が完了する。最後に第1のゲート信号線602および第2のゲート信号線603の選択が終了し、TFT606、

50

607がOFFする。

**【0025】**

続いて、発光動作に移る。第3のゲート信号線604にパルスが入力され、TFT609がONする。保持容量610には、先ほど書き込んだVGSが保持されているため、TFT608はONしており、電流供給線605から、 $I_{data}$ の電流が流れる。これによりEL素子611が発光する。このとき、TFT608が飽和領域において動作するようにしておけば、TFT608のソース・ドレイン間電圧が変化したとしても、 $I_{data}$ は変わらなく流れることが出来る。

**【0026】**

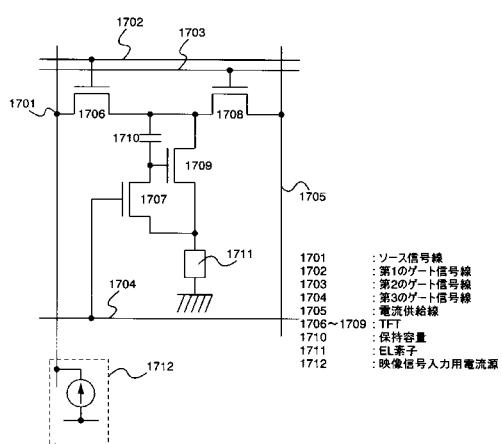

図17に第2の構成例を示す。図17の画素は、ソース信号線1701、第1～第3のゲート信号線1702～1704、電流供給線1705、TFT1706～1709、保持容量1710、EL素子1711、信号電流入力用電流源1712を有する。

10

**【0027】**

TFT1706のゲート電極は、第1のゲート信号線1702に接続され、第1の電極はソース信号線1701に接続され、第2の電極はTFT1708の第1の電極と、TFT1709の第1の電極とに接続されている。TFT1708のゲート電極は、第2のゲート信号線1703に接続され、第2の電極は電流供給線1705に接続されている。TFT1707のゲート電極は、第3のゲート信号線1704に接続され、第1の電極は、TFT1709のゲート電極に接続され、第2の電極はTFT1709の第2の電極と、EL素子1711の一方の電極とに接続されている。保持容量1710は、TFT1709のゲート電極と第1の電極との間に接続され、TFT1709のゲート・ソース間電圧を保持する。電流供給線1705およびEL素子1711の他方の電極には、それぞれ所定の電位が入力され、互いに電位差を有する。

20

**【0028】**

図18を用いて、信号電流の書き込みから発光までの動作について説明する。図中、各部を示す図番は、図17に準ずる。図18(A)～(C)は、電流の流れを模式的に表している。図18(D)は、信号電流の書き込み時ににおける各経路を流れる電流の関係を示しており、図18(E)は、同じく信号電流の書き込み時に、保持容量1710に蓄積される電圧、つまりTFT1709のゲート・ソース間電圧について示している。

30

**【0029】**

まず、第1のゲート信号線1702および第3のゲート信号線1704にパルスが入力され、TFT1706、1707がONする。このとき、ソース信号線1701を流れる電流、すなわち信号電流を $I_{data}$ とする。

**【0030】**

ソース信号線1701を流れる電流 $I_{data}$ は、図18(A)に示すように、画素内では、電流の経路は $I_1$ と $I_2$ とに分かれて流れる。これらの関係を図18(D)に示している。なお、 $I_{data} = I_1 + I_2$ であることは言うまでもない。

**【0031】**

TFT1706がONした瞬間には、まだ保持容量1710には電荷が保持されていないため、TFT1709はOFFしている。よって、 $I_2 = 0$ となり、 $I_{data} = I_1$ となる。すなわちこの間は、保持容量1710における電荷の蓄積による電流のみが流れている。

40

**【0032】**

その後、徐々に保持容量1710に電荷が蓄積され、両電極間に電位差が生じ始める(図18(E))。両電極の電位差がVthとなると(図18(E) A点)、TFT1709がONして、 $I_2$ が生ずる。先に述べたように、 $I_{data} = I_1 + I_2$ であるので、 $I_1$ は次第に減少するが、依然電流は流れしており、さらに保持容量には電荷の蓄積が行われる。

**【0033】**

保持容量1710においては、その両電極の電位差、つまりTFT1709のゲート・ソース間電圧が所望の電圧、つまりTFT1709が $I_{data}$ の電流を流すことが出来るだけの電圧(VGS)になるまで電荷の蓄積が続く。やがて電荷の蓄積が終了する(図18(E))

50

B点)と、電流 $I_1$ は流れなくなり、さらにTFT1709はそのときのVGSに見合った電流が流れ、 $I_{data} = I_2$ となる(図18(B))。以上で信号の書き込み動作が完了する。最後に第1のゲート信号線1702および第3のゲート信号線1704の選択が終了し、TFT1706、1707がOFFする。

#### 【0034】

続いて、第2のゲート信号線1703にパルスが入力され、TFT1708がONする。今、保持容量1710には、先ほど書き込んだVGSが保持されているため、TFT1709はONしており、電流供給線1705から、 $I_{data}$ の電流が流れる。これによりEL素子1711が発光する。このとき、TFT1709が飽和領域において動作するようにしておけば、TFT1709のソース・ドレイン間電圧が多少変化したとしても、 $I_{data}$ は変わりなく流れることが出来る。

#### 【0035】

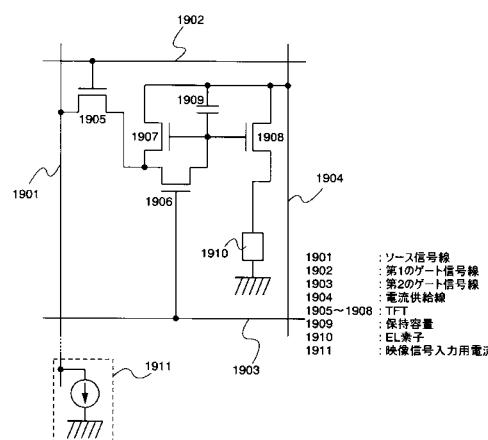

図19に第3の構成例を示す。図19の画素は、ソース信号線1901、第1および第2のゲート信号線1902、1903、電流供給線1704、TFT1905～1908、保持容量1909、EL素子1910、信号電流入力用電流源1911を有する。

#### 【0036】

TFT1905のゲート電極は、第1のゲート信号線1902に接続され、第1の電極はソース信号線1901に接続され、第2の電極はTFT1906の第1の電極と、TFT1907の第1の電極とに接続されている。TFT1906のゲート電極は、第2のゲート信号線1903に接続され、第2の電極はTFT1907のゲート電極と、TFT1908のゲート電極とに接続されている。TFT1907の第2の電極と1908の第1の電極とはともに電流供給線1904に接続され、TFT1908の第2の電極はEL素子1910の陽極に接続されている。保持容量1909は、TFT1907、1908のゲート電極と、TFT1907の第2の電極およびTFT1908の第1の電極との間に接続され、TFT1907、1908のゲート・ソース間電圧を保持する。電流供給線1904およびEL素子1910の陰極には、それぞれ所定の電位が入力され、互いに電位差を有する。

#### 【0037】

図20を用いて、信号電流の書き込みから発光までの動作について説明する。図中、各部を示す図番は、図19に準ずる。図20(A)～(C)は、電流の流れを模式的に表している。図20(D)は、信号電流の書き込み時ににおける各経路を流れる電流の関係を示しており、図20(E)は、同じく信号電流の書き込み時に、保持容量1909に蓄積される電圧、つまりTFT1907、1908のゲート・ソース間電圧について示している。

#### 【0038】

まず、第1のゲート信号線1902および第2のゲート信号線1903にパルスが入力され、TFT1905、1906がONする。このとき、ソース信号線1901を流れる電流、すなわち信号電流を $I_{data}$ とする。

#### 【0039】

ソース信号線1901を流れる電流 $I_{data}$ は、図20(A)に示すように、画素内では、電流の経路は $I_1$ と $I_2$ とに分かれて流れ。これらの関係を図20(D)に示している。なお、 $I_{data} = I_1 + I_2$ であることは言うまでもない。

#### 【0040】

TFT1905がONした瞬間には、まだ保持容量1909には電荷が保持されていないため、TFT1907、1908はOFFしている。よって、 $I_2 = 0$ となり、 $I_{data} = I_1$ となる。すなわちこの間は、保持容量1909における電荷の蓄積による電流のみが流れている。

#### 【0041】

その後、徐々に保持容量1909に電荷が蓄積され、両電極間に電位差が生じ始める(図20(E))。両電極の電位差が $V_{th}$ となると(図20(E) A点)、TFT1907がONして、 $I_2$ が生ずる。先に述べたように、 $I_{data} = I_1 + I_2$ があるので、 $I_1$ は次第

10

20

30

40

50

に減少するが、依然電流は流れしており、さらに保持容量には電荷の蓄積が行われる。

#### 【0042】

ここで、TFT1907がONする一方、TFT1908もONし、電流が流れ始める。ただし、この電流は、図20(A)に示すように独立したバスで流れるため、 $I_{data}$ の値は変わらず、 $I_1$ 、 $I_2$ にも影響しない。

#### 【0043】

保持容量1909においては、その両電極の電位差、つまりTFT1907、1908のゲート・ソース間電圧が所望の電圧、つまりTFT1907が $I_{data}$ の電流を流すことが出来るだけの電圧(VGS)になるまで電荷の蓄積が続く。やがて電荷の蓄積が終了する(図20(E) B点)と、電流 $I_2$ は流れなくなり、さらにTFT1907はそのときのVGSに見合った電流が流れ、 $I_{data} = I_2$ となる(図20(B))。以上で信号の書き込み動作が完了する。最後に第1のゲート信号線1902および第2のゲート信号線1903の選択が終了し、TFT1905、1906がOFFする。

#### 【0044】

今、保持容量1909には、TFT1907に $I_{data}$ の電流を流すことが出来るだけの電圧をゲート・ソース間に与えるだけの電荷が保持されている。TFT1907、1908はカレントミラーを形成しているので、その電圧がTFT1908にも与えられ、TFT1908を電流が流れる。図20においては、この電流を $I_{EL}$ で表している。

#### 【0045】

TFT1907とTFT1908のゲート長およびチャネル幅が等しければ、 $I_{EL} = I_{data}$ となる。つまりカレントミラーを構成するTFT1907、1908のサイズの決定の仕方によって、信号電流 $I_{data}$ と、EL素子を流れる電流 $I_{EL}$ との関係を決定することが出来る。

#### 【0046】

以上に一例を示した、電流書き込み型のメリットとして、TFT608の特性等にばらつきがあった場合であっても、保持容量610には、電流 $I_{data}$ を流すのに必要なゲート・ソース間電圧が保持されるため、所望の電流を正確にEL素子に供給することが出来、よってTFTの特性ばらつきに起因した輝度ばらつきを抑えることが可能になる点がある。

#### 【0047】

ここで、各構成の特徴を表1に示す。

#### 【0048】

#### 【表1】

|                                             | 第1の構成(図6)                          | 第2の構成(図17)                           | 第3の構成(図19)                 |

|---------------------------------------------|------------------------------------|--------------------------------------|----------------------------|

| 映像信号電流 $I_{data}$ とEL素子を流れる電流 $I_{EL}$ との関係 | $I_{data} = I_{EL}$                | $I_{data} = I_{EL}$                  | $I_{data} \neq I_{EL}$     |

| 電流電圧変換用TFTと駆動用TFTとの関係                       | 変換用TFT:608 → 同一<br>駆動用TFT:608 → 同一 | 変換用TFT:1709 → 同一<br>駆動用TFT:1709 → 同一 | 変換用TFT:1907<br>駆動用TFT:1908 |

| 書き込み時の映像信号電流                                | EL素子に流れない                          | EL素子に流れる                             | EL素子に流れない                  |

| ゲート信号線の本数                                   | 3                                  | 3                                    | 2                          |

#### 【0049】

まず、信号電流 $I_{data}$ と、EL素子を流れる電流 $I_{EL}$ の関係について考える。アナログ階調方式の半導体装置においては、階調が電流値で表されるため、高階調のときは大きい電流が流れ、低階調のときは小さい電流が流れる。つまり、階調によって、信号電流を書き込む信号電流の大きさが異なることになる。その場合、低階調の信号を画素に書き込む場合には、高階調の信号を画素に書き込む場合よりも長い時間を要することになってしまう。また、低階調の信号は、電流が小さいため、ノイズの影響を極めて受けやすくなってしまう。

10

20

30

40

50

まう。

**【0050】**

続いて、電流 - 電圧変換用 TFT と駆動用 TFT との関係について考える。ここで、電流 - 電圧変換用 TFT とは、ソース信号線から入力される信号電流を、電圧信号に変換するのに用いている TFT であり、駆動用 TFT とは、保持容量に保持された電圧に従って電流を流すための TFT である。表 1 には、各構成における電流 - 電圧変換用 TFT (変換用 TFT と表記) と、駆動用 TFT の図番を示している。

**【0051】**

変換用 TFT と、駆動用 TFT とが共通であるとはすなわち、書き込み動作と発光動作を共通の TFT が担当するということである。よって、TFT のばらつきの影響が少ない。一方、第 3 の構成のように、変換用 TFT と駆動用 TFT とが別である場合、画素内の特性ばらつきの影響を受けることになってしまう。

10

**【0052】**

続いて、信号電流の書き込み時の経路について考える。第 1 の構成および第 3 の構成においては、信号電流は、電流源から電流供給線、あるいは電流供給線から電流源へと流れる。一方、第 2 の構成によると、信号電流の書き込み時に、信号電流は電流源から、EL 素子を通って流れている。このような構成においては、低階調の信号が書き込まれた後に高階調の信号を書き込む場合、あるいはその逆の動作において、EL 素子自体が負荷となるため、書き込み時間を長くする必要が生ずる。

**【0053】**

20

また、第 1 の構成および第 2 の構成の場合、1 行あたり 3 本のゲート信号線を用いて画素の制御を行っているため、従来の半導体装置と比較して、開口率が大きく低下することになる。

**【0054】**

本発明は、信号線を増やすことなく上述の様々な問題点を解決することの出来る半導体装置を提供するものである。

**【0055】**

**【課題を解決するための手段】**

従来の電流書き込み型の問題点の 1 つに、信号の書き込みを行うために流れる電流と、発光時に EL 素子を流れる電流とが等しい点があった。つまり、この問題を解決するためには、信号の書き込みを行うために流れる電流が、常に発光時に EL 素子を流れる電流よりも大きくすることが出来れば良い。

30

**【0056】**

電流の大きさに差を付けるには、トランジスタを流れる電流の大きさに差を与えてやれば良い。そこで本発明では、トランジスタのゲート長 L に注目し、信号電流の書き込み時に電流が流れるトランジスタのゲート長 L を、発光時に EL 素子に供給する電流が流れるトランジスタのゲート長 L よりも小さくし、本来 EL 素子に流れる電流よりも大きな電流によって書き込みを行うようにする。これにより、低階調の場合に書き込み時間が長くなる点を解決し、さらに信号電流自体がノイズの影響を受けにくくすることが出来る。

**【0057】**

40

また、書き込み時と発光時で、一部共通のトランジスタを用いているため、書き込み動作と発光動作に別のトランジスタを用いる構成よりも、トランジスタの特性ばらつきが輝度に影響しにくくすることが出来る。

**【0058】**

本発明の構成を以下に記す。

**【0059】**

本発明の半導体装置は、

入力された信号電流を電圧に変換し、前記変換された電圧に応じた電流を電源より負荷に供給する第 1 の手段と、

前記変換された電圧を保持する第 2 の手段と、

50

前記第2の手段において、前記電圧の保持もしくは解放を選択する第3の手段と、

前記信号電流が入力されている期間においては、前記電源から前記負荷への電流の供給を遮断し、前記負荷を駆動する期間においては、前記変換された電圧に応じて、前記電源より前記負荷に電流を供給する第4の手段とを有することを特徴とする。

【0060】

本発明の半導体装置は、

入力された信号電流を電圧に変換し、前記変換された電圧に応じた電流を電源より負荷に供給する第1の手段と、

前記変換

された電圧を保持する第2の手段と、

10

前記第2の手段において、前記電圧の保持もしくは解放を選択する第3の手段と、

前記信号電流が入力されている期間においては、前記電源から前記負荷への電流の供給を遮断し、前記負荷を駆動する期間においては、前記変換された電圧に応じて、前記電源より前記負荷に電流を供給する第4の手段と、

前記第1の手段への、前記信号電流の入力を制御する第5の手段とを有することを特徴とする。

【0061】

本発明の半導体装置は、

入力された信号電流を電圧に変換し、前記変換された電圧に応じた電流を電源より負荷に供給する第1の手段と、

20

前記変換された電圧を保持する第2の手段と、

前記第2の手段において、前記電圧の保持もしくは解放を選択する第3の手段と、

前記信号電流が入力されている期間においては、前記電源から前記負荷への電流の供給を遮断し、前記負荷を駆動する期間においては、前記変換された電圧に応じて、前記電源より前記負荷に電流を供給する、並列接続された第4の手段と、

前記第1の手段への、前記信号電流の入力を制御する第5の手段と、

前記複数の第4の手段のうち少なくとも1つを選択して、前記電源から前記負荷への電流供給経路とする複数の第6の手段とを有することを特徴とする。

【0062】

本発明の半導体装置は、

30

入力された信号電流を電圧に変換し、前記変換された電圧に応じた電流を電源より負荷に供給する、並列接続された第1の手段と、

前記変換された電圧を保持する第2の手段と、

前記第2の手段において、前記電圧の保持もしくは解放を選択する第3の手段と、

前記信号電流が入力されている期間においては、前記電源から前記負荷への電流の供給を遮断し、前記負荷を駆動する期間においては、前記変換された電圧に応じて、前記電源より前記負荷に電流を供給する第4の手段と、

前記第1の手段への、前記信号電流の入力を制御する第5の手段と、

前記複数の第1の手段のうち少なくとも1つを選択して、前記電源から前記負荷への電流供給経路とする複数の第6の手段とを有することを特徴とする。

40

【0063】

本発明の半導体装置は、

入力された信号電流を電圧に変換し、前記変換された電圧に応じた電流を電源より負荷に供給する変換・駆動用トランジスタと、

前記変換された電圧を保持する保持容量手段と、

前記保持容量手段において、前記電圧の保持もしくは解放を選択する保持用トランジスタと、

前記信号電流が入力されている期間においては、前記電源から前記負荷への電流の供給を遮断し、前記負荷を駆動する期間においては、前記変換された電圧に応じて、前記電源より前記負荷に電流を供給する駆動用トランジスタとを有することを特徴とする。

50

**【 0 0 6 4 】**

本発明の半導体装置は、

入力された信号電流を電圧に変換し、前記変換された電圧に応じた電流を電源より負荷に供給する変換・駆動用トランジスタと、

前記変換された電圧を保持する保持容量手段と、

前記保持容量手段において、前記電圧の保持もしくは解放を選択する保持用トランジスタと、

前記信号電流が入力されている期間においては、前記電源から前記負荷への電流の供給を遮断し、前記負荷を駆動する期間においては、前記変換された電圧に応じて、前記電源より前記負荷に電流を供給する駆動用トランジスタと、

前記変換・駆動用トランジスタへの、前記信号電流の入力を制御するスイッチング用トランジスタとを有することを特徴とする。

**【 0 0 6 5 】**

本発明の半導体装置は、

入力された信号電流を電圧に変換し、前記変換された電圧に応じた電流を電源より負荷に供給する変換・駆動用トランジスタと、

前記変換された電圧を保持する保持容量手段と、

前記保持容量手段において、前記電圧の保持もしくは解放を選択する保持用トランジスタと、

前記信号電流が入力されている期間においては、前記電源から前記負荷への電流の供給を遮断し、前記負荷を駆動する期間においては、前記変換された電圧に応じて、前記電源より前記負荷に電流を供給する、並列接続された複数の駆動用トランジスタと、

前記変換・駆動用トランジスタへの、前記信号電流の入力を制御するスイッチング用トランジスタと、

前記複数の駆動用トランジスタのうち少なくとも1つを選択して、前記電源から前記負荷への電流供給経路とする複数の電流選択用トランジスタとを有することを特徴とする。

**【 0 0 6 6 】**

本発明の半導体装置は、

入力された信号電流を電圧に変換し、前記変換された電圧に応じた電流を電源より負荷に供給する、並列接続された変換・駆動用トランジスタと、

前記変換された電圧を保持する保持容量手段と、

前記保持容量手段において、前記電圧の保持もしくは解放を選択する保持用トランジスタと、

前記信号電流が入力されている期間においては、前記電源から前記負荷への電流の供給を遮断し、前記負荷を駆動する期間においては、前記変換された電圧に応じて、前記電源より前記負荷に電流を供給する駆動用トランジスタと、

前記変換・駆動用トランジスタへの、前記信号電流の入力を制御するスイッチング用トランジスタと、

前記複数の変換・駆動用トランジスタのうち少なくとも1つを選択して、前記電源から前記負荷への電流供給経路とする複数の電流選択用トランジスタとを有することを特徴とする。

**【 0 0 6 7 】**

本発明の半導体装置は、

前記電源から前記負荷への電流供給経路は、複数が並列に配置され、そのうち少なくとも1つを用いて前記負荷に電流を供給することを特徴とする。

**【 0 0 6 8 】**

本発明の半導体装置は、

前記発光素子への電流供給は、複数の前記電流供給経路を時間的に切り替え、時間的に異なる経路によってなされることを特徴とする。

**【 0 0 6 9 】**

10

20

30

40

50

本発明の半導体装置は、

前記保持容量手段は、前記変換・駆動用トランジスタの前記変換・駆動用トランジスタのゲート・ソース間電圧を保持し、

前記保持用トランジスタは、そのON、OFFによって前記変換・駆動用トランジスタのゲート電極とドレイン領域とを導通、もしくは非導通の状態とすることを特徴とする。

#### 【0070】

本発明の半導体装置は、

前記変換・駆動用トランジスタと、前記駆動用トランジスタとは同一極性であることを特徴とする。

#### 【0071】

10

本発明の半導体装置は、

前記変換・駆動用トランジスタと、前記駆動用トランジスタとは、前記電源から前記負荷への電流供給経路において直列に配置され、それぞれのゲート電極が電気的に接続されていることを特徴とする。

#### 【0072】

本発明の半導体装置は、

前記信号電流の経路は、前記第1の手段を少なくとも経由し、

前記負荷の駆動時に前記電源から前記負荷に供給される電流の経路は、前記第1の手段と、前記第4の手段とを少なくとも経由することを特徴とする。

#### 【0073】

20

本発明の半導体装置は、

前記信号電流の経路は、前記変換・駆動用トランジスタのソース・ドレイン間を少なくとも経由し、

前記負荷の駆動時に前記電源から前記負荷に供給される電流の経路は、前記変換・駆動用トランジスタのソース・ドレイン間と、前記駆動用トランジスタのソース・ドレイン間を少なくとも経由することを特徴とする。

#### 【0074】

本発明の半導体装置は、

前記信号電流  $I_{Data}$  と、前記電源から前記負荷に供給される電流  $I_{EL}$  との関係が

$I_{Data} = I_{EL}$

30

となることを特徴とする。

#### 【0075】

本発明の半導体装置において、

前記負荷は、エレクトロルミネッセンス素子を含む発光素子であることを特徴とする。

#### 【0076】

#### 【発明の実施の形態】

##### [実施の形態1]

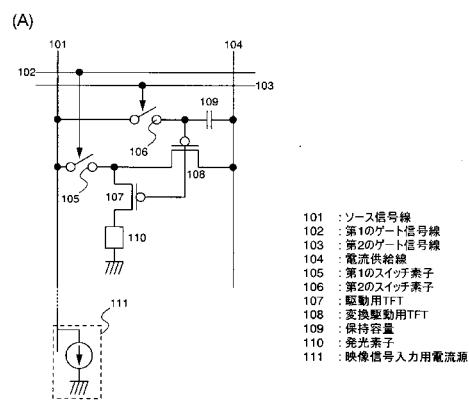

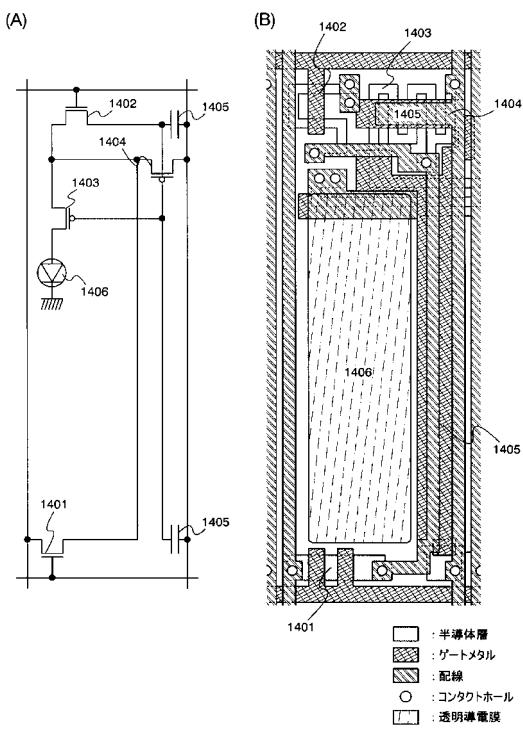

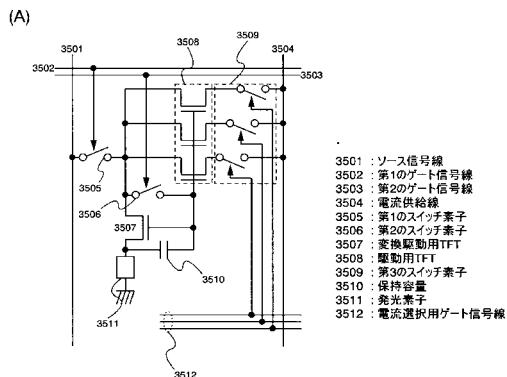

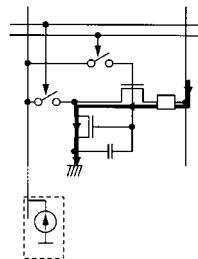

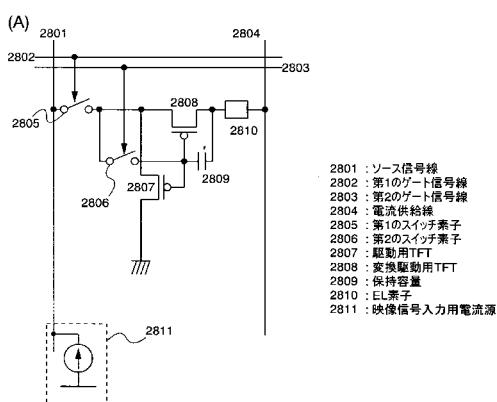

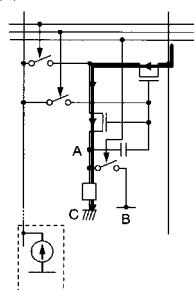

図1(A)に、本発明の一構成について示す。図1(A)の画素は、ソース信号線101、第1および第2のゲート信号線102、103、電流供給線104、第1のスイッチ素子105、第2のスイッチ素子106、駆動用TFT107、変換・駆動用TFT108、保持容量109、EL素子110、信号電流入力用電流源111とを有する。

40

#### 【0077】

なお、保持容量109は、配線、活性層、ゲート材料等とその間の絶縁層とによって容量素子として形成しても良いし、トランジスタのゲート容量を用いて省略しても良い。つまり、必要な期間、変換・駆動用TFT108のゲート・ソース間電圧を保持出来るだけの能力があれば良い。

#### 【0078】

第1のスイッチ素子105は、第1のゲート信号線102によって制御される。その第1の電極はソース信号線101に接続され、第2の電極は駆動用TFT107の第1の電極と、変換・駆動用TFT108の第1の電極とに接続されている。第2のスイッチ素子1

50

06は、第2のゲート信号線103によって制御される。その第1の電極は、駆動用TFT107のゲート電極と、変換・駆動用TFT108のゲート電極とに接続され、第2の電極はソース信号線101に接続されている。駆動用TFT107の第2の電極は、EL素子110の陽極に接続されている。変換・駆動用TFT108の第2の電極は、電流供給線104に接続されている。保持容量109は、変換・駆動用TFT108のゲート電極と第2の電極との間に接続され、変換・駆動用TFT108のゲート・ソース間電圧を保持する。電流供給線104およびEL素子110の陰極には、それぞれ所定の電位が入力され、互いに電位差を有する。

#### 【0079】

なお、保持容量109は、変換・駆動用TFT108のゲート・ソース間に接続されていることが望ましい。10

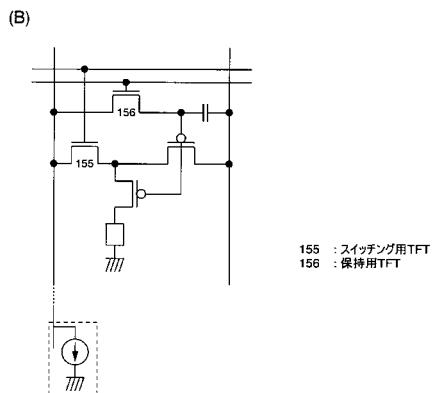

#### 【0080】

第1、第2のスイッチ素子は、他のTFTと同様の構成を有するTFTを用いて形成すれば良い。第1のスイッチ素子105、第2のスイッチ素子106をそれぞれ、スイッチング用TFT155、保持用TFT156として形成する例を図1(B)に示す。ここで、スイッチング用TFT155、保持用TFT156に関しては、ON、OFFによって導通、非導通を選択するスイッチとしてのみ働くので、ここではその極性を問わない。

#### 【0081】

本実施形態に限らず、スイッチ素子にTFTを用いる場合、その極性は問わない。さらに、ここではトランジスタ、特にTFTを用いているが、単結晶シリコンやSOI上に形成されるトランジスタを用いても構わない。20

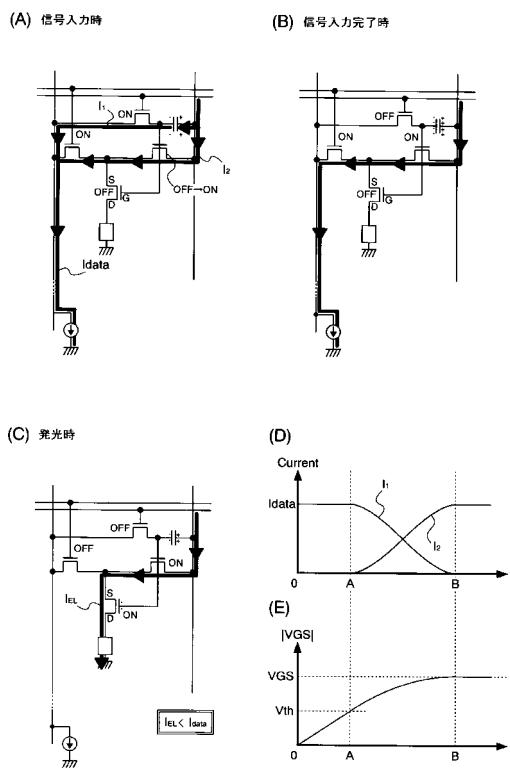

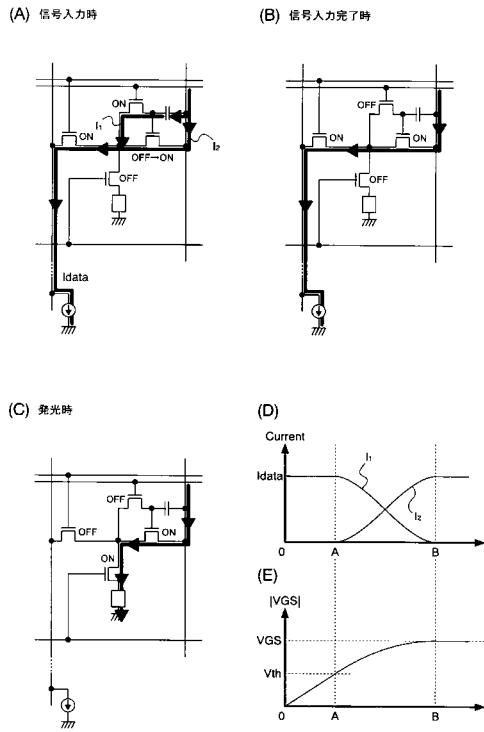

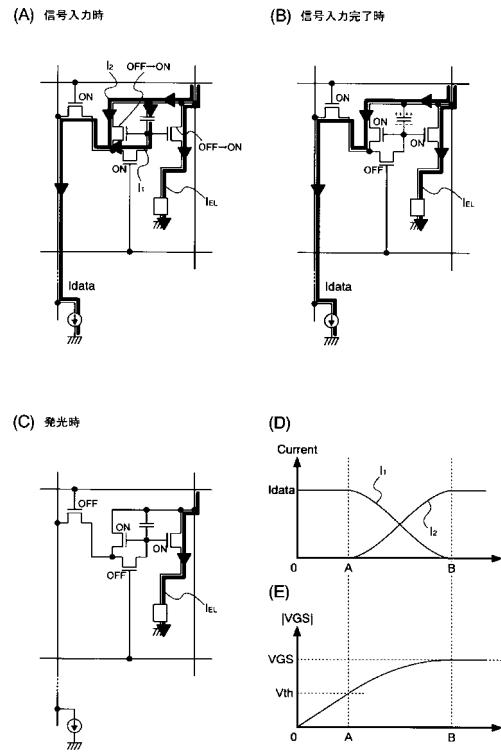

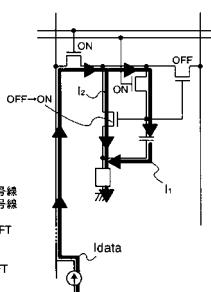

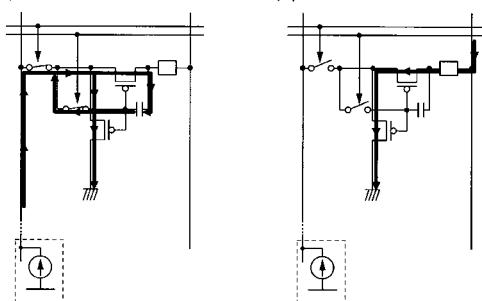

#### 【0082】

図2を用いて、信号電流の書き込みから発光までの動作について説明する。図中、各部を示す図番は、図1(A)(B)に準ずる。図2(A)～(C)は、それぞれ、信号入力時、信号入力完了時、および発光時における電流の流れを模式的に示したものである。図2(D)は、信号電流の書き込み時における各経路を流れる電流の関係を、図2(E)は、同じく信号電流の書き込み時に、保持容量に蓄積される電圧、つまりTFT108のゲート・ソース間電圧について示している。

#### 【0083】

まず、第1のゲート信号線102および第2のゲート信号線103にパルスが入力され、スイッチング用TFT155、保持用TFT156がONする。このとき、ソース信号線を流れる電流を $I_{data}$ とする。30

#### 【0084】

ソース信号線には、電流 $I_{data}$ が流れているので、図2(A)に示すように、画素内では、電流の経路は $I_1$ と $I_2$ とに分かれて流れる。これらの関係を図2(D)に示している。なお、 $I_{data} = I_1 + I_2$ であることは言うまでもない。またこのとき、駆動用TFT107に関しては、スイッチング用TFT156と、保持用TFT155とが共にONすることによって、ゲート電極の電位と入力電極の電位は等しくなる。つまりゲート・ソース間電圧が0となっているため、自らOFFしている。仮に、この状態で駆動用TFT107がONしていると、EL素子111に電流が流れるため、正確に電流 $I_{Data}$ の設定が出来なくなる。40

#### 【0085】

スイッチング用TFT155がONした瞬間には、まだ保持容量109には電荷が保持されていないため、変換・駆動用TFT108はOFFしている。よって、 $I_2 = 0$ となり、 $I_{data} = I_1$ となる。すなわちこの間は、保持容量109における電荷の蓄積による電流のみが流れている。

#### 【0086】

その後、徐々に保持容量109に電荷が蓄積され、両電極間に電位差が生じ始める(図2(D))。両電極の電位差がVthを上回ると(図2(E) A点)、変換・駆動用TFT108がONして、 $I_2$ が生ずる。先に述べたように、 $I_{data} = I_1 + I_2$ があるので、 $I_1$ は次第50

に減少するが、依然電流は流れしており、さらに保持容量には電荷の蓄積が行われる。保持容量 109においては、その両電極間の電位差、つまり変換・駆動用 TFT108 のゲート・ソース間電圧 VGS が所望の電圧、つまり変換・駆動用 TFT が  $I_{data}$  を流すことが出来るだけの電圧(VGS)になるまで電荷の蓄積が続く。やがて電荷の蓄積が終了する(図 2(E) B 点)と、電流  $I_1$  は流れなくなり、さらに変換・駆動用 TFT108 はそのときの VGS に見合った電流が流れ、 $I_{data} = I_2$  となる(図 2(B))。次いで、第 2 のゲート信号線 103 の選択が終了し、保持用 TFT156 が OFF して、信号の書き込み動作が完了する。

#### 【0087】

続いて、発光動作に移る。第 1 のゲート信号線 102 の選択が終了すると、スイッチング用 TFT155 が OFF する。すると、電流供給線 スイッチング用 TFT105 電流源の電流パスが遮断されるため、今まで変換・駆動用 TFT108 に  $I_{data}$  を流すために保持容量 109 に蓄積されていた電荷の一部が、駆動用 TFT107 のゲート電極へと移動する。これにより、駆動用 TFT107 が自動的に ON する。よって、図 2(C)に示すように、電流供給線 変換・駆動用 TFT108 駆動用 TFT107 EL 素子 110 という電流パスが生じ、電流  $I_{EL}$  が流れる。よって EL 素子 110 が発光する。

#### 【0088】

このとき、変換・駆動用 TFT108 のゲート電極と、駆動用 TFT107 のゲート電極とは接続されているため、変換・駆動用 TFT108 と、駆動用 TFT107 とは 1 つのマルチゲート型 TFT として機能することになる。一般に、TFTにおいてはゲート長 L が大きくなると、ドレイン電流は小さくなる。この場合、信号の書き込み動作においては、電流  $I_{data}$  は最終的に変換・駆動用 TFT108 のみを流れているのに対し、発光時には変換・駆動用 TFT108 および駆動用 TFT107 を、電流  $I_{EL}$  が流れている。よって、発光時の方が、ゲート電極の本数が多くなり、結果としてゲート長 L が大きくなっていることから、電流の大きさは、 $I_{data} > I_{EL}$  となる。

#### 【0089】

なお、駆動用 TFT107 のチャネル幅 W と、変換・駆動用 TFT108 のチャネル幅 W とは、同じ大きさとしても良いし、異なっていても良い。ゲート長 L に関しても同様である。

#### 【0090】

以上の手順により、信号の書き込みから発光までを行う。本発明によると、EL 素子を低階調で発光させたい場合の信号書き込み時にも、EL 素子を流す電流  $I_{EL}$  よりも大きな電流  $I_{data}$  を用いて書き込むことが出来る。よって、信号電流がノイズに埋もれる等のトラブルを回避し、かつ迅速な書き込み動作が可能となる。

#### 【0091】

また、発光時に、駆動用 TFT107 と変換・駆動用 TFT108 とがマルチゲート型 TFT として動作するため、これらの TFT は同極性とすることが望ましい。さらに、図 2 の方向に電流が流れる場合には、その極性を P チャネル型とするのが望ましい。

#### 【0092】

なお、EL 素子 110 に流れる電流の向きが図 2 と逆の方向に流れる場合の構成へも容易に変形出来る。この場合の構成を図 36 に示す。ここでは、変換・駆動用 TFT と駆動用 TFT の極性は、図 2 と逆の極性としている。信号電流書き込み時と発光時における電流経路は、図 36(B)(C)に示すとおりである。

#### 【0093】

さらに、変換・駆動用 TFT108 は、信号の書き込み時においても、発光時においても用いられている。つまり、信号の書き込みと発光で、一部共通の TFT を用いていることによって、TFT の特性ばらつきが、信号の書き込み動作や発光に影響しにくくなっている。

#### 【0094】

また、図 2(B) (C)の状態に移る際、すなわち発光動作に移る瞬間に、保持容量 109

10

20

30

40

50

に蓄積された電荷の一部は、駆動用 TFT107 のゲート電極に移動する。そのため、実際に保持容量 109 に保持された TFT108 のゲート・ソース間電圧は、書き込み時の所望の値よりも、発光時にはわずかに小さくなっている。よって、TFT107、108 の特性ばらつきが生じた場合にも、TFT のゲート・ソース間電圧は、わずかながら流れにくい方向にいくことになり、TFT のオフリーコンデンサによって黒表示の際に素子が発光することを防ぐことが出来る。

#### 【0095】

なお、本実施形態では、スイッチング用 TFT155 および保持用 TFT156 はそれぞれ、第 1 のゲート信号線 102 と第 2 のゲート信号線 103 によって ON、OFF が制御されているが、信号書き込みが完了した後、直ちに EL 素子が発光する場合は、同時に ON、OFF の制御が行われても良い。よって、スイッチング用 TFT155 と、保持用 TFT156 の極性が同じである場合には、互いのゲート電極を同一のゲート信号線に接続して制御することにより、ゲート信号線の本数を減らすことも出来る。10

#### 【0096】

なおここでは、駆動用 TFT107 と変換・駆動用 TFT108 とが駆動する負荷として、EL 素子 110 を用い、発光装置の画素への適用を前提として説明したが、本発明の用途はこれに限定されない。つまり、負荷としてダイオード、トランジスタ、容量、抵抗等、またそれらを組み合わせた回路を負荷として駆動することが可能である。これは、他の実施形態、実施例についても同様である。

#### 【0097】

##### [実施の形態 2]

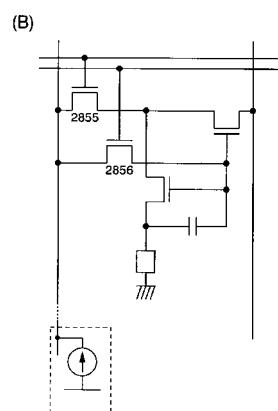

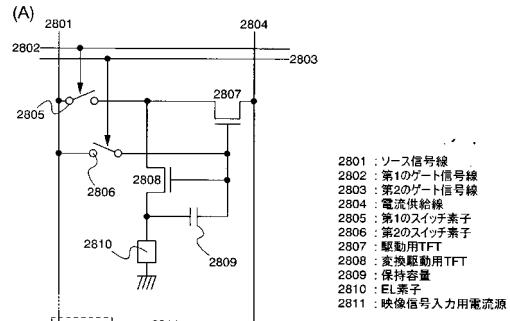

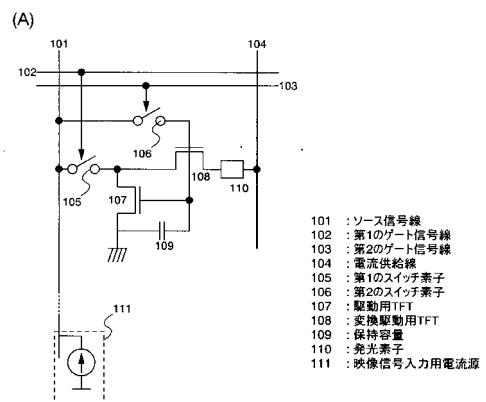

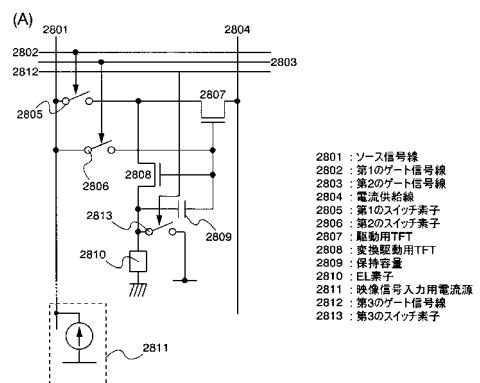

図 28(A)に、本発明の第 2 の形態について示す。図 28(A)の画素は、ソース信号線 2801、第 1 および第 2 のゲート信号線 2802、2803、電流供給線 2804、第 1 のスイッチ素子 2805、第 2 のスイッチ素子 2806、駆動用 TFT2807、変換・駆動用 TFT2808、保持容量 2809、EL 素子 2810 とを有する。各ソース信号線は、信号電流入力用電流源 2811 を有する。

#### 【0098】

なお、保持容量 2809 は、配線、活性層、ゲート材料等とその間の絶縁層とによって容量素子として形成しても良いし、トランジスタのゲート容量を用いて省略しても良い。つまり、必要な期間、変換・駆動用 TFT2808 のゲート・ソース間電圧を保持出来るだけの能力があれば良い。30

#### 【0099】

第 1 のスイッチ素子 2805 は、第 1 のゲート信号線 2802 によって制御される。その第 1 の電極はソース信号線 2801 に接続され、第 2 の電極は変換・駆動用 TFT2808 の第 1 の電極と、駆動用 TFT2807 の第 1 の電極とに接続されている。第 2 のスイッチ素子 2806 は、第 2 のゲート信号線 2803 によって制御される。その第 1 の電極はソース信号線 2801 に接続され、第 2 の電極は変換・駆動用 TFT2808 のゲート電極と、駆動用 TFT2807 のゲート電極とに接続されている。駆動用 TFT2807 の第 2 の電極は、電流供給線 2804 に接続され、変換・駆動用 TFT2808 の第 2 の電極は、EL 素子 2810 の一方の電極に接続されている。保持容量 2809 は、変換・駆動用 TFT2808 のゲート電極と第 2 の電極との間に接続され、変換・駆動用 TFT2808 のゲート・ソース間電圧を保持する。電流供給線 2804 および EL 素子 2810 の他方の電極には、それぞれ所定の電位が入力され、互いに電位差を有する。40

#### 【0100】

なお、保持容量 2809 は、変換・駆動用 TFT2808 のゲート・ソース間に接続されていることが望ましい。

#### 【0101】

第 1、第 2 のスイッチ素子は、他の TFT と同様の構成を有する TFT を用いて形成すれば良い。第 1 のスイッチ素子 2805、第 2 のスイッチ素子 2806 をそれぞれ、スイッチング用 TFT2855、保持用 TFT2856 として形成する例を図 28(B)に示す。50

ここで、スイッチング用 TFT2855、保持用 TFT2856 に関しては、ON、OFF によって導通、非導通を選択するスイッチとしてのみ働くので、ここではその極性を問わない。

#### 【0102】

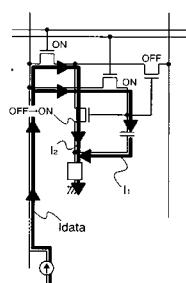

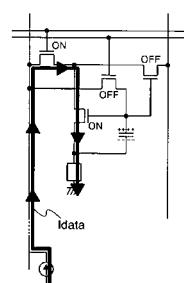

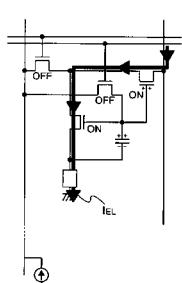

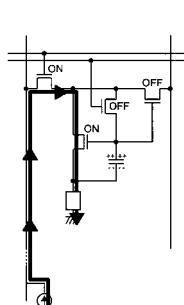

図29を用いて、信号電流の書き込みから発光までの動作について説明する。図中、各部を示す図番は、図28(A)に準ずる。図29(A)～(C)はそれぞれ、信号入力時、信号入力完了時、および発光時における電流の経路を模式的に示したものである。図29(D)は、信号電流の書き込み時における各経路を流れる電流の関係を、図29(E)は、同じく信号電流の書き込み時に、保持容量に蓄積される電圧、つまり変換・駆動用 TFT2808 のゲート・ソース間電圧について示している。

10

#### 【0103】

まず、第1のゲート信号線2802および第2のゲート信号線2803にパルスが入力され、スイッチング用 TFT2855 と保持用 TFT2856 がONする。このとき、ソース信号線2801には、信号電流が入力されており、これを  $I_{data}$  とする。

#### 【0104】

ソース信号線2801には、電流  $I_{data}$  が流れている。今、画素内には、図29(A)に示すような電流経路があり、 $I_{data}$  はこの経路を通って、 $I_1$  と  $I_2$  とに分かれる。これらの関係を図29(D)に示している。なお、 $I_{data} = I_1 + I_2$  である。またこのとき、駆動用 TFT2807 に関しては、スイッチング用 TFT2855 および保持用 TFT2856 がONしているので、ゲート電極の電位と第2の電極の電位が等しくなる。つまりゲート・ソース間電圧が0であるため、駆動用 TFT2807 は自らOFFしている。仮に、この状態で駆動用 TFT2807 がONしていると、EL素子2810に電流が流れるため、正確に電流  $I_{Data}$  の設定が出来なくなる。

20

#### 【0105】

スイッチング用 TFT2855 がONした瞬間には、まだ保持容量2809には電荷が蓄積されていないため、変換・駆動用 TFT2808 はOFFしている。よって、 $I_2 = 0$  となり、 $I_{data} = I_1$  となる。つまりここでは、容量2809に電荷が蓄積するため、その分の電流が生じている。

#### 【0106】

その後、徐々に保持容量2809に電荷が蓄積され、両電極間に電位差が生じ始める。両電極の電位差がVth、すなわち変換・駆動用 TFT2808 のしきい値に到達する(図29(E) A点)と、変換・駆動用 TFT2808 がONして、 $I_2$  が生ずる。先に述べたように、 $I_{data} = I_1 + I_2$  であるので、 $I_1$  は次第に減少するが、保持容量2809への電荷の蓄積が完了するまでは0にはならず、依然電流が生じている。

30

#### 【0107】

保持容量2809においては、その両電極間の電位差、つまり変換・駆動用 TFT2808 のゲート・ソース間電圧が所望の電圧、つまり変換・駆動用 TFT2808 が  $I_{data}$  を流すだけの電圧(VGS)になるまで電荷が蓄積される。やがて電荷の蓄積が終了する(図29(E) B点)と、電流  $I_1$  は流れなくなり、かつ変換・駆動用 TFT2808 はそのときのVGSに見合った電流が流れ、 $I_{data} = I_2$  となる(図29(B))。次いで、第2のゲート信号線2803の選択が終了し、保持用 TFT2856 がOFFする。その後、第1のゲート信号線2802の選択が終了し、スイッチング用 TFT2855 がOFFして、信号の書き込み動作が完了する。

40

#### 【0108】

続いて、発光動作に移る。第1のゲート信号線2802の選択が終了すると、スイッチング用 TFT2855 がOFFする。すると、ソース信号線2801～スイッチング用 TFT2855～変換・駆動用 TFT2808～EL素子2810の電流パスが遮断されるため、今まで変換・駆動用 TFT2808 に  $I_{data}$  を流すために保持容量2809に蓄積されていた電荷の一部が、駆動用 TFT2807 のゲート電極へと移動する。これによって、駆動用 TFT2807 が自動的にONする。よって、図29(C)に示すように、電流供

50

給線 2804 駆動用 TFT2807 変換・駆動用 TFT2808 EL 素子 2810 という電流パスが生じ、発光電流  $I_{EL}$  が流れる。よって EL 素子 2810 が発光する。

#### 【0109】

このとき、駆動用 TFT2807 のゲート電極と変換・駆動用 TFT2808 のゲート電極とは接続されているため、この 2 つの TFT はマルチゲート型 TFT として機能することになる。一般に、TFTにおいてはゲート長 L が大きくなると、ドレイン電流は小さくなる。この場合、信号電流の書き込み動作においては、信号電流は最終的に変換・駆動用 TFT2808 のみを流れていたのに対し、発光時には、発光電流は駆動用 TFT2807 および変換・駆動用 TFT2808 を流れている。よって、発光時の方がゲート電極の本数が多いことになり、結果としてゲート長 L が大きくなっていることから、電流の大きさは  $I_{data} > I_{EL}$  となる。

10

#### 【0110】

なお、駆動用 TFT2807 のチャネル幅 W と、変換・駆動用 TFT2808 のチャネル幅 W とは、同じ大きさとしても良いし、異なっていても良い。ゲート長 L に関しても同様である。

#### 【0111】

以上の手順により、信号電流の書き込みから発光までを行う。本発明によると、EL 素子を低階調で発光させたい場合の信号書き込み時にも、発光電流  $I_{EL}$  よりも大きな信号電流  $I_{data}$  を用いて書き込みを行うことが出来る。さらに、EL 素子が負荷となっていても、十分に大きな電流での書き込みを行うことにより、書き込み時間の短縮が可能となる。

20

#### 【0112】

また、発光時に、駆動用 TFT2807 と変換・駆動用 TFT2808 とがマルチゲート型 TFT として動作するため、これらの TFT は同極性とすることが望ましい。さらに、図 29 の方向に電流が流れる場合には、その極性を N チャネル型とするのが望ましい。

#### 【0113】

また、実施形態 1 で説明したように、EL 素子に流れる電流の向きが逆になる場合にも容易に構成が変形出来る。この場合の構成を図 37(A) に示す。ここでは、変換・駆動用 TFT と駆動用 TFT の極性は、図 29 と逆の極性としている。信号電流書き込み時、発光時の電流経路は、図 37(B)(C) に示すとおりである。その他、以後の実施例においても同様の変形が可能であるので、以降は説明を省略する。

30

#### 【0114】

さらに、変換・駆動用 TFT2808 は、信号の書き込み時においても、発光時においても用いられている。つまり、信号の書き込みと発光で、一部共通の TFT を用いていることによって、TFT の特性ばらつきが、信号の書き込み動作や発光に影響しにくくなっている。

#### 【0115】

また、図 29(B) (C) の状態に移る際、すなわち発光動作に移る瞬間に、保持容量 2809 に蓄積された電荷の一部は、駆動用 TFT2807 のゲート電極に移動する。そのため、実際に保持容量 2809 に保持された TFT2808 のゲート・ソース間電圧は、書き込み時の所望の値よりも、発光時にはわずかに小さくなっている。よって、TFT2807、2808 の特性ばらつきが生じた場合にも、TFT のゲート・ソース間電圧は、わずかながら流れにくい方向にいくことになり、TFT のオフリーケ電流によって黒表示の際に素子が発光することを防ぐことが出来る。

40

#### 【0116】

なお、本実施形態では、スイッチング用 TFT2855 および保持用 TFT2856 はそれぞれ、第 1 のゲート信号線 2802 と第 2 のゲート信号線 2803 によって ON、OFF が制御されているが、信号書き込みが完了した後、直ちに EL 素子が発光する場合は、同時に ON、OFF の制御が行われても良い。よって、スイッチング用 TFT2855 と、保持用 TFT2856 の極性が同じである場合には、互いのゲート電極を同一のゲート信号線に接続して制御することにより、ゲート信号線の本数を減らすことも出来る。

50

## 【0117】

前出の表1に、本発明の第1の形態および第2の形態にて示した構成を加え、比較したものを表2に示す。

## 【0118】

## 【表2】

|                                                    | 第1の構成(図6)                    | 第2の構成(図17)                     | 第3の構成(図19)                     | 本発明の形態1(図1)                      | 本発明の形態2(図28)                        |

|----------------------------------------------------|------------------------------|--------------------------------|--------------------------------|----------------------------------|-------------------------------------|

| 映像信号電流 $I_{data}$ と<br>EL素子を流れる電流 $I_{EL}$<br>との関係 | $I_{data} = I_{EL}$          | $I_{data} = I_{EL}$            | $I_{data} \neq I_{EL}$         | $I_{data} \neq I_{EL}$           | $I_{data} \neq I_{EL}$              |

| 電流電圧変換用TFTと<br>駆動用TFTとの関係                          | 変換用TFT : 608<br>駆動用TFT : 608 | 変換用TFT : 1709<br>駆動用TFT : 1709 | 変換用TFT : 1907<br>駆動用TFT : 1906 | 変換用TFT : 108<br>駆動用TFT : 107+108 | 変換用TFT : 2808<br>駆動用TFT : 2807+2808 |

| 書き込み時の<br>映像信号電流                                   | EL素子に流れない                    | EL素子に流れる                       | EL素子に流れない                      | EL素子に流れない                        | EL素子に流れる                            |

| ゲート信号線の本数                                          | 3                            | 3                              | 2                              | 2                                | 2                                   |

## 【0119】

また、本発明の主旨は、信号電流の入力を受けて、任意のタイミングでこの電流の保持を行い、出力するというサンプル・ホールド動作において、電流経路となるTFTをマルチゲート化して用いる点にある。本明細書においては、代表的にはEL素子を用いた発光装置の画素における実施形態を挙げてきたが、特に用途はこれに限られず、振幅変換回路等をはじめとしたアナログ回路に適用しても有効である。

## 【0120】

## 【実施例】

以下に、本発明の実施例について記載する。

## 【0121】

## [実施例1]

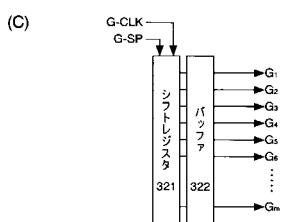

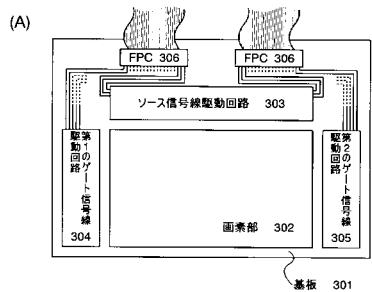

本実施例においては、映像信号にアナログ映像信号を用いて表示を行う半導体装置の構成について説明する。図3(A)に、半導体装置の構成例を示す。基板301上に、複数の画素がマトリクス状に配置された画素部302を有し、画素部周辺には、ソース信号線駆動回路303および、第1、第2のゲート信号線駆動回路304、305を有している。図3(A)においては、2組のゲート信号線駆動回路を用いているが、実施形態の項で説明したように、画素の駆動に複数のゲート信号線の選択を必要としない場合には、いずれか一方のみの配置でも良い。また、ゲート信号線の両端に対称配置し、両側からゲート信号線を駆動する構成としても良い。

## 【0122】

ソース信号線駆動回路303、第1のゲート信号線駆動回路304、および第2のゲート信号線駆動回路305に入力される信号は、フレキシブルプリント基板(Flexible Print Circuit: FPC)306を介して外部より供給される。

## 【0123】

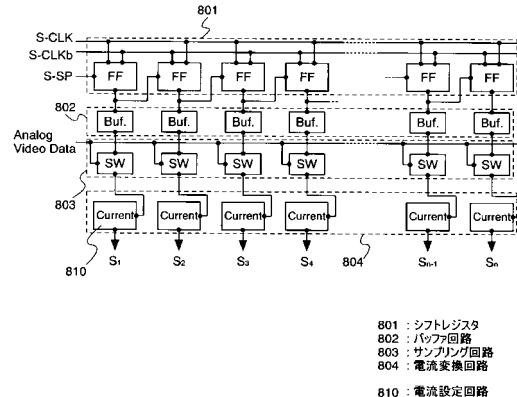

図3(B)に、ソース信号線駆動回路の構成例を示す。これは、映像信号にアナログ映像信号を用いて表示を行うためのソース信号線駆動回路であり、シフトレジスタ311、バッファ312、サンプリング回路313、電流変換回路314を有している。特に図示していないが、必要に応じてレベルシフタ等を追加しても良い。

## 【0124】

ソース信号線駆動回路の動作について説明する。図8に、より詳細な構成を示したので、そちらを参照する。

## 【0125】

シフトレジスタ801は、フリップフロップ回路(FF)等を複数段用いてなり、クロック信号(S-CLK)、クロック反転信号(S-CLKb)、スタートパルス(S-SP)が入力される。これらの信号のタイミングに従って、順次サンプリングパルスが出力される。

**【0126】**

シフトレジスタ801より出力されたサンプリングパルスは、バッファ802等を通って増幅された後、サンプリング回路へと入力される。サンプリング回路803は、サンプリングスイッチ(SW)を複数段用いてなり、サンプリングパルスが入力されるタイミングに従って、ある列で映像信号のサンプリングを行う。具体的には、サンプリングスイッチにサンプリングパルスが入力されると、サンプリングスイッチがONし、そのときに映像信号が有する電位が、サンプリングスイッチを介して電流変換回路804に入力される。

**【0127】**

電流変換回路804は、電流設定回路810を複数段用いてなり、サンプリングされた映像信号に従って、ソース信号線( $S_i : 1 \dots n$ )に所定の電流を出力する。

10 電流設定回路810の動作について、図10を用いて以下に説明する。

**【0128】**

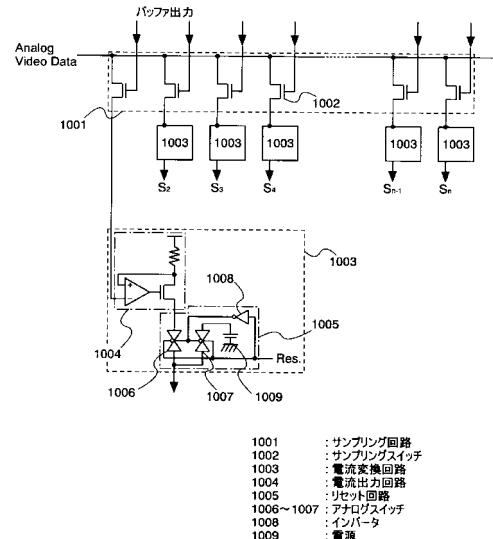

図10は、サンプリング回路および電流変換回路についてその構成を示したものである。サンプリング回路1001の動作については上述の通りである。ここでは、サンプリングスイッチ1002は、1個のTFTを用いているが、Nチャネル型TFTとPチャネル型TFTとを用いて構成したアナログスイッチ等を用いても良い。

**【0129】**

電流変換回路1003は、電流出力回路1004と、リセット回路1005とを有し、サンプリングされた電圧信号を、電流信号に変換する。電流出力回路1004には、映像信号が入力され、その電位に従って、所定の信号電流( $I_{data}$ )を出力する。図10においては、電流出力回路はオペアンプおよびTFTを用いて構成されているが、特にこの構成には限定しない。入力される信号の電位に従って、所定の信号電流を出力できるものであれば良い。

20

**【0130】**

電流出力回路1004から出力された信号電流は、リセット回路1005に入力される。リセット回路1005は、アナログスイッチ1006、1007と、インバータ1008、電源1009とを有する。

**【0131】**

アナログスイッチ1006、1007は、ともにリセット信号(Res.)と、インバータ1008によって反転されたリセット信号とを用いて制御され、一方がONのとき、他方はOFFといった動作をする。

30

**【0132】**

通常の書き込みの際には、リセット信号は入力されておらず、従って、アナログスイッチ1006がONし、アナログスイッチ1007はOFFしている。このとき、ソース信号線には、電流出力回路1004から出力された信号電流が出力されていく。一方、リセット信号が入力されると、アナログスイッチ1006がOFFし、アナログスイッチ1007がONする。このとき、ソース信号線の電位は、電源1009で与えられる電位が印加され、ソース信号線がリセットされる。なお、このリセット動作は、水平帰線期間等で行われる。なお、この電源1009の与える電位は、画素部における電流供給線にほぼ等しい電位であることが望ましい。すなわち、ソース信号線がリセットされた時、ソース信号線に流れる電流を0と出来ることが望ましい。

40

**【0133】**

図3(C)に、ゲート信号線駆動回路の構成例を示す。シフトレジスタ321、バッファ322を有する。回路の動作はソース信号線駆動回路と同様であり、クロック信号とスタートパルスに従って、シフトレジスタ321は順次パルスを出力する。その後、バッファ322で増幅された後、ゲート信号線に入力されて、1行づつ選択状態としていく。選択されたゲート信号線によって制御される画素列に、順にソース信号線から信号電流が画素に書き込まれる。

**【0134】**

なお、ここではシフトレジスタの一例として、フリップフロップを複数段用いてなるもの

50

を図示したが、デコーダ等によって、信号線を選択出来るような構成としていても良い。

#### 【0135】

##### [実施例2]

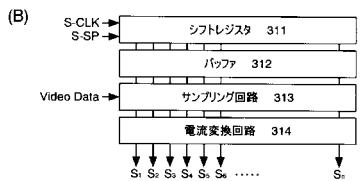

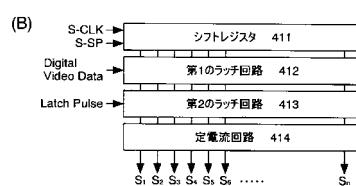

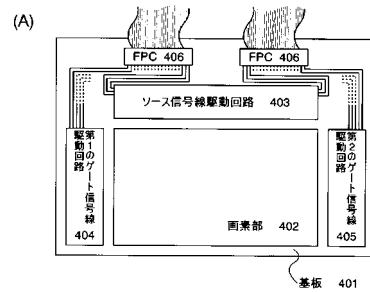

本実施例においては、映像信号にデジタル映像信号を用いて表示を行う半導体装置の構成について説明する。図4(A)に、半導体装置の構成例を示す。基板401上に、複数の画素がマトリクス状に配置された画素部402を有し、画素部周辺には、ソース信号線駆動回路403および、第1、第2のゲート信号線駆動回路404、405を有している。図4(A)においては、2組のゲート信号線駆動回路を用いているが、実施形態の項で説明したように、画素の駆動に複数のゲート信号線の選択を必要としない場合には、いずれか一方のみの配置でも良い。また、ゲート信号線の両端に対称配置し、両側からゲート信号線を駆動する構成としても良い。10

#### 【0136】

ソース信号線駆動回路403、第1のゲート信号線駆動回路404、および第2のゲート信号線駆動回路405に入力される信号は、フレキシブルプリント基板(Flexible Print Circuit: FPC)406を介して外部より供給される。

#### 【0137】

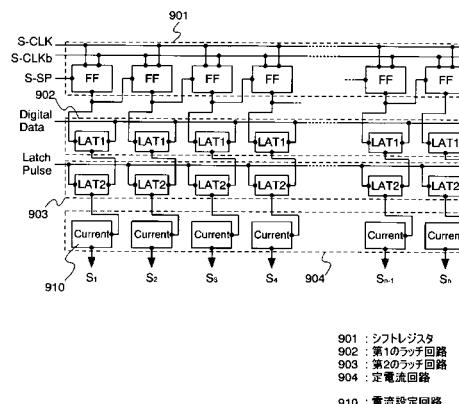

図4(B)に、ソース信号線駆動回路の構成例を示す。これは、映像信号にデジタル映像信号を用いて表示を行うためのソース信号線駆動回路であり、シフトレジスタ411、第1のラッチ回路412、第2のラッチ回路413、定電流回路414を有している。特に図示していないが、必要に応じてレベルシフタ等を追加しても良い。20

#### 【0138】

ゲート信号線駆動回路404、405については、実施例1にて示したものと同様で良いので、ここでは図示および説明を省略する。

#### 【0139】

ソース信号線駆動回路の動作について説明する。図9に、より詳細な構成を示したので、そちらを参照する。

#### 【0140】

シフトレジスタ901は、フリップフロップ回路(FF)等を複数段用いてなり、クロック信号(S-CLK)、クロック反転信号(S-CLKb)、スタートパルス(S-SP)が入力される。これらの信号のタイミングに従って、順次サンプリングパルスが出力される。30

#### 【0141】

シフトレジスタ901より出力されたサンプリングパルスは、第1のラッチ回路902に入力される。第1のラッチ回路902には、デジタル映像信号が入力されており、サンプリングパルスが入力されるタイミングに従って、各段でデジタル映像信号を保持していく。

#### 【0142】

第1のラッチ回路902において、最終段までデジタル映像信号の保持が完了すると、水平帰線期間中に、第2のラッチ回路903にラッチパルス(Latch Pulse)が入力され、第1のラッチ回路902に保持されていたデジタル映像信号は、一斉に第2のラッチ回路903に転送される。その後、第2のラッチ回路903に保持されたデジタル映像信号は、1行分が同時に、定電流回路904へと入力される。40

#### 【0143】

第2のラッチ回路903に保持されたデジタル映像信号が定電流回路904に入力されている間、シフトレジスタ901においては再びサンプリングパルスが出力される。以後、この動作を繰り返し、1フレーム分の映像信号の処理を行う。

#### 【0144】

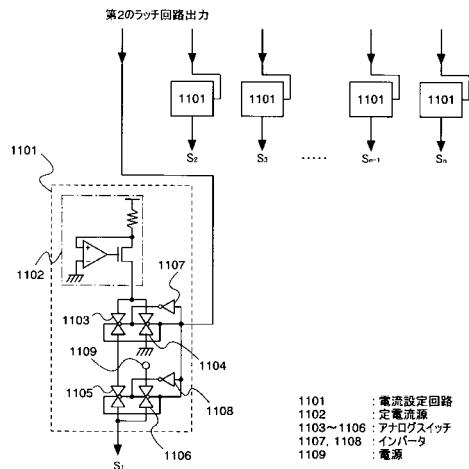

図11は、定電流回路についてその構成を示したものである。定電流回路は、電流設定回路1101を複数段用いてなる。各段に設けられた電流設定回路1101は、第2のラッチ回路から入力されてくるデジタル映像信号が有する1または0の情報によって、ソース信号線に所定の信号電流( $I_{data}$ )を出力する。50

**【0145】**

電流設定回路1101は、信号電流を供給する定電流源1102、アナログスイッチ1103～1106、インバータ1107、1108および電源1109を有する。図11においては、定電流源1102はオペアンプおよびTFTを用いて構成されているが、特にこの構成には限定しない。

**【0146】**

第2のラッピング回路903から出力されてくるデジタル映像信号によって、アナログスイッチ1103～1106のON、OFFが制御される。アナログスイッチ1103と1104とは、互いに排他的に動作し、一方がONのとき、他方がOFFとなる。同様に、アナログスイッチ1105と1106もまた、排他の的に動作する。

10

**【0147】**

第2のラッピング回路903に保持されたデジタル映像信号が1、すなわちここではHレベルのとき、アナログスイッチ1103、1105がONし、アナログスイッチ1104、1106はOFFする。よって、定電流源1102より、所定の信号電流が、アナログスイッチ1103、1105を介してソース信号線に出力される。

**【0148】**

一方、第2のラッピング回路903に保持されたデジタル映像信号が0、すなわちここではLレベルのとき、アナログスイッチ1104、1106がONし、アナログスイッチ1103、1105はOFFする。よって、定電流源1102より出力される信号電流は、ソース信号線には出力されず、アナログスイッチ1104を介してグラウンド側に落とされる。一方、電源1109の電位が、アナログスイッチ1106を介してソース信号線に与えられる。なお、この電源1109の電位は、画素部における電流供給線にほぼ等しい電位であることが望ましい。すなわち、デジタル映像信号がLレベルの時、ソース信号線に流れる電流を0と出来ることが望ましい。

20

**【0149】**

前記の動作が、1水平期間内に、全段にわたって同時に行われる。よって、全てのソース信号線に出力される信号電流の値が決定する。

**【0150】**

なお、電流設定回路においては、スイッチとしてアナログスイッチを用いていたが、トランジションミッショングート等、他の型式のものを用いても良い。また、実施例1においても述べたとおり、シフトレジスタの代わりにデコーダ等を用いて、信号線を選択出来るような構成としていても良い。

30

**【0151】****[実施例3]**

実施例2に示した、デジタル映像信号を用いた表示装置においては、表示は白、黒の2階調となる。本実施例においては、同様にデジタル映像信号を用いて多階調を表示するための駆動回路について説明する。

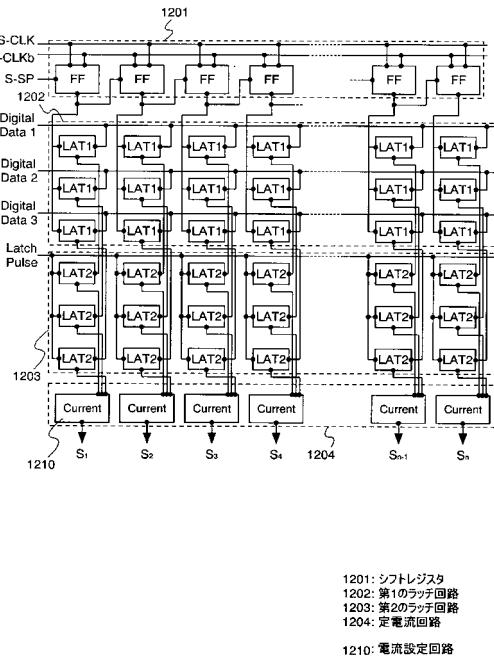

**【0152】**

図12は、3ビットデジタル階調表示を行うためのソース信号線駆動回路の構成例を示している。動作に関しては、実施例2に示した1ビットのものと同様、シフトレジスタ1201、第1のラッピング回路1202、第2のラッピング回路1203、定電流回路1204を有する。定電流回路1204は、実施例2と同様、電流設定回路1210を複数段用いてなる。

40

**【0153】**

3ビットのデジタル映像信号は、ビット毎に入力され(Digital Data 1～3)、第1のラッピング回路1202、第2のラッピング回路1203は、3ビット分並列に配置され、シフトレジスタから出力されるサンプリングパルスによって、3ビット分のデジタル映像信号が同時に保持動作を行う。第2のラッピング回路1203に保持された3ビットデジタル映像信号は、定電流回路1204へと入力される。

**【0154】**

50

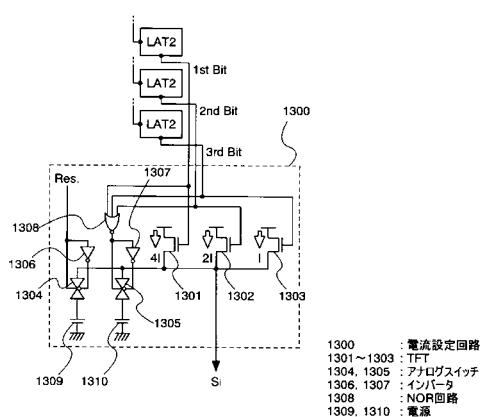

図13は、本実施例の定電流回路を構成する電流設定回路の構成例を示している。電流設定回路1300は、TFT1301～1303、アナログスイッチ1304、1305、インバータ1306、1307、NOR回路1308、電源1309、1310を有する。

#### 【0155】

3ビットデジタル映像信号はそれぞれ、TFT1301～1303のゲート電極と、NOR回路1308に入力される。TFT1301～1303は、それぞれ異なるチャネル幅Wを有し、それぞれのON電流が4：2：1となるようにしている。

#### 【0156】

TFT1301～1303のゲート電極に入力されるデジタル映像信号が1、すなわちHレベルのとき、そのTFTがONし、所定の電流がソース信号線に供給される。ソース信号線に供給される電流は、TFT1301～1303を介して供給される電流の総和となり、各TFTのON電流は、前述の通り4：2：1となっているので、 $2^3$ 、すなわち8段階で電流の大きさを制御出来る。

#### 【0157】

TFT1301～1303のゲート電極に入力されるデジタル映像信号がいずれも0、すなわちLレベルのときは、TFT1301～1303は全てOFFする。一方、NORからHレベルが出力され、アナログスイッチ1305がONし、電源1310の電源電位がソース信号線に与えられる。

#### 【0158】

また、水平帰線期間中に、リセット信号(Reset)が入力されると、アナログスイッチ1304がONし、電源1309の電源電位がソース信号線に与えられる。

#### 【0159】

ここで、電源1309、1310の電位はそれぞれ、画素部の電流供給線と同電位としておき、ソース信号線に電源電位が与えられた時、ソース信号線に流れる電流を0と出来ることが望ましい。

#### 【0160】

以上のようにして、階調表示を行うことが出来る。なお、本実施例では3ビットデジタル階調の場合を例に挙げたが、特にこれに限定するものではなく、さらに高階調の表示をしたい場合にも同様の方法での実施が可能である。

#### 【0161】

#### [実施例4]

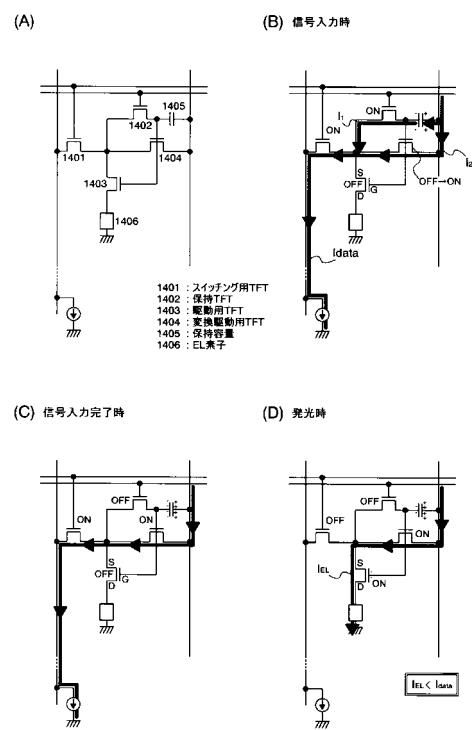

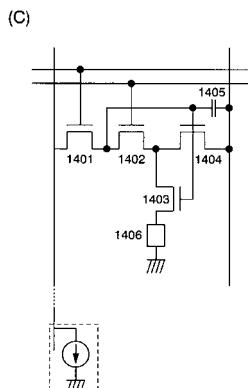

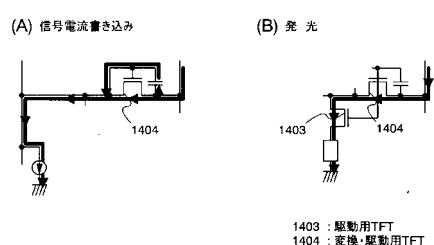

図1に示した構成においては、保持TFT156の第2の電極は、ソース信号線101に接続されていた。この保持TFT156は、図14(A)に示すように、スイッチング用TFT1401の出力電極、駆動用TFT1403の入力電極に接続しても良い。

#### 【0162】

信号の書き込み、発光動作については図14(B)～(D)に示すが、I<sub>2</sub>の電流経路がやや異なる以外は、同様の動作であるので、ここでは説明は省略する。

#### 【0163】

また、保持TFT1402の接続を本実施例のようにすることで、デジタル映像信号を用いて、時間階調方式によって駆動される半導体装置においては、この保持TFT1402を、リセット用TFTとして用いることが出来る。発光期間の終了後、保持TFT1402がONすることにより、駆動用TFT1403のゲート・ソース間電圧が0となってOFFする。その結果、EL素子の発光が停止する。

#### 【0164】

なお、ここでは特に時間階調方式について詳細な説明は省略するが、2001-5426号、特願2000-86968号等に記載されている方法によれば良い。

#### 【0165】

この構成を、アクティブマトリクス型の表示装置に適用した例を図34(A)(B)に示す。

図34(B)は、実際に素子、配線類をレイアウトした例であり、図34(A)は各素子の位

10

20

30

40

50

置関係を反映して表現した等価回路図である。図中の番号は、図14に準ずる。

#### 【0166】

なお、図14以外の構成でも同様の動作が可能である。要は、信号電流の入力時には図38(A)のような経路が確立し、発光時には図38(B)のような経路が確立していれば良い。従って、スイッチ素子の位置等は前記経路に矛盾のないように配置すれば良いので、図38(C)のような接続も可能である。

#### 【0167】

##### [実施例5]

本実施例では、半導体装置の作製方法について示す。なお、ここでは代表的に、駆動回路部を構成するNチャネル型TFTおよびPチャネル型TFTと、画素部に設けられるTFTを示す。なお画素を構成するTFTの一部については特に図示しないが、本実施例の作製方法に従って作製することが可能である。

#### 【0168】

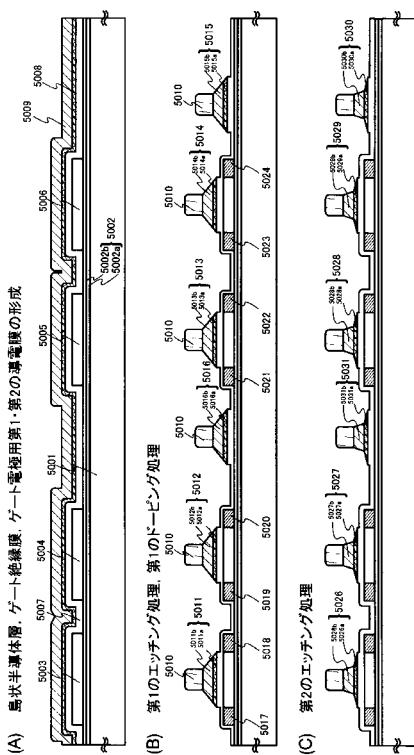

まず、図21(A)に示すように、コーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラス、またはアルミニオホウケイ酸ガラスなどのガラスから成る基板5001上に酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜5002を形成する。例えば、プラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜5002aを10~200[nm](好ましくは50~100[nm])形成し、同様にSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化水素化シリコン膜5002bを50~200[nm](好ましくは100~150[nm])の厚さに積層形成する。本実施例では下地膜5002を2層構造として示したが、前記絶縁膜の単層膜または2層以上積層させた構造として形成しても良い。

#### 【0169】

島状半導体層5003~5006は、非晶質構造を有する半導体膜をレーザー結晶化法や公知の熱結晶化法を用いて作製した結晶質半導体膜で形成する。この島状半導体層5003~5006の厚さは25~80[nm](好ましくは30~60[nm])の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコングルマニウム(SiGe)合金などで形成すると良い。

#### 【0170】

レーザー結晶化法で結晶質半導体膜を作製する場合は、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、YVO<sub>4</sub>レーザーを用いる。これらのレーザーを用いる場合には、レーザー発振器から放射されたレーザー光を光学系で線状に集光し、半導体膜に照射する方法を用いると良い。結晶化の条件は実施者が適宜選択するものであるが、エキシマレーザーを用いる場合はパルス発振周波数300[Hz]とし、レーザーエネルギー密度を100~400[mJ/cm<sup>2</sup>](代表的には200~300[mJ/cm<sup>2</sup>])とする。また、YAGレーザーを用いる場合にはその第2高調波を用いパルス発振周波数30~300[kHz]とし、レーザーエネルギー密度を300~600[mJ/cm<sup>2</sup>](代表的には350~500[mJ/cm<sup>2</sup>])とすると良い。そして幅100~1000[μm]、例えば400[μm]で線状に集光したレーザー光を基板全面に渡って照射し、この時の線状レーザー光の重ね合わせ率(オーバーラップ率)を50~90[%]として行う。

#### 【0171】

なお、レーザーは連続発振またはパルス発振の気体レーザーもしくは固体レーザーを用いることができる。気体レーザーとして、エキシマレーザー、Arレーザー、Krレーザーなどがあり、固体レーザーとして、YAGレーザー、YVO<sub>4</sub>レーザー、YLFレーザー、YAlO<sub>3</sub>レーザー、ガラスレーザー、ルビーレーザー、アレキサンドライドレーザー、Ti:サファイアレーザなどが挙げられる。固体レーザーとしては、Cr、Nd、Er、Ho、Ce、Co、Ti又はTmがドーピングされたYAG、YVO<sub>4</sub>、YLF、YAlO<sub>3</sub>などの結晶を使ったレーザー等も使用可能である。当該レーザーの基本波はドーピングする材料によって異なり、1[μm]前後の基本波を有するレーザー光が得られる。基本波に対する高調波は、非線形光学素子を用いることで得ることができる。

10

20

30

40

50

## 【0172】

非晶質半導体膜の結晶化に際し、大粒径に結晶を得るためにには、連続発振が可能な固体レーザーを用い、基本波の第2高調波～第4高調波を適用するのが好ましい。代表的には、Nd:YVO<sub>4</sub>レーザー(基本波1064[nm])の第2高調波(532[nm])や第3高調波(355[nm])を適用するのが望ましい。具体的には、出力10Wの連続発振のYVO<sub>4</sub>レーザーから射出されたレーザー光を非線形光学素子により高調波に変換する。また、共振器の中にYVO<sub>4</sub>結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または橜円形状のレーザー光に成形して、被処理体に照射する。このときのエネルギー密度は0.01～100[MW/cm<sup>2</sup>]程度(好ましくは0.1～10[MW/cm<sup>2</sup>])が必要である。そして、10～2000[cm/s]程度の速度でレーザー光に対して相対的に半導体膜を移動させて照射する。

## 【0173】

次いで、島状半導体層5003～5006を覆うゲート絶縁膜5007を形成する。ゲート絶縁膜5007はプラズマCVD法またはスパッタ法を用い、厚さを40～150[nm]としてシリコンを含む絶縁膜で形成する。本実施例では、120[nm]の厚さで酸化窒化シリコン膜で形成する。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものではなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。例えば、酸化シリコン膜を用いる場合には、プラズマCVD法でTEOS(Tetraethyl Orthosilicate)とO<sub>2</sub>とを混合し、反応圧力40[Pa]、基板温度300～400[ ]とし、高周波(13.56[MHz])、電力密度0.5～0.8[W/cm<sup>2</sup>]で放電させて形成することが出来る。このようにして作製される酸化シリコン膜は、その後400～500[ ]の熱アニールによりゲート絶縁膜として良好な特性を得ることが出来る。

## 【0174】

そして、ゲート絶縁膜5007上にゲート電極(ゲート)を形成するための第1の導電膜5008と第2の導電膜5009とを形成する。本実施例では、第1の導電膜5008をTaで50～100[nm]の厚さに形成し、第2の導電膜5009をWで100～300[nm]の厚さに形成する。

## 【0175】

Ta膜はスパッタ法で、TaのターゲットをArでスパッタすることにより形成する。この場合、Arに適量のXeやKrを加えると、Ta膜の内部応力を緩和して膜の剥離を防止することが出来る。また、相のTa膜の抵抗率は20[μ cm]程度でありゲート電極に使用することが出来るが、相のTa膜の抵抗率は180[μ cm]程度でありゲート電極とするには不向きである。相のTa膜を形成するために、Taの相に近い結晶構造をもつ窒化タンタルを10～50[nm]程度の厚さでTaの下地に形成しておくと相のTa膜を容易に得ることが出来る。

## 【0176】

W膜を形成する場合には、Wをターゲットとしたスパッタ法で形成する。その他に6フッ化タンゲステン(WF<sub>6</sub>)を用いる熱CVD法で形成することも出来る。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20[μ cm]以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることが出来るが、W中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。このことより、スパッタ法による場合、純度99.9999または99.99[%]のWターゲットを用い、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9～20[μ cm]を実現することが出来る。

## 【0177】

なお、本実施例では、第1の導電膜5008をTa、第2の導電膜5009をWとしたが、特に限定されず、いずれもTa、W、Ti、Mo、Al、Cuなどから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングしたポリシリコン膜に代表される半導体膜を用いてもよい。本実施例以外の他の組み合わせの一例で望ましいものとしては、第1の導電膜5008

を窒化タンタル(TaN)で形成し、第2の導電膜5009をWとする組み合わせ、第1の導電膜5008を窒化タンタル(TaN)で形成し、第2の導電膜5009をAlとする組み合わせ、第1の導電膜5008を窒化タンタル(TaN)で形成し、第2の導電膜5009をCuとする組み合わせが挙げられる。

#### 【0178】

次に、レジストによるマスク5010を形成し、電極及び配線を形成するための第1のエッチング処理を行う。本実施例ではICP(Inductively Coupled Plasma: 誘導結合型プラズマ)エッチング法を用い、エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>を混合し、1[Pa]の圧力でコイル型の電極に500[W]のRF(13.56[MHz])電力を投入してプラズマを生成して行う。基板側(試料ステージ)にも100[W]のRF(13.56[MHz])電力を投入し、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>を混合した場合にはW膜及びTaN膜とも同程度にエッチングされる。10

#### 【0179】

上記エッチング条件では、レジストによるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。テーパー部の角度は15~45°となる。ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10~20[%]程度の割合でエッチング時間を増加させると良い。W膜に対する酸化窒化シリコン膜の選択比は2~4(代表的には3)があるので、オーバーエッチング処理により、酸化窒化シリコン膜が露出した面は20~50[nm]程度エッチングされることになる。こうして、第1のエッチング処理により第1の導電層と第2の導電層から成る第1の形状の導電層5011~5016(第1の導電層5011a~5016aと第2の導電層5011b~5016b)を形成する。このとき、ゲート絶縁膜5007においては、第1の形状の導電層5011~5016で覆われない領域は20~50[nm]程度エッチングされ薄くなった領域が形成される。20(図21(B))

#### 【0180】

そして、第1のドーピング処理を行いN型を付与する不純物元素を添加する。ドーピングの方法はイオンドープ法もしくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を $1 \times 10^{13} \sim 5 \times 10^{14}$ [atoms/cm<sup>2</sup>]とし、加速電圧を60~100[keV]として行う。N型を付与する不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いるが、ここではリン(P)を用いる。この場合、導電層5011~5014がN型を付与する不純物元素に対するマスクとなり、自己整合的に第1の不純物領域5017~5024が形成される。第1の不純物領域5017~5024には $1 \times 10^{20} \sim 1 \times 10^{21}$ [atoms/cm<sup>3</sup>]の濃度範囲でN型を付与する不純物元素を添加する。30(図21(B))

#### 【0181】

次に、図21(C)に示すように、レジストマスクは除去しないまま、第2のエッチング処理を行う。エッチングガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、W膜を選択的にエッチングする。この時、第2のエッチング処理により第2の形状の導電層5026~5031(第1の導電層5026a~5031aと第2の導電層5026b~5031b)を形成する。このとき、ゲート絶縁膜5007においては、第2の形状の導電層5026~5031で覆われない領域はさらに20~50[nm]程度エッチングされ薄くなった領域が形成される。40。

#### 【0182】

W膜やTaN膜のCF<sub>4</sub>とCl<sub>2</sub>の混合ガスによるエッチング反応は、生成されるラジカルまたはイオン種と反応生成物の蒸気圧から推測することが出来る。WとTaNのフッ化物と塩化物の蒸気圧を比較すると、Wのフッ化物であるWF<sub>6</sub>が極端に高く、その他のWC<sub>1.5</sub>、TaF<sub>5</sub>、TaC<sub>1.5</sub>は同程度である。従って、CF<sub>4</sub>とCl<sub>2</sub>の混合ガスではW膜及びTaN膜共にエッチングされる。しかし、この混合ガスに適量のO<sub>2</sub>を添加するとCF<sub>4</sub>とO<sub>2</sub>が反応してCOとFになり、FラジカルまたはFイオンが多量に発生する。その結果、フッ化物の蒸気圧が高いW膜のエッチング速度が増大する。一方、TaNはFが増大しても相対50

的にエッティング速度の増加は少ない。また、TaはWに比較して酸化されやすいので、O<sub>2</sub>を添加することでTaの表面が酸化される。Taの酸化物はフッ素や塩素と反応しないためさらにTa膜のエッティング速度は低下する。従って、W膜とTa膜とのエッティング速度に差を作ることが可能となりW膜のエッティング速度をTa膜よりも大きくすることが可能となる。

#### 【0183】

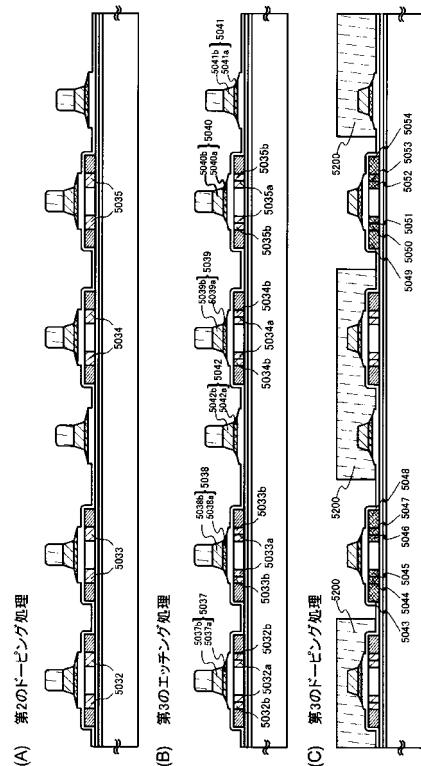

そして、図22(A)に示すように第2のドーピング処理を行う。この場合、第1のドーピング処理よりもドーズ量を下げる高い加速電圧の条件としてN型を付与する不純物元素をドーピングする。例えば、加速電圧を70～120[keV]とし、 $1 \times 10^{13} [\text{atoms/cm}^2]$ のドーズ量で行い、図21(B)で島状半導体層に形成された第1の不純物領域の内側に新たな不純物領域を形成する。ドーピングは、第2の形状の導電層5026～5029を不純物元素に対するマスクとして用い、第1の導電層5026a～5029aの下側の領域にも不純物元素が添加されるようにドーピングする。こうして、第3の不純物領域5032～5035が形成される。この第3の不純物領域5032～5035に添加されたリン(P)の濃度は、第1の導電層5026a～5029aのテーパー部の膜厚に従って緩やかな濃度勾配を有している。なお、第1の導電層5026a～5029aのテーパー部と重なる半導体層において、第1の導電層5026a～5029aのテーパー部の端部から内側に向かって若干、不純物濃度が低くなっているものの、ほぼ同程度の濃度である。

10

#### 【0184】

図22(B)に示すように第3のエッティング処理を行う。エッティングガスにCHF<sub>6</sub>を用い、反応性イオンエッティング法(RIE法)を用いて行う。第3のエッティング処理により、第1の導電層5026a～5031aのテーパー部を部分的にエッティングして、第1の導電層が半導体層と重なる領域が縮小される。第3のエッティング処理によって、第3の形状の導電層5037～5042(第1の導電層5037a～5042aと第2の導電層5037b～5042b)を形成する。このとき、ゲート絶縁膜5007においては、第3の形状の導電層5037～5042で覆われない領域はさらに20～50[nm]程度エッティングされ薄くなった領域が形成される。

20

#### 【0185】

第3のエッティング処理によって、第3の不純物領域5032～5035においては、第1の導電層5037a～5040aと重なる第3の不純物領域5032a～5035aと、第1の不純物領域と第3の不純物領域との間の第2の不純物領域5032b～5035bとが形成される。

30

#### 【0186】

そして、図22(C)に示すように、Pチャネル型TFTを形成する島状半導体層5004、5006に第1の導電型とは逆の導電型の第4の不純物領域5043～5054を形成する。第3の形状の導電層5038b、5040bを不純物元素に対するマスクとして用い、自己整合的に不純物領域を形成する。このとき、Nチャネル型TFTを形成する島状半導体層5003、5005および配線部5041、5042はレジストマスク5200で全面を被覆しておく。不純物領域5043～5054にはそれぞれ異なる濃度でリンが添加されているが、ジボラン(B<sub>2</sub>H<sub>6</sub>)を用いたイオンドープ法で形成し、そのいずれの領域においても不純物濃度が $2 \times 10^{20} \sim 2 \times 10^{21} [\text{atoms/cm}^3]$ となるようにする。

40

#### 【0187】

以上までの工程でそれぞれの島状半導体層に不純物領域が形成される。島状半導体層と重なる第3の形状の導電層5037～5040がゲート電極として機能する。また、5042は島状の第1走査線として機能する。5041は島状の第3走査線と第3の形状の導電層5040を接続する配線として機能する。

#### 【0188】

レジストマスク5200を除去した後、導電型の制御を目的として、それぞれの島状半導体層に添加された不純物元素を活性化する工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行う。その他に、レーザーアニール法、またはラピッドサーマル

50

アニール法(R T A法)を適用することが出来る。熱アニール法では酸素濃度が1[ppm]以下、好ましくは0.1[ppm]以下の窒素雰囲気中で400~700[ ],代表的には500~600[ ]で行うものであり、本実施例では500[ ]で4時間の熱処理を行う。ただし、第3の形状の導電層5037~5042に用いた配線材料が熱に弱い場合には、配線等を保護するため層間絶縁膜(シリコンを主成分とする)を形成した後で活性化を行うことが好ましい。レーザーハニール法を用いる場合、結晶化の際に用いたレーザーを使用することが可能である。活性化の場合は、移動速度は結晶化と同じにし、0.01~100[MW/cm<sup>2</sup>]程度(好ましくは0.01~10[MW/cm<sup>2</sup>])のエネルギー密度が必要となる。

#### 【0189】

さらに、3~100[%]の水素を含む雰囲気中で、300~450[ ]で1~12時間の熱処理を行い、島状半導体層を水素化する工程を行う。この工程は熱的に励起された水素により半導体層のダンギングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。

10

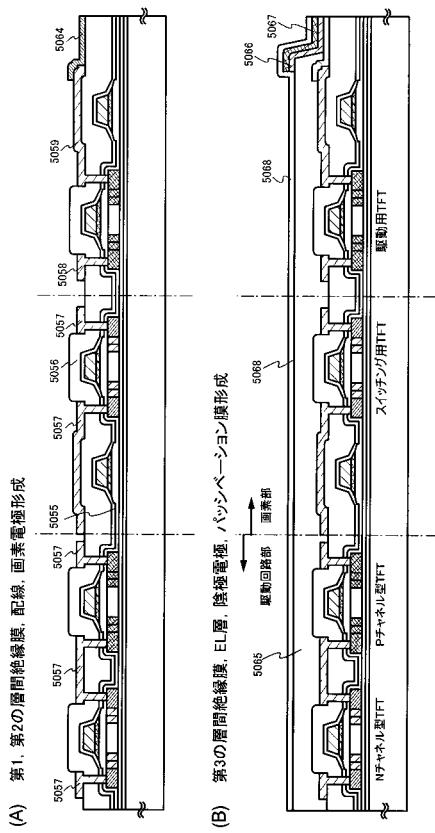

#### 【0190】

次いで、図23(A)に示すように、第1の層間絶縁膜5055を酸化室化シリコン膜から100~200[nm]の厚さで形成する。その上に有機絶縁物材料から成る第2の層間絶縁膜5056を形成した後、第1の層間絶縁膜5055、第2の層間絶縁膜5056、およびゲート絶縁膜5007に対してコンタクトホールを形成し、配線5057、電流供給線5058、接続配線5059をパターニング形成した後、接続配線5062に接する画素電極5064をパターニング形成する。

20

#### 【0191】

第2の層間絶縁膜5056としては、有機樹脂を材料とする膜を用い、その有機樹脂としてはポリイミド、ポリアミド、アクリル、BCB(ベンゾシクロブテン)等を使用することが出来る。特に、第2の層間絶縁膜5056は平坦化の意味合いが強いので、平坦性に優れたアクリルが好ましい。本実施例ではTFTによって形成される段差を十分に平坦化しうる膜厚でアクリル膜を形成する。好ましくは1~5[μm](さらに好ましくは2~4[μm])とすれば良い。

#### 【0192】

コンタクトホールの形成は、ドライエッティングまたはウェットエッティングを用い、N型の不純物領域5017、5018、5021、5022またはP型の不純物領域5043、5048、5049、5054に達するコンタクトホール、配線5042に達するコンタクトホール(図示せず)、電源供給線に達するコンタクトホール(図示せず)、およびゲート電極に達するコンタクトホール(図示せず)をそれぞれ形成する。

30

#### 【0193】

また、配線(接続配線、信号線を含む)5057~5062として、Ti膜を100[nm]、Tiを含むアルミニウム膜を300[nm]、Ti膜150[nm]をスパッタ法で連続形成した3層構造の積層膜を所望の形状にパターニングしたものを用いる。勿論、他の導電膜を用いても良い。

#### 【0194】

また、本実施例では、画素電極5064としてITO膜を110[nm]の厚さに形成し、パターニングを行った。画素電極5064を接続配線5062と接して重なるように配置することでコンタクトを取っている。また、酸化インジウムに2~20[%]の酸化亜鉛(ZnO)を混合した透明導電膜を用いても良い。この画素電極5064が発光素子の陽極となる。(図23(A))

40

#### 【0195】

次に、図23(B)に示すように、珪素を含む絶縁膜(本実施例では酸化珪素膜)を500[nm]の厚さに形成し、画素電極5064に対応する位置に開口部を形成して、バンクとして機能する第3の層間絶縁膜5065を形成する。開口部を形成する際、ウェットエッティング法を用いることで容易にテーパー形状の側壁とすることが出来る。開口部の側壁が十分になだらかでないと段差に起因する有機発光層の劣化が顕著な問題となってしまうため、

50

注意が必要である。

【0196】

次に、有機発光層5066および陰極(MgAg電極)5067を、真空蒸着法を用いて大気解放しないで連続形成する。なお、有機発光層5066の膜厚は80～200[nm](典型的には100～120[nm])、陰極5067の厚さは180～300[nm](典型的には200～250[nm])とすれば良い。

【0197】

この工程では、赤色に対応する画素、緑色に対応する画素および青色に対応する画素に対して順次、有機発光層を形成する。但し、有機発光層は溶液に対する耐性に乏しいためフォトリソグラフィ技術を用いずに各色個別に形成しなくてはならない。そこでメタルマスクを用いて所望の画素以外を隠し、必要箇所だけ選択的に有機発光層を形成するのが好ましい。

10

【0198】

即ち、まず赤色に対応する画素以外を全て隠すマスクをセットし、そのマスクを用いて赤色発光の有機発光層を選択的に形成する。次いで、緑色に対応する画素以外を全て隠すマスクをセットし、そのマスクを用いて緑色発光の有機発光層を選択的に形成する。次いで、同様に青色に対応する画素以外を全て隠すマスクをセットし、そのマスクを用いて青色発光の有機発光層を選択的に形成する。なお、ここでは全て異なるマスクを用いるように記載しているが、同じマスクを使いまわしても構わない。

【0199】

ここではRGBに対応した3種類の発光素子を形成する方式を用いたが、白色発光の発光素子とカラーフィルタを組み合わせた方式、青色または青緑発光の発光素子と蛍光体(蛍光性の色変換層:CCM)とを組み合わせた方式、陰極(対向電極)に透明電極を利用してRGBに対応した発光素子を重ねる方式などを用いても良い。

20

【0200】

なお、有機発光層5066としては公知の材料を用いることが出来る。公知の材料としては、駆動電圧を考慮すると有機材料を用いるのが好ましい。例えば正孔注入層、正孔輸送層、発光層および電子注入層でなる4層構造を有機発光層とすれば良い。

【0201】

次に、メタルマスクを用いて陰極5067を形成する。なお本実施例では陰極5067としてMgAgを用いたが、本発明はこれに限定されない。陰極5067として他の公知の材料を用いても良い。

30

【0202】

最後に、窒化珪素膜でなるパッシベーション膜5068を300[nm]の厚さに形成する。パッシベーション膜5068を形成しておくことで、有機発光層5066を水分等から保護することができ、発光素子の信頼性をさらに高めることが出来る。

【0203】

こうして図23(B)に示すような構造の半導体装置が完成する。

【0204】

ところで、本実施例の半導体装置は、画素部だけでなく駆動回路部にも最適な構造のTFTを配置することにより、非常に高い信頼性を示し、動作特性も向上しうる。また結晶化工程においてNi等の金属触媒を添加し、結晶性を高めることも可能である。それによって、信号線駆動回路の駆動周波数を10[MHz]以上にすることが可能である。

40

【0205】

まず、極力動作速度を落とさないようにホットキャリア注入を低減させる構造を有するTFTを、駆動回路部を形成するCMOS回路のNチャネル型TFTとして用いる。なお、ここでいう駆動回路としては、シフトレジスタ、バッファ、レベルシフタ、線順次駆動におけるラッチ、点順次駆動におけるトランスマッシュゲートなどが含まれる。

【0206】

本実施例の場合、Nチャネル型TFTの活性層は、ソース領域(ソース)、ドレイン領域(

50

ドレイン)、ゲート絶縁膜を間に挟んでゲート電極と重なるオーバーラップ LDD 領域( $L_{OV}$ 領域)、ゲート絶縁膜を間に挟んでゲート電極と重ならないオフセット LDD 領域( $L_{OF}$ 領域)およびチャネル形成領域を含む。

#### 【0207】

また、CMOS回路のPチャネル型TFTは、ホットキャリア注入による劣化が殆ど気にならないので、特にLDD領域を設けなくても良い。勿論、Nチャネル型TFTと同様にLDD領域を設け、ホットキャリア対策を講じることも可能である。

#### 【0208】

その他、駆動回路において、チャネル形成領域を双方に電流が流れるようなCMOS回路、即ち、ソース領域とドレイン領域の役割が入れ替わるようなCMOS回路が用いられる場合、CMOS回路を形成するNチャネル型TFTは、チャネル形成領域の両サイドにチャネル形成領域を挟む形でLDD領域を形成することが好ましい。このような例としては、点順次駆動に用いられるトランスマッショングートなどが挙げられる。また駆動回路において、オフ電流を極力低く抑える必要のあるCMOS回路が用いられる場合、CMOS回路を形成するNチャネル型TFTは、 $L_{OV}$ 領域を有していることが好ましい。このような例としては、やはり、点順次駆動に用いられるトランスマッショングートなどが挙げられる。

10

#### 【0209】

なお、実際には図23(B)の状態まで完成したら、さらに外気に曝されないように、気密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィルム等)や透光性のシーリング材でパッケージング(封入)することが好ましい。その際、シーリング材の内部を不活性雰囲気にしたり、内部に吸湿性材料(例えば酸化バリウム)を配置したりすると発光素子の信頼性が向上する。

20

#### 【0210】

また、パッケージング等の処理により気密性を高めたら、基板上に形成された素子又は回路から引き回された端子と外部信号端子とを接続するためのFPCを取り付けて製品として完成する。このような出荷出来る状態にまでした状態を本明細書中では半導体装置という。

#### 【0211】

また、本実施例で示す工程に従えば、半導体装置の作製に必要なフォトマスクの数を抑えることが出来る。その結果、工程を短縮し、製造コストの低減及び歩留まりの向上に寄与することが出来る。

30

#### 【0212】

##### [実施例6]

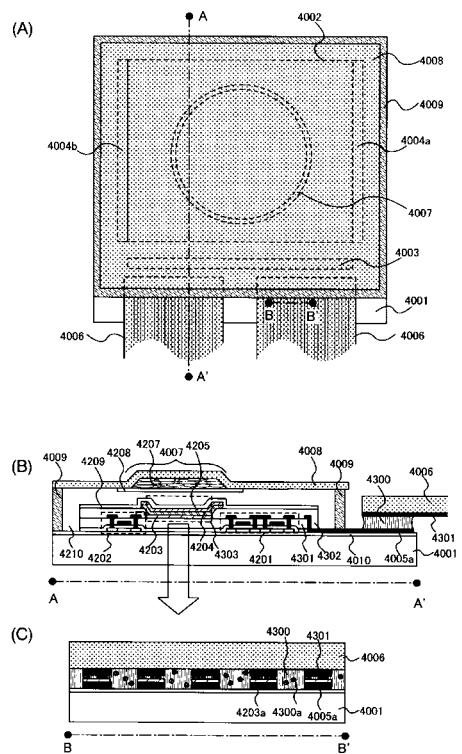

本実施例では、本発明を用いて半導体装置を作製した例について、図15を用いて説明する。

#### 【0213】

図15(A)は、TFTが形成された素子基板をシーリング材によって封止することによって形成された半導体装置の上面図であり、図15(B)は、図15(A)のA-A'における断面図、図15(C)は図15(A)のB-B'における断面図である。

40

#### 【0214】

基板4001上に設けられた画素部4002と、ソース信号線駆動回路4003と、第1及び第2のゲート信号線駆動回路4004a、bとを囲むようにして、シール材4009が設けられている。また画素部4002と、ソース信号線駆動回路4003と、第1及び第2のゲート信号線駆動回路4004a、bとの上にシーリング材4008が設けられている。よって画素部4002と、ソース信号線駆動回路4003と、第1及び第2のゲート信号線駆動回路4004a、bとは、基板4001とシール材4009とシーリング材4008とによって、充填材4210で密封されている。

#### 【0215】

また基板4001上に設けられた画素部4002と、ソース信号線駆動回路4003と、

50

第1及び第2のゲート信号線駆動回路4004a、bとは、複数のTFTを有している。図15(B)では代表的に、下地膜4010上に形成された、ソース信号線駆動回路4003に含まれるTFT(但し、ここではNチャネル型TFTとPチャネル型TFTを図示する)4201及び画素部4002に含まれるTFT4202を図示した。

#### 【0216】

TFT4201及び4202上には層間絶縁膜(平坦化膜)4301が形成され、その上にTFT4202のドレインと電気的に接続する画素電極(陽極)4203が形成される。画素電極4203としては仕事関数の大きい透明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物、酸化インジウムと酸化亜鉛との化合物、酸化亜鉛、酸化スズまたは酸化インジウムを用いることができる。また、前記透明導電膜にガリウムを添加したもの用いても良い。10

#### 【0217】

そして、画素電極4203の上には絶縁膜4302が形成され、絶縁膜4302は画素電極4203の上に開口部が形成されている。この開口部において、画素電極4203の上には有機発光層4204が形成される。有機発光層4204は公知の有機発光材料または無機発光材料を用いることができる。また、有機発光材料には低分子系(モノマー系)材料と高分子系(ポリマー系)材料があるがどちらを用いても良い。

#### 【0218】

有機発光層4204の形成方法は公知の蒸着技術もしくは塗布法技術を用いれば良い。また、有機発光層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層を自由に組み合わせて積層構造または単層構造とすれば良い。20

#### 【0219】

有機発光層4204の上には遮光性を有する導電膜(代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極4205が形成される。また、陰極4205と有機発光層4204の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、有機発光層4204を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極4205を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスター・ツール方式)の成膜装置を用いることで上述のような成膜を可能とする。そして陰極4205は所定の電圧が与えられている。30

#### 【0220】

以上のようにして、画素電極(陽極)4203、有機発光層4204及び陰極4205からなる発光素子4303が形成される。そして発光素子4303を覆うように、絶縁膜4302上に保護膜4209が形成されている。保護膜4209は、発光素子4303に酸素や水分等が入り込むのを防ぐのに効果的である。

#### 【0221】

4005aは電源線に接続された引き回し配線であり、TFT4202の入力電極に接続されている。引き回し配線4005aはシール材4009と基板4001との間を通り、異方導電性フィルム4300を介してFPC4006が有するFPC用配線4301に電気的に接続される。40

#### 【0222】

シーリング材4008としては、ガラス材、金属材(代表的にはステンレス材)、セラミック材、プラスチック材(プラスチックフィルムも含む)を用いることができる。プラスチック材としては、FRP(Fiberglass Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

#### 【0223】

但し、発光素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたは50

アクリルフィルムのような透明物質を用いる。

**【0224】**

また、充填材4210としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。本実施例では充填材として窒素を用いた。

**【0225】**

また充填材4210を吸湿性物質(好ましくは酸化バリウム)もしくは酸素を吸着しうる物質にさらしておくために、シーリング材4008の基板4001側の面に凹部4007を設けて吸湿性物質または酸素を吸着しうる物質4207を配置する。そして、吸湿性物質または酸素を吸着しうる物質4207が飛び散らないように、凹部カバー材4208によって吸湿性物質または酸素を吸着しうる物質4207は凹部4007に保持されている。なお凹部カバー材4208は目の細かいメッシュ状になっており、空気や水分は通し、吸湿性物質または酸素を吸着しうる物質4207は通さない構成になっている。吸湿性物質または酸素を吸着しうる物質4207を設けることで、発光素子4303の劣化を抑制できる。

**【0226】**

図15(C)に示すように、画素電極4203が形成されると同時に、引き回し配線4005a上に接するように導電性膜4203aが形成される。

**【0227】**

また、異方導電性フィルム4300は導電性フィラー4300aを有している。基板4001とFPC4006とを熱圧着することで、基板4001上の導電性膜4203aとFPC4006上のFPC用配線4301とが、導電性フィラー4300aによって電気的に接続される。

**【0228】**

**[実施例7]**

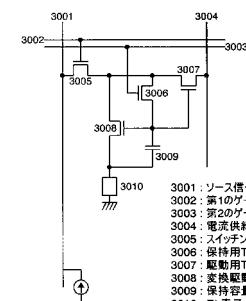

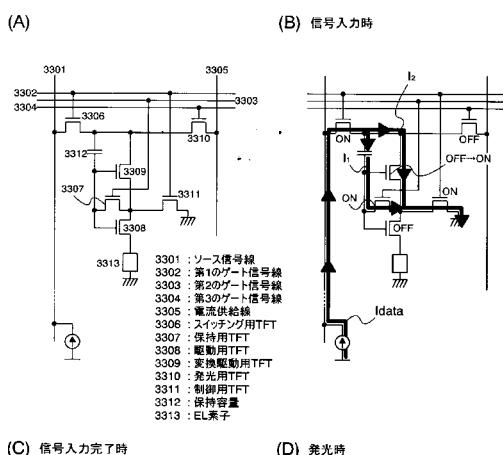

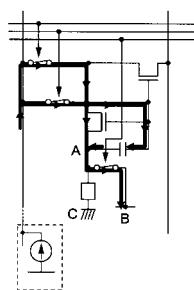

図28(B)に示した構成では、保持用TFT2856の第1の電極は、ソース信号線2801に接続されていた。この保持用TFT2856の接続を変更した例を図30(A)に示す。ここでは、保持用TFT3006の第1の電極は、スイッチング用TFT3005の第2の電極と、駆動用TFT3007の第1の電極とに接続されている。

**【0229】**

信号電流の書き込み、および発光動作については図30(B)~(D)に示すが、 $I_1$ の電流経路がやや異なる以外は同様の動作であるので、ここでは説明を省略する。

**【0230】**

また、保持用TFT3006の接続を本実施例のようにすることで、デジタル映像信号を用いて、時間階調方式によって駆動される発光装置においては、この保持用TFT3006を、リセット用TFTとして用いることが出来る。発光期間の終了後、保持用TFT3006がONすることにより、駆動用TFT3007のゲート・ソース間電圧が0となってOFFする。その結果、EL素子3010への電流経路が遮断される。また、保持容量3009に蓄積されていた電荷も、保持容量3009 保持用TFT3006 変換・駆動用TFT3008という経路をたどって放電される。以上の結果、発光期間が終了する。

**【0231】**

なお、ここでは特に時間階調方式について詳細な説明は省略するが、特開2001-5426号、特願2000-86968号等に記載されている方法によれば良い。

**【0232】**

なお、図30以外の構成でも同様の動作が可能である。要は、信号電流の入力時には図39(A)のような経路が確立し、発光時には図39(B)のような経路が確立していれば良い。従って、スイッチ素子の位置等は前記経路に矛盾のないように配置すれば良い。

10

20

30

40

50

**【0233】****[実施例8]**

まず、実施形態2で示した画素について考える。信号電流の書き込み時には、スイッチング用TFT2855および保持用TFT2856がONしているため、駆動用TFT2807はゲート電極と第2の電極とが同電位となっている。つまりゲート・ソース間電圧が0となってOFFしている。

**【0234】**

しかし、製造プロセス不良等の原因によってTFTのゲート・ソース間電圧が0であってもドレイン電流が流れてしまう場合(ノーマリーオン)がある。このような場合、駆動用TFT2807は信号電流の書き込み時にもONしてしまうことになる。

10

**【0235】**

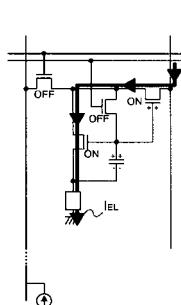

スイッチング用TFT2855や保持用TFT2856に関しては、仮にノーマリーオンとなった場合にも、ゲート信号線の電位を変更することによって正常動作は可能であるが、駆動用TFT2807に関しては、そのゲート・ソース間電圧は保持用TFT2856のON、OFFに依存する部分があり、信号線の電位を変更しても解決出来ない。よって、図31(A)に示すように、発光用TFT3112を、電流供給線3105と駆動用TFT3108との間に配置することによって、このような問題を解決しても良い。

**【0236】**

なお、発光用TFT3112は、駆動用TFT3108と直列に接続し、駆動用TFT3108から漏れてくる電流を遮断出来る場所であればどこに挿入しても良い。また、発光用TFT3112は単なるスイッチ素子として用いられるため、その極性は問わない。

20

**【0237】**

動作について、図31(B)~(D)に示す。信号電流の書き込み時には、発光用TFT3112をOFFするようにしておき、発光時にONするようにする。それ以外の動作は実施形態に示したものと同様で良い。

**【0238】**

また、前述のように、スイッチング用TFT3106と保持用TFT3107とは、同一のゲート信号線によって制御されるようにしても良い。このようにすることで、ゲート信号線の本数を減らし、開口率を高めることが出来る。

30

**【0239】**

また、実施例7でも述べたように、スイッチング用TFT3106や保持用TFT3107の接続を変更しても良い。実施形態1や実施例4に対しても同様の変更が可能である。

**【0240】****[実施例9]**

実施形態2にて、図28で示した構成の場合、信号電流の書き込み時においては、駆動用TFT2807はゲート・ソース間電圧が0であるため、OFFしていた。その後、スイッチング用TFT2855がOFFすると、保持容量2809に蓄積されていた電荷の一部が、駆動用TFT2807のゲート電極に移動することによって、駆動用TFT2807がONして発光する。

40

**【0241】**

ここで、駆動用TFT2807のゲート電極に寄生する容量を考慮した場合、信号電流の書き込み時には、駆動用TFT2807のゲート電極には電荷が蓄積されず、発光時には駆動用TFT2807のゲート電極に電荷が移動することになる。その電荷の供給元は保持容量2809であるから、この電荷の移動により、本来保持容量2809にて保持されているべき電圧(VGS)は、駆動用TFT2807のゲート寄生容量分だけ小さくなる。

**【0242】**

これを解決するためには、あらかじめ駆動用TFT2807がONしていれば良い。本実施例においては、そのような動作を行う場合の構成について示す。

**【0243】**

50

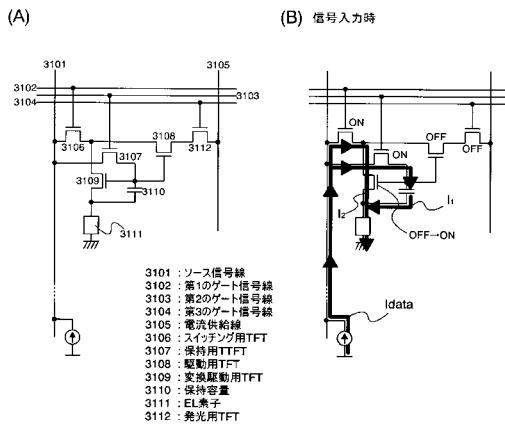

図32(A)に構成を示す。図28に示した構成に加えて、第3のゲート信号線3204、発光用TFT3210、補正用TFT3211が追加されている。第3のゲート信号線3204によって、発光用TFT3210が制御され、補正用TFT3211は、スイッチング用TFT3206と同じく第1のゲート信号線3202によって制御される。発光用TFT3210は、スイッチング用TFT3206の第2の電極と、駆動用TFT3208の第1の電極との間に配置され、補正用TFT3211は、駆動用TFT3208の第1の電極と、EL素子3213の一方の電極との間に配置されている。なお、ここで追加したTFTは、単なるスイッチ素子として用いるので、その極性は問わない。

#### 【0244】

まず、信号電流の書き込み動作から説明する。第1のゲート信号線3202および第2のゲート信号線3203が選択され、スイッチング用TFT3206、保持用TFT3207、および補正用TFT3211がONし、ソース信号線3201より信号電流が入力される。

#### 【0245】

ここで、信号電流 $I_{data}$ は、 $I_1$ と $I_2$ とに分かれて流れる。書き込み開始直後は、保持容量3212にはまだ電荷の蓄積がないため、駆動用TFT3208および変換・駆動用TFT3209はいずれもOFFしており、この時点では $I_2 = 0$ である。よって、 $I_{data} = I_1$ となり、この期間は、保持容量への電荷の蓄積に伴う電荷の移動による電流が生ずるのみである。

#### 【0246】

その後、徐々に保持容量3212に電荷が蓄積され、両電極間に電位差が生じ始める。両電極間の電位差が変換・駆動用TFT3209のしきい値に到達すると、変換・駆動用TFT3209がONして、 $I_2$ が生ずる。先に述べたように、 $I_{data} = I_1 + I_2$ であるので、 $I_1$ は次第に減少するが、保持容量3212への電荷の蓄積が完了するまでは0にはならず、依然電流が生じている。

#### 【0247】

一方、駆動用TFT3208のゲート・ソース間電圧は、実施形態等においては信号電流の書き込み中は0となっていたが、本実施例の場合には発光用TFT3210が配置され、これがOFFしていることから、駆動用TFT3208のゲート・ソース間には電位差が生じてONする。かつ、補正用TFT3211がONしているため、図32(B)に示すように、電流供給線3205 駆動用TFT3208 補正用TFT3211 EL素子3213という電流パスが生じ、電流 $I_3$ が生ずる。なお、 $I_3$ は $I_{data}$ 、 $I_1$ 、 $I_2$ には影響しない、独立した電流である。

#### 【0248】

保持容量3212においては、その両電極間の電位差、つまり変換・駆動用TFT3209のゲート・ソース間電圧が所望の電圧、つまり変換・駆動用TFT3209が $I_{data}$ を流すだけの電圧(VGS)になるまで電荷が蓄積される。やがて電荷の蓄積が終了すると、電流 $I_1$ は流れなくなり、かつ変換・駆動用TFT3209はそのときのVGSに見合った電流が流れ、 $I_{data} = I_2$ となる(図32(B))。次いで、第2のゲート信号線3203の選択が終了し、保持用TFT3207がOFFして、信号の書き込み動作が完了する。

#### 【0249】

続いて、発光動作に移る。第1のゲート信号線3202の選択が終了し、スイッチング用TFT3206、補正用TFT3211がOFFする。一方、第3のゲート信号線3204が選択され、発光用TFT3210がONする。今、保持容量3212には、変換・駆動用TFT3209のゲート・ソース間電圧が保持されており、かつ駆動用TFT3208のゲート電極には、既に電荷が流入した状態となっているため、電流供給線 駆動用TFT3208 発光用TFT3210 変換・駆動用TFT3209 EL素子という電流パスが生じ、発光電流 $I_{EL}$ が流れる。よってEL素子3213が発光する。

#### 【0250】

このとき、駆動用TFT3208のゲート電極と変換・駆動用TFT3209のゲート電

10

20

30

40

50

極とは接続されているため、この2つのTFTはマルチゲート型TFTとして機能することになる。一般に、TFTにおいてはゲート長Lが大きくなると、ドレイン電流は小さくなる。この場合、信号電流の書き込み動作においては、信号電流は最終的に変換・駆動用TFT3209のみを流れていたのに対し、発光時には、駆動用TFT3208および変換・駆動用TFT3209を流れている。よって、発光時の方がゲート電極の本数が多いことになり、結果としてゲート長Lが大きくなっていることから、電流の大きさは $I_{data} > I_{EL}$ となる。

#### 【0251】

本実施例によると、信号電流の書き込み時にも駆動用TFT3208はONしているため、そのゲート電極には電荷が流入しており、発光時に保持容量3212からの電荷の移動が生じないため、駆動用TFT3208のゲート寄生容量が階調に影響を及ぼすことがない。

10

#### 【0252】

また、前述のように、スイッチング用TFT3206と保持用TFT3207とは、同一のゲート信号線によって制御されるようにしても良い。このようにすることで、ゲート信号線の本数を減らし、開口率を高めることが出来る。

#### 【0253】

また、実施例7でも述べたように、スイッチング用TFT3206や保持用TFT3207の接続を変更しても良い。実施形態1や実施例4に対しても同様の変更が可能である。

#### 【0254】

#### [実施例10]

本実施例においては、変換・駆動用TFTおよび駆動用TFTにPチャネル型TFTを用い、実施形態1とは異なる構成について説明する。なお、変換・駆動用TFTおよび駆動用TFT以外のTFTは、単なるスイッチ素子として用いるので、その極性は問わない。

#### 【0255】

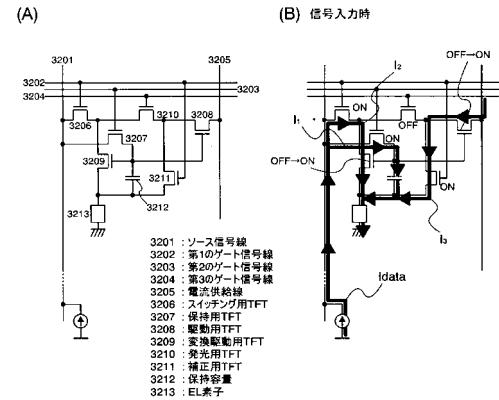

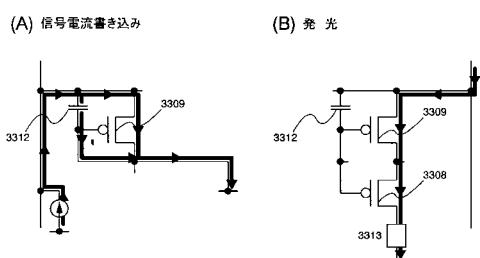

図33(A)に構成を示す。図33(A)の画素は、ソース信号線3301、第1～第3のゲート信号線3302～3304、電流供給線3305、スイッチング用TFT3306、保持用TFT3307、駆動用TFT3308、変換・駆動用TFT3309、発光用TFT3310、制御用TFT3311、保持容量3312、EL素子3313とを有する。

30

#### 【0256】

スイッチング用TFT3306のゲート電極は、第1のゲート信号線3302に接続され、第1の電極は、ソース信号線3301に接続され、第2の電極は、変換・駆動用TFT3309の第1の電極と、発光用TFT3310の第1の電極とに接続されている。変換・駆動用TFT3309の第2の電極は、駆動用TFT3308の第1の電極に接続され、変換・駆動用TFT3309および駆動用TFT3308のゲート電極は互いに接続されている。駆動用TFT3308の第2の電極は、EL素子3313の一方の電極に接続されている。保持用TFT3307のゲート電極は、第2のゲート信号線3303に接続され、第1の電極は、変換・駆動用TFT3309のゲート電極と、駆動用TFT3308のゲート電極とに接続され、第2の電極は、変換・駆動用TFT3309の第2の電極と、駆動用TFT3308の第1の電極とに接続されている。発光用TFT3310のゲート電極は、第3のゲート信号線3304に接続され、第2の電極は電流供給線3305に接続されている。制御用TFT3311のゲート電極は、第1のゲート信号線3302に接続され、第1の電極は、変換・駆動用TFT3309の第2の電極と、駆動用TFT3308の第1の電極と、保持用TFT3307の第2の電極に接続されている。電流供給線3305およびEL素子3313の第2の電極には、それぞれ所定の電位が入力され、互いに電位差を有する。また、制御用TFT3311の第2の電極には、ある一定電位が入力されている。この電位は、ソース信号線3301の電位よりも常に低くなれば良く、特に限定はしない。また、保持用TFT3307の第2の電極は、駆動用TFT3308の第1の電極および変換・駆動用TFT3309の第2の電極に接続されている

40

50

が、制御用 TFT3311 の第 2 の電極、つまりある一定電位に接続しても良い。

#### 【0257】

図 33(B)～(D)を用いて、信号電流の書き込みから発光までの動作について説明する。まず、第 1 および第 2 のゲート信号線が選択され、スイッチング用 TFT3306、制御用 TFT3311、および保持用 TFT3307 が ON し、ソース信号線 3301 より信号電流が入力される(図 33(B))。

#### 【0258】

ここで、映像信号電流  $I_{data}$  は、 $I_1$  と  $I_2$  とに分かれて流れる。書き込み開始直後は、保持容量 3312 にはまだ電荷の蓄積がないため、駆動用 TFT3308 および変換・駆動用 TFT3309 はいずれも OFF しており、この時点では  $I_2 = 0$  である。駆動用 TFT3308 は、保持用 TFT3307 が ON しているため、ゲート・ソース間電圧が 0 となり、自ら OFF している。よって、 $I_{data} = I_1$  となり、この期間は、保持容量への電荷の蓄積に伴う電荷の移動による電流が生ずるのみである。

#### 【0259】

その後、徐々に保持容量 3312 に電荷が蓄積され、両電極間に電位差が生じ始める。両電極間の電位差が変換・駆動用 TFT3309 のしきい値に到達すると、変換・駆動用 TFT3309 が ON して、 $I_2$  が生ずる。先に述べたように、 $I_{data} = I_1 + I_2$  であるので、 $I_1$  は次第に減少するが、保持容量 3312 への電荷の蓄積が完了するまでは 0 にはならず、依然電流が生じている。

#### 【0260】

また、駆動用 TFT3308 は、保持用 TFT3307 が ON することによってゲート・ソース間電圧が 0 となっているため、OFF している。よって信号電流  $I_{data}$  は、制御用 TFT3311 を通って流れ、EL 素子 3313 には流れ込まない。

#### 【0261】

保持容量 3312 においては、その両電極間の電位差、つまり変換・駆動用 TFT3309 のゲート・ソース間電圧が所望の電圧、つまり変換・駆動用 TFT3309 が  $I_{data}$  を流すだけの電圧(VGS)になるまで電荷が蓄積される。やがて電荷の蓄積が終了すると、電流  $I_1$  は流れなくなり、かつ変換・駆動用 TFT3309 はそのときの VGS に見合った電流が流れ、 $I_{data} = I_2$  となる(図 33(C))。次いで、第 2 のゲート信号線 3303 の選択が終了し、保持用 TFT3307 が OFF する。その後、第 1 のゲート信号線 3302 の選択が終了し、スイッチング用 TFT3306 および制御用 TFT3311 が OFF して、信号の書き込み動作が完了する。

#### 【0262】

続いて、発光動作に移る。信号電流の書き込み動作が終了すると、ソース信号線 3301 スイッチング用 TFT3306 変換・駆動用 TFT3309 制御用 TFT3311 電源の電流パスが遮断されるため、今まで変換・駆動用 TFT3309 に  $I_{data}$  を流すために保持容量 3312 に蓄積されていた電荷の一部が、駆動用 TFT3308 のゲート電極へと移動する。これによって、駆動用 TFT3308 が自動的に ON する。続いて、第 3 のゲート信号線が選択されて発光用 TFT3310 が ON すると、図 33(D)に示すように、電流供給線 3305 発光用 TFT3310 変換・駆動用 TFT3309 駆動用 TFT3308 EL 素子 3313 という電流パスが生じ、発光電流  $I_{EL}$  が流れる。よって EL 素子 3313 が発光する。

#### 【0263】

このとき、駆動用 TFT3308 のゲート電極と変換・駆動用 TFT3309 のゲート電極とは接続されているため、この 2 つの TFT はマルチゲート型 TFT として機能することになる。一般に、TFTにおいてはゲート長 L が大きくなると、ドレイン電流は小さくなる。この場合、信号電流の書き込み動作においては、信号電流は最終的に変換・駆動用 TFT3309 のみを流れていたのに対し、発光時には、駆動用 TFT3308 および変換・駆動用 TFT3309 を流れている。よって、発光時の方がゲート電極の本数が多いことになり、結果としてゲート長 L が大きくなっていることから、電流の大きさは  $I_{data}$

10

20

30

40

50

>  $I_{EL}$  となる。

**【0264】**

なお、信号電流の入力時には図39(A)のような経路が確立し、発光時には図39(B)のような経路が確立していれば良い。従って、スイッチ素子の位置等は前記経路に矛盾のないように配置すれば良い。

**【0265】**

本実施例によると、信号電流の書き込み時には、信号電流  $I_{data}$  は EL 素子 3313 に流れ込まない。よって、EL 素子 3313 が負荷として影響する事がないため、信号電流の書き込みをより高速にすることができる。

**【0266】**

また、前述のように、スイッチング用 TFT 3306 と保持用 TFT 3307 とは、同一のゲート信号線によって制御されるようにしても良い。このようにすることで、ゲート信号線の本数を減らし、開口率を高めることができます。

**【0267】**

また、実施形態や他の実施例における構成においても、本実施例を適用して、変換・駆動用 TFT および駆動用 TFT を P チャネル型として構成することができます。

**【0268】**

また、同様に図28に示した構成において、変換・駆動用 TFT および駆動用 TFT を P チャネル型として構成することも可能である。その場合の一構成例を図37(A)に示す。変換・駆動用 TFT および駆動用 TFT を除く、スイッチ素子として用いる TFT の位置は、信号電流入力時に図37(B)のような経路が確立し、発光時には図37(C)のような経路が確立するように配置されなければ良い。

**【0269】**

なお、本実施例では、信号電流  $I_{Data}$  は EL 素子に流れ込まない。もし、信号電流  $I_{Data}$  が EL 素子に流れ込むと、EL 素子が定常状態となるまでの時間が、保持容量への電荷の書き込み時間、つまり本来の電流設定の時間に加わることになり、結果として信号書き込み期間が長く必要になってしまう。そこで、これまでの実施例で挙げてきた回路において、信号電流  $I_{Data}$  が EL 素子に流れる構成をとっているもの、例えば図28、図30等においても、信号の書き込み時間を短くしたい場合には、図40のようにすれば良い。

**【0270】**

図40(A)は、図28の回路に上記の手段を適用した例である。EL 素子の共通電極と接続されていない方の端子と、ある電位を持ったノード(電源線等が望ましい)を、TFT を介して接続する。信号電流の書き込み時に TFT は ON し、発光時には OFF する。信号電流書き込み時と発光時のそれぞれにおける電流経路は、図40(B)(C)に示すとおりである。

**【0271】**

信号電流書き込み時に TFT を ON すると、点 A の電位はすばやく点 B の電位に固定される。そのため、すばやく定常状態とすることが出来、信号電流書き込みが短い時間で完了出来る。

**【0272】**

点 B の電位は任意であるが、表示に影響を与えないようにするには、EL 素子が発光しないような電位とすることが望ましい。また、点 C の電位、つまり EL 素子の一方の電極(図40の場合は陰極)よりも低くしておけば、信号電流の書き込み時には、EL 素子に逆バイアスを印加することも可能である。

**【0273】**

**[実施例11]**

TFT を用いて回路を構成する場合の1つの問題として、素子間の特性ばらつきがある。通常、近接配置された素子においては、その特性ばらつきは比較的小さく出来るが、画素部の素子特性のばらつきを考えた場合、例えば、隣接した画素間での特性ばらつきが生じていると、そのばらつきがわずかであっても、表示ムラとして認識されてしまう。

10

20

30

40

50

**【0274】**

そこで、このような隣接間ばらつきによる表示ムラを改善する方法として、使用する TFT をある期間ごとに切り替えて使用するようとする。このようにすると、TFT の特性ばらつきが時間的に平均化され、表示ムラを認識されにくくすることが出来る。ここで、切り替えの対象となる TFT は、表示ムラに影響を与える可能性のあるものとする。つまり、単なるスイッチ素子として用いる TFT は、特に切り替えを行う必要はない。

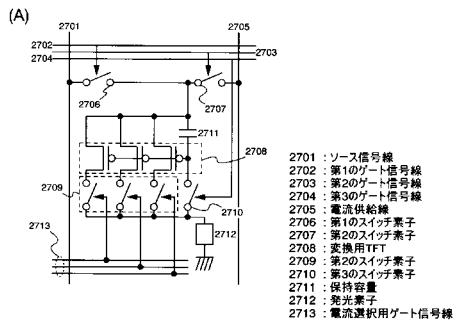

**【0275】**

例として、図 24 に示すような構成を提案する。図 24(A) は、図 1(A) に示した構成に対して適用した例である。図 1(A) の回路では、変換・駆動用 TFT108 と、駆動用 TFT107 の特性に違いがあると、表示ムラが生ずる可能性がある。そこで、駆動用 TFT107 を、図 24(A) で 2407 で示すように複数個(図では例として 3 個)並列に配置し、そのそれぞれに電流が流れるようにしている。さらにスイッチ素子 2413 によって、各経路の導通、遮断の制御を行なうようにしている。ただし、スイッチ素子 2413 は、並列接続した TFT の電流経路を選択、制御出来る部位であるならば図 24 の位置には限定しない。

**【0276】**

駆動方法の基本的な部分は図 1 に示したものと同様であるが、発光時には、スイッチ素子 2413 のうち少なくとも 1 つが ON し、その経路を通じて発光素子 2410 に電流が供給される。

**【0277】**

なお、スイッチ素子 2413 のうち複数を同時に ON し、複数の経路を通じて発光素子 2410 に電流が供給されても良い。

**【0278】**

例えば、1 フレーム期間、あるいは 1 サブフレーム期間ごとにスイッチ素子 2413 によって電流経路を変える。このようにすることで、TFT に隣接間ばらつきがあったとしても、それぞれ異なるばらつきを持った TFT を経時的に切り替えて用いているため、表示ムラが時間的に平均化される。これにより、表示ムラが認識されにくくなるという効果を得られる。

**【0279】**

図 24(B) は、駆動用 TFT2407 は 1 つのみであるが、変換・駆動用 TFT2408 が複数個(図では例として 3 個)並列に配置され、スイッチ素子 2413 によって電流の経路の切り替えを行うようにしたものである。図 24(A) と回路構成は異なっているが、時間的に異なる電流経路を切り替えて用いることによって、表示ムラを平均化出来るという効果は同様である。ここでは、電流書き込み時には、スイッチ素子 2413 を全て導通し、発光時には少なくとも 1 つを導通する。

**【0280】**

なお、電流書き込み時に、スイッチ素子 2413 のうち一部のみを導通するようにしても良いが、全て導通することによって書き込み時の電流経路が増え、より短い期間での書き込み動作が可能となるため、より望ましい。

**【0281】**

なお発光時には、スイッチ素子 2413 のうち複数を同時に ON し、複数の経路を通じて発光素子 2410 に電流が供給されても良い。

**【0282】**

電流経路を切り替えるためのスイッチ素子 2413 は、電流選択用ゲート信号線 2412 に入力されるパルスのタイミングによって制御される。このパルスは、例えば図 25 に示すように、書き込み用ゲート信号線駆動回路によって生成されるゲート信号線選択パルスをラッチ回路 2501 等で保持しておき、外部から電流選択用信号線 2502 にタイミングパルスを入力して、所望のタイミングでいずれかのスイッチ素子が導通するようにすれば良い。あるいは全画素におけるスイッチ素子 2413 が一斉に切り替わるような動作であっても良い。

10

20

30

40

50

**【0283】**

また、ここで設けられたスイッチ素子2413は、発光素子に供給される電流の値を制御するものではなく、あくまで複数の電流経路のうち1つを選択するためのスイッチとしてのみの機能を有するものであり、その極性は問わない。

**【0284】**

なお、ここで提案した構成は、他の構成の画素においても容易に適用が可能である。図26(A)に示した構成は、図5に示した構成に本実施例で提案した構成を適用したものであり、スイッチ素子2606によって、電流経路が選択され、複数個(図では例として3個)並列に配置された駆動用TFT2605のうち少なくとも1つを経由して発光素子2608に電流が供給される。

10

**【0285】**

図26(B)は、図6に示した構成に本実施例で提案した構成を適用したものであり、TFT608を複数個(図では例として3個)並列に配置した変換用TFT2617とスイッチ素子2618とを有する。スイッチ素子2618によって電流経路が選択され、変換用TFT2617のいずれか1つを経由して発光素子2621に電流が供給される。

**【0286】**

なお、電流書き込み時には、スイッチ素子2618をより多く導通し、発光時にはより少なく導通することにより、書き込み動作のための映像信号電流をより大きく出来る。よって、より短い期間で書き込み動作が行える。

**【0287】**

図27(A)は、図17に示した構成に本実施例で提案した構成を適用したものであり、TFT1709を複数個(図では例として3個)並列に配置した変換用TFT2708とスイッチ素子2709とを有する。スイッチ素子2709によって電流経路が選択され、変換用TFT2708の少なくとも1つを経由して発光素子2712に電流が供給される。

20

**【0288】**

なお、電流書き込み時には、スイッチ素子2709をより多く導通し、発光時にはより少なく導通することにより、書き込み動作のための映像信号電流をより大きく出来る。よって、より短い期間で書き込み動作が行える。

**【0289】**

図27(B)は、図19に示した構成に本実施例で提案した構成を適用したものであり、TFT1908を複数個(図では例として3個)並列に配置した変換用TFT2728とスイッチ素子2729とを有する。スイッチ素子2729によって電流経路が選択され、変換用TFT2728のいずれか1つを経由して発光素子2731に電流が供給される。

30

**【0290】**

なお、図27(B)では、駆動用TFTの方に対して切り替えを適用したが、変換・駆動用TFTの方に適用しても良い。

**【0291】**

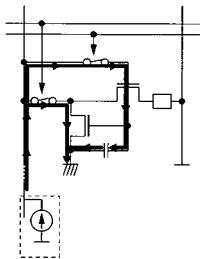

図35は、図30に示した構成に本実施例で提案した構成を適用したものであり、TFT3007を複数個(図では例として3個)並列に配置した駆動用TFT3508と第3のスイッチ素子3509とを有する。第3のスイッチ素子3509によって電流経路が選択され、駆動用TFT3508のいずれか1つを経由して発光素子3511に電流が供給される。

40

**【0292】**

本実施例では、数例の構成の画素においてのみ例示してきたが、並列配置したTFTを時間的に切り替えて用いることによって、特性ばらつきを平均化するといった手法は、他の回路にも容易に適用が可能である。

**【0293】****[実施例12]**

本発明において、三重項励起子からの燐光を発光に利用できる有機発光材料を用いることで、外部発光量子効率を飛躍的に向上させることができる。これにより、発光素子の低消

50

費電力化、長寿命化、および軽量化が可能になる。

【0294】

ここで、三重項励起子を利用し、外部発光量子効率を向上させた報告を示す。

(T.Tsutsui, C.Adachi, S.Saito, Photochemical Processes in Organized Molecular Systems, ed.K.Honda, (Elsevier Sci.Pub., Tokyo,1991) p.437.)

【0295】

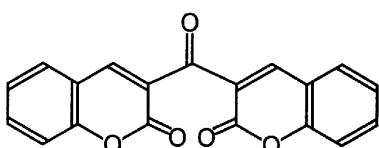

上記の論文により報告された有機発光材料(クマリン色素)の分子式を以下に示す。

【0296】

【化1】

10

【0297】

(M.A.Baldo, D.F.O 'Brien, Y.You, A.Shoustikov, S.Sibley, M.E.Thompson, S.R.Forrest, Nature 395 (1998) p.151.)

20

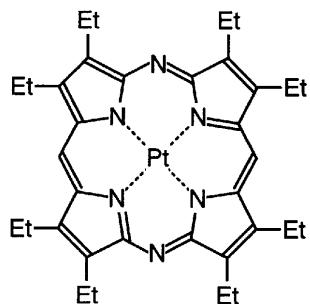

【0298】

上記の論文により報告された有機発光材料(Pt錯体)の分子式を以下に示す。

【0299】

【化2】

30

【0300】

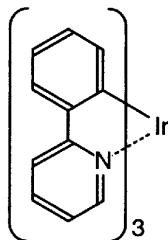

(M.A.Baldo, S.Lamansky, P.E.Burrows, M.E.Thompson, S.R.Forrest, Appl.Phys.Lett., 75 (1999) p.4.) (T.Tsutsui, M.-J.Yang, M.Yahiro, K.Nakamura, T.Watanabe, T.tsuchi, Y.Fukuda, T.Wakimoto, S.Mayaguchi, Jpn.Appl.Phys., 38 (12B) (1999) L1502.)

40

【0301】

上記の論文により報告された有機発光材料(Ir錯体)の分子式を以下に示す。

【0302】

【化3】

**【 0 3 0 3 】**

10

以上のように三重項励起子からの熒光発光を利用できれば原理的には一重項励起子からの蛍光発光を用いる場合より3~4倍の高い外部発光量子効率の実現が可能となる。

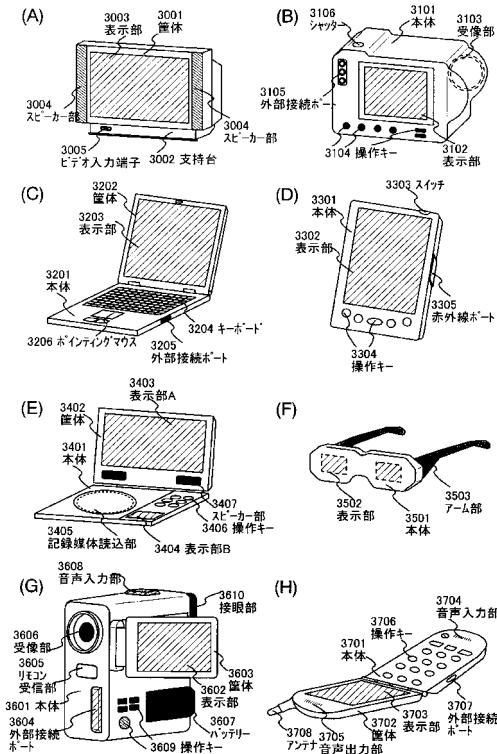

**【 0 3 0 4 】****[実施例 1 3 ]**

発光素子を用いた半導体装置は自発光型であるため、液晶ディスプレイに比べ、明るい場所での視認性に優れ、視野角が広い。従って、様々な電子機器の表示部に用いることができる。

**【 0 3 0 5 】**

本発明の半導体装置を用いた電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。特に、斜め方向から画面を見る機会が多い携帯情報端末は、視野角の広さが重要視されるため、自発光型の半導体装置を用いることが望ましい。それら電子機器の具体例を図16に示す。

20

**【 0 3 0 6 】**

図16(A)は発光素子表示装置であり、筐体3001、支持台3002、表示部3003、スピーカー部3004、ビデオ入力端子3005等を含む。本発明の半導体装置は表示部3003に用いることができる。半導体装置は自発光型であるためバックライトが必要なく、液晶ディスプレイよりも薄い表示部とすることができます。なお、発光素子表示装置は、パソコン用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

30

**【 0 3 0 7 】**

図16(B)はデジタルスチルカメラであり、本体3101、表示部3102、受像部3103、操作キー3104、外部接続ポート3105、シャッター3106等を含む。本発明の半導体装置は表示部3102に用いることができる。

**【 0 3 0 8 】**

40

図16(C)はノート型パーソナルコンピュータであり、本体3201、筐体3202、表示部3203、キーボード3204、外部接続ポート3205、ポインティングマウス3206等を含む。本発明の半導体装置は表示部3203に用いることができる。

**【 0 3 0 9 】**

図16(D)はモバイルコンピュータであり、本体3301、表示部3302、スイッチ3303、操作キー3304、赤外線ポート3305等を含む。本発明の半導体装置は表示部3302に用いることができる。

**【 0 3 1 0 】**

図16(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体3401、筐体3402、表示部A3403、表示部B3404、記録媒体(DVD等)読込部3405、操作キー3406、スピーカー部3407等を含む。表示部A3403

50

403は主として画像情報を表示し、表示部B3404は主として文字情報を表示するが、本発明の半導体装置はこれら表示部A、B3403、3404に用いることができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。

#### 【0311】

図16(F)はゴーグル型ディスプレイ(ヘッドマウントディスプレイ)であり、本体3501、表示部3502、アーム部3503を含む。本発明の半導体装置は表示部3502に用いることができる。

#### 【0312】

図16(G)はビデオカメラであり、本体3601、表示部3602、筐体3603、外部接続ポート3604、リモコン受信部3605、受像部3606、バッテリー3607、音声入力部3608、操作キー3609、接眼部3610等を含む。本発明の半導体装置は表示部3602に用いることができる。

10

#### 【0313】

図16(H)は携帯電話であり、本体3701、筐体3702、表示部3703、音声入力部3704、音声出力部3705、操作キー3706、外部接続ポート3707、アンテナ3708等を含む。本発明の半導体装置は表示部3703に用いることができる。なお、表示部3703は黒色の背景に白色の文字を表示することで携帯電話の消費電流を抑えることができる。

#### 【0314】

なお、将来的に有機発光材料の発光輝度が高くなれば、出力した画像情報を含む光をレンズ等で拡大投影してフロント型若しくはリア型のプロジェクターに用いることも可能となる。

20

#### 【0315】

また、上記電子機器はインターネットやCATV(ケーブルテレビ)などの電子通信回線を通じて配信された情報を表示することが多くなり、特に動画情報を表示する機会が増してきている。有機発光材料の応答速度は非常に高いため、自発光型の半導体装置は動画表示に好ましい。

#### 【0316】

また、自発光型の半導体装置は発光している部分が電力を消費するため、発光部分が極力少なくなるように情報を表示することが望ましい。従って、携帯情報端末、特に携帯電話や音響再生装置のような文字情報を主とする表示部に半導体装置を用いる場合には、非発光部分を背景として文字情報を発光部分で形成するように駆動することが望ましい。

30

#### 【0317】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。また、本実施例の電子機器は実施例1～12に示したいたずれの構成の半導体装置を用いても良い。

#### 【発明の効果】

本発明によって、低階調時にも大きな電流によって書き込み動作を行うことにより、書き込み時間を高速にすることが出来る。また、信号書き込み時には変換用TFTを用い、発光時には駆動用TFTに加えて、さらに変換用TFTを用いて発光素子への電流供給を行うため、書き込み時と発光時におけるTFTの特性ばらつきの影響を低減することができる。さらに、1行の画素を駆動するのに必要なゲート信号線は2本、あるいは1本であるため、従来代表的であった電流書き込み型の画素に比較して、高開口率を実現することができる。

40

#### 【図面の簡単な説明】

【図1】 本発明の一実施形態を示す図。

【図2】 図1に示した画素の、信号書き込み時および発光時の動作と電流の経路について説明する図。

【図3】 本発明の一実施例であるアナログ映像信号入力方式の半導体装置の構成例を示す図。

50

- 【図 4】 本発明の一実施例であるデジタル映像信号入力方式の半導体装置の構成例を示す図。

- 【図 5】 一般的な半導体装置における画素の構成を示す図。

- 【図 6】 代表的な電流書き込み型の半導体装置の画素構成を示す図。

- 【図 7】 図 6 に示した画素の、信号書き込み時および発光時の動作と電流の経路について示す図。

- 【図 8】 図 3 に示した半導体装置におけるソース信号線駆動回路の構成例を示す図。

- 【図 9】 図 4 に示した半導体装置におけるソース信号線駆動回路の構成例を示す図。

- 【図 10】 図 3 に示した半導体装置におけるサンプリング回路および電流変換回路の構成例を示す図。 10

- 【図 11】 図 4 に示した半導体装置における定電流回路の構成例を示す図。

- 【図 12】 図 4 に示した半導体装置におけるソース信号線駆動回路の構成例を示す図。

- 【図 13】 3 ビットデジタル階調に対応した電流設定回路の構成例を示す図。

- 【図 14】 実施形態 1 とは異なる構成とした画素と、その動作および電流の経路について示す図。

- 【図 15】 半導体装置の外観図および断面図。

- 【図 16】 本発明が適用可能な電子機器の例を示す図。

- 【図 17】 代表的な電流書き込み型の半導体装置の画素構成を示す図。

- 【図 18】 図 17 に示した画素の、信号書き込み時および発光時の動作と電流の経路について示す図。 20

- 【図 19】 代表的な電流書き込み型の半導体装置の画素構成を示す図。

- 【図 20】 図 19 に示した画素の、信号書き込み時および発光時の動作と電流の経路について示す図。

- 【図 21】 半導体装置の作製工程を説明する図。

- 【図 22】 半導体装置の作製工程を説明する図。

- 【図 23】 半導体装置の作製工程を説明する図。

- 【図 24】 TFT の隣接間ばらつきによる表示ムラを平均化する構成を有する一例を示す図。 30

- 【図 25】 図 24 に示した画素の駆動方法とその駆動回路の構成を簡略に説明する図。

- 【図 26】 TFT の隣接間ばらつきによる表示ムラを平均化する構成を有する一例を示す図。

- 【図 27】 TFT の隣接間ばらつきによる表示ムラを平均化する構成を有する一例を示す図。

- 【図 28】 本発明の他の一実施形態を示す図。

- 【図 29】 図 28 に示した画素の、信号書き込み時および発光時の動作と電流の経路について説明する図。

- 【図 30】 実施形態 2 とは異なる構成とした画素と、その動作および電流の経路について示す図。 40

- 【図 31】 実施形態 2 とは異なる構成とした画素と、その動作および電流の経路について示す図。

- 【図 32】 実施形態 2 とは異なる構成とした画素と、その動作および電流の経路について示す図。

- 【図 33】 実施形態 2 とは異なる構成とした画素と、その動作および電流の経路について示す図。

- 【図 34】 素子のレイアウト例とその等価回路を示す図。

- 【図 35】 TFT の隣接間ばらつきによる表示ムラを平均化する構成を有する一例を示す図。

- 【図 36】 図 1 に示した画素の構成を一部変更した場合の図。 50

- 【図37】 図28に示した画素の構成を一部変更した場合の図。

- 【図38】 図14に示した画素の電流経路と、構成を一部変更した例を示す図。

- 【図39】 図33に示した画素の電流経路を示す図。

- 【図40】 図28に示した画素の構成を一部変更した例を示す図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図27】

【図28】

【図29】

(A) 信号入力時

(B) 信号入力完了時

(C) 発光時

(D)

(A)

(B) 信号入力時

(C) 信号入力完了時

(D) 発光時

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

(B) 信号電流書き込み

(C) 発光

【図37】

(B) 信号電流書き込み

(C) 発光

【図38】

(C)

1401 : スイッチ用TFT

1402 : 保持用TFT

1403 : 駆動用TFT

1404 : 變換・駆動用TFT

1405 : 保持容量

1406 : 発光素子

【図39】

【図40】

(B) 信号電流書き込み

(C) 発光

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 29/78 6 1 4

H 0 5 B 33/14 A

(31)優先権主張番号 特願2002-152727(P2002-152727)

(32)優先日 平成14年5月27日(2002.5.27)

(33)優先権主張国 日本国(JP)