# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**H01L 31/00** (2006.01)

(21) 출원번호 **10-2009-0097184**

(22) 출원일자 **2009년10월13일** 심사청구일자 **2009년10월13일**

(65) 공개번호 **10-2011-0040058**

(43) 공개일자 2011년04월20일

(56) 선행기술조사문헌

JP07045811 A JP11054563 A JP2000049102 A

JP2004031906 A

전체 청구항 수 : 총 20 항

(45) 공고일자 2012년11월09일

(11) 등록번호 10-1199302

(24) 등록일자 2012년11월02일

(73) 특허권자

#### 한국전자통신연구원

대전광역시 유성구 가정로 218 (가정동)

(72) 발명자

#### 한영탁

대전광역시 서구 월평2동 한아름아파트 102-1201

#### 박상호

대전광역시 유성구 어은로 57, 한빛APT 118동 1301호 (어은동)

(뒷면에 계속)

(74) 대리인

오세준, 권혁수, 송윤호

심사관 : 여덕호

### (54) 발명의 명칭 **광 소자 및 그 제조 방법**

### (57) 요 약

광 소자가 제공된다. 이 광 소자는 도파로 영역 및 실장 영역을 갖는 기판, 기판의 도파로 영역 상에 제공된 하부 클래드층 및 상부 클래드층, 및 이들 사이에 개재된 플랫폼 코어로 구성된 광 도파로, 기판의 실장 영역 상에 하부 클래드층이 식각되어 형성되되, 인터로킹부(interlocking part)를 갖는 테라스, 기판의 실장 영역에 실장되되, 내부에 칩 코어를 갖는 광 능동 칩, 및 광 능동 칩의 실장면에 제공된 칩 정렬 마크를 포함한다. 광 능동 칩은 테라스의 인터로킹부와 광 능동 칩의 칩 정렬 마크와의 인터로킹에 의해 정렬되어 실장 영역 상에 실장되는 것을 특징으로 한다.

### 대 표 도 - 도1b

### (72) 발명자

### 이동훈

대전광역시 유성구 가정로 65, 101동 1203호 (신성 동, 대림두레아파트)

#### 신장욱

대전광역시 유성구 반석서로 98, 602동 2501호 (반석동, 반석마을6단지아파트)

## 이 발명을 지원한 국가연구개발사업

과제고유번호 2007-S-011-03 부처명 지식경제부

연구사업명 IT성장동력기술개발

연구과제명 ROADM용 광스위치 기술개발

주관기관 한국전자통신연구원 연구기간 2007-03-01 ~ 2010-02-28

## 한상필

대전광역시 서구 월평동로 45, 108동 403호 (월평 동, 진달래아파트)

## 백용순

대전광역시 유성구 엑스포로 448, 엑스포APT 207동 504호 (전민동)

### 특허청구의 범위

#### 청구항 1

도파로 영역 및 실장 영역을 갖는 기판;

상기 기판의 상기 도파로 영역 상에 제공된 하부 클래드층 및 상부 클래드층, 및 이들 사이에 개재된 플랫폼 코 어로 구성된 광 도파로;

상기 기판의 상기 실장 영역 상에 상기 하부 클래드층이 식각되어 형성되되, 인터로킹부(interlocking part)를 갖는 테라스;

상기 기판의 상기 실장 영역에 실장되되, 내부에 칩 코어를 갖는 광 능동 칩; 및

상기 광 능동 칩의 실장면에 제공된 칩 정렬 마크를 포함하되,

상기 광 능동 칩은 상기 테라스의 상기 인터로킹부와 상기 광 능동 칩의 상기 칩 정렬 마크와의 인터로킹에 의해 정렬되어 상기 실장 영역 상에 실장되는 것을 특징으로 하는 광 소자.

#### 청구항 2

제 1항에 있어서,

상기 인터로킹부는 상기 테라스가 식각되어, 상기 테라스 내부에 형성된 트렌치인 것을 특징으로 하는 광 소자.

#### 청구항 3

제 1항에 있어서,

상기 인터로킹부는 상기 테라스의 상부면 상에 제공된 플랫폼 정렬 마크인 것을 특징으로 하는 광 소자.

#### 청구항 4

제 3항에 있어서.

상기 테라스의 상기 플랫폼 정렬 마크 및 상기 광 능동 칩의 상기 칩 정렬 마크는 각각 서로 대응되는 음각 및 양각의 모양을 갖는 것을 특징으로 하는 광 소자.

#### 청구항 5

제 1항에 있어서.

상기 기판의 상기 실장 영역 상에서 상기 테라스 주변의 상기 하부 클래드층이 식각된 표면 상에 제공된 플랫폼 범핑 하지 금속; 및

상기 광 능동 칩의 상기 실장면 상에 제공된 칩 범핑 하지 금속을 더 포함하는 것을 특징으로 하는 광 소자.

#### 청구항 6

제 5항에 있어서,

상기 플랫폼 범핑 하지 금속 및 상기 칩 범핑 하지 금속을 전기적으로 연결하는 솔더 필름을 더 포함하는 것을 특징으로 하는 광 소자.

#### 청구항 7

제 1항에 있어서,

상기 칩 정렬 마크 상에 제공되는 추가적인 솔더 필름을 더 포함하는 것을 특징으로 하는 광 소자.

#### 청구항 8

도파로 영역 및 실장 영역을 갖는 기판 상에 하부 클래드층, 플랫폼 코어 및 상부 클래드층을 순차적으로 형성 하는 단계; 상기 기판의 상기 실장 영역 상의 상기 상부 클래드층, 상기 플랫폼 코어 및 상기 하부 클래드층을 제 1 식각 공정으로 식각하여, 상기 도파로 영역에는 광 도파로를 형성하고, 그리고 상기 실장 영역에는 제 1 높이의 하부 클래드층을 형성하는 단계;

상기 기판의 상기 실장 영역 상의 상기 제 1 높이의 하부 클래드층을 제 2 식각 공정으로 식각하여 트렌치를 갖는 제 1 높이의 테라스 및 제 2 높이의 하부 클래드층을 형성하는 단계;

내부에 칩 코어를 갖는 광 능동 칩의 실장면 상에 칩 정렬 마크를 형성하는 단계; 및

상기 기판의 상기 실장 영역 상에 상기 광 능동 칩을 실장하는 단계를 포함하되.

상기 광 능동 칩은 상기 테라스의 상기 트렌치와 상기 광 능동 칩의 상기 칩 정렬 마크와의 인터로킹 (interlocking)에 의해 정렬되어 상기 실장 영역 상에 실장되는 것을 특징으로 하는 광 소자의 제조 방법.

#### 청구항 9

제 8항에 있어서,

상기 기판의 상기 실장 영역 상의 상기 테라스 주변의 상기 제 2 높이의 하부 클래드 상에 플랫폼 범핑 하지 금속을 형성하는 단계; 및

상기 광 능동 칩의 상기 실장면 상에 칩 범핑 하지 금속을 형성하는 단계를 더 포함하는 것을 특징으로 하는 광소자의 제조 방법.

#### 청구항 10

제 9항에 있어서.

상기 칩 범핑 하지 금속 및 상기 칩 정렬 마크는 동시에 형성되는 것을 특징으로 하는 광 소자의 제조 방법.

#### 청구항 11

제 9항에 있어서.

상기 플랫폼 범핑 하지 금속 및 상기 칩 범핑 하지 금속 중 적어도 하나 상에 솔더 필름을 형성하는 단계를 더 포함하는 것을 특징으로 하는 광 소자의 제조 방법.

# 청구항 12

제 11항에 있어서,

상기 플랫폼 범핑 하지 금속 및 상기 칩 범핑 하지 금속 상에 각각 상기 솔더 필름을 형성하는 것을 특징으로 하는 광 소자의 제조 방법.

## 청구항 13

제 8항에 있어서,

상기 칩 정렬 마크 상에 추가적인 솔더 필름을 형성하는 단계를 더 포함하는 것을 특징으로 하는 광 소자의 제조 방법.

## 청구항 14

도파로 영역 및 실장 영역을 갖는 기판 상에 하부 클래드층, 플랫폼 코어 및 상부 클래드층을 순차적으로 형성 하는 단계;

상기 기판의 상기 실장 영역 상의 상기 상부 클래드층, 상기 플랫폼 코어 및 상기 하부 클래드층을 제 1 식각 공정으로 식각하여, 상기 도파로 영역에는 광 도파로를 형성하고, 그리고 상기 실장 영역에는 제 1 높이의 하부 클래드층을 형성하는 단계;

상기 기판의 상기 실장 영역 상의 상기 제 1 높이의 하부 클래드층을 제 2 식각 공정으로 식각하여 제 1 높이의 테라스 및 제 2 높이의 하부 클래드층을 형성하는 단계; 상기 기판의 상기 실장 영역 상의 상기 테라스의 상부면 상에 플랫폼 정렬 마크를 형성하는 단계;

내부에 칩 코어를 갖는 광 능동 칩의 실장면 상에 칩 정렬 마크를 형성하는 단계; 및

상기 기판의 상기 실장 영역 상에 상기 광 능동 칩을 실장하는 단계를 포함하되,

상기 광 능동 칩은 상기 테라스의 상기 플랫폼 정렬 마크와 상기 광 능동 칩의 상기 칩 정렬 마크와의 인터로킹 (interlocking)에 의해 정렬되어 상기 실장 영역 상에 실장되는 것을 특징으로 하는 광 소자의 제조 방법.

### 청구항 15

제 14항에 있어서,

상기 테라스의 상기 플랫폼 정렬 마크 및 상기 광 능동 칩의 상기 칩 정렬 마크는 각각 서로 대응되는 음각 및 양각의 모양을 갖도록 형성되는 것을 특징으로 하는 광 소자의 제조 방법.

#### 청구항 16

제 14항에 있어서,

상기 기판의 상기 실장 영역 상의 상기 테라스 주변의 상기 제 2 높이의 하부 클래드층 상에 플랫폼 범핑 하지 금속을 형성하는 단계; 및

상기 광 능동 칩의 상기 실장면 상에 칩 범핑 하지 금속을 형성하는 단계를 더 포함하는 것을 특징으로 하는 광소자의 제조 방법.

### 청구항 17

제 16항에 있어서,

상기 플랫폼 범핑 하지 금속 및 상기 플랫폼 정렬 마크는 동시에 형성되는 것을 특징으로 하는 광 소자의 제조 방법.

#### 청구항 18

제 16항에 있어서,

상기 칩 범핑 하지 금속 및 상기 칩 정렬 마크는 동시에 형성되는 것을 특징으로 하는 광 소자의 제조 방법.

### 청구항 19

제 16항에 있어서.

상기 플랫폼 범핑 하지 금속 및 상기 칩 범핑 하지 금속 중 적어도 하나 상에 솔더 필름을 형성하는 단계를 더 포함하는 것을 특징으로 하는 광 소자의 제조 방법.

## 청구항 20

제 19항에 있어서,

상기 플랫폼 범핑 하지 금속 및 상기 칩 범핑 하지 금속 상에 각각 상기 솔더 필름을 형성하는 것을 특징으로 하는 광 소자의 제조 방법.

### 명 세 서

[0001]

### 발명의 상세한 설명

#### 기 술 분 야

본 발명은 광 소자 및 그 제조 방법에 관한 것으로, 더 구체적으로 레이저 다이오드 및 포토 다이오드 등과 같은 광 능동 칩과 광 도파로가 집적된 평면광회로 플랫폼이 이종 결합된 광 소자 및 그 제조 방법에 관한 것이다. [0002] 본 발명은 지식경제부의 IT성장동력기술개발사업의 일환으로 수행한 연구로부터 도출된 것이다[과제관리번호: 2007-S-011-03, 과제명: ROADM용 광스위치 기술개발].

## 배경기술

- [0003] 대용량의 데이터(data)를 초고속 및 효과적으로 전송하기 위한 광 네트워크(optical network)에서, 광원, 광 검 출 및 광 증폭 기능을 수행하는 광 능동(optical active) 소자와 광 파장분할 및 광 분합이 가능한 광 도파로 (light waveguide)를 집적하여 광 송수신 및 광 증폭 모듈(module)을 저가로 구현하는 기술이 필수적이다.

- [0004] 이러한 집적화 기술에는 광 능동 소자와 광 도파로를 단일 물질인 광 반도체로 구현 및 집적하는 단일 집적 (monolithic integration) 기술 및 광 능동 소자를 이종의 평면광회로(Planar Lightwave Circuit : PLC) 플랫폼(platform)에 플립칩 본딩(Flip Chip bonding : F/C bonding)을 이용하여 집적하는 평면광회로 하이브리드 (hybrid) 집적 기술로 구분된다.

- [0005] 단일 집적 기술은 각 광 소자를 단일 기판에 집적했을 때, 각 광 소자의 최적화(optimization), 재현성 (reproducibility) 및 생산 수율(productivity) 문제로 인하여 저가의 광 송수신 모듈 구현에 제약이 있다. 반면에, 평면광회로 하이브리드 집적 기술은 최적의 성능을 갖는 광 능동 소자를 광 도파 및 파장분할 다중화 (Wavelength Division Multiplexing: WDM) 필터(filter) 기능을 포함하는 평면광회로 플랫폼에 하이브리드 집 적함으로써, 생산 수율을 높일 수 있기 때문에, 광 송수신 및 광 증폭 모듈을 저가로 구현할 수 있는 핵심기술로 주목받고 있다.

- [0006] 평면광 회로 플랫폼은 기존의 광 도파로 제작 기술과, 식각(Etching) 및 금속 증착 등과 같은 플랫폼 후공정으로 쉽게 제작 가능하다. 따라서, 광 능동 소자인 반도체 칩과 광 도파로가 집적된 평면광회로 플랫폼 사이의 광 결합(optical coupling) 효율이 하이브리드 집적된 소자의 성능을 좌우하기 때문에, 상호 정렬 정밀도를 높일수 있는 플립칩 본딩 구조 및 방법이 필수적이다.

## 발명의 내용

### 해결 하고자하는 과제

- [0007] 본 발명이 해결하고자 하는 과제는 광 도파로 플랫폼에 광 능동 칩을 본딩할 때, 정렬 정밀도를 높여 광 결합 효율을 향상시킬 수 있는 광 소자를 제공하는 데 있다.

- [0008] 본 발명이 해결하고자 하는 다른 과제는 광 도파로 플랫폼에 광 능동 칩을 본딩할 때, 정렬 정밀도를 높여 광 결합 효율을 향상시킬 수 있는 광 소자의 제조 방법을 제공하는 데 있다.

- [0009] 본 발명이 해결하고자 하는 과제는 이상에서 언급한 과제에 제한되지 않으며, 언급되지 않은 또 다른 과제들은 아래의 기재로부터 당업자에게 명확하게 이해될 수 있을 것이다.

## 과제 해결수단

- [0010] 상기한 과제를 달성하기 위하여, 본 발명은 광 소자를 제공한다. 이 광 소자는 도파로 영역 및 실장 영역을 갖는 기판, 기판의 도파로 영역 상에 제공된 하부 클래드층 및 상부 클래드층, 및 이들 사이에 개재된 플랫폼 코어로 구성된 광 도파로, 기판의 실장 영역 상에 하부 클래드층이 식각되어 형성되되, 트렌치를 갖는 테라스, 기판의 실장 영역 상에서 테라스 주변의 하부 클래드층이 식각된 표면 상에 제공된 플랫폼 범핑 하지 금속(Under Bump Metallurgy: UBM), 기판의 실장 영역에 실장되되, 내부에 칩 코어를 갖는 광 능동 칩, 광 능동 칩의 실장면에 제공된 칩 범핑 하지 금속 및 칩 정렬 마크, 및 플랫폼 범핑 하지 금속 및 칩 범핑 하지 금속을 전기적으로 연결하는 솔더 필름을 포함할 수 있다. 광 능동 칩은 테라스의 트렌치와 광 능동 칩의 칩 정렬 마크와의 인터로킹(interlocking)에 의해 정렬되어 실장 영역 상에 실장되는 것을 특징으로 할 수 있다.

- [0011] 테라스의 트렌치의 내주면과 광 능동 칩의 칩 정렬 마크의 외주면 사이의 간격은 약 1~2 μm 범위일 수 있다.

- [0012] 솔더 필름의 두께는 2~8 μm 범위일 수 있다.

- [0013] 솔더 필름은 AuSn 솔더를 포함할 수 있다.

- [0014] 칩 정렬 마크 상에 제공되는 추가적인 솔더 필름을 더 포함할 수 있다.

- [0015] 광 도파로와 광 능동 칩 사이의 거리는 2.5~20 µm 범위일 수 있다.

- [0016] 또한, 본 발명은 다른 광 소자를 제공한다. 이 광 소자는 도파로 영역 및 실장 영역을 갖는 기판, 기판의 도파로 영역 상에 제공된 하부 클래드층 및 상부 클래드층, 및 이들 사이에 개재된 플랫폼 코어로 구성된 광도파로, 기판의 실장 영역 상에 하부 클래드층이 식각되어 형성된 테라스, 기판의 실장 영역 상에서 테라스 주변의 하부 클래드층이 식각된 표면 상에 제공된 플랫폼 범핑 하지 금속, 테라스의 상부면 상에 제공된 플랫폼 정렬 마크, 기판의 실장 영역에 실장되되, 내부에 칩 코어를 갖는 광 능동 칩, 광 능동 칩의 실장면에 제공된 칩 범핑 하지 금속 및 칩 정렬 마크, 및 플랫폼 범핑 하지 금속 및 칩 범핑 하지 금속을 전기적으로 연결하는 솔더 필름을 포함할 수 있다. 광 능동 칩은 테라스의 플랫폼 정렬 마크와 광 능동 칩의 칩 정렬 마크와의 인터로킹에 의해 정렬되어 실장 영역 상에 실장되는 것을 특징으로 할 수 있다.

- [0017] 테라스의 플랫폼 정렬 마크 및 광 능동 칩의 칩 정렬 마크는 각각 서로 대응되는 음각 및 양각의 모양을 가질 수 있다. 테라스의 플랫폼 정렬 마크와 광 능동 칩의 칩 정렬 마크 사이의 간격은 약 1~2 µm 범위일 수 있다.

- [0018] 솔더 필름의 두께는 2~8 μm 범위일 수 있다.

- [0019] 솔더 필름은 AuSn 솔더를 포함할 수 있다.

- [0020] 광 도파로와 광 능동 칩 사이의 거리는 2.5~20 µm 범위일 수 있다.

- [0021] 상기한 다른 과제를 달성하기 위하여, 본 발명은 광 소자의 제조 방법을 제공한다. 이 방법은 도파로 영역 및 실장 영역을 갖는 기판 상에 하부 클래드층, 플랫폼 코어 및 상부 클래드층을 순차적으로 형성하는 단계, 기판의 실장 영역 상의 상부 클래드층, 플랫폼 코어 및 하부 클래드층을 제 1 식각 공정으로 식각하여 도파로 영역에는 광 도파로를 형성하고, 그리고 실장 영역에는 제 1 높이의 하부 클래드층을 형성하는 단계, 기판의 실장 영역 상의 제 1 높이의 하부 클래드층을 제 2 식각 공정으로 식각하여 트렌치를 갖는 제 1 높이의 테라스 및 제 2 높이의 하부 클래드층을 형성하는 단계, 기판의 실장 영역 상의 테라스 주변의 제 2 높이의 하부 클래드층 상에 플랫폼 범핑 하지 금속을 형성하는 단계, 내부에 칩 코어를 갖는 광 능동 칩의 실장면 상에 칩 범핑 하지 금속을 형성하는 단계, 광 능동 칩의 실장면 상에 칩 정렬 마크를 형성하는 단계, 플랫폼 범핑 하지 금속 및 칩 범핑 하지 금속이 울더 필름을 형성하는 단계, 및 기판의 실장 영역 상에 플랫폼 범핑 하지 금속 및 칩 범핑 하지 금속이 울더 필름에 의해 전기적으로 연결되도록 광 능동 칩을 실장하는 단계를 포함할수 있다. 광 능동 칩은 테라스의 트렌치와 광 능동 칩의 칩 정렬 마크와의 인터로킹에 의해 정렬되어 실장 영역 상에 실장되는 것을 특징으로 할 수 있다.

- [0022] 테라스의 트렌치의 내주면과 광 능동 칩의 칩 정렬 마크의 외주면 사이의 간격은 약 1~2 μm 범위일 수 있다.

- [0023] 플랫폼 범핑 하지 금속 및 칩 범핑 하지 금속 상에 각각 솔더 필름을 형성할 수 있다. 솔더 필름의 두께는 1~4  $\mu$ m 범위를 갖도록 형성될 수 있다.

- [0024] 솔더 필름은 AuSn 솔더로 형성될 수 있다.

- [0025] 칩 범핑 하지 금속 및 칩 정렬 마크는 동시에 형성될 수 있다.

- [0026] 칩 정렬 마크 상에 추가적인 솔더 필름을 형성하는 단계를 더 포함할 수 있다.

- [0027] 광 도파로와 광 능동 칩 사이의 거리는 2.5~20 μm 범위일 수 있다.

- [0028] 또한, 본 발명은 다른 광 소자의 제조 방법을 제공한다. 이 방법은 도파로 영역 및 실장 영역을 갖는 기판 상에 하부 클래드층, 플랫폼 코어 및 상부 클래드층을 순차적으로 형성하는 단계, 기판의 실장 영역 상의 상부 클래드층, 플랫폼 코어 및 하부 클래드층을 제 1 식각 공정으로 식각하여 도파로 영역에는 광 도파로를 형성하고, 그리고 실장 영역에는 제 1 높이의 하부 클래드층을 형성하는 단계, 기판의 실장 영역 상의 제 1 높이의 하부 클래드층을 형성하는 단계, 기판의 실장 영역 상의 테라스 주변의 제 2 높이의 해부 클래드층 상에 플랫폼 범핑 하지 금속을 형성하는 단계, 기판의 실장 영역 상의 테라스 주변의 제 2 높이의 하부 클래드층 상에 플랫폼 범핑 하지 금속을 형성하는 단계, 기판의 실장 영역 상의 테라스의 상부면 상에 플랫폼 정렬 마크를 형성하는 단계, 내부에 칩 코어를 갖는 광 능동 칩의 실장면 상에 칩 범핑 하지 금속을 형성하는 단계, 광 능동 칩의 실장면 상에 칩 정렬 마크를 형성하는 단계, 필랫폼 범핑 하지 금속 및 칩 범핑 하지 금속이 솔더 필름에 의해 전기적으로 연결되도록 광 능동 칩을 실장하는 단계를 포함할 수 있다. 광 능동 칩은 테라스의 플랫폼 정렬 마크와 광 능동 칩의 칩 정렬 마크와의 인터로킹에 의해 정렬되어 실장 영역 상에 실장되는 것을 특징으로 할 수 있다.

- [0029] 테라스의 플랫폼 정렬 마크 및 광 능동 칩의 칩 정렬 마크는 각각 서로 대응되는 음각 및 양각의 모양을 갖도록

형성될 수 있다. 테라스의 플랫폼 정렬 마크와 광 능동 칩의 칩 정렬 마크 사이의 간격은 약  $1\sim2\,\mu\mathrm{m}$  범위일 수 있다.

- [0030] 플랫폼 범핑 하지 금속 및 칩 범핑 하지 금속 상에 각각 솔더 필름을 형성할 수 있다. 솔더 필름의 두께는 1~4 μm 범위를 갖도록 형성될 수 있다.

- [0031] 솔더 필름은 AuSn 솔더로 형성될 수 있다.

- [0032] 플랫폼 범핑 하지 금속 및 플랫폼 정렬 마크는 동시에 형성될 수 있다.

- [0033] 칩 범핑 하지 금속 및 칩 정렬 마크는 동시에 형성될 수 있다.

- [0034] 광 도파로와 광 능동 칩 사이의 거리는 2.5~20 µm 범위일 수 있다.

### 直 과

- [0035] 상술한 바와 같이, 본 발명의 과제 해결 수단들에 따르면 광 소자의 평면광회로 플랫폼과 광 능동 칩이 서로 인터로킹을 이용하여 플립칩 본딩되는 구조를 가짐으로써, 솔더의 자기정렬을 이용하기 위해 수십 μm 이상의 솔더 범프를 사용하는 종래와는 달리, 수 μm의 솔더 필름이 사용될 수 있다. 이에 따라, 고가의 솔더 형성 공정비용을 줄일 수 있는 장점이 있다. 또한, 평면광회로 플랫폼 및 광 능동 칩 양 쪽에 각각의 솔더 필름이 형성됨으로써, 각각의 솔더 필름의 두께가 더 얇아질 수 있다. 이에 따라, 솔더 형성 공정 비용이 추가적으로 절감될수 있다.

- [0036] 또한, 본 발명의 과제 해결 수단들에 따르면 광 소자의 평면광회로 플랫폼에 광 능동 칩과의 인터로킹을 위한 구조를 형성하기 위한 추가적인 공정이 필요하지 않기 때문에, 기존의 평면광회로 플랫폼 형성 공정이 그대로 이용될 수 있다. 이에 따라, 평면광회로 플랫폼에 광 능동 칩과의 인터로킹을 위한 구조가 쉽게 구현될 수 있는 동시에, 추가적인 공정 비용이 소요되지 않는 장점이 있다.

- [0037] 이에 더하여, 본 발명의 과제 해결 수단들에 따르면 광 소자의 평면광회로 플랫폼과 광 능동 칩이 서로 인터로 킹을 이용하여 플립칩 본딩되는 구조를 가짐으로써, 솔더 필름이 용용될 때 발생할 수 있는 비정렬이 2 μm 이내로 제한될 수 있다. 이에 따라, 평면광회로 플랫폼과 광 능동 칩 사이의 광 결합 효율이 향상될 수 있을 뿐만 아니라, 플립칩 본딩에 의한 수율이 극대화될 수 있는 장점이 있다.

- [0038] 결과적으로, 본 발명의 과제 해결 수단들에 따른 광 소자는 평면광회로 하이브리드 집적 기술을 이용한 광 모듈의 상용화에 걸림돌(bottleneck)이었던 솔더 형성 공정 비용이 줄어들 수 있을 뿐만 아니라, 플립칩 본딩에 의한 수율 및 플립칩 본딩으로 인한 광 결합 효율이 향상될 수 있다. 이에 따라, 본 발명의 과제 해결 수단들에 따른 광 소자는 광 송수신 모듈 및 광 증폭 모듈의 대량 생산시, 궁극적으로 생산 수율 향상 및 광 모듈의 저가 격화에 기여할 수 있다.

## 발명의 실시를 위한 구체적인 내용

- [0039] 이하, 첨부된 도면들을 참조하여 본 발명의 바람직한 실시예를 상세히 설명하기로 한다. 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면들과 함께 상세하게 후술되어 있는 실시예를 참조하면 명확해질 것이다. 그러나 본 발명은 여기서 설명되는 실시예에 한정되는 것이 아니라 서로 다른 형태로 구체화될 수도 있다. 오히려, 여기서 소개되는 실시예는 개시된 내용이 철저하고 완전해질 수 있도록 그리고 당업자에게 본 발명의 사상이 충분히 전달될 수 있도록 하기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될뿐이다. 명세서 전문에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

- [0040] 본 명세서에서 사용된 용어는 실시예들을 설명하기 위한 것이며 본 발명을 제한하고자 하는 것은 아니다. 본 명세서에서, 단수형은 문구에서 특별히 언급하지 않는 한 복수형도 포함한다. 명세서에서 사용되는 '포함한다 (comprises)' 및/또는 '포함하는(comprising)'은 언급된 구성요소, 단계, 동작 및/또는 소자는 하나 이상의 다른 구성요소, 단계, 동작 및/또는 소자의 존재 또는 추가를 배제하지 않는다. 또한, 바람직한 실시예에 따른 것이기 때문에, 설명의 순서에 따라 제시되는 참조 부호는 그 순서에 반드시 한정되지는 않는다. 이에 더하여, 본명세서에서, 어떤 막이 다른 막 또는 기판 상에 있다고 언급되는 경우에 그것은 다른 막 또는 기판 상에 직접형성될 수 있거나 또는 그들 사이에 제 3의 막이 개재될 수도 있다는 것을 의미한다.

- [0041] 또한, 본 명세서에서 기술하는 실시예들은 본 발명의 이상적인 예시도인 단면도 및/또는 평면도들을 참고하여 설명될 것이다. 도면들에 있어서, 막 및 영역들의 두께는 기술적 내용의 효과적인 설명을 위해 과장된 것이다.

따라서, 제조 기술 및/또는 허용 오차 등에 의해 예시도의 형태가 변형될 수 있다. 따라서, 본 발명의 실시예들은 도시된 특정 형태로 제한되는 것이 아니라 제조 공정에 따라 생성되는 형태의 변화도 포함하는 것이다. 예를 들면, 직각으로 도시된 식각 영역은 라운드지거나 소정 곡률을 가지는 형태일 수 있다. 따라서, 도면에서 예시된 영역들은 개략적인 속성을 가지며, 도면에서 예시된 영역들의 모양은 소자의 영역의 특정 형태를 예시하기위한 것이며 발명의 범주를 제한하기 위한 것이 아니다.

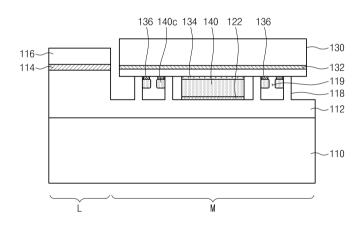

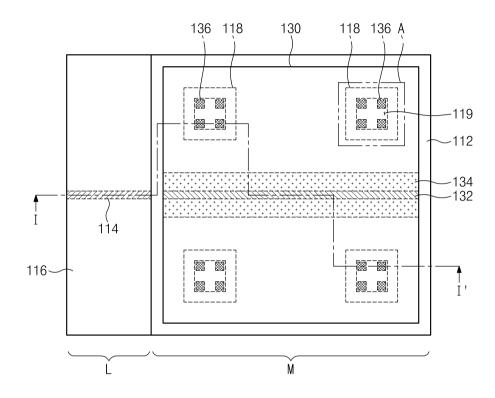

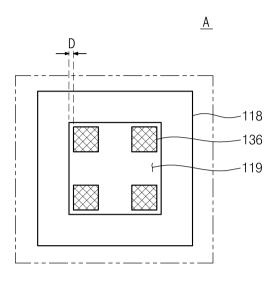

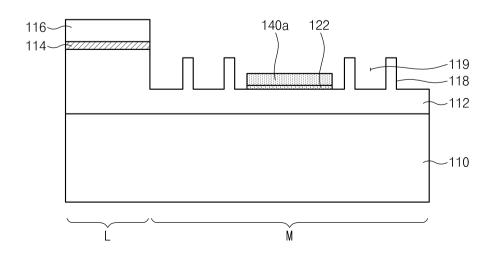

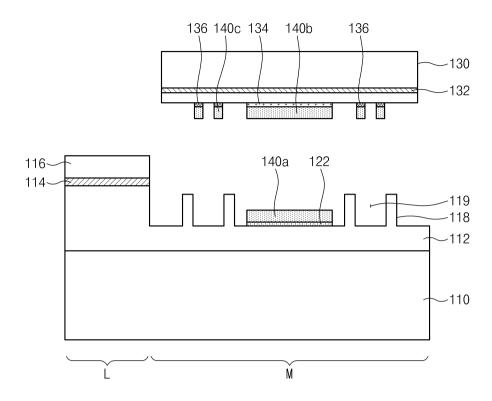

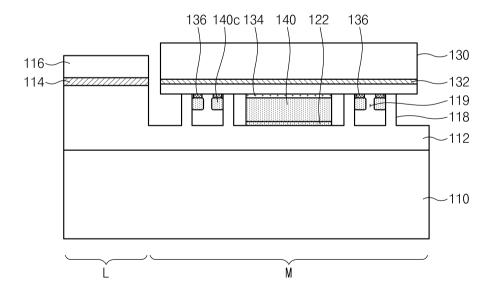

- [0042] 도 1a는 본 발명의 실시예에 따른 광 소자를 설명하기 위한 평면도이고, 도 1b는 도 1a의 I-I' 선을 따라 절단한 단면도, 그리고 도 1c는 도 1a의 A 부분을 확대한 평면도이다.

- [0043] 도 1a 내지 도 1c를 참조하면, 광 소자는 광 도파로 영역(L) 및 실장 영역(M)을 갖는 평면광회로 플랫폼, 및 이 의 실장 영역(M)에 실장된 광 능동 칩(130)을 포함할 수 있다.

- [0044] 평면광회로 플랫폼은 기판(110)을 포함할 수 있다. 기판(110)은 실리콘(Si) 기판일 수 있다.

- [0045] 평면광회로 플랫폼의 광 도파로 영역(L)에는 하부 클래드층(lower clad layer, 112), 평면광회로 (플랫폼) 코어 (PLC (platform) core, 114) 및 상부 클래드층(upper clad layer, 116)으로 구성된 광 도파로가 제공될 수 있다. 하부 클래드층(112), 평면광 회로 코어(114) 및 상부 클래드층(116)은 실리카(silica)를 포함할 수 있다. 이에 따라, 광 도파로는 실리카 광 도파로일 수 있다.

- [0046] 평면광회로 플랫폼의 실장 영역(M)에는 하부 클래드층(112)이 식각(etching)되어 형성된 트렌치(119)를 갖는 테라스(terrace, 118)가 제공될 수 있다. 평면광회로 플랫폼의 실장 영역(M)의 테라스(118) 주변의 하부 클래드층 (112) 상에 플랫폼 범핑 하지 금속(Under Bump Metallurgy: UBM, 122)이 제공될 수 있다. 플랫폼 범핑 하지 금속(122)은 Cr/Ni/Au, NiCr/Ni/Au, Ti/Ni/Au, Cr/Pt/Au, NiCr/Pt/Au 또는 Ti/Pt/Au 등으로 이루어진 3중막, 또는 Ni/Au 등으로 이루어진 2중막을 포함할 수 있다.

- [0047] 광 능동 칩(130)은 내부에 칩 코어(chip core, 132)을 포함할 수 있다. 광 능동 칩(130)은 레이저 다이오드 (laser diode) 및 포토 다이오드(photodiode) 등일 수 있다. 광 능동 칩(130)의 실장면에는 칩 범핑 하지 금속 (134) 및 칩 정렬 마크(alignment mark, 136)가 제공될 수 있다. 칩 범핑 하지 금속(134)은 Cr/Ni/Au, NiCr/Ni/Au, Ti/Ni/Au, Cr/Pt/Au, NiCr/Pt/Au 또는 Ti/Pt/Au 등으로 이루어진 3중막, 또는 Ni/Au 등으로 이루 어진 2중막을 포함할 수 있다. 칩 정렬 마크(136)는 칩 범핑 하지 금속(134)과 동일한 물질을 포함할 수 있다.

- [0048] 평면광회로 플랫폼의 실장 영역(M)에 광 능동 칩(130)이 실장되는 것은 플립칩 본딩을 이용하는 것일 수 있다. 즉, 평면광회로 플랫폼의 실장 영역(M)에 광 능동 칩(130)이 실장되는 것은 솔더 필름(solder film, 140)에 의해 플랫폼 범핑 하지 금속(122) 및 칩 범핑 하지 금속(134)이 전기적으로 연결되는 것일 수 있다. 솔더 필름(140)은 AuSn 솔더를 포함할 수 있다. 솔더 필름(140)의 두께는 2~8 μm 범위일 수 있다.

- [0049] 레이저 다이오드 및 포토 다이오드 등과 같은 광 능동 칩(130)의 칩 코어(132)는 실장면(p-side 표면)으로부터 2~5 µm 이내에 위치하기 때문에, 평면광회로 플랫폼의 실장 영역(M)이 깊게 식각될 필요가 없다. 따라서, 수 µ m의 두께를 갖는 솔더 필름(140)이 사용될 수 있다.

- [0050] 테라스(118)의 트렌치(119)의 내주면과 광 능동 칩(130)의 칩 정렬 마크(136)의 외주면은 서로 대응되는 형태를 가질 수 있다. 광 능동 칩(130)의 칩 정렬 마크(136)의 평단면이 폐도형이면, 테라스(118)의 트렌치(119)의 내주면의 평단면은 광 능동 칩(130)의 칩 정렬 마크(136)의 평단면보다 넓은 면적을 갖는 동일한 형태의 폐도형일수 있다. 이와는 달리, 도 1a 및 도 1c에 도시된 것과 같이, 광 능동 칩(130)의 칩 정렬 마크(136)가 복수의 패턴들로 이루어진 경우에는, 테라스(118)의 트렌치(119)의 내주면의 평단면은 복수의 패턴들에 접하도록 둘러싸는 외주면보다 넓은 면적을 갖는 동일한 형태의 폐도형일 수 있다.

- [0051] 광 능동 칩(130)은 테라스(118)의 트렌치(119)와 광 능동 칩(130)의 칩 정렬 마크(136) 사이의 인터로킹 (interlocking)에 의해 정렬되어 평면광회로 플랫폼의 실장 영역(M) 상에 실장될 수 있다. 이에 따라, 광 능동 칩(130)은 테라스(118)에 의해 수직 방향으로의 움직임이 정지되어 평면광회로 플랫폼에 수직 방향으로 정렬될 수 있으며, 그리고 테라스(118)의 트렌치(119)와 광 능동 칩(130)의 칩 정렬 마크(136)와의 인터로킹에 의해 수평 방향으로의 움직임이 정지되어 평면광회로 플랫폼에 수평 방향으로 정렬될 수 있다.

- [0052] 일반적으로, 상용화된 플립칩 본딩 장비의 정렬 정밀도는 약 1μm 정도이다. 이러한 플립칩 본딩 장비를 이용하여 광 능동 칩(130)과 평면광회로 플랫폼을 서로 정밀하게 정렬한 후, 일정한 하중을 가하여 광 능동 칩(130)과 평면광회로 플랫폼을 서로 접촉만 시킬때에는 플립칩 본딩 장비의 정렬 정밀도에 의해 정렬 정밀도가 결정된다. 하지만, 광 능동 칩(130)을 평면광회로 플랫폼에 실장하기 위해, 광 능동 칩(130)과 평면광회로 플랫폼 사이에

제공된 솔더 필름(140)을 용융시키기 위해 플립칩 본딩 장비의 온도를 높이게 되면, 광 능동 칩(130), 평면광회로 플랫폼 및 플립칩 본딩 장비 사이의 열 팽창 계수의 차이로 인해 솔더 필름(140)이 용융되는 동안 상당한 비정렬(misalignment)이 발생할 수 있다. 또한, 솔더 필름(140)이 용융될 때, 용융된 솔더의 양이 지나치게 많을 경우, 용융된 솔더에 의해 광 능동 칩(130)이 미끄러지는 문제가 발생할 수도 있다. 이에 따라, 수  $\mu$ m 이상의 비정렬이 발생할 수 있고, 이로 인해 광 결합 효율이 급격하게 저하되는 문제가 발생할 수 있다.

- [0053] 하지만, 본 발명의 실시예에 따른 광 소자는 테라스(118)의 트렌치(119)와 광 능동 칩(130)의 칩 정렬 마크 (136)와의 인터로킹에 의해 수평 방향으로의 움직임이 정지될 수 있기 때문에, 광 능동 칩(130)을 평면광회로 플랫폼에 실장하기 위해 솔더 필름(140)이 용유되는 동안 발생하는 비정렬이 최소화될 수 있다.

- [0054] 테라스(118)의 트렌치(119)의 내주면과 광 능동 칩(130)의 칩 정렬 마크(136)의 외주면 사이의 간격(D)은 약  $1\sim2\,\mu\mathrm{m}$  범위일 수 있다. 이에 따라, 광 능동 칩(130)을 평면광회로 플랫폼에 실장하기 위해 솔더 필름(140)이 용유되는 동안, 비정렬이 발생하더라도  $2\,\mu\mathrm{m}$  이내의 정렬 정밀도가 확보될 수 있다.

- [0055] 칩 정렬 마크(136) 상에 제공되는 추가적인 솔더 필름(140c)을 더 포함할 수 있다. 추가적인 솔더 필름(140c)은 테라스(118)의 트렌치(119)와 광 능동 칩(130)의 칩 정렬 마크(136) 사이의 인터로킹 구조를 위한 수직 방향으로의 높이 단차를 추가로 확보함과 동시에, 광 능동 칩(130)을 평면광회로 플랫폼에 실장하는 동안 추가적인 솔더 필름(140c)이 용용되어 테라스(118)의 트렌치(119)와의 밀착을 강화함으로써, 정렬 정밀도를 추가로 향상시키기 위한 것일 수 있다.

- [0056] 상기한 테라스(118)의 트렌치(119)와 광 능동 칩(130)의 칩 정렬 마크(136)와의 인터로킹에 의해 광 도파로와 광 능동 칩(130) 사이의 거리는 2.5~30 μm 범위일 수 있다. 바람직하게는, 본 발명의 실시예에 따른 광 소자의 광 도파로와 광 능동 칩(130) 사이의 거리는 2.5~20 μm 범위일 수 있다.

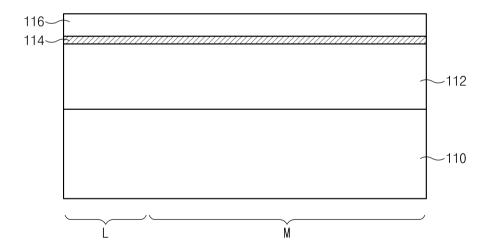

- [0057] 도 2a 내지 도 2f는 본 발명의 실시예에 따른 광 소자의 제조 방법을 설명하기 위해, 도 1a의 I-I' 선을 따라 절단한 공정 단면도들이다.

- [0058] 도 2a를 참조하면, 도파로 영역(L) 및 실장 영역(M)을 갖는 기판(110) 상에 하부 클래드층(112), 평면광회로 코어(114) 및 상부 클래드층(116)을 순차적으로 형성한다.

- [0059] 기판(110)은 실리콘 기판을 포함할 수 있다. 하부 클래드층(112), 평면광회로 코어(114) 및 상부 클래드층(116)은 실리카막으로 형성될 수 있다.

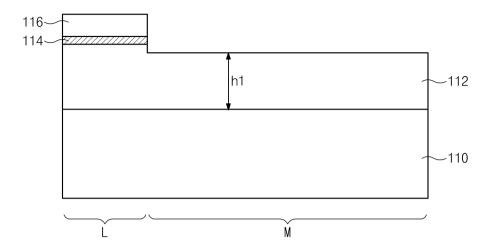

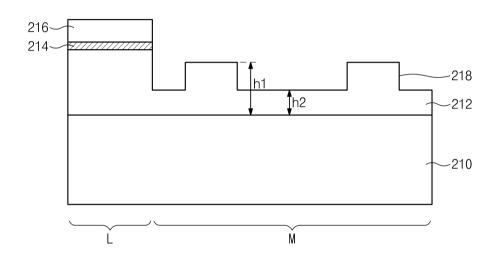

- [0060] 도 2b를 참조하면, 기판(110)의 실장 영역(M) 상의 상부 클래드층(116), 평면광회로 코어(114) 및 하부 클래드 층(112)을 제 1 식각 공정으로 식각하여, 도파로 영역(L)에는 하부 클래드층(112), 플랫폼 코어(114) 및 상부 클래드층(116)으로 구성된 광 도파로를 형성하고, 그리고 실장 영역(M)에는 제 1 높이(h1)의 하부 클래드층 (112)을 형성한다. 이에 따라, 광 도파로는 실리카 광 도파로일 수 있다.

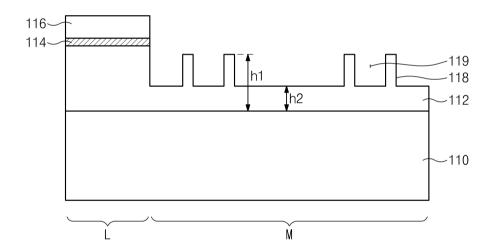

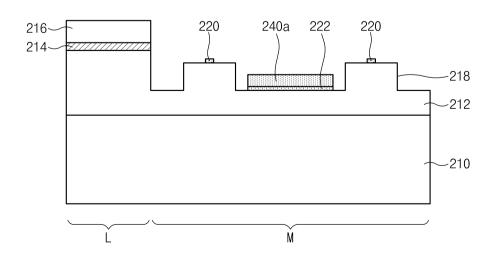

- [0061] 도 2c를 참조하면, 기판(110)의 실장 영역(M) 상의 제 1 높이(h1)의 하부 클래드층(112)을 제 2 식각 공정으로 식각하여 트렌치(119)를 갖는 제 1 높이(h1)의 테라스(118) 및 제 2 높이(h2)의 하부 클래드층(112)을 형성한다.

- [0062] 트렌치(119)는 제 1 높이(h1)의 테라스(118)를 형성하기 위한 제 2 식각 공정에 사용되는 포토마스크 패턴 (photomask pattern)의 모양을 단순히 변경하는 것에 의해, 제 1 높이(h1)의 테라스(118)와 동시에 형성될 수 있다. 따라서, 트렌치(119)를 형성하기 위한 추가적인 공정이 필요 없다.

- [0063] 도 2d를 참조하면, 기판(110)의 실장 영역(M) 상의 테라스(118) 주변의 제 2 높이(h2)의 하부 클래드층(112) 상에 플랫폼 범핑 하지 금속(122)을 형성한다.

- [0064] 플랫폼 범핑 하지 금속(122)은 Cr/Ni/Au, NiCr/Ni/Au, Ti/Ni/Au, Cr/Pt/Au, NiCr/Pt/Au 또는 Ti/Pt/Au 등으로 이루어진 3중막, 또는 Ni/Au 등으로 이루어진 2중막으로 형성될 수 있다.

- [0065] 이에 따라, 도파로 영역(L)에는 광 도파로가, 그리고 실장 영역(M)에는 트렌치(119)를 갖는 테라스(118)가 구비된 평면광회로 플랫폼이 형성될 수 있다.

- [0066] 플랫폼 범핑 하지 금속(122) 상에 플랫폼용 솔더 필름(140a)을 형성한다. 플랫폼용 솔더 필름(140a)은 AuSn 솔더를 포함할 수 있다. 플랫폼용 솔더 필름(140a)은 1~4μm 범위의 두께를 갖도록 형성될 수 있다. 만약, 광 능동 칩(도 2e의 130)의 실장면 상의 칩 범핑 하지 금속(도 2e의 134 참조) 상에 충분한 두께(2~8μm 범위)를 갖는 칩용 솔더 필름(도 2e의 140b 참조)이 형성될 경우, 플랫폼용 솔더 필름(140a)을 형성하는 것은 생략될 수

있다.

- [0067] 도 2e를 참조하면, 내부에 칩 코어(132)를 갖는 광 능동 칩(130)을 준비한다. 광 능동 칩(130)은 레이저 다이오 드 및 포토 다이오드 등일 수 있다.

- [0068] 광 능동 칩(130)의 실장면 상에 칩 범핑 하지 금속(134) 및 칩 정렬 마크(136)을 형성한다. 칩 범핑 하지 금속 (134) 및 칩 정렬 마크(136)는 Cr/Ni/Au, NiCr/Ni/Au, Ti/Ni/Au, Cr/Pt/Au, NiCr/Pt/Au 또는 Ti/Pt/Au 등으로 이루어진 3중막, 또는 Ni/Au 등으로 이루어진 2중막으로 형성될 수 있다. 칩 범핑 하지 금속(134) 및 칩 정렬 마크(136)는 서로 다른 공정 및 다른 물질로 각각 형성되거나, 또는 동일한 공정 및 동일한 물질로 동시에 형성될 수 있다.

- [0069] 테라스(118)의 트렌치(119)의 내주면과 광 능동 칩(130)의 칩 정렬 마크(136)의 외주면은 서로 대응되는 형태를 갖도록 형성될 수 있다. 광 능동 칩(130)의 칩 정렬 마크(136)의 평단면이 폐도형을 갖도록 형성되면, 테라스 (118)의 트렌치(119)의 내주면의 평단면은 광 능동 칩(130)의 칩 정렬 마크(136)의 평단면보다 넓은 면적을 갖는 동일한 형태의 폐도형을 갖도록 형성될 수 있다. 이와는 달리, 도시된 것과 같이, 광 능동 칩(130)의 칩 정렬 마크(136)가 복수의 패턴들로 형성된 경우에는, 테라스(118)의 트렌치(119)의 내주면의 평단면은 복수의 패턴들에 접하도록 둘러싸는 외주면보다 넓은 면적을 갖는 동일한 형태의 폐도형을 갖도록 형성될 수 있다. 테라스(118)의 트렌치(119)의 내주면과 광 능동 칩(130)의 칩 정렬 마크(136)의 외주면 사이의 간격(도 1c의 D참조)은 약 1~2 μm 범위일 수 있다.

- [0070] 칩 범핑 하지 금속(134) 상에 칩용 솔더 필름(140b)을 형성한다. 칩용 솔더 필름(140b)은 AuSn 솔더를 포함할 수 있다. 칩용 솔더 필름(140b)은 1~4 μm 범위의 두께를 갖도록 형성될 수 있다. 만약, 기판(110)의 실장 영역 (M) 상의 제 2 높이(h2)의 하부 클래드층(112) 상의 플랫폼 범핑 하지 금속(122) 상에 충분한 두께(2~8 μm 범위)를 갖는 플랫폼용 솔더 필름(140a)이 형성될 경우, 칩용 솔더 필름(140b)을 형성하는 것은 생략될 수 있다.

- [0071] 첩용 솔더 필름(140b)이 형성될 때, 첩 정렬 마크(136) 상에도 추가적인 솔더 필름(140c)이 형성될 수 있다. 추가적인 솔더 필름(140c)은 추후 광 능동 칩(130)을 평면광회로 플랫폼의 실장 영역(M)에 실장할 때(도 2f 참조), 테라스(118)의 트렌치(119)와 광 능동 칩(130)의 칩 정렬 마크(136) 사이의 인터로킹 구조를 위한 수직 방향으로의 높이 단차를 추가로 확보함과 동시에, 광 능동 칩(130)을 평면광회로 플랫폼에 실장하는 동안 추가적인 솔더 필름(140c)이 용융되어 테라스(118)의 트렌치(119)와의 밀착을 강화함으로써, 정렬 정밀도를 추가로 향상시키기 위한 것일 수 있다.

- [0072] 도 2f를 참조하면, 기판(110)의 실장 영역(M) 상에 플랫폼 범핑 하지 금속(122) 및 칩 범핑 하지 금속(134)이 솔더 필름(140)에 의해 전기적으로 연결되도록 광 능동 칩(130)을 실장한다.

- [0073] 앞서 설명된 것과 같이, 솔더 필름(140)은 플랫폼 범핑 하지 금속(122) 또는 칩 범핑 하지 금속(134) 상에 형성된 것이거나, 또는 플랫폼 범핑 하지 금속(122) 및 칩 범핑 하지 금속(134) 상에 각각 형성된 플랫폼용 솔더 필름(140a) 및 칩용 솔더 필름(140b)가 합쳐진 것일 수 있다.

- [0074] 광 능동 칩(130)은 테라스(118)의 트렌치(119)와 광 능동 칩(130)의 칩 정렬 마크(136)와의 인터로킹에 의해 정렬되어 평면광회로 플랫폼의 실장 영역(M) 상에 실장될 수 있다. 이에 따라, 광 능동 칩(130)은 테라스(118)에 의해 수직 방향으로의 움직임이 정지되어 평면광회로 플랫폼에 수직 방향으로 정렬될 수 있으며, 그리고 테라스(118)의 트렌치(119)와 광 능동 칩(130)의 칩 정렬 마크(136) 사이의 인터로킹에 의해 수평 방향으로의 움직임이 정지되어 평면광회로 플랫폼에 수평 방향으로 정렬될 수 있다.

- [0075] 일반적으로, 상용화된 플립칩 본딩 장비의 정렬 정밀도는 약 1 μm 정도이다. 이러한 플립칩 본딩 장비를 이용하여 광 능동 칩(130)과 평면광회로 플랫폼을 서로 정밀하게 정렬한 후, 일정한 하중을 가하여 광 능동 칩(130)과 평면광회로 플랫폼을 서로 접촉만 시킬때에는 플립칩 본딩 장비의 정렬 정밀도에 의해 정렬 정밀도가 결정된다. 하지만, 광 능동 칩(130)을 평면광회로 플랫폼에 실장하기 위해, 광 능동 칩(130)과 평면광회로 플랫폼 사이에 제공된 솔더 필름(140)을 용융시키기 위해 플립칩 본딩 장비의 온도를 높이게 되면, 광 능동 칩(130), 평면광회로 플랫폼 및 플립칩 본딩 장비 사이의 열 팽창 계수의 차이로 인해 솔더 필름(140)이 용융되는 동안 상당한 비 정렬이 발생할 수 있다. 또한, 솔더 필름(140)이 용융될 때, 용융된 솔더의 양이 지나치게 많을 경우, 용융된 솔더에 의해 광 능동 칩(130)이 미끄러지는 문제가 발생할 수도 있다. 이에 따라, 수 μm 이상의 비정렬이 발생할 수 있고, 이로 인해 광 결합 효율이 급격하게 저하되는 문제가 발생할 수 있다.

- [0076] 하지만, 본 발명의 실시예에 따른 광 소자는 테라스(118)의 트렌치(119)와 광 능동 칩(130)의 칩 정렬 마크

(136)와의 인터로킹에 의해 수평 방향으로의 움직임이 정지될 수 있기 때문에, 광 능동 칩(130)을 평면광회로 플랫폼에 실장하기 위해 솔더 필름(140)이 용융되는 동안 발생하는 비정렬이 최소화될 수 있다.

- [0077] 테라스(118)의 트렌치(119)의 내주면과 광 능동 칩(130)의 칩 정렬 마크(136)의 외주면 사이의 간격은 약 1~2 μ m 범위를 갖기 때문에, 광 능동 칩(130)을 평면광회로 플랫폼에 실장하기 위해 솔더 필름(140)이 용융되는 동안, 비정렬이 발생하더라도 2 μm 이내의 정렬 정밀도가 확보될 수 있다.

- [0078] 상기한 방법에 따라 제조된 광 소자는 테라스(118)의 트렌치(119)와 광 능동 칩(130)의 칩 정렬 마크(136)와의 인터로킹에 의해 광 도파로와 광 능동 칩(130) 사이의 거리가 2.5~30 μm 범위를 갖도록 제조될 수 있다. 바람직하게는, 본 발명의 실시예에 따른 광 소자의 광 도파로와 광 능동 칩(130) 사이의 거리는 2.5~20 μm 범위일 수 있다.

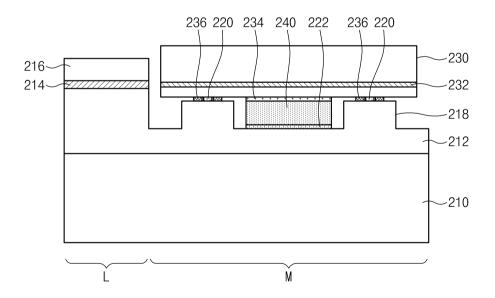

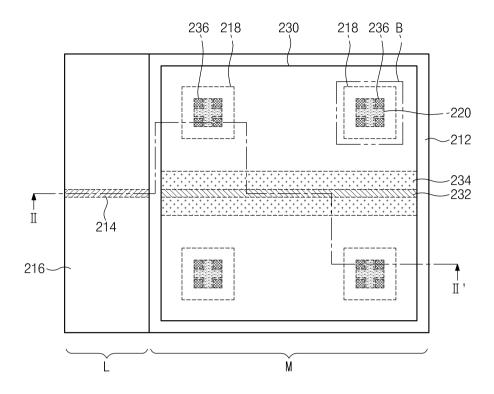

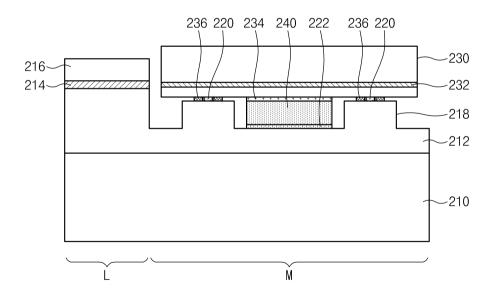

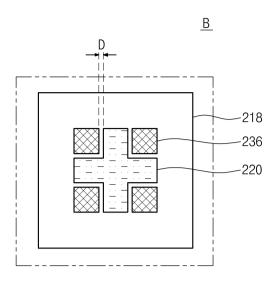

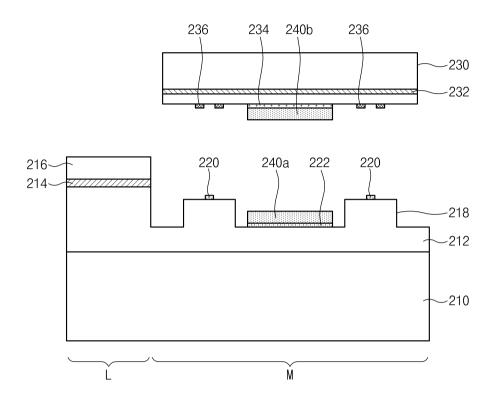

- [0079] 도 3a는 본 발명의 다른 실시예에 따른 광 소자를 설명하기 위한 평면도, 도 3b는 도 3a의 Ⅱ-Ⅱ' 선을 따라 절단한 단면도, 그리고 도 3c는 도 3a의 B 부분을 확대한 평면도이다.

- [0080] 도 3a 내지 도 3c를 참조하면, 광 소자는 광 도파로 영역(L) 및 실장 영역(M)을 갖는 평면광회로 플랫폼, 및 이 의 실장 영역(M)에 실장된 광 능동 칩(230)을 포함할 수 있다.

- [0081] 평면광회로 플랫폼은 기판(210)을 포함할 수 있다. 기판(210)은 실리콘 기판일 수 있다.

- [0082] 평면광회로 플랫폼의 광 도파로 영역(L)에는 하부 클래드층(212), 평면광 회로 코어(214) 및 상부 클래드층 (216)으로 구성된 광 도파로가 제공될 수 있다. 하부 클래드층(212), 평면광회로 코어(214) 및 상부 클래드층 (216)은 실리카를 포함할 수 있다. 이에 따라, 광 도파로는 실리카 광 도파로일 수 있다.

- [0083] 평면광회로 플랫폼의 실장 영역(M)에는 하부 클래드층(212)이 식각되어 형성된 테라스(218)가 제공될 수 있다. 평면광회로 플랫폼의 실장 영역(M)의 테라스(218) 주변의 하부 클래드층(212) 상에 플랫폼 범핑 하지 금속(22 2)이 제공될 수 있다. 플랫폼 범핑 하지 금속(222)은 Cr/Ni/Au, NiCr/Ni/Au, Ti/Ni/Au, Cr/Pt/Au, NiCr/Pt/Au 또는 Ti/Pt/Au 등으로 이루어진 3중막, 또는 Ni/Au 등으로 이루어진 2중막을 포함할 수 있다. 테라스(218)의 상부면 상에 플랫폼 정렬 마크(220)이 제공될 수 있다. 플랫폼 정렬 마크(220)는 플랫폼 범핑 하지 금속(222)과 동일한 물질을 포함할 수 있다.

- [0084] 광 능동 칩(230)은 내부에 칩 코어(232)을 포함할 수 있다. 광 능동 칩(230)은 레이저 다이오드 및 포토 다이오 드 등일 수 있다. 광 능동 칩(230)의 실장면에는 칩 범핑 하지 금속(234) 및 칩 정렬 마크(236)가 제공될 수 있다. 칩 범핑 하지 금속(234)은 Cr/Ni/Au, NiCr/Ni/Au, Ti/Ni/Au, Cr/Pt/Au, NiCr/Pt/Au 또는 Ti/Pt/Au 등으로 이루어진 3중막, 또는 Ni/Au 등으로 이루어진 2중막을 포함할 수 있다. 칩 정렬 마크(236)는 칩 범핑 하지 금속 (234)과 동일한 물질을 포함할 수 있다.

- [0085] 평면광회로 플랫폼의 실장 영역(M)에 광 능동 칩(230)이 실장되는 것은 플립칩 본딩을 이용하는 것일 수 있다. 즉, 평면광회로 플랫폼의 실장 영역(M)에 광 능동 칩(230)이 실장되는 것은 솔더 필름(240)에 의해 플랫폼 범핑하지 금속(222) 및 칩 범핑 하지 금속(234)이 전기적으로 연결되는 것일 수 있다. 솔더 필름(240)은 AuSn 솔더를 포함할 수 있다. 솔더 필름(240)의 두께는 2~8 μm 범위일 수 있다.

- [0086] 레이저 다이오드 및 포토 다이오드 등과 같은 광 능동 칩(230)의 칩 코어(232)는 실장면(p-side 표면)으로부터 2~5 µm 이내에 위치하기 때문에, 평면광회로 플랫폼의 실장 영역(M)이 깊게 식각될 필요가 없다. 따라서, 수 µ m의 두께를 갖는 솔더 필름(240)이 사용될 수 있다.

- [0087] 테라스(218)의 플랫폼 정렬 마크(220) 및 광 능동 칩(230)의 칩 정렬 마크(236)는 서로 대응되는 음각 및 양각의 모양을 가질 수 있다. 광 능동 칩(230)의 칩 정렬 마크(236)가 댐(dam) 형태의 폐도형이면, 테라스(218)의 플랫폼 정렬 마크(220)는 광 능동 칩(230)의 칩 정렬 마크(236)의 폐도형보다 좁은 또는 넓은 면적을 포함하는 동일한 형태의 폐도형일 수 있다. 이와는 달리, 도 3a 및 도 3c에 도시된 것과 같이, 광 능동 칩(230)의 칩 정렬 마크(236)가 복수의 패턴들로 이루어진 경우에는, 테라스(218)의 플랫폼 정렬 마크(220)는 복수의 패턴들 사이의 내부 공간을 채우는 다른 형태의 폐도형 또는 복수의 패턴들일 수 있다. 이와는 반대로, 테라스(218)의 플랫폼 정렬 마크(220)가 복수의 패턴들로 이루어진 경우에는, 광 능동 칩(230)의 칩 정렬 마크(236)는 복수의 패턴들 사이의 내부 공간을 채우는 다른 형태의 폐도형 또는 복수의 패턴들일 수 있다.

- [0088] 광 능동 칩(230)은 테라스(218)의 플랫폼 정렬 마크(220)와 광 능동 칩(230)의 칩 정렬 마크(236)와의 인터로킹에 의해 정렬되어 평면광회로 플랫폼의 실장 영역(M) 상에 실장될 수 있다. 이에 따라, 광 능동 칩(230)은 테라스(218)의 플랫폼 정렬 마크(220)와 광 능동 칩(230)의 칩 정렬 마크(236)와의 인터로킹에 의해 수직 및 수평

방향으로의 움직임이 정지되어 평면광회로 플랫폼에 수직 및 수평 방향으로 정렬될 수 있다.

- [0089] 일반적으로, 상용화된 플립칩 본딩 장비의 정렬 정밀도는 약 1μm 정도이다. 이러한 플립칩 본딩 장비를 이용하여 광 능동 칩(230)과 평면광회로 플랫폼을 서로 정밀하게 정렬한 후, 일정한 하중을 가하여 광 능동 칩(230)과 평면광회로 플랫폼을 서로 접촉만 시킬때에는 플립칩 본딩 장비의 정렬 정밀도에 의해 정렬 정밀도가 결정된다. 하지만, 광 능동 칩(230)을 평면광회로 플랫폼에 실장하기 위해, 광 능동 칩(230)과 평면광회로 플랫폼 사이에 제공된 솔더 필름(240)을 용융시키기 위해 플립칩 본딩 장비의 온도를 높이게 되면, 광 능동 칩(230), 평면광회로 플랫폼 및 플립칩 본딩 장비 사이의 열 팽창 계수의 차이로 인해 솔더 필름(240)이 용융되는 동안 상당한 비 정렬이 발생할 수 있다. 또한, 솔더 필름(240)이 용융될 때, 용융된 솔더의 양이 지나치게 많을 경우, 용융된 솔더에 의해 광 능동 칩(230)이 미끄러지는 문제가 발생할 수도 있다. 이에 따라, 수 μm 이상의 비정렬이 발생할 수 있고, 이로 인해 광 결합 효율이 급격하게 저하되는 문제가 발생할 수 있다.

- [0090] 하지만, 본 발명의 다른 실시예에 따른 광 소자는 테라스(218)의 플랫폼 정렬 마크(220)와 광 능동 칩(230)의 칩 정렬 마크(236)와의 인터로킹에 의해 수평 방향으로의 움직임이 정지될 수 있기 때문에, 광 능동 칩(230)을 평면광회로 플랫폼에 실장하기 위해 솔더 필름(240)이 용융되는 동안 발생하는 비정렬이 최소화될 수 있다.

- [0091] 테라스(218)의 플랫폼 정렬 마크(220)와 광 능동 칩(230)의 칩 정렬 마크(236) 사이의 간격(D)은 약 1~2 μm 범위일 수 있다. 이에 따라, 광 능동 칩(230)을 평면광회로 플랫폼에 실장하기 위해 솔더 필름(240)이 용융되는 동안, 비정렬이 발생하더라도 2 μm 이내의 정렬 정밀도가 확보될 수 있다.

- [0092] 상기한 테라스(218)의 플랫폼 정렬 마크(220)와 광 능동 칩(230)의 칩 정렬 마크(236) 사이의 인터로킹에 의해 광 도파로와 광 능동 칩(230) 사이의 거리는 2.5~30 μm 범위일 수 있다. 바람직하게는, 본 발명의 실시예에 따른 광 소자의 광 도파로와 광 능동 칩(230) 사이의 거리는 2.5~20 μm 범위일 수 있다.

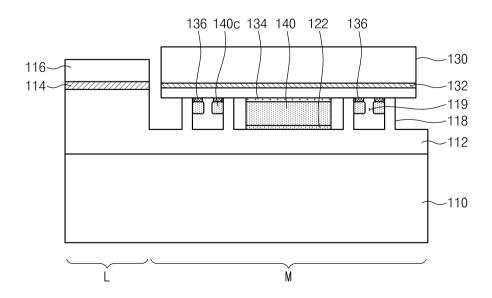

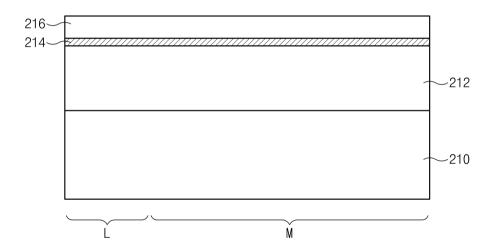

- [0093] 도 4a 내지 도 4f는 본 발명의 다른 실시예에 따른 광 소자의 제조 방법을 설명하기 위해, 도 3a의 Ⅱ-Ⅱ' 선을 따라 절단한 공정 단면도들이다.

- [0094] 도 4a를 참조하면, 도파로 영역(L) 및 실장 영역(M)을 갖는 기판(210) 상에 하부 클래드층(212), 평면광회로 코어(214) 및 상부 클래드층(216)을 순차적으로 형성한다.

- [0095] 기판(210)은 실리콘 기판을 포함할 수 있다. 하부 클래드층(212), 평면광 회로 코어(214) 및 상부 클래드층 (216)은 실리카막으로 형성될 수 있다.

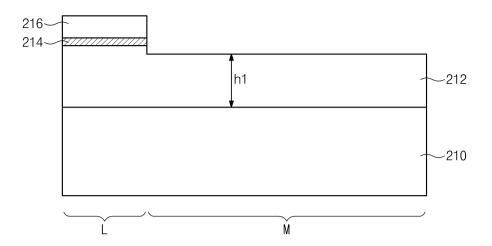

- [0096] 도 4b를 참조하면, 기판(210)의 실장 영역(M) 상의 상부 클래드충(216), 평면광회로 코어(214) 및 하부 클래드충(212)을 제 1 식각 공정으로 식각하여, 도파로 영역(L)에는 하부 클래드충(212), 플랫폼 코어(214) 및 상부 클래드충(216)으로 구성된 광 도파로를 형성하고, 그리고 실장 영역(M)에는 제 1 높이(h1)의 하부 클래드충(212)을 형성한다. 이에 따라, 광 도파로는 실리카 광 도파로일 수 있다.

- [0097] 도 4c를 참조하면, 기판(210)의 실장 영역(M) 상의 제 1 높이(h1)의 하부 클래드층(212)을 제 2 식각 공정으로 식각하여 제 1 높이(h1)의 테라스(218) 및 제 2 높이(h2)의 하부 클래드층(212)을 형성한다.

- [0098] 도 4d를 참조하면, 기판(210)의 실장 영역(M) 상의 테라스(218)의 상부면 및 테라스(218) 주변의 제 2 높이의 하부 클래드층(212) 상 각각에 플랫폼 정렬 마크(220) 및 플랫폼 범핑 하지 금속(222)을 형성한다.

- [0099] 플랫폼 정렬 마크(220) 및 플랫폼 범핑 하지 금속(222)은 Cr/Ni/Au, NiCr/Ni/Au, Ti/Ni/Au, Cr/Pt/Au, NiCr/Pt/Au 또는 Ti/Pt/Au 등으로 이루어진 3중막, 또는 Ni/Au 등으로 이루어진 2중막으로 형성될 수 있다. 플랫폼 정렬 마크(220) 및 플랫폼 범핑 하지 금속(222)은 서로 다른 공정 및 다른 물질로 각각 형성되거나, 또는 동일한 공정 및 동일한 물질로 동시에 형성될 수 있다.

- [0100] 플랫폼 정렬 마크(220)는 플랫폼 범핑 하지 금속(222)을 형성하기 위한 증착 및 패터닝 공정에서 동시에 형성될 수 있다. 따라서, 플랫폼 정렬 마크(220)를 형성하기 위한 추가적인 공정이 필요 없다.

- [0101] 이에 따라, 도파로 영역(L)에는 광 도파로가, 그리고 실장 영역(M)에는 플랫폼 정렬 마크(220)를 갖는 테라스 (218)가 구비된 평면광회로 플랫폼이 형성될 수 있다.

- [0102] 플랫폼 범핑 하지 금속(222) 상에 플랫폼용 솔더 필름(240a)을 형성한다. 플랫폼용 솔더 필름(240a)은 AuSn 솔더를 포함할 수 있다. 플랫폼용 솔더 필름(240a)은 1~4μm 범위의 두께를 갖도록 형성될 수 있다. 만약, 광 능동 칩(도 4e의 230)의 실장면 상의 칩 범핑 하지 금속(도 4e의 234 참조) 상에 충분한 두께(2~8μm 범위)를 갖는 칩용 솔더 필름(도 4e의 240b 참조)이 형성될 경우, 플랫폼용 솔더 필름(240a)을 형성하는 것은 생략될 수

있다.

- [0103] 도 4e를 참조하면, 내부에 칩 코어(232)를 갖는 광 능동 칩(230)을 준비한다. 광 능동 칩(230)은 레이저 다이오 드 및 포토 다이오드 등일 수 있다.

- [0104] 광 능동 칩(230)의 실장면 상에 칩 범핑 하지 금속(234) 및 칩 정렬 마크(236)을 형성한다. 칩 범핑 하지 금속(234) 및 칩 정렬 마크(236)는 Cr/Ni/Au, NiCr/Ni/Au, Ti/Ni/Au, Cr/Pt/Au, NiCr/Pt/Au 또는 Ti/Pt/Au 등으로 이루어진 3중막, 또는 Ni/Au 등으로 이루어진 2중막으로 형성될 수 있다. 칩 범핑 하지 금속(234) 및 칩 정렬 마크(236)는 서로 다른 공정 및 다른 물질로 각각 형성되거나, 또는 동일한 공정 및 동일한 물질로 동시에 형성될 수 있다.

- [0105] 테라스(218)의 플랫폼 정렬 마크(220) 및 광 능동 칩(230)의 칩 정렬 마크(236)는 서로 대응되는 음각 및 양각의 모양을 갖도록 형성될 수 있다. 광 능동 칩(230)의 칩 정렬 마크(236)가 댐 형태의 폐도형을 갖도록 형성되면, 테라스(218)의 플랫폼 정렬 마크(220)는 광 능동 칩(230)의 칩 정렬 마크(236)의 폐도형보다 좁은 또는 넓은 면적을 포함하는 동일한 형태의 폐도형을 갖도록 형성될 수 있다. 이와는 달리, 도시된 것과 같이, 광 능동칩(230)의 칩 정렬 마크(236)가 복수의 패턴들로 형성된 경우에는, 테라스(218)의 플랫폼 정렬 마크(220)는 복수의 패턴들 사이의 내부 공간을 채우는 다른 형태의 폐도형 또는 복수의 패턴들을 갖도록 형성될 수 있다. 이와는 반대로, 테라스(218)의 플랫폼 정렬 마크(220)가 복수의 패턴들로 형성된 경우에는, 광 능동칩(230)의 칩 정렬 마크(236)는 복수의 패턴들 사이의 내부 공간을 채우는 다른 형태의 폐도형 또는 복수의 패턴들로 형성될수 있다. 테라스(218)의 플랫폼 정렬 마크(220)와 광 능동칩(230)의 칩 정렬 마크(236) 사이의 간격(도 3c의 D참조)은 약 1~2 μm 범위일 수 있다.

- [0106] 칩 범핑 하지 금속(234) 상에 칩용 솔더 필름(240b)을 형성한다. 칩용 솔더 필름(240b)은 AuSn 솔더를 포함할 수 있다. 칩용 솔더 필름(240b)은 1~4 μm 범위의 두께를 갖도록 형성될 수 있다. 만약, 기판(210)의 실장 영역 (M) 상의 제 2 높이의 하부 클래드층(212) 상의 플랫폼 범핑 하지 금속(222) 상에 충분한 두께(2~8 μm 범위)를 갖는 플랫폼용 솔더 필름(240a)이 형성될 경우, 칩용 솔더 필름(240b)을 형성하는 것은 생략될 수 있다.

- [0107] 도 4f를 참조하면, 기판(210)의 실장 영역(M) 상에 플랫폼 범핑 하지 금속(222) 및 칩 범핑 하지 금속(234)이 솔더 필름(240)에 의해 전기적으로 연결되도록 광 능동 칩(230)을 실장한다.

- [0108] 앞서 설명된 것과 같이, 솔더 필름(240)은 플랫폼 범핑 하지 금속(222) 또는 칩 범핑 하지 금속(234) 상에 형성된 것이거나, 또는 플랫폼 범핑 하지 금속(222) 및 칩 범핑 하지 금속(234) 상에 각각 형성된 플랫폼용 솔더 필름(240a) 및 칩용 솔더 필름(240b)가 합쳐진 것일 수 있다.

- [0109] 광 능동 칩(230)은 테라스(218)의 플랫폼 정렬 마크(220)와 광 능동 칩(230)의 칩 정렬 마크(236) 사이의 인터로킹에 의해 정렬되어 평면광회로 플랫폼의 실장 영역(M) 상에 실장될 수 있다. 이에 따라, 광 능동 칩(230)은 테라스(218)의 플랫폼 정렬 마크(220)와 광 능동 칩(230)의 칩 정렬 마크(236)와의 인터로킹에 의해 수직 및 수평 방향으로의 움직임이 정지되어 평면광회로 플랫폼에 수직 및 수평 방향으로 정렬될 수 있다.

- [0110] 일반적으로, 상용화된 플립칩 본딩 장비의 정렬 정밀도는 약 1μm 정도이다. 이러한 플립칩 본딩 장비를 이용하여 광 능동 칩(230)과 평면광회로 플랫폼을 서로 정밀하게 정렬한 후, 일정한 하중을 가하여 광 능동 칩(230)과 평면광회로 플랫폼을 서로 접촉만 시킬때에는 플립칩 본딩 장비의 정렬 정밀도에 의해 정렬 정밀도가 결정된다. 하지만, 광 능동 칩(230)을 평면광회로 플랫폼에 실장하기 위해, 광 능동 칩(230)과 평면광회로 플랫폼 사이에 제공된 솔더 필름(240)을 용융시키기 위해 플립칩 본딩 장비의 온도를 높이게 되면, 광 능동 칩(230), 평면광회로 플랫폼 및 플립칩 본딩 장비 사이의 열 팽창 계수의 차이로 인해 솔더 필름(240)이 용융되는 동안 상당한 비 정렬이 발생할 수 있다. 또한, 솔더 필름(240)이 용융될 때, 용융된 솔더의 양이 지나치게 많을 경우, 용융된 솔더에 의해 광 능동 칩(230)이 미끄러지는 문제가 발생할 수도 있다. 이에 따라, 수 μm 이상의 비정렬이 발생할 수 있고, 이로 인해 광 결합 효율이 급격하게 저하되는 문제가 발생할 수 있다.

- [0111] 하지만, 본 발명의 다른 실시예에 따른 광 소자는 테라스(218)의 플랫폼 정렬 마크(220)와 광 능동 칩(230)의 칩 정렬 마크(236)와의 인터로킹에 의해 수평 방향으로의 움직임이 정지될 수 있기 때문에, 광 능동 칩(230)을 평면광회로 플랫폼에 실장하기 위해 솔더 필름(240)이 용융되는 동안 발생하는 비정렬이 최소화될 수 있다.

- [0112] 테라스(218)의 플랫폼 정렬 마크(220)와 광 능동 칩(230)의 칩 정렬 마크(236) 사이의 간격은 약 1~2 μm 범위를 갖기 때문에, 광 능동 칩(230)을 평면광회로 플랫폼에 실장하기 위해 솔더 필름(240)이 용융되는 동안, 비정렬이 발생하더라도 2 μm 이내의 정렬 정밀도가 확보될 수 있다.

- [0113] 상기한 방법에 따라 제조된 광 소자는 테라스(218)의 플랫폼 정렬 마크(220)와 광 능동 칩(230)의 칩 정렬 마크 (236)와의 인터로킹에 의해 광 도파로와 광 능동 칩(230) 사이의 거리가 2.5~30μm 범위를 갖도록 제조될 수 있다. 바람직하게는, 본 발명의 실시예에 따른 광 소자의 광 도파로와 광 능동 칩(230) 사이의 거리는 2.5~20μm 범위일 수 있다.

- [0114] 상기한 본 발명의 실시예들에 따른 광 소자들은 평면광회로 플랫폼과 광 능동 칩이 서로 인터로킹을 이용하여 플립칩 본딩되는 구조를 가짐으로써, 솔더의 자기정렬을 이용하기 위해 수십 μm 이상의 솔더 범프를 사용하는 종래와는 달리, 수 μm의 솔더 필름이 사용될 수 있다. 이에 따라, 고가의 솔더 형성 공정 비용을 줄일 수 있는 광 소자가 제공될 수 있다. 또한, 평면광회로 플랫폼 및 광 능동 칩 양 쪽에 각각의 솔더 필름이 형성됨으로써, 각각의 솔더 필름의 두께가 더 얇아질 수 있다. 이에 따라, 솔더 형성 공정 비용이 추가적으로 절감될 수 있는 광 소자가 제공될 수 있다.

- [0115] 또한, 본 발명의 실시예들에 따른 광 소자의 제조 방법들은 평면광회로 플랫폼에 광 능동 칩과의 인터로킹을 위한 구조를 형성하기 위한 추가적인 공정이 필요하지 않기 때문에, 기존의 평면광회로 플랫폼 형성 공정이 그대로 이용될 수 있다. 이에 따라, 평면광회로 플랫폼에 광 능동 칩과의 인터로킹을 위한 구조가 쉽게 구현될 수 있는 동시에, 추가적인 공정 비용이 소요되지 않을 수 있는 광 소자가 제공될 수 있다.

- [0116] 이에 더하여, 본 발명의 실시예들에 따른 광 소자들은 평면광회로 플랫폼과 광 능동 칩이 서로 인터로킹을 이용하여 플립칩 본딩되는 구조를 가짐으로써, 솔더 필름이 용용될 때 발생할 수 있는 비정렬이  $2\mu m$  이내로 제한될수 있다. 이에 따라, 평면광회로 플랫폼과 광 능동 칩 사이의 광 결합 효율이 향상될 수 있을 뿐만 아니라, 플립칩 본딩에 의한 수율이 극대화될 수 있는 광 소자가 제공될 수 있다.

- [0117] 결과적으로, 본 발명의 실시예들에 따른 광 소자들은 평면광회로 하이브리드 집적 기술을 이용한 광 모듈의 상용화에 걸림돌이었던 솔더 형성 공정 비용이 줄어들 수 있을 뿐만 아니라, 플립칩 본딩에 의한 수율 및 플립칩 본딩으로 인한 광 결합 효율이 향상될 수 있다. 이에 따라, 본 발명의 실시예들에 따른 광 소자들은 광 송수신 모듈 및 광 증폭 모듈의 대량 생산시, 궁극적으로 생산 수율 향상 및 광 모듈의 저가격화에 기여할 수 있다.

- [0118] 이상, 첨부된 도면을 참조하여 본 발명의 실시예를 설명하였지만, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자는 본 발명이 그 기술적 사상이나 필수적인 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시예에는 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해해야만 한다.

#### 도면의 간단한 설명

- [0119] 도 1a는 본 발명의 실시예에 따른 광 소자를 설명하기 위한 평면도;

- [0120] 도 1b는 도 1a의 I-I' 선을 따라 절단한 단면도;

- [0121] 도 1c는 도 1a의 A 부분을 확대한 평면도;

- [0122] 도 2a 내지 도 2f는 본 발명의 실시예에 따른 광 소자의 제조 방법을 설명하기 위해, I-I' 선을 따라 절단한 공정 단면도들;

- [0123] 도 3a는 본 발명의 다른 실시예에 따른 광 소자를 설명하기 위한 평면도;

- [0124] 도 3b는 도 3a의 Ⅱ-Ⅱ' 선을 따라 절단한 단면도;

- [0125] 도 3c는 도 3a의 B 부분을 확대한 평면도;

- [0126] 도 4a 내지 도 4f는 본 발명의 다른 실시예에 따른 광 소자의 제조 방법을 설명하기 위해, Ⅱ-Ⅱ' 선을 따라 절 단한 공정 단면도들.

- [0127] \*도면의 주요 부분에 대한 부호의 설명\*

- [0128] 110, 210 : 기판 112, 212 : 하부 클래드층

- [0129] 114, 214 : 평면광회로 코어 116, 216 : 상부 클래드층

- [0130] 118, 218 : 테라스 119 : 트렌치

- [0131] 122, 222 : 플랫폼 범핑 하지 금속 130, 230 : 광 능동 칩

[0132] 132. 232 : 칩 코어 134, 234 : 칩 범핑 하지 금속

[0133] 136, 236 : 칩 정렬 마크

[0134] 140, 140a, 140b, 240, 240a, 240b : 솔더 필름

[0135] 220 : 플랫폼 정렬 마크

## 도면

## 도면1a

## *도면1b*

# *도면1c*

# 도면2a

# 도면2b

# 도면2c

# *도면2d*

# 도면2e

# 도면2f

## 도면3a

# 도면3b

# 도면3c

# 도면4a

# *도면4b*

# 도면4c

# *도면4d*

# *도면4e*

# *도면4f*