(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6932056号

(P6932056)

(45) 発行日 令和3年9月8日(2021.9.8)

(24) 登録日 令和3年8月19日(2021.8.19)

(51) Int.CI.

HO2M 3/155 (2006.01)

F 1

HO2M 3/155

HO2M 3/155H

C

請求項の数 4 (全 11 頁)

(21) 出願番号 特願2017-196188 (P2017-196188)

(22) 出願日 平成29年10月6日 (2017.10.6)

(65) 公開番号 特開2019-71715 (P2019-71715A)

(43) 公開日 令和1年5月9日 (2019.5.9)

審査請求日 令和2年9月30日 (2020.9.30)

(73) 特許権者 715010864

エイブリック株式会社

東京都港区三田三丁目9番6号

(72) 発明者 高田 幸輔

千葉県千葉市美浜区中瀬1丁目8番地 エ

スアイアイ・セミコンダクタ株式会社内

審査官 遠藤 尊志

最終頁に続く

(54) 【発明の名称】スイッチングレギュレータ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の電源端子に供給される電源電圧から出力端子に所定の出力電圧を生成するスイッチングレギュレータであって、

一端が前記出力端子に接続されたインダクタと、

前記第1の電源端子と前記インダクタの他端との間に接続されたスイッチング素子と、

前記出力電圧に基づく電圧と第1の基準電圧との差を増幅し、第1の誤差電圧を出力する第1の誤差増幅回路と、

第1の入力ノードに入力される前記第1の誤差電圧と第2の入力ノードに入力される第2の基準電圧とに基づき出力ノードに第2の誤差電圧を生成するクランプ回路と、

第1の入力端子に入力される前記第2の誤差電圧と第2の入力端子に入力される前記第2の基準電圧とを比較し、第1のレベルまたは第2のレベルの比較結果信号を出力するP

F M 比較回路と、

前記比較結果信号が前記第1のレベルのとき所定周波数のクロック信号を出力し、前記比較結果信号が前記第2のレベルのとき前記クロック信号の出力を停止する発振回路と、

前記第2の誤差電圧と前記発振回路の出力とに基づいて前記スイッチング素子を所望のパルス幅でオン・オフするP W M 変換回路とを備え、

前記クランプ回路は、入力が前記第1の入力ノードに接続され、出力が前記出力ノードに接続されたバッファ回路と、

一端が前記出力ノードに接続され、定電圧を発生する定電圧発生部と、

10

20

前記定電圧発生部の他端の電圧と前記第2の基準電圧との差を増幅する第2の誤差増幅回路と、

第2の電源端子と前記第1の入力ノードとの間に接続され、ゲートが前記第2の誤差増幅回路の出力に接続されたMOSトランジスタとを有し、

前記第2の誤差電圧の下限値を前記第2の基準電圧の電圧値から前記定電圧を減算した電圧値にクランプすることを特徴とするスイッチングレギュレータ。

#### 【請求項2】

前記定電圧発生部は、前記第2の誤差増幅回路の前記定電圧発生部の他端の電圧が入力される端子と前記出力ノードとの間に接続されていることを特徴とする請求項1に記載のスイッチングレギュレータ。 10

#### 【請求項3】

前記定電圧発生部は、前記バッファ回路の出力と前記出力ノードとの間に接続されていることを特徴とする請求項1に記載のスイッチングレギュレータ。

#### 【請求項4】

前記バッファ回路は、ソースフォロワ回路で構成されていることを特徴とする請求項1乃至3のいずれか一項に記載のスイッチングレギュレータ。 20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、スイッチングレギュレータに関する。 20

##### 【背景技術】

##### 【0002】

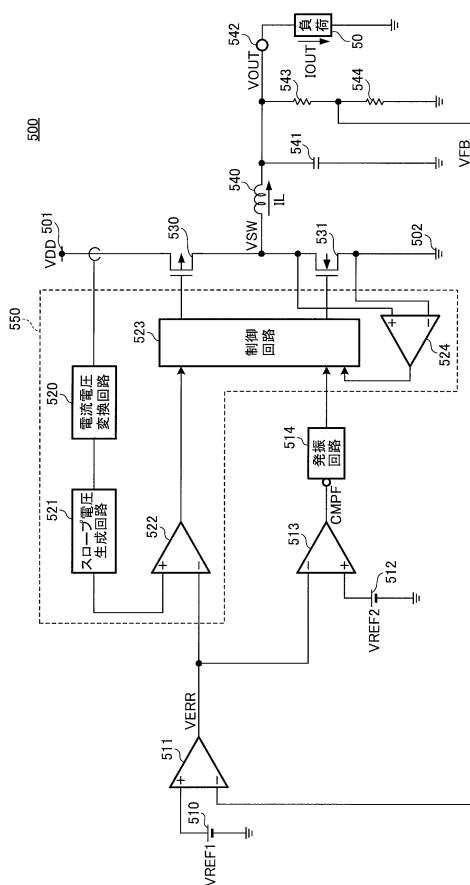

図5に、従来のスイッチングレギュレータ500の回路図を示す。

##### 【0003】

従来のスイッチングレギュレータ500は、電源端子501と、接地端子502と、基準電圧源510と、誤差増幅回路511と、基準電圧源512と、PFM比較回路513と、発振回路514と、PMOSトランジスタ530と、NMOSトランジスタ531と、インダクタ540と、容量541と、抵抗543及び544と、出力端子542と、電流電圧変換回路520、スロープ電圧生成回路521、PWM比較回路522、制御回路523、及び逆流検出回路524からなるPWM変換回路550とを備え、これらが図示のように接続されて構成されている（例えば、特許文献1参照）。 30

##### 【0004】

このような構成によって負帰還ループが機能し、スイッチングレギュレータ500は、出力端子542の電圧を抵抗543と抵抗544とで分圧した電圧VFBが基準電圧源510の基準電圧VREF1と等しくなるように動作して、出力端子542に所定の出力電圧VOOUTを生成する。

##### 【0005】

従来のスイッチングレギュレータ500では、PFM比較回路513が誤差増幅回路511の出力である誤差電圧VERRと基準電圧源512の基準電圧VREF2とを比較し、その出力である比較結果信号CMPFにより発振回路514をイネーブル又はディスエーブルさせてPWM動作とPFM動作を切り替える方式を採用することにより、出力端子542に接続される外部の負荷50に流れる負荷電流IOUTが小さいときにPFM動作に移行し、電力変換効率を向上させることを可能としている。 40

##### 【先行技術文献】

##### 【特許文献】

##### 【0006】

【特許文献1】特開2010-68671号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0007】

10

20

30

40

50

しかしながら、上記のような従来のスイッチングレギュレータ500では、PFM動作中に負荷電流I<sub>OUT</sub>が急増すると出力電圧V<sub>OUT</sub>が大きく低下するという課題があった。

#### 【0008】

この原因は、一般に、スイッチングレギュレータにおける誤差增幅回路のゲインは非常に大きく設定されることから、PFM動作中、誤差增幅回路511の出力である誤差電圧V<sub>ERR</sub>が0Vまで低下するためである。誤差電圧V<sub>ERR</sub>が0Vまで低下してしまうことから、誤差電圧V<sub>ERR</sub>が0Vから基準電圧V<sub>REF2</sub>を超えてPWM動作するまでに大幅な遅延が発生し、この間に出力電圧V<sub>OUT</sub>が大きく低下することとなる。

#### 【0009】

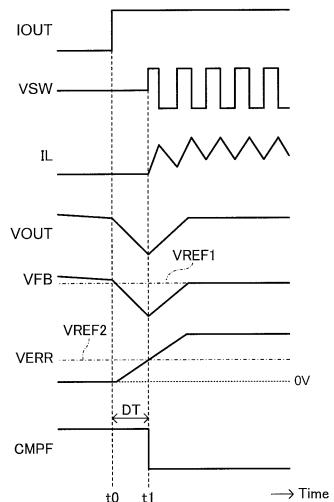

かかる原因について、以下、図6の波形図を用いて詳細に説明する。

#### 【0010】

図6は、従来のスイッチングレギュレータ500における負荷電流I<sub>OUT</sub>、PMOSトランジスタ530のドレインから出力される電圧V<sub>SW</sub>、インダクタ540に流れるインダクタ電流I<sub>L</sub>、出力電圧V<sub>OUT</sub>、電圧V<sub>FB</sub>、誤差電圧V<sub>ERR</sub>、比較結果信号CMPFの波形を示している。また、電圧V<sub>FB</sub>の波形に重ねて、基準電圧V<sub>REF1</sub>を一点差線で示し、誤差電圧V<sub>ERR</sub>の波形に重ねて、基準電圧V<sub>REF2</sub>を一点差線で、0Vを点線で示している。

#### 【0011】

時刻t0では、比較結果信号CMPFがハイレベルとなっており、スイッチングレギュレータ500は、PFM動作している。よって、PMOSトランジスタ530及びNMOSトランジスタ531は、スイッチング動作を停止してオフしている。この状態で、時刻t0において負荷電流I<sub>OUT</sub>が急増すると、これに従い、出力電圧V<sub>OUT</sub>が低下していく、電圧V<sub>FB</sub>も低下していく。そして、電圧V<sub>FB</sub>が基準電圧V<sub>REF1</sub>を下回ると、誤差電圧V<sub>ERR</sub>が0Vから上昇し始める。その後、時刻t1において、誤差電圧V<sub>ERR</sub>が基準電圧V<sub>REF2</sub>を上回ると、比較結果信号CMPFがローレベルに反転する。これにより、PMOSトランジスタ530及びNMOSトランジスタ531がスイッチング動作を開始し、インダクタ電流I<sub>L</sub>が流れ出力電圧V<sub>OUT</sub>が上昇に転じる。このように、時刻t0から時刻t1まで、すなわち、負荷電流I<sub>OUT</sub>が急増してからPMOSトランジスタ530及びNMOSトランジスタ531がスイッチング動作を開始するまでに遅延時間DTが発生する。したがって、出力電圧V<sub>OUT</sub>が大きく低下することとなる。

#### 【0012】

本発明は、以上のような課題を解決するためになされたものであり、PFM動作中に負荷電流が急増しても、出力電圧の大幅な低下を抑制することが可能なスイッチングレギュレータを提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0013】

本発明のスイッチングレギュレータは、電源端子に供給される電源電圧から出力端子に所定の出力電圧を生成するスイッチングレギュレータであって、一端が前記出力端子に接続されたインダクタと、前記電源端子と前記インダクタの他端との間に接続されたスイッチング素子と、前記出力電圧に基づく電圧と第1の基準電圧との差を増幅し、第1の誤差電圧を出力する第1の誤差増幅回路と、第1の入力ノードに入力される前記第1の誤差電圧と第2の入力ノードに入力される第2の基準電圧とに基づき出力ノードに第2の誤差電圧を生成するクランプ回路と、第1の入力端子に入力される前記第2の誤差電圧と第2の入力端子に入力される前記第2の基準電圧とを比較し、第1のレベルまたは第2のレベルの比較結果信号を出力するPFM比較回路と、前記比較結果信号が前記第1のレベルのとき所定周波数のクロック信号を出力し、前記比較結果信号が前記第2のレベルのとき前記クロック信号の出力を停止する発振回路と、前記第2の誤差電圧と前記発振回路の出力とに基づいて前記スイッチング素子を所望のパルス幅でオン・オフするPWM変換回路とを

10

20

30

40

50

備え、前記クランプ回路は、入力が前記第1の入力ノードに接続され、出力が前記出力ノードに接続されたバッファ回路と、一端が前記出力ノードに接続され、定電圧を発生する定電圧発生部と、前記定電圧発生部の他端の電圧と前記第2の基準電圧との差を増幅する第2の誤差増幅回路と、第2の電源端子と前記第1の入力ノードとの間に接続され、ゲートが前記第2の誤差増幅回路の出力に接続されたMOSトランジスタとを有し、前記第2の誤差電圧の下限値を前記第2の基準電圧の電圧値から前記定電圧を減算した電圧値にクランプすることを特徴とする。

#### 【発明の効果】

#### 【0014】

本発明のスイッチングレギュレータによれば、PFM比較回路の第1の入力端子に入力される第2の誤差電圧の下限値が第2の基準電圧の電圧値から所定の電圧値を減算した電圧値にクランプされる。すなわち、PFM比較回路の第1の入力端子に入力される電圧の下限値を0Vよりも第2の基準電圧に近い電圧に設定することができる。これにより、PFM動作中に負荷電流が急増した場合でもPFM動作からPWM動作へ短時間で移行できる。したがって、出力電圧が大幅に低下することを抑制することが可能となる。

10

#### 【図面の簡単な説明】

#### 【0015】

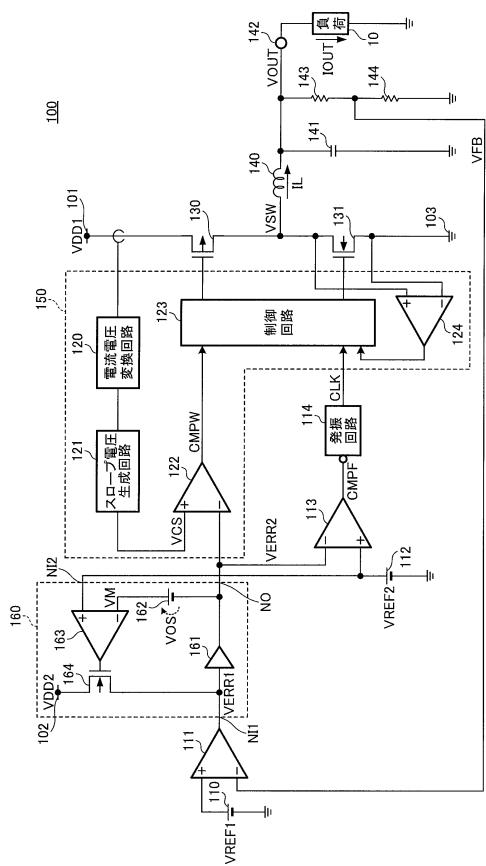

【図1】本発明の第1の実施形態のスイッチングレギュレータを示す回路図である。

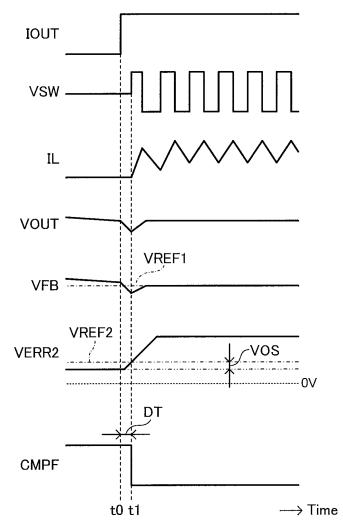

【図2】図1に示すスイッチングレギュレータの各ノードの信号波形を示す図である。

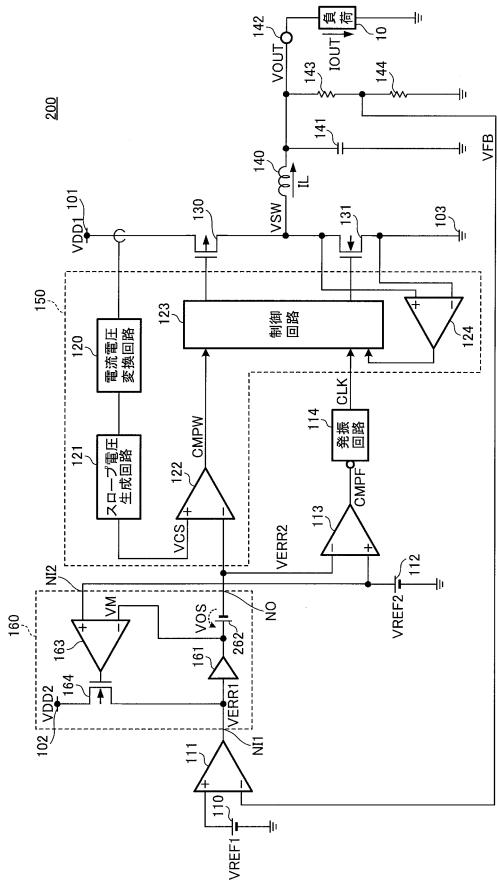

【図3】本発明の第2の実施形態のスイッチングレギュレータを示す回路図である。

20

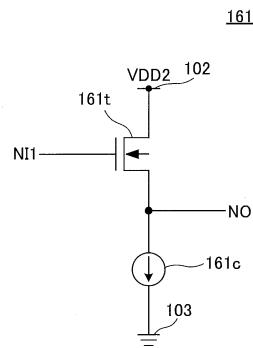

【図4】図1及び図2に示すバッファ回路の一具体例を示す回路図である。

【図5】従来のスイッチングレギュレータの回路図である。

【図6】図5のスイッチングレギュレータの各ノードの信号波形を示す図である。

#### 【発明を実施するための形態】

#### 【0016】

以下、本発明の実施形態について、図面を参照して説明する。

#### 【0017】

図1は、本発明の第1の実施形態のスイッチングレギュレータ100の回路図である。

#### 【0018】

本実施形態のスイッチングレギュレータ100は、電源電圧VDD1が供給される電源端子101と、電源電圧VDD2が供給される電源端子102と、接地端子103と、基準電圧源110と、誤差増幅回路111と、基準電圧源112と、PFM比較回路113と、発振回路114と、PMOSトランジスタ130（「スイッチング素子」ともいう）と、NMOSトランジスタ131（「同期整流素子」ともいう）と、インダクタ140と、容量141と、抵抗143及び144と、出力端子142と、電流電圧変換回路120、スロープ電圧生成回路121、PWM比較回路122、制御回路123、及び逆流検出回路124からなるPWM変換回路150と、クランプ回路160とを備えている。

30

#### 【0019】

クランプ回路160は、入力が入力ノードNI1に接続されたバッファ回路161と、一端がバッファ回路の出力及び出力ノードNOに接続された定電圧発生部162と、反転入力端子が定電圧発生部162の他端に接続され、非反転入力端子が入力ノードNI2に接続された誤差増幅回路163と、ゲートが誤差増幅回路163の出力に接続され、ドレンが電源端子102に接続され、ソースが入力ノードNI1に接続されたNMOSトランジスタ164とを有している。

40

#### 【0020】

基準電圧源110は、一端が誤差増幅回路111の非反転入力端子に接続され、他端が接地端子103に接続されている。誤差増幅回路111は、反転入力端子が抵抗143と抵抗144との接続点に接続され、出力がクランプ回路160の入力ノードNI1に接続されている。クランプ回路160は、入力ノードNI1が誤差増幅回路111の出力に接続され、入力ノードNI2が基準電圧源112の一端に接続され、出力ノードNOがPF

50

M比較回路113の反転入力端子及びPWM比較回路122の反転入力端子に接続されている。基準電圧源112の一端は、PFM比較回路113の非反転入力端子に接続され、他端は接地端子103に接続されている。PFM比較回路113は、出力が発振回路114の入力に接続されている。発振回路114は、出力が制御回路123の入力に接続されている。

#### 【0021】

スロープ電圧生成回路121は、入力が電流電圧変換回路120の出力に接続され、出力がPWM比較回路122の非反転入力端子に接続されている。PWM比較回路122は、出力が制御回路123の入力に接続されている。PMOSトランジスタ130は、ソースが電源端子101及び電流電圧変換回路120の入力に接続され、ゲートが制御回路123の出力に接続され、ドレインがインダクタ140の一端、逆流検出回路124の非反転入力端子、及びNMOSトランジスタ131のドレインに接続されている。NMOSトランジスタ131は、ゲートが制御回路123の出力に接続され、ソースが接地端子103に接続されている。逆流検出回路124は、反転入力端子が接地端子103に接続され、出力が制御回路123の入力に接続されている。

#### 【0022】

インダクタ140は、他端が容量141の一端、抵抗143の一端、及び出力端子142に接続されている。容量141の他端は、接地端子103に接続されている。抵抗144の他端は、接地端子103に接続されている。

#### 【0023】

以下、上記のように構成されたスイッチングレギュレータ100の動作について説明する。

#### 【0024】

誤差增幅回路111は、出力端子142の出力電圧VOUTを抵抗143と抵抗144とで分圧した電圧VFBと基準電圧源110の基準電圧VREF1とを比較して、誤差電圧VERR1を出力する。

#### 【0025】

クランプ回路160は、入力ノードNI1に入力される誤差電圧VERR1と入力ノードNI2に入力される基準電圧源112の基準電圧VREF2とに基づき、出力ノードNOに誤差電圧VERR2を生成する。具体的には、バッファ回路161の出力インピーダンスが誤差增幅回路111の出力インピーダンスよりも低く設定されており、バッファ回路161は、誤差電圧VERR1に比例した誤差電圧VERR2を出力ノードNOに生成する。定電圧発生部162は、定電圧VOSを生成する。誤差增幅回路163は、誤差電圧VERR2に定電圧VOSを加算した電圧VMと基準電圧VREF2とを比較してNMOSトランジスタ164のゲートに出力電圧を入力する。これにより、クランプ回路160は、電圧VMが基準電圧VREF2よりも小さいとき、誤差電圧VERR2を基準電圧VREF2よりも定電圧VOS分低い電圧にクランプする。

#### 【0026】

電流電圧変換回路120は、PMOSトランジスタ130のソース電流を電圧に変換し、スロープ電圧生成回路121に出力する。スロープ電圧生成回路121は、電流電圧変換回路120の出力にノコギリ波を加算し、電圧VCSを出力する。PWM比較回路122は、誤差電圧VERR2と電圧VCSとを比較し、比較結果信号CMPWを制御回路123に出力する。

#### 【0027】

PFM比較回路113は、基準電圧源112の基準電圧VREF2と誤差電圧VERR2とを比較し、比較結果信号CMPFを発振回路114に出力する。発振回路114は、比較結果信号CMPFがローレベルのとき、所定の周波数で発振し（イネーブルされ）、出力信号CLKとしてクロック信号を出力する。また、発振回路114は、比較結果信号CMPFがハイレベルのとき、発振を停止し（ディスエーブルされ）、出力信号CLKをローレベルに固定する。

10

20

30

40

50

**【0028】**

逆流検出回路124は、NMOSトランジスタ131のドレイン電圧とソース電圧とを比較し、ドレイン電圧がソース電圧より高くなると、逆電流検出信号を制御回路123に出力する。

**【0029】**

制御回路123は、入力された各信号に従って、PMOSトランジスタ130とNMOSトランジスタ131のオン・オフを制御する。

**【0030】**

インダクタ140と容量141は、PMOSトランジスタ130のドレインから出力される電圧VSWを平滑する。

10

**【0031】**

このような回路構成によって負帰還ループが機能し、スイッチングレギュレータ100は、電圧VFBが基準電圧VREF1と等しくなるように動作して、出力端子142に出力電圧VOOUTを生成する。

**【0032】**

スイッチングレギュレータ100では、出力端子142に接続される負荷10に流れる負荷電流IOUTの大きさによって、以下のように、PWM(Pulse Width Modulation)動作とPFM(Pulse Frequency Modulation)動作が切り替わる。

**【0033】**

負荷電流が大きい場合、出力電圧VOOUTの低下を補うように誤差電圧VERR1、すなわち、誤差電圧VERR2が上昇する。したがって、誤差電圧VERR2が基準電圧VREF2よりも定的に大きくなり、発振回路114は、出力信号CLKとして所定周波数のクロック信号を出力し続ける。このクロック信号の立ち上がりに同期して、PWM変換回路150は、PMOSトランジスタ130をオンさせ、NMOSトランジスタ131をオフさせる。このとき、PMOSトランジスタ130のオン時間を制御する信号のパルス幅は、PWM変換回路150により決定される。このように、負荷電流IOUTが大きい場合には、スイッチングレギュレータ100は、PWM動作となる。

20

**【0034】**

その後、上述の状態から、負荷電流IOUTが小さくなった場合、負荷電流IOUTが小さくなつてすぐの時点では、誤差電圧VERR2が基準電圧VREF2よりも定的に大きい状態が続いている。しかし、負荷電流IOUTが小さくなっていることから、負荷電流IOUTによる出力電圧VOOUTの低下が少ないため、PMOSトランジスタ130をオンさせることによる出力電圧VOOUTの上昇が大きくなる。したがって、この出力電圧VOOUTの上昇を補うように誤差電圧VERR2が低下し、基準電圧VREF2よりも低い電圧値となる。よって、PMOSトランジスタ130がオフとなり、出力電圧VOOUTは、低下していく。

30

**【0035】**

そして、誤差電圧VERR2が上昇していき基準電圧VREF2よりも大きくなると、発振回路114は、出力信号CLKとしてクロック信号を出力する。このクロック信号の立ち上がりに同期して、PWM変換回路150は、PMOSトランジスタ130をオンさせ、NMOSトランジスタ131をオフさせる。このとき、負荷電流IOUTが小さいことから、PMOSトランジスタ130がオンしたことにより、出力電圧VOOUTがすぐに所望の電圧値を上回るため、誤差電圧VERR2は低下する。すると、PWM変換回路150は、PMOSトランジスタ130をオフさせ、NMOSトランジスタ131をオンさせる。また、発振回路114は、出力信号CLKをローレベルに固定する。このように、負荷電流IOUTが小さい場合には、発振回路114は、発振と停止とを繰り返す。すなわち、スイッチングレギュレータ100は、PFM動作となる。

40

**【0036】**

このようにして、本実施形態のスイッチングレギュレータ100は、負荷電流IOUT

50

が小さいときにPFM動作に移行し、電力変換効率を向上させることができる。

#### 【0037】

かかる本実施形態のスイッチングレギュレータ100の特徴的な構成を説明するため、以下、スイッチングレギュレータ100がPFM動作しているときに、負荷電流I<sub>OUT</sub>が急増した場合の回路動作について詳述する。

#### 【0038】

図2は、本実施形態のスイッチングレギュレータ100における負荷電流I<sub>OUT</sub>、電圧V<sub>SW</sub>、インダクタ140に流れるインダクタ電流I<sub>L</sub>、出力電圧V<sub>OUT</sub>、電圧V<sub>FB</sub>、誤差電圧V<sub>ERR2</sub>、比較結果信号CMPFの波形を示している。また、電圧V<sub>FB</sub>の波形に重ねて、基準電圧V<sub>REF1</sub>を一点差線で示し、誤差電圧V<sub>ERR2</sub>の波形に重ねて、基準電圧V<sub>REF2</sub>を一点差線で、0Vを点線で示している。

10

#### 【0039】

時刻t0では、比較結果信号CMPFがハイレベルとなっており、スイッチングレギュレータ100は、PFM動作している。よって、PMOSトランジスタ130及びNMOSトランジスタ131は、スイッチング動作を停止してオフしている。このとき、電圧V<sub>FB</sub>が基準電圧V<sub>REF1</sub>より高いことから、誤差增幅回路111は、誤差電圧V<sub>ERR1</sub>として低い電圧(0V)を出力しようとする。しかし、上述のとおり、クランプ回路160は、電圧V<sub>M</sub>が基準電圧V<sub>REF2</sub>より小さくなると、誤差電圧V<sub>ERR2</sub>を基準電圧V<sub>REF2</sub>よりも定電圧V<sub>OS</sub>分低い電圧にクランプするため、誤差電圧V<sub>ERR2</sub>(誤差電圧V<sub>ERR1</sub>)は、基準電圧V<sub>REF2</sub>よりも低く、0Vよりも高い電圧となっている。

20

#### 【0040】

上述の状態で、時刻t0において負荷電流I<sub>OUT</sub>が急増すると、これに従い、出力電圧V<sub>OUT</sub>が低下していく、電圧V<sub>FB</sub>も低下していく。そして、電圧V<sub>FB</sub>が基準電圧V<sub>REF1</sub>を下回ると、誤差電圧V<sub>ERR2</sub>は、基準電圧よりも定電圧V<sub>OS</sub>分低い電圧から上昇し始める。

#### 【0041】

その後、時刻t1において、誤差電圧V<sub>ERR2</sub>が基準電圧V<sub>REF2</sub>を上回ると、比較結果信号CMPFがローレベルに反転する。これにより、PMOSトランジスタ130及びNMOSトランジスタ131がスイッチング動作を開始し、インダクタ電流I<sub>L</sub>が流れ、出力電圧V<sub>OUT</sub>が上昇に転じる。

30

#### 【0042】

このように、本実施形態のスイッチングレギュレータ100は、誤差電圧V<sub>ERR2</sub>の下限値が基準電圧V<sub>REF2</sub>の電圧値から定電圧V<sub>OS</sub>分を減算した電圧値にクランプされるように動作することにより、時刻t0から時刻t1まで、すなわち、PFM動作中に負荷電流I<sub>OUT</sub>が急増してからPWM動作に移行するまでに遅延時間DTを短縮することができる。したがって、出力電圧V<sub>OUT</sub>が大きく低下することを抑制することが可能となる。

#### 【0043】

次に、図3を参照して、本発明の第2の実施形態のスイッチングレギュレータ200について説明する。

40

#### 【0044】

本実施形態のスイッチングレギュレータ200は、第1の実施形態のスイッチングレギュレータ100のクランプ回路160において、誤差增幅回路163の反転入力端子と出力ノードNOとの間に接続されていた定電圧発生部162が削除され、代わりに、バッファ回路161の出力と出力ノードNOとの間に定電圧発生部262が接続された構成となっている。その他の構成については、図1のスイッチングレギュレータ100と同一であるため、同一の構成要素には同一符号を付し、重複する説明は適宜省略する。

#### 【0045】

上述の構成により、本実施形態のスイッチングレギュレータ200も、第1の実施形態

50

のスイッチングレギュレータ100と同様、誤差電圧VERR2の下限値が基準電圧VR

EF2の電圧値から定電圧VOS分を減算した電圧値にクランプされるように動作する。

これにより、PFM動作中に負荷電流IOUTが急増した場合でも、負荷電流IOUTが

急増してからPWM動作に移行するまでの遅延時間DTを短縮し、出力電圧VOUTが大

きく低下することを抑制することができる。

#### 【0046】

図4は、第1及び第2の実施形態におけるバッファ回路161の位置具体例を示してい

る。バッファ回路161は、ドレンが電源端子102に接続され、ソースがクランプ回

路160の出力ノードNOに接続され、ゲートがクランプ回路160の入力ノードNI1

に接続されNMOSトランジスタ161tと、出力ノードNOと接地端子103との間に

接続された定電流源161cにより構成されている。すなわち、バッファ回路161は

、ソースフォロワ回路で構成されている。

#### 【0047】

かかる構成によれば、少ない素子数で出力インピーダンスの低いバッファ回路を実現す

ることができる。

#### 【0048】

以上、本発明の実施形態について説明したが、本発明は上記実施形態に限定されず、本

発明の趣旨を逸脱しない範囲において種々の変更が可能であることは言うまでもない。

#### 【0049】

例えば、上記実施形態において、定電圧発生部162、262は、定電圧が生成可能で

あれば、その構成は特に限定されない。

#### 【0050】

また、上記実施形態においては、電流モード制御方式のスイッチングレギュレータを例

として説明したが、本発明は、電圧モード制御方式のスイッチングレギュレータにも適用

可能である。

#### 【0051】

また、上記実施形態においては、スイッチング素子及び同期整流素子としてMOSトラン

ジスタを用いた例を説明したが、バイポーラトランジスタ等を用いてもよい。

#### 【0052】

また、上記実施形態においては、同期整流方式のスイッチングレギュレータを例として

説明したが、本発明は、ダイオード整流方式のスイッチングレギュレータにも適用可能で

ある。なお、ダイオード整流方式とした場合は、逆流検出回路は不要である。

#### 【符号の説明】

#### 【0053】

|                 |              |

|-----------------|--------------|

| 100、200         | スイッチングレギュレータ |

| 101、102、501     | 電源端子         |

| 103、502         | 接地端子         |

| 110、112、510、512 | 基準電圧源        |

| 111、163、511     | 誤差増幅回路       |

| 113、513         | PFM比較回路      |

| 114、514         | 発振回路         |

| 120、520         | 電流電圧変換回路     |

| 121、521         | スロープ電圧生成回路   |

| 122、522         | PWM比較回路      |

| 123、523         | 制御回路         |

| 124、524         | 逆流検出回路       |

| 130、530         | PMOSトランジスタ   |

| 131、164、531     | NMOSトランジスタ   |

| 140、540         | インダクタ        |

| 141、541         | 容量           |

10

20

30

40

50

142、542 出力端子

143、144、543、544 抵抗

150、550 PWM変換回路

160 クランプ回路

161 バッファ回路

162、262 定電圧発生部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(56)参考文献 特開2010-259257(JP,A)

特開2010-004653(JP,A)

特開2013-168880(JP,A)

特開2005-210335(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/00 - 3/44