(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-5834

(P2007-5834A)

(43) 公開日 平成19年1月11日(2007.1.11)

(51) Int.CI.

H01L 21/304 (2006.01)

B24B 39/04 (2006.01)

F 1

H01L 21/304 622R

B24B 39/04 Z

テーマコード(参考)

3C058

審査請求 有 請求項の数 9 O L (全 14 頁)

|            |                                     |          |                                                  |

|------------|-------------------------------------|----------|--------------------------------------------------|

| (21) 出願番号  | 特願2006-275955 (P2006-275955)        | (71) 出願人 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区丸の内二丁目4番1号  |

| (22) 出願日   | 平成18年10月10日 (2006.10.10)            | (74) 代理人 | 100084032<br>弁理士 三品 岩男                           |

| (62) 分割の表示 | 特願2002-157952 (P2002-157952)<br>の分割 | (72) 発明者 | 大嶽 敦<br>茨城県日立市大みか町七丁目1番1号 株<br>式会社日立製作所日立研究所内    |

| 原出願日       | 平成14年5月30日 (2002.5.30)              | (72) 発明者 | 小林 金也<br>茨城県日立市大みか町七丁目1番1号 株<br>式会社日立製作所日立研究所内   |

|            |                                     | (72) 発明者 | 荒井 利行<br>神奈川県横浜市戸塚区吉田町292番地<br>株式会社日立製作所生産技術研究所内 |

最終頁に続く

(54) 【発明の名称】研磨方法および研磨システム

## (57) 【要約】

【課題】複数種の半導体製品を効率的に生産する。

【解決手段】加工済みの製品種「A」の半導体ウエハのマスクデータおよび実測残膜厚値に基づき、基礎式に含まれるパラメータの値を、CMP装置の特性を再現するように決定する(S202)。つぎに加工対象となる製品種「B」の半導体ウエハのマスクデータと、S202でパラメータ値を定めた基礎式とを用いて、製品種「B」の半導体ウエハの最適研磨時間を予測する(S203)。以降、加工対象となる製品種が切り替わるごとに同様な処理を実行することによって、最適研磨時間を予測する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

互いに異なる設計データに基づき作成された第1品種の加工物と第2品種の加工物とを研磨する研磨システムであって、

前記第1品種の加工物を研磨し、前記第1品種の加工物の研磨が終了してから前記第2品種の加工物を研磨する研磨装置と、

前記研磨装置で研磨された、前記第1品種の加工物の形状に相関する寸法を、前記第2品種の加工物の研磨に先立ち測定する測定装置と、

前記第1品種の加工物の設計データと前記測定装置の出力データと前記第2品種の加工物の設計データとに基づき、前記第2品種の加工物の研磨時間を算出する情報処理装置と

10

、

前記研磨装置が前記第2品種の加工物を研磨する時間を、前記情報処理装置が算出した研磨時間に基づき制御するコントローラと、

を備えることを特徴とする研磨システム。

**【請求項 2】**

互いに異なる設計データに基づき膜が形成された第1品種の加工物と第2品種の加工物とを研磨する研磨システムであって、

前記第1品種の加工物の膜を研磨し、前記第1品種の加工物の膜の研磨が終了してから前記第2品種の加工物の膜を研磨する研磨装置と、

研磨後の前記第1品種の加工物の残膜厚を、前記第2品種の加工物の膜の研磨に先立ち測定する測定装置と、

前記第1品種の加工物の設計データと前記測定装置の出力データと前記第2品種の加工物の設計データとに基づき、前記第2品種の加工物の膜の研磨時間を算出する情報処理装置と、

前記研磨装置が前記第2品種の加工物の膜を研磨する時間を、前記情報処理装置が算出した研磨時間に基づき制御するコントローラと、

を備えることを特徴とする研磨システム。

**【請求項 3】**

請求項1または2記載の研磨システムであって、

前記情報処理装置は、

加工物の研磨時間と研磨後の寸法との関数に含まれるパラメータの値を、前記第1品種の加工物の設計データと前記測定装置の出力データとに基づき決定し、当該決定された値がパラメータに設定された関数と前記第2品種の加工物の設計データとに基づき前記研磨時間を算出する、

ことを特徴とする研磨システム。

30

**【請求項 4】**

互いに異なる設計データに基づき膜が作成された第1品種の加工物と第2品種の加工物とを研磨装置で研磨する研磨方法であって、

前記第1品種の加工物の膜を前記研磨装置で研磨する第一研磨処理と、

前記第一研磨処理後の前記第1品種の加工物の残膜厚を測定装置で測定する測定処理と

40

、

情報処理装置が、前記第1品種の加工物の設計データと前記測定装置の出力データと前記第2品種の加工物の設計データとに基づき、前記第2品種の加工物の膜の研磨時間を算出する演算処理と、

前記情報処理装置が算出した研磨時間、前記第2品種の加工物の膜を前記研磨装置が研磨する第二研磨処理と、

を含むことを特徴とする研磨方法。

**【請求項 5】**

請求項4記載の研磨方法であって、

前記演算処理は、

50

加工物の研磨時間と研磨後の残膜厚との関数に含まれるパラメータの値を、前記第1加工物の設計データと前記測定装置の出力データとに基づき決定する第一ステップと、

前記第一ステップで決定したパラメータ値が設定された前記関数と前記第2品種の加工物の設計データとに基づき、前記第2品種の加工物の膜の研磨時間を算出する第二ステップと、

を含むことを特徴とする研磨方法。

#### 【請求項6】

請求項4または5記載の研磨方法であって、

前記情報処理装置が、前記第1品種の加工物の残膜厚が最大となる第1位置および最小となる第2位置を示す情報を、前記第1品種の加工物の設計データに基づき算出する測定位置選定処理を含み、

前記測定処理において、前記測定装置は、前記測定位置選定処理で算出された情報が示す第1および第2位置で、前記第1品種の加工物の残膜厚を測定することを特徴とする研磨方法。

#### 【請求項7】

請求項4、5および6のうちのいずれか1項に記載の研磨方法であって、

前記第一研磨処理で前記第1品種の加工物が複数研磨される場合、前記測定処理において、前記複数の加工物のうち、最後に研磨された加工物の残膜厚または最後に研磨された加工物を含むロット内の加工物の残膜厚を測定することを特徴とする研磨方法。

#### 【請求項8】

互いに異なる設計データに基づき作成された第1品種の加工物と第2品種の加工物とを研磨する研磨システムに用いられる情報処理装置であって、

前記第1品種の加工物が前記第2品種の加工物よりも先に研磨された場合、研磨後の前記第1品種の加工物の残膜厚の入力を受け付け、当該残膜厚と前記第1品種の加工物の設計データと前記第2品種の加工物の設計データとに基づき、前記第2品種の加工物の膜の研磨時間を算出し、当該研磨時間を出力する演算手段を備えることを特徴とする情報処理システム。

#### 【請求項9】

請求項8記載の情報処理システムであって、

前記演算手段は、

加工物の研磨時間と研磨後の寸法との関数に含まれるパラメータの値を、前記第1品種の加工物の設計データと前記測定装置の出力データとに基づき決定し、当該決定された値がパラメータに設定された関数と前記第2品種の加工物の設計データとに基づき前記研磨時間を算出することを特徴とする情報処理システム。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体製造プロセスに係り、特に、半導体製造プロセスにおいて複数種の製品を効率的に生産するための技術に関する。

#### 【背景技術】

#### 【0002】

半導体ウエハの平坦化プロセスには、一般に、化学機械研磨(CMP:chemical mechanical polishing)が適用される。半導体ウエハに対するCMPの終点を決定するための技術として、特表2001-523586号公報記載の技術、特表2001-501545号公報記載の技術、特開平11-186204号公報記載の技術が知られている。特表2001-523586号公報記載の技術は、CMPの実験結果とシミュレート結果(例えば、研磨時間の経過に伴うフィルム厚変化を表すフィルム厚さプロファイル)とを比較することによって、研磨時間を含むモデル化パラメータを最適化するものである。また、特表2001-501545号公報記載の技術は、研磨前後のウエハの厚さ測定値に基づき線形推定ファクタを決定し、つぎのウエハに対する研磨時間をその線形推定ファクタで調整す

10

20

30

40

50

るものである。さらに、特開平11-186204号公報記載の技術は、ロットの半導体ウエハの研磨前後の膜厚差と研磨時間とから最新の研磨レートを算出し、つぎのロットの半導体ウエハの研磨時間を、最新の研磨レートと研磨必要量とに基づき算出するものである。

【発明の開示】

【発明が解決しようとする課題】

【0003】

ところが、特表2001-523586号公報記載の技術によれば、生産対象製品の製品種が切り替わるごとに、CMPのシミュレーションおよび研磨を繰り返す必要がある。このため、この技術を半導体プロセスに適用した場合、複数種類の半導体製品を効率的に生産することが困難である。10

【0004】

また、特表2001-501545号公報記載の技術、特開平11-186204号公報記載の技術においては、生産対象製品の製品種が切り替わることが考慮されていない。このため、これらの技術を、生産対象製品の製品種が切り替わる場合にそのまま適用することはできない。

【0005】

そこで、本発明は、複数種類の半導体製品の、効率的な生産を可能とすることを目的とする。20

【課題を解決するための手段】

【0006】

上記課題を解決するため、本発明では、互いに異なる設計データに基づき作成された第1品種の加工物と第2品種の加工物とを研磨する研磨システムにおいて、先に研磨された第1品種の加工物の形状に相關する寸法を、第2品種の加工物の研磨に先立ち測定し、その測定値と第1品種の加工物の設計データと第2品種の加工物の設計データとに基づき、第2品種の加工物の研磨時間を算出することとした。

【発明の効果】

【0007】

本発明によれば、複数種類の半導体製品を効率的に生産することができる。

【発明を実施するための最良の形態】

【0008】

以下、添付の図面を参照ながら、本発明の実施の一形態について説明する。

【0009】

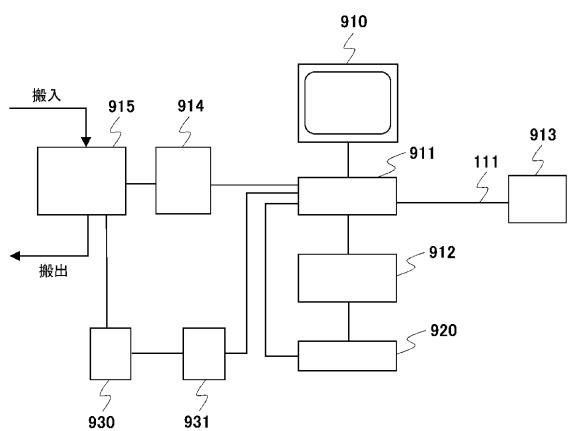

まず、図8により、本実施の形態に係る研磨システムの概略構成について説明する。

【0010】

本研磨システムは、搬入系91から搬入された半導体ウエハを研磨するCMP装置915、CMP装置915を制御するCMP装置コントローラ914、研磨済み半導体ウエハの表面の残膜厚を測定する膜厚計(ここでは、光学式膜厚計)930、膜厚計930を制御する膜厚計コントローラ931、膜厚計930の出力および新たな製品種の半導体回路の設計データ(GDSIIフォーマットのマスクデータ)に基づき新たな製品種の半導体ウエハの研磨時間を定める情報処理装置911、ストレージ912、情報処理装置911の出力データが表示される表示装置910、ユーザからデータ入力を受け付ける入力装置(マウス、キーボード等)920、加工対象が新たな製品種に切り替わる場合にその新たな製品種の半導体ウエハ上の半導体回路の設計データ等を情報処理装置911に通信回線111を介して与えるサーバ913、が含まれている。なお、ストレージ912には、情報処理装置911が実行する研磨時間予測処理が定義されたソフトウェアおよび情報処理装置911が実行する研磨時間予測処理に必要なデータ(CMP装置の特性を模擬する基礎式のパラメータ初期値、チップ上に定めた分割領域の重心座標等)が、CD-ROM等の記憶媒体から、または、通信回線111を介してあらかじめインストールされている。40

【0011】

10

20

30

40

50

なお、本実施の形態では、研磨システムの膜厚計 930 として光学式膜厚計を用いているが、必ずしも、この通りにする必要はない。例えば、光学式膜厚計の代わりに、触針式膜厚計、電気抵抗測定式膜厚計および走査型電子顕微鏡のうちのいずれかを用いてもよいし、光学式膜厚計、触針式膜厚計、電気抵抗測定式膜厚計および走査型電子顕微鏡のうちの 2 つ以上の組合せを用いてもよい。

#### 【0012】

つぎに、図 8 の研磨システムの加工対象となる製品種の一例について説明する。

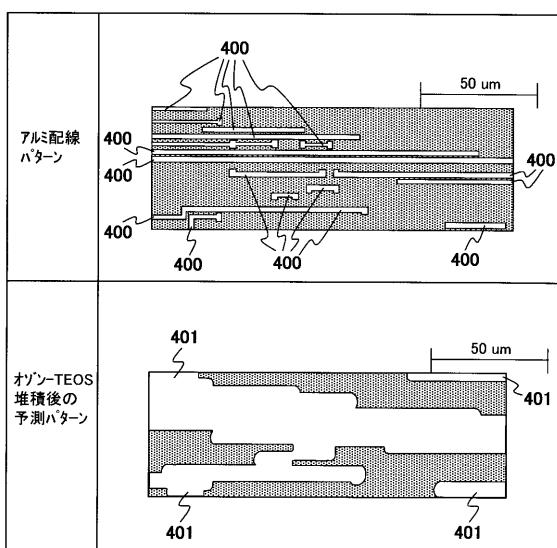

#### 【0013】

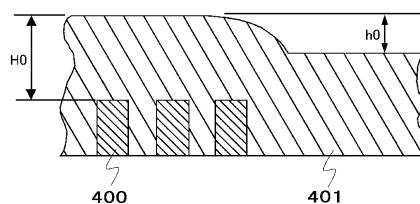

加工対象となる各製品種の半導体ウエハには、テストチップが作り込まれている。各製品種の半導体ウエハのテストチップには、それぞれ、図 5 に示すように、露光マスクパターンを用いて配線 400 が形成され、さらに、予め定めた膜厚 H0 の酸化膜 401 が配線 400 上に堆積されている。酸化膜 401 の表面には、配線 400 の膜厚と同程度の高さの段差 h0 が生じるため、この酸化膜 401 が、図 8 の研磨システムが行う研磨プロセスにおける研磨対象となる。

#### 【0014】

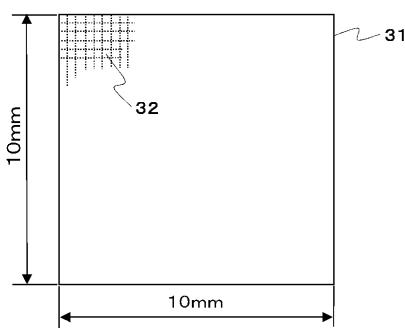

図 4 に示すように、このような各製品種の半導体ウエハに作りこまれたテストチップ 31 を仮想的に複数の領域 32 に分割し、各分割領域 32 の識別番号 ( $j = 1, 2, \dots, m$ ) および重心座標  $r_j$  の対応情報がストレージ 901 にあらかじめ格納してある。 $10\text{ mm} \times 10\text{ mm}$  のテストチップであれば、例えば、10000 個の、 $100\mu\text{m} \times 100\mu\text{m}$  の正方形領域にチップを分割すればよい(図 4 参照)。そして、これらの分割領域の重心座標のなかから、複数個 ( $n$  個) の座標を選択し、それらの座標も、膜厚計による測定位置の座標としてあらかじめストレージ 901 に格納しておく。

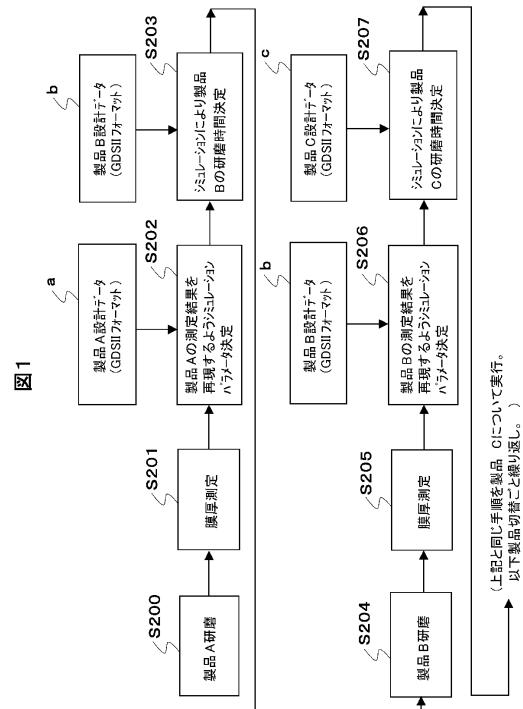

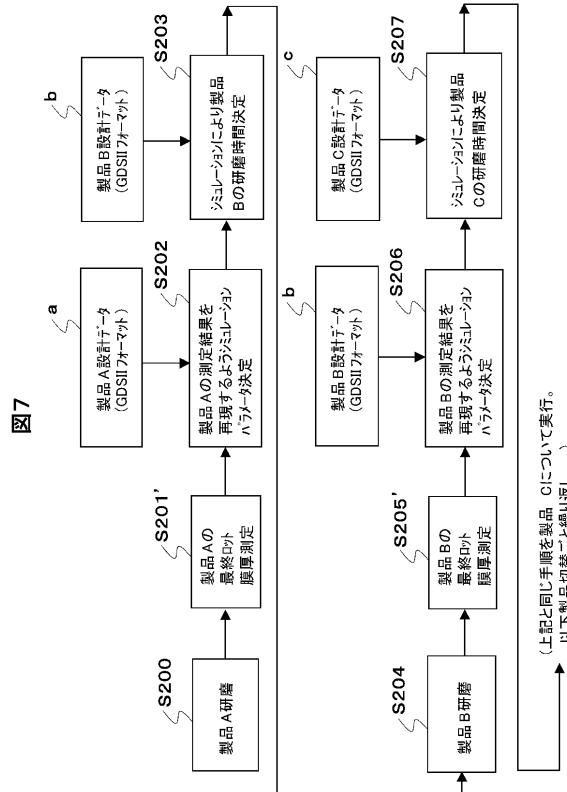

つぎに、図 1 により、図 8 の研磨システムを用いて実行される研磨プロセスの概要について説明する。ここでは、加工対象の半導体ウエハの製品種が、「A」から「B」に切り替わり、さらに「B」から「C」に切り替わる場合を例に挙げる。

#### 【0015】

制御装置 914 の制御下において、CMP 装置 915 が、製品種「A」に属する半導体ウエハを順次研磨する(S200)。その後、製品種「A」に属する研磨済み半導体ウエハのなかから、無作為に所定枚数(複数枚)の半導体ウエハが膜厚測定対象として選定されると、情報処理装置 911 は、測定位置の座標をストレージから読み出し、それらの座標を含む指令を膜厚計コントローラ 931 に与える。なお、本実施の形態では、膜厚計による測定点を 4 点とし、4 つの座標  $r_s, r_k, r_l, r_m$  を含む指令が膜厚計コントローラ 931 に与えられることとする。膜厚計コントローラ 931 は、この指令に含まれていた 4 つの座標  $r_s, r_k, r_l, r_m$  により定まる測定位置で、各膜厚測定対象の半導体ウエハの表面の残膜厚をそれぞれ測定する(S201)。なお、ここでは、製品種「A」に属する研磨済み半導体ウエハのなかから膜厚測定対象を選定するようしているが、製品種「A」に属する研磨済み半導体ウエハのすべてを膜厚測定対象とするようにしてもよい。

#### 【0016】

情報処理装置 911 は、すべての膜厚測定対象の測定データを膜厚計コントローラ 931 を介して受け付けると、測定位置の座標  $r_s, r_k, r_l, r_m$  ごとに、すべての膜厚測定対象の測定データの平均値  $H_e(1), H_e(2), H_e(3), H_e(4)$  を算出し、それら平均値を、各測定位置における実測膜厚データとしてストレージ 912 に格納する。

#### 【0017】

その後、製品種「A」の半導体回路の設計データ a (GDSII フォーマット)、製品種「A」のパラメータ初期値、および、各測定位置における実測膜厚データ  $H_e(1), H_e(2), H_e(3), H_e(4)$  をストレージ 912 から読み込み、これらのデータに基づき CMP 装置 915 の研磨特性を再現する。具体的には、製品種「A」の半導体回路の設計データ a を用いて得られるシミュレーション結果と各測定位置における実測膜厚データとの誤差関数が最小になるように、CMP 装置 915 の研磨特性を模擬する基礎式に含まれるパラメータの値を決定する(S202)。

10

20

30

40

50

## 【0018】

このようにしてパラメータ値を決定すると、情報処理装置911は、つぎの加工対象に関するデータの送信リクエストをサーバ913に送信する。この送信リクエストに応じて、サーバ913が、つぎの加工対象となる製品種「B」の半導体回路の設計データb(GDS IIフォーマット)およびパラメータ初期値を返信すると、情報処理装置911は、それらのデータをストレージ912に格納するとともに、製品種「B」の半導体回路の設計データbとS202でパラメータ値を定めた基礎式とを用いて、製品種「B」に属する半導体ウエハの最適研磨時間(半導体ウエハ表面の残膜厚を所期の値にするまでの研磨時間)を予測する(S203)。情報処理装置911は、このとき予測した最適研磨時間を、ストレージ912に格納しておき、適當なタイミングとなったらストレージ912から読み出してCMP装置コントローラ914に与える。これにより、CMP装置コントローラ914の制御下において、CMP装置915は、製品種「B」に属する半導体ウエハを最適研磨時間だけ研磨する(S204)。

10

## 【0019】

その後、製品種「B」に属する研磨済み半導体ウエハのなかから、無作為に所定枚数(複数枚)の半導体ウエハが膜厚測定対象として選定されると、情報処理装置911は、4点の測定位置の座標 $r_s, r_k, r_l, r_m$ をストレージから読み出し、それらの座標 $r_s, r_k, r_l, r_m$ を含む指令を膜厚計コントローラ931に与える。膜厚計コントローラ931は、この指令に含まれていた座標 $r_s, r_k, r_l, r_m$ により定まる測定位置で、各膜厚測定対象の半導体ウエハの表面上の残膜厚を測定する(S205)。なお、ここでは、製品種「B」に属する研磨済み半導体ウエハのなかから膜厚測定対象を選定するようにしているが、製品種「B」に属する研磨済み半導体ウエハのすべてを膜厚測定対象とするようにしてもよい。

20

## 【0020】

情報処理装置911は、すべての膜厚測定対象の測定データを膜厚計コントローラ931を介して受け付けると、測定位置の座標 $r_s, r_k, r_l, r_m$ ごとに、すべての膜厚測定対象の測定データの平均値 $H_e(1), H_e(2), H_e(3), H_e(4)$ を算出し、それらの平均値 $H_e(1), H_e(2), H_e(3), H_e(4)$ を、各測定位置における実測膜厚データとしてストレージ912に格納する。

30

## 【0021】

その後、情報処理装置911は、つぎの加工対象となる製品種「B」の半導体回路の設計データbおよびのパラメータ初期値、各測定位置における実測膜厚データ $H_e(1), H_e(2), H_e(3), H_e(4)$ をストレージ912から読み込み、これらのデータに基づきCMP装置の研磨特性を再現する。具体的には、製品種「B」の半導体回路の設計データbを用いて得られるシミュレーション結果と、膜厚計930による測定データとの誤差関数が最小になるように、CMP装置の研磨特性を模擬する基礎式に含まれるパラメータ値を決定する(S206)。

## 【0022】

このようにしてパラメータ値を決定すると、情報処理装置911は、つぎの加工対象に関するデータの送信リクエストをサーバ913に送信する。この送信リクエストに応じて、サーバ913が、つぎの加工対象になる製品種「C」の半導体回路の設計データc(GDS IIフォーマット)およびパラメータ初期値を返信すると、情報処理装置911は、それらのデータをストレージ912に格納するとともに、製品種「C」の設計データcとS206でパラメータを定めた基礎式とを用いて、製品種「C」に属する半導体ウエハの最適研磨時間を予測する(S207)。情報処理装置911は、このとき予測した最適研磨時間を、ストレージ912に一旦格納しておき、適當なタイミングとなったら、ストレージ912から読み出してCMP装置コントローラ914に与える。これにより、CMP装置コントローラ914の制御下において、CMP装置915は、製品種「C」に属する半導体ウエハを最適研磨時間だけ研磨する。

40

## 【0023】

50

その後、加工対象が「C」から別の製品種にさらに切り替わる場合には、情報処理装置911は、S205～S207と同様な処理を実行する。

#### 【0024】

このような処理によれば、加工対象の製品種が切り替わる場合、加工済み製品種の設計データと実測膜厚データに基づき基礎式のパラメータを決定し、新たに加工対象とする製品種の最適研磨時間を、その基礎式を用いて予測することができる。この予測結果をCMPプロセスにフィードフォワードすることによって、新たな製品種の最適研磨時間を定めるためのCMP実験を事前に行う必要がなくなる、このため、CMP装置の加工対象の製品種をスムーズに切り替えることができる。したがって、本実施の形態に係る研磨システムを、半導体製造プロセスの平坦化プロセスに適用すれば、複数種類の半導体製品を効率的に生産することができるようになる。例えば、多品種少量生産を効率的に遂行することができる。10

#### 【0025】

なお、本実施の形態においては、膜厚計による測定データが、膜厚計コントローラ911から情報処理装置911に送信されることとしているが、必ずしも、このようにする必要はない。例えば、作業者が、膜厚計による測定データを入力装置920から入力するようにもよい。また、作業者が、膜厚計による測定データを、可搬型記憶媒体(フレキシブルディスク等)に記憶させ、その可搬型記憶媒体から情報処理装置911に読み込ませるようにしてもよい。また、基礎式に含まれるパラメータの初期値も、これらの方針によって情報処理装置911に与えられるようにしてもよい。20

また、本実施の形態では、最適研磨時間をCMP装置コントローラ914だけに出力しているが、必要に応じて、情報処理装置911から、表示装置910、サーバ913等に最適研磨時間が出力されるようにしてもよい。20

#### 【0026】

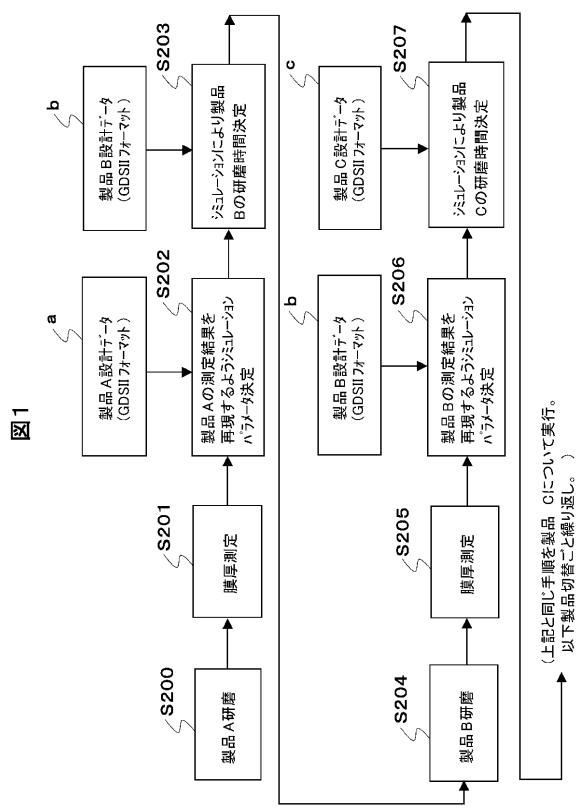

つぎに、図2により、情報処理装置が実行する研磨時間予測処理の詳細について説明する。なお、酸化膜に関するシミュレーションにおける理論式は多数存在しているが、ここでは、「半導体CMP技術」土肥俊郎編著,P162～、B.Stine et.al. 鄭 closed-form analytic model for ILD thickness variation in CMP process Proc. CMP-MIC, Santa Clara(Feb.'97)に記載されている基礎式の変形を用いることとする。

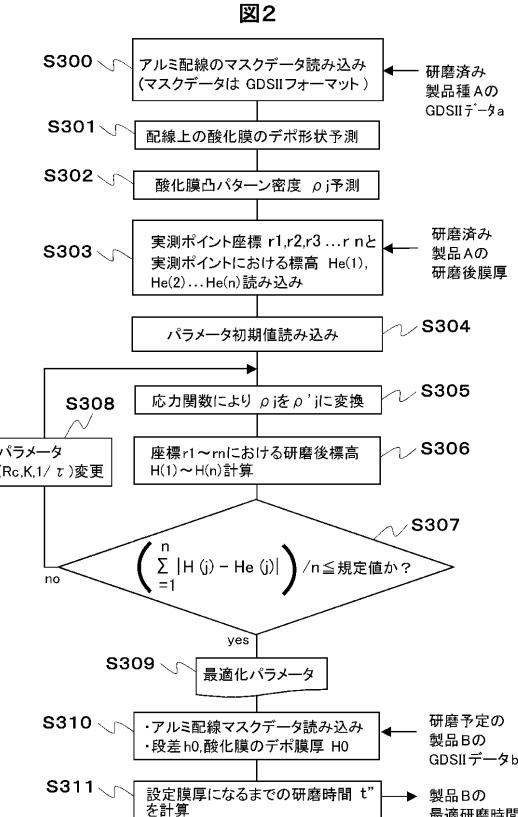

まず、製品種「A」の半導体回路の設計データaをストレージから読み込み、配線の形成に使用した露光マスクデータを、その設計データaから抽出する(S300)。なお、このとき抽出した露光マスクデータは、配線の位置を1nm～10nmの精度で検出することができるものである。30

図3に示すように、配線とその上に堆積させた酸化膜とでは、表面形状が相違している。具体的には、酸化膜の凸領域(白色パターン401)が、配線の凸領域(白色パターン400)よりも広くなる。そこで、酸化膜の表面形状を、S300で抽出したマスクデータに基づき予測する(S301)。なお、この予測には、例えば、特開平11-186205号公報の技術を用いることができる。

その予測結果に基づき、テストチップの各分割領域32内における、酸化膜の凸領域の占める面積率( $j$ )(以下、密度と呼ぶ)を算出し、それらを、分割領域の識別番号jに対応付けてストレージ912に格納する(S302)。40

#### 【0027】

つぎに、各測定位置における実測膜厚データHe(1), He(2), He(3), He(4)をストレージ912から読み込み(S303)、さらに、パラメータ初期値(後述のRc, K, 1/ $j$ )および各分割領域の重心座標 $r_j$ をストレージ912から読み込む(S304)。そして、各分割領域における密度 $j$ を、次式によって平均化パターン密度 $'_j$ に変換する(S305)。なお、ここで求めた、各分割領域の平均化パターン密度 $'_j$ が、表示装置910に表示されるようにもよい。

$$'_j = r' \{ F(r_j + r', R_c) (r_j (r_j + r')) \} / r' \{ F(r_j + r', R_c) \}$$

$F(r, r_c)$  : ガウス型関数、2次関数、指数関数等の応力関数

(ここではガウス型関数を用いる)

$R_c$  : 応力関数  $F$  の半値幅(酸化膜 C M P の場合、数 mm)

$R_c$  が大きくなるほど、注目点から離れた部位の密度  $j$  が研磨速度に寄与する。

#### 【0028】

$r'$  :  $R_c$  よりも十分大きな値。

このようにして求めた、各分割領域の平均化パターン密度 ' $j$ ' のうち、膜厚計 930 による各測定位置を中心とする分割領域の平均化パターン密度と研磨時間とを、研磨時間  $t$  と研磨後の残膜厚  $H_j$  との関数(次式:以下、モデルと呼ぶ)に代入することによって、各測定位置の研磨済み酸化膜の残膜厚の予測値(以下、予測膜厚データと呼ぶ)  $H_j$  を算出する(S306)。

#### 【0029】

(A)  $t < t_c (= \frac{1}{j^2} \cdot h_0/K)$  の場合

$$H_j = H_0 - [t_c \cdot K / j + K \cdot (t - t_c) + (1 - j) \cdot h_1 \cdot (1 - \exp(-(t - t_c)/))]$$

(B)  $t = t_c (= \frac{1}{j^2} \cdot h_0/K)$  の場合

$$H_j = H_0 - Kt / j$$

ここで、 $j$  : Preston 定数

$V$  : 研磨パッドとウエハとの接触速度

$K$  : パターン密度 100% の場合の研磨速度

$G$  : 研磨パッドのヤング率

$P$  : 研磨パッドとウエハとの間の圧力

$d$  : 研磨パッドの厚さ

$H_0$  : 研磨前の酸化膜の膜厚

$h_0$  : 研磨前の酸化膜表面の段差(=配線膜厚)

$$h_1 = h_0 \cdot (1 - j)$$

$$1/V = K \cdot V \cdot G / d = K \cdot G / (P \cdot d)$$

以上のシミュレーションの結果得られた、各測定位置における予測膜厚データ  $H_s, H_k, H_l, H_m$  ( $= H(1), H(2), H(3), H(4)$ ) と各測定位置における実測膜厚データ  $H_e(1), H_e(2), H_e(3), H_e(4)$  とを以下の誤差関数に代入し、その結果得られた値  $Cv$  と規定値(例えば 10 nm)とを比較する(S308)。

$$Cv = \left( \sum_{i=1}^n |H(i) - He(i)| \right) / n$$

その結果、誤差関数の値  $Cv$  が規定値よりも大きければ、各パラメータ  $R_c, K, 1/V$  ( $= K \cdot G / (P \cdot d)$ ) の値を変更してから、再度、再度、S306 以降の処理を実行する(S309)。各パラメータの変更は、例えば、最小二乗法によって行うことができる。 $1/V$  および  $K$  については、パラメータに関する微分式が得られるため、線形最小二乗法による変更を行うことができる。なお、本実施の形態では、 $R_c, K$  および  $1/V$  の値を変更しているが、 $R_c, K, G$  および  $d$  の値を変更してもよい。

#### 【0030】

一方、誤差関数の値  $Cv$  が規定値以下であった場合、すなわち、収束した場合には、S306 および S307 で用いたパラメータセット  $R_c, K, 1/V$  (最適パラメータセット) を用いて、さらに全分割領域における予測膜厚データ  $H_j$  を算出し、その算出結果をストレージ内のファイルに出力する(S310)。

そして、つぎの加工対象となる製品種「B」の半導体回路の設計データ  $b$  をストレージから読み込み、配線の形成に使用した露光マスクデータを、その設計データ  $b$  から抽出する(S311)。そのマスクデータと、S306 で用いたモデルと、最適パラメータセットとを用いて最適研磨時間を算出する(S312)。具体的には、チップ内の所定の位置(座

標  $r''$ )における膜厚が設定膜厚  $z''$  [nm]になるまでの研磨時間  $t''$  を、つぎの加工対象となる製品種「B」の最適研磨時間として算出する。ただし、モデルは、厳密解を得ることができないため、ニュートン法、二分法等の数値解法を用いて解く必要がある。

#### 【0031】

以上の研磨時間予測処理を研磨プロセスに適用することの妥当性を検討するため、A1配線(配線膜厚 500 nm)とA1配線を被覆したO<sub>3</sub>-TEOS酸化膜(H0 = 1000 nm)とを有する10 mm × 10 mmのテストチップ(チップ端部における設定膜厚 350 nm)が形成される製品種「A」「B」を用いて実験を行った。なお、テストチップに設定する分割領域を、10000個の、100 μm × 100 μmの正方形分割領域とし、膜厚計による測定位置を4点とし、S307で用いる規定値を10 nmとした。

10

#### 【0032】

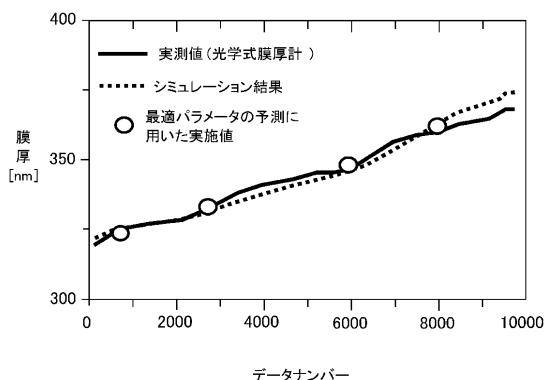

まず、S310で、製品種「A」のテストチップの全分割領域における予測膜厚データ H<sub>j</sub> が得られた時点で、製品種「A」のテストチップの全分割領域における膜厚を膜厚計で測定した。そして、製品種「A」のテストチップの全分割領域における予測膜厚データと、製品種「A」のテストチップの全分割領域における実測膜厚データとを、同一グラフ上に、値の小さな順番にプロットした。その結果、図6に示すようなグラフが得られた。誤差関数の値が10 nm以下となるように定めたパラメータセット R<sub>c, K, 1 /</sub> を用いることによって、チップの全領域における膜厚分布を、膜厚実測値と10 nm ~ 15 nm程度の誤差で再現できることが、このグラフより確認された。

20

また、S312において、ニュートン法を用いて、製品「B」の最適研磨時間を算出したところ、122 s となった。この最適研磨時間だけ製品「B」のO<sub>3</sub>-TEOS酸化膜を研磨し、チップ端部における残膜厚を測定した。その測定値と設定膜厚との誤差を算出した、12 nm程度に抑制されていることがわかった。

#### 【0033】

これらのことから、以上の研磨時間予測処理によれば、CMP装置の研磨特性が精度よく再現され、かつ、製品種「B」の最適研磨時間として適正な値が得られることが確認された。

#### 【0034】

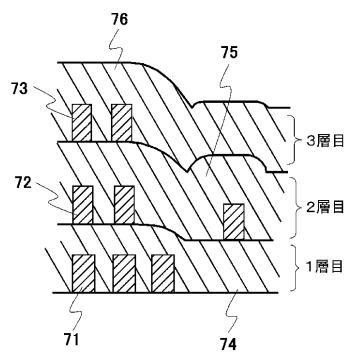

以上、単層の配線層を有するチップ(図5参照)が作り込まれた半導体ウエハを加工対象とする場合について説明したが、本実施の形態に係る研磨時間予測処理は、多層配線層を有するチップが作り込まれた半導体ウエハにも適用可能である。しかし、図9に示すように、多層配線層(ここでは一例として3層)の最上層76の表面には、最上層76に含まれているA1配線73の影響だけでなく、A1配線71, 72を含む下層74, 75の影響も受けて段差が生じている、このため、このような多層配線層を有する半導体ウエハを加工対象とする場合には、A1配線を含む配線層74, 75, 76の厚さ分布を足し合せ、その結果得られた厚さ分布から、研磨前の段差 h<sub>0</sub> を求める必要がある。なお、多層配線層のなかに、段差に影響を与えない層(例えば、厚さ分布の小さな層)が介在している場合には、その層の厚さ分布は、必ずしも、A1配線を含む配線層の厚さ分布に足し合せる必要はない。

30

#### 【0035】

その他については上述の場合と同様な条件を用いて、3層の配線層を有する10 mm × 10 mmのテストチップが作り込まれた半導体ウエハの最適研磨時間を求め、その最適研磨時間だけ3層の配線層を研磨した。これにより、3層の配線層が約800 nm研磨された。そして、研磨後の半導体ウエハの全分割領域(10000個)の残膜厚を測定し、その実測膜厚データとシミュレーションによる予測膜厚データとを比較したところ、誤差が10 nm程度に抑制されていることが確認された。このことから、本実施の形態に係る研磨時間予測処理は、積層膜の平坦化プロセスにも適用可能であることが判る。ところで、以上においては、膜厚計による複数の測定位置をあらかじめ任意に定めることとしたが、一定のルールにしたがって、膜厚計による測定位置を定めることにしてもよい。例えば、膜厚計による膜厚測定処理の効率化を図るために、膜厚計による測定位置を減

40

50

らしたい場合には、研磨後の残膜厚が最も大きく位置  $r_{max}$  および最も小さくなる位置  $r_{min}$  を、配線の露光マスクデータを用いたシミュレーションによってあらかじめ予測し、それら 2 つの位置を、膜厚計による測定位置とすることが望ましい。このような 2 つの位置を測定位置とすることの妥当性を検討するため、A1 配線(配線膜厚 500 nm)と A1 配線を被覆した O<sub>3</sub>-TEOS 酸化膜(H0 = 1000 nm)とを有する 10 mm × 10 mm のテストチップ(チップ端部における設定膜厚 350 nm)が形成される製品種を用いて実験を行った。なお、テストチップに設定する分割領域を、10000 個の、100 μm × 100 μm の正方形分割領域とし、膜厚計による測定位置を、研磨後の残膜厚が最大になる位置  $r_{max}$  と最小になる位置  $r_{min}$  の 2 点とし、S307 で用いる規定値を、10 nm とした。

10

#### 【0036】

そして、研磨後のテストチップの全分割領域において残膜厚を膜厚計で測定した。その結果、テストチップの全分割領域について、実測膜厚データと、最適パラメータセットを用いて得られた予測膜厚データとの誤差が、15 nm 以下に抑制されていることが判った。この誤差値と、膜厚計による測定位置を 4 点とした場合(図 6 参照)の誤差値とを比較すると、酸化膜の残膜厚が最大になる位置  $r_{max}$  と最小になる位置  $r_{min}$  の 2 点で残膜厚を測定すれば、4 点で残膜厚を測定した場合と遜色のない精度で残膜厚をシミュレートできることが判った。このことから、研磨後の残膜厚が最大になると予測された位置  $r_{max}$  と最小になると予測された位置  $r_{min}$  の最小 2 点で残膜厚を測定すれば、シミュレーションの精度を落とすことなく、膜厚計による膜厚測定処理の効率化を図ることができることが判る。また、研磨後の残膜厚が最大になる位置  $r_{max}$  と最小になる位置  $r_{min}$  の残膜厚をほぼ確実に再現できるため、テストチップ内の残膜厚のレンジを規格値以内にすることができる。

20

#### 【0037】

また、以上においては、研磨済み半導体ウエハのなかから、無作為に膜厚測定対象を選定していたが、膜厚測定対象の選定に一定のルールを設けてもよい。例えば、ある製品種のすべての半導体ウエハの研磨が終了したら、それら研磨済み半導体ウエハのうち、最後に研磨された半導体ウエハ、または、最後に研磨された半導体ウエハを含むロットのいずれかの半導体ウエハを膜厚測定対象として選定するようにしてもよい。

30

#### 【0038】

CMP 装置の特性(パッドの研磨速度、平坦化特性等)は、研磨枚数に応じて徐々に変化するが、このような選定ルールにしたがって膜厚測定対象を選定することによって、つぎの製品種の研磨開始直前の CMP 装置の特性をより正確に再現することができる。このため、つぎの製品種の半導体ウエハに対する最適研磨時間をより正確に予測することができる。また、複数枚の半導体ウエハを膜厚測定対象としなくとも、つぎの製品種の研磨開始直前の CMP 装置の特性をより正確に再現することができるため、複数の半導体ウエハを膜厚測定対象とする場合と比較して、膜厚測定に要する時間を短縮することができる。

#### 【0039】

以上のような選定ルールを採用した場合に図 8 の研磨システムで実行される処理のフローチャートを図 7 に示しておく。このフローチャートに示した処理は、加工済み製品種に属する半導体ウエハ群のなかから、最後に研磨された半導体ウエハまたは最後に研磨された半導体ウエハを含むロットのなかのいずれかの半導体ウエハを膜厚測定対象として選定する点(S201'、S205')においてのみ、図 1 のフローチャートに示した処理と相違する。この相違以外については、図 1 のフローチャートに示した処理と同様である。

40

#### 【0040】

以上、O<sub>3</sub>-TEOS 酸化膜を研磨対象とした場合を例に挙げたが、本実施の形態に係る研磨時間予測処理は、O<sub>3</sub>-TEOS 酸化膜だけでなく、プラズマ TEOS 酸化膜、高密度プラズマ CVD 膜、スピンドルコート絶縁膜、窒化シリコン膜、めっき Cu 膜、タンゲステン膜、タンタル膜、ルテニウム膜、窒化チタン膜等を研磨対象とする研磨プロセスにも適用可能である。また、O<sub>3</sub>-TEOS 酸化膜、プラズマ TEOS 酸化膜、高密度プラズ

50

マ C V D 膜、スピンドルコート絶縁膜、窒化シリコン膜、めっき Cu 膜、タンクステン膜、タンタル膜、ルテニウム膜、窒化チタン膜等を含む積層膜にも適用可能である。また、互いに異なる設計データに基づき加工された複数種類の加工物を生産する多品種少量生産プロセスの研磨プロセスにも適用可能である。

【図面の簡単な説明】

【0041】

【図1】本発明の実施の一形態に係る CMP プロセスのフロー チャートである。

【図2】本発明の実施の一形態に係る研磨時間予測処理を説明するためのフロー チャートである。

【図3】A1 配線が形成されたウエハ表面、および、A1 配線上に O<sub>3</sub>-TEOS 酸化膜を堆積させた場合のウエハ表面の拡大図である。 10

【図4】本発明の実施の一形態に係る研磨時間予測処理における、半導体チップの領域分割方法を説明するための図である。

【図5】研磨前の半導体製品の断面図である。

【図6】本発明の実施の一形態に係る CMP 後の半導体製品の膜厚分布を示した図である。 20

【図7】本発明の一実施の形態に係る CMP プロセスのフロー チャートである。

【図8】本発明の実施の一形態に係る研磨システムの概略構成図である。

【図9】CMP 前の半導体ウエハの断面図である。

【符号の説明】

【0042】

31...半導体チップ、32...分割領域、91...搬入系、92...搬出系、400...A1 配線、401...O<sub>3</sub>-TEOS 酸化膜、910...表示装置、911...情報処理装置、912...ストレージ、913...サーバ、914...CMP 装置コントローラ、920...入力装置、930...膜厚計、931...膜厚計コントローラ

【図1】

【図2】

【図3】

図3

白色部：凸領域

黒色部：凹領域。

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

【図8】

図8

【図9】

図9

---

フロントページの続き

(72)発明者 川崎 貴彦

神奈川県横浜市戸塚区吉田町 292 番地 株式会社日立製作所生産技術研究所内

F ターム(参考) 3C058 AA07 AC02 BA02 BA07 BA14 BB02 BB06 BB09 BC02 CA05

CB01 CB03 DA12 DA17