(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5371229号

(P5371229)

(45) 発行日 平成25年12月18日(2013.12.18)

(24) 登録日 平成25年9月27日(2013.9.27)

|                          |                     |

|--------------------------|---------------------|

| (51) Int.Cl.             | F 1                 |

| HO 1 L 21/20 (2006.01)   | HO 1 L 21/20        |

| HO 1 L 21/265 (2006.01)  | HO 1 L 21/265 Q     |

| HO 1 L 21/336 (2006.01)  | HO 1 L 21/265 602 B |

| HO 1 L 29/78 (2006.01)   | HO 1 L 21/265 602 C |

| HO 1 L 21/8238 (2006.01) | HO 1 L 29/78 301 S  |

請求項の数 17 外国語出願 (全 20 頁) 最終頁に続く

|              |                               |           |                                                                                                                                                                    |

|--------------|-------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2007-291240 (P2007-291240)  | (73) 特許権者 | 390040660<br>アプライド マテリアルズ インコーポレ<br>イテッド<br>A P P L I E D M A T E R I A L S, I<br>N C O R P O R A T E D<br>アメリカ合衆国 カリフォルニア州 95<br>054 サンタ クララ バウアーズ ア<br>ベニュー 3050 |

| (22) 出願日     | 平成19年11月8日 (2007.11.8)        | (74) 代理人  | 100109726<br>弁理士 園田 吉隆                                                                                                                                             |

| (65) 公開番号    | 特開2008-147633 (P2008-147633A) | (74) 代理人  | 100101199<br>弁理士 小林 義教                                                                                                                                             |

| (43) 公開日     | 平成20年6月26日 (2008.6.26)        |           |                                                                                                                                                                    |

| 審査請求日        | 平成22年10月13日 (2010.10.13)      |           |                                                                                                                                                                    |

| (31) 優先権主張番号 | 11/778, 212                   |           |                                                                                                                                                                    |

| (32) 優先日     | 平成19年7月16日 (2007.7.16)        |           |                                                                                                                                                                    |

| (33) 優先権主張国  | 米国 (US)                       |           |                                                                                                                                                                    |

| (31) 優先権主張番号 | 11/566, 058                   |           |                                                                                                                                                                    |

| (32) 優先日     | 平成18年12月1日 (2006.12.1)        |           |                                                                                                                                                                    |

| (33) 優先権主張国  | 米国 (US)                       |           |                                                                                                                                                                    |

最終頁に続く

(54) 【発明の名称】シリコンと炭素を含有するエピタキシャル層の形成及び処理

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上の Si : C エピタキシャル層を処理する方法であって、

基板上に炭素とシリコンを含有するエピタキシャル層が堆積されている基板を準備する

ステップであって、該炭素が格子間炭素と 0.5 原子 % を超える置換炭素を含む前記ステ

ップと、

該エピタキシャル層に、P、As、Si、Ge、及びそれらの組合せから選ばれた元素

をイオン注入するステップと、該イオン注入により、該エピタキシャル層の少なくとも一部

のアモルファス化が得られ、

該基板とエピタキシャル層を 800 ~ 1350 の温度で、900 ミリ秒未満の時間

アニールして、該エピタキシャル層内の格子間炭素の少なくとも一部を置換炭素に変換し

て、該置換炭素レベルを 0.5 原子 % を超えるまで増加させるステップと、

を含む前記方法。

## 【請求項 2】

イオン注入前の該層内の置換炭素と格子間炭素を合わせた総量が、0.5 ~ 2 原子

パーセントの範囲にある、請求項 1 に記載の方法。

## 【請求項 3】

イオン注入前の該エピタキシャル層内の置換炭素の量が 1 原子 % を超える、請求項 1 に

記載の方法。

## 【請求項 4】

10

20

該イオン注入が P、A s、S i、及びそれらの組合せから選ばれた元素を少なくとも  $1.5 \times 10^{-15} \text{ cm}^2$  の用量で含む、請求項 1 に記載の方法。

【請求項 5】

アニールが、動的表面アニール、レーザアニール、ミリ秒アニール、フラッシュアニール又はスパイクアニールの一つ以上によって行われる、請求項 1 に記載の方法。

【請求項 6】

該アニールの後、急速熱アニールが 10 秒未満行われる、請求項 1 に記載の方法。

【請求項 7】

該アニールの前、急速熱アニールが 10 秒未満行われる、請求項 1 に記載の方法。

【請求項 8】

該 S i : C エピタキシャル膜が、トランジスタ製造プロセスの製作ステップで形成され、該方法が、

基板上にゲート誘電体を形成するステップと、

該ゲート誘電体上にゲート電極を形成するステップと、

該電極の対向側の該基板上にソース/ドレイン領域を形成するとともに該ソース/ドレイン領域間にチャネル領域を画成するステップと、

該ソース/ドレイン領域の直上にシリコンと炭素を含有する該エピタキシャル層を堆積させるステップと、

を更に含む請求項 1 に記載の方法。

【請求項 9】

置換炭素と格子間炭素を合わせた総量が、1 原子パーセントを超える、請求項 8 に記載の方法。

【請求項 10】

注入前の該エピタキシャル層内の置換炭素量が、1 原子 % を超える、請求項 8 に記載の方法。

【請求項 11】

イオン注入が、P、A s、S i、及びそれらの組合せより選ばれた元素を少なくとも  $1.5 \times 10^{-15} \text{ cm}^2$  の用量で含む、請求項 8 に記載の方法。

【請求項 12】

アニールが、動的表面アニール、レーザアニール、ミリ秒アニール、フラッシュアニール又はスパイクアニールの一つ以上で行われる、請求項 8 に記載の方法。

【請求項 13】

該アニールの後、急速熱アニールが 10 秒未満行われる、請求項 8 に記載の方法。

【請求項 14】

該アニールの前、急速熱アニールが 10 秒未満行われる、請求項 8 に記載の方法。

【請求項 15】

注入とアニール後の該層内の置換炭素量が、0.5 原子パーセントを超える、請求項 8 に記載の方法。

【請求項 16】

イオン注入が、P、A s、及びそれらの組合せから選ばれる元素を用いて少なくとも  $1.5 \times 10^{-15} \text{ cm}^2$  の用量で多量にドープされたドレインを形成するように行われる、請求項 8 に記載の方法。

【請求項 17】

該トランジスタが、チャネルを持つ n M O S トランジスタを含み、該方法が、n M O S トランジスタの該チャネル内の引張歪みを増大させる、請求項 8 に記載の方法。

【発明の詳細な説明】

【関連出願】

【0001】

[0001] 本出願は、2006年12月1日出願の米国特許出願第 11/566,058 号の一部継続出願である2007年7月16日出願の米国特許出願第 11/788,212 号の

10

20

30

40

50

恩典を主張する。これらの開示内容は共に本明細書に全体で援用されている。

【背景】

【0002】

[0002]本発明の実施形態は、一般的には、シリコンと炭素 (Si : C) を含有するエピタキシャル層の形成及び処理に関する。個々の実施形態は、半導体デバイス、例えば、金属酸化物半導体電界効果トランジスタ (MOSFET) デバイスにおけるエピタキシャル層の形成及び処理に関する。

【0003】

[0003]典型的には、金属酸化物半導体 (MOS) トランジスタは、半導体基板と、ソースと、ドレインと、基板上のソースとドレインの間に位置するチャネルを含み、これは、普通、シリコンから製造されている。通常、ゲートスタックは、チャネルの上にあり、ゲートスタックは、チャネルの直上にあるゲート酸化物層又はゲート電極と、ゲート酸化物層の上のゲート導体材料と、側壁スペーサとから構成されている。側壁スペーサは、ゲート導体の側壁を保護する。ゲート電極は、一般的には、ドープされた多結晶シリコン (Si) から形成され、ゲート誘電材料は、二酸化シリコン (SiO<sub>2</sub>) 又は窒素ドープされた二酸化シリコン等の高誘電率材料 (例えば、4.0 を超える誘電率) の薄層 (例えば、< 20 オングストローム) を含むことができる。

【0004】

[0004]MOSトランジスタのチャネルに流れる電流量は、チャネル内のキャリアの移動度に正比例し、高移動度MOSトランジスタの使用はより電流が流れることを可能にし、結果としてより速い回路性能を可能にする。MOSトランジスタのチャネルにおけるキャリアの移動度は、チャネル内に機械的応力を生じることにより増加し得る。圧縮歪み下のチャネル、例えば、シリコン上で成長したシリコンは、pMOSトランジスタを得る大幅に高められたホール移動度を持つ。引張歪み下のチャネル、例えば、弛緩したシリコン-ゲルマニウム上で成長したシリコンチャネル薄層は、nMOSトランジスタを得る大幅に高められた電子移動度を達成する。

【0005】

[0005]引張歪み下のnMOSトランジスタチャネルもまた、ソースとドレイン領域内に一つ以上の炭素ドープされたシリコンエピタキシャル層を形成することにより設けることができ、それはpMOSトランジスタにおけるSiGeソースとドレインによって形成された圧縮歪みチャネルに補完的であってもよい。従って、炭素ドープされたシリコンとシリコン-ゲルマニウムエピタキシャル層は、各々nMOSとcMOSのトランジスタのソース/ドレイン上に堆積され得る。ソースとドレインの領域は、平坦か又は選択的Siドライエッティングによって埋め込まれ得る。正確に製造された場合、炭素ドープされたシリコンエピタキシーで覆われたnMOSソースとドレインは、チャネル内に引張歪みを加え、nMOS駆動電流を増加させる。

【0006】

[0006]炭素ドープされたシリコンエピタキシーを用いた埋め込まれたソース/ドレインを持つnMOSトランジスタのチャネルにおいて電子移動度の増大を達成するために、選択的な堆積か又は堆積後処理によってソース/ドレイン上に炭素ドープされたシリコンエピタキシャル層を選択的に形成することが望ましい。その上、炭素ドープされたシリコンエピタキシャル層がチャネル内の引張歪みを誘発する置換C原子を含有することが望ましい。より高いチャネル引張歪みは、炭素ドープされたシリコンソースとドレインにおける置換C含量の増加により達成し得る。しかしながら、典型的な選択的Si : Cエピタキシープロセス (例えば、プロセス温度 > 700 度) によって組込まれた炭素原子のほとんどが、Si格子の非置換 (即ち、格子間) 部位を占める。成長温度を下げることによって、より高い割合の置換炭素レベルを達成し得る (例えば、550 の成長温度で 100 % 近い) が、これらのより低い温度での緩慢な成長速度はデバイス適用に望ましくなく、このような選択的処理はより低い温度で可能なものではない。

【0007】

10

20

30

40

50

[0007] それ故、炭素ドープされたシリコンエピタキシャル層における置換炭素含量を改善する方法を提供することが求められている。

【概要】

【0008】

[0008] 本発明の一実施形態は、シリコンと炭素を含有するエピタキシャル層を形成し処理する方法に関する。他の実施形態は、シリコンと炭素を含有するエピタキシャル層を含む組立トランジスタデバイスの製造方法に関する。個々の実施形態において、高い置換炭素レベルの n-ドープされた Si : C を含有する nMOSトランジスタを形成する方法が提供される。

【0009】

10

[0009] 本発明の一実施形態によれば、基板上のシリコンと炭素を含有するエピタキシャル層を処理する方法であって、基板上に堆積された炭素とシリコンを含有するエピタキシャル層を持つ基板を準備するステップと、基板とエピタキシャル層を約 800 ~ 約 1350 の温度にアニールして、エピタキシャル層内の格子間炭素の少なくとも一部を置換炭素に変換するステップと、を含む前記方法が提供される。一実施形態によれば、置換炭素（初期に存在する場合には）と格子間炭素を合わせた総量は、約 0.5 原子パーセントを超える、個々の実施形態において、約 1 原子パーセントを超える、より具体的には約 2 原子パーセントを超える。

【0010】

20

[0010] 或る実施形態によれば、方法は、更に、エピタキシャル層をイオン注入するステップを含むことができる。イオン注入により、エピタキシャル層の少なくとも一部のアモルファス化を得ることができる。アモルファス化は、プレアモルファス化（例えば、Si を用いる）注入を含む典型的なアモルファス化手順によって達成され得る。ここに用いられるアモルファス化注入は、少なくともエピタキシャル層の一部のアモルファス化を引き起こす注入法を意味する。他の実施形態において、エピタキシャル層は、デバイスのソースとドレイン領域に形成される。ソースとドレインを含むデバイスの実施形態において、イオン注入は、深いソースとドレインの接合又はエピタキシャル層において置換炭素を増加させるプレアモルファス化注入を付随した深いソースとドレイン注入を形成するために用いられる同一条件を含むことができる。アモルファス化を含む実施形態において、アニールは一つ以上の動的表面アニール、レーザアニール、ミリ秒アニール、フラッシュアニール又はスパイクアニールによって行うことができる。一以上の実施形態において、アニールは 10 秒未満行われる。他の実施形態において、アニールは 900 ミリ秒未満行われる。例えば、アニールは、レーザアニール又はミリ秒アニールが 900 ミリ秒未満、例えば、10 ミリ秒未満行うのがよい。一以上の実施形態によれば、全体の順序、注入条件、アニール条件は、エピタキシャル層内の置換炭素を最大にするように選ばれる。

30

【0011】

[0011] 他の実施形態において、アニールは、レーザアニール又はミリ秒アニールが 900 ミリ秒未満、続いて急速熱アニールが 10 秒未満行われる。更に他の実施形態において、アニールは、急速熱アニールによって 10 秒未満、続いてレーザアニール又はミリ秒アニールが 10 秒未満行われる。

40

【0012】

[0012] Si : C エピタキシャル膜を形成する方法は、トランジスタ製造プロセスの組立ステップの間に用いることができる。発明の実施形態は、トランジスタの製造方法であって、基板上にゲート誘電体を形成するステップと、ゲート誘電体上にゲート電極を形成するステップと、電極の対向側に第二導電性を有するソース/ドレイン領域間を形成するステップと、ソース/ドレイン領域の間にチャネル領域を画成するステップと、ソース/ドレイン領域の直上にシリコンと炭素を含有するエピタキシャル層を堆積させるステップであって、炭素の一部が置換炭素であり、炭素の残りが格子間炭素である、前記ステップと、基板とエピタキシャル層を約 800 ~ 約 1350 の温度でアニールして、エピタキシャル層内の格子間炭素の少なくとも一部を置換炭素に変換するステップを含む、前記方法

50

に関する。或る実施形態において、置換炭素と格子間炭素の合わせた総量は、約0.5原子パーセントを超える、個々の実施形態において、約1原子パーセントを超える、更に個々の実施形態において、約2原子パーセントを超える。格子間と置換炭素の量は、約0.5～2原子パーセントの範囲であるのがよい。

【0013】

[0013]或る実施形態において、トランジスタの作製方法は、更に、エピタキシャル層へのイオン注入、続いてアニールするステップを含むのがよい。アニールは、ミリ秒アニール（例えば、動的表面アニール、レーザアニール、又はフラッシュアニール）又は急速熱アニール（例えば、スパイクアニール）によって行われるのがよい。上述のアニールの様は、トランジスタの製造に用いるのがよい。全体の順序、注入条件、アニール条件は、本発明の実施形態に従って、置換炭素含量が最大になるように選択される。

10

【0014】

[0014]上記は、本発明の或る特徴と技術的利点をむしろ広く述べてきた。開示された個々の実施形態は、本発明の範囲内で他の構造又はプロセスの変更又は設計に基づいて容易に用いることができるることは当業者によって理解されなければならない。このような等価な構成は、添付の特許請求の範囲に示された本発明の精神と範囲を逸脱しないこともまた、当業者によって認識されなければならない。

【0015】

[0015]上に挙げた本発明の特徴を詳細に理解することができるよう、上で簡単にまとめた本発明のより具体的な説明は、実施形態によって参照することができ、それらの一部が添付の図面によって示されている。しかしながら、添付の図面は、本発明の典型的な実施形態のみを示し、それ故、本発明の範囲を制限するものとみなすべきでなく、本発明は他の等しく有効な実施形態を許容することができる。

20

【詳細な説明】

【0016】

[0024]本発明の実施形態は、一般的に、シリコンと炭素を含有するエピタキシャル層を形成し処理する方法を提供する。他の実施形態は、トランジスタの製造の方法に関する。

【0017】

[0025]具体的な実施形態において、nMOSトランジスタのソースとドレイン領域においてSi:Cを形成する方法が提供される。個々の実施形態において、高置換Cはチャネル歪みに維持され、nMOSトランジスタについてはSi:Cがn-ドープ剤（例えば、P、As、又はそれらの組合せ）で多量にドープされる。エピタキシャルイオン注入後の手順が注入誘起損傷を引き起こし、Si:Cエピタキシャル層を劣化させる。注入誘起損傷により、結晶欠陥だけでなく置換Cの損失が生じ、それはチャネル歪み又はチャネル移動度、従ってデバイス性能に直接関係する。置換Cの損失を最小にするか、或いは注入後プロセス、例えば、ミリ秒アニールのような進歩したアニール、例えば、動的表面アニール（DSA）、レーザアニール、又はフラッシュアニールにより失われた置換Cを回復させる方法が提供されることが望ましい。ドープ剤の活性化に用いられる従来のスパイクアニールが置換Cの回復をするだけでなく、ミリ秒レーザアニール、特にDSAが失われた置換Cを回復させ、注入プロセスの前の開始エピタキシャル層を超えるレベルまで置換Cを増加させするのに非常に効果的であることを実験は明らかにした。本発明の一以上の実施形態によれば、堆積時のレベルか又は注入後のレベルからの置換Cのレベルは増加する。

30

【0018】

[0026]エピタキシャル層の形成し処理する方法は、基板上に堆積された炭素とシリコンを含有するエピタキシャル層を持つ基板を準備するステップであって、炭素が格子間炭素を含む、前記ステップと、基板とエピタキシャル層を約800～1350の温度でアニールして、エピタキシャル層における格子間炭素の少なくとも一部を置換炭素に変換するステップと、を含む。一実施形態において、トランジスタの製造方法は、基板上にゲート誘電体を形成するステップと、ゲート誘電体上にゲート電極を形成するステップと、電

40

50

極の対向側に第二度伝導性を有する基板上にソース/ドレイン領域を形成し、ソース/ドレイン領域の間のチャネル領域を画成するステップと、ソース/ドレイン領域の直上にシリコンと炭素を含有するエピタキシャル層を堆積するステップであって、炭素が格子間炭素を含む前記ステップと、基板とエピタキシャル層を約800～約1350の温度でアニールして、エピタキシャル層における格子間炭素の少なくとも一部を置換炭素に変換するステップと、を含む。エピタキシャル層は、バルク基板と多結晶シリコン層と区別される。

#### 【0019】

[0027]ここで用いられるエピタキシャル堆積は、基板上の単結晶層の堆積を意味するので、堆積された層の結晶構造は基板の結晶構造と適合する。従って、エピタキシャル層又は膜は、基板の結晶構造に適合する結晶構造を持つ単結晶層又は膜である。

10

#### 【0020】

[0028]発明の実施形態によれば、炭素とシリコンを含有するエピタキシャル膜の処理は、膜の置換C含量を増加させる。Si : C層内の置換C含量は、堆積時の非置換C原子を置換Si格子部位に変換することによって増加させ得る。本発明はいずれの特定の理論によっても縛られるものではないが、非置換(又は格子間)炭素原子の置換部位へのこのような変換が、空孔、自己格子間、他の関係のない格子間だけでなく欠陥クラスタのような点欠陥の分布に關係があると考えられる。最初の(堆積時)欠陥分布とシリコン格子をより多くの炭素原子に好都合な構造に変化させて、置換部位を占有することによって、置換C含量を増加させることができる。置換炭素の量を増加させることについて述べることは、本発明を、置換炭素を含有する堆積時膜に限定するものでないことは理解される。本発明の実施形態によれば、最初の堆積されたエピタキシャル膜は、置換炭素を含有しなくてもよく、本発明の実施形態によれば、格子間炭素を含む膜は、格子間炭素の量を減少させ、堆積時膜において置換炭素をゼロから増加させるように処理される。このような構造の変化と置換C含量の増加は、本明細書に記載されるプロセス順序によって達成され得る。

20

#### 【0021】

[0029]一以上の実施形態において、シリコンと炭素を含有するエピタキシャル膜は、更に後述される注入とアニールによって形成され処理される。エピタキシャル層は、選択的又は非選択的エピタキシャル層の堆積によって形成されてもよい。

30

#### 【0022】

[0030]一以上の実施形態において、置換C含量の増加は、以下の例示的なプロセス順序の注入とアニールの組合せによって達成され得る。(1)選択的又は非選択的堆積プロセスによる総炭素濃度が大きい(例えば、約0.5原子パーセントを超える、又は約1原子パーセントを超える)シリコンと炭素を含有する一つ又は複数のエピタキシャル層の堆積。(2)シリコンと炭素を含有するエピタキシャル層の、例えば、シリコンのようなイオンの注入によるアモルファス化。一般的には、エネルギーと用量がエピタキシャル層の少なくとも一部が注入後に格子結晶性を含まずにアモルファス化されるようなものであることが望ましい。(3)アニールを60秒未満、例えば、動的表面アニール、ミリ秒アニール又はレーザアニール、動的表面アニール(DSA)チャンバ。一以上の実施形態において、アニール温度は、10s～100s mm/sの範囲で種々のスキャン速度(又は滞留時間)で1000を超える。一以上の実施形態によれば、連続した順序、しかしながら、プロセスを行う方法は、上記の正確なステップに限定されない。例えば、他のプロセスは、プロセス順序の順序が維持される限りステップの間に挿入し得る。プロセスの個々のステップは、ここで、一実施形態に従って記載される。

40

#### 【0023】

##### 基板

[0031]基板は、典型的には、シリコン基板であり、パターン形成された基板であり得る。パターン形成された基板は、基板表面の中に又は上に形成された電子特徴部を含む基板である。パターン形成された基板は、単結晶表面と、少なくとも一つの単結晶ではない第二表面、例えば、多結晶又はアモルファス表面を含有することができる。単結晶表面は、

50

たいていシリコン、シリコンゲルマニウム又はシリコン炭素のような物質から作られたむき出しの結晶基板又は堆積された単結晶層を含む。多結晶表面又はアモルファス表面は、酸化物又は窒化物、特に酸化シリコン又は窒化シリコンのような誘電材料だけでなく、アモルファスシリコン表面を含むことができる。

【0024】

エピタキシャル堆積

[0032]シリコン炭素層は、例えば、Epi RP又はCentura、いずれもカリフオルニア州サンタクララ、アプライドマテリアルズ社から入手できる適切な処理チャンバにおいてエピタキシャルプロセスを用いて堆積させることができる。一般的には、プロセスチャンバは、エピタキシャルプロセス全体に一貫した温度に維持される。しかしながら、一部のステップは種々の温度で行うことができる。プロセスチャンバは、約250～1,000、例えば、約500～900の範囲の温度で保持される。エピタキシャルプロセスを行うのに適した温度は、シリコンと炭素を含有する物質を堆積及び/又はエッチングするために用いられる具体的な前駆物質に左右され、当業者によって決定され得る。プロセスチャンバは、通常は、約0.1トール～約200トールの圧力に維持される。圧力は、この堆積ステップの間に変動してもよいが、たいてい一定である。

【0025】

[0033]エピタキシャル堆積プロセスの間、基板を堆積ガスにさらして、第二表面上に多結晶層を形成しつつ、単結晶表面上にエピタキシャル層を形成する。堆積プロセスの個々の暴露時間は、エッチングプロセスの間の暴露時間だけでなく、プロセスに用いられる具体的な前駆物質と温度に関連して決定される。一般的に、基板は、堆積の間、容易にエッチングされ得る多結晶層の最小の厚さを形成しつつ、エピタキシャル層の最大の厚さを形成するのに十分長く堆積ガスにさらされる。

【0026】

[0034]堆積ガスは、少なくともシリコンソース、キャリアガス、炭素ソースを含有する。代替的実施形態において、堆積ガスは、少なくとも一つのエッチング剤、例えば、塩化水素又は塩素を含んでもよい。

【0027】

[0035]シリコンソースは、通常、約5sccm～約500sccm、例えば、約10sccm～約300sccm、特に約50sccm～約200sccm、更に特に約100sccmの範囲にある流量でプロセスチャンバへ供給される。シリコンと炭素を含有する化合物を堆積する堆積ガスに有用なシリコンソースとしては、シラン、ハロゲン化シラン、オルガノシランが挙げられるがこれらに限定されない。シランとしては、シラン(SiH<sub>4</sub>)及び実験式Si<sub>x</sub>H<sub>(2x+2)</sub>を有する高級シラン、例えば、ジシラン(Si<sub>2</sub>H<sub>6</sub>)、トリシラン(Si<sub>3</sub>H<sub>8</sub>)、テトラシラン(Si<sub>4</sub>H<sub>10</sub>)等が挙げられる。ハロゲン化シランとしては、実験式X<sup>1-y</sup>Si<sub>x</sub>H<sub>(2x+2-y)</sub>、(式中、X'=F、Cl、Br又はI)を有する化合物、例えば、ヘキサクロロジシラン(Si<sub>2</sub>Cl<sub>6</sub>)、テトラクロロシラン(SiCl<sub>4</sub>)、ジクロロシラン(Cl<sub>2</sub>SiH<sub>2</sub>)、トリクロロシラン(Cl<sub>3</sub>SiH)が挙げられる。オルガノシランとしては、実験式R<sub>y</sub>Si<sub>x</sub>H<sub>(2x+2-y)</sub>、(式中、R=メチル、エチル、プロピル又はブチル)を有する化合物、例えば、メチルシラン((CH<sub>3</sub>)SiH<sub>3</sub>)、ジメチルシラン((CH<sub>3</sub>)<sub>2</sub>SiH<sub>2</sub>)、エチルシラン((CH<sub>3</sub>CH<sub>2</sub>)SiH<sub>3</sub>)、メチルジシラン((CH<sub>3</sub>)Si<sub>2</sub>H<sub>5</sub>)、ジメチルジシラン((CH<sub>3</sub>)<sub>2</sub>Si<sub>2</sub>H<sub>4</sub>)、ヘキサメチルジシラン((CH<sub>3</sub>)<sub>6</sub>Si<sub>2</sub>)のような化合物が挙げられる。

【0028】

[0036]シリコンソースは、通常、キャリアガスと共にプロセスチャンバへ分配される。キャリアガスは、約1slm(標準リットル毎分)～約100slm、例えば、約5slm～75slm、特に約10slm～約50slm、例えば、約25slmの流量を持つ。キャリアガスとしては、窒素(N<sub>2</sub>)、水素(H<sub>2</sub>)、アルゴン、ヘリウム、それらの組合せを挙げることができる。不活性キャリアガスが好ましく、窒素、アルゴン、ヘリウ

10

20

30

40

50

ム及びそれらの組合せが挙げられる。キャリアガスは、用いられる一つ又は複数の前駆物質及び/又はエピタキシャルプロセス120の間のプロセス温度に基づいて選択することができる。通常、キャリアガスは各ステップ全体に同一である。しかしながら、一部の実施形態は、具体的なステップにおいて異なるキャリアガスを用いてもよい。

#### 【0029】

[0037]シリコンソースとキャリアガスと共にステップ120の間プロセスチャンバに供給して、シリコンと炭素を含有する化合物、例えば、シリコン炭素物質を形成する炭素ソースは、通常、約0.1sccm～約20sccm、例えば、約0.5sccm～約10sccm、更に特に約1sccm～5sccm、例えば、約2sccmの範囲の流量でプロセスチャンバへ供給される。シリコンと炭素を含有する化合物を堆積するのに有用な炭素ソースとしては、オルガノシラン、エチル、プロピル及びブチルのアルキル、アルケン及びアルキンが挙げられるがこれらに限定されない。このような炭素ソースとしては、メチルシラン( $\text{CH}_3\text{SiH}_3$ )、ジメチルシラン( $(\text{CH}_3)_2\text{SiH}_2$ )、トリメチルシラン( $(\text{CH}_3)_3\text{SiH}$ )、エチルシラン( $\text{CH}_3\text{CH}_2\text{SiH}_3$ )、メタン( $\text{CH}_4$ )、エチレン( $\text{C}_2\text{H}_4$ )、エチノ( $\text{C}_2\text{H}_2$ )、プロパン( $\text{C}_3\text{H}_8$ )、プロペン( $\text{C}_3\text{H}_6$ )、ブチン( $\text{C}_4\text{H}_6$ )等が挙げられる。エピタキシャル層の炭素濃度は、約200ppm～約5原子パーセント、例えば、約1原子パーセント～約3原子パーセント、更に特に少なくとも約2原子パーセント又は少なくとも約1.5原子パーセントの範囲である。一実施形態において、炭素濃度は、エピタキシャル層内でかえてもよく、好ましくはエピタキシャル層の上の部分よりエピタキシャル層の下の部分がより高い炭素濃度でかえてもよい。或いは、ゲルマニウムソースと炭素ソースは、いずれもシリコンと炭素を含有する化合物、例えば、シリコンゲルマニウム炭素物質を形成するために、シリコンソースとキャリアガスとともにプロセスチャンバへ添加することができる。

#### 【0030】

[0038]堆積プロセスを終了させる。一実施形態において、プロセスチャンバは、バージガス又はキャリアガスでフラッシュされるのがよく、及び/又はプロセスチャンバは真空ポンプによって排気されるのがよい。バージプロセス及び/又は排気プロセスは、過剰の堆積ガス、反応副生成物、他の汚染物質を除去する。他の一例において、堆積プロセスが終了すると、プロセスチャンバをバージ及び/又は排気せずにエッチングプロセスが直ちに開始される。

#### 【0031】

##### エッチング

[0039]所望のエッチングプロセスが行われてもよい。エッチングプロセスは、基板表面上のエピタキシャル層の一部を除去する。エッチングプロセスはエピタキシャル又は単結晶シリコン物質とアモルファス又は多結晶シリコン物質の双方を除去する。基板表面上に堆積された多結晶シリコン層があるとすれば、エピタキシャル層より速い速度で除去される。エッチングプロセスの持続時間は、基板上の所望の領域上に選択的に形成されたエピタキシャル層の正味の堆積を生じる堆積プロセスの持続時間と釣り合う。それ故、堆積プロセスとエッチングプロセスの正味の結果は、多結晶物質の成長があるとすれば最小にしつつ、選択的且つエピタキシャルに成長したシリコンと炭素を含有する物質を形成する。

#### 【0032】

[0040]エッチングプロセスの間、基板は約10秒～約90秒、例えば、約20秒～約60秒、更に特に約30秒～約45秒の範囲にある時間エッチングガスにさらされる。エッチングガスは、少なくとも一つのエッチング剤及びキャリアガスを含んでいる。エッチング剤は、通常、約10sccm～約700sccm、例えば、約50sccm～約500sccmの範囲にある速度でプロセスチャンバへ供給される。エッチングガスに用いられるエッチング剤としては、塩素( $\text{Cl}_2$ )、塩化水素( $\text{HCl}$ )、三塩化ホウ素( $\text{BCl}_3$ )、塩化メチル( $\text{CH}_3\text{Cl}$ )、四塩化炭素( $\text{CCl}_4$ )、三フッ化塩素( $\text{ClF}_3$ )、及びそれらの組合せを挙げることができる。好ましくは、塩素又は塩化水素がエッチング剤として用いられる。

10

20

30

40

50

## 【0033】

[0041]エッティング剤は、通常、キャリアガスと共にプロセスチャンバへ供給される。キャリアガスは、約1s1m～約100s1m、例えば、約5s1m～約75s1m、更に特に約10s1m～50s1m、例えば、約25s1mの範囲にある流量を持つ。キャリアガスは、窒素(N<sub>2</sub>)、水素(H<sub>2</sub>)、アルゴン、ヘリウム及びそれらの組合せを挙げることができる。ある実施形態において、不活性ガスが好ましく、窒素、アルゴン、ヘリウム及びそれらの組合せが挙げられる。キャリアガスは、エピタキシャルプロセスの間に用いられる一つ又は複数の個々の前駆物質及び/又は温度に基づいて選択することができる。

## 【0034】

[0042]エッティングプロセスを終了させる。一例において、プロセスチャンバは、バージガス又はキャリアガスでフラッシュすることができ、及び/又はプロセスチャンバは真空ポンプで排気することができる。バージ及び/又は排気プロセスは、過剰のエッティングガス、反応副生成物及びその他の汚染物質を除去する。他の一例において、エッティングプロセスが終了すると、プロセスチャンバをバージ及び/又は排気せずにエピタキシャル層の厚さが直ちに開始される。

## 【0035】

[0043]エピタキシャル層と多結晶層の厚さは決定することができる。所定の厚さが達成される場合には、エピタキシャルプロセスが終了する。しかしながら、所定の厚さが達成されない場合には、所望の厚さが達成されるまで堆積プロセスが一サイクルとして繰り返される。エピタキシャル層は、通常、約10オングストローム～約2,000オングストローム、例えば、約100オングストローム～約1,500オングストローム、更に特に約400オングストローム～約1200オングストローム、例えば、約800オングストロームの範囲の厚さを持つように成長される。多結晶層は、通常、厚さがあるとすれば、原子層～約500オングストロームの範囲で堆積される。シリコンと炭素を含有するエピタキシャル層又はシリコンと炭素を含有する多結晶層の所望の又は所定の厚さは、具体的な製造プロセスに特異的である。一例において、エピタキシャル層は所定の厚さに達することができるが、多結晶層は厚すぎる。

## 【0036】

## 堆積中のドープ剤暴露(又はインサイチュドープ)

[0044]堆積プロセスの間、エピタキシャル層は、所望により、ドープ剤にさらされてもいい。典型的なドープ剤としては、ホウ素、ヒ素、リン、ガリウム又はアルミニウムのような元素ドープ剤のソースを与える少なくとも一つのドープ剤化合物を挙げることができる。ドープ剤は、堆積されたシリコンと炭素を含有する化合物に電子デバイスが必要とする制御され所望された経路における方向性電子流のような種々の導電性特性を与える。シリコンと炭素を含有する化合物の膜を具体的なドープ剤でドープして、所望の導電性特性が達成される。一例において、シリコンと炭素を含有する化合物は、例えば、ジボランを用いて、約10<sup>15</sup>原子/cm<sup>3</sup>～約10<sup>21</sup>原子/cm<sup>3</sup>の範囲にある濃度でボロンを加えることによりp形にドープされる。一例において、p形ドープ剤は、少なくとも5×10<sup>19</sup>原子/cm<sup>3</sup>の濃度を持つ。他の例において、p形ドープ剤は、約1×10<sup>20</sup>原子/cm<sup>3</sup>～約2.5×10<sup>21</sup>原子/cm<sup>3</sup>である。他の例において、シリコンと炭素を含有する化合物は、約5×10<sup>19</sup>原子/cm<sup>3</sup>～約5×10<sup>21</sup>原子/cm<sup>3</sup>の濃度のリン及び/又はヒ素のようにn形にドープされる。

## 【0037】

[0045]ドープ剤ソースは、通常、堆積中プロセスチャンバに供給される。ドープ剤ソースとして有用なボロン含有ドープ剤としては、ボロン及び有機ボロンが含まれる。ボランとしてはボロン、ジボラン(B<sub>2</sub>H<sub>6</sub>)、トリボラン、テトラボラン及びペントボランが挙げられ、アルキルボランとしては、実験式R<sub>x</sub>BH<sub>(3-x)</sub>、(式中、R=メチル、エチル、プロピル又はブチル、x=1, 2又は3)の化合物が挙げられる。アルキルボランとしては、トリメチルボラン((CH<sub>3</sub>)<sub>3</sub>B)、ジメチルボラン((CH<sub>3</sub>)<sub>2</sub>BH)。

10

20

30

40

50

、トリエチルボラン( $(CH_3CH_2)_3B$ )及びジエチルボラン( $(CH_3CH_2)_2BH$ )が挙げられる。ドープ剤としても、実験式 $R_xPH_{(3-x)}$ (式中、 $R$ =メチル、エチル、プロピル又はブチル、 $x=1, 2$ 又は $3$ )のようにアルシン( $AsH_3$ )、ホスフィン( $PH_3$ )及びアルキルホスフィンが挙げられる。アルキルホスフィンとしては、トリメチルホスフィン( $(CH_3)_3P$ )、ジメチルホスフィン( $(CH_3)_2PH$ )、トリエチルホスフィン( $(CH_3)_3P$ )、ジメチルホスフィン( $(CH_3)_2PH$ )、トリメチルホスフィン( $(CH_3CH_2)_3PH$ )及びジエチルホスフィン( $(CH_3CH_2)_2PH$ )が挙げられる。

## 【0038】

## イオン注入

10

[0046]エピタキシャル層のイオン注入が行われ、それにより、エピタキシャル層の少なくとも一つのアモルファス化を得ることができる。イオン注入はソースとドレインのようなドープされた領域を形成するために用いることができ、それにより、エピタキシャル層のアモルファス化を得ることができる。例えば、これは、トランジスタの製造プロセスの一部として、少量に、また、多量にドープされたドレイン領域又はソースドレインエクステンション及びディープソースとドレインの形成の間に行われるのがよい。Si : Cソース/ドレインを含有するトランジスタのn形ドープについて、ドープ領域の厚さは、典型的には1000オングストローム未満である、所望のソース/ドレイン接合深さによって決められる。リン、ヒ素、又はこれら二つの組合せの注入は、典型的には、nMOSトランジスタのSi : Cのために用いられる。ピークドープ剤の不純物濃度は $1 \times 10^{20}$ 原子/ $cm^3$ 以上であるのがよく、ドープ量は $2 \times 10^{15}/cm^2$ 以上であるのがよい。一以上の実施形態において、プレアモルファス化として知られる追加のアモルファス化ステップは、Si、Ge又はAsイオン注入により行うことができるが、他の方法も使用し得る。アモルファス化の深さは、化学種を注入するイオンエネルギーによって決定される。当該技術において既知であるように、シリコン注入により結晶シリコン、例えば、 $1E15/cm^2$ のアモルファス化を引き起こすために最少量が必要とされる。

20

## 【0039】

[0047]シリコンと炭素を含有するエピタキシャル層のアモルファス化注入とドープ注入は、カリフォルニア州サンタクララのアプライドマテリアルズから入手できるQuantum注入機によって達成することができる。イオン注入は、置換SiとC原子を非置換部位に置き換えることによって、最初のSi : Cエピ層(結晶構造)の少なくとも一部をアモルファス化する。

30

## 【0040】

## アニール

[0048]本発明の一つ以上の実施形態によれば、エピタキシャル層はアニールされる。個々の実施形態において、アニールは、比較的短い時間、例えば、急速熱アニールチャンバ又は急速熱処理チャンバ内で行うことができる。ここに用いられる急速熱アニール(RTA)と急速熱プロセス(RTP)の双方は、試料を室温から高温、例えば、1200程度まで加熱する非常に短く、更に高度に制御された熱サイクルに試料を供するプロセスを意味する。RTP又はRTAの間の熱サイクルの持続時間は、典型的には、約60秒未満、典型的には約30秒未満である。或る実施形態において、RTP又はRTAの持続時間は、約20秒、15秒、10秒、又は5秒未満である。スパイクアニールは、試料を約10秒又は5秒未満の間高温にさらされるプロセスを意味する。例えば、スパイクアニールは、約800~1200の高温で約5秒未満行われるのがよい。ミリ秒アニールは、試料を室温から高温、例えば、1350程度に約900ミリ秒未満、より典型的には約500ミリ秒未満で加熱する熱サイクルに試料を供するプロセスを意味する。個々の実施形態において、約1000を超える高温のドウェル時間は約5ミリ秒以下である。ミリ秒アニールは、レーザアニール(例えば、アプライドマテリアルズの動的表面アニール)、フラッシュアニールによって達成され得る。名前が示すように、レーザアニールはレーザを用いて試料を加熱する。

40

50

## 【0041】

[0049]アニールプロセスとしては、急速熱アニール、急速熱プロセス、ミリ秒アニール、及び/又はスパイクアニール又はそれらの組合せのような急速熱プロセスを挙げることができる。アニール温度は、用いられるプロセスに左右されるものである。例えば、スパイクアニールは約1000～約1100の範囲にある温度、好ましくは約1050を持つのがよく、固相エピタキシーは500以上で行われるのがよい。

## 【0042】

[0050]アニールプロセスとしては、ガス雰囲気、例えば、酸素、窒素、水素、アルゴン、ヘリウム又はそれらの組合せでスパイクアニール、急速熱プロセス(RTP)の一種を挙げることができる。アニールプロセスは、約800～約1200、好ましくは約1050～約1100の温度で行われる。アニールプロセスは、シリコンと炭素を含有する層が堆積された直後又は基板が持ちこたえる種々の他のプロセスステップの直後に行うことができる。

## 【0043】

[0051]一実施形態において、スパイクアニールは、大気圧より著しく低いレベルのアニール雰囲気においてガス圧を維持することができるRTPシステムで行われる。このようなRTPシステムの一例は、アプライドマテリアルズ社、カリフォルニア州サンタクララから市販されるRADIANCE CENTURA(登録商標)システムである。スパイクアニールは、更に、2005年5月24日発行のADVANCE IN SPIKE ANNEAL PROCESSES FOR ULTRA SHALLOW JUNCTIONSと称する共同譲渡された米国特許第6,897,131号や2004年10月12日発行のOPTIMAL SPIKE ANNEAL AMBIENTと称する共同譲渡された米国特許第6,803,297号に述べられ、これらの開示内容は本明細書と特許請求の範囲と抵触しない程度まで本明細書に援用されている。

## 【0044】

[0052]1000を超えるアプライドマテリアルズDSAチャンバ/システムにおけるミリ秒アニール又はレーザアニールが優れた結果を得ることが見出された。ミリ秒アニール又はレーザアニールは、非置換C原子を置換部位に戻すのに十分なエネルギーを供給して、エピタキシャル層の置換炭素含量を増加させる。適切なDSAシステムの例は、米国特許第6,987,240号、同第7,005,601号、同第7,078,651号に開示され、これらの各々の開示内容は本明細書に援用されている。

## 【0045】

[0053]本発明のプロセスは、当該技術において周知の装置で行われ得る。装置は、プロセスチャンバに入る前に堆積ガスとその他のプロセスガスを維持するために複数のガスラインを含有してもよい。その後、ガスは、シリコンと炭素を含有する膜が成長する加熱された基板と接触する。シリコンと炭素を含有する膜を堆積するために使用し得るハードウェアとしては、カリフォルニア州サンタクララにあるアプライドマテリアルズ社から入手できるEpi Centura(登録商標)システムとPoly Gen(登録商標)システムが挙げられる。他の装置としては、当該技術において周知のバッチ、高温炉が挙げられる。

## 【実施例】

## 【0046】

## 実施例1

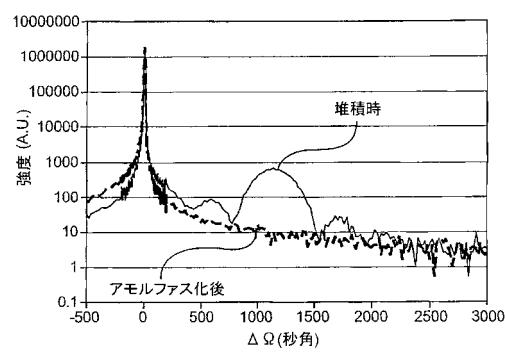

[0054]300mmのむき出しのシリコンウエハを、カリフォルニア州サンタクララのアプライドマテリアルズ社から入手できる300mm Epi Centura減圧チャンバ内に配置した。第一処理ステップの間に、500オングストローム厚のドープされていないSi:Cエピタキシャル膜を、300mmのむき出しのシリコンウエハ上に堆積した。堆積時Si:C膜は2.3%全Cを含有し、図1の高分解能X線回折計(HR-XRD)の測定において膜ピーク位置の約1200秒角によって示されるように1.04%のCが置換炭素であった。その後、第二処理ステップの間に、膜をアプライドマテリアルズのQu

10

20

30

40

50

a n t a u m X 注入機において 25 keV のイオンエネルギーと  $1.5 \times 10^{-5} \text{ cm}^2$  の用量で Si イオン注入に供した。Si 注入は、Si : Cepi 層をアモルファス化するために行われた。堆積時の Si : C 膜は、HRXRD ピーク約 1200 秒角が膜において 1.04% 置換 C に対応することを示すが、Si : C 膜のピークはシリコン注入後消失する。このことにより、結晶性の損失又はアモルファス化が示される。置換炭素は、本実施例と P.C.Kelires, Phys. Rev. B 55 (14), 8784 (1997) に記載されている Kelires モデルを用いたその他の実施例で決定した。この開示内容は本明細書に援用されている。

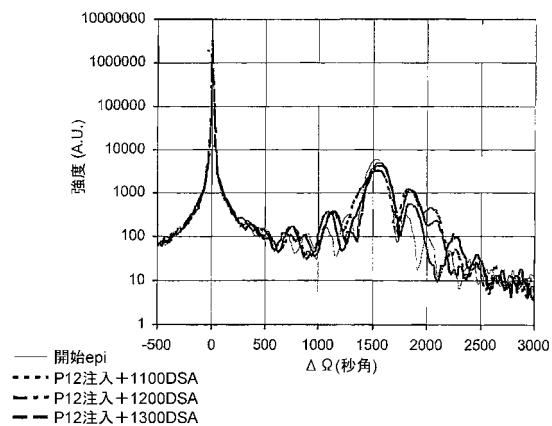

#### 【0047】

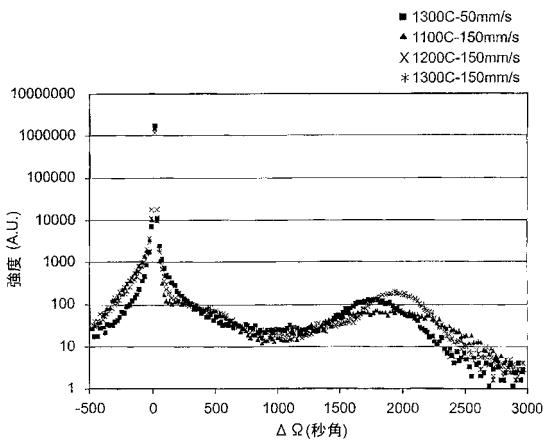

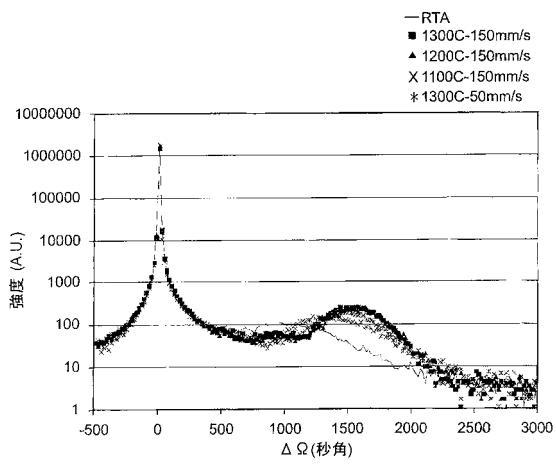

[0055] 図 1 は、シリコン注入後の高分解能 X 線回折計 (HR-XRD) スキャンが膜ピークを生じないことを示しているが、Si 基板に対応する 0 秒角の標準 Si ピークのみを示し、最初の結晶性 Si : C エピタキシャル層が存在しないことを意味する。その後、アモルファス化構造を、1100-1300 の温度範囲で 150 mm/s 又は 50 mm/s (0.5 ms 又は 1.5 ms のドウェル時間に対応する) スキャン速度でアプライドマテリアルズ社の動的表面アニールシステムにおいてアニールした。得られた HRXRD は図 2 に見られ、それは約 2000 のピークの出現を示し、DSA 後の約 1.75% の置換 C の結晶層の形成を意味する。試料 Si ウエハを、更に、Centurion RTP を用いて 1050 で 10% の O<sub>2</sub> と 90% の N<sub>2</sub> の雰囲気においてスパイクアニールとして処理した。図 3 にみられるように、アニール (DSA + スパイク) された試料の置換 C レベルは、堆積時レベルの 1.04% と比較して約 1.32% である。

#### 【0048】

##### 実施例 2

[0056] 図 2 は、1100-1300 の温度とスキャン速度 50-150 mm/s における動的表面アニール後の同一 Si : C 試料の XRD を示すグラフである。1.56-1.75% の置換 C に対応する 1800-2000 秒角の新しい膜ピークは、DSA 後に現れる。観測された 1.56-1.75% の置換 C は、図 1 に示された堆積時の Si : C 層の最初の 1.04% の置換 C 含量より多い。

#### 【0049】

##### 実施例 3

[0057] 図 3 は、提案された 3 ステップに続く 1050 のスパイクアニール後の Si : C 層の HRXRD を示すグラフである。1500 秒角のピーク位置は、図 1 に示された堆積時の含量の 1.04% より多い置換 C 含量の 1.32% を示している。動的表面アニールを含まない上記順序を通じて処理された試料は “RTA” と分類され、1000 秒角より下の膜のピーク位置を示し、0.88% 未満の置換 C を表している。受容した置換 C は、注入時の Si : Cepi 膜から増加したが、増加した置換 C は従来のスパイクアニールだけでは達成されなかった。増加した置換 C は、動的表面アニール又は表面アニールに続いてスパイクアニールによって達成された。

#### 【0050】

[0058] 従って、本実施例は、Si : C の増加した置換 C 含量が、活性化アニールの前に上記のプロセス順序を行うことにより 1050 までの従来のドープ剤活性化アニールの後でさえ堆積時の置換 C 含量を超えるレベルに維持されることを証明している。以上の実施形態によれば、増加した置換 C を維持するために提案された全体のプロセス順序は、Si : C エピタキシャル層堆積、続いて注入によるアモルファス化、続いて動的表面アニール、又は 1050 までの動的表面アニールとスパイクアニールの組合せである。

#### 【0051】

##### 実施例 4

[0059] 300 mm のむき出しのシリコンウエハを、カリフォルニア州サンタクララのアプライドマテリアルズ社から入手できる 300 mm Epi Centurion 減圧チャンバー内に配置した。1000 オングストローム厚のドープされていない Si : C エピタキシャル膜は、300 mm のむき出しのシリコンウエハ上に堆積した。堆積時の Si : C 層は、

10

20

30

40

50

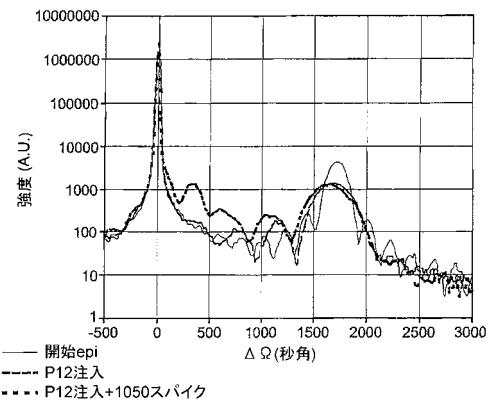

約 1.5 原子% の総 C を含有し、1.5 原子% の C は、図 4 において高分解能 X 線回折計 (H R - X R D ) の測定の膜ピーク位置約 1740 秒角によって示されるように置換炭素である。調製された e p i 膜に組込まれた置換 C 量は、 $7.5 \times 10^{15} / \text{cm}^2$  に対応する。その後、膜を、アプライドマテリアルズの Quantum X 注入機において 12 keV イオンエネルギーと  $4 \times 10^{15} \text{ cm}^2$  の用量でリンイオン注入に供した。注入条件は、適切なソースとドレインの接合の深さにより Si : C をドープするように選んだ。注入後、最上層 (この場合、~400 オングストローム) は損傷し、置換 C は損傷した層内で減少した。フリンジの消失と膜ピークの広がりは、膜の物理的变化を意味する。注入後に組込まれた置換 C 量は、約  $4 \times 10^{15} / \text{cm}^2$  である。その後、試料を CMOS トランジスタの製造に用いられる従来のアニール、詳しくは、アプライドマテリアルズの Radiance Plus において 1050 で 10% の O<sub>2</sub> / 90% の N<sub>2</sub> の雰囲気でスパイクアニールに供した。Si 基板のピーク付近でのピークの出現は、失われた置換 C の少量がスパイクアニールによって最上層に回復されたことを意味する。1500 秒角を超えるフリンジの消失 (注入とスパイクアニール後) は、最上層の置換 C の損失と結晶損傷を意味する。対応する組込まれた置換 C は、 $4 \times 10^{15} / \text{cm}^2$  を超えるが、 $5 \times 10^{15} / \text{cm}^2$  を超えない。

### 【0052】

#### 実施例 5

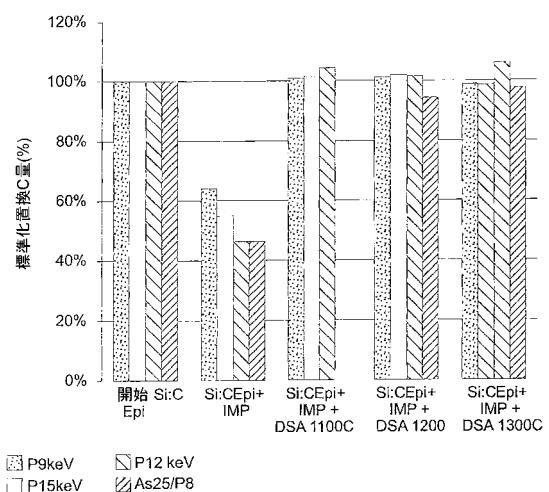

[0060] 出発 Si : C エピタキシャル層を、実施例 4 と同様の方法で調製した。堆積時の Si : C 膜は 1.42% の総 C を含有し、1.35% の C は、図 5 において高分解能 X 線回折計 (H R - X R D ) の測定の膜ピーク位置約 1500 秒角によって示されるように置換炭素であった。調製したエピタキシャル膜に組込まれた置換 C 量は、約  $7 \times 10^{15} / \text{cm}^2$  に対応する。その後、膜を実施例 4 における試料と同様の注入条件に供した (アプライドマテリアルズの Quantum X 注入機において 12 keV のイオンエネルギーと  $4 \times 10^{15} / \text{cm}^2$  の用量でリンイオン注入)。注入後、実施例 4 と同様に、最上層 (この場合、~400 オングストローム) は損傷し、置換 C は損傷した層では減少した。その後、試料をアプライドマテリアルズの動的表面アニールシステムを用いて 1100 ~ 1300 の温度、150 mm/s のスキャン速度でミリ秒アニールに供した。図 5 における H R X R D は、強いフリンジを示し、特にミリ秒アニール後の 1500 秒角の膜ピークを超え、高置換 C の存在を意味する。ミリ秒アニール後の対応する置換 C 量は、注入とアニール前の開始 Si : C e p i 層における置換 C 量に匹敵する約  $7 \times 10^{15} / \text{cm}^2$  であった。

### 【0053】

#### 実施例 6

[0061] 図 6 は、置換炭素含量に対するいくつかの試料の動的表面アニールの効果を示すグラフである。試料を種々の注入条件で調製し、1100 ~ 1300 の範囲の温度で D S A によりアニールした。図 6 は、注入後と 3 ステップのプロセス順序後の置換炭素含量と 300 mm のむき出しのシリコンウエハ上の堆積時のエピタキシャル層の置換炭素含量とを比較したグラフである。比較のために、各膜の置換 C は、e p i 層の上に組込まれ、用量として表され、堆積時の Si : C エピタキシャル膜における置換 C 量として標準化され、従って、開始 Si : C e p i 層は標準化された置換 C 量 (図 6 では y 軸) で 100 % に設定した。ウエハの各々を、カリフォルニア州サンタクララのアプライドマテリアルズ社から入手できる 300 mm の E p i C e n t u r a 減圧チャンバ内に配置した。100 オングストローム厚のドープされていない Si : C エピタキシャル膜を、300 mm のむき出しのシリコンウエハ上に堆積させた。最初の置換炭素含量を測定した。調製されたエピタキシャル膜の各々を、以下の四つ注入条件の一つに供した。 (i) 9 keV において  $4 \times 10^{15} / \text{cm}^2$  量のリン、(ii) 12 keV において  $4 \times 10^{15} / \text{cm}^2$  量のリン、(iii) 15 keV において  $4 \times 10^{15} / \text{cm}^2$  量のリン、(iv) 8 keV において  $2 \times 10^{15} / \text{cm}^2$  量のリンと 25 keV において  $2 \times 10^{15} / \text{cm}^2$  量におけるヒ素。n M O S トランジスタの製造において、注入条件は、ターゲットソースとドレイン

接合位置に適合するように選ばれ得る。例えば、Si : Cにおける12 keVの注入条件でのリンは、表面から約600オングストロームにおいて $2 \times 10^{18} / \text{cm}^3$ と $3 \times 10^{18} / \text{cm}^3$ のリン濃度による接合を生じる。より低いエネルギーはより浅い接合が生じるが、高いエネルギーはより深い接合が生じる。従って、これらの四つの注入条件はHDDの形成をまねるよう選ばれた。その後、四つの条件の一つで注入された各試料は、0.5ミリ秒ドウェル時間に対応する150mm/秒のスキャン速度でDSAを用いて異なる温度(1100、1200、又は1300)で処理した。全ての注入条件について、置換C量は、HDD注入の後、堆積時の用量の45-65%に減少するが、DSA処理後に94%以上に増加し、Si : C層においてDSAによる置換Cの有効な回復が証明される。

10

#### 【0054】

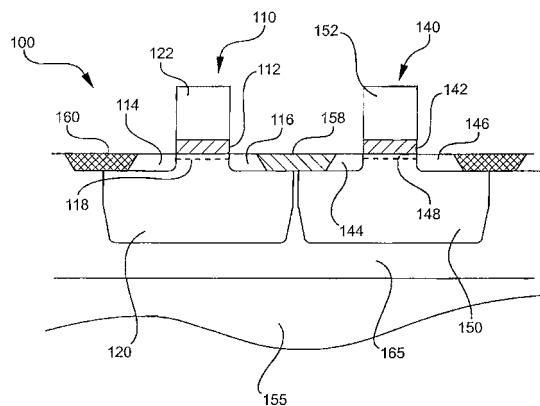

[0062]本発明の一つ以上の実施形態は、相補型金属酸化物半導体(CMOS)集積回路を形成するのに特に有用である方法を提供し、それに関連して記載される。他のデバイスと適用もまた本発明の範囲内である。図7は、典型的なCMOSデバイスにおいて一組のFETの断面図の一部を示す図である。デバイス100は、ウェルを形成してソース/ドレイン領域を設けた後の半導体基板と、ゲート誘電体と、NMOSデバイスとPMOSデバイスのゲート電極とを備えている。デバイス100は、従来の半導体プロセス、例えば、単結晶シリコンの成長及びトレンチエッティングによる浅いトレンチ絶縁構造の形成及びトレンチ開口部の誘電体の成長又は堆積を用いて形成し得る。これらの種々の構造を形成するための詳細な手順は、当該技術において既知であり、本明細書には更に記載されない。

20

#### 【0055】

[0063]デバイス100は、半導体基板155、例えば、p形物質でドープされたシリコン基板と、基板155上のp形エピタキシャル層165と、エピタキシャル層165内に画成されたp形ウェル領域120とn形ウェル領域150と、pウェル領域120内に画成されたn形トランジスタ(NMOSFET)110とnウェル150内に画成されたp形トランジスタ(PMOSFET)140を備えている。第一絶縁領域158はNMOS110とPMOS140トランジスタを電気的に絶縁し、第二絶縁領域160は基板155上の他の半導体デバイスからトランジスタ110と140の一組を電気的に絶縁する。

30

#### 【0056】

[0064]本発明の一以上の実施形態によれば、NMOSトランジスタ110は、ゲート電極122と、第一ソース領域114と、ドレイン領域116とを備えている。NMOSゲート電極122の厚さは、拡張可能であり、デバイス性能に関連する問題に基づいて調整することができる。NMOSゲート電極122は、n形デバイスの仕事関数に対応する仕事関数を持っている。ソースとドレイン領域は、ゲート電極122の対向側のn形領域である。チャネル118は、ソース領域114とドレイン領域116の間に置かれる。ゲート誘電体層112は、チャネル領域118とゲート電極122を分離する。NMOSゲート電極122と誘電体層を形成するためのプロセスは、当業者に既知であり、本明細書では更に述べない。本発明の実施形態によればSi : Cepi層は、ソース/ドレイン領域114又は116の一部又は全体を充填することになると理解される。

40

#### 【0057】

[0065]一以上の実施形態によれば、PMOSトランジスタ140は、ゲート電極152と、ソース領域144と、ドレイン領域146とを備えている。PMOSゲート電極152の厚さは、拡張可能であり、デバイス性能に関連する問題に基づいて調整することができる。PMOSゲート電極152は、p形デバイスの仕事関数に対応する仕事関数を持っている。ソースとドレイン領域は、ゲート電極152の対向側のp形領域である。チャネル148は、ソース領域144とドレイン領域146の間に置かれる。ゲート誘電体142は、チャネル領域148とゲート電極152を分離する。誘電体142はゲート電極152をチャネル領域148から電気的に絶縁する。図4に示され、直上に記載されたト

50

ンジスタ 110 と 140 の構造は、例示だけであり、物質、層等の種々の変形例は、本発明の範囲内である。

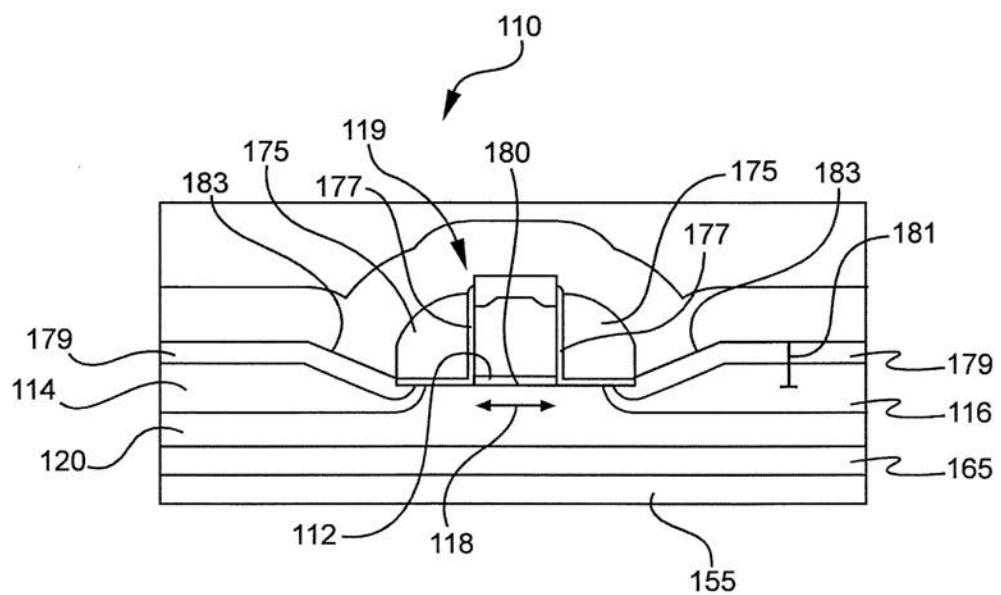

【0058】

[0066] ここで図 8 を参照すると、スペーサ、ソース/ドレイン領域の上の層、例えば、シリサイド層の形成と、エッティングストップの形成後の図 7 の NMOS デバイス 110 の詳細を更に示す図である。図 4 に示される PMOS デバイスが、更に以下に記載される NMOS デバイスのチャネルに生じる応力に影響する寸法及び/又は組成で調整することができる同様のスペーサと層を含有することができることは理解される。しかしながら、説明のために、NMOS デバイスだけが図示され、詳細に記載される。

【0059】

[0067] 図 8 は、ゲート 119 の周りに組込まれた適切な誘電材料から形成することができるスペーサ 175 を示す図である。オフセットスペーサ 177 もまた、設けられ、スペーサ 175 の各々を囲んでいる。スペーサ 175 と 177 の形状、サイズ、及び厚さを形成する方法は、当該技術において既知であり、本明細書に更に記載されない。金属シリサイド層 179 は、ソース領域 114 とドレイン領域 116 の上に形成することができる。シリサイド層 179 は、いずれの適切なプロセス、例えば、スパッタリング又は PVD (物理的気相堆積) によってもニッケル、チタン、又はコバルトのような適切な金属で形成することができる。シリサイド層 179 は、下に横たわる表面の一部に拡散することができる。ドレイン領域 116 の上昇は、矢印 181 で示され、基板表面 180 からシリサイド層 179 の最上部までの距離として示されている。ソースドレイン領域のファセット 183 は、角のある表面として示されている。当業者が理解するように、上記の例示的デバイスは、ソース/ドレイン又は本明細書に記載された方法に従って変更することができる Si : C エピタキシャル層を持つソース/ドレインエクステンションを含むように変更することができる。従って、本発明の実施形態は、注入の後に置換 C を回復することによる順序を行うことによって Si : C 層内の置換 C を最大にする方法を提供する。一実施形態のプロセス順序は、Si : C エピタキシャル堆積、続いて HDD 又はディープ S/D 注入、続いてミリ秒アニールを含んでいる。個々の実施形態において、開始エピタキシャル層は、約 1 原子% 以上の置換 C を含有し、注入/アニール順序の後の最後のエピタキシャル層は、約 1 原子% 以上の置換 C を含有する。一以上の実施形態において、アニール後の最終のエピタキシャル層に組込まれた C 量は、少なくとも約 90% の開始エピタキシャル層である。

【0060】

[0068] 注入は、nMOS のディープソース/ドレインの形成を含むことができ、多量にドープされたドレイン “HDD” としても知られる。例示的な注入条件としては、リンのみ、As/P の同時注入、又は As のみを含んでもよい。個々の例は、P のみ : 6 - 15 keV、As : 25 keV/P : 8 keV、As のみ : 25 keV 以上である。全量約  $4 \times 10^{15} / \text{cm}^2$ 。n 形の注入は、トランジスタ製造流れ (これは HDD ステップの間又は前であってもよい) において追加のアモルファス化注入 (例えば、Si) によって達成することができ、これにより、エピタキシャル層の少なくとも一部のアモルファス化が得られる。本発明は、特定の理論によってしばられるものではないが、注入はエピタキシャル膜損傷を引き起こし、エピタキシャル膜の少なくとも一部の置換 C を減少させる。結果として、堆積時の膜内に組込まれた置換 C は、注入後の置換 C を超える。

【0061】

[0069] 注入後のエピタキシャル膜を、例えば、ミリ秒アニールによってアニールする際に、置換 C は注入後のレベルから増加し、堆積時の置換 C レベル未満、そのレベルと匹敵する、又はそのレベルを超える最後の置換 C が得られる。上述したように、アニール順序は変動し得る。例えば、より低温のスパイクアニールは、以下の順序、Si : C エピタキシャル堆積、続いて HDD 又はディープ S/D 注入、続いてより低温のアニール、続いてミリ秒アニールのような、これらに限定されない順序で、挿入され得る。他の例において、このような順序でミリ秒アニール後にスパイクアニールを加えることができる : Si

10

20

30

40

50

：C エピタキシャル堆積に続いてH D D又はS / D注入、続いてD S A、続いてスパイクアニール。

【0062】

[0070]本明細書全体で“一実施形態”、“或る実施形態”、“一以上の実施形態”又は“実施形態”について述べることは、実施形態とともに記載される具体的な特徴、構造、物質、又は特性が本発明の少なくとも一実施形態に含まれることを意味する。従って、本明細書全体に種々の場所で“一以上の実施形態において”、“或る実施形態において”、“一実施形態において”又は“実施形態において”のような言葉の出現は、必ずしも本発明の同じ実施形態を意味しない。更に、具体的な特徴、構造、物質、又は特性は、一以上の実施形態においていかなる適切な方法で組み合わせてもよい。上の方法の記載の順序は10、限定するものとしてみなされるべきでなく、方法は、記載された操作の順序によらずに、又は省略又は追加して用いてもよい。

【0063】

[0071]上記は、例示のためのものであり、限定されることは理解されるべきである。多くの他の実施形態は、上記を再検討する際に当業者に明らかになるであろう。それ故、本発明の範囲は、このような特許請求の範囲が与える等価物の十分な範囲と共に、添付の特許請求の範囲によって決定すべきである。

【図面の簡単な説明】

【0064】

【図1】図1は、アモルファス化後のシリコンと炭素を含有するエピタキシャル層の構造変化を示すH R X R Dスペクトルである。20

【図2】図2は、アモルファス化し、1100～1300の温度で表面アニールした後のシリコンと炭素を含有するエピタキシャル層の構造変化を示すH R X R Dスペクトルである。

【図3】図3は、アモルファス化し、1100～1300の温度で表面アニールし、更にスパイクアニールで処理された後のシリコンと炭素を含有するエピタキシャル層の構造変化を示すH R X R Dスペクトルである。

【図4】図4は、P 12 k e V、 $4 \times 10^{15} / \text{cm}^2$ の注入後と、1050のスパイクアニール後の開始エピタキシャル層を示すH R X R Dスペクトルである。

【図5】図5は、開始エピタキシャル層とP 12 k e V、 $4 \times 10^{15} / \text{cm}^2$ の注入と1100、1200、1300でミリ秒レーザアニールで動的表面アニール後の処理を示すH R X R Dスペクトルである。30

【図6】図6は、種々のエネルギーレベルでPのみとAsとPの組合せを用いた注入と、1100～1300の動的表面アニールによって更に処理された試料について標準化された比較置換Cデータを示すグラフである。

【図7】図7は、本発明の実施形態の電界効果トランジスタの一組の断面図である。

【図8】図8は、デバイス上に形成された追加の層を持つ図1に示されたN M O S電界効果トランジスタの断面図である。

【符号の説明】

【0065】

100…デバイス、110…N M O S、114…ソース領域、116…ドレイン領域、118…チャネル領域、119…ゲート、120…p形ウェル領域、122…ゲート電極、140…P M O S、142…誘電体、144…ソース領域、146…ドレイン領域、150…n形ウェル領域、152…ゲート電極、155…基板、158…第一絶縁領域、160…第二絶縁領域、165…p形エピタキシャルシリコン層、175…スペーサ、177…オフセットスペーサ、179…シリサイド層、180…基板表面、183…ファセット。40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(51)Int.CI. F I

H 0 1 L 27/092 (2006.01) H 0 1 L 27/08 3 2 1 E

(72)発明者 チョ ヨナー

アメリカ合衆国, カリフォルニア州, サニーヴェール, ナンバー 427, イースト フレ

モント アヴェニュー 880

(72)発明者 キム イーワン

アメリカ合衆国, カリフォルニア州, ミルピタス, ヘヴンリー プレイス 825

審査官 河合 俊英

(56)参考文献 特開2007-201336 (JP, A)

特開平07-161731 (JP, A)

特開平08-111528 (JP, A)

(58)調査した分野(Int.CI., DB名)

H 0 1 L 21/20

H 0 1 L 21/265

H 0 1 L 21/336

H 0 1 L 21/8238

H 0 1 L 27/092

H 0 1 L 29/78