(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2014-0107221

(43) 공개일자 2014년09월04일

- (51) 국제특허분류(Int. Cl.)

**H04L 25/02** (2006.01)

(21) 출원번호 10-2014-7014688

(22) 출원일자(국제) 2012년11월01일

심사청구일자 없음

(85) 번역문제출일자 2014년05월30일

(86) 국제출원번호 PCT/US2012/062965

(87) 국제공개번호 WO 2013/067118

국제공개일자 2013년05월10일

(30) 우선권주장

61/554,223 2011년11월01일 미국(US)

- (71) 출원인

뉴랜스, 인코포레이티드.

미국 메사추세츠 01720 액톤 스위트 215 나고그

파크 43

(72) 발명자

垢타, 데브, 브이.

미국 메사추세츠 01742 콩코드 마티슨 드라이브

356

(74) 대리인

특허법인이상

전체 청구항 수 : 총 23 항

**(54) 발명의 명칭 광대역 신호 처리**

**(57) 요약**

본 발명의 예시적인 실시예는 50MHz에서 20GHz, 혹은 그 이상의 대역폭에 걸쳐 동작 가능한(예를 들어) 광대역 신호를 처리하기 위한 바이쿼드 회로를 포함한다. 상기 회로는 제 1 단계와, 제 2 단계를 포함할 수 있고, 상기 제 1 단계는 제 1 합산 회로와 제 1 복수의 적분기 라인을 포함한다. 상기 제 1 합산 회로는 각각의 상기 제 1 복수의 적분기 라인의 출력 뿐만 아니라, 입력 신호(예컨대, 처리될 광대역 신호)를 수신한다. 각각의 상기 적분기 라인은 직렬로 결합된 하나 이상의 적분기 회로를 포함하고, 상기 제 1 합산 회로의 출력을 수신한다. 상기 제 2 단계는 제 2 합산 회로와 제 2 복수의 적분기 라인을 포함한다. 상기 제 2 복수의 적분기 라인은 적어도 하나의 적분기 회로를 포함하고, 상기 제 1 합산 회로의 상기 출력을 수신한다. 상기 제 2 합산 회로는 각각의 상기 제 2 복수의 적분기 라인의 출력을 수신하고, 상기 바이쿼드 회로의 출력 신호를 생성한다.

추가적인 실시예에서, 상기 제 2 단계는 상기 제 1 합산 회로의 상기 출력을 상기 제 2 합산 회로의 상기 입력에 선택적으로 연결하도록 구성된 스위치를 포함할 수 있다. 상기 적분기 라인의 하나 이상의 상기 적분기 회로는 상기 바이쿼드 출력 신호의 조정을 일으킬 가변 이득을 포함할 수 있다. 상기 제 1 복수의 적분기 라인은 공통의 입력 노드에 연결될 수 있다. 마찬가지로, 상기 제 2 복수의 적분기 라인은 공통의 입력 노드에 연결될 수 있다. 각각의 상기 제 1 복수의 적분기 라인의 상기 출력은 제 1 합산 회로에서 반전될 수 있다. 마찬가지로, 각각의 상기 제 2 복수의 적분기 라인의 상기 출력은 상기 제 2 합산 회로에서 선택적으로 반전될 수 있다.

또 다른 실시예에서, 손실 패드는 상기 제 1 및 제 2 적분기 라인의 하나 이상의 적분기 회로 대신에 구현될 수 있다. 상기 손실 패드는 상술한 바와 같이 적분기 회로에 비교할 수 있는 방법으로 구성될 수 있다. 특히, 상기 손실 패드는 적분기 라인에 병렬로 연결될 수 있고, 공통의 노드에 연결될 수 있고, 반전되거나 선택적으로 반전된 합산 회로에 입력을 제공할 수 있다.

**대 표 도** - 도21

## 특허청구의 범위

### 청구항 1

광대역 신호를 처리하기 위한 회로로서, 제1단과 제2단을 포함하고,

상기 제1단은,

입력 신호를 수신하도록 구성된 제1 합산 회로; 및

상기 합산 회로의 출력을 수신하도록 구성된 복수의 제1 적분기 라인들을 포함하고, 상기 복수의 제1 적분기 라인들의 각각은 적어도 하나의 적분기 회로를 포함하며, 상기 제1 합산 회로는 상기 복수의 제1 적분기 라인들의 각각의 출력을 수신하도록 구성되고,

상기 제2단은,

상기 제1 합산회로의 출력을 수신하는 복수의 제2 적분기 라인들; 및

상기 복수의 제2 적분기 라인들의 출력을 수신하도록 구성된 제2 합산회로를 포함하고, 상기 복수의 제2 적분기 라인들의 각각은 적어도 하나의 적분기 회로들을 포함하고, 상기 제2 합산회로는 출력 신호를 출력하도록 구성된,

광대역 신호를 처리하기 위한 회로.

### 청구항 2

청구항 1에 있어서, 상기 제 2 단은,

상기 제 1 합산 회로의 상기 출력을 상기 제 2 합산 회로의 상기 입력에 선택적으로 연결하도록 구성된 스위치를 더 포함하는 광대역 신호를 처리하기 위한 회로.

### 청구항 3

청구항 1에 있어서,

상기 복수의 제1 적분기 라인들과 상기 복수의 제2 적분기 라인들의 상기 적어도 하나의 적분기 회로는 가변 이득을 가지는,

광대역 신호를 처리하기 위한 회로.

### 청구항 4

청구항 1에 있어서,

상기 복수의 제1 적분기 라인들과 상기 복수의 제2 적분기 라인들은 가변 이득을 가지는 복수의 적분기 회로들을 포함하는, 광대역 신호를 처리하기 위한 회로.

### 청구항 5

청구항 1에 있어서,

상기 복수의 제1 적분기 라인들과 상기 복수의 제2 적분기 라인들 중, 적어도 하나의 적분기 라인은 복수의 적분기 회로들을 가지는, 광대역 신호를 처리하기 위한 회로.

### 청구항 6

청구항 5에 있어서,

상기 적분기 회로들의 적어도 하나는 가변이득을 가지는,

광대역 신호를 처리하기 위한 회로.

### 청구항 7

청구항 1에 있어서,

상기 복수의 제1 적분기 라인들은 공통 입력 노드에 연결되는,

광대역 신호를 처리하기 위한 회로.

### 청구항 8

청구항 1에 있어서,

상기 복수의 제2 적분기 라인들은 공통 입력 노드에 연결되는,

광대역 신호를 처리하기 위한 회로.

### 청구항 9

청구항 1에 있어서,

상기 복수의 제1 적분기 라인들 각각의 출력은

상기 제 1 합산 회로에서 반전되는, 광대역 신호를 처리하기 위한 회로.

### 청구항 10

청구항 1에 있어서,

상기 복수의 제2 적분기 라인들 각각의 출력은,

상기 제 2 합산 회로에서 선택적으로 반전되는, 광대역 신호를 처리하기 위한 회로.

### 청구항 11

광대역 신호를 처리하기 위한 회로로서, 제1 단과 제2 단을 포함하고,

상기 제1 단은,

입력 신호를 수신하도록 구성된 제1 합산 회로;

상기 합산 회로의 출력을 수신하도록 구성된 제1 적분기 라인; 및

상기 제1 적분기 라인에 결합된 입력을 가지는 제1 손실 패드를 포함하고, 상기 제1 적분기 라인은 적어도 하나의 적분기 회로를 포함하고, 상기 제1 합산 회로는 상기 제1 적분기 라인의 출력을 수신하도록 구성되고, 상기 제1 합산 회로는 상기 제1 손실 패드의 출력을 수신하도록 구성되며,

상기 제2 단은,

상기 제1 합산 회로의 출력을 수신하도록 구성된 제2 적분기 라인;

상기 제2 적분기 라인에 결합된 입력을 가지는 제2 손실 패드; 및

상기 제2 적분기 라인과 상기 제2 손실 패드 각각의 출력을 수신하도록 구성된 제2 합산회로를 포함하고, 상기 제2 적분기 라인은 적어도 하나의 적분기 회로를 포함하고, 상기 제2 합산회로는 출력 신호를 출력하도록 구성된, 광대역 신호를 처리하는 회로.

### 청구항 12

청구항 11에 있어서,

상기 제 2 단은,

상기 제 1 합산 회로의 출력을 상기 제 2 합산 회로의 입력에 선택적으로 연결하도록 구성된 스위치를 더 포함하는, 광대역 신호를 처리하기 위한 회로.

### 청구항 13

청구항 11에 있어서,

상기 제 1 및 제 2 적분기 라인들의 상기 적어도 하나의 적분기 회로는,

가변 이득을 가지는, 광대역 신호를 처리하기 위한 회로.

#### 청구항 14

청구항 11에 있어서,

상기 제 1 및 제 2 적분기 라인들은,

가변 이득을 가지는 복수의 적분기 회로들을 각각 포함하는, 광대역 신호를 처리하기 위한 회로.

#### 청구항 15

청구항 11에 있어서,

상기 제1 및 제2 적분기 라인들 중 적어도 하나는 복수의 적분기 회로들을 포함하는, 광대역 신호를 처리하기 위한 회로.

#### 청구항 16

청구항 15에 있어서,

상기 복수의 적분기 회로들 중 적어도 하나는 가변 이득을 가지는, 광대역 신호를 처리하기 위한 회로.

#### 청구항 17

청구항 11에 있어서,

상기 제 1 손실 패드의 입력은, 제 1 적분기 회로의 출력과 상기 제 1 적분기 라인의 제 2 적분기 회로의 입력에 결합된 노드에 연결되는, 광대역 신호를 처리하기 위한 회로.

#### 청구항 18

청구항 11에 있어서,

상기 제 2 손실 패드의 입력은,

제 1 적분기 회로의 출력과 상기 제 2 적분기 라인의 제 2 적분기 회로의 입력에 결합된 노드에 연결되는, 광대역 신호를 처리하기 위한 회로.

#### 청구항 19

청구항 11에 있어서,

상기 제1 및 제2 손실 패드들 중 적어도 하나는

가변 손실 값을 가지는, 광대역 신호를 처리하기 위한 회로.

#### 청구항 20

청구항 11에 있어서,

상기 제 1 적분기 라인의 출력은,

상기 제 1 합산 회로에서 반전되는, 광대역 신호를 처리하기 위한 회로.

#### 청구항 21

청구항 11에 있어서,

상기 제 1 손실 패드의 출력은,

상기 제 1 합산 회로에서 반전되는, 광대역 신호를 처리하기 위한 회로.

## 청구항 22

청구항 11에 있어서,

상기 제 2 적분기 라인의 출력은,

상기 제 2 합산 회로에서 선택적으로 반전되는, 광대역 신호를 처리하기 위한 회로.

## 청구항 23

청구항 11에 있어서,

상기 제 2 손실 패드의 출력은,

상기 제 2 합산 회로에서 선택적으로 반전되는, 광대역 신호를 처리하기 위한 회로.

## 명세서

### 기술 분야

[0001]

본 발명은 광대역 신호를 처리하기 위한 기술에 관한 것으로, 더욱 상세하게는 더 큰 속도 및 대역폭 처리 능력을 갖춘 회로에 관한 것이다.

### 배경 기술

[0002]

신호 대역폭(signal bandwidths)과 데이터 전송률(data rates)의 증가는 광대역 신호(wideband signal)와 관련된 도전을 해결하는 새로운 신호 처리 기술의 발전을 일으켰다. 증가된 신호 대역폭은 이기종(heterogeneous) 환경에서의 초광대역(UWB, Ultra WideBand) 기술 기반의 액티브 무선 주파수 식별(RFID)을 포함한 새로운 애플리케이션들을 가능하게 만들었다. 덧붙여, 신호 대역폭의 증가는 레이더, 이미징 및 다른 애플리케이션들에 대해서 광대역 기술들을 특히 매력적으로 만들며, 레인징(ranging) 정확성을 향상시킨다.

[0003]

불행히도, 클럭 속도, 스위칭, 열 분산(heat dissipation) 및 장애 복구의 어려움에 대한 근본적인 스케일링 한계는 디지털 로직을 광대역 신호 처리에 부적합하게 만든다. 예를 들어, 오늘날의 DSP 기술은 고선명 TV, 소프트웨어 정의 라디오(SDR), 무선 인지(cognitive radio), 4G 휴대용 서비스, 화이트 스페이스, UWB 기반 서비스 및 실시간 GHz/THz 의료 영상과 같은 최근 생겨나는 애플리케이션에 필요한 광대역 신호를 처리 할 수 없다. 더 큰 속도 및 대역폭 처리 능력에 대한 필요성 이외에도, 전력 소비를 줄이기 위한 방법은 다수의 신호 처리 애플리케이션에서 큰 매력 및 유용성을 또한 갖는다. 예를 들어, 모바일 장치에서의 전력 소비는 중요하다. 고속 DSP는 휴대 전화 및 PDA의 배터리 수명을 단축시킨다.

[0004]

광대역 애플리케이션에 있어서, 나이퀴스트 율(Nyquist rates)은 초당 수기가(giga) 샘플 단위의 범위에 있게 되므로, 비교적 간단한 신호처리만이 구현될 수 있고, 고도로 파이프 라인되고 병렬적인 처리 아키텍처들을 필요로 할 수 있다. 앞으로, CMOS-기반 디지털 신호 처리 구조의 제한은 더 이상 무어의 법칙에 따라 확장되지 않기 때문에, DSP 기술은 이러한 애플리케이션에 의해 요구되는 능력에 도달하지 않을 것이다. 실제로, 딥 서브 마이크론(deep sub-micron) CMOS 게이트는 분자 단위로 측정되는 폭을 가지고 있어, 트랜지스터의 크기(및 스위칭 속도)가 그들의 근본적인 한계에 가까워지고 있다. 즉, 트랜지스터 크기에 반대되는 트랜지스터 스위칭 속도는 더 빨라질 수 없기 때문에, DSP 기술의 대역폭 프로세싱 능력을 증가시킬 여지가 거의 없다.

[0005]

다음으로, 아날로그 로직은 자신의 한계를 가지고 있다. 아날로그 회로는 엄밀하게 독립된 블록으로 형성되지 않으므로, 아날로그 로직 중 하나의 블록을 변경하는 것은 회로의 모든 다른 블록의 변화를 강제할 수 있다. 또한, 공정 기술의 발전은 너무 빨리 발생하여 애플리케이션에 특화된 디자인은 종종 그들이 제작되기 전에 시대에 뒤떨어지게 된다. 결국, 아날로그 회로는 완전히 재구성 가능(reconfigurable)하지도, 완전히 프로그래머블(programmable)하지도 않다.

### 발명의 내용

#### 해결하려는 과제

[0006]

위와 같은 문제점을 해결하기 위한 본 발명의 목적은 더 큰 속도 및 대역폭 처리 능력을 갖춘 바이쿼드 회로를

제공하는 데 있다.

[0007] 또한 아날로그 로직의 한계를 극복하여 재구성 가능하고 프로그래머블한 디지털 로직을 제공하는 데 있다.

### 과제의 해결 수단

[0008] 상기 목적을 달성하기 위한 본 발명의 일 실시예에 따른 광대역 신호를 처리하기 위한 회로는, 광대역 신호를 처리하기 위한 회로로서, 제1단과 제2단을 포함하고, 제1단은, 입력 신호를 수신하도록 구성된 제1 합산 회로와, 합산 회로의 출력을 수신하도록 구성된 복수의 제1 적분기 라인들을 포함하고, 복수의 제1 적분기 라인들의 각각은 적어도 하나의 적분기 회로를 포함하며, 제1 합산 회로는 복수의 제1 적분기 라인들의 각각의 출력을 수신하도록 구성되고, 제2단은, 상기 제1 합산회로의 출력을 수신하는 복수의 제2 적분기 라인들과, 복수의 제2 적분기 라인들의 출력을 수신하도록 구성된 제2 합산회로를 포함하고, 복수의 제2 적분기 라인들의 각각은 적어도 하나의 적분기 회로들을 포함하고, 제2 합산회로는 출력 신호를 출력하도록 구성될 수 있다.

[0009] 여기에서, 제 2 단은, 제 1 합산 회로의 출력을 제 2 합산 회로의 입력에 선택적으로 연결하도록 구성된 스위치를 더 포함하여 구성될 수 있다.

[0010] 여기에서, 복수의 제1 적분기 라인들과 복수의 제2 적분기 라인들의 적어도 하나의 적분기 회로는 가변 이득을 가질 수 있다.

[0011] 여기에서, 복수의 제1 적분기 라인들과 복수의 제2 적분기 라인들은 가변 이득을 가지는 복수의 적분기 회로들을 포함할 수 있다.

[0012] 여기에서, 복수의 제1 적분기 라인들과 복수의 제2 적분기 라인들 중, 적어도 하나의 적분기 라인은 복수의 적분기 회로들을 가질 수 있다. 나아가, 적분기 회로들의 적어도 하나는 가변이득을 가질 수 있다.

[0013] 여기에서, 복수의 제1 적분기 라인들은 공통 입력 노드에 연결될 수 있다.

[0014] 여기에서, 복수의 제2 적분기 라인들은 공통 입력 노드에 연결될 수 있다.

[0015] 여기에서, 복수의 제1 적분기 라인들 각각의 출력은, 제 1 합산 회로에서 반전될 수 있다.

[0016] 여기에서, 복수의 제2 적분기 라인들 각각의 출력은, 제 2 합산 회로에서 선택적으로 반전될 수 있다.

[0017] 상기 목적을 달성하기 위한 본 발명의 다른 실시예에 따른 광대역 신호를 처리하기 위한 회로는, 광대역 신호를 처리하기 위한 회로로서, 제1 단과 제2 단을 포함하고, 제1 단은, 입력 신호를 수신하도록 구성된 제1 합산 회로와, 합산 회로의 출력을 수신하도록 구성된 제1 적분기 라인과, 제1 적분기 라인에 결합된 입력을 가지는 제1 손실 패드를 포함하고, 제1 적분기 라인은 적어도 하나의 적분기 회로를 포함하고, 제1 합산 회로는 제1 적분기 라인의 출력을 수신하도록 구성되고, 제1 합산 회로는 제1 손실 패드의 출력을 수신하도록 구성되며, 제2 단은, 제1 합산 회로의 출력을 수신하도록 구성된 제2 적분기 라인과, 제2 적분기 라인에 결합된 입력을 가지는 제2 손실 패드와, 제2 적분기 라인과 제2 손실 패드 각각의 출력을 수신하도록 구성된 제2 합산회로를 포함하고, 제2 적분기 라인은 적어도 하나의 적분기 회로를 포함하고, 제2 합산회로는 출력 신호를 출력하도록 구성될 수 있다.

[0018] 여기에서, 제 2 단은, 제 1 합산 회로의 출력을 제 2 합산 회로의 입력에 선택적으로 연결하도록 구성된 스위치를 더 포함할 수 있다.

[0019] 여기에서, 제 1 및 제 2 적분기 라인들의 적어도 하나의 적분기 회로는, 가변 이득을 가질 수 있다.

[0020] 여기에서, 제 1 및 제 2 적분기 라인들은, 가변 이득을 가지는 복수의 적분기 회로들을 각각 포함할 수 있다.

[0021] 여기에서, 제1 및 제2 적분기 라인들 중 적어도 하나는 복수의 적분기 회로들을 포함할 수 있다. 나아가, 복수의 적분기 회로들 중 적어도 하나는 가변 이득을 가질 수 있다.

[0022] 여기에서, 제 1 손실 패드의 입력은, 제 1 적분기 회로의 출력과 제 1 적분기 라인의 제 2 적분기 회로의 입력에 결합된 노드에 연결될 수 있다.

[0023] 여기에서, 제 2 손실 패드의 입력은, 제 1 적분기 회로의 출력과 제 2 적분기 라인의 제 2 적분기 회로의 입력에 결합된 노드에 연결될 수 있다.

- [0024] 여기에서, 제1 및 제2 손실 패드를 중 적어도 하나는 가변 손실 값을 가질 수 있다.

- [0025] 여기에서, 제 1 적분기 라인의 출력은, 제 1 합산 회로에서 반전될 수 있다.

- [0026] 여기에서, 제 1 손실 패드의 출력은, 제 1 합산 회로에서 반전될 수 있다.

- [0027] 여기에서, 제 2 적분기 라인의 출력은, 제 2 합산 회로에서 선택적으로 반전될 수 있다.

- [0028] 여기에서, 제 2 손실 패드의 출력은, 제 2 합산 회로에서 선택적으로 반전될 수 있다.

### 도면의 간단한 설명

- [0029] 참조 부호처럼 다른 관점에 걸쳐 동일한 부분을 참조하는 첨부 도면에 도시된 바와 같이, 상술한 것은 본 발명의 예시적인 실시예의 다음의 보다 특별한 설명으로부터 명백할 것이다. 도면은 반드시 축척되지 않고, 강조는 대신에 본 발명의 실시예를 설명하기에 배치된다.

- 도 1은 바이쿼드 회로(biquad circuit)의 블록도이다.

- 도 2는 본 발명의 실시예에서 구현될 수 있는 적분기 회로(integrator circuit)의 회로도이다.

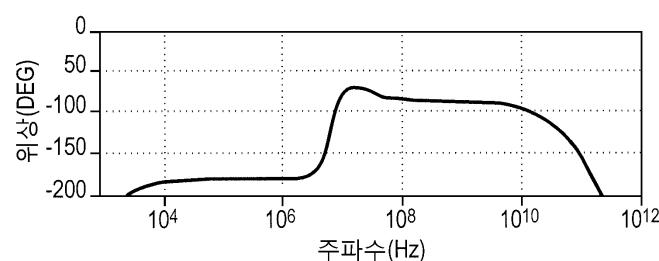

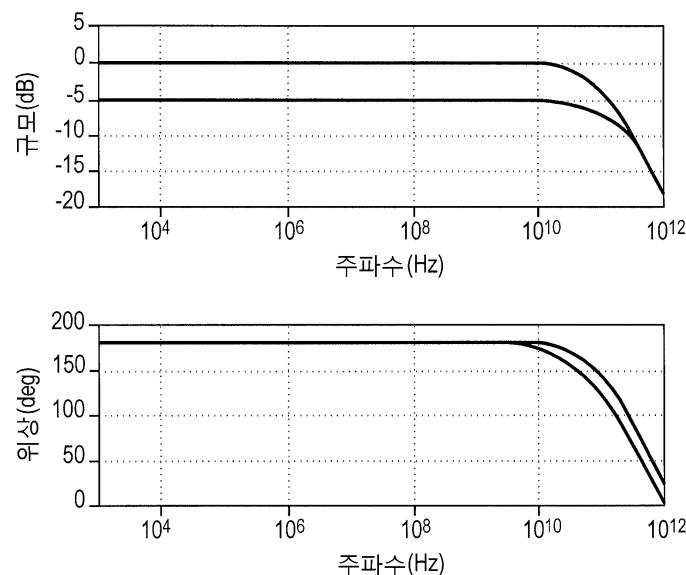

- 도 3은 도 2의 상기 적분기 회로의 주파수 응답(frequency response)을 나타낸 도면이다.

- 도 4는 전압 제어 저항기(voltage-controlled resistor)를 구현하는 적분기 회로의 회로도이다.

- 도 5는 추가적인 실시예에서의 적분기 회로의 회로도이다.

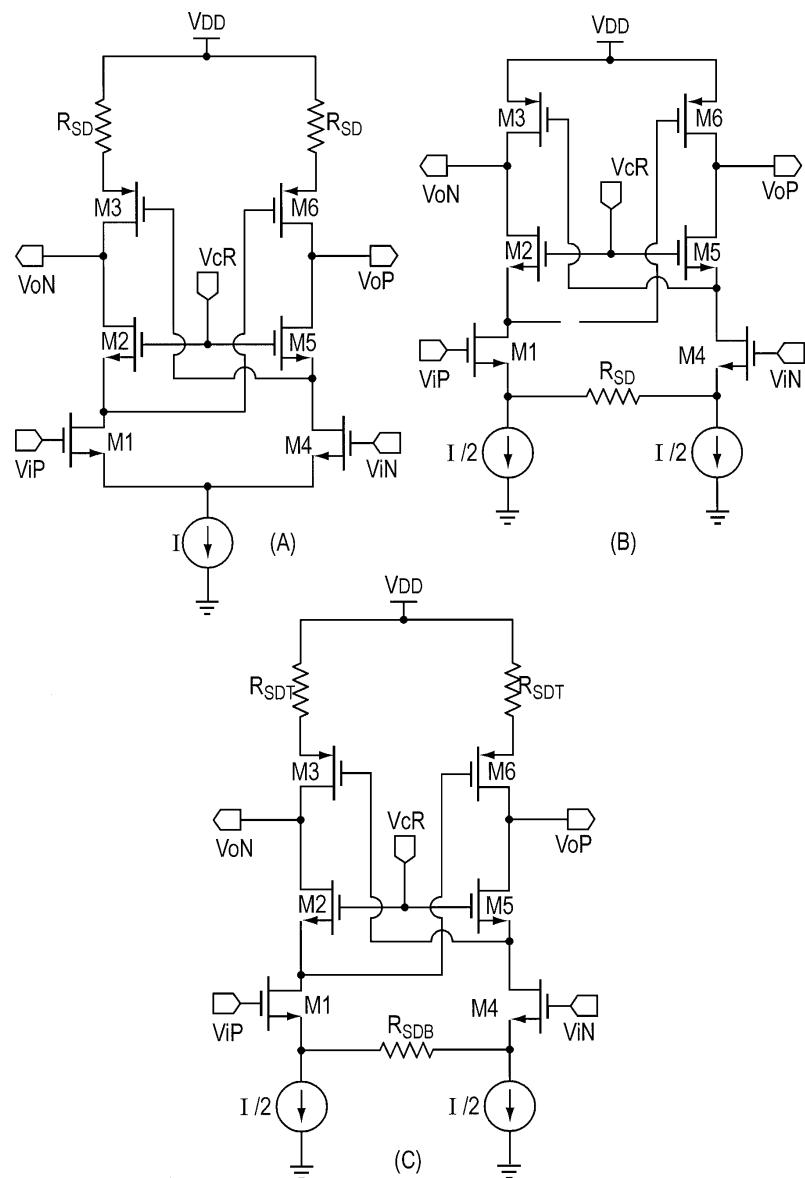

- 도 6(a)-(c)는 또 다른 실시예에서의 적분기 회로의 회로도이다.

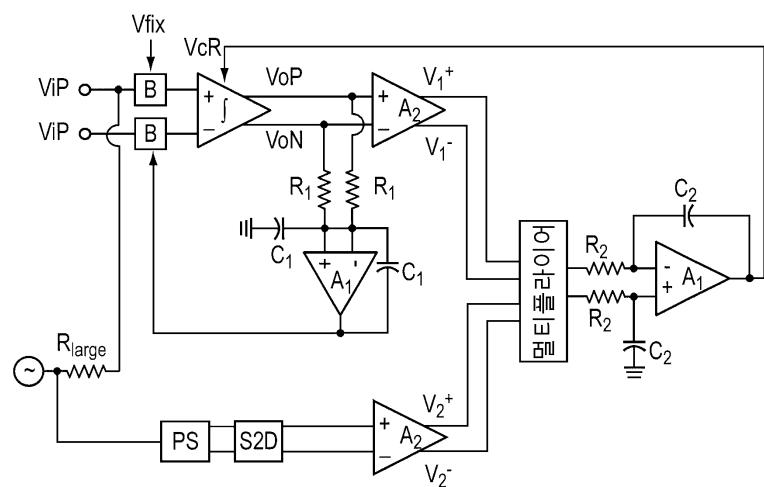

- 도 7은 튜너 회로(tuner circuit)로 구성된 적분기 회로의 회로도이다.

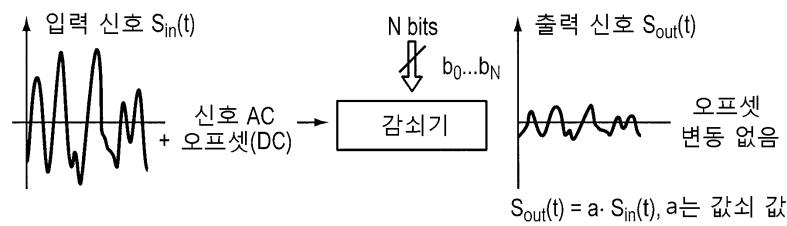

- 도 8은 감쇠기 회로(attenuator circuit)의 입력과 출력을 설명하는 블록도이다.

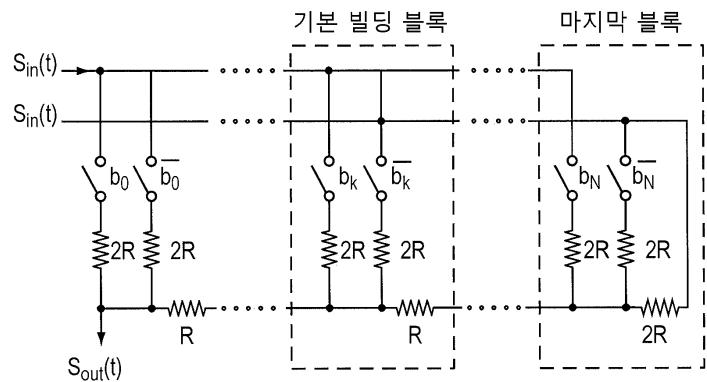

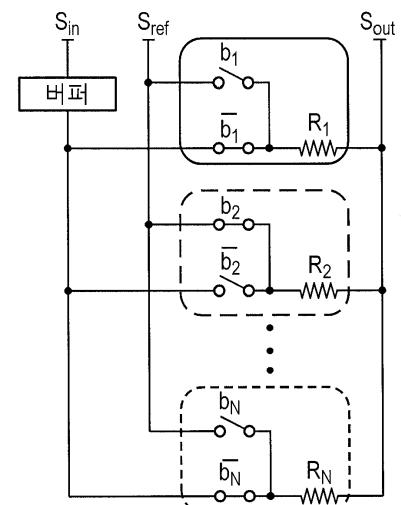

- 도 9는 감쇠기 회로의 회로도이다.

- 도 10은 본 발명의 실시예에서 구현될 수 있는 감쇠기 회로의 회로도이다.

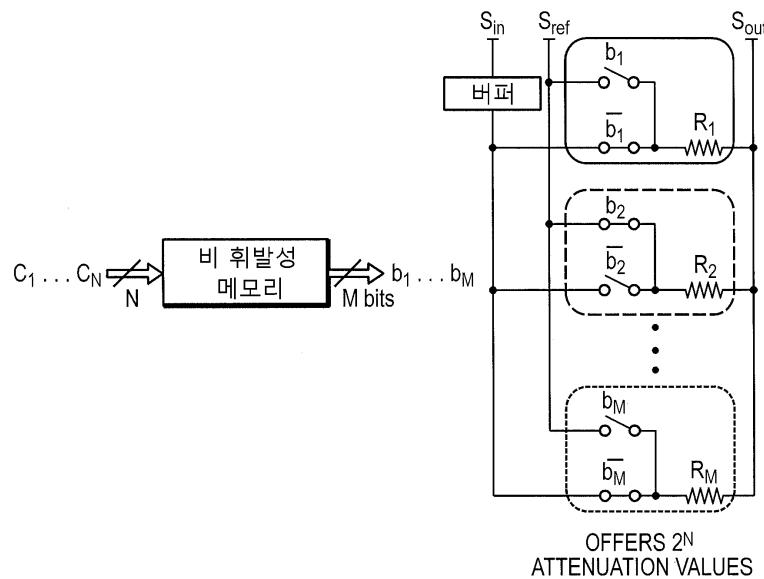

- 도 11은 추가적인 실시예에서의 감쇠기 회로의 회로도이다.

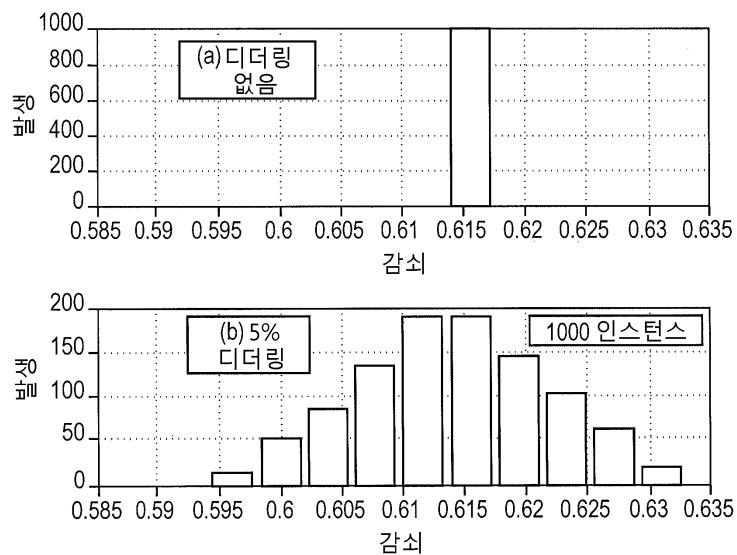

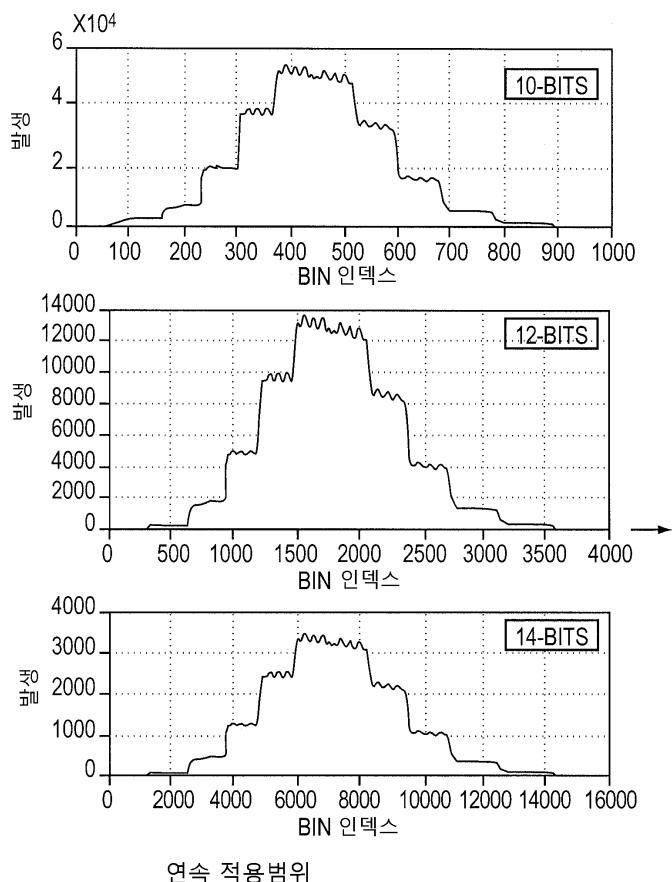

- 도 12는 감쇠 값의 분포를 설명하는 도면이다.

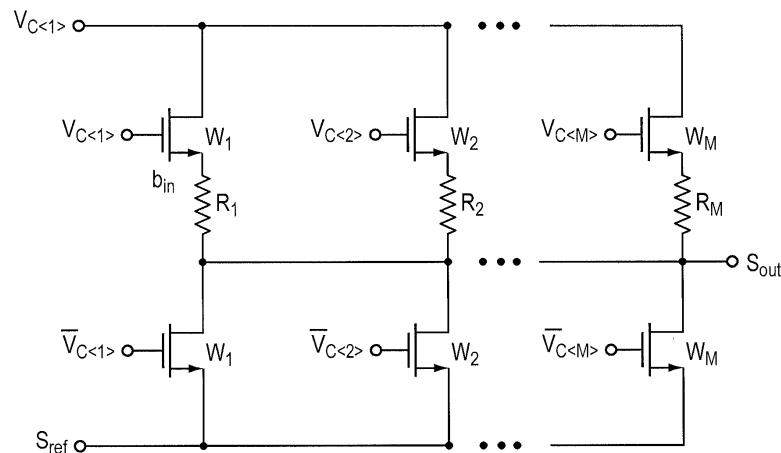

- 도 13은 추가적인 실시예에서의 감쇠기 회로의 회로도이다.

- 도 14는 감쇠기 회로의 다양한 구성에 상응하는 감쇠 값의 분포를 설명하는 도면이다.

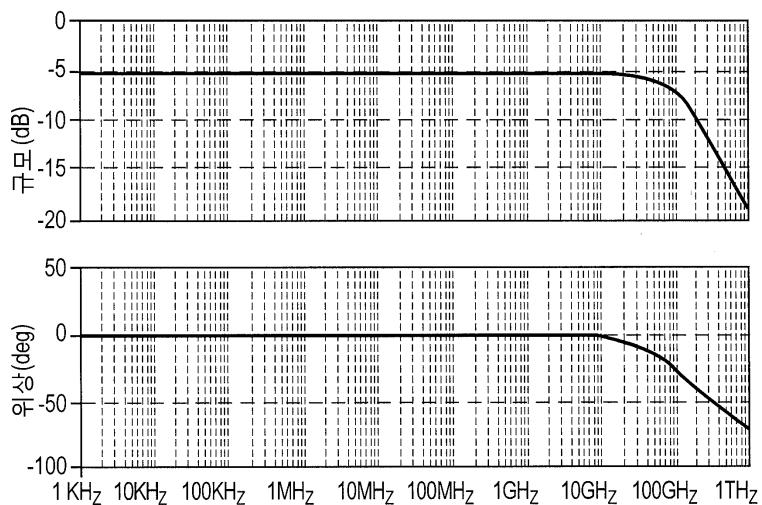

- 도 15는 감쇠기 회로의 규모(magnitude)와 위상(phase)을 설명하는 도면이다.

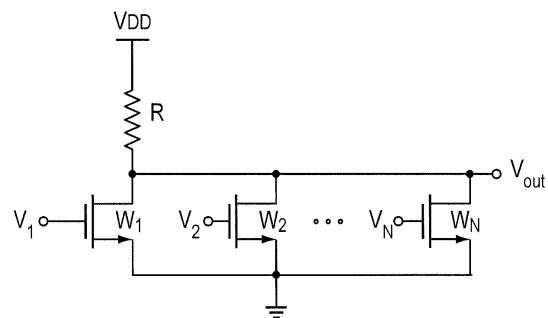

- 도 16은 본 발명의 실시예에서 구현될 수 있는 합산기 회로(summer circuit)의 회로도이다.

- 도 17은 출력 특성을 측정하도록 구성되는 회로의 회로도이다.

- 도 18은 합산 회로의 주파수 응답을 설명하는 도면이다.

- 도 19는 본 발명의 실시예가 구현될 수 있는 바이쿼드 회로의 구성의 블록도이다.

- 도 20은 하나의 실시예에서의 바이쿼드 회로의 블록도이다.

- 도 21은 추가적인 실시예에서의 바이쿼드 회로의 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0030] 본 발명의 예시적인 실시예들의 설명은 다음과 같다.

- [0031] 본 발명의 실시예는 Dev V. Gupta와 Divi Gupta의 미국 출원 번호 12/921,987에서 설명되고, 미국 특허 공개 2011/0051782로 공개되었으며, 그 전체가 여기에 참고로 인용된 바대로 광대역 신호 처리를 위한 방법 및 장치를 포함한다. 무선 주파수 광대역 아날로그 컴포넌트 블록의 실시예는 Dev V Gupta와 Zhiguo Lai의 국제 출원 번호 PCT/US2011/024542에 따라 그 전체가 여기에 참고 인용되어 구성될 수 있다.

- [0032] 광대역 신호 처리(WiSP, Wideband Signal Processing)는 아날로그 신호 처리 기술이다; 즉, 50MHz에서 20GHz

또는 그 이상 대역폭에 걸쳐 프로그래머블하고 실행 가능한 아날로그 컴퓨팅을 구현한다. WiSP의 기본적인 기초는 CMOS 딥 서브 마이크론 기술과 결합될 때, 저주파수 신호 처리 기술을 마이크론 내지 밀리미터 파장으로 연장하는 것을 가능하게 하는 상태 변수 이론(state variable theory)이다. WiSP는 Complementary-Metal-Oxide-Semiconductor(CMOS), Silicon Germanium(SiGe) 기술, 및 Silicon-On-Insulator(SOI) 기술로 실현될 수 있다.

[0033] 상태 변수 머신의 파라미터는 10비트의 정확도로 설정될 수 있기 때문에 WiSP는 매우 정확하다. WiSP는 또한 주파수 만능(frequency agile)이고, 이득(gain)과 같은 상태 변수 파라미터를 변경함으로써, 전체 주파수 대역에 걸치는 것을 가능하게 한다. 예를 들어, 1GHz의 주파수를 중심으로 한 상태 변수 머신은 이득 파라미터를 변경하여 10GHz의 주파수로 시프트될 수도 있다. WiSP 기술은 선형 시간 불변 신호 처리 및 시간 변화 신호 처리 모두에 적합하다. 상태 변수 시스템은 단일 입력/출력 모드와 다중 입력/다중 출력(MIMO, Multiple Input/Multiple Output) 모드에서 사용될 수 있다 - 예를 들어, MIMO 무선 안테나 시스템을 모방하여 -

[0034] 커패시터(capacitors) 및 저항기(resistors) 등과, 인쇄 회로 기판(PCB, Printed Circuit Board)에 이들을 연결하는 트레이스(traces)와 같은 컴포넌트들은 처리되는 신호의 파장에 비해 작기 때문에. 종래의 저주파 아날로그 설계는 대부분 비교적 간단하고 정확한 과학이다. 분산 효과(distributed effect)가 없기 때문에, 컴포넌트들은 집중 요소(lumped element)로 취급될 수 있다. 또한, 저주파 아날로그 컴포넌트는 전형적으로 신호 대역폭보다 큰(예를 들어, 적어도 10배) 대역폭을 가진다. 이 상대적으로 높은 대역폭은 설계를 단순화하고, 시스템을 안정화하고, 시스템 성능을 개선하고, 그들을 더 정확하게 하는 등의 피드백의 사용을 허용한다. 피드백은 프로그래머블한 하드웨어의 구현을 또한 허용한다; 예를 들어, 일부 프로그래머블한 저항기를 가진 연산 증폭기(on-amps)는 프로그래머블한 이득 장치를 구축하는데 사용될 수 있다. 따라서, 그러한 프로그래머빌리티는 프로그래머블 접근을 사용하여 복잡한 시스템을 만드는 것을 허용한다.

[0035] 불행히도, 고주파 신호의 파장은 회로 소자의 크기와 비슷하기 때문에 종래의 고주파수 설계는 동일한 장점을 허용하지 않는다. PCB 상에 소자들을 연결하는 트레이스는 고주파 신호의 파장에 필적하는 크기이다. 종래의 고주파 설계에서, 트레이스는 전송선으로 다루어지며 PCB 상의 반사 등을 방지하기 위해 필요한 수준 및 치수로 설계된다. 일반적으로, 그러한 설계는 매우 전력 깊주림(power hungry)하고, PCB의 재료들은 대역폭을 제한한다. 또한, 인쇄된 트레이스의 정확도 한계가 이러한 분산 요소들이 상호작용하는 것을 방지할 수 있다. 또한, 종래의 고주파수 설계는 매우 정확한 설계를 가능하게 하는 피드백의 사용을 허용하지 않는다.

[0036] 고주파수 파장과 CMOS 트레이스 크기의 비율은 저주파수 파장과 PCB 트레이스 크기의 비율과 거의 동일하기 때문에 PCB보다는 CMOS 기판에 광대역 아날로그 장치를 만드는 것이 저주파수 설계의 사용을 가능하게 한다. 사실, 딥 서브 마이크론 CMOS 기술을 사용하는 작은 트레이스 크기는 나노미터 스케일이고, 나노 미터 스케일에서, 모든 것은 요소로 간주될 수 있다; 사실상, 회로의 분산된 특성이 무시될 수 있다. 그래서, 컴포넌트 대역폭이 충분히 높지 않기 때문에 피드백이 여전히 사용할 수 없다는 사실을 제외하고 CMOS 기판 상에서의 고주파 설계는 PCB 상의 저주파 설계와 같은 것이다.

[0037] 여기에 개시된 실시예들은 피드백을 가진 고주파수 CMOS 설계를 가능하게 하는 데 필요한 높은 이득과 여분의 높은 대역폭을 제공한다. 기본이 되는 기본 요소는, 예를 들어, 80dB보다 크고, 100dB 또는 120dB까지 이르는 높은 이득 및 200GHz의 범위 내의 대역폭을 가진 트랜스컨덕터(transconductors)이다. 이러한 트랜스컨덕터는 또한 하나의 최하위 비트(LSB, Least Significant Bit)까지 정확한 감쇠기를 구축하기 위해 사용될 수 있다. 이러한 감쇠기는 10비트 정확도, 또는 1000에서 약 1 부분으로 디지털 프로그램될 수 있다. 이러한 정확성은 우리가 프로그래머블 아날로그 하드웨어를 구축하는 것을 허용한다.

[0038] 트랜스컨덕터 및 감쇠기를 광대역 스케일링 정보와 결합하는 것은 광대역 아날로그 프로세서를 구축하기 위한 기본 빌딩 블록인 바이쿼드(biquad)의 제조를 허용한다. 특히, 여기에 개시된 트랜스컨덕터, 감쇠기, 및 스케일러블 합산기는 주파수 만능(frequency agile) 및/또는 시간 변화성(time-variant)인 프로그래머블 바이쿼드 구조를 만드는 데 사용될 수 있다. 이러한 바이쿼드는 Gupta 등의 PCT/US2009/001512에 설명되고, 2009. 3. 10. 제출되고, WO2009/114123로 공개된 것처럼, 그 전체가 여기에 참고로 인용되어, 프로그래머블 전달 함수 합성기를 형성하기 위해 캐스캐이드 될 수 있다. 바이쿼드 기반의 회로는 레이더로부터 무선 인지, 무선 주파수 식별에 이르는 최종 사용을 위하여 민첩 필터(agile filter), 이퀄라이저, 지연 라인(delay lines) 등을 만들기 위해 사용될 수 있다.

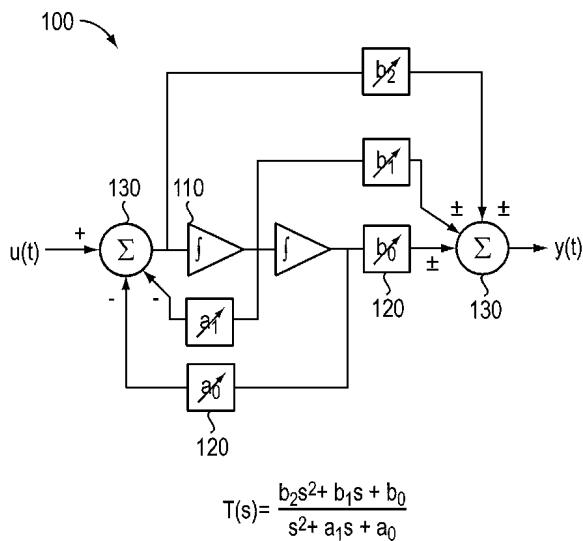

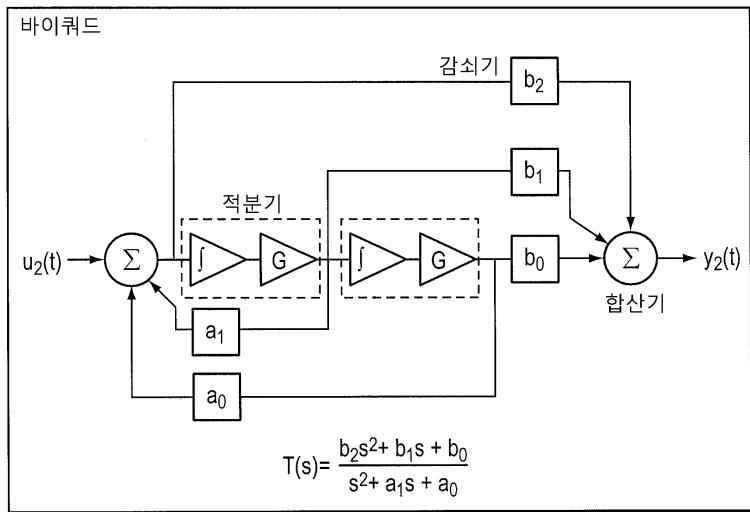

[0039] 도 1은 바이쿼드 회로(100)의 블록도이다. 바이쿼드 회로(100)는, 컴포넌트로서, 하나 이상의 적분기(110), 감쇠기(120) 및 합산기(130)를 포함한다. 바이쿼드 출력  $y(t)$ 의 특성은 바이쿼드(100)의 전달 함수(transfer function)  $T(s)$ 를 변경함으로써 바뀔 수 있다. 이는  $a_0, a_1, b_0, b_1$ 으로 구성되는 감쇠기(120)의 값을 변경함으

로써 달성된다. 전달 함수의 중심 주파수는 적분기(110)의 이득 G를 변경함으로써 스위핑된다. 감쇠기(120)의 값과 적분기(110)의 이득은 12비트 정확도를 가진 직렬 주변기기 인터페이스(SPI, Serial Peripheral Interface)에 의해 디지털 방식으로 제어될 수 있다.

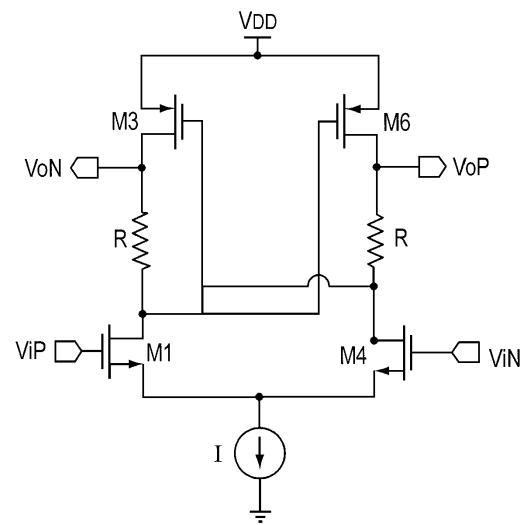

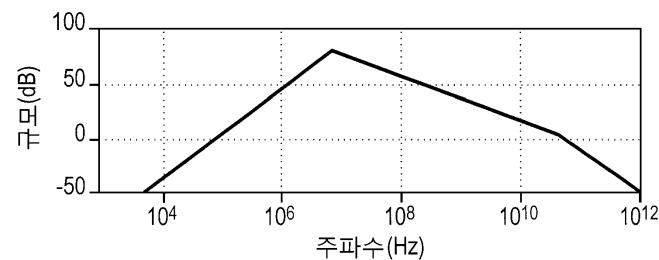

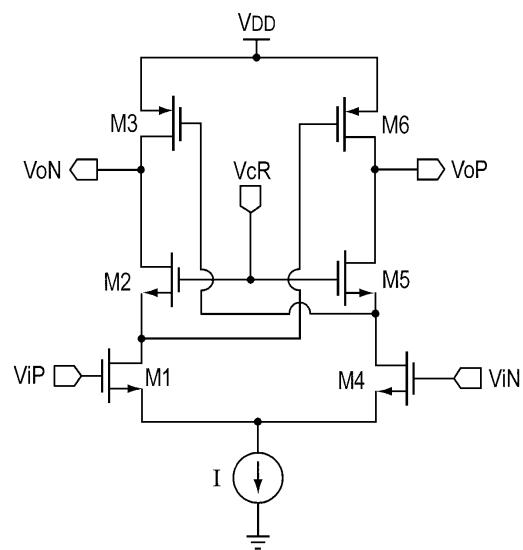

[0040] 도 2는 도 1의 바이쿼드 회로(100)에서 구현될 수 있는 적분기 회로(200)를 설명한다. 적분기(200)는 피드포워드-규제 토플로지(feedforward-regulated topology)를 사용하는 광대역 자기 조정 적분기(broadband self-tuned integrator)이다. 적분기(200)는 마이크로웨이브 주파수에서 애플리케이션에 특히 적합하도록 높은 대역폭, 높은 선형성과 낮은 상호변조 왜곡(intermodulation distortion)을 가지고 있다.

[0041] 작은 신호 분석은 이 회로의 전달 함수가 다음의 형태임을 보여준다:

$$T(s) = \frac{\Omega_0 \cdot (s/z_1 - 1) \cdot (s/z_2 - 1)}{s \cdot (s/p + 1) + a_0}$$

[0042] 여기에서,

$$z_1 = \frac{g_{m1}}{C_{gd1}}$$

$$z_2 = \frac{(g_{m3} + 1/R)}{C_{gd3}}$$

$$\Omega_0 = \frac{g_{m1} \cdot (g_{m3} + 1/R)}{(C_{gs3} + C_{gd3} + C_{gd1} + C_{ds1}) \cdot (g_{ds3} + 1/R) + (C_{gd3} + C_{ds3}) \cdot (g_{ds1} + 1/R) + C_{gd3} \cdot (g_{m3} + 2/R)}$$

$$p = \frac{(C_{gs3} + C_{gd3} + C_{gd1} + C_{ds1}) \cdot (g_{ds3} + 1/R) + (C_{gd3} + C_{ds3}) \cdot (g_{ds1} + 1/R) + C_{gd3} \cdot (g_{m3} + 2/R)}{(C_{gs3} + C_{gd3} + C_{gd1} + C_{ds1}) \cdot (C_{gd3} + C_{ds3}) - C_{gd3}^2}$$

$$a_0 = \frac{(g_{ds1} + 1/R) \cdot (g_{ds3} + 1/R) - (g_{m3} + 1/R)/R}{(C_{gs3} + C_{gd3} + C_{gd1} + C_{ds1}) \cdot (g_{ds3} + 1/R) + (C_{gd3} + C_{ds3}) \cdot (g_{ds1} + 1/R) + C_{gd3} \cdot (g_{m3} + 2/R)}$$

[0046] 저항기 R은 일반적으로  $1/gm1$ ,  $1/gm3$ ,  $1/gds1$ , 및  $1/gds3$ 과 비교하여 작은 것으로 선택된다. 딥 서브 마이크론 CMOS 기술의 경우(예를 들어 130나노미터 이하),  $C_{gs}$ 가 모든 기생 캐패시턴스(parasitic capacitance)을 지배하는 것이 통상적으로 사실이다. 이러한 관점에서, 우리는:

$$z_1 > \frac{g_{m1}}{C_{gs1}} \approx 2\pi \cdot f_T$$

$$z_2 > \frac{1}{R \cdot C_{gd3}}$$

$$p \approx \frac{1}{R \cdot C_{gd3}}$$

[0048] 를 일반적으로 큰 단일 이득 주파수인  $f_T$ 와 함께 가지고 있다. 작은 R에 대하여,  $z_2$ 와 p는 일반적으로 매우 크다. 전달 함수는 따라서 다음과 같이 근사화 될 수 있다

$$T(s) \approx \frac{\Omega_0}{s + a_0}$$

[0050] R이 다음과 같이 선택되면  $a_0=0$ 임을 참고하라

$$R = \frac{g_{m3} - g_{ds1} - g_{ds3}}{g_{ds1} \cdot g_{ds3}}$$

[0051] 이것은 나아가 전달 함수  $T(s)$ 를 다음과 같이 단순화한다

$$T(s) \approx \frac{\Omega_0}{s}$$

[0053] [0054] 이는 정확하게 완벽한 적분기의 반응이다. 트랜지스터는 일반적으로  $gm1 > gm3$ 와 같은 것으로 선택되고 이런 이유로

$$\Omega_0 \approx \frac{g_{m1}}{C_{gs3}} > \frac{g_{m3}}{C_{gs3}} \approx 2\pi \cdot f_T$$

[0055] [0056] 이것은 적분기(200)의 단일 이득 주파수가 기술의 그것과 근사적으로 동일함을 의미한다.

[0057] 도 3은 TSMC의 65나노미터 CMOS에서 구현되는 적분기(200)의 주파수 응답을 도시한다. 단일 주파수는 약 60GHz이다. 50MHz에서 10GHz까지 위상은 약 -90도(±10도 이내)인 동안 약 10MHz에서 60GHz까지 규모는 20dB/dec 감쇠를 가진다.

[0058] 도 2에서 보이는 적분기 회로(200)의 실시예는 다수의 방식으로 수정될 수 있다. 도 4의 적분기 회로(400)에서 보이는 바와 같이, 도 2에서의 중간 저항기  $R$ 은 그것의 게이트가 전압 소스에 연결되는 트랜지스터(transistor)를 사용하여 구현될 수 있다. 저항 값(따라서 전달 함수에서  $a_0$  값)은 단순히 전압을 변화시킴으로써 변화될 수 있다. 다음 섹션에서 설명될 바와 같이 이것은 피드백 제어 회로(feedback control circuit)를 통해 사용자가 적분기를 튜닝할 수 있게 한다.

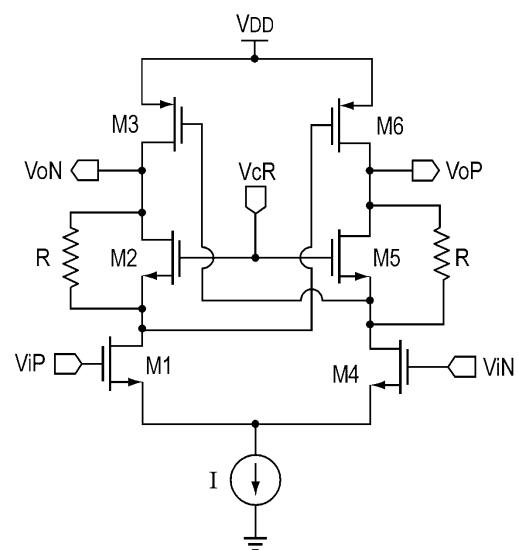

[0059] 도 5는 적분기 회로(500)의 추가적인 실시예를 도시하고, 도 4에서 M2(및 M5)의 저항은 전압  $V_{cR}$ 에 의해 제어된다. 일반적으로 저항은  $V_{cR}$ 에 증가함에 따라 감소한다.  $V_{cR}$ 이 너무 커지는 것을 방지하기 위해, 고정 저항기가 M2(및 M5)와 병렬로 추가될 수 있다.

[0060] 도 6(a)-(c)는 적분기(601, 602, 603)의 또 다른 실시예를 도시한다. 선형성을 더 개선하기 위해, 도 6(a) 적분기 회로(601)에서 보이는 바와 같이 두 개의 소스 변성 저항기는 상단에 추가될 수 있다. 약간 다른 접근방식은 두 개의 동일한 것들로 전류 소스를 분리하는 것이고 단일 소스 변성 저항기가 도 6(b)의 적분기 회로(602)에서 보이는 것처럼 두 개의 분기 사이에 추가될 수 있다. 도 6(c)에서, 적분기 회로(603)는 상단 및 하단 소스 변성 저항기를 모두 포함한다.

[0061] 도 7은 적분기 튜닝 회로(700)를 형성하는 튜닝 회로(702)로 구성되는 적분기 회로(701)(도 2 및 4 내지 6을 참조하여 상술된 적분기 회로와 같은)를 도시한다. 상술한 바와 같이, 전압  $V_{cR}$ 은 완벽한 적분기를 달성하기 위해 올바르게 선택되어야 한다. 이 선택은 튜닝 회로(702)를 통하여 된다. 완전한 튜닝 회로는 두 부분, 즉, DC 교정(calibration) 및 이득 제어를 포함한다. DC 교정이 작동하기 위해서는, 두 개의 동일한 버퍼(예를 들어, 소스 팔로워)가 적분기의 앞에 삽입된다. 하나의 버퍼가 단순히 그 입력으로 적분기의 차동 출력(differential outputs)을 얻는 적분기 회로인 피드백 루프를 통해 제어되는 반면 다른 하나는 고정 전압  $V_{fix}$ 로 바이어스된다. DC 교정 회로는 거의 동일한 바이어스 전압을 갖는 적분기의 차동 출력을 보장한다. 이것은 결국 튜닝될 때 높은 공통 모드 제거(common mode rejection)를 위해 적분기를 보장한다.

[0062]  $V_{cR}$ 이 변화함에 따라, DC 교정 적분기는 낮은 주파수에서 상당한 위상 변화를 가질 수 있고 위상은  $V_{cR}$ 과 함께 단조롭게 변화한다. 이득 제어 회로는 따라서 본질적으로 주어진 낮은 주파수에서 원하는 위상 응답을 가지는 DC 교정 적분기를 구동하는 위상 검출기이다. 도 7에 보이는 바와 같이, 오실레이터는 그 출력이 그 다음에 증폭되는 적분기에 공급되는 200kHz 신호를 생성한다. 같은 200kHz 신호는 또한 이상기(PS, Phase Shifter)와 단일-차동 컨버터(S2D, Single-to-Differential converter)에 공급되고 그 다음에 증폭된다(같은 증폭기를 사용하여). 두 증폭된 신호는 멀티플라이어(multiplier)에 공급된다. 멀티플라이어의 DC 성분은 두 개의 증폭된 신호들 사이의 위상차(phase difference)를 나타낸다. 더 구체적으로, DC 값들은 위상에 있을 때 최대화되고 위상이 위상에서 90도일 때 제로이다. 이상기(phase shifter)에 대해 적절히 선택된 위상 값을 가지고, 멀티플라이어

어에 뒤따르는 적분 회로(integration circuit)는 바람직한 VcR 값, 200kHz에서 바람직한 위상 응답(phase response)을 가지는 적분기를 구동한다.

[0063] 도 8은 각각의 입력 및 출력 신호와 감쇠기 회로(800)를 도시한다. 감쇠기는 프로세서 또는 DSP에 의해 지정된 주어진 이진수에 비례하는 신호를 감소시킨다. 감쇠기는 "전압의 선형(linear in voltage)" 또는 "dB의 선형(linear in dB)"가 되도록 설계된다. 감쇠기(800)는 "전압의 선형" 감쇠기이다. "dB의 선형" 감쇠기는 감쇠가 dB 단위에서 수행된다는 것을 제외하고 유사하다.

[0064] 감쇠기의 애플리케이션은 셀룰러 네트워크에서의 신호 처리 소자, 케이블 모뎀, 디지털 가입자 루프(digital subscriber loops), 이미징 시스템, 어댑티브 필터 및 다양한 애플리케이션에서 사용되는 이퀄라이저를 포함한다. 수천만의 감쇠기는 전자 부품 시장에서 판매되고 있고 몇 배(many times) 이상이 VLSI 설계에 포함된다.

[0065] 도 9는 R/2R 사다리를 이용한 전형적인 감쇠기(900)를 도시한다. 전형적인 감쇠기 설계는 감쇠기 기능을 구현하기 위해 다단계 저항 사다리(multistage resistive ladders)를 사용한다. 감쇠를 제어하는 바이너리 비트의 비트 수만큼의 단계가 있다. 원하는 정확성이 성장함에 따라 단계의 수는 성장하고 허용 오차는 더 악화된다. 이것은 실현 가능한 동적 범위를 제한한다. CMOS 설계에서 이것은 6 내지 8비트의 구조 및 64 내지 256의 동적 범위의 유용성을 제한한다. 더 높은 정확도는 레이저 트리밍(laser trimming)에 달성 가능하지만, 그러나 이것은 비용을 증가시킨다. 또한, 각 단계는 고유의 대역폭을 가지고 있으며 많은 단계가 종속됨에 따라, 대역폭은 감소한다. 따라서, 저비용, 10비트 이상의 정확성을 가진 광대역 감쇠기가 필요한 경우 이 다단계 저항 사다리 구조는 쓸모 없을 것이다.

[0066] 도 10은 본 발명의 실시예에서 구현될 수 있고, 확률적인 설계 기법을 사용하여 상술된 제한을 극복하는 감쇠기 회로(1000)를 도시한다. 여기에서, 시리즈 암(series arm)(소스와 출력 사이에) 또는 로드 암(load arm)(출력과 그라운드 사이에)으로 전환될 수 있는 저항기 R의 그룹으로 구성된다. 각 저항기는 직렬 암 또는 그렇지 않으면 로드 암에 있다.

[0067] 저항기가 비율 R, 2R, 4R, ..., (2N)R에 정렬되어 있다면, 우리가 N비트 감쇠기를 가지고 있는지 보여주기 쉽다. FET를 온오프(on-off)하는 스위치는 일반적으로 정전 용량(capacitance)을 가지고 있기 때문에, 우리는 더 큰 저항기가 대역폭 문제를 만들 것이라고 예상할 수 있다. 가장 작은 저항기는 임피던스의 스위치보다 훨씬 더 커야 하므로, 그래서 가장 큰 저항기는  $N > 9$ 에 대해서 정말 클 것이다. 이것은 광대역 성능을 위한 진짜 문제이다. 또한 가장 큰 저항기는 정말 크게 될 것이고 이것은 많은 실리콘 영역을 사용할 것이다. 하나의 종류는 충분한 범위를 갖지 않고, 다른 종류(families)의 저항기(다른 열 계수를 가진)가 저항기 값의 넓은 범위를 수용하는 데 사용되어야 할 것이기 때문에 정확도가 특히 온도와 타협될 것이다.

[0068] 각 암(arm)의 RC 시간 상수가 동일하므로 대역폭 문제는 저항기 크기에 반비례하는 FET 스위치 크기를 선택함으로써 완화될 수 있다. 이론적으로, 이것은 무한의 대역폭을 제공할 것이다. 그러나 가장 작은 FET는 불일치 관련 편차(mismatch related variance)를 가질만큼 충분히 크고 가장 작은 저항기에 비해 상대적으로 작아야 하기 때문에 가장 큰 것과 가장 작은 FET의 비율이 매우 커질 것이고 레이아웃과 실리콘 크기 문제가 있을 것이다.

[0069] 감쇠기(1000)는  $2^N$  감쇠 값을 제공하는 N 저항기를 사용한다. 설계자는 오직 N 값을 설정할 수 있기 때문에 이러한 감쇠기는 자유도 N을 갖는다. 감쇠기가 이상적이면, 0부터 1까지 가는 수직선 상에 감쇠의  $2^N$  똑같이 이격된 포인트(equally spaced points)를 제공할 것이다. 감쇠 값의 분포는 이렇게 하여 구간 [0, 1]을 따라서 균일( $1/2^N$  binning하게 됨)할 것이다. 비 이상적인 상황에서 많은 빈(bin)이 비어있을 것이고 많은 빈이 여러 값에 가질 것이다. 레이저 트리밍으로 감쇠 값이 모든 빈에 존재하는 값을 갖도록 이동하여 분포를 변경하려고 시도할 수 있다. 그러나 이것은 어렵고 비용이 많이 듈다.

[0070] 도 11은 추가적인 실시예에서 감쇠기 회로(1100)를 도시한다. 어떤 실시예에서는, M>N에서 자유도(저항기의 수) M이 있다. 구간 [0, 1]을 따라서 2M 포인트를 만들 수 있다. 제대로 M 저항기를 선택함으로써, 각각의  $2^N$  빈에서의 여러 포인트들로 분포를 만들 수 있다.

[0071] 큰 비율의 결과는 모든 빈에 있는 적어도 하나의 포인트로 분포를 여전히 얻을 것을 확인하기 위하여 포함된 저항기/FET 허용 오차를 가지고 몬테 카를로 시뮬레이션을 수행할 수 있다. 완성품은  $2^N$  원하는 값에 해당하는 제어 M비트 조합을 결정하기 위해  $2^M$  포인트를 통한 실행에 의해 교정될 수 있다. 이 테이블은 각 M비트 길이의  $2^N$  워드 크기의 메모리에 저장될 수 있다. N 어드레스 라인이 원하는 감쇠 값으로 설정되면, 메모리는 원하는 감쇠에 이르게 하는 대응하는 M비트 값을 감쇠기에 출력한다(데이터 버스에). 만약  $N < N^* < M$ 인  $N^*$  비트 정확도를 원하지만 몇 가지 누락된 코드(예를 들면, 0 또는 1 코너 근처의 코드)를 기꺼이 용인할 수 있다면, 해당 프

로그램은 크기  $M$ 의  $2^N \times$  워드 크기의 메모리에 넣어질 수 있다. 이러한 실시예는 도 11의 감쇠기 회로(1100)에 도시되어 있다.

[0072] 도 12(a)는  $N$ 비트 정확도, 저항기  $R$ ,  $2R$ ,  $\dots$ ,  $(2N)R$ 를 갖는  $M$  자유도 네트워크를 갖는 감쇠기 회로에 대하여 달성된 감쇠의 분포를 도시한다. 이제 간격( $1 - x/100$ ,  $1 + x/100$ , 즉,  $X$  퍼센트의 오류)에 놓여 있는 균일하게 분포된 확률 변수로써 각 저항기의 값을 디더링하면(바꾸면), 동일한 제어 비트 패턴을 위한 전형적인 실현이 도 12(b)에 보여진다. 알 수 있는 바와 같이, 분포는 이제 도 12(a)에 나타난 값 주변의 확산을 갖는다. 이 방법은 일부 채워진 빈(bin)들 주변의 비어 있는 빈들, 특히 다수의 채워진 빈들의 중간을 채우는 데 사용될 수 있다. 이 결과는 "분포 스무딩(smoothing the distribution)"으로 지칭될 수 있다.

[0073] 도 13은  $N$ 비트(본 예시에서  $N=12$ ) 정확도를 가진  $M$ 비트(본 예시에서  $M=24$ ) 감쇠기(1300)를 나타낸다. 최대 저항기(따라서 FET 스위치) 비율은 약 64이다. 우리는 저항  $R$ ,  $2R$ ,  $4R$ ,  $8R$ ,  $16R$ ,  $32R$ ,  $64R$ 로 시작하고 번호 59, 47, 43, 41, 37, 31은 번호 2, 4, 8, 16, 32, 64에 프라임(prime)인 값 59R, 53R, 47R, 43R, 41R, 37R, 31R의 저항기를 더한다. 결과 분포는  $X=5\%$ 를 사용하여  $2N$  빈에 가능한 최선의 분포(채움의 최대 범위)를 얻기 위해 디더링된다. 우리가  $M$  저항기(여기에는 우리가 값  $R$ 의 10 저항기들을 추가한다)를 가질 때까지 우리는 값  $R$ 의 저항기로 채운다.

[0074] 도 14는  $N=10$ 에서  $N=14$  빈에 대한 결과 분포를 도시한다. 몬테 카를로 시뮬레이션은 크기  $R=100\Omega$ 의 최소 저항기 및 크기  $0.12\mu m$ 의 최소 FET가 사용될 때 FET와 저항기가 65nm CMOS 기술의 불일치에서 약 1.5%의 변화가 있다는 것을 보여준다. 시뮬레이션은 2% X세트로 구성되고, 장기적으로 500 설계 중 500이  $N=12$ 에 대한 요구 사항을 충족하는지 나타내고, 범위 [0, 1]에서 이 212 빈 중 두 개의 극단적인 빈 0과 1023을 제외한 모두가 적어도 하나의 요소를 가진다.

[0075] 도 15는 특정한 손실 패턴에 대하여 감쇠기(1300)의 주파수 도메인의 성능을 나타낸다. 일반적으로, 감쇠기는 모든 다른 감쇠 값에서 10GHz 대역폭보다 크게 나타난다. 특정한 감쇠기를 교정하기 위해, 명목상의 설계로 시작한다. 빈의 테이블과 각 빈을 가로질러 분포되는 최대 10 제어 비트 조합을 만든다. 물론 10 제어 비트 조합보다 적게 가지는 빈은 모든 자신의 요소를 리스트한다.

[0076] 감쇠기를 보정함에 있어서, 빈  $i$  ( $1 \leq i \leq 2N$ )와, 그 빈에 대한 명목상 제어 비트 패턴으로 시작한다. 달성된 실제 감쇠를 측정하고 오차를 계산한다. 이 오류는 오류를 수정하기 위해 많은 빈들이 이동하는 방법을 결정하기 위하여  $2N$ 이 곱해진다. 운동의 방향은 에러의 극성에 의존한다. 측정된 값이 너무 높으면 낮은 빈 값의 방향으로 이동하고 그 역 또한 같다. 새로운 제어 비트 패턴이 결정되고(선택된 빈의 일부 제어 패턴이 여기에 우리가 최선을 유지, 다른 것보다 더 나은 가치를 줄 수 있다) 원하는 정확도가 달성될 때까지 프로세스가 반복된다. 실제로는 2 내지 3단계에서 원하는 정확도를 얻는다는 것이 발견되었다.

[0077]  $2N$  빈 값의 전체 테이블과 대응하는 제어 비트 패턴을 얻을 때까지 전체 프로세스는 모든 빈에 대하여 반복된다.

[0078] 상술한 방법은 매우 정확하고, 저렴한 비용, 높은 대역폭, 높은 수율의 CMOS 감쇠기를 제공한다. 원하는  $N$ 비트 정확도를 위하여, 우리는  $M(M > N)$  저항기와 스위치로 시작한다.  $N$ 보다 충분히 큰  $M$ 을 선택함으로써 우리는 감쇠기의 큰 비율은 컴포넌트 허용 오차에도 불구하고  $N$ 비트 정확도를 충족시킬 것이라는 것을 통계적으로 "보장"하기에 충분한 정확도를 얻는다. 어떠한 레이저 트리밍도 제조 공정에서 요구되지 않는다.

[0079] 또한, 최적의 분포에 대한 저항기를 선택하는 방법이 설명되었다. 감쇠기의 구체적인 실현을 교정하는 방법이 설명되었다. 상술한 예시적인 실시예는 "전압에서의 선형" 감쇠기를 제공하지만, 당업자 중 하나는 "dB에서의 선형" 감쇠기를 만드는 동일한 방법을 적용할 수 있다.

[0080] 도 16은 도 1을 참조하여 상술한 바이쿼드 회로(100)에서, 그리고 도 20 내지 21을 참조하여 아래에서 설명되는 바이쿼드 회로(200, 201)에서 구현될 수 있는 합산기 회로(1600)를 도시한다. 합산기 회로(1600)는 단일 저항기  $R$ 과  $N$  트랜지스터를 포함한다. 합산기(1600)는 광대역 아날로그 신호 처리를 필요로 하는 회로 토플로지에 사용될 수 있다. 트랜지스터  $N$ 의 수는 합산될 입력 신호의 개수에 의해 결정된다.

[0081] 합산기는 입력 신호  $V_1$ ,  $V_2$ ,  $\dots$ ,  $V_N$ 을 수신하고, 출력 신호  $V_{out}$ 을 제공하며, 이 모든 것은 DC 및 AC 텀(terms)을 담고 있다. 저항기  $R$ 은 합산 네트워크를 통해 DC 전류를 설정하고 합산 블록의 전체 이득에 기여한다. 중첩(superposition)을 사용하고, 이 때 하나의 트랜지스터를 고려하면, 우리는 공통 소스(CS, Common Source) 증폭기를 분석하게 된다. 출력에서 DC 바이어스 텀을 무시하고 AC 텀에만 집중함으로써, CS 증

폭기의 출력은 다음으로 주어진다

### 수학식 1

$$[0082] v_o = -g_m v_{in} (R || r_o)$$

[0083] 수학식 1에서, 텁  $g_m$ 은 트랜지스터(즉, 트랜스컨덕턴스)의 이득이며,  $r_o$ 는 트랜지스터의 출력 저항이다.  $r_o \gg R$ 를 가정하면 도 1의 회로의 전체 출력은 다음과 같이 주어진다

### 수학식 2

$$[0084] v_{out} = -(g_{m1}v_1 + g_{m2}v_2 + \dots + g_{mN}v_N)R$$

[0085] 수학식 2에서, 입력 신호를 동반하는  $g_m$  텁은 합산 계수로 볼 수 있다. 저항기  $R$ 이 고정되어 있기 때문에, 우리는 트랜지스터 이득  $g_m$ 을 변경하여 합산 계수를 조정할 수 있다. 트랜지스터 이득  $g_m$ 은 트랜지스터 폭  $W$ 의 텁으로 표현될 수 있고,

### 수학식 3

$$[0086] g_m = \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TN})$$

[0087] 수학식 3에 따르면, 트랜지스터 이득은 트랜지스터 폭에 비례하고 따라서 트랜지스터 폭을 변화시킴으로써, 우리는 합산 계수를 조정할 수 있다.

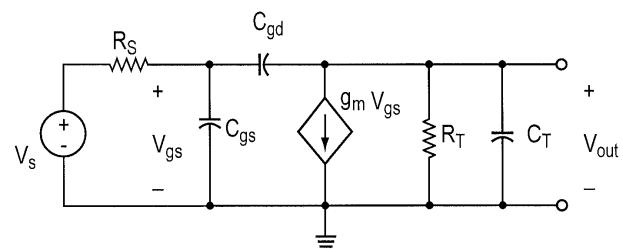

[0088] 합산 회로(1600)의 대역폭은 CS 증폭기 대역폭에 의해 결정된다. 도 17은 일반적으로 CS 증폭기의 고주파 동작을 분석하는데 사용되는 상응하는 작은-신호(small-signal) 회로 모델(1700)을 도시한다. 저항기  $R_T$ 는  $R || r_o$ 에 의해 주어지고 캐패시터  $C_T$ 는 트랜지스터(즉, 로드 캐패시턴스, 트랜지스터의 내부 기생 캐패시턴스, 그 이후의 단계의 입력 캐패시턴스)의 출력 노드와 그라운드(ground) 사이의 총 캐패시턴스이다.

[0089] RS가 비교적 크고 CT는 비교적 작은 애플리케이션에 대해 CS 증폭기의 대역폭.

### 수학식 4

$$[0090] f_{3dB} = \frac{1}{2\pi(C_{GS} + C_{GD}(1+g_m R_T)) R_S}$$

[0091] RS가 작은 애플리케이션에 대해 CS 증폭기의 대역폭.

### 수학식 5

$$[0092] f_{3dB} = \frac{1}{2\pi(C_L + C_{GD}) R_T}$$

[0093] 3-입력 합산 회로는 TSMC의 65nm 프로세스를 사용하여 케이던스(Cadence)에 구성되었다. 도 18은  $10\Omega$ 으로 설정된 소스 저항  $R_S$ 로 주어진 회로를 위한 주파수 응답을 나타낸다. 실선(solid lines)은  $R=26\Omega$ 의 경우에 해당한다. 회로는  $5.4\text{dB}$  손실이 있지만 약  $200\text{GHz}$ 의  $3\text{dB}$  대역폭을 가지고 있다. 파선(dashed lines)은  $R=60\Omega$ 의 경우에 해당한다. 회로는 약  $0\text{dB}$  손실이 있고  $3\text{dB}$  대역폭은  $90\text{GHz}$ 까지 감소된다.

- [0094] 도 19는 상술한 적분기, 감쇠기 및 합산기의 실시예가 구현될 수 있는 일련의 바이쿼드 회로(1900)를 도시한다. 바이쿼드 구성은 2차(second order) 상태 변수 구조이다. 2Nth 순서 전달 함수(order transfer function)  $T(s)$ '는 N 바이쿼드 캐스캐이딩 함으로써 얻어진다.

- [0095] 도 19에 나타낸 전달 함수는 또한 단일 입력 단일 출력(SISO, Single Input Single Output) 필드 프로그래머블 아날로그 어레이(FPGA, Field Programmable Analog Array)를 설명한다. 감쇠기 및 적분기 이득의 값을 변화시킴으로써, 적응 필터 및 지연 라인 특성의 모음(assortment)을 얻을 수 있다. 아날로그 도메인에서 작동할 수 있는 능력은 엔지니어들에게 광대역 신호를 처리하는 강력한 도구를 제공한다.

- [0096] 다시 도 1로 돌아가. 상술한 바이쿼드 회로(100)는 각 단계 내에서 감쇠기가 동작하는 가변 이득으로, 두 개의 적분/이득 단계를 포함하는 2차 상태 변수 구조를 구현한다. 광대역 입력에 기반하여 결합된 신호는 제 1 적분/이득 단계에 공급되고, 차례로, 이것은 제 2 적분/이득 단계에 입력을 제공한다. 가변 이득 감쇠기는 각각의 두 개의 적분기의 입력 및 출력으로부터 순방향(b's) 및 역방향(a's) 신호를 공급한다. 이러한 신호는 피드백 신호 및 피드-포워드(feed-forward) 신호를 결합한 제 2 합산 블록을 결합한 제 1 합산 블록에서 종료된다. 2 차 상태 변수 필터 예는 단편적인 이득 블록 및 추가적인 합산기를 또한 포함할 수 있다. 가변 이득 블록의 이득 변화는 2차 상태 변수 필터 실시예의 중심 주파수를 변경한다. 바이쿼드 회로(100)로부터 구성된 광대역 신호 처리 필터의 전달 함수 계수는 가변 감쇠기 값에 의해 결정된다.

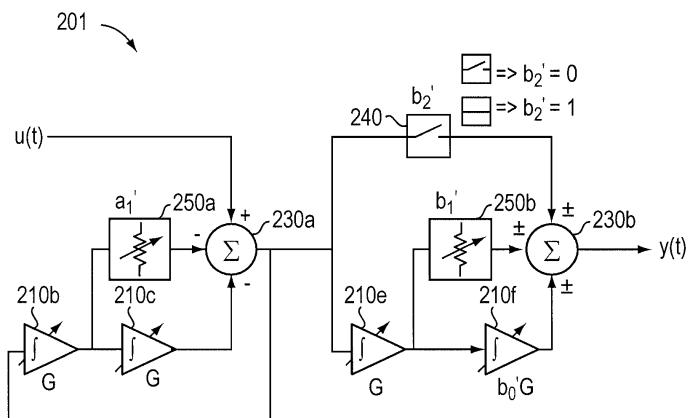

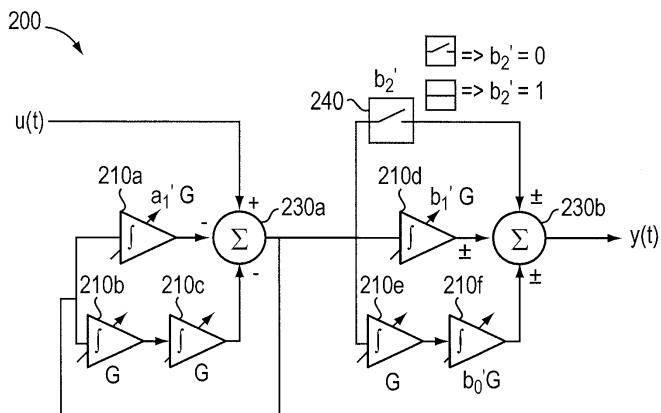

- [0097] 도 20은 예시적인 실시예에서 바이쿼드 회로(200)를 도시한다. 바이쿼드 회로(200)는 두 개의 적분/이득 단계를 포함하는 2차 상태 변수 구조를 구현하고, 이들 각각은 세 개의 가변 이득 적분기(210a-f)를 포함하고, 이들 중 두 개는 합산 블록(230a-b)에 작동 가능하게 결합된다. 특히, 제 1 단계는 합산기(230a)에 병렬로 연결되는 두 개의 적분기 라인을 포함하고, 여기에서 하나의 적분기 라인은 적분기(210a)와 직렬로 연결되는 적분기(210b와 210c)를 포함하는 다른 적분기 라인을 포함한다. 두 적분기 라인은 공통 노드에서 합산기(230a)의 출력을 수신하고, 합산기(230a)에 출력(반전될 수 있다)을 제공하도록 연결된다. 마찬가지로, 제 2 단계는 합산기(230b)에 병렬로 연결되는 두 개의 적분기 라인을 포함하고, 여기에서 하나의 적분기 라인은 적분기(210d)와 직렬로 연결되는 적분기(210e와 210f)를 포함하는 다른 적분기 라인을 포함한다. 또한, 스위치(240)는 제 1 합산기의 출력을 제 2 합산기(230b)의 입력에 선택적으로 결합하고, 그리하여 제 3, 이진값 신호를 제 2 단계 합산기(230b)에 제공한다. 두 적분기 라인은 공통 모드에서 합산기(230b)의 출력을 수신하도록 연결되고, 합산기(230a)에 출력(선택적으로 반전될 수 있다)을 제공한다.

- [0098] 동작에 있어서, 광대역 입력에 기반하여, 합성된 신호  $U(t)$ 는 제 1 적분/이득 단계에 제공되고, 차례로, 제 2 적분/이득 단계에 입력을 제공한다. 2차 상태 변수 필터 예는 또한 단편적인 이득 블록과 추가적인 합산기(미도시)를 포함할 수 있다. 가변 이득 블록의 이득 변화는 2차 상태 변수 필터 실시예의 중심 주파수를 변경한다. 도 20에서 나타나는 정달 함수  $T(s)$ 는 바이쿼드 회로(200)의 전달 함수를 정의한다. 전달 함수  $T(s)$ 의 계수는 적분기 이득 값에 의하여 결정된다.

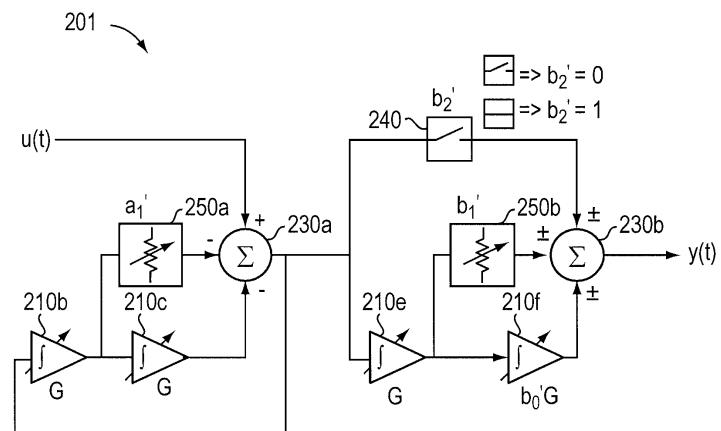

- [0099] 도 21은 또 다른 실시 예에서 바이쿼드 회로(201)를 도시하고, 두 개의 적분/이득 단계를 포함하는 2차 상태 변수 구조를 포함하고, 이들 각각은 하나의 가변(tunable) 손실 패드(250a-b) 및 두 개의 적분기(210b-c 210ef)를 포함한다. 광대역 입력에 기반하여 결합된 신호는 제 1 적분/이득 단계에 공급되고, 차례로, 제 2 적분/이득 단계에 입력을 제공한다. 특히, 제 1 단계는 직렬로 연결되는 적분기(210b와 210c)를 포함하는 단일 적분기 라인을 포함한다. 적분기 라인은 합산기(230a)의 출력(반전될 수 있다)을 수신하고 합산기(230a)에 출력을 제공하도록 연결된다. 가변 손실 패드(250a)는 적분기(210b)의 출력을 수신하고 합산기(230a)에 출력을 제공하도록 구성된다. 제 2 단계는 직렬로 연결되는 적분기(210e와 210f)를 포함하는 단일 적분기 라인을 포함한다. 적분기 라인은 합산기(230b)의 출력을 수신하고 합산기(230b)로 출력(선택적으로 반전될 수 있다)을 제공하도록 연결된다. 가변 손실 패드(250b)는 적분기(210b)의 출력을 수신하고 합산기(230a)에 출력을 제공하도록 구성된다. 또한, 스위치(240)는 제 1 합산기(230a)의 출력을 제 2 합산기(230b)의 입력에 선택적으로 결합하고, 그리하여 제 3, 이진값 신호를 제 2 단계 합산기(230b)에 제공한다.

- [0100] 추가적인 실시예에서, 바이쿼드 회로(201)는 단편적인 이득 블록 및 추가적인 합산기(미도시)와 같은 추가적인 2차 상태 변수 필터들을 포함할 수 있다. 가변 이득 블록(예를 들어, 적분기(210b-c, 210e-f)의 이득 값을 조정하는 것은, 차례로 2차 상태 변수 필터의 중심 주파수를 변경한다. 바이쿼드 회로(201)에 의해 제공되는 광대역 신호 처리 필터의 전달 함수 계수는 가변 손실 패드 및 적분기 이득 값에 의해 결정된다.

- [0101] 상술한 바이쿼드 회로(200, 201)는 도 1에 나타난 바이쿼드 회로(100)로부터 여러 가지 면에서 구별된다. 특히, 바이쿼드 회로(200, 201)는 감쇠기의 제거, 적분기의 프로그래머빌리티, 적분기의 글로벌 컨트롤(튜닝)로부터

혜택을 누릴 수 있다. 감쇠기를 제거함으로써, 바이쿼드 회로(200, 201)는 증가된 정확도, 안정성, 및 대역폭을 제공한다. 또한, 프로그래머블한 적분기(예를 들어, 적분기(210a-f))는 "제어 플레인(control plane)"으로 고려될 수 있는 것을 생성하여, 실시간 프로세스 변화와 온도 변화에 반응하여 전달 함수의 제어를 가능하게 한다. 이러한 제어는 입력  $u(t)$ 로부터 출력  $y(t)$ 까지의 경로를 따르는 "사용자 평면(user plane)"과 구별된다. SPI 버스는 관리 플레인(management plane)을 구현하고, 이를 통하여 적분기와  $b_2'$ 를 인스턴스화하는(instantiating) 스위치가 제어된다. 적분기들의 개별적인 튜닝보다는 글로벌 제어를 제공함으로써, 많은 튜닝 회로 오버헤드가 제거될 수 있고 바이쿼드의 확장성(scalability)은 크게 증가될 수 있다. 예를 들어, 실리콘의 평방 밀리미터 당 10+ 바이쿼드의 밀도를 달성할 수 있다.

[0102] 또한, 도 20의 바이쿼드 회로(200)는, 두 개의 프로그래머블한 적분기(210a-b)가 적분기(210b, 210e)의 출력에 연결되는 두 개의 가변 손실 패드(250a-b)에 의해 대체되는 점에서, 도 21의 바이쿼드 회로(201)와 구별된다. 일부 실시예에서, 적분기 대신 가변 손실 패드를 구현하는 것은 성능을 희생하지 않고 회로 복잡도 및 크기를 감소시킬 수 있다.

[0103] 모든 특허, 공개된 애플리케이션 및 여기에 인용된 참고 문헌의 개시는 그 전체가 참고로 인용된다.

[0104] 본 발명은 도면에 도시된 예시적인 실시예를 참조하여 설명되었지만, 형태 및 세부 사항에서 다양한 변화가 첨부된 청구항에 포함되는 발명의 범위를 벗어나지 않고 이루어질 수 있다는 점은 당해 기술 분야에 숙련된 자들에게 이해될 것이다.

## 도면

### 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10

OFFERS  $2^N$  ATTENUATION VALUES

## 도면11

## 도면12

## 도면13

## 도면14

| Bits | LOW BIN NUMBER <sup>A</sup> | HIGH BIN NUMBER <sup>B</sup> | DYNAMIC RANGE | STEP SIZE | NUMBER OF BINS    |

|------|-----------------------------|------------------------------|---------------|-----------|-------------------|

| 10   | 1                           | 1,022                        | 60dB          | 0.000977  | $2^{10} = 1,024$  |

| 12   | 5                           | 4,079                        | 58dB          | 0.000244  | $2^{12} = 4,096$  |

| 14   | 62                          | 14,489                       | 47dB          | 0.000061  | $2^{14} = 16,384$ |

<sup>A</sup> LOWEST BIN NUMBER WITH AT LEAST ONE ATTENUATION VALUE PRESENT<sup>B</sup> HIGHEST BIN NUMBER WITH AT LEAST ONE ATTENUATION VALUE PRESENT

## 도면15

**도면16****도면17****도면18**

## 도면19

$u(t) \rightarrow \text{바이쿼드}_1 \rightarrow \text{바이쿼드}_2 \rightarrow \dots \rightarrow \text{바이쿼드}_N \rightarrow y(t)$

$$T(s)' = \sum_{j=1}^N \frac{b_{2j} s^2 + b_{1j} s + b_{0j}}{s^2 + a_{1j} s + a_{0j}}$$

## 도면20

$$T(s) = \frac{b_2' + b_1' G/s + b_0' G^2/s^2}{1 + a_1' G/s + G^2/s^2}$$

WHERE  $a_1' = a_1/s$

$$b_0' = b_0/s^2$$

$$b_1' = b_1/s$$

$$b_2' = b_2^2$$

## 도면21