(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5537020号

(P5537020)

(45) 発行日 平成26年7月2日(2014.7.2)

(24) 登録日 平成26年5月9日(2014.5.9)

(51) Int.Cl.

H01L 27/10 (2006.01)

G11C 17/06 (2006.01)

F 1

H01L 27/10 431

G11C 17/06 A

請求項の数 12 (全 24 頁)

(21) 出願番号 特願2008-314894 (P2008-314894)

(22) 出願日 平成20年12月10日 (2008.12.10)

(65) 公開番号 特開2009-290189 (P2009-290189A)

(43) 公開日 平成21年12月10日 (2009.12.10)

審査請求日 平成23年12月8日 (2011.12.8)

(31) 優先権主張番号 特願2008-9509 (P2008-9509)

(32) 優先日 平成20年1月18日 (2008.1.18)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2008-118638 (P2008-118638)

(32) 優先日 平成20年4月30日 (2008.4.30)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100080816

弁理士 加藤 朝道

(72) 発明者 児玉 典昭

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

(72) 発明者 日高 憲一

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

(72) 発明者 小畠 弘之

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板上に形成された選択トランジスタ及びアンチフューズを有する不揮発性半導体記憶装置であって、

前記選択トランジスタと前記アンチフューズとの間には、前記半導体基板に形成された素子分離領域を有し、

前記選択トランジスタは、

前記半導体基板上に形成された第1絶縁膜と、

前記第1絶縁膜上に形成されたゲート電極と、

前記半導体基板内に形成されるとともに、前記ゲート電極の一方の側面側に形成された第1拡散層と、

前記半導体基板内に形成されるとともに、前記ゲート電極の他方の側面側に形成された第2拡散層と、

前記アンチフューズは、

前記半導体基板上に形成された第2絶縁膜と、

前記第2絶縁膜上に形成された上部電極と、

前記半導体基板内に形成されるとともに、前記上部電極の他方の側面側に形成され、かつ、下部電極を構成する第3拡散層と、

を有し、

10

前記アンチフューズは、

前記半導体基板上に形成された第3絶縁膜と、

前記第3絶縁膜上に形成された下部電極と、

前記半導体基板内に形成されるとともに、前記下部電極の他方の側面側に形成され、かつ、上部電極を構成する第4拡散層と、

を有し、

20

前記第2拡散層は、前記素子分離領域と接しており、

前記上部電極の一方の側面は、前記素子分離領域上に位置しており、

前記第2拡散層と前記上部電極とは、電気的に接続しており、

前記ゲート電極の一方の側面、前記ゲート電極の他方の側面、前記上部電極の一方の側面、及び、前記上部電極の他方の側面には、それぞれサイドウォールが形成されており、

前記第3拡散層は、前記上部電極に対して前記サイドウォールの幅だけ離間していることを特徴とする不揮発性半導体記憶装置。

## 【請求項2】

前記選択トランジスタ及び前記アンチフューズ上には、層間絶縁膜が形成されており、

前記層間絶縁膜には、前記第2拡散層および前記上部電極の両方に達する開口部が形成されており、

前記開口部内に形成された接続コンタクトを有することを特徴とする請求項1記載の不揮発性半導体記憶装置。

10

## 【請求項3】

前記選択トランジスタ及び前記アンチフューズ上には層間絶縁膜が形成されており、

前記層間絶縁膜には、前記第2拡散層に達する第1開口部、及び、前記上部電極に達する第2開口部が形成されており、

前記第1開口部内に形成された第1接続コンタクトを有し、

前記第2開口部内に形成された第2接続コンタクトを有し、

前記層間絶縁膜上には、前記第1接続コンタクト及び前記第2接続コンタクトのそれと接続する配線が形成されていることを特徴とする請求項1記載の不揮発性半導体記憶装置。

20

## 【請求項4】

前記第1拡散層及び前記第2拡散層並びに前記第3拡散層は、それぞれn型の不純物が拡散していることを特徴とする請求項1乃至3のいずれか1項に記載の不揮発性半導体記憶装置。

## 【請求項5】

前記第1拡散層及び前記第2拡散層は、それぞれn型の不純物が拡散しており、

前記第3拡散層は、p型の不純物が拡散していることを特徴とする請求項3記載の不揮発性半導体記憶装置。

30

## 【請求項6】

前記第1拡散層及び前記第2拡散層は、それぞれp型の不純物が拡散しており、

前記第3拡散層は、n型の不純物が拡散していることを特徴とする請求項3記載の不揮発性半導体記憶装置。

## 【請求項7】

前記上部電極と前記第3拡散層とは、水平位置が重複しないように位置していることを特徴とする請求項1乃至6のいずれか1項に記載の不揮発性半導体記憶装置。

## 【請求項8】

前記不揮発性半導体記憶装置の書き込み動作は、前記第3拡散層に接地電位を印加するとともに、前記ゲート電極及び前記第1拡散層に同じ電位を印加し、かつ、前記第2絶縁膜を破壊することで行われることを特徴とする請求項1乃至7のいずれか1項に記載の不揮発性半導体記憶装置。

40

## 【請求項9】

前記不揮発性半導体記憶装置の読み出し動作は、前記第3拡散層に接地電位を印加するとともに、前記ゲート電極および前記第1拡散層に同じ電位を印加することで、前記第2絶縁膜が破壊されていれば前記選択トランジスタが導通し、前記第2絶縁膜が破壊されなければ前記選択トランジスタが非導通となることにより判定することを特徴とする請求項8記載の不揮発性半導体記憶装置。

## 【請求項10】

前記第1絶縁膜の膜厚は、前記第2絶縁膜の膜厚よりも大きいことを特徴とする請求項

50

1乃至9のいずれか1項に記載の不揮発性半導体記憶装置。

**【請求項11】**

前記サイドウォールの幅は、10nm以上かつ50nm以下であることを特徴とする請求項1乃至10のいずれか1項に記載の不揮発性半導体記憶装置。

**【請求項12】**

前記素子分離領域は、STI構造であることを特徴とする請求項1~11の何れか1項に記載の不揮発性半導体記憶装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

10

本発明は、アンチフューズ型のメモリセルを有する不揮発性半導体記憶装置に関する。

**【背景技術】**

**【0002】**

20

デジタル家電や携帯電話向けLSI (Large Scale Integration) におけるセキュリティコードの格納や、LCD (Liquid Crystal Display) ドライバにおける色調調整パラメータ、温度補償型水晶発振器 (TCXO ; temperature compensated crystal oscillator) の制御の温度パラメータなどのトリミングなどに小容量の不揮発性ROMの必要性が高まっている。不揮発性ROMは、EEPROM (Electronically Erasable and Programmable Read Only Memory) の別チップをSIP (System in Package) で搭載している場合が多い。最近は、工程追加なしの標準CMOS (Complementary Metal Oxide Semiconductor) プロセスにて不揮発性ROMが形成できる技術が開示されている。例えば、特許文献1、2、非特許文献1等にはアンチフューズ型メモリが開示されている。

**【0003】**

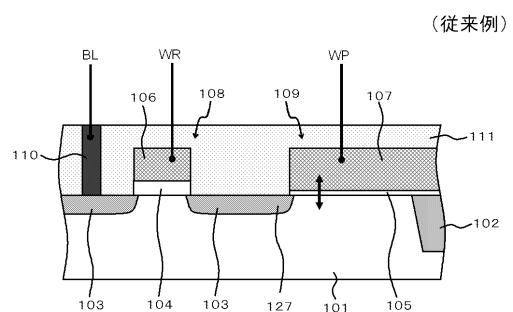

20

アンチフューズ型メモリでは、例えば、図8のように、P型の半導体基板101のチャネルの両側にN+型のソース・ドレイン拡散層103が形成され、かつ、チャネル上に厚ゲート絶縁膜104を介してゲート電極106が形成された選択トランジスタ108を有する。選択トランジスタ108と隣接する領域では、ソース・ドレイン拡散層103の一方と接続されたフューズ下部電極拡散層127と、半導体基板101上に形成された素子分離領域102との間の半導体基板101上に、厚ゲート絶縁膜104より薄い薄ゲート絶縁膜105を介して、ポリシリコンよりなるフューズ上部電極107が形成されたアンチフューズ109を有する。選択トランジスタ108の他方のソース・ドレイン拡散層103は、層間絶縁膜111に形成された下穴に埋め込まれたビットコンタクト110を介してビット線BLに電気的に接続されている。ゲート電極106は、ワード線WRに電気的に接続されている。フューズ上部電極107は、プレート線WPに電気的に接続されている。

30

**【0004】**

この種のアンチフューズメモリセルの書き込み動作は、アンチフューズ109の薄ゲート絶縁膜105を破壊して行う。この際にアンチフューズ109の下部電極となるN+のフューズ下部電極拡散層127に高い正電位を印加して薄ゲート絶縁膜105を破壊すると、アバランチエやバンド間トンネルなどのホットキャリアが薄ゲート絶縁膜105に注入されながら絶縁破壊が誘起されるので、破壊時間が不安定でバラツキが生じやすく、また信頼性的にも劣る傾向がある。そのため、書き込み動作では、薄ゲート絶縁膜105の破壊時のソース・ドレイン拡散層103近傍からのホットキャリアの生成を抑制するように印加電位が設定される。

40

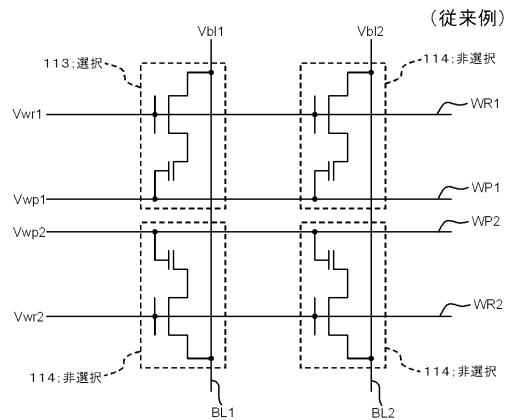

**【0005】**

例えば、書き込み動作において、図9のようにメモリセルを選択/非選択とする場合、選択メモリセル113では、選択プレート線WP1の電位Vwp1を高い正の破壊電位VPとし、選択ワード線WR1の電位Vwrr1をVPP/2とし、選択ビット線BL1の電位Vb11を0Vとすることで、フューズ下部電極拡散層127には電位を印加しないで薄ゲート絶縁膜105を破壊する。非選択メモリセル114では、非選択ビット線BL2

50

の電位  $V_{b12}$  を  $V_{PP}/2$  にしてアンチフューズのゲート破壊が起きないように抑止電位を印加して行っている。

【0006】

読み出し動作では、選択メモリセル 113 のアンチフューズを流れる電流が書き込み動作と同じ向きにすることが信頼性上重要であるが、アンチフューズの上部電極から下部電極、選択トランジスタを介してビット線に電子が流れるように選択プレート線 WP1 の電位  $V_{WP1}$  を I/O 部の電源電位  $V_{ddIO}$  にし、選択トランジスタの選択ワード線 WR1 の電位  $V_{WR1}$  を電源電位  $V_{dd}$  にし、選択ビット線 BL1 の電位  $V_{b11}$  を 0V にし、非選択ビット線 BL2 の電位  $V_{b12}$  を選択ワード線 WR1 と同じ  $V_{dd}$  とすることで、選択メモリセル 113 の読み出しを行う。

10

【0007】

【特許文献 1】米国特許第 6 7 9 8 6 9 3 号明細書

【特許文献 2】特開 2001-308283 号公報

【非特許文献 1】Bernard Aronson (Kilopass)、「A Novel embedded OTP NVM Using Standard Foundry CMOS Logic Technology」、IEDM 2006 (国際電子デバイス会議; International Electron Devices Meeting)、米国、アメリカ電気・電子通信学会 (IEEE)、2006 年、p. 24

【発明の開示】

【発明が解決しようとする課題】

【0008】

20

しかしながら、従来例 (図 8 ~ 10 参照) では、書き込み動作において  $V_{PP}$ 、 $V_{PP}/2$ 、0V の 3 種類の電位が必要であり、読み出し動作において  $V_{ddIO}$ 、 $V_{dd}$ 、0V の 3 種類が必要となり、合計 5 種類の電位がセル動作に必要であり、周辺制御回路が複雑になり、回路規模が大きくなるという問題があった。

【0009】

本発明の主な課題は、動作電位種が少なく周辺回路の回路規模を小さくできるメモリセルを有する不揮発性半導体記憶装置を提供することである。

【課題を解決するための手段】

【0010】

本発明の一観点においては、半導体基板上に形成された選択トランジスタ及びアンチフューズを有する不揮発性半導体記憶装置であって、前記選択トランジスタと前記アンチフューズとの間には、前記半導体基板に形成された素子分離領域を有し、前記選択トランジスタは、前記半導体基板上に形成された第 1 絶縁膜と、前記第 1 絶縁膜上に形成されたゲート電極と、前記半導体基板内に形成されるとともに、前記ゲート電極の一方の側面側に形成された第 1 拡散層と、前記半導体基板内に形成されるとともに、前記ゲート電極の他方の側面側に形成された第 2 拡散層と、を有し、前記アンチフューズは、前記半導体基板上に形成された第 2 絶縁膜と、前記第 2 絶縁膜上に形成された上部電極と、前記半導体基板内に形成されるとともに、前記上部電極の他方の側面側に形成され、かつ、下部電極を構成する第 3 拡散層と、を有し、前記第 2 拡散層は、前記素子分離領域と接しており、前記上部電極の一方の側面は、前記素子分離領域上に位置しており、前記第 2 拡散層と前記上部電極とは、電気的に接続しており、前記ゲート電極の一方の側面、前記ゲート電極の他方の側面、前記上部電極の一方の側面、及び、前記上部電極の他方の側面には、それぞれサイドウォールが形成されており、前記第 3 拡散層は、前記上部電極に対して前記サイドウォールの幅だけ離間していることを特徴とする。

30

【発明の効果】

【0013】

本発明によれば、書き込み動作の際、非選択のビット線やワード線に破壊抑制電位を印加する必要がなく、メモリセル動作制御に抑止電位が不要となり、動作電位種が少なく動作が単純であるので、周辺回路の回路規模が小さくできる。

【発明を実施するための最良の形態】

40

50

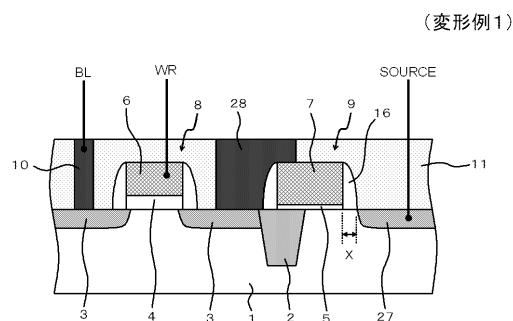

## 【0014】

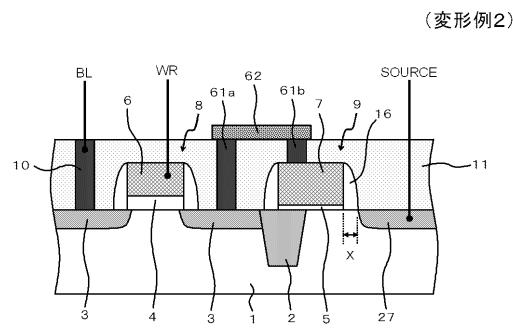

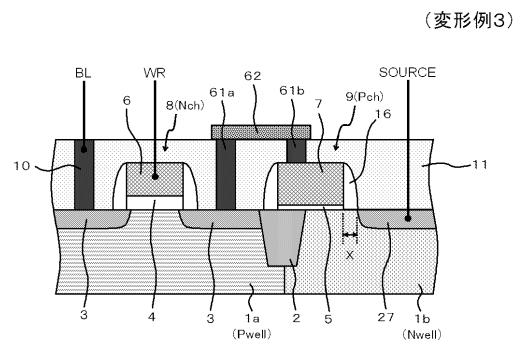

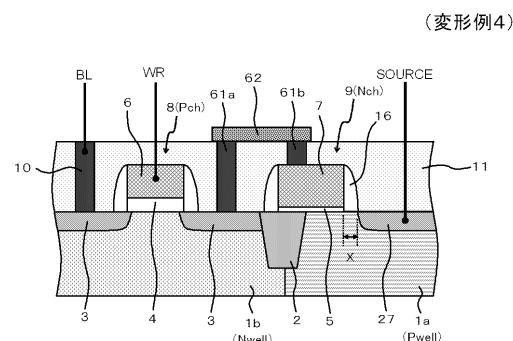

本発明の実施形態に係る不揮発性半導体記憶装置では、半導体基板（図23及び図25の1、図26及び図27の1a及び1b）上に形成された選択トランジスタ（図23、図25、図26、図27の8）及びアンチフューズ（図23、図25、図26、図27の9）を有する不揮発性半導体記憶装置であって、前記選択トランジスタと前記アンチフューズとの間には、前記半導体基板に形成された素子分離領域（図23、図25、図26、図27の2）を有し、前記選択トランジスタは、前記半導体基板上に形成された第1絶縁膜（図23、図25、図26、図27の4）と、前記第1絶縁膜上に形成されたゲート電極（図23、図25、図26、図27の6）と、前記半導体基板内に形成されるとともに、前記ゲート電極の一方の側面側（図23、図25、図26、図27の左側）に形成された第1拡散層（図23、図25、図26、図27の左側の3）と、前記半導体基板内に形成されるとともに、前記ゲート電極の他方の側面側（図23、図25、図26、図27の右側）に形成された第2拡散層（図23、図25、図26、図27の右側の3）と、を有し、前記アンチフューズは、前記半導体基板上に形成された第2絶縁膜（図23、図25、図26、図27の5）と、前記第2絶縁膜上に形成された上部電極（図23、図25、図26、図27の7）と、前記半導体基板内に形成されるとともに、前記上部電極の他方の側面側（図23、図25、図26、図27の右側）に形成され、かつ、下部電極を構成する第3拡散層（図23、図25、図26、図27の27）と、を有し、前記第2拡散層は、前記素子分離領域と接しており、前記上部電極の一方の側面（図23、図25、図26、図27の左側の面）は、前記素子分離領域上に位置しており、前記第2拡散層と前記上部電極とは、電気的に接続しており、前記ゲート電極の一方の側面、前記ゲート電極の他方の側面、前記上部電極の一方の側面、及び、前記上部電極の他方の側面には、それぞれサイドウォール（図23、図25、図26、図27の16）が形成されており、前記第3拡散層は、前記上部電極に対して前記サイドウォールの幅（図23、図25、図26、図27のX）だけ離間している。

10

20

## 【実施例1】

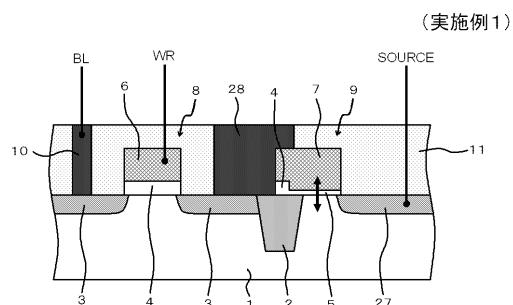

## 【0015】

本発明の実施例1に係る不揮発性半導体記憶装置について図面を用いて説明する。図1は、本発明の実施例1に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した部分断面図である。

30

## 【0016】

実施例1に係る不揮発性半導体記憶装置におけるメモリセルでは、選択トランジスタ8とアンチフューズ9を有する。

## 【0017】

選択トランジスタ8では、P型の半導体基板1のチャネルの両側にN+型のソース・ドレイン拡散層3が形成されており、チャネル上に厚ゲート絶縁膜4を介してゲート電極6が形成されている。一方のソース・ドレイン拡散層3は、層間絶縁膜11に形成された下穴に埋め込まれた接続コンタクト28を介してアンチフューズ9のフューズ上部電極7と電気的に接続されている。他方のソース・ドレイン拡散層3は、層間絶縁膜11に形成された下穴に埋め込まれたビットコンタクト10を介してビット線B\_Lに電気的に接続されている。ゲート電極6は、ワード線W\_Rに電気的に接続されている。

40

## 【0018】

アンチフューズ9は、薄ゲート絶縁膜5を絶縁破壊し、半導体基板1とフューズ上部電極7の間を短絡させて書き込みが行える記憶ノードである。アンチフューズ9は、選択トランジスタ8の一方のソース・ドレイン拡散層3と隣接する領域の半導体基板1に形成されたSTI(Shallow Trench Isolation)型の素子分離領域2に隣接した領域に形成されている。アンチフューズ9では、MOSトランジスタ構造となっており、半導体基板1内に形成されたN+型のフューズ下部電極拡散層27と素子分離領域2との間の領域の半導体基板1上に、厚ゲート絶縁膜4よりも薄い薄ゲート絶縁膜5を介して、ポリシリコンよりなるフューズ上部電極7が形成されている。フューズ上部電極7（アンチフューズの一

50

端)は、層間絶縁膜11に形成された下穴に埋め込まれた接続コンタクト28を介して選択トランジスタ8の一方のソース・ドレイン拡散層3と電気的に接続されている。フューズ下部電極拡散層27(アンチフューズの他端)は、共通ソース線SOURCEと電気的に接続されている。なお、フューズ上部電極7下の薄ゲート絶縁膜5は、素子分離領域2上において厚ゲート絶縁膜4と同じ膜厚としてもよい。

【0019】

接続コンタクト28は、選択トランジスタ8及びアンチフューズ9上に成膜された層間絶縁膜11に形成された下穴(ソース・ドレイン拡散層3の一部とフューズ上部電極7の一部とを含んだ1つの開口部)に埋め込まれた導電体(例えば、タングステン)である。接続コンタクト28は、選択トランジスタ8の一方のソース・ドレイン拡散層3と、アンチフューズ9のフューズ上部電極7とを跨ぐようにして、一方のソース・ドレイン拡散層3の表面の一部からフューズ上部電極7の表面の一部にかけて連続的に配され、一方のソース・ドレイン拡散層3及びフューズ上部電極7とそれぞれ接している。

【0020】

なお、アンチフューズ9のフューズ下部電極拡散層27は、ここではP型の半導体基板1上にN+型の不純物が拡散したものであるが、P型の半導体基板1上のP+型の不純物が拡散したものでもよい。フューズ下部電極拡散層27がP型の半導体基板1上のP+型の不純物が拡散したものであれば、アンチフューズ部の抵抗を小さくできるというメリットがある。また、ここでは選択トランジスタ8をNチャネル型のメモリセルを想定して説明したが、Pチャネル型でも同様にできる。

【0021】

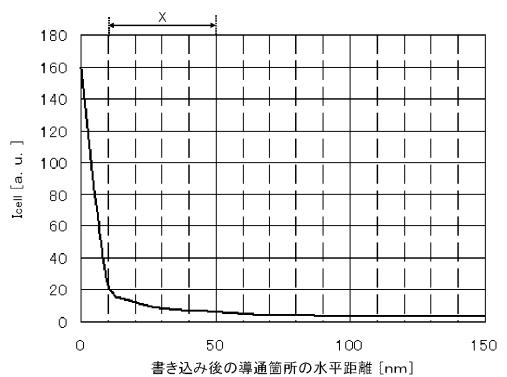

アンチフューズ9は、上部電極7と下部電極27を離間(図の横方向(水平方向)に離間)させることが望ましい(図23参照)。つまり、下部電極27は、上部電極7に対して水平位置関係が重複しないようにすることが望ましい。この構造は、標準のCMOS製造プロセスにおいてLDD(lightly doped drain)注入もしくはエクステンション注入をマスクして抑制することにより上部電極7と下部電極27をサイドウォール16の幅Xだけ離間させることによって容易に実現できる。この構造にすることによって、読み出し電流のバラツキを抑制することができる。基板表面の電極27のジャンクション位置と書き込み後に形成される導通箇所の水平距離(最も下部電極27に近接した箇所で導通した場合は図23の距離Xと等しい)と、書き込み後の上部電極7と下部電極27間を流れる電流量(Icell)の関係を調べると図24のようになる。距離Xが小さすぎるとIcellが極度に増加することが分かっている。この事により、安定したIcellを実現するためには距離Xの値を10nm以上することが望ましい。一方、距離Xが大きすぎるとオフセットトランジスタになるためにIcellが著しく減少する弊害もある。よって、距離Xの値は、10nm~50nmになるように形成することが望ましい。

【0022】

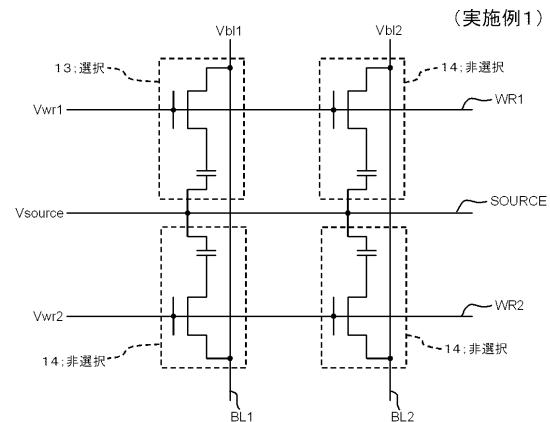

図1のようなメモリセル(セット)は、図2のように選択トランジスタとアンチフューズが直列に接続された構成となる。メモリセルは行列に配列しており、行方向の各メモリセルのゲート電極はワード線WR1、WR2に接続されており、列方向の各メモリセルの他方のソース・ドレイン拡散層はピット線BL1、BL2に接続されており、各メモリセルのアンチフューズの他端は共通ソース線SOURCEに電気的に接続されている。

【0023】

なお、実施例1に係る不揮発性半導体記憶装置は、標準CMOSプロセスで製造することができる。例えば、半導体基板1に素子分離領域2を形成し、その後、半導体基板1表面を熱酸化することで熱酸化膜を形成し、その後、厚ゲート絶縁膜4を形成する領域の熱酸化膜をエッティング除去し、その後、半導体基板1表面を熱酸化することで厚い熱酸化膜と薄い熱酸化膜を形成し、その後、ポリシリコンを成膜し、その後、エッティングすることでゲート電極6及び厚ゲート絶縁膜4とフューズ上部電極7及び薄ゲート絶縁膜5を形成し、その後、不純物を導入することでソース・ドレイン拡散層3及びフューズ下部電極拡散層27を形成し、その後、層間絶縁膜11を成膜し、その後、ピットコンタクト10及

10

20

30

40

50

び接続コンタクト 28 を形成するための下穴を形成し、その後、下穴にピットコンタクト 10 及び接続コンタクト 28 を埋め込むことで、図1のようなメモリセルができる。

【0024】

次に、本発明の実施例1に係る不揮発性半導体記憶装置の動作について図面を用いて説明する。図2は、本発明の実施例1に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。図3は、本発明の実施例1に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

【0025】

書き込み動作では、半導体基板(図1の1)及びフューズ下部電極拡散層(図1の27)に接続された共通ソース線SOURCEを接地電位にし、選択ピット線BL1、及び選択ワード線WR1に書き込み電位VPP(正の高電位)を印加する。これにより、選択メモリセル13のアンチフューズ(図1の9)のフューズ上部電極(図1の7)にのみ破壊電位が印加され、アンチフューズ(図1の9)の薄ゲート絶縁膜(図1の5)を破壊する。つまり、選択トランジスタ側からアンチフューズの一端にアンチフューズを破壊しうる電位を印加する。

【0026】

読み出し動作では、半導体基板(図1の1)及びフューズ下部電極拡散層(図1の27)に接続された共通ソース線SOURCEを接地電位にし、選択ワード線WR1、及び選択ピット線BL1にIO電位VddIOを印加する。これにより、アンチフューズ(図1の8)の薄ゲート絶縁膜(図1の5)が破壊されていれば導通し、破壊されていなければ非導通で、メモリセルに書き込まれたデータを読み出すことができる。

【0027】

なお、各配線の電位制御は、図示されていないコントローラによって行われる。また、ここでの書き込み動作では、半導体基板(図1の1)及びフューズ下部電極拡散層(図1の27)を接地電位にし、選択トランジスタ(図1の8)のドレイン(図1の3)とゲート電極(図1の6)を正の高電位にしているが、半導体基板(図1の1)及びフューズ下部電極拡散層(図1の27)を正の高電位にし、選択トランジスタ(図1の8)のドレイン(図1の3)とゲート電極(図1の6)を接地電位にしてもよい。

【0028】

実施例1によれば、メモリセル動作制御に抑止電位が不要となり、動作電位種が少なく動作が単純であるので、周辺回路の回路規模が小さくでき、マクロサイズの小さい、小チップサイズの低コストのものが得られる。また、アンチフューズ9の薄ゲート絶縁膜5を絶縁破壊して書き込みする際、絶縁破壊が確実に行われ、破壊後に抵抗変化することなく、信頼性の高い不揮発性半導体記憶装置が得られる効果がある。つまり、選択トランジスタ8を介してアンチフューズ9に伝わる書き込み電位はフューズ上部電極7に印加されるため、選択メモリセル13のアンチフューズ9の薄ゲート絶縁膜5の破壊をFNトンネル電流により引き起こすことが可能になり、ポリシリコン端部近傍でのフューズ下部電極拡散層27側からのアバランチ降伏やバンド間トンネルにより生じるホットなキャリアによるゲート破壊を抑制できる。さらに、標準CMOSプロセスにおいて工程追加なしで、製造コストを抑えて形成できる。

【実施例2】

【0029】

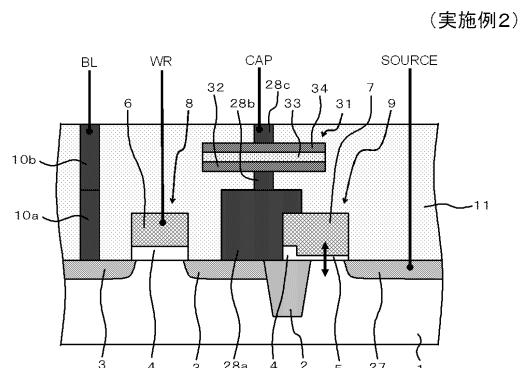

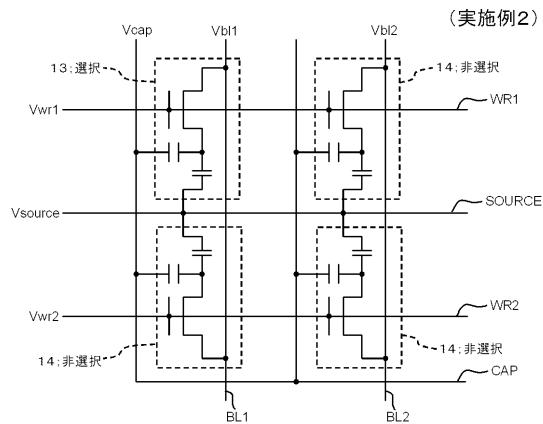

本発明の実施例2に係る不揮発性半導体記憶装置について図面を用いて説明する。図4は、本発明の実施例2に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した部分断面図である。

【0030】

実施例2に係る不揮発性半導体記憶装置は、一方のソース・ドレイン拡散層3とフューズ上部電極7に接続された接続コンタクト28a上の層間絶縁膜11中に、下層側から順に、キャパシタ下部電極32、キャパシタ絶縁膜33、キャパシタ上部電極34が積層したキャパシタ31が形成されている。キャパシタ下部電極32は、接続コンタクト28b

10

20

30

40

50

を介して接続コンタクト 28a に電気的に接続されている。キャパシタ上部電極 34 は、接続コンタクト 28c を介してキャパシタプレート線 CAP に電気的に接続されている。その他の基本的構成（選択トランジスタ 8、アンチフューズ 9）は、実施例 1 と同様である。また、図 4 のようなメモリセルは、図 5 のように選択トランジスタとアンチフューズが直列に接続された構成となる。メモリセルは行列に配列しており、行方向の各メモリセルのゲート電極はワード線 WR 1、WR 2 に接続されており、列方向の各メモリセルの他方のソース・ドレイン拡散層はビット線 BL 1、BL 2 に接続されており、各メモリセルのアンチフューズの一端は共通ソース線 SOURCE に接続されており、各メモリセルのキャパシタ上部電極は共通のキャパシタプレート線 CAP に接続されている。

## 【0031】

10

次に、本発明の実施例 2 に係る不揮発性半導体記憶装置の動作について図面を用いて説明する。図 5 は、本発明の実施例 2 に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。図 6 は、本発明の実施例 2 に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

## 【0032】

書き込み動作では、半導体基板（図 4 の 1）及びフューズ下部電極拡散層（図 4 の 27）に接続された共通ソース線 SOURCE を接地電位にし、選択ビット線 BL 1 に VPP / 2 を印加し、選択ワード線 WR 1 に VPP を印加し、フューズ上部電極（図 4 の 7）のノードを充電した後、選択ワード線 WR 1 と選択ビット線 BL 1 の電位を下げ、キャパシタ上部電極（図 4 の 34）に接続されるキャパシタプレート線 CAP に VPP / 2 の書き込み電位を印加し、キャパシタ下部電極（図 4 の 32）に接続されるフューズ上部電極（図 4 の 7）の電位を該 VPP 程度に昇圧し、フューズ上部電極（図 4 の 7）下の薄ゲート絶縁膜（図 4 の 5）を破壊する。

20

## 【0033】

読み出し動作は、実施例 1 と同様なので説明を省略する。

## 【0034】

実施例 2 によれば、アンチフューズ 9 の薄ゲート絶縁膜 5 の破壊はキャパシタ 31 による昇圧電位で行うため、過剰電流が流れることがなく、書き込み時の消費電力を低減できる利点がある。また、キャパシタ 31 がアンチフューズ 9 の上部に形成されるので、メモリセルの面積を増加することなく形成できる。

30

## 【実施例 3】

## 【0035】

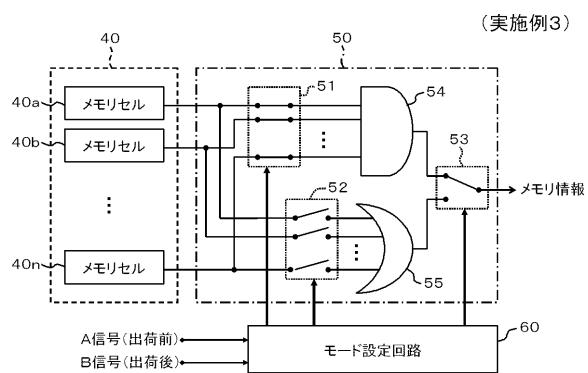

本発明の実施例 3 に係る不揮発性半導体記憶装置について図面を用いて説明する。図 7 は、本発明の実施例 3 に係る不揮発性半導体記憶装置の回路構成を模式的に示した図である。

## 【0036】

実施例 3 に係る不揮発性半導体記憶装置は、メモリセルユニット 40 と、制御回路 50 と、モード設定回路 60 と、を有する。

## 【0037】

メモリセルユニット 40 は、実施例 1 の選択トランジスタ（図 1 の 8）とアンチフューズ（図 1 の 9）が直列に接続されたメモリセル 40a、40b、……、40n を有する。メモリセルユニット 40 は、複数のメモリセル 40a、40b、……、40n によって 1 つの情報を記憶する。各メモリセル 40a、40b、……、40n のビット線（図 1 の BL）は、制御回路 50 の第 1 選択回路 51 および第 2 選択回路 52 のそれぞれに電気的に接続されている。

40

## 【0038】

制御回路 50 は、メモリセルユニット 40 の各メモリセル 40a、40b、……、40n からの信号に応じてメモリ情報の出力を制御する。制御回路 50 は、モード設定回路 60 からの制御信号に基づいてメモリ情報の出力を制御する。制御回路 50 は、第 1 選択回路 51 と、第 2 選択回路 52 と、第 3 選択回路 53 と、AND 回路 54 と、OR 回路 55

50

と、を有する。

【0039】

第1選択回路51は、モード設定回路60からの制御信号に基づいて、各メモリセル40a、40b、……、40nとAND回路54の間の各配線のスイッチングを制御する。第1選択回路51は、モード設定回路60にA信号が入力されているときに各配線をON状態にし、モード設定回路60にB信号が入力されているときに各配線をOFF状態にする。

【0040】

第2選択回路52は、モード設定回路60からの制御信号に基づいて、各メモリセル40a、40b、……、40nとOR回路55の間の各配線のスイッチングを制御する。第2選択回路52は、モード設定回路60にA信号が入力されているときに各配線をOFF状態にし、モード設定回路60にB信号が入力されているときに各配線をON状態にする。

【0041】

第3選択回路53は、モード設定回路60からの制御信号に基づいて、AND回路54及びOR回路55からの一方の情報を選択して出力するように制御する。第3選択回路53は、モード設定回路60にA信号が入力されているときにAND回路54からの情報を出力し、モード設定回路60にB信号が入力されているときにOR回路55からの情報を出力する。

【0042】

AND回路54は、メモリセルユニット40の各メモリセル40a、40b、……、40nから第1選択回路51を介して入力された信号が全て1(図1のアンチフューズ9が導通)のときに第3選択回路53に向けてメモリ情報として1を出力し、それ以外のときは第3選択回路53に向けてメモリ情報として0を出力する。

【0043】

OR回路55は、メモリセルユニット40の各メモリセル40a、40b、……、40nから第2選択回路52を介して入力された信号のいずれか又は全てが1(図1のアンチフューズ9が導通)のときに第3選択回路53に向けてメモリ情報として1を出力し、それ以外のときは第3選択回路53に向けてメモリ情報として0を出力する。

【0044】

モード設定回路60は、制御回路50の動作モードを制御する。モード設定回路60は、A信号が入力されているときに、第1選択回路51をON状態にするとともに、第2選択回路52をOFF状態にし、第3選択回路53をAND回路54側を選択するように制御信号を出力するように制御する。モード設定回路60は、B信号が入力されているときに、第1選択回路51をOFF状態にするとともに、第2選択回路52をON状態にし、第3選択回路53をOR回路55側を選択するように制御信号を出力するように制御する。

【0045】

不揮発性半導体記憶装置の動作の一例を説明する。

【0046】

出荷前では、A信号をモード設定回路60に入力すると、メモリセルユニット40の各メモリセル40a、40b、……、40nからの信号が第1選択回路51を介してAND回路54に入力され、各信号が全て1であればAND回路54から第3選択回路53を介してメモリ情報として1が出力される。

【0047】

出荷時には、B信号をモード設定回路60に入力すると、メモリセルユニット40の各メモリセル40a、40b、……、40nからの信号が第2選択回路52を介してOR回路55に入力され、各信号のいずれか又は全てが1であればOR回路55から第3選択回路53を介してメモリ情報として1が出力される。

【0048】

10

20

30

40

50

実施例3によれば、例えば、アンチフューズ(図1の9)の良否判定基準を出荷前より出荷後の方を緩和させることで、メモリセル40a、40b、……、40nの書き込み後のアンチフューズ(図1の9)の抵抗変動等の経時・経ストレス変化に対して、出荷後にアンチフューズ(図1の9)に起因する不良発生の確率を減少させることができる。

【実施例4】

【0049】

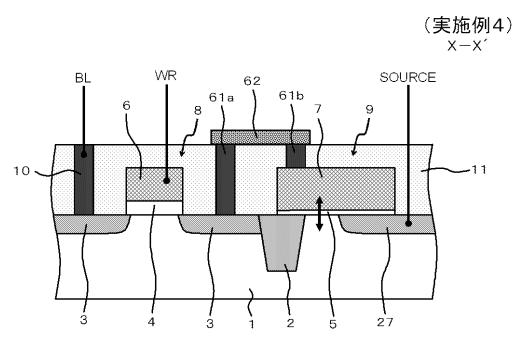

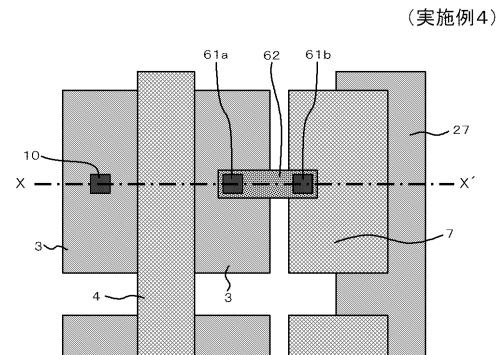

本発明の実施例4に係る不揮発性半導体記憶装置について図面を用いて説明する。図1 1は、本発明の実施例4に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した図12のX-X'間の断面図である。図12は、本発明の実施例4に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した部分平面図である。

【0050】

実施例1(図1参照)に係る不揮発性半導体記憶装置では、接続コンタクト(図1の28)が、選択トランジスタ(図1の8)及びアンチフューズ(図1の9)上に成膜された層間絶縁膜(図1の11)に形成されるとともにソース・ドレイン拡散層(図1の3)の一部とフューズ上部電極(図1の7)の一部とを含んだ1つの開口部内に形成されている。一方、実施例4に係る不揮発性半導体記憶装置では、接続コンタクトが、選択トランジスタ8及びアンチフューズ9上に成膜された層間絶縁膜11に形成されるとともにソース・ドレイン拡散層3の一部を含んだ第1開口部内に形成された接続コンタクト61aと、層間絶縁膜11に形成されるとともにフューズ上部電極7の一部を含んだ第2開口部内に形成された接続コンタクト61bと、接続コンタクト61aと接続コンタクト61bとを電気的に接続するメタル配線62とからなる。アンチフューズ9では、MOSハーフトランジスタ構造となっており、フューズ下部電極拡散層27と素子分離領域2との間の領域の半導体基板1乃至フューズ下部電極拡散層27上的一部に、薄ゲート絶縁膜5を介して、ポリシリコンよりなるフューズ上部電極7が形成されている。なお、その他の構成、及び動作については、実施例1と同様である。

【0051】

なお、アンチフューズ9は、上部電極7と下部電極27を離間させることが望ましい(図25参照)。詳細については、実施例1と同様である。

【0052】

実施例4によれば、ソース・ドレイン拡散層3とフューズ上部電極7とを2つの接続コンタクト61a、61bとメタル配線62を用いて電気的に接続するので、実施例1の1つの接続コンタクトを用いる場合と比べて、変形コンタクトを用いないので製造が容易になるという利点がある。

【実施例5】

【0053】

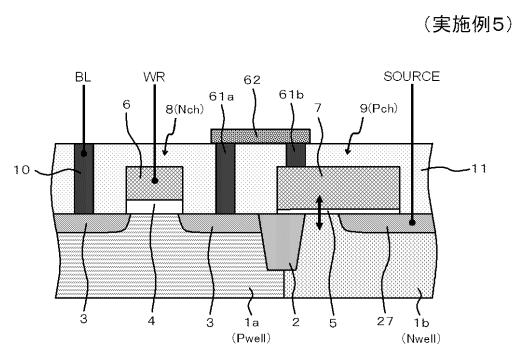

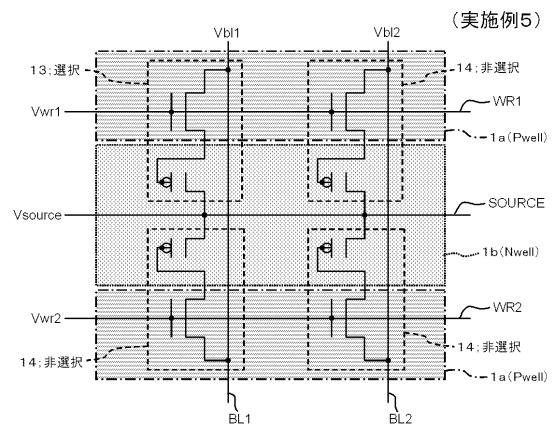

本発明の実施例5に係る不揮発性半導体記憶装置について図面を用いて説明する。図1 3は、本発明の実施例5に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した部分断面図である。

【0054】

実施例5に係る不揮発性半導体記憶装置では、選択トランジスタ8がNチャネル型であって半導体基板(図示せず)に形成されたPウェル1a上に構成され、アンチフューズ9がPチャネル型であって半導体基板(図示せず)に形成されたNウェル1b上に構成されている。その他の構成は、実施例4と同様である。

【0055】

なお、アンチフューズ9は、上部電極7と下部電極27を離間させることが望ましい(図26参照)。詳細については実施例1と同様である。

【0056】

なお、図13のようなメモリセル(セット)は、図14のように選択トランジスタとアンチフューズが直列に接続された構成となる。メモリセルは行列に配列しており、行方向の各メモリセルのゲート電極はワード線WR1、WR2に接続されており、列方向の各メ

10

20

30

40

50

モリセルの他方のソース・ドレイン拡散層はビット線 B L 1、B L 2 に接続されており、各メモリセルのアンチフューズの他端は共通ソース線 S O U R C E に電気的に接続されている。選択トランジスタ部のNウェル 1 b は、ワード線 W R 1、W R 2 に沿って行方向に配置されている。アンチフューズ部のPウェル 1 a は、Nウェル 1 b 間に配置されている。選択トランジスタ部の各Nウェル 1 b は、セルアレイ全体に共通に電気的に接続されている。アンチフューズ部の各Pウェル 1 a は、セルアレイ全体に共通に電気的に接続されている。共通ソース線 S O U R C E もセルアレイ全体に共通に電気的に接続されている。

#### 【0057】

次に、本発明の実施例 5 に係る不揮発性半導体記憶装置の動作について図面を用いて説明する。図 14 は、本発明の実施例 5 に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。図 15 は、本発明の実施例 5 に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

10

#### 【0058】

書き込み動作では、Pウェル 1 a、及びNウェル 1 b を接地電位とし、共通ソース線 S O U R C E を負の書き込み電位 - V P P とし、選択ビット線 B L 1 と選択ワード線 W R 1 を正の書き込み電位 V P P とすることで、フューズ下部電極拡散層（図 13 の 27）とフューズ上部電極（図 13 の 7）から正負の書き込み電位 + / - V P P により、アンチフューズ（図 13 の 9）の薄ゲート絶縁膜（図 13 の 5）を破壊する。

#### 【0059】

読み出し動作では、Pウェル 1 a、Nウェル 1 b、及び共通ソース線 S O U R C E を接地電位にし、選択ワード線 W R 1 と選択ビット線 B L 1 に I O 電位 V d d I O を印加して行う。アンチフューズ（図 13 の 9）の薄ゲート絶縁膜（図 13 の 5）が破壊されれば導通し、破壊されていなければ非導通で、メモリセルに書き込まれたデータを読み出すことができる。

20

#### 【0060】

なお、各配線の電位制御は、図示されていないコントローラによって行われる。

#### 【0061】

実施例 5 によれば、正負の書き込み電位 + / - V P P をアンチフューズに印加して書き込みを行うので、書き込み電位を低い絶対値の電位にすることができるという利点がある。

30

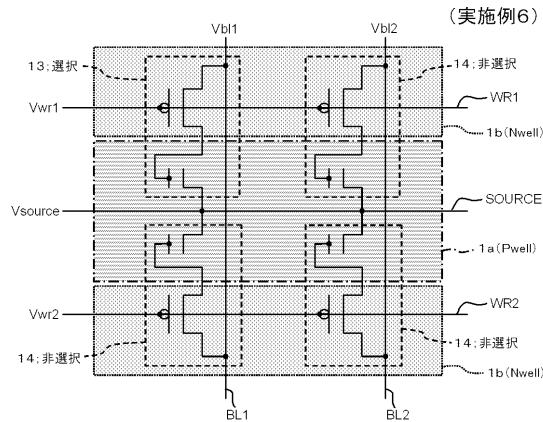

#### 【実施例 6】

#### 【0062】

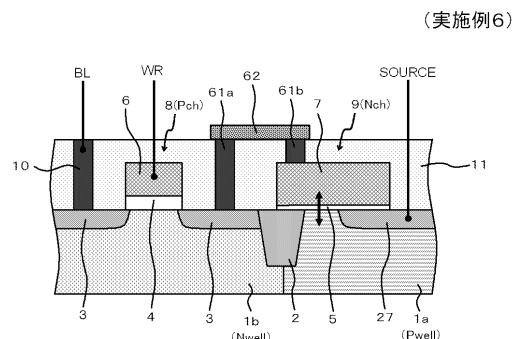

本発明の実施例 6 に係る不揮発性半導体記憶装置について図面を用いて説明する。図 16 は、本発明の実施例 6 に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した部分断面図である。

#### 【0063】

実施例 6 に係る不揮発性半導体記憶装置では、選択トランジスタ 8 が P チャネル型であって半導体基板（図示せず）に形成された N ウェル 1 b 上に構成され、アンチフューズ 9 が N チャネル型であって半導体基板（図示せず）に形成された P ウェル 1 a 上に構成されている。その他の構成は、実施例 4 と同様である。

40

#### 【0064】

なお、アンチフューズ 9 は、上部電極 7 と下部電極 27 を離間させることが望ましい（図 27 参照）。詳細については、実施例 1 と同様である。

#### 【0065】

なお、図 16 のようなメモリセル（セット）は、図 17 のように選択トランジスタとアンチフューズが直列に接続された構成となる。メモリセルは行列に配列しており、行方向の各メモリセルのゲート電極はワード線 W R 1、W R 2 に接続されており、列方向の各メモリセルの他方のソース・ドレイン拡散層はビット線 B L 1、B L 2 に接続されており、各メモリセルのアンチフューズの他端は共通ソース線 S O U R C E に電気的に接続されている。選択トランジスタ部のNウェル 1 b は、ワード線 W R 1、W R 2 に沿って行方向に

50

配置されている。アンチフューズ部のPウェル1aは、Nウェル1b間に配置されている。選択トランジスタ部の各Nウェル1bとアンチフューズ部の各Pウェル1aとは、それぞれセルアレイ全体に共通に電気的に接続され、フューズ下部電極（図16の27）に電気的に接続された共通ソース線SOURCEもセルアレイ全体に共通に電気的に接続されている。

#### 【0066】

次に、本発明の実施例6に係る不揮発性半導体記憶装置の動作について図面を用いて説明する。図17は、本発明の実施例6に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。図18は、本発明の実施例6に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

10

#### 【0067】

書き込み動作では、Pウェル1a、及び共通ソース線SOURCEを接地電位とし、選択ビット線BL1、選択ワード線WR1、及びNウェル（図16の1b）を書き込み電位VPP（正の電位）とすることで、アンチフューズ（図16の9）の薄ゲート絶縁膜（図16の5）を破壊する。

#### 【0068】

読み出し動作では、Pウェル1a、及び共通ソース線SOURCEを接地電位にし、選択ワード線WR1、選択ビット線BL1、及びNウェル1bにIO電位VddIOを印加して行う。アンチフューズ（図16の9）の薄ゲート絶縁膜（図16の5）が破壊されていれば導通し、破壊されていなければ非導通で、メモリセルに書き込まれたデータを読み出すことができる。

20

#### 【0069】

なお、各配線の電位制御は、図示されていないコントローラによって行われる。

#### 【0070】

実施例6によれば、選択トランジスタ8をPチャネル型にすることで、書き込み電位VPPのVt落ち（しきい値電位の低下）を抑止することができ、ドレイン（選択ビット線BL）に印加した書き込み電位VPPをそのままフューズ上部電極7に印加できるので、結果的に書き込み電位VPPを低電圧化できるという利点がある。なお、実施例5のように選択トランジスタ（図16の8）がNチャネル型の場合、ドレイン（選択ビット線BL）に印加した書き込み電位VPPのしきい値分の電位が下がってフューズ上部電極（図16の7）に印加される。

30

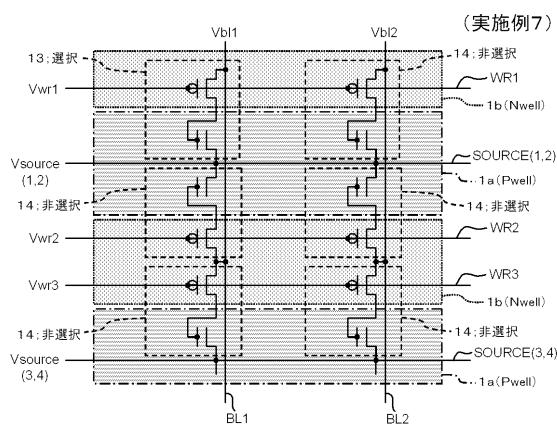

#### 【実施例7】

#### 【0071】

本発明の実施例7に係る不揮発性半導体記憶装置について図面を用いて説明する。図19は、本発明の実施例7に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。図20は、本発明の実施例7に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

#### 【0072】

実施例7に係る不揮発性半導体記憶装置は、実施例6（図17参照）の行方向にメモリセルを増やしたものである。

40

#### 【0073】

実施例7に係る不揮発性半導体記憶装置は、選択トランジスタがPチャネル型であって半導体基板（図示せず）に形成されたNウェル1b上に構成され、アンチフューズがNチャネル型であって半導体基板（図示せず）に形成されたPウェル1a上に構成されている点は、実施例6（図16参照）と同様である。選択トランジスタとアンチフューズからなるメモリセル（セット）は、図19のように選択トランジスタとアンチフューズが直列に接続された構成となる。メモリセルは行列に配列しており、行方向の各メモリセルのゲート電極はワード線WR1、WR2、WR3に接続されており、列方向の各メモリセルの他方のソース・ドレイン拡散層はビット線BL1、BL2に接続されている。1行目と2行目のメモリセルのフューズ下部電極（図16の27）は、ソース線SOURCE（1, 2

50

) に電気的に接続されている。3行目と4行目のメモリセルのフューズ下部電極(図16の27)は、ソース線SOURCE(3、4)に電気的に接続されている。図示されていないn行目とn+1行目のメモリセルのフューズ下部電極(図16の27)は、ソース線SOURCE(n、n+1)に電気的に接続されることになる。選択トランジスタ部のNウェル1bは、ワード線WR1、WR2に沿って行方向に配置されている。アンチフューズ部のPウェル1aは、Nウェル1b間に配置されている。選択トランジスタ部の各Nウェル1bは、セルアレイ全体に共通に電気的に接続されている。アンチフューズ部の各Pウェル1aは、セルアレイ全体に共通に電気的に接続されている。

#### 【0074】

書込み動作では、Pウェル1a、及びソース線SOURCE(1、2)を接地電位とし、ソース線SOURCE(3、4)を浮遊(open)とし、選択ビット線BL1、非選択ワード線WR2、WR3、及びNウェル1bとを書き込み電位VPP(正の電位)とすることで、アンチフューズ(図16の9)の薄ゲート絶縁膜(図16の5)を破壊する。

10

#### 【0075】

読み出し動作では、Pウェル1a、及びソース線SOURCE(1、2)、SOURCE(3、4)を接地電位にし、選択ビット線BL1、非選択ワード線WR2、WR3、及びNウェル1bにIO電位VddIOを印加して行う。アンチフューズの薄ゲート絶縁膜(図16の5)が破壊されていれば導通し、破壊されていなければ非導通で、メモリセルに書き込まれたデータを読み出すことができる。

#### 【0076】

20

なお、各配線の電位制御は、図示されていないコントローラによって行われる。

#### 【0077】

実施例7によれば、ソース線をワード線2本毎に分離し、書き込み時には選択セルに連結されるソース線のみを接地させ、他のソース線は浮遊状態にして、ソースが浮遊状態の非選択セルのアンチフューズに加わる書き込みディスターブは大きく緩和されるという利点がある。なお、実施例7では、選択トランジスタのNウェルがセルアレイ共通であり、書き込み時に非選択のセル全部のNウェルにもVPPが印加されるので、非選択セルのアンチフューズ上部電極のノード電位が浮き上がり、接地された共通ソースの下部電極との間の電位がアンチフューズの絶縁膜に印加される書き込みディスターブを受けることがある。

30

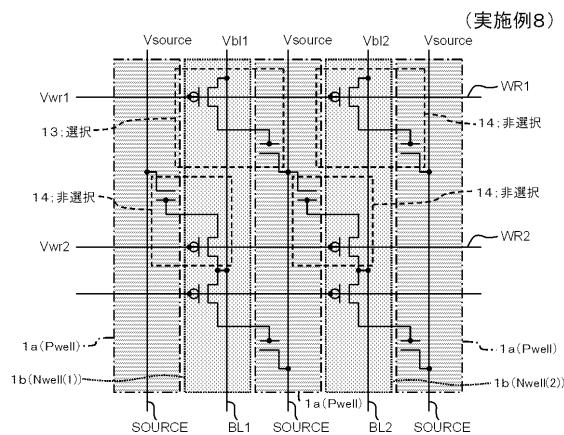

#### 【実施例8】

#### 【0078】

本発明の実施例8に係る不揮発性半導体記憶装置について図面を用いて説明する。図21は、本発明の実施例8に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。図22は、本発明の実施例8に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

#### 【0079】

実施例8に係る不揮発性半導体記憶装置は、実施例6(図16参照)のように行方向に延在したPウェル1a、Nウェル1bを交互に配置するのではなく、列方向に延在したPウェル1a、Nウェル1bを交互に配置したものである。

40

#### 【0080】

実施例8に係る不揮発性半導体記憶装置では、選択トランジスタがPチャネル型であつて半導体基板(図示せず)に形成されたNウェル1b上に構成され、アンチフューズがNチャネル型であつて半導体基板(図示せず)に形成されたPウェル1a上に構成される点は、実施例6(図16参照)と同様である。選択トランジスタとアンチフューズからなるメモリセル(セット)は、図21のように選択トランジスタとアンチフューズが直列に接続された構成となる。メモリセルは行列に配列しており、行方向の各メモリセルのゲート電極はワード線WR1、WR2に接続されており、列方向の各メモリセルの他方のソース・ドレイン拡散層はビット線BL1、BL2に接続されている。各メモリセルのフューズ下部電極(図16の27)は、列方向に延在した共通ソース線SOURCEに電気的に接

50

続されている。選択トランジスタ部のNウェル1bは、ピット線BL1、BL2に沿って列方向に配置されている。アンチフューズ部のPウェル1aは、Nウェル1b間に配置されている。選択トランジスタ部のNウェル(1)1bとNウェル(2)1bは、別々に電位制御される。アンチフューズ部の各Pウェル1aは、セルアレイ全体に共通に電気的に接続され、フューズ下部電極(図16の27)に電気的に接続された共通ソース線SOURCEも、セルアレイ全体に共通に電気的に接続されている。

【0081】

書き込み動作では、Nウェル(2)1b、Pウェル1a、及び共通ソース線SOURCEを接地電位とし、選択ピット線BL1、非選択ワード線WR2、及びNウェル(1)1bを書き込み電位VPP(正の電位)とすることで、アンチフューズの薄ゲート絶縁膜(図16の5)を破壊する。

【0082】

読み出し動作では、Nウェル(2)1b、Pウェル1a、及び共通ソース線SOURCEを接地電位とし、選択ピット線BL1、非選択ワード線WR2、及びNウェル(1)1bにIO電位VddIOを印加して行う。アンチフューズの薄ゲート絶縁膜(図16の5)が破壊されていれば導通し、破壊されていなければ非導通で、メモリセルに書き込まれたデータを読み出すことができる。

【0083】

実施例8によれば、書き込み時の非選択セルのアンチフューズに印加される書き込みディスターブを受ける問題に關し、Nウェル(1)、Nウェル(2)を列配置にピット線毎に分離し、書き込み時には選択したセル列のNウェルにのみ書き込み電圧VPPを印加するので、書き込みディスターブを受けるのは同一列のセルのみとなり、ディスターブ時間が大幅に緩和されるというメリットがある。

【図面の簡単な説明】

【0084】

【図1】本発明の実施例1に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した部分断面図である。

【図2】本発明の実施例1に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。

【図3】本発明の実施例1に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

【図4】本発明の実施例2に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した部分断面図である。

【図5】本発明の実施例2に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。

【図6】本発明の実施例2に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

【図7】本発明の実施例3に係る不揮発性半導体記憶装置の回路構成を模式的に示した図である。

【図8】従来例に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した部分断面図である。

【図9】従来例に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。

【図10】従来例に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

【図11】本発明の実施例4に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した図12のX-X'間の断面図である。

【図12】本発明の実施例4に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した部分平面図である。

【図13】本発明の実施例5に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した部分断面図である。

10

20

30

40

50

【図14】本発明の実施例5に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。

【図15】本発明の実施例5に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

【図16】本発明の実施例6に係る不揮発性半導体記憶装置におけるメモリセルの構成を模式的に示した部分断面図である。

【図17】本発明の実施例6に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。

【図18】本発明の実施例6に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

【図19】本発明の実施例7に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。

【図20】本発明の実施例7に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

【図21】本発明の実施例8に係る不揮発性半導体記憶装置の構成を模式的に示した回路図である。

【図22】本発明の実施例8に係る不揮発性半導体記憶装置の各配線の書き込み時及び読み出し時の電位を示した表である。

【図23】本発明の実施例1に係る不揮発性半導体記憶装置におけるメモリセルの構成の変形例(変形例1)を模式的に示した部分断面図である。

【図24】メモリセルのアンチフューズにおける書き込み後の導通箇所の水平距離と電流量の関係を模式的に示したグラフである。

【図25】本発明の実施例4に係る不揮発性半導体記憶装置におけるメモリセルの構成の変形例(変形例2)を模式的に示した部分断面図である。

【図26】本発明の実施例5に係る不揮発性半導体記憶装置におけるメモリセルの構成の変形例(変形例3)を模式的に示した部分断面図である。

【図27】本発明の実施例6に係る不揮発性半導体記憶装置におけるメモリセルの構成の変形例(変形例4)を模式的に示した部分断面図である。

#### 【符号の説明】

##### 【0085】

- 1、101 半導体基板

- 1 a P ウエル

- 1 b N ウエル

- 2、102 素子分離領域

- 3、103 ソース・ドレイン拡散層(ソース/ドレイン)

- 4、104 厚ゲート絶縁膜(第1ゲート絶縁膜)

- 5、105 薄ゲート絶縁膜(第2ゲート絶縁膜)

- 6、106 ゲート電極

- 7、107 フューズ上部電極(上部電極)

- 8、108 選択トランジスタ

- 9、109 アンチフューズ

- 10、10a、10b、110 ピットコンタクト

- 11、111 層間絶縁膜

- 13、113 選択メモリセル

- 14、114 非選択メモリセル

- 16 サイドウォール

- 27、127 フューズ下部電極拡散層(フューズ下部電極)

- 28、28a、28b、28c 接続コンタクト

- 31 キャパシタ

- 32 キャパシタ下部電極

10

20

30

40

50

|                   |              |    |

|-------------------|--------------|----|

| 3 3               | キャパシタ絶縁膜     |    |

| 3 4               | キャパシタ上部電極    |    |

| 4 0               | メモリセルユニット    |    |

| 4 0 a、4 0 b、4 0 n | メモリセル        |    |

| 5 0               | 制御回路         |    |

| 5 1               | 第1選択回路       |    |

| 5 2               | 第2選択回路       |    |

| 5 3               | 第3選択回路       |    |

| 5 4               | AND回路        |    |

| 5 5               | OR回路         | 10 |

| 6 0               | モード設定回路      |    |

| 6 1 a、6 1 b       | 接続コンタクト      |    |

| 6 2               | メタル配線        |    |

| W R               | ワード線         |    |

| W R 1             | 選択ワード線       |    |

| V w r 1           | 選択ワード線電位     |    |

| W R 2、W R 3       | 非選択ワード線      |    |

| V w r 2、V w r 3   | 非選択ワード線電位    |    |

| W P               | プレート線        |    |

| W P 1             | 選択プレート線      | 20 |

| V w p 1           | 選択プレート線電位    |    |

| W P 2             | 非選択プレート線     |    |

| V w p 2           | 非選択プレート線電位   |    |

| B L               | ビット線(デジット線)  |    |

| B L 1             | 選択ビット線       |    |

| V b 1 1           | 選択ビット線電位     |    |

| B L 2             | 非選択ビット線      |    |

| V b 1 2           | 非選択ビット線電位    |    |

| S O U R C E       | ソース線         |    |

| V s o u r c e     | ソース線電位       | 30 |

| C A P             | キャパシタプレート線   |    |

| V c a p           | キャパシタプレート線電位 |    |

【図1】

【図2】

【図3】

| (実施例1) |       |       |       |       |         |

|--------|-------|-------|-------|-------|---------|

|        | (選択)  | (非選択) | (選択)  | (非選択) |         |

|        | Vbl1  | Vbl2  | Vwr1  | Vwr2  | Vsource |

| 書き込み   | VPP   | 0     | VPP   | 0     | 0       |

| 読み出し   | VddIO | 0     | VddIO | 0     | 0       |

【図4】

【図5】

【図6】

(実施例2)

|      | (選択)        | (非選択) | (選択)      | (非選択) |             |         |

|------|-------------|-------|-----------|-------|-------------|---------|

|      | Vbl1        | Vbl2  | Vwr1      | Vwr2  | Vcap        | Vsource |

| 書き込み | VPP/2<br>→0 | 0     | VPP<br>→0 | 0     | 0→<br>VPP/2 | 0       |

| 読み出し | VddIO       | 0     | VddIO     | 0     | VddIO       | 0       |

【図7】

【図8】

【図 9】

【図 10】

(従来例)

|      | (選択) | (非選択) | (選択)  | (非選択) | (選択) | (非選択) |

|------|------|-------|-------|-------|------|-------|

| 書込み  | Vbl1 | Vbl2  | Vwr1  | Vwr2  | Vwp1 | Vwp2  |

| 読み出し | 0    | VPP/2 | VPP/2 | 0     | VPP  | 0     |

|      | (選択) | (非選択) | (選択) | (非選択) | (選択)  | (非選択) |

|------|------|-------|------|-------|-------|-------|

| 書込み  | Vbl1 | Vbl2  | Vwr1 | Vwr2  | Vwp1  | Vwp2  |

| 読み出し | 0    | Vdd   | Vdd  | 0     | VddIO | 0     |

【図 11】

【図 12】

【図13】

【図14】

【図15】

(実施例5)

|      | 選択    | 非選択  | 選択    | 非選択  |       |         |       |

|------|-------|------|-------|------|-------|---------|-------|

|      | Vbl1  | Vbl2 | Vwr1  | Vwr2 | Pwell | Vsource | Nwell |

| 書き込み | VPP   | 0    | VPP   | 0    | 0     | -VPP    | 0     |

| 読み出し | VddIO | 0    | VddIO | 0    | 0     | 0       | 0     |

【図16】

【図17】

【図18】

(実施例6)

|      | 選択            | 非選択        | 選択            | 非選択        |                |              |                 |

|------|---------------|------------|---------------|------------|----------------|--------------|-----------------|

| 書込み  | Vbl1<br>VPP   | 0<br>VPP   | Vwr1<br>VPP   | 0<br>VddIO | Nwell<br>VPP   | 0<br>VddIO   | Pwell<br>0<br>0 |

| 読み出し | Vwr2<br>VddIO | 0<br>VddIO | Vbl2<br>VddIO | 0<br>VddIO | SOURCE<br>open | Vsource<br>0 | WR1<br>Pwell    |

【図19】

【図20】

(実施例7)

|      | 選択            | 非選択    | 選択            | 非選択        | 非選択                                   | 選択                        | 非選択                    |               |                   |

|------|---------------|--------|---------------|------------|---------------------------------------|---------------------------|------------------------|---------------|-------------------|

| 書込み  | Vbl1<br>VPP   | 0<br>0 | Vbl2<br>VPP   | 0<br>VddIO | Vwr1<br>VPP                           | 0<br>VddIO                | Vwr2<br>VddIO          | Nwell<br>open | Pwell<br>VPP<br>0 |

| 読み出し | Vwr3<br>VddIO | 0<br>0 | Vbl1<br>VddIO | 0<br>VddIO | SOURCE<br>Vsource<br>(1, 2)<br>(3, 4) | Vsource<br>(1, 2)<br>open | Vsource<br>(3, 4)<br>0 | VddIO<br>0    | VddIO<br>0        |

【図21】

【図22】

(実施例8)

|      | 選択    | 非選択  | 選択   | 非選択   | 選択           | 非選択          |         |       |

|------|-------|------|------|-------|--------------|--------------|---------|-------|

|      | Vbl1  | Vbl2 | Vwr1 | Vwr2  | Nwell<br>(1) | Nwell<br>(2) | Vsource | Pwell |

| 書き込み | VPP   | 0    | 0    | VPP   | VPP          | 0            | 0       | 0     |

| 読み出し | VddIO | 0    | 0    | VddIO | VddIO        | 0            | 0       | 0     |

【図23】

【図24】

【図25】

【図26】

【図27】

---

フロントページの続き

(72)発明者 大沼 卓司

神奈川県川崎市中原区下沼部1753番地 NECエレクトロニクス株式会社内

審査官 井出 和水

(56)参考文献 米国特許第04502208(US, A)

特開平10-112505(JP, A)

特開2001-308283(JP, A)

特開2003-179132(JP, A)

特開2004-221141(JP, A)

特表2005-504434(JP, A)

特開平11-214538(JP, A)

特開平08-316427(JP, A)

特開平10-189768(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/10

G11C 17/06