(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6769975号

(P6769975)

(45) 発行日 令和2年10月14日 (2020.10.14)

(24) 登録日 令和2年9月28日 (2020.9.28)

|              |              |

|--------------|--------------|

| (51) Int.CI. | F 1          |

| G 11 C 11/22 | (2006.01)    |

| G 11 C 7/14  | (2006.01)    |

| G 11 C 7/04  | (2006.01)    |

|              | G 11 C 11/22 |

|              | G 11 C 7/14  |

|              | G 11 C 7/04  |

請求項の数 22 (全 19 頁)

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2017-543727 (P2017-543727)  |

| (86) (22) 出願日      | 平成28年2月16日 (2016.2.16)        |

| (65) 公表番号          | 特表2018-514891 (P2018-514891A) |

| (43) 公表日           | 平成30年6月7日 (2018.6.7)          |

| (86) 国際出願番号        | PCT/US2016/018011             |

| (87) 国際公開番号        | W02016/133869                 |

| (87) 国際公開日         | 平成28年8月25日 (2016.8.25)        |

| 審査請求日              | 平成31年2月12日 (2019.2.12)        |

| (31) 優先権主張番号       | 62/116,977                    |

| (32) 優先日           | 平成27年2月17日 (2015.2.17)        |

| (33) 優先権主張国・地域又は機関 | 米国 (US)                       |

| (31) 優先権主張番号       | 15/019,026                    |

| (32) 優先日           | 平成28年2月9日 (2016.2.9)          |

| (33) 優先権主張国・地域又は機関 | 米国 (US)                       |

|               |                                                                                                                       |

|---------------|-----------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者     | 390020248<br>日本テキサス・インスツルメンツ合同会社<br>東京都新宿区西新宿六丁目24番1号                                                                 |

| (73) 特許権者     | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 75265<br>-5474 ダラス メイル ステイショ<br>ン 3999 ピーオーボックス 655<br>474 |

| (74) 上記1名の代理人 | 100098497<br>弁理士 片寄 恒三                                                                                                |

最終頁に続く

(54) 【発明の名称】強誘電体メモリにおけるデータ感知のための基準電圧の設定

## (57) 【特許請求の範囲】

## 【請求項 1】

1 トランジスタ・1 キャパシタ (1T-1C) タイプの強誘電体メモリセルを含む集積回路において基準電圧を設定する方法であって、

複数の前記強誘電体メモリセルを第1のデータ状態にプログラミングすることであって、前記第1のデータ状態が第2のデータ状態より低いキャパシタンス分極状態に対応する、前記プログラミングすることと、

読み出すときに最弱メモリセルが前記第2のデータ状態をリターンする基準電圧レベルに対応する第1の基準電圧限界を識別するために、前記複数のプログラミングされた強誘電体メモリセルを複数の基準電圧レベルで反復的に読み出すことであって、

前記強誘電体メモリセルの全てが前記第1のデータ状態をリターンする初期基準電圧レベルで前記複数の強誘電体メモリセルを読み出すことであって、前記初期基準電圧レベルが前記複数の基準電圧レベルの第1の電圧レベルである、前記読み出すことと、

その後、前記第1の基準電圧限界が識別されるまで、前記初期基準電圧レベルを徐々に下げるにより前記残りの複数の基準電圧レベルの各々で前記複数の強誘電体メモリセルを読み出すことと、

前記複数の基準電圧レベルの各々で前記複数の強誘電体メモリセルの各々に対して、前記強誘電体メモリセルにアクセスすることと、

前記強誘電体メモリセルが前記第1のデータ状態又は前記第2のデータ状態をリターンするか否かを判定するために、前記アクセスすることに応答して前記強誘電体メモリセル

により生成される電圧を前記基準電圧レベルと比較することと、

を含む、前記反復的に読み出すことと、

前記基準電圧を前記第1の基準電圧限界に基づく動作レベルに設定するように前記集積回路を構成することと、

を含む、方法。

【請求項2】

請求項1に記載の方法であって、

前記反復的に読み出す前に、電気的パラメータを前記第1のデータ状態の読み出しに対する最悪ケース条件に設定することを更に含む、方法。

【請求項3】

請求項2に記載の方法であって、

電気的パラメータを最悪ケース条件に設定することが、電源電圧を高電源電圧仕様限界に対応するレベルに設定することを含む、方法。

【請求項4】

請求項1に記載の方法であって、

前記反復的に読み出す前に、前記集積回路に対する環境パラメータを前記第1のデータ状態を読み出すことに対する最悪ケース条件に設定することを更に含む、方法。

【請求項5】

請求項4に記載の方法であって、

環境パラメータを最悪ケース条件に設定することが、前記集積回路を高温仕様限界に対応する温度まで加熱することを含む、方法。

【請求項6】

請求項1に記載の方法であって、

前記アクセスすることに応答して前記強誘電体メモリセルにより生成される電圧が前記強誘電体メモリセルに関連するビット線に提供され、

前記第1のデータ状態が、印加される電圧がない場合に前記強誘電体メモリセルにおける強誘電体キャパシタが第1の極性の電圧を保持する第1の分極状態に対する前記強誘電体キャパシタの分極に対応し、

前記アクセスすることが、

前記強誘電体メモリセルにおける前記強誘電体キャパシタの第1のプレートを前記強誘電体メモリセルに関連する前記ビット線に結合することと、

電圧パルスを前記強誘電体キャパシタの第2のプレートに印加することと、

前記ビット線での前記電圧を前記基準電圧レベルと比較することと、

を含む、方法。

【請求項7】

請求項6に記載の方法であって、

前記強誘電体メモリセルにおける前記強誘電体キャパシタの第1のプレートを前記強誘電体メモリセルに関連する前記ビット線に結合することが、前記ビット線と前記強誘電体キャパシタの前記第1のプレートとの間に結合されるトランジスタを活性化するために前記強誘電体メモリセルに関連するワード線に電圧を供給することを含む、方法。

【請求項8】

請求項1に記載の方法であって、

前記基準電圧を設定するように前記集積回路を構成することが、構成レジスタのコンテンツを前記第1の基準電圧限界と公差との加算に対応する値を用いて書き込むことを含む、方法。

【請求項9】

請求項1に記載の方法であって、

前記動作レベルが、前記第1の基準電圧限界と公差との加算に等しい、方法。

【請求項10】

請求項1に記載の方法であって、

10

20

30

40

50

前記集積回路が、単一の集積回路ウエハに形成される複数の類似する集積回路の1つであり、

前記プログラミングすることと、反復的読み出すことと、構成することとが、ウエハ形式での前記集積回路を用いて実施される、方法。

【請求項11】

請求項1に記載の方法であって、

前記集積回路がパッケージ化された集積回路である、方法。

【請求項12】

請求項1に記載の方法であって、

前記アクセスすることに応答して前記強誘電体メモリセルにより生成される前記電圧が感知增幅器を用いて前記基準電圧レベルと比較される、方法。10

【請求項13】

1トランジスタ・1キャパシタ(1T-1C)タイプの強誘電体メモリセルを含む集積回路において基準電圧を設定する方法であって、

複数の前記強誘電体メモリセルを第1のデータ状態にプログラムすることであって、前記第1のデータ状態が第2のデータ状態より高いキャパシタンス分極状態に対応する、前記プログラムすることと、

読み出すときに最弱メモリセルが前記第2のデータ状態をリターンする基準電圧レベルに対応する第1の基準電圧限界を識別するために、前記複数のプログラムされた強誘電体メモリセルを複数の基準電圧レベルで反復的に読み出すことであって、20

前記強誘電体メモリセルの全てが前記第1のデータ状態をリターンする初期基準電圧レベルで前記複数の強誘電体メモリセルを読み出すことであって、前記初期基準電圧レベルが前記複数の基準電圧レベルの第1の電圧レベルである、前記読み出すことと、

その後、前記第1の基準電圧限界が識別されるまで、前記初期基準電圧レベルを徐々に上げることにより前記残りの複数の基準電圧レベルの各々で前記複数の強誘電体メモリセルを読み出すことと、

前記複数の基準電圧レベルの各々で前記複数の強誘電体メモリセルの各々に対して、

前記強誘電体メモリセルにアクセスすることと、

前記強誘電体メモリセルが前記第1のデータ状態又は前記第2のデータ状態をリターンするか否かを判定するために、前記アクセスすることに応答して前記強誘電体メモリセルにより生成される電圧を前記基準電圧レベルと比較することと、30

を含む、前記反復的に読み出すことと、

前記基準電圧を前記第1の基準電圧限界に基づく動作レベルに設定するように前記集積回路を構成することと、

を含む、方法。

【請求項14】

請求項13に記載の方法であって、

前記反復的に読み出す前に、電気的パラメータを前記第1のデータ状態の読み出しに対する最悪ケース条件に設定することを更に含む、方法。

【請求項15】

請求項14に記載の方法であって、

電気的パラメータを最悪ケース条件に設定することが、電源電圧を低電源電圧仕様限界に対応するレベルに設定することを含む、方法。40

【請求項16】

請求項13に記載の方法であって、

前記反復的に読み出す前に、前記集積回路に対する環境パラメータを前記第1のデータ状態の読み出しに対する最悪ケース条件に設定することを更に含む、方法。

【請求項17】

請求項16に記載の方法であって、

環境パラメータを最悪ケース条件に設定することが、前記集積回路を低温仕様限界に対50

応する温度まで冷却することを含む、方法。

【請求項 1 8】

請求項 1 3 に記載の方法であって、

前記アクセスすることに応答して前記強誘電体メモリセルにより生成される前記電圧が前記強誘電体メモリセルに関連するビット線に提供され、

前記第 1 のデータ状態が、印加される電圧がない場合に前記強誘電体メモリセルにおける強誘電体キャパシタが第 1 の極性の電圧を保持する第 1 の分極状態に対する前記強誘電体キャパシタの分極に対応し、

前記アクセスすることが、

前記強誘電体メモリセルにおける前記強誘電体キャパシタの第 1 のプレートを前記強誘電体メモリセルに関連する前記ビット線に結合することと、

電圧パルスを前記強誘電体キャパシタの第 2 のプレートに印加することと、

前記ビット線での前記電圧を前記基準電圧レベルと比較することと、

を含む、方法。

【請求項 1 9】

請求項 1 3 に記載の方法であって、

前記集積回路を前記基準電圧に設定するように構成することが、前記第 1 の基準電圧限界と公差との減算に対応する値を用いて、構成レジスタのコンテンツを書き込むことを含む、方法。

【請求項 2 0】

請求項 1 3 に記載の方法であって、

前記動作するレベルが、前記第 1 の基準電圧限界からの公差の減算に等しい、方法。

【請求項 2 1】

請求項 1 3 に記載の方法であって、

前記集積回路が、単一の集積回路ウエハに形成される複数の類似する集積回路の 1 つであり、

前記プログラムすることと、反復的に読み出すことと、構成することが、ウエハ形式での前記集積回路を用いて実施される、方法。

【請求項 2 2】

請求項 1 3 に記載の方法であって、

前記集積回路がパッケージ化された集積回路である、方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本願は、全般的に、不揮発性メモリ集積回路に関し、特に、強誘電体メモリデバイスにおける動作パラメータの設定に関する。

【背景技術】

【0 0 0 2】

最近の電子システムでは、大規模集積に対する高密度化及び適合性に加え、高速スイッチング時間と低電力損失との最良の組み合わせを提供するという理由で、従来の金属酸化物半導体 (MOS) 及び相補型 MOS (CMOS) ロジック及びメモリデバイスが普及している。しかしながら、基本的に、これらの技術に従って構築されるロジック及びメモリ回路がバイアス電力の除去時にデータ状態を保持しないため、それらのデバイスは本質的に揮発性である。メモリ及びロジック状態を不揮発性様式でストアする能力は、特にモバイル及び小型システムにおいては極めて望ましい。その結果、近年、不揮発性デバイスを構築するための種々の技術が開発されてきた。

【0 0 0 3】

不揮発性ソリッドステートメモリ技術の一つは、誘電体材料がジルコン酸チタン酸鉛 (PZT) 又はストロンチウムビスマスタンタル酸塩 (SBT) 等の分極性強誘電体材料であるようなキャパシタの構築に関与する。キャパシタプレートから電圧が取り除かれた後

10

20

30

40

50

、これらの強誘電体キャパシタの電荷対電圧(  $Q - V$  )特性におけるヒステリシスが、バイナリ状態の不揮発性ストレージを可能にし、その際、ストアされた状態は強誘電体材料の分極状態に対応する。これに対して、従来のMOSキャパシタは、キャパシタ電圧の除去時に、ストアされた電荷を失う。トランジスタレベルより上及び材料導体レベルより下にキャパシタを配置する等の、最近のCMOS集積回路と大いに互換性のあるプロセスによって強誘電体キャパシタが構築され得る。

#### 【0004】

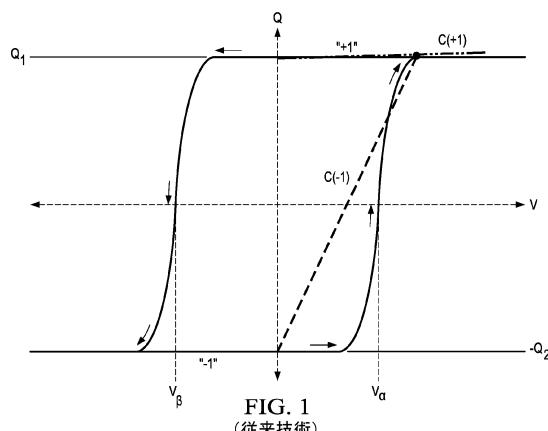

図1は、従来の強誘電体キャパシタの  $Q - V$  特性の例を示す。図示されるように、導電プレートを横切ってストアされる電荷(  $Q$  )は、プレートに印加される電圧(  $V$  )に依存し、またその電圧の最近の履歴に依存する。キャパシタプレートを横切って印加される電圧  $V$  が、「保磁( coercive )」電圧  $+ V$  を超える場合、キャパシタは「+1」状態に分極する。この特性に従って、「+1」状態に分極された後、電圧  $V$  が保磁電圧  $- V$  を上まわったままである限り、キャパシタは  $+ Q_1$  のストアされた電荷を示す。反対に、キャパシタプレートを横切って印加される電圧  $V$  が保磁電圧  $- V$  よりマイナスの場合、キャパシタは、「-1」状態に分極され、 $+ V$  より低い印加された電圧  $V$  に対して、 $- Q_2$  のストアされた電荷を示す。

#### 【0005】

不揮発性ソリッドステートメモリにおいて用いられるような強誘電体キャパシタの或る重要な特性は、強誘電体キャパシタが分極された状態間で示すキャパシタンスにおける差である。基本的に、エレメントのキャパシタンスは、ストアされた電荷対印加された電圧の比を指す。強誘電体キャパシタが、誘電体膜( 即ち、強誘電体材料 )により分離される平行プレートとしてのその構成故に線形キャパシタンスを有する一方、強誘電体キャパシタはまた、分極電圧の印加の際に起こる分極状態における変化に応答して、有意な分極キャパシタンス( 即ち、電荷ストレージ )を示す。例えば、図1を参照すると、「-1」状態から「+1」状態への強誘電体キャパシタの分極は、相対的に高いキャパシタンス  $C(-1)$  において反映され、保磁電圧  $V$  を超える電圧による分極状態の変化に応答して、キャパシタにおける分極電荷のストレージに反映する。一方、すでにその「+1」状態にあるキャパシタは、その強誘電体ドメインが、印加された保磁電圧の方向に既に整合され、少量の付加的分極電荷しかストアされないので、分極に起因して少量のキャパシタンス  $C(+1)$  しか示さない。

#### 【0006】

この強誘電体の挙動は、一般に「強誘電体RAM」又は「FeRAM」又は「FRAM」デバイスと称される、不揮発性強誘電体の読み出し/書き込みランダムアクセスメモリ( RAM )デバイスに採用されている。FRAMは、特にポータブル電子デバイス及びシステム等の多くの電子システムに用いられ、とりわけペースメーカー及び除細動器等の埋め込み可能な医療デバイスにおいて注目されている。2T-2C( 2トランジスタ、2キャパシタ )セルを含む強誘電体キャパシタを含む種々のメモリセルアーキテクチャが知られている。2T-2Cでは、セルにおける2つの強誘電体キャパシタが相補状態に分極され、その際、相補分極の極性はストアされたデータ状態を示す。2T-2Cセルの相補分極状態は、読み出し動作において、一対のビット線に差分信号を出力する。ビット線ペアにおけるこの差分信号は、ストアされたデータ状態をリトリーブするために、従来のメモリアーキテクチャにおける差分感知増幅器によって感知される。

#### 【0007】

強誘電体メモリセルの別の既知の配置は、1T-1C( 1トランジスタ、1キャパシタ )配置である。1T-1Cセルは、2T-2C及びそれより大型の( 例えば、6T )FRAMセルタイプに比較すると、このセルに対して必要とされるチップ面積が小さいため、注目されている。しかしながら、後で詳述するように、1T-1C FRAMセルの感知は必然的にシングルエンドであり、従って、2T-2Cセルの差分感知の読み出しに比べて有意に少ない読み出しマージンしか提供しない。

#### 【0008】

10

20

30

40

50

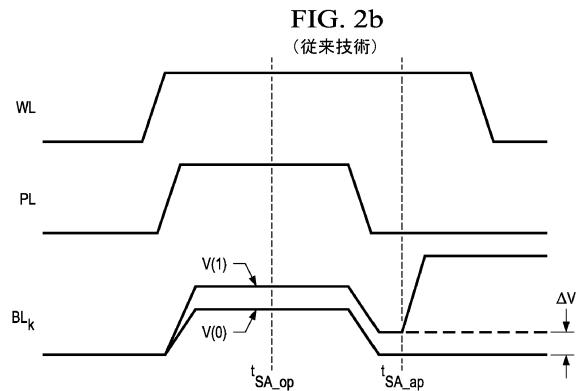

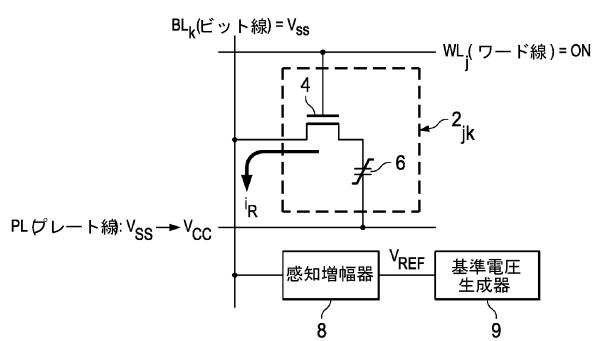

図2aは、従来の1T-1C F R A Mセル $2_{j,k}$ の典型的な配置を示し、類似のセル2のアレイの行j及び列kに存在する単一のセルを表す。セル $2_{j,k}$ は、nチャネルバストランジスタ4、及び強誘電体キャパシタ6を含む。トランジスタ4のソース/ドレインパスは、アレイの列kに対するビット線 $B_{L,k}$ と強誘電体キャパシタ6の頂部プレートとの間に接続される。トランジスタ4のゲートは、アレイの行jに対するワード線 $W_{L,j}$ によって制御される。強誘電体キャパシタ6の底部プレートはプレート線 $P_L$ に接続され、プレート線 $P_L$ は、アレイにおいて（または、アーキテクチャによってはアレイの特定の部分において）全てのセル2に対して共通であり得る。従って、1T-1C F R A Mセルは、従来の動的RAMメモリセルと同様に構築される。感知增幅器8が、ビット線 $B_{L,k}$ に結合され、後述するように、読み出し電流 $i_R$ によって生成されるビット線電圧を、基準電圧生成回路9によって生成される基準電圧 $V_{REF}$ と比較するように動作する。

#### 【0009】

図2aのセル $2_{j,k}$ 等の1T-1Cメモリセルでは、感知されるときに高いキャパシタンスを示す分極状態、即ちこのケースでは「-1」の分極状態は「1」データ状態として考えられ、低いキャパシタンス「+1」の分極状態は「0」データ状態として考えられる。セル $2_{j,k}$ は、電圧をプレート線 $P_L$ 、及びビット線 $B_{L,k}$ に印加することによって書き込まれ、それが、付勢されたワード線 $W_{L,j}$ を用いて、キャパシタ6を所望の分極状態に分極する。この例において、低電圧( $V_{ss}$ )をビット線 $B_{L,k}$ に印加し、ワード線 $W_{L,j}$ をオンにし、その後、プレート線 $P_L$ を高電圧( $V_{cc}$ )に上昇させることによって、図1の「+1」の分極状態に対応する「0」データ状態が書き込まれる。反対に、低電圧( $V_{ss}$ )をプレート線 $P_L$ に印加し、ワード線 $W_{L,j}$ をオンにし、その後、ビット線 $B_{L,k}$ を高電圧( $V_{cc}$ )まで上昇させることによって、「-1」の分極状態に対応する「1」データ状態が書き込まれる。

#### 【0010】

セル $2_{j,k}$ の読み出し動作は、ビット線 $B_{L,k}$ の低電圧（例えば、 $V_{ss}$ ）へのプリチャージで始まる。図2bに示されるように、ビット線 $B_{L,k}$ がプリチャージされた後、ワード線 $W_{L,j}$ が付勢されて、トランジスタ4をオンにし、キャパシタ6をビット線 $B_{L,k}$ に結合する。図1のヒステリシスの図に従って、低電圧 $V_{ss}$ からのプレート線 $P_L$ の電圧は、その後、高電圧 $V_{cc}$ まで上昇されて、キャパシタ6の分極キャパシタンスの問い合わせを行う。特に、プレート線 $P_L$ の付勢は、ビット線 $B_{L,k}$ 上に読み出し電流 $i_R$ を誘導して、ビット線 $B_{L,k}$ 上に電圧を生成する。ビット線 $B_{L,k}$ 上に生成された電圧レベルは、ビット線キャパシタンスに対して、セル $2_{j,k}$ における強誘電体キャパシタ6によって示されるキャパシタンスに依存する。図2bに示されるように、キャパシタ6が「+1」分極状態にある場合、読み出し電流 $i_R$ は相対的に低く、従って、相対的に低レベルのビット線電圧 $V(0)$ を生成する。反対に、キャパシタ6の「-1」分極状態は、相対的に強い読み出し電流 $i_R$ となり、ビット線 $B_{L,k}$ において一層高いレベルの電圧 $V(1)$ となる。

#### 【0011】

図2bに示すような「アフターパルス感知」アプローチに従って、プレート線 $P_L$ パルスの後、時間 $t_{sA\_ap}$ で感知增幅器8がアクティブにされ、感知增幅器8が、ビット線電圧を基準電圧生成器9からの基準電圧 $V_{REF}$ と比較する。ストアされたデータ状態を識別するために、それぞれ、予期される低データ状態レベルと高データ状態レベルである $V(0)$ と $V(1)$ の間（即ち、図2bのウインドウ $V$ の範囲内）の公称電圧に基準電圧 $V_{REF}$ が設定される。時間 $t_{sA\_ap}$ に続いて、感知增幅器8は、図2bに示されるように、高いビット線電圧 $V(1)$ を検出することに応答してビット線 $B_{L,k}$ をフルロジック「1」レベルまで駆動し、低いビット線電圧 $V(0)$ を検出することに応答してフルロジック「0」レベルまで駆動する。

#### 【0012】

「ステップ感知」又は「オン・パルス感知」と称される、別の従来の感知アプローチは、図2bに示される時間 $t_{sA\_op}$ 等のプレート線パルスの間、感知增幅器8をアクテ

10

20

30

40

50

イブにする。図2bに示されるように、データ「0」状態の非スイッチングキャパシタンスは感知される電圧には影響しないので、アフターパルス感知の例では、ビット線電圧V(0)、V(1)は一層低い共通モード電圧を表す。アフターパルス感知は、強誘電体キャパシタの非スイッチングキャパシタンスにおける変動のビット線電圧への影響を最小にするための多くの実装において好適である。

#### 【0013】

いずれのケースにおいても、「1」データ状態の読み出しあは、この読み出し動作が、本質的に、セル $2_{j_k}$ を逆のデータ状態にプログラムするので、破壊的である。セル $2_{j_k}$ を前の分極状態に戻すために、その後、典型的にライトバック動作（図2bにおいては示されていない）が実施される。

10

#### 【0014】

上の説明から明らかなように、1T-1C F R A Mセル $2_{j_k}$ からの読み出し信号は、シングルエンドであり、基準電圧 $V_{REF}$ 等の基準レベルとの比較によって感知される。一方、2T-2C F R A Mセルは、差動信号を感知増幅器に提供し、そこで、セルからの相補ビット線電圧の極性によってデータ状態が示される。従って、上述されたように、読み出しマージンは1T-1C F R A Mセルに伴う重要な課題である。

#### 【0015】

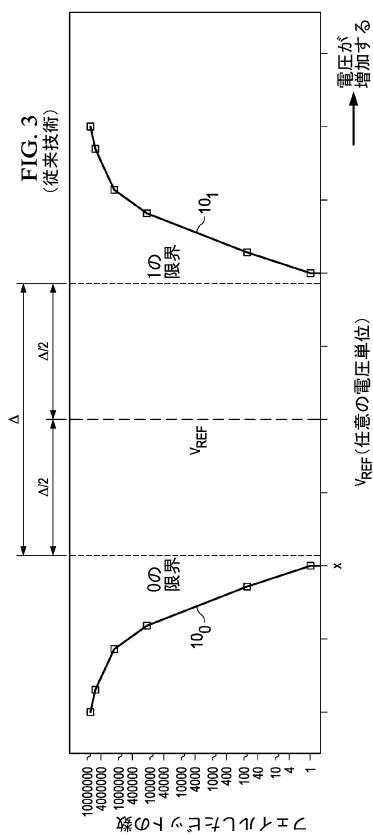

図3は、両方のデータ状態に対して、従来の1T-1C F R A Mメモリに対する基準電圧の累積ビットフェイル分布の例を示す。曲線 $10_0$ 及び $10_1$ は、それぞれ、種々の基準電圧 $V_{REF}$ （最強の「0」セルがフェイルする基準電圧に対して基準単位で表現される）でフェイルする「0」データ状態ビット及び「1」データ状態ビットの数を示す。図3から明らかなように、一層低い基準電圧 $V_{REF}$ は、「0」データ状態が正しく読み出されることが一層難しく、「1」データ状態が正しく読み出されることが一層容易であり、また、一層高い基準電圧 $V_{REF}$ は、「1」データ状態が正しく読み出されることが一層難しく、「0」データ状態が正しく読み出されることが一層容易である。別の言い方をすると、一方向への基準電圧 $V_{REF}$ の移動が、一方のデータ状態に対する読み出しマージンを改善させるが、他方のデータ状態に対する読み出しマージンを減少させる。従って、従来のF R A Mメモリは典型的に、最悪ケースの読み出しマージンを最大にするために、通常動作に対するそれらの基準電圧 $V_{REF}$ を、最弱「0」セルがフェイルするレベルと最弱「1」セルがフェイルするレベルから等距離である電圧に設定する。図3に示されるように、基準電圧 $V_{REF}$ は、最弱「0」セルがフェイルする「0の限界」より $/2$ 上で、且つ、最弱「1」セルがフェイルする「1の限界」より $/2$ 上あるレベルに設定される。ここで、 $/2$ は0の限界と1の限界との間の差である。実際には、この中間点基準電圧レベルは、典型的に、各デバイスの電気的テストの間に、各デバイスにおいて基準電圧を変化させてセルをテストした結果に基づいて構成レジスタをプログラミングすること等によって設定される。

20

#### 【0016】

更なる背景として、同時継続中であり本願の譲受人に譲渡され、参照として本明細書に組み込まれる、米国特許出願公開番号U S 2 0 1 5 / 0 3 5 7 0 5 0は、テストされている各集積回路に対して高い分極キャパシタンスデータ状態（例えば「1」状態）の読み出しに対する基準電圧レベルが決定される、F R A Mセルのデータ保持信頼性スクリーンを記載している。集積回路における複数のF R A Mセルが「1」データ状態にプログラムされ、その後、上昇された温度で読み出される。フェイルするセルの数は、パス/フェイル閾値に対して比較されて、その集積回路が長期データ保持欠陥に対して脆弱であるか否かが判定される。

30

#### 【0017】

更なる背景として、同時継続中であり本願と同一譲受人に譲渡され、参照として本明細書に組み込まれる、2 0 1 5 年9月18日に出願された米国特許出願番号U S 1 4 / 8 5 7, 8 7 3は、高い分極キャパシタンス状態にプログラミングされた後で、且つ、上昇された温度での緩和中断の後、サンプリングされたセルグループが種々の基準電圧レベルで

40

50

テストされる、F R A Mメモリアレイのデータ保持信頼性スクリーンを記載している。集積回路におけるF R A Mセルの全てをテストする際に用いられるサンプルグループのフェイルビットカウントからテスト基準電圧が演繹される。

【発明の概要】

【0 0 1 8】

説明される例は、デバイスの動作寿命にわたって最適な読み出しマージンを維持するため、1トランジスタ1キャパシタ(1 T - 1 C)タイプの強誘電体メモリセルを含む集積回路において、読み出し基準電圧を設定する方法を含む。

【0 0 1 9】

説明される例は、大幅な付加的製造テスト時間無しに実装可能であり、パッケージ化された形態又はウエハ形態のいずれにおいても集積回路上で実施可能であり、強誘電体メモリの設計に変更を必要とすることなく実装可能な方法を提供する。

【0 0 2 0】

或る実施形態に従って、1 T - 1 Cタイプの強誘電体メモリセルのアレイを含む集積回路を設定する方法がテストシーケンスの間に実装される。第1のセルがフェイルする基準電圧における第1の限界を判定するために、複数のメモリセルが、一層低い分極キャパシタス状態に対応する第1のデータ状態にプログラムされ、そのデータ状態に対する最悪ケース条件下で基準電圧を変動させて読み出される。その後、通常動作において用いられるための基準電圧が、第1の限界又はその付近のレベルに設定される。

【図面の簡単な説明】

【0 0 2 1】

【図1】従来の強誘電体キャパシタの電荷対電圧特性のグラフである。

【0 0 2 2】

【図2 a】従来の1 T - 1 C強誘電体メモリセル及びその動作を概略ブロック形態で図示する電気図である。

【0 0 2 3】

【図2 b】図2 aの1 T - 1 C強誘電体メモリセルの読み出しの動作を図示するタイミング図である。

【0 0 2 4】

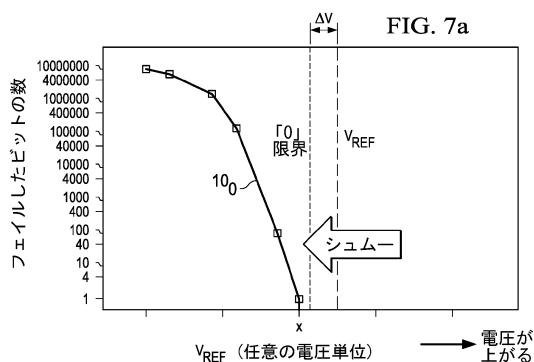

【図3】1 T - 1 Cタイプの強誘電体ランダムアクセスメモリ(F R A M)に対する累積ビットフェイル分布対基準電圧レベルのグラフを示す。

【0 0 2 5】

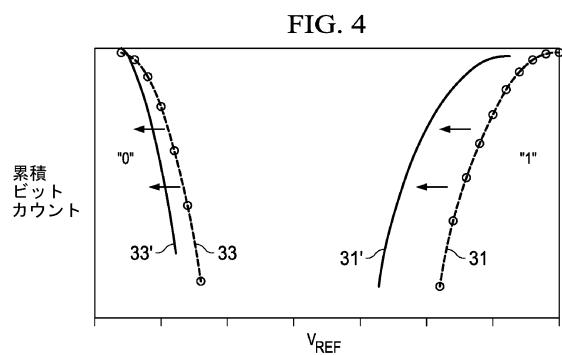

【図4】製造時と加速動作寿命テスト時における、1 T - 1 C F R A Mセルに対する累積ビットフェイル分布対基準電圧レベルのグラフを示す。

【0 0 2 6】

【図5】一実施形態に従ったF R A Mのブロック形態における電気図である。

【0 0 2 7】

【図6 a】実施形態に従った、図5のF R A Mに対して動作基準電圧を設定する方法を図示するフローチャートである。

【図6 b】実施形態に従った、図5のF R A Mに対して動作基準電圧を設定する方法を図示するフローチャートである。

【0 0 2 8】

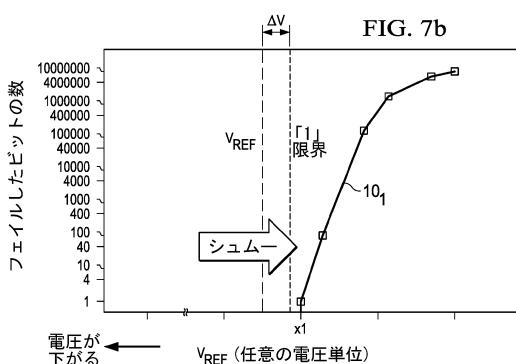

【図7 a】図6 aの実施形態に従った、図4の累積ビットフェイル分布のプロットに対する動作基準電圧の選択の例を示す。

【図7 b】図6 bの実施形態に従った、図4の累積ビットフェイル分布のプロットに対する動作基準電圧の選択の例を示す。

【発明を実施するための形態】

【0 0 2 9】

本明細書において説明される例示の実施形態は、1トランジスタ1キャパシタ(1 T - 1 C)ビットセルタイプの強誘電体ランダムアクセスメモリ(F R A M)の製造テストに

10

20

30

40

50

実装され、その文脈においてそのような実装は特に有利である。しかしながら、例示の実施形態の概念は、メモリセル以外の他のタイプの強誘電体要素を含む集積回路等の他の用途にも有利に適用され得る。

### 【0030】

高温焼成による等の長時間信頼性テストから明らかにされているように、強誘電体キャパシタは長期にわたると脱分極に対して脆弱である。この脱分極は、水素障壁フィルムの不均一性、又はデバイスピリュレーションに対する水素暴露における変動に因るものであり、その結果、強誘電体材料の中への水素の浸潤、及び従って、その材料を組み込む強誘電体キャパシタのヒステリシス特性における劣化に繋がると考えられている。F R A Mメモリ用途において、この脱分極は、感知電圧の印加によって感知されるとき、一層高い分極キャパシタンスを示す、分極状態に対する弱化されたデータ保持によって示される。図2a、及び図2bに対して上述したように従来のF R A M読み出し動作の場合、一層高いキャパシタンス（「-1」）分極状態は、F R A Mセル $2_{j_k}$ の「1」データ状態に対応し、したがって、弱化されたデータ保持が、ストアされた「1」データ値に対する劣化された読み出しマージンとして現れる。上述したように、2T-2Cセルによって生成される相補ビット線電圧の差動感知に因って、2T-2C F R A Mセルは1T-1C F R A Mセルに比べて、この種のデータ保持欠陥の影響を受けにくい。実際に、このデータ保持脆弱性は、1T-1C F R A Mメモリの多くのシステム用途における使用を限定し続けると考えられている。

### 【0031】

図4は、図2a及び図2bに関して上述したように、F R A Mセル $2_{j_k}$ のアレイに対するこの読み出しマージン劣化のメカニズムの挙動を図示する。図3のグラフは、基準電圧生成回路9によって生成され、図2aの感知增幅器8に印加される基準電圧 $V_{REF}$ のレベルを変動させて用い、「0」及び「1」にプログラムされたデータ状態に対し、及び長時間のデータ保持焼成の前と後で、「アフターパルス」感知が用いられる読み出し動作における、累積のフェイルしたビットカウントのグラフの形式である。特に、プロット31は、「1」データ状態にプログラムされ、時間ゼロ（即ち、データ保持焼成の前）で読み出されるとき、基準電圧レベル $V_{REF}$ が変動するとともに不正な「0」データ値をリターンする、アレイにおけるビットの累積数を図示する。このデータ状態では、一層高い基準電圧 $V_{REF}$ レベルが、一層多いビットをフェイルさせ、その際、最弱ビットが最低の基準電圧 $V_{REF}$ でフェイルする。同様に、プロット33は、データ保持焼成の前の、「0」データ状態に対する同じアレイについて累積のフェイルしたビットを図示する。このデータ状態では、最弱ビットが最高基準電圧 $V_{REF}$ レベルでフェイルする。

### 【0032】

プロット31'、33'は、125度で1000時間のデータ保持焼成に続く同じポビュレーションのF R A Mセルについて、それぞれ、累積のフェイルした「1」及び「0」のデータ状態ビットにおける変化を図示する。このデータ保持焼成は、F R A Mの動作寿命にわたって予期されるされるデータ保持信頼性の加速測定である。図4のプロット31からプロット31'へのシフトから明らかのように、このデータ保持焼成は「1」データ状態累積フェイルビットカウントが基準電圧 $V_{REF}$ の一層低いレベルへシフトするという結果になり、このデータ状態に対してデータ保持が弱化し、読み出しマージンが低減することを示している。反対に、プロット33'は、時間ゼロのプロット33に対して、「0」データ状態に対する累積のフェイルしたカウントが、同様に、基準電圧 $V_{REF}$ の一層低いレベルにシフトすることを図示する。しかしながら、このシフトは「0」データ状態に対する1T-1Cセルの読み出しマージンを実際に改善する。

### 【0033】

例示の実施形態に関連し、1T-1C F R A Mセルを用いるメモリに対して、基準電圧 $V_{REF}$ のレベルは、システム寿命の間、脱分極の影響による付加的なビット欠陥のリスクを冒すことなく最弱の「0」セルがフェイルする「「0」限界」に一層近くに設定され得ることが観察されている。このアプローチに従って「0」データ状態の読み出しマージン

10

20

30

40

50

ジンが低減されたとしても、その読み出しマージンは典型的に時間と共に改善し、一方で、「1」データ状態セルに対して有意な付加的マージンを提供し、従ってF R A Mデバイスの全体的なデータ保持信頼性を改善する。

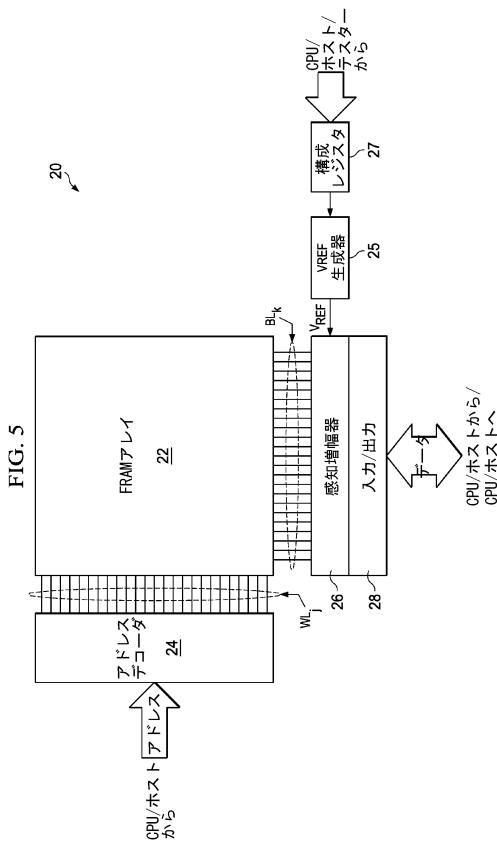

【0034】

図5は、実施形態が実装され得る、構築された強誘電体ランダムアクセスメモリ(F R A M)20のアーキテクチャを示す。この例において、F R A M 20はスタンダードアロンの強誘電体メモリデバイスとして示される。或いは、F R A M 20は、マイクロプロセッサ、単一チップマイクロコンピュータ、又は所謂システムオンチップ等の、大規模ロジックデバイスに統合され得る。F R A M 20は、所望により、そのような大規模集積回路において実現され得る。

10

【0035】

どのケースにおいても、これらの実施形態に従ったF R A M 20は、F R A Mアレイ22を含み、F R A Mアレイ22において、図2a及び図2bに関連して上述したセル $2_{j_k}$ 等の1T-1CタイプのF R A Mセルのアレイが行及び列に配置される。F R A Mアレイ22は、図5によって示唆されるように、F R A M 20において単一メモリブロックとして配置され得る。或いは、複数のメモリブロック又はアレイ22が、F R A M 20内で、及びそれが実装される集積回路内で実現され得る。このアーキテクチャにおいて、同じ行 $j$ におけるF R A Mセルは共通のワード線 $W L_j$ を共有し、同じ列 $k$ におけるF R A Mセルは共通のビット線 $B L_k$ を共有する。

【0036】

20

中央処理装置(C P U)又は他のホストプロセッサ等の外部デバイスからメモリアドレス値をデコードするために、従来の構成であり得るアドレスデコーダ24が、F R A M 20において提供される。そのメモリアドレスの行アドレス部に応答して、アドレスデコーダ24は、所望のメモリ動作(読み出し、又は書き込み/プログラミング)に対して適切に、選択されたワード線 $W L_j$ をアクティブにする。アレイ22からのビット線 $B L_k$ は、図2bに関連して上述したように、対応する感知增幅器26に結合される。概して、入力/出力回路要素28は、アレイ22におけるセルとデータバスD A T Aとの間のデータの通信のために、感知增幅器26に結合される。典型的に、入力/出力回路要素28は、メモリアドレスの列アドレス部に対応するアドレスデコーダ24から選択信号を受信し、それに基づいて、選択されたビット線 $B L_k$ からデータが転送(読み出し動作の場合)される、又は書き込まれる(書き込み動作の場合)。データバスD A T Aは、図5によって示唆されるように、ホスト又はC P Uと通信し得る。

30

【0037】

これらの実施形態に従って、読み出しサイクルにおいて、感知增幅器26の各々は、対応するビット線 $B L_k$ 上に誘導された電圧をその列における選択された行のF R A Mセルからの読み出し電流によって感知する。図2bに関連して上述したように、この感知は、図5に示されるように、そのビット線電圧を、 $V_{R E F}$ 生成器25からの基準電圧 $V_{R E F}$ と比較することによって実施される。

【0038】

$V_{R E F}$ 生成器25は、これらの実施形態に従って種々の方式で構築され得る。一つの実装に従って、 $V_{R E F}$ 生成器25は、n個の強誘電体キャパシタのバンクとして構築される。強誘電体キャパシタは、F R A Mセルと同様の様式でプログラム可能に分極され、感知增幅器26に転送される基準電圧を生成するように、互いに並列に選択的に接続され得る。更に具体的には、この実施形態において、構成レジスタ27のコンテンツに応答して、互いに並列であるこれらn個のキャパシタの×のサブセットの選択的接続を可能にするために、スイッチのバンクが提供され得る。或いは、 $V_{R E F}$ 生成器25が他のアプローチに従って構築され得る。例としては、強誘電体又は非強誘電体キャパシタ、従来の電圧基準生成回路、及びその他の可変基準電圧回路を備える「ダミー」メモリセルを用いることが含まれる。他の例は、オギワラらの「ファティーグフリー基準キャパシタを用いる可変基準ビット線電圧スキームを備える0.5mm、3V、1T1C、1-MビットF R

40

50

AM」、J. Solid State Circ., Vol. 35, No.4 (IEEE, 2000年4月)、545~551頁、及びJungらの「1T1C FRAMにおけるファティーグフリー基準スキーム及びプロセス誘発損傷」、J. Korean Phys. Soc., Vol. 39, No.1 (2001年7月)、80~86頁に記載され、両方とも参考として本明細書に組み込まれる。

【非特許文献1】Ogiwara et al., "A 0.5-mm, 3-V, 1T1C, 1-Mbit FRAM with a Variable reference Bit-Line Voltage Scheme using a Fatigue-Free Reference Capacitor", J. Solid State Circ, Vol. 35, No. 4 (IEEE, April 2000), pp. 545-551

【非特許文献2】Jung et al., "Fatigue-Free Reference Scheme and Process-Induced Damage in a 1T1C FRAM", J. Korean Phys. Soc, Vol. 39, No. 1 (July 2001), pp. 80-86

10

### 【0039】

この実施形態において、構成レジスタ27は、所望により1T-1C又は2T-2C構成のFRAMセルのバンクとして構築され得、そのコンテンツを動作寿命を通して保持する（即ち、不揮発性である）一方、FRAM20のテスト又は動作の間に再書き込みされ得る。或いは、構成レジスタ27は他の方式で構築され得る。これらの実施形態において、構成レジスタ27のコンテンツは、CPU、ホストプロセッサ、外部テスト機器、又は幾つかの他のデータソースによって設定され得る。また、これらの実施形態に従って、下記に説明するように、実施されるべき基準電圧 $V_{REF}$ を変化させてアレイ22のセルのフェイルビットカウントの「シュムー(shmoo)」を実施するために、構成レジスタ27を介して又は構成レジスタ27をバイパスすることにより、FRAM20の電気的テストの間、CPU、ホスト、外部テスト機器、又は幾つかの他のソースによって、感知増幅器26に印加される基準電圧 $V_{REF}$ が変えられ得る。

20

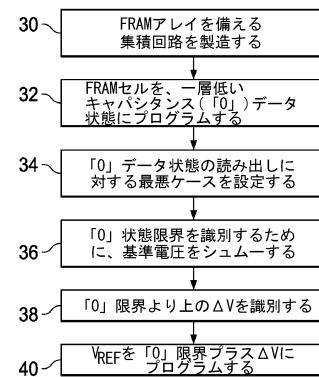

### 【0040】

図6a及び図7aを参照すると、FRAM20における基準電圧 $V_{REF}$ のレベルを設定する例示の方法において、基準電圧 $V_{REF}$ の設定は、製造元によりその製造におけるFRAM20のための最終電気的テストにおいて実施される。これにより、この方法によって設定される基準電圧 $V_{REF}$ のレベルが、意図されたシステム環境において通常動作使用に対して準備が整っていることが確実となる。FRAM20が実装される集積回路が、後のアッセンブリのため「チップ」又はウエハの形式で提供されるケースでは、この実施形態の方法は、ウエハ形式の場合FRAM20を含む集積回路の「マルチプローブ」電気的テストにおいて実施され得る。マルチプローブ電気的テストは、1つ又は複数の従来のマルチプローブテストステーションにおいて実装される従来の電気的テスト機器を用いて実施され得るもの等である。集積回路がパッケージ化された形式において製造及び提供されるケースでは、この実施形態の方法は、パッケージ化されたデバイスの最終電気的テストにおいて従来の電気的テスト機器によって実施され得る。或いは、FRAM20における基準電圧 $V_{REF}$ の設定は、所望により最終的なシステム用途において実施可能にされてもよい。いずれのケースでも、図6aを参照すると、この実施形態の方法はプロセス30から開始する。プロセス30では、FRAM20を含む集積回路が、所望のように製造され、それらは基準電圧 $V_{REF}$ の設定に対して所望の物理的形態である。

30

### 【0041】

この実施形態に従った、FRAM20における基準電圧 $V_{REF}$ の設定は、製造される集積回路におけるFRAMアレイの各事例に対して、又は複数のFRAMアレイ22をサポートする場合は $V_{REF}$ 生成回路25の各事例に対して、個別に実施される。これは、この実施形態に従って設定される基準電圧 $V_{REF}$ が集積回路毎に異なることが多く、従って、各FRAM事例が最良の基準電圧 $V_{REF}$ レベルを用いて最適化され得るようにするためである。或いは、テスト時間を省略するため又はその他の理由により、この方法はサンプル単位で適用され得、その際、1つのFRAM20の結果が他のFRAM20に適用される。しかしながら、このアプローチは、歩留まり損失が過度になるか又は最適なデータ保持性能に満たないという結果になり得る。

40

### 【0042】

50

また、この実施形態に従った、F R A M 2 0 における基準電圧  $V_{REF}$  の設定において自動テスト機器により実施される特定のプロセスは、全体的な機能的及びパラメータ的電気テストプログラム又はシーケンスの一部として含まれ得る。その点で、別の状況でフェイルしたセルに冗長メモリセルが置き替わることを可能にすることを含み、F R A M 2 0 が、完全に機能的であること及び所望の仕様に合致することを確実にするために、基準電圧  $V_{REF}$  の設定は、典型的に、所望に応じてそのようなテストに従う。

【 0 0 4 3 】

図 6 a を再度参照すると、プロセス 3 0 における F R A M 2 0 の製造、及び上述のようなその他の電気的テストに続き、プロセス 3 2 において、F R A M 2 0 のアレイ 2 2 における F R A M セルのポピュレーションが、上述の例での「0」データ状態に対応する一層低いキャパシタンス分極状態にプログラムされる（即ち、書き込まれる）。プロセス 3 2 においてプログラムされる F R A M セルのポピュレーションは、アレイ 2 2 における F R A M セルの全体のサブセットであり得るが、基準電圧  $V_{REF}$  の設定を最適化するために、プロセス 3 2 において、アレイ 2 2 の全ての F R A M セルが一層低いキャパシタンス分極状態にプログラムされることが好ましい。

【 0 0 4 4 】

プロセス 3 4 において、F R A M アレイ 2 2 から「0」（一層低いキャパシタンス）データ状態を読み出すことに対する最悪のケースに対する 1 つ又は複数の電気的及び環境的条件が、自動テスト機器によって又は自動テスト機器において設定される。上述のように構築される F R A M 2 0 のケースでは、「0」データ状態の読み出しに対する最悪のケースは、F R A M 2 0 に対する高温仕様限界（例えば、30 より上）に対応する温度、及び F R A M 2 0 に対する最大電源仕様電圧（即ち、最大  $V_{dd}$ ）を含む。プロセス 3 4 において実際に適用される特定の温度及び電源電圧は、F R A M 2 0 を含む集積回路デバイスに対する仕様限界、及びそのような適切な「ガードバンド」、及びデバイスの電気的テストにおいて用いられる仕様限界に対するその他の調整に依存し得る。また、パラメータに対する最悪のケースの設定は、プロキシによって適用され得る。例えば、室温でテストするとき、電源電圧は、仕様限界における高い周囲温度の影響を模倣するために、その電圧に対する仕様限界を超えて選択される増分だけ増大され得る。一層低いキャパシタンス分極状態の読み出しに対する最悪のケースに到達する際に有用なその他の電気的又は環境的条件が、所望に応じ、プロセス 3 4 において追加的に設定され得る。プロセス 3 4 において、これらの最悪ケース条件の幾つか又は全ての設定は、所望に応じ、プログラミングのプロセス 3 2 の前に適用され得る。

【 0 0 4 5 】

プロセス 3 6 において、プログラムされた「0」レベルのリターンを第 1 の（即ち、最弱）セルがフェイルする電圧に対応する「0」限界を識別するために、アレイ 2 2 が読み出されるにつれて基準電圧  $V_{REF}$  を「シュムー」するように自動テスト機器が操作される。逆に、電圧及び温度の予期される条件（即ち、最初のビットがフェイルする電圧よりも漸進的に高い）のもとで全ての「0」セルがパスする最低の基準電圧  $V_{REF}$  が、代わりに「0」限界として考えられ得る。「シュムー（shmoo）」とは、1 つ又は複数の電気的パラメータの複数の値で反復的に実施されるテスト動作を指す。この実施形態において、シュムープロセス 3 6 において変化するパラメータは、 $V_{REF}$  生成回路 2 5 によって生成され、図 5 の F R A M 2 0 における感知增幅器 2 6 に印加される基準電圧  $V_{REF}$  であり、その際、アレイ 2 2 のセルは、各基準電圧レベルで読み出される。基準電圧  $V_{REF}$  が 1 つの反復から次の反復に漸進的に変化する方式は、 $V_{REF}$  生成回路 2 5 の構成及び動作に依存し得る。 $V_{REF}$  生成回路 2 5 が強誘電体キャパシタのバンクとして構築される上述の F R A M 2 0 の実施形態では、基準電圧  $V_{REF}$  の変動は、感知增幅器 2 6 に印加される基準電圧  $V_{REF}$  を変調させるように、各反復において 1 つ又は複数の付加的キャパシタを選択的にスイッチを入れる（又は、場合によりスイッチを切る）ことによって達成される。図 7 a の例において、各基準単位は、 $V_{REF}$  生成回路 2 5 における付加的なキャパシタンス単位に対応し、この例において約 3 . 5 mV である。

10

20

30

40

50

## 【0046】

図7aにおいて示唆されるように、プロセス36のシムーの1つの例は、基準電圧 $V_{REF}$ を、少なくとも第1のセルが読み出しをフェイルするまで全てのセルが「0」レベルをリターンする高いレベルから、一層低いレベルへ漸進的に下げる変化させる。それは、図7aにおける約20の基準単位の $V_{REF}$ である。この例では、第1のビットの基準電圧 $V_{REF}$ が「0」データ状態読み出しをフェイルするので、このプロセス36において、「0」限界が識別される。或いは、プロセス36のシムーは、各連続する一層低いレベルでフェイルするセルの数を識別するように基準電圧 $V_{REF}$ を変化させ続けてもよく、それによって累積フェイルビット分布（図7aの曲線10<sub>0</sub>）が識別される。このアプローチにおいて、「0」限界は、所望に応じ、第1のビットがフェイルする実際のレベルではなく累積フェイルビット分布の外挿によって決定され得る。しかしながら、第1のフェイルビット（即ち、「0」限界）を通り過ぎて連続してシムーすることは、付加的なテスト時間を必要とする。

## 【0047】

好ましくは、シムーテストプロセス36において、基準電圧 $V_{REF}$ の各レベルでF R A M 2 0の全てのセルが読み出され、それによって、デバイスにおける真の最弱ビット及びそれがフェイルする $V_{REF}$ レベルが最も正確に識別され得る。しかしながら、代替として、テスト時間を短縮するために、各シムーステップにおいてF R A M 2 0のセルのサブセットが代わりに読み出されてもよい。

## 【0048】

プロセス36が最弱「0」ビットがフェイルする「0」限界を決定すると、基準電圧 $V_{REF}$ のプログラムされたレベルがこの実施形態に従って決定される。理論的には、図4に対して上述したように「0」セルはシステム寿命にわたり一層強くなるだけであるという仮定に基づいて、プログラムされた基準電圧 $V_{REF}$ は、この例において「0」限界より僅かに高い電圧に設定され得る。しかしながら、実際には、テスターとシステム実装との間の電圧の変動、及びデバイスの温度の変動に対して或る程度の公差を提供するように、基準電圧 $V_{REF}$ を「0」限界より充分に高い電圧に設定することが有用である。特に、1T-1Cタイプの典型的なF R A Mデバイスにおいて、感知增幅器26の動作に或るレベルのランダム性が存在することが観察されている。そのため、ランダムな感知增幅器の変動に対する公差も、動作におけるデータ読み出し欠陥を避ける際に有用である。これらのファクターの1つ又は複数に基づいて、プロセス38において、F R A M 2 0のための公差 $V$ が識別される。この公差 $V$ は、特徴付け又はその他の方式によって決定され得、類似のタイプ及び製造の全てのF R A M 2 0に適用される。例として、およそ15mVの公差 $V$ が、最近の1T-1C F R A Mデバイスに対して適切であると考えられている。この公差 $V$ は、典型的に「0」限界と、最弱「1」ビットがフェイルする基準電圧 $V_{REF}$ に対応する「1」限界との間の電圧差の20%に或いはそれ未満に、例えば、典型的に電圧差のおよそ10%等に設定される。しかしながら、この実施形態に従って、基準電圧 $V_{REF}$ のプログラムされたレベルは、その差に基づくのではなく、感知增幅器性能、温度、及び電圧において変動があることを前提として、「0」限界に実行可能な限り近い電圧に置かれる。

## 【0049】

この実施形態に従ったプロセス40において、「0」限界プラス公差 $V$ での基準電圧 $V_{REF}$ に対応する $V_{REF}$ のレベルが、システム使用における通常動作のためにF R A M 2 0内にプログラムされる。上述のように構築されるF R A M 2 0において、このプロセス40は構成レジスタ27をプログラムすることによって実施され、その際、コンテンツは「0」限界プラス公差 $V$ での基準電圧 $V_{REF}$ に対応する。この基準電圧 $V_{REF}$ は、従って、F R A M 2 0の通常動作において読み出し動作を実施するために感知增幅器26によって用いられる基準になる。その後、基準電圧 $V_{REF}$ の設定が完了し、所望により付加的なテスト又はF R A M 2 0のその他の処理が実施され得る。

## 【0050】

10

20

30

40

50

或る最悪ケース条件下で、時間ゼロにおいて最弱「0」セルがフェイルするレベル又はそのレベル近くの電圧に基準電圧 $V_{REF}$ をプログラムすることによって、この実施形態は、一層高いキャパシタンス強誘電体状態（例えば、上述の実施形態における「1」データ状態）でFRAMセルに対する読み出しマージンを最大化することに役立つ。これにより、データ読み出し欠陥という結果になる前に、「1」データ状態セルを大きくシフトさせることによって、図4に対して上述したような強誘電体デバイスにおいて生じる分極の損失に対して一層大きい公差を可能にする。上記で説明したように、「0」データセルに対する累積フェイルビット分布は長期にわたると一層低い $V_{REF}$ レベルにシフトし易いので、時間ゼロにおいて基準電圧 $V_{REF}$ を「0」限界近くにプログラムする結果「0」データ状態の読み出しマージンが低減されることによるリスクが少ない。従って、データ保持の観点から、FRAM20の動作寿命の性能は、回路設計又は製造プロセスの変更を必要とすることなく、この実施形態に従って有意に改善され得る。

10

#### 【0051】

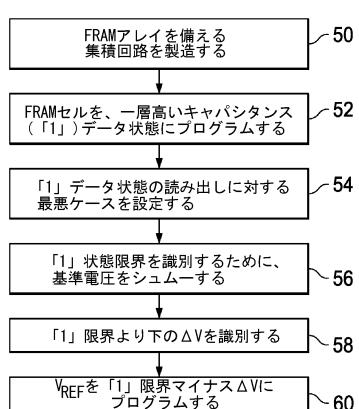

上述したように、この実施形態は、図4に示されるように、フェイルビット分布が動作寿命にわたって基準電圧 $V_{REF}$ の一層低いレベルに向かってシフトするという認識に基づいている。例示の実施形態に関連して、プレート線に印加されるパルスの完了の後、感知增幅器がアクティブにされ、メモリセルの強誘電体材料がPZTである、「アフターパルス」感知を用いる1T-1C FRAMメモリに対してもこの挙動は観察された。しかしながら、フェイルビット分布は、他のタイプの1T-1C FRAMデバイスに対して、この同じ方向に必ずしもシフトするわけではない。例えば、感知增幅器がプレート線でのパルスの間アクティブにされる、読み出し動作における「オン・パルス」又は「ステップ感知」を用いる幾つかの1T-1C FRAM、及び、他の強誘電体材料を用いる、又は上述した例とは異なるように構築される幾つかの1T-1C FRAMは、動作寿命にわたり、基準電圧 $V_{REF}$ の一層高いレベルへのフェイルビット分布のシフトを示し得る。従って、図6b及び図7bを参照して説明するように、通常動作における基準電圧 $V_{REF}$ のレベルを設定するための代替方法がこれらの1T-1C FRAMデバイスに対して適切であり得る。

20

#### 【0052】

この実施形態に従って、基準電圧 $V_{REF}$ を設定する方法は、概して、図6aに関連して上述したものに対応するが、逆のデータ状態、特に、一層高いキャパシタンス分極状態の場合である。従って、FRAM20を含む集積回路は、プロセス50において製造され、所望により、所望の機能的及びパラメータ的電気テストを受ける。プロセス52において、アレイ22におけるFRAMセルの幾つか又は全てが、それらの一層高いキャパシタンス分極状態にプログラムされるか又は書き込まれる。図2aに対して上述したFRAMセル $2_{j,k}$ の例では、この一層高いキャパシタンス分極状態は「1」データ状態である。上述したように、基準電圧 $V_{REF}$ を決定するために用いられるポピュレーションサイズを最大化するために、アレイ22のFRAMセルの全てがプロセス52においてプログラムされることが望ましい。或いは、テスト時間を短縮するために、セルのサブセットのみがプログラムされてもよい。

30

#### 【0053】

プロセス54において、一層高いキャパシタンス（「1」）データ状態を読み出すことに対する最悪のケースが、FRAM20に対して、1つ又は複数の電気的及び環境的条件に対して設定される。上述のように構築されたFRAM20では、「1」データ状態の読み出しに対する最悪のケースは、FRAM20の低温仕様限界（例えば、-30）に対応する温度、及び最小電源仕様電圧（即ち、最小 $V_{dd}$ ）である。前述のように、プロセス54において設定される特定の条件は、FRAM20に対する仕様限界に依存し得、直接的に設定され得るか、又は「ガードバンド」及び仕様限界に対するその他の調整を用いて確立され得るか、又は最悪ケース条件を推定するプロキシ（例えば、温度の影響をエミュレートするための電源電圧レベルの使用）によって設定され得る。一層高いキャパシタンス分極状態の読み出しに対する最悪のケースを設定するその他の電気的又は環境的条件

40

50

もまた、所望とされる場合、プロセス 54 において設定され得る。このプロセス 54 は、テストフローに応じて、プロセス 52 のプログラミングの前か後のいずれかに実施されてもよい。

#### 【0054】

この一層高いキャパシタンス分極状態（「1」状態）に対する1つ又は複数の最悪ケース条件が設定された後、この例ではプログラムされた「1」レベルのリターンを第1の（即ち、最弱）セルがフェイルする基準電圧  $V_{REF}$  の限界を識別するために、自動テスト機器はプロセス 56 において基準電圧  $V_{REF}$  のシュムーを実施する。このシュムーは、この例では、 $V_{REF}$  生成回路 25 によって生成され図 5 の F R A M 20 における感知増幅器 26 に印加される基準電圧  $V_{REF}$  のレベルを変動させながら、「1」状態にプログラムされた F R A M セルのポピュレーションを反復的に読み出すことによって実施される。図 6 a に対して上述したように、基準電圧  $V_{REF}$  を1つの反復から次の反復に漸進的に変化させる方式は、 $V_{REF}$  生成回路 25 の構成及び動作に依存し得る。図 7 b は、プログラムされたセルの各読み出しに対して、全てのセルが「1」データ状態をリターンする低レベルから、正しくないデータ状態を第1のセルがリターンする  $V_{REF}$  レベルまで、基準電圧  $V_{REF}$  を漸進的に増加することによってプロセス 56 のシュムーの効率的な実装を示唆する。最弱セルが、プログラムされた「1」データ状態のリターンをフェイルするこの  $V_{REF}$  レベル（又は、逆に、全ての F R A M セルが正しいデータ状態をリターンする最高  $V_{REF}$  レベル）は、図 1 b において「「1」限界」として示される。或いは、上述したように、プロセス 56 のシュムーは、累積フェイルビット分布（図 7 b の曲線 10<sub>1</sub>）を特徴付けることによって、及び最弱ビットに対する  $V_{REF}$  限界を推定するために外挿することによって、この「1」限界を識別し得る。

10

#### 【0055】

プロセス 56 が、最弱ビットがフェイルする「1」限界を決定すると、プロセス 58 及び 60 において、この実施形態に従って、基準電圧  $V_{REF}$  のプログラムされたレベルが決定される。プロセス 58 において、テスターとシステム実装との間の電圧の変動、デバイスの温度における変動、及び感知増幅器 26 の動作におけるランダム性を許容するよう、F R A M 20 に対して基準電圧  $V_{REF}$  における公差  $V$  が識別される。この公差  $V$  は、F R A M 20 の通常動作における過度のデータ読み出し欠陥の可能性を低減する一方、デバイスの寿命にわたり、分極における予期された劣化に対して良好なマージンを提供する。また、この公差  $V$  は、特徴付け又はその他の方式によって決定され得、類似のタイプ及び製造の全ての F R A M 20 に適用される。典型的な最近の 1 T - 1 C F R A M デバイスに対する公差  $V$  の例はおよそ 15 mV（例えば、「0」限界と「1」限界との間の電圧差の 20 % 以下、例えば 10 %）である。また、この実施形態に従って、基準電圧  $V_{REF}$  のプログラムされたレベルは、「0」限界と「1」限界との間の差に基づくのではなく、感知増幅器性能、温度、及び電圧における変動を考慮して、「1」限界に実行可能な限り近い電圧に置かれる。

20

#### 【0056】

プロセス 60 において、この実施形態に従って、プロセス 58 において識別された公差  $V$  の分を低減された「1」限界の  $V_{REF}$  レベルに対応する基準電圧  $V_{REF}$  のレベルが、システム使用におけるその通常動作に対して F R A M 20 内にプログラムされる。上述したように、プロセス 60 は、「1」限界マイナス公差  $V$  での基準電圧  $V_{REF}$  に対応するコンテンツを用いて構成レジスタ 27 をプログラムすることによる等、構成レジスタ 27 の構成に対して適切な方式で実施され得る。プログラムされた後、この基準電圧  $V_{REF}$  は、F R A M 20 の通常動作においてアクセスされた F R A M セルのデータ状態を認識するための参照として感知増幅器 27 に適用される。所望により、付加的なテスト又は F R A M 20 のその他の処理がその後実施され得る。

30

#### 【0057】

この実施形態において、或る最悪ケース条件下で、時間ゼロにおいて最弱「1」セルがフェイルするレベルか又はそのレベル近くの電圧に基準電圧  $V_{REF}$  を設定することで、

40

50

一層高いキャパシタンス強誘電体状態におけるF R A Mセルに対する読み出しマージンが最大化される。これにより、「オン・パルス」感知を用いるか又はこの時間依存挙動を示す代替材料で構築されるF R A Mデバイス等の、両方のデータ状態の累積フェイルビット分布が基準電圧 $V_{REF}$ の一層高いレベルにシフトする強誘電体デバイスにおいて生じる分極の損失に対して、データ読み出し欠陥という結果になる前に「0」データ状態セルを大きくシフトさせることによって、一層大きな公差が可能となる。上述したように、これらのタイプのデバイスでは、「1」データセルに対する累積フェイルビット分布が、長期にわたり一層高い $V_{REF}$ レベルにシフトする傾向があるため、「1」データ状態に対する読み出しマージンを低減することによって導入されるリスクが小さい。従って、F R A M 2 0の動作寿命性能は、データ保持の観点から、回路設計又は製造プロセスに変更を必要とすることなく、この実施形態に従って有意に改善され得る。

#### 【0058】

これらの実施形態に従って、1 T - 1 Cタイプの強誘電体不揮発性メモリのデータ保持信頼性は、有意に最適化及び改善され得、従って、これらのデバイスのシステム寿命は、相対的に少ないコストで延長される。特に、システム寿命及び信頼性におけるこの改善は、回路設計又は物理的製造プロセスにおいて変更を必要とすることなく、及びメモリ自体の電気的性能に影響を与えることなく取得され得る。これらの実施形態は、メモリ自体のアーキテクチャに応じ、複数の製造段階の任意の1つにおいて実装され得、或いは、システム使用におけるレトロフィット(retrofit)として実装され得る。

#### 【0059】

また、これらの実施形態によって提供される改善されたデータ保持信頼性は、以前は2 T - 2 C F R A Mを必要とした重要な用途における1 T - 1 C F R A Mの使用を可能にし得る。その結果、これらの実施形態は、メモリのピット当たりのコストを大きく低減し得、以前はF R A Mがコスト上法外であった又は制限されていた用途に対する不揮発性メモリの使用を可能にする。

#### 【0060】

本明細書において「0」及び「1」データ状態を参照する場合、説明されるバイアス及び感知スキームに対して、「0」データ状態は一層低いキャパシタンス分極状態に対応し、「1」データ状態は一層高いキャパシタンス分極状態に対応する点で、上述のようなF R A Mの特定の構成を参照して言及される。幾つかの実装において、代わりに、「1」データ状態は、一層低いキャパシタンス分極状態に対応し得、「0」データ状態は、一層高いキャパシタンス状態に対応し得る。そのようなケースでは、データ状態は、上述の例とは逆にされ、本明細書において説明される実施形態をそのような逆のデータ状態に適応することが容易に成され得る。

#### 【0061】

本発明の請求の範囲内で、説明された実施形態において変更が可能であり、また、他の実施形態が可能である。

10

20

30

【図1】

【図2 b】

【図2 a】

FIG. 2a

(従来技術)

【図3】

【図4】

【図5】

【図 6 a】

FIG. 6a

【図6b】

FIG. 6b

【図 7 b】

【図 7 a】

---

フロントページの続き

(72)発明者 カール ゼット ゾウ

アメリカ合衆国 75093 テキサス州 プラノ, クラウンデール ドライブ 5641

(72)発明者 キース エイ レマック

アメリカ合衆国 75082 テキサス州 リチャードソン, エルク スプリングス トレイル

4149

(72)発明者 ジョン エイ ロドリゲス

アメリカ合衆国 75244 テキサス州 ダラス, ハーベスト ヒル ロード 5009

審査官 堀田 和義

(56)参考文献 特開2004-139632 (JP, A)

特開平9-134594 (JP, A)

特開2004-348953 (JP, A)

特開2002-216498 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/22

G11C 7/14

G11C 7/04