(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5538697号

(P5538697)

(45) 発行日 平成26年7月2日(2014.7.2)

(24) 登録日 平成26年5月9日(2014.5.9)

(51) Int.Cl.

G01R 31/26 (2014.01)

F 1

G01R 31/26

H

請求項の数 6 (全 10 頁)

(21) 出願番号 特願2008-231892 (P2008-231892)

(22) 出願日 平成20年9月10日 (2008.9.10)

(65) 公開番号 特開2010-66091 (P2010-66091A)

(43) 公開日 平成22年3月25日 (2010.3.25)

審査請求日 平成23年9月2日 (2011.9.2)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100089071

弁理士 玉村 静世

(72) 発明者 清藤 彰

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 西水 朋洋

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 佐藤 浩治

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体装置のテスト方法

## (57) 【特許請求の範囲】

## 【請求項 1】

- (a) 半導体装置を準備する工程と、

(b) テスト基板の第1主面上に設置されたソケットに前記半導体装置をセットする工程と、

(c) 前記テスト基板の外部から電圧を印加することにより前記半導体装置の電気的試験を行う工程と、を有し、

前記テスト基板の前記第1主面とは反対側の第2主面上には、これと間隔を置いて、板状の金属部材が配置され、

前記半導体装置の外部電極は、前記ソケット内に配置されたコンタクトピンを介して前記テスト基板と電気的に接続され、

前記テスト基板の前記第2主面の前記ソケットに対応する部分と前記金属部材との間に放熱シートが配置され、前記放熱シートは、前記コンタクトピンの下端部と近接するように、前記テスト基板の前記第2主面と前記金属部材とに貼り付けられている半導体装置のテスト方法。

## 【請求項 2】

請求項1に記載の半導体装置のテスト方法において、前記ソケットの前記コンタクトピンは、前記テスト基板に挿入されることにより前記テスト基板と電気的に接続されている。

## 【請求項 3】

10

20

請求項 1 に記載の半導体装置のテスト方法において、前記半導体装置は、BGA型パッケージであって、前記外部電極はバンプ電極である。

【請求項 4】

請求項 1 に記載の半導体装置のテスト方法において、前記半導体チップはSRAMチップである。

【請求項 5】

請求項 1 に記載の半導体装置のテスト方法において、前記(c)工程は、高温環境下において実施する。

【請求項 6】

請求項 1 に記載の半導体装置のテスト方法において、前記放熱シートは、シリコーンゴムで構成されている。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路装置（または半導体装置）の製造方法におけるテスト技術、特にバーンイン処理に適用して有効な技術に関する。

【背景技術】

【0002】

日本特開2003-084030号公報（特許文献1）には、BGA型の半導体集積回路装置に対するバーンイン処理において、バーンイン処理装置に装着されたバーンイン・ボード上の複数のバーンイン・ソケットに挿入された被検査デバイスに上面からヒートシンク・ユニットを押し付けることにより、発熱量の大きい複数のデバイスのバーンイン処理を可能とする技術が開示されている。 20

【0003】

日本特開平11-067396号公報（特許文献2）には、BGA型の半導体集積回路装置に対するバーンイン処理において、バーンイン・ソケットとバーンイン・ボード間にソケット・ピッチ変換基板を挿入することによって、バーンイン・ボードの更なる微細化や多層化をすることなく狭ピッチのデバイスのバーンイン処理を可能とする技術が開示されている。

【0004】

30

【特許文献1】特開2003-084030号公報

【特許文献2】特開平11-067396号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

バーンイン処理においては、以下のような問題が発生することが、本願発明者らによつて、明らかにされた。すなわち、大電流・高発熱の超高速SRAMのバーンイン時に、デバイス温度が上昇して熱暴走し、デバイスが焼損してしまうというものである。これらの超高速SRAM製品は狭ピッチBGAのためバーンイン・ソケットに変換基板を使っているが、この部分で熱伝導が悪いことが、熱暴走の原因である。パッケージの上方に放熱構造体を取り付ける等の方法を検討したが、デバイス上面に傷・汚れが残り、また作業性も悪く、量産に不向きであることが明らかとなった。 40

【0006】

本願発明は、これらの課題を解決するためになされたものである。

【0007】

本発明の目的は、量産に適合した半導体集積回路装置の製造プロセスを提供することにある。

【0008】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。 50

## 【課題を解決するための手段】

## 【0009】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

## 【0010】

すなわち、本願発明はソケット・ピッチ変換基板を用いた半導体集積回路装置の製造工程におけるバーンイン処理において、バーンイン・ボードとバーンイン・ソケット間に熱伝導シートを介在させるものである。

## 【発明の効果】

## 【0011】

10

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

## 【0012】

すなわち、ソケット・ピッチ変換基板を用いた半導体集積回路装置の製造工程におけるバーンイン処理において、バーンイン・ボードとバーンイン・ソケット間に熱伝導シートを介在させることで、大電流・高発熱の超高速S R A Mのバーンイン時に、放熱の悪さから来る熱暴走の発生を防止することができる。

## 【発明を実施するための最良の形態】

## 【0013】

20

## 〔実施の形態の概要〕

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

## 【0014】

1. 以下の工程を含む半導体集積回路装置の製造方法：

- (a) バーンイン・ボードの第1の主面上に設置された多数のバーンイン・ソケットの各々に被テスト・デバイスをセットする工程；

- (b) 前記工程(a)の後、前記被テスト・デバイスがセットされた前記バーンイン・ボードをバーンイン装置内に導入する工程；

- (c) 前記工程(b)の後、前記バーンイン装置内において、バーンイン処理を実行する工程、

ここで、各バーンイン・ソケットと前記バーンイン・ボードの前記第1の主面間にはソケット・ピッチ変換基板が設置されており、このソケット・ピッチ変換基板と前記バーンイン・ボードの前記第1の主面間には放熱シートが設置されている。

## 【0015】

次に、本願において開示される発明のその他の実施の形態について概要を説明する。

## 【0016】

2. 以下の工程を含む半導体集積回路装置の製造方法：

- (a) バーンイン・ボードの第1の主面上に設置された多数のバーンイン・ソケットの各々に被テスト・デバイスをセットする工程；

- (b) 前記工程(a)の後、前記被テスト・デバイスがセットされた前記バーンイン・ボードをバーンイン装置内に導入する工程；

- (c) 前記工程(b)の後、前記バーンイン装置内において、バーンイン処理を実行する工程、

ここで、前記バーンイン・ボードの第2の主面側には裏面保護金属板が設置されており、この裏面保護金属板と各バーンイン・ソケットに対応する前記バーンイン・ボードの前記第2の主面間には放熱シートが設置されている。

## 【0017】

## 〔本願における記載形式・基本的用語・用法の説明〕

1. 本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、单一の例の各部分、一方が他方の一部詳細または一部または全部の

40

50

変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

【0018】

2. 同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といつても、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。たとえば、「シリコン部材」等といつても、純粋なシリコンに限定されるものではなく、SiGe合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。

10

【0019】

3. 同様に、図形、位置、属性等に関して、好適な例示をするが、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、厳密にそれに限定されるものではないことは言うまでもない。

【0020】

4. さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

20

【0021】

5. 「半導体チップ」または単に「チップ」というときは、通常は半導体集積回路装置（半導体装置、電子装置も同じ）をその上に形成する単結晶シリコン・チップを指すが、エピタキシャル基板、S O I 基板、L C D ガラス基板等の絶縁基板と半導体層等の複合基板等も含むことは言うまでもない。なお、本願において、基板としての半導体は、主にシリコン系半導体をさすが、G a A s 系その他の化合物系半導体であってもよい。

20

【0022】

6. 「バーンイン処理」は、半導体集積回路装置の製造工程中に行われる各種の電気的特性試験とともに行われるスクリーニング処理の一種であり、エージング処理とも呼ばれる。一般に、（常温と比較して）高温下において（たとえば摂氏125度程度）、通常よりも高電圧を印加するので、バーンインとよばれる。ここでは、テスト・バーンインを含む。

30

【0023】

7. 上下方向の記載については、図示に対応して記載するが、実際のバーンイン処理は、バーンイン・ボードを任意の配向でセットして実施可能である。

【0024】

〔実施の形態の詳細〕

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

【0025】

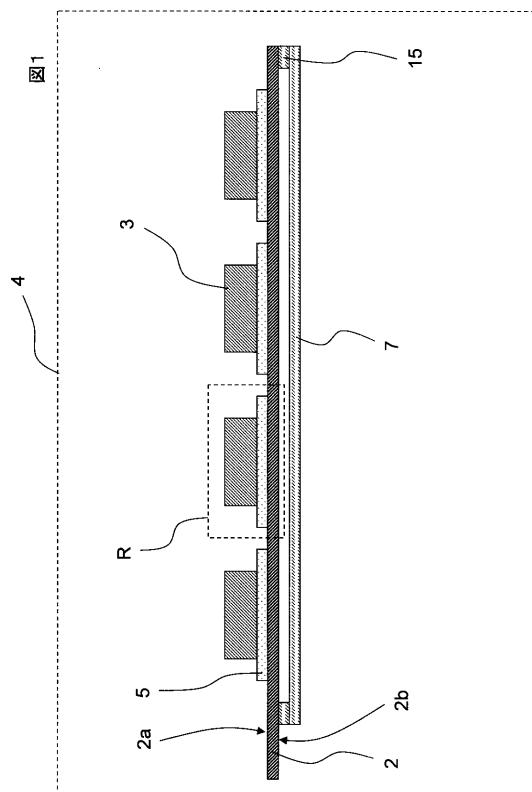

1. 本願の一実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理等の説明（主に図1から3）

40

この例は、シリコン系の半導体基体（チップ）に集積され、B G A型のパッケージ構造とされた0.5ミリ・メートル・ピッチ（ピン数800から900程度）の超高速S R A Mに対するバーンイン処理の例を示す。

【0026】

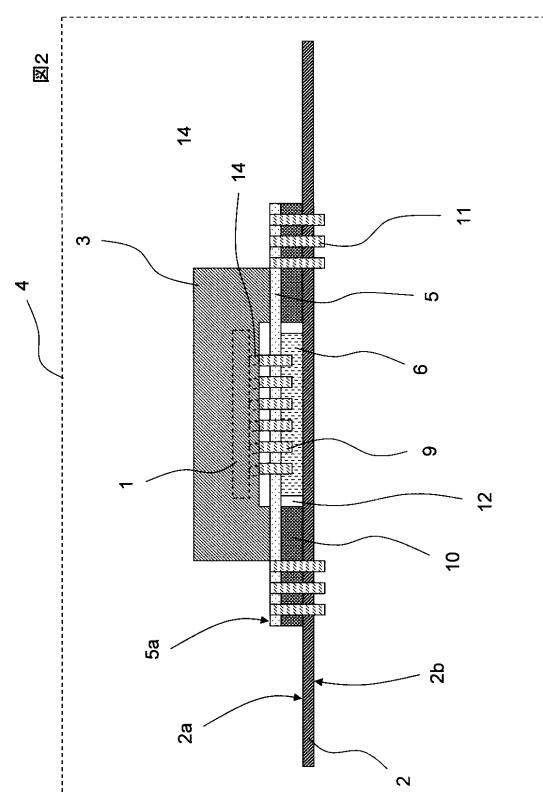

図1は本願の一実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理に使用するバーンイン・ボードの全体断面図である。図2は本願の一実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理に使用するバーンイン・ボードの単位部分（図1のR部分に対応）の図3X-X'断面に対応する要部断面図である。図3は本願の一実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理に使用するバーン

50

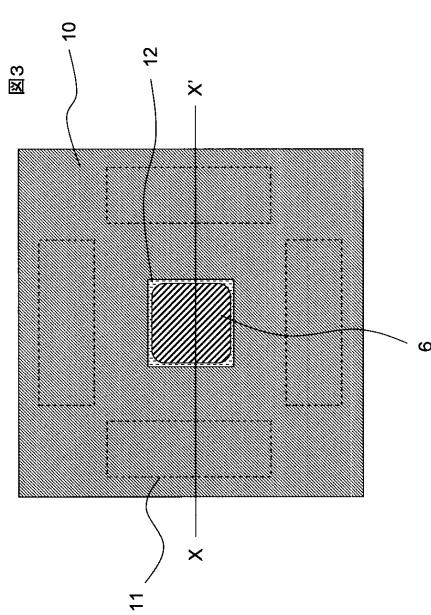

イン・ボード上のソケット・ピッチ変換基板の模式裏面図である。これらに基づいて、本願の一実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理等を説明する。

#### 【0027】

図1に示すように、ガラス・エポキシ配線基板等（一般に多層配線基板）で構成されたバーンイン・ボード本体2の裏面2b（第2の主面）には、補強枠体15を介して裏面保護金属板7が取り付けられている。バーンイン・ボード本体2の表面2a（第1の主面）には、多数のバーンイン・ソケット3（たとえば50から150個）がソケット・ピッチ変換基板5を介して、取り付けられている。各バーンイン・ソケット3内には、被処理デバイス1（たとえばBGA型パッケージ形状を有するデバイス）がセットされている（図2参照）。そして、この状態で、バーンイン・ボード2は、他の複数のバーンイン・ボード2（通常、数枚から数十枚）とともに、バーンイン装置4のバーンイン・チャンバ内のスロットに装着されて、高温下においてバーンイン・ボード2の外部から必要な電圧（信号等を含む）が印加され、バーンイン処理が実行される。

#### 【0028】

次に、図1のR部の詳細を説明する。図2に示すように、バーンイン・ソケット3内には、被処理デバイス1がバンプ面を下にして、セットされている。各バンプ電極14は、ソケット・コンタクト・ピン9と電気的に接続されている（直接又は間接にコンタクト接続されている）。ソケット・コンタクト・ピン9は、バーンイン・ボード本体2と同様なガラス・エポキシ配線基板等で構成されたソケット・ピッチ変換基板5にその上面5a側から挿入されており、その部分でソケット・ピッチ変換基板5と電気的に接続されている。これらのソケット・コンタクト・ピン9は、ソケット・ピッチ変換基板5内の多層配線により、エキスパンドされ対応する変換基板接続端子11と電気的に接続されている。変換基板接続端子11は、変換基板の絶縁枠体10を貫通してバーンイン・ボード2に挿入され、そこでバーンイン・ボード2と電気的に接続されている。絶縁枠体10には、中央リセス部12があり、その部分に放熱シート6が貼り付けられている。ここで、放熱シート6としては、たとえば、信越シリコーン社製の熱伝導シート（シリコーン・ゴム）TC-200TEX等が好適である。寸法は、たとえば、縦・横15ミリ・メートルで厚さは、2ミリ・メートル程度である。

#### 【0029】

図3にソケット・ピッチ変換基板5に裏面、すなわち、絶縁枠体10の下面を示す。図3に示すように、絶縁枠体10の周辺部には変換基板接続端子配列領域11があり、中央部には中央リセス部12がある。そして、この中央リセス部12に放熱シート6が固定されている。

#### 【0030】

このようにソケット・ピッチ変換基板5とバーンイン・ソケット3の間に放熱シート6を介在させることで、図2に示すように、被処理デバイス1、バンプ電極14、放熱シート6、およびバーンイン・ボード本体2からなる直接放熱経路を構成することができ、その結果、ソケット・ピッチ変換基板5を使用したバーンイン・ボード2の放熱を改善することができる。また、微細ピッチ品においても、ソケット・ピッチ変換基板5を使用できるので、高価な高集積多層配線基板を使用する必要がなく、バーンイン・ボードの単価を下げることが可能となり、結果として、バーンイン処理の費用を削減できる。

#### 【0031】

2. 本願の他の実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理等の説明（主に図4及び図5）

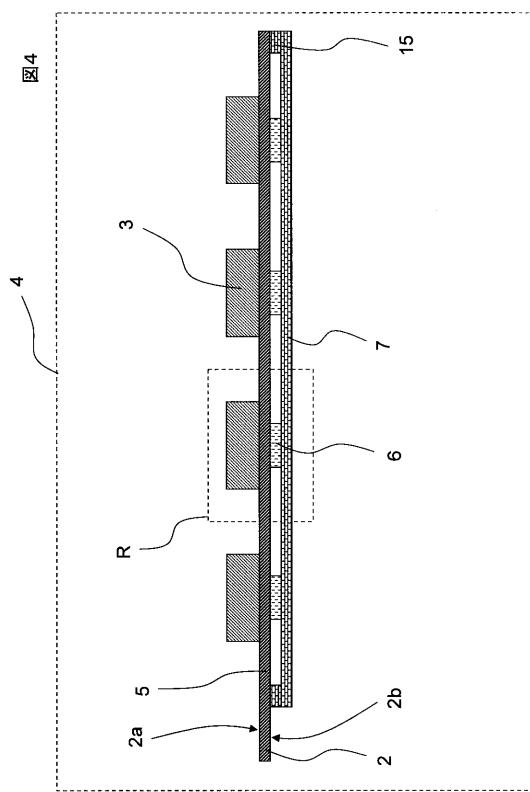

この例は、シリコン系の半導体基体（チップ）に集積され、BGA型のパッケージ構造とされた1.0ミリ・メートル・ピッチ（ピン数200から300程度）の超高速SRAMに対するバーンイン処理の例を示す。

#### 【0032】

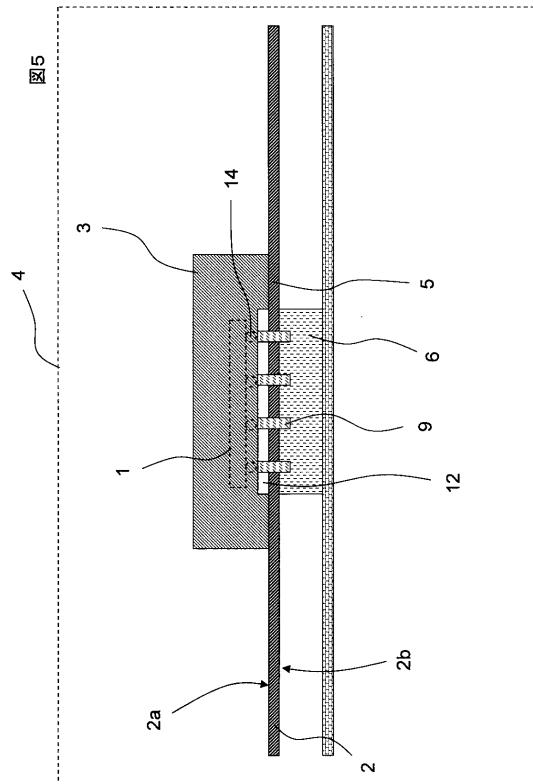

図4は本願の他の実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理

10

20

30

40

50

に使用するバーンイン・ボードの全体断面図である。図5は本願の他の実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理に使用するバーンイン・ボードの要部単位断面図(図4のR部分に対応)である。これらに基づいて、本願の他の実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理等を説明する。

【0033】

図4に示すように、ガラス・エポキシ配線基板等(一般に多層配線基板)で構成されたバーンイン・ボード本体2の裏面2b(第2の主面)には、放熱シート6および補強枠体15を介して裏面保護金属板7が取り付けられている。バーンイン・ボード本体2の表面2a(第1の主面)には、多数のバーンイン・ソケット3(たとえば50から150個)が取り付けられている。各バーンイン・ソケット3内には、被処理デバイス1(たとえばBGA型パッケージ形状を有するデバイス)がセットされている(図5参照)。そして、この状態で、バーンイン・ボード2は、他の複数のバーンイン・ボード2(通常、数枚から数十枚)とともに、バーンイン装置4のバーンイン・チャンバ内のスロットに装着されて、高温下においてバーンイン・ボード2の外部から必要な電圧(信号等を含む)が印加され、バーンイン処理が実行される。

【0034】

次に、図4のR部の詳細を説明する。図5に示すように、バーンイン・ソケット3内には、被処理デバイス1がバンプ面を下にして、セットされている。各バンプ電極14は、ソケット・コンタクト・ピン9と電気的に接続されている(直接又は間接にコンタクト接続されている)。ソケット・コンタクト・ピン9は、バーンイン・ボード2に挿入され、そこでバーンイン・ボード2と電気的に接続されている。

【0035】

前記のように、裏面保護金属板7の上面とバーンイン・ボード2の第2の主面2b(下面)間の各バーンイン・ソケット3に対応する部分には、放熱シート6が貼り付けられている。前記したように、放熱シート6としては、たとえば、信越シリコーン社製の熱伝導シート(シリコーン・ゴム)TC-200TEX等が好適である。寸法は、たとえば、縦・横15ミリ・メートルで厚さは、2ミリ・メートル程度である。

【0036】

このように裏面保護金属板7の上面とバーンイン・ボード2の第2の主面2b(下面)間の各バーンイン・ソケット3に対応する部分に放熱シート6を介在させることで、図5に示すように、被処理デバイス1、バンプ電極14、バーンイン・ボード本体2、放熱シート6、および裏面保護金属板7からなる直接放熱経路を構成することができ、その結果、バーンイン・ボード2の放熱を改善することができる。

【0037】

なお、セクション2の裏面保護金属板7とバーンイン・ボード2間の放熱シート6をセクション1のソケット・ピッチ変換基板5を用いたバーンイン・ボード2に単独で、またはソケット・ピッチ変換基板5とバーンイン・ボード2間の放熱シート6と併せて適用してもよい。

【0038】

3. サマリ

以上本発明者によってなされた発明を実施の形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0039】

例えば、前記実施の形態においては、高速SRAMのバーンイン処理を具体的に説明したが、本願発明はそれに限定されるものではなく、DRAM, フラッシュ・メモリ、その他のメモリ、これらのメモリを有するSOC(System On Chip)型の半導体集積回路装置、マイクロ・コンピュータ用半導体集積回路装置、及びロジック又はデータ処理用半導体集積回路装置等のバーンイン処理等に広く適用できることは言うまでもない。

10

20

30

40

50

## 【図面の簡単な説明】

## 【0040】

【図1】本願の一実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理に使用するバーンイン・ボードの全体断面図である。

【図2】本願の一実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理に使用するバーンイン・ボードの単位部分(図1のR部分に対応)の図3X-X'断面に対応する要部断面図である。

【図3】本願の一実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理に使用するバーンイン・ボード上のソケット・ピッチ変換基板の模式裏面図である。

【図4】本願の他の実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理に使用するバーンイン・ボードの全体断面図である。 10

【図5】本願の他の実施の形態の半導体集積回路装置の製造方法におけるバーンイン処理に使用するバーンイン・ボードの要部単位断面図(図4のR部分に対応)である。

## 【符号の説明】

## 【0041】

- |     |                           |    |

|-----|---------------------------|----|

| 1   | 被処理デバイス                   |    |

| 2   | バーンイン・ボード(または同本体)         |    |

| 2 a | バーンイン・ボードの第1の主面           |    |

| 2 b | バーンイン・ボードの第2の主面           |    |

| 3   | バーンイン・ソケット                | 20 |

| 4   | バーンイン装置                   |    |

| 5   | ソケット・ピッチ変換基板              |    |

| 5 a | ソケット・ピッチ変換基板のデバイス面        |    |

| 6   | 放熱シート(熱伝導絶縁シート)           |    |

| 7   | 裏面保護金属板                   |    |

| 9   | ソケット・コンタクト・ピン             |    |

| 10  | 変換基板の絶縁枠体                 |    |

| 11  | 変換基板接続端子(または変換基板接続端子配列領域) |    |

| 12  | 絶縁枠体の中央リセス部               |    |

| 14  | バンプ電極                     | 30 |

| 15  | 裏面保護金属板の補強枠体              |    |

| R   | 要部単位領域                    |    |

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 高田 繁

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

審査官 菅藤 政明

(56)参考文献 特開平06-317630 (JP, A)

特開平11-102756 (JP, A)

特開2003-084030 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G01R 31/26

H01R 33/76