(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-214479

(P2004-214479A)

(43) 公開日 平成16年7月29日(2004.7.29)

(51) Int.Cl.<sup>7</sup>H01L 29/78

H01L 29/423

H01L 29/49

F 1

H01L 29/78

H01L 29/58301G

G

テーマコード(参考)

4M104

5F140

審査請求 未請求 請求項の数 5 O L (全 13 頁)

(21) 出願番号

(22) 出願日特願2003-911 (P2003-911)

平成15年1月7日 (2003.1.7)

(71) 出願人 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100092152

弁理士 服部 毅麿

(72) 発明者 志渡 秀治

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 岸井 貞浩

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法および半導体装置

## (57) 【要約】

【課題】形成時または形成後のメタルゲート電極からの層間絶縁膜への金属の拡散を防止する。

【解決手段】ポリシリコンをエッチングしてダミーゲートを形成した後(ステップS1)、エッチング後の露出表面を例えば熱酸化して拡散防止膜を形成する。(ステップS2)、その後、そのダミーゲートに接触するように金属からなるメタル層を形成して(ステップS5)、熱処理によって金属とそのダミーゲートとを置換し(ステップS6)、メタルゲート電極を形成する(ステップS7)。これにより、拡散防止膜の形成後に層間絶縁膜が形成されても、ダミーゲートは拡散防止膜によって層間絶縁膜と隔離されるようになる。そのため、形成時あるいは形成後のメタルゲート電極からの層間絶縁膜への金属の拡散は防止され、低抵抗なゲート電極を有する高耐圧の半導体装置が実現される。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

ダミーゲートを形成して前記ダミーゲートの露出する表面に拡散防止膜を形成する工程と、

前記ダミーゲートに接触するように金属からなるメタル層を形成する工程と、

前記メタル層の前記金属と前記ダミーゲートとを置換してメタルゲート電極を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

**【請求項 2】**

前記ダミーゲートを形成して前記ダミーゲートの露出する表面に前記拡散防止膜を形成する工程においては、前記ダミーゲートの露出する表面を酸化することにより前記拡散防止膜を形成することを特徴とする請求項 1 記載の半導体装置の製造方法。 10

**【請求項 3】**

前記ダミーゲートの露出する表面を酸化することにより前記拡散防止膜を形成する際には、形成すべき前記メタルゲート電極の寸法に応じて、形成する前記拡散防止膜の膜厚を変化させることを特徴とする請求項 2 記載の半導体装置の製造方法。

**【請求項 4】**

前記ダミーゲートを形成して前記ダミーゲートの露出する表面に前記拡散防止膜を形成する工程の後に、前記拡散防止膜をマスクの一部にして半導体基板にソース領域およびドレイン領域を形成する工程を有することを特徴とする請求項 1 記載の半導体装置の製造方法 20。

。

**【請求項 5】**

金属からなるメタルゲート電極を有する半導体装置において、

前記メタルゲート電極の表面の一部に、前記メタルゲート電極からの前記金属の拡散を防止するための拡散防止膜を有していることを特徴とする半導体装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は半導体装置の製造方法および半導体装置に関し、特にアルミニウムなどの金属からなるメタルゲート電極を有する半導体装置の製造方法および半導体装置に関する。 30

**【0002】****【従来の技術】**

半導体装置に形成されるゲート電極には、その材料としてポリシリコンが広く用いられており、その形成に用いる露光装置の性能向上、更にその周辺プロセスにおける装置の性能向上などによって微細化が実現されてきた。しかし、このようなゲート電極の微細化が進む一方で、ゲート電極の抵抗の増大が問題となり、そのため、ゲート電極へのシリサイド層の形成や不純物添加などによりゲート電極の低抵抗化が図られている。ところが、近年ではグレインサイズの関係から、微細なゲート電極にシリサイド層を形成することも困難になってきており、また、ゲート電極に不純物を添加した場合には、半導体基板への突き抜けが問題となる場合がある。 40

**【0003】**

これらの問題を回避して低抵抗なゲート電極を実現するため、近年では、ポリシリコンなどをダミーゲートとして形成しておき、これを熱置換反応によってアルミニウム (A1) などの金属で置換したメタルゲート電極が提案されている (例えば特許文献 1 参照)。

**【0004】****【特許文献 1】**

特開 2001-24187 号公報 (段落番号 [0014] ~ [0020] , 図 1)

**【0005】****【発明が解決しようとする課題】**

従来のメタルゲート電極の形成は、ポリシリコンなどからなるダミーゲート上に A1 から 50

なるメタル層を形成した後、数百  $^{\circ}\text{C}$  の温度で熱処理してダミーゲートの全部または一部を Al で置換する方法が一般的である。しかし、このように熱処理を経てダミーゲートを Al で置換する際、更には置換後の製造工程で行われる熱処理の際には、ダミーゲートの周囲に形成されている層間絶縁膜に Al が拡散してしまう場合がある。このような拡散には、メタル層から層間絶縁膜へ Al が拡散するような場合や、形成時あるいは形成後のメタルゲート電極内の Al が層間絶縁膜へ拡散するような場合などが考えられる。このように層間絶縁膜内に Al が拡散してしまうと、半導体装置の耐圧が低下するという問題が生じる。

#### 【 0 0 0 6 】

特に、層間絶縁膜を、  $\text{100K}$  材料を用いた低誘電率絶縁膜とした場合には、メタルゲート電極形成時など、半導体装置の製造に伴う熱処理の過程で層間絶縁膜への金属の拡散が発生し易くなる。これは、  $\text{100K}$  材料が、従来の例えば  $\text{SiO}_2$  などの層間絶縁膜材料に比べて、ポーラスであったり有機膜であったりするためである。

#### 【 0 0 0 7 】

本発明はこのような点に鑑みてなされたものであり、メタルゲート電極の形成に用いる金属の層間絶縁膜への拡散を抑制し、低抵抗なメタルゲート電極を有する高耐圧の半導体装置の製造方法および半導体装置を提供することを目的とする。

#### 【 0 0 0 8 】

##### 【課題を解決するための手段】

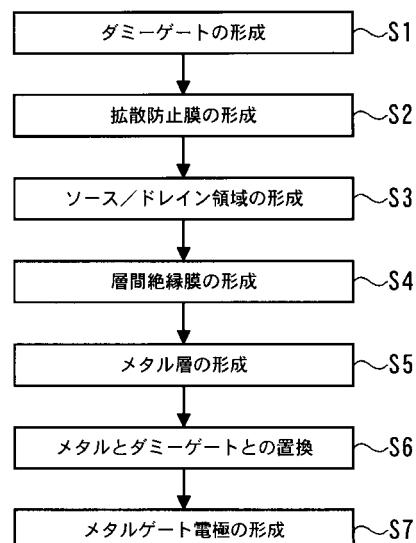

本発明では上記課題を解決するために、図 1 に例示するフローによって実現可能な半導体装置の製造方法が提供される。本発明の半導体装置の製造方法は、ダミーゲートを形成して前記ダミーゲートの露出する表面に拡散防止膜を形成する工程と、前記ダミーゲートに接触するように金属からなるメタル層を形成する工程と、前記メタル層の前記金属と前記ダミーゲートとを置換してメタルゲート電極を形成する工程と、を有することを特徴とする。

#### 【 0 0 0 9 】

このような半導体装置の製造方法によれば、ダミーゲートの形成後(ステップ S 1)、その露出する表面に、例えばダミーゲート表面を酸化することによって拡散防止膜を形成し(ステップ S 2)、ダミーゲートに接触するメタル層を形成して(ステップ S 5)、例えば熱処理によって金属とダミーゲートとを置換することにより(ステップ S 6)、メタルゲート電極が形成される(ステップ S 7)。

#### 【 0 0 1 0 】

ダミーゲート形成後の露出表面に拡散防止膜が形成されるため、その後、例えばその周囲に層間絶縁膜が形成され、ダミーゲートが金属により置換された場合でも、形成時のメタルゲート電極内からのその層間絶縁膜への金属の拡散は防止される。さらに、このように拡散防止膜が形成されることにより、置換後に形成されるメタルゲート電極内の金属は、その後に熱処理を経ても、メタルゲート電極からのその層間絶縁膜への拡散が防止される。このように、拡散防止膜によって、形成時あるいは形成後のメタルゲート電極からの金属の拡散が防止されるので、半導体装置のゲート電極の低抵抗化とともに、その高耐圧化を図れるようになる。

#### 【 0 0 1 1 】

また、本発明では上記課題を解決するために、金属からなるメタルゲート電極を有する半導体装置において、前記メタルゲート電極の表面の一部に、前記メタルゲート電極からの前記金属の拡散を防止するための拡散防止膜を有していることを特徴とする半導体装置が提供される。

#### 【 0 0 1 2 】

このような半導体装置によれば、拡散防止膜が、メタルゲート電極からの金属の拡散を防止し、例えば拡散防止膜の周囲に形成される層間絶縁膜への金属の拡散が防止されるようになる。これにより、低抵抗なゲート電極を有する高耐圧の半導体装置が実現される。

#### 【 0 0 1 3 】

10

20

30

40

50

## 【発明の実施の形態】

まず、本発明の概略について説明する。図1は半導体装置の一製造フローの概略を説明する図である。

### 【0014】

図1に示す半導体装置の製造においては、まず、所定の領域に素子分離層およびゲート絶縁膜が形成されたSi基板などの半導体基板上に、ポリシリコンを所定の膜厚で堆積する。そして、堆積したポリシリコンをエッチングし、形成するメタルゲート電極の寸法に応じた寸法のダミーゲートを形成する(ステップS1)。

### 【0015】

次いで、このダミーゲートを、例えば温度800～1000程度の酸素雰囲気で所定の酸化時間で熱酸化することにより、そのダミーゲートの露出表面に酸化膜を形成して拡散防止膜を形成する(ステップS2)。この拡散防止膜は、後述するように、形成時または形成後のメタルゲート電極から周りの層間絶縁膜へAlなどの金属が拡散してしまうのを防止する目的で形成される。そのため、この拡散防止膜は、金属を層間絶縁膜へ拡散させないような緻密な結晶構造を有していることが好ましく、その点で、拡散防止膜の形成方法として熱酸化法が好適に用いられる。また、熱酸化によって拡散防止膜を形成する場合には、その膜厚を、酸化の温度、時間、雰囲気などの各条件により変化させることができる。

### 【0016】

なお、この拡散防止膜は、ダミーゲート形成後に露出する表面の全面に形成しても、あるいはダミーゲートの上面には他の絶縁膜を形成しておくなどしてその側壁のみ酸化して拡散防止膜を形成するようにしてもよい。

### 【0017】

この拡散防止膜の形成後は、半導体基板に所定の導電型の不純物を導入してソース／ドレイン領域を形成する(ステップS3)。その際、拡散防止膜は、ダミーゲートの側壁部においてサイドウォールとしての役割を果たし、この拡散防止膜をマスクの一部にしてソース／ドレイン領域が自己整合的に形成される。

### 【0018】

そして、このようにダミーゲートの露出表面に拡散防止膜を形成した後に、全面にCVD(Chemical Vapour Deposition)法によってSiO<sub>2</sub>を堆積し、あるいはLOWK材料をスピンドルコーティングなどの方法で形成し、層間絶縁膜を形成する(ステップS4)。

### 【0019】

次いで、この層間絶縁膜を貫通してダミーゲート表面まで達する開口部を形成し、その開口部内を含む層間絶縁膜上に、メタルゲート電極に用いられる金属からなるメタル層を形成する(ステップS5)。これにより、ダミーゲートとメタル層とが接触して形成されるようになり、金属とダミーゲートとが熱によって置換可能な状態となる。なお、メタル層に用いる金属には例えばAlを用いることができ、メタル層はCVD法やスパッタ法を用いて形成される。

### 【0020】

この状態で所定の温度で熱処理を施すことにより、その熱によってメタル層の金属がダミーゲート内へと移動して反応し、金属とダミーゲートとが置換される(ステップS6)。これにより、メタルゲート電極が形成される(ステップS7)。以降は、メタルゲート電極表面が露出するまでCMP(Chemical Mechanical Polishing)により平坦化し、層間絶縁膜形成、コンタクトホール形成、配線形成などの通常の工程を経て半導体装置が形成される。

### 【0021】

このように、ダミーゲートの形成後にその露出表面に拡散防止膜を形成するようになると、その後に層間絶縁膜を形成しても、ダミーゲートとその層間絶縁膜とが拡散防止膜によって隔離されるようになる。これにより、形成時のメタルゲート電極からの層間絶縁膜

10

20

30

40

50

膜への金属の拡散が防止されるようになる。さらに、形成後に熱処理が施された場合でも、メタルゲート電極からの層間絶縁膜への金属の拡散が防止されるようになる。そのため、メタルゲート電極の電気的な耐性が確保され、低抵抗なゲート電極を有する高耐圧の半導体装置が得られる。

【0022】

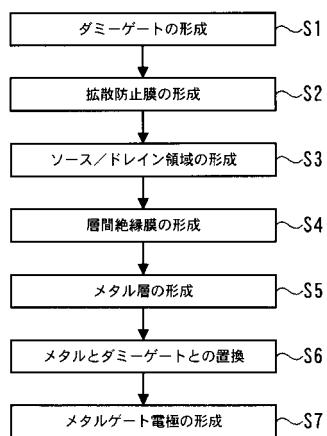

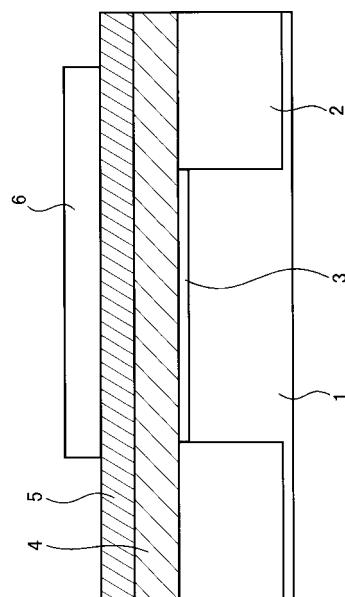

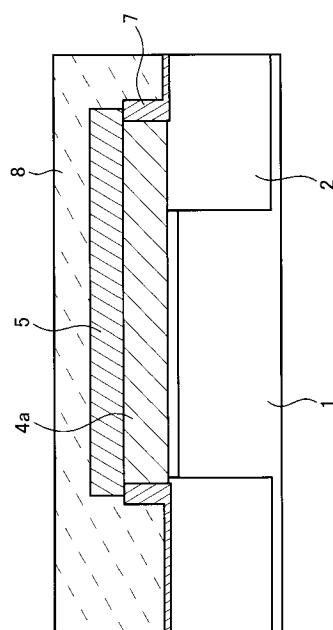

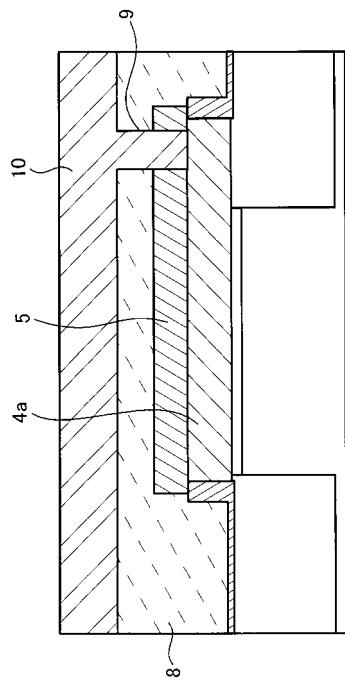

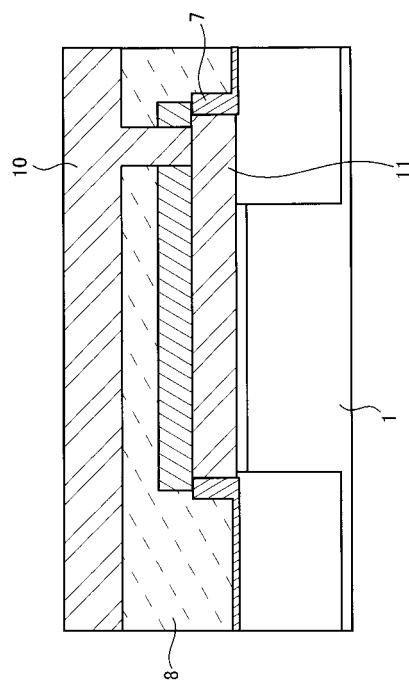

次に、半導体装置の形成方法を図2から図5を参照して具体的に説明する。図2はレジストパターニング工程、図3は層間絶縁膜形成工程、図4はメタル層形成工程、図5はメタルゲート電極形成工程、をそれぞれ示す図である。ただし、図2から図5は、半導体装置に形成されるメタルゲート電極を長手方向で切断したときの断面図にそれぞれ対応させて示している。

10

【0023】

まず、図2に示すように、Si基板1に、トレンチ法によって素子分離層2を形成した後、Si基板1上のメタルゲート電極形成予定領域に、SiO<sub>2</sub>、SiON、Al<sub>2</sub>O<sub>3</sub>などを用いて膜厚約2nmのゲート絶縁膜3を形成する。続いて、全面に膜厚約100nmのポリシリコン層4を形成し、更にこのポリシリコン層4上にSiO<sub>2</sub>またはSiNからなる膜厚約150nmのキャップ層5を形成する。このキャップ層5上に、形成するメタルゲート電極の目的寸法に応じた寸法でレジストパターン6を形成する。

【0024】

次いで、そのレジストパターン6をマスクにしてキャップ層5およびポリシリコン層4をエッチングし、レジストパターン6を除去して、図3に示す拡散防止膜7形成前のダミーゲート4aを形成する。このダミーゲート4aの形成後は、必要に応じてエクステンション領域を形成する。そして、例えば温度800～1000程度の酸素雰囲気で熱酸化を行い、次いで、ポリシリコン層4のエッチング後に表面に露出したダミーゲート4aの側壁に拡散防止膜7を形成する。

20

【0025】

このように拡散防止膜7をダミーゲート4aの側壁酸化によって形成する場合は、その酸化温度が800を大きく下回るような場合には、緻密な拡散防止膜7を形成することが難しくなり、その金属拡散防止効果が小さくなってしまう。また、酸化時間は、形成すべき拡散防止膜7の膜厚および酸化温度に応じて設定される。

30

【0026】

なお、ダミーゲート4aの側壁酸化の際には、通常は、素子分離層2表面や、キャップ層5がSiO<sub>2</sub>からなる場合にはそのキャップ層5表面にも、ダミーゲート4aの側壁に形成される拡散防止膜7よりも薄い膜厚で酸化膜が形成される。しかし、Si基板1表面や、キャップ層5がSiNからなる場合にはそのキャップ層5表面においては、ポリシリコンやSiO<sub>2</sub>との酸化速度の違いから酸化膜はほとんど形成されない。

【0027】

拡散防止膜7の形成後は、これをサイドウォールとし、Si基板1に所定の導電型の不純物を導入してソース/ドレイン領域(図示せず)を形成する。その後、全面にCVD法によってSiO<sub>2</sub>を堆積し、あるいはLOWK材料をスピンドルコーティングなどの方法で形成し、層間絶縁膜8を形成する。LOWK材料としては、ここではフッ素化酸化シリコン(SiOF)、Flare(ハネウェル社の登録商標)、SiLK(ザ・ダウ・ケミカル・カンパニーの登録商標)、水素化シルセスキオキサン(HSQ)、有機スピンドルガラス(有機SOG)をそれぞれ用いている。

40

【0028】

次いで、図4に示すように、その層間絶縁膜8およびキャップ層5の一部をエッチングにより除去してダミーゲート4a表面に達する開口部9を形成する。その後、開口部9内および層間絶縁膜8上に、Alからなるメタル層10をCVD法またはスパッタ法により堆積して形成する。

【0029】

その状態で例えば温度450～500程度の熱処理を施すことにより、ダミーゲート

50

4 a がメタル層 1 0 の A 1 によって置換され、図 5 に示すようにメタルゲート電極 1 1 が形成される。その後は、メタルゲート電極 1 1 表面が露出するまで C M P により平坦化し、層間絶縁膜形成、コンタクトホール形成、配線形成などの通常の工程を経て半導体装置が形成される。

【 0 0 3 0 】

このように、ダミーゲート 4 a の側壁に拡散防止膜 7 を形成することにより、形成時あるいは形成後のメタルゲート電極 1 1 からの A 1 の拡散を防止することができる。特に、拡散防止膜 7 を熱酸化によって形成することで、高い A 1 拡散防止効果が得られる。

【 0 0 3 1 】

なお、層間絶縁膜 8 とメタル層 1 0 との境界領域に拡散した A 1 は、C M P による平坦化の際に除去することが可能である。また、たとえ層間絶縁膜 8 内の S i 基板 1 表面に近い領域にまで A 1 が拡散した場合でも、層間絶縁膜 8 とメタルゲート電極 1 1 とが拡散防止膜 7 で隔離されているため、電気的寄与は抑制される。

【 0 0 3 2 】

ここで、A 1 の拡散挙動について、上記のようにダミーゲート 4 a の側壁に拡散防止膜 7 を形成する場合と、形成しない場合とを比較する。

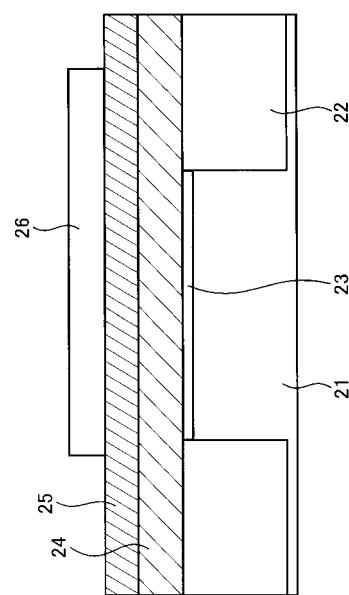

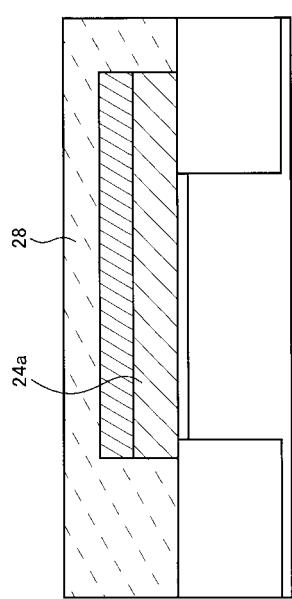

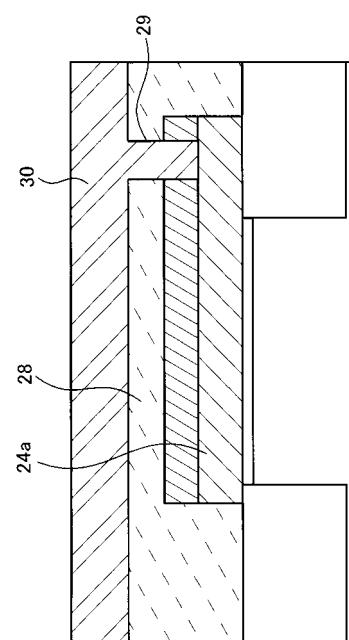

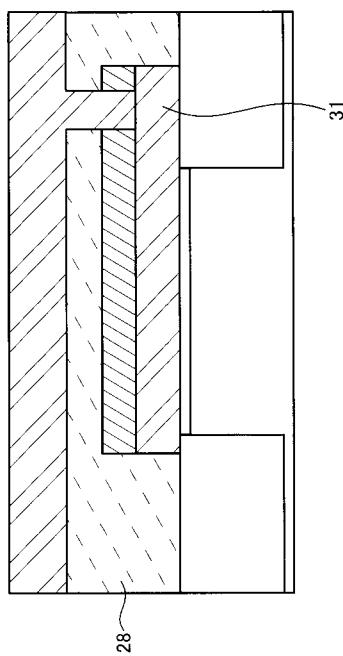

なお、ここで比較に用いる試料（以下「比較試料」という。）は、以下の図 6 から図 9 に示す手順で形成される。図 6 は比較試料のレジストパターニング工程、図 7 は比較試料の層間絶縁膜形成工程、図 8 は比較試料のメタル層形成工程、図 9 は比較試料のメタルゲート電極形成工程、をそれぞれ示す図である。ただし、図 6 から図 9 は、比較試料に形成されるメタルゲート電極を長手方向で切断したときの断面図にそれぞれ対応させて示している。

【 0 0 3 3 】

比較試料の形成は、まず、図 6 に示すように、S i 基板 2 1 に素子分離層 2 2 およびゲート絶縁膜 2 3 を形成した後、全面にポリシリコン層 2 4 、その上にキャップ層 2 5 を形成し、所定の寸法でレジストパターン 2 6 を形成する。次いで、レジストパターン 2 6 をマスクにしてエッチングを行い、図 7 に示すダミーゲート 2 4 a を形成する。そして、必要に応じエクステンション領域を形成し、通常の方法でソース / ドレイン領域を形成した後（図示せず）、全面に層間絶縁膜 2 8 を形成する。その後は、図 8 に示すように、ダミーゲート 2 4 a 表面に達する開口部 2 9 を形成して開口部 2 9 内および層間絶縁膜 2 8 上にメタル層 3 0 を形成し、所定温度の熱処理を施して、図 9 に示すように、メタルゲート電極 3 1 を形成する。その後は、C M P による平坦化、層間絶縁膜形成、コンタクトホール形成、配線形成などの通常の工程を経て、比較試料が形成される。

【 0 0 3 4 】

ただし、ここに示した各工程における層（膜）の材質、形成条件、熱処理条件は、上記の拡散防止膜 7 を有する半導体装置を形成する場合の対応する各工程における層（膜）の材質、形成条件、熱処理条件と同じである。

【 0 0 3 5 】

図 2 から図 5 に示した方法で形成した半導体装置と、図 6 から図 9 に示した方法で形成した比較試料とについて、それらの A 1 の拡散は、層間絶縁膜 8, 2 8 として S i O<sub>2</sub> または各 L o w K 材料を用いた場合のそれぞれについて、T E M ( T r a n s m i s s i o n E l e c t r o n M i c r o s c o p e ) を用いた E D X ( E n e r g y D i p e r s i v e X - r a y S p e c t r o s c o p y ) 分析により比較している。

【 0 0 3 6 】

例えば層間絶縁膜 8 に S i O<sub>2</sub> を用いてダミーゲート 4 a の側壁に拡散防止膜 7 を形成した半導体装置の場合には、E D X 分析の結果より、半導体装置形成後の層間絶縁膜 8 に相当する領域に A 1 の存在は認められなかった。これにより、形成時あるいは形成後のメタルゲート電極 1 1 からの層間絶縁膜 8 への A 1 の拡散は、拡散防止膜 7 によって防止されていることが確認された。

【 0 0 3 7 】

10

20

30

40

50

これに対し、層間絶縁膜28にSiO<sub>2</sub>を用いてダミーゲート24aに拡散防止膜を形成しなかった比較試料の場合には、比較試料形成後の層間絶縁膜28に相当する領域にA1の存在が認められた。特に、ソース／ドレイン領域上部に相当する層間絶縁膜28の領域にもA1の存在が認められ、形成時あるいは形成後のメタルゲート電極31からの層間絶縁膜28へのA1の拡散が確認された。

【0038】

層間絶縁膜8, 28を、各100K材料を用いて形成した場合にもそれぞれ上記同様のEDX分析結果が得られ、層間絶縁膜8の材質に依らず、拡散防止膜7によるメタルゲート電極11からのA1の拡散防止効果が確認された。

【0039】

また、上記図2から図5に示したように、ダミーゲート4aの上面にキャップ層5を形成しておき、ダミーゲート4aの側壁を酸化して拡散防止膜7を形成する場合には、メタルゲート電極11を微細化して形成することができるようになる。これは、ダミーゲート4aの側壁が酸化されるときには、その内部にも酸化が進行して拡散防止膜7が形成され、A1で置換されるダミーゲート4aの寸法が、ポリシリコン層4のエッチング直後の寸法、すなわちレジストパターン寸法よりも小さくなるためである。

【0040】

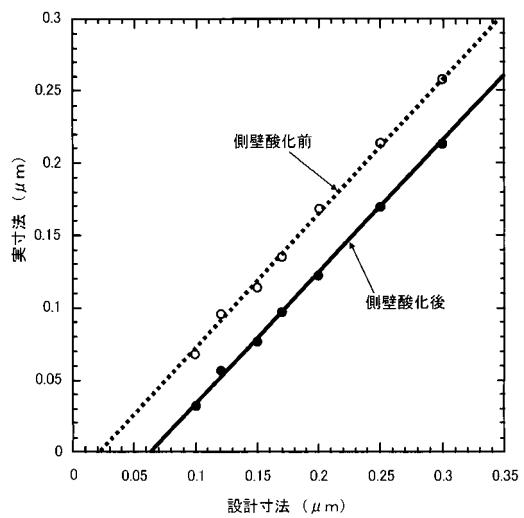

図10はダミーゲートの設計寸法と側壁酸化前後のダミーゲートの実寸法との関係を示す図である。図10では、横軸は設計寸法(μm)、縦軸は実寸法(μm)を表しており、また、点線はダミーゲートの設計寸法と側壁酸化前のダミーゲートの実寸法との関係を表し、実線はダミーゲートの設計寸法と側壁酸化後のダミーゲートの実寸法との関係を表している。この図10には、ダミーゲートの側壁酸化を温度900のドライ酸素雰囲気で75分間の条件で行い、その側壁酸化前後のダミーゲートの寸法を測長した結果をプロットしている。

【0041】

図10より、側壁酸化後のダミーゲートの実寸法は、拡散防止膜が形成されることにより、側壁酸化前のダミーゲートの実寸法よりも約40nm小さくなっている。そして、このように微細化されたダミーゲートがA1と置換され、メタルゲート電極が形成されるようになる。このように、レジストパターン寸法でエッチングしたダミーゲートを、側壁酸化によってその寸法を更に微細化してからA1で置換することができるため、微細なメタルゲート電極を形成することができる。

【0042】

なお、この図10において示した側壁酸化の酸化条件は単なる例であって、その他の酸化条件を設定した場合であっても、同様に微細化したメタルゲート電極を形成することが可能である。そして、その酸化条件によって拡散防止膜の膜厚、すなわち形成するメタルゲート電極の寸法を変化させ、調整することができる。なお、酸化条件は、酸化温度については、上述のように温度800～1000程度とすることが好ましく、また、酸化時間については、酸化温度、形成する拡散防止膜の膜厚、目的とするメタルゲート電極の寸法などに応じて設定する。

【0043】

ただし、酸化条件によっては、拡散防止膜としてダミーゲートの側壁に厚い膜厚の酸化膜が形成されたり、Si基板表面に酸化膜が形成されたりする。そして、その酸化膜が、SiO<sub>2</sub>などの酸化物で形成されているゲート絶縁膜にまで達してしまうと、目的のデバイス特性が得られなくなる、あるいは半導体装置を正常に動作させることができなくなる、といった問題が生じる可能性がある。したがって、酸化条件を設定する際には、形成する半導体装置の構造や形成する拡散防止膜の膜厚などの条件を考慮するようとする。または、ゲート絶縁膜を、その材料にSiNやSiONなどの窒化物を用いるなど、酸化の影響を受けないあるいは受け難い材料にして、半導体装置を形成するようにしてよい。

【0044】

以上述べたように、ダミーゲートの形成後にその露出表面に拡散防止膜を形成することに

10

20

30

40

50

より、形成時あるいは形成後のメタルゲート電極からのA1の拡散を防止することができる。これにより、微細かつ低抵抗なメタルゲート電極を形成することができるとともに、層間絶縁膜へのA1の拡散による半導体装置の耐圧低下を抑えることができる。

#### 【0045】

なお、上記のようにポリシリコン層上にキャップ層を形成してエッチングした後にダミーゲートの側壁を酸化して拡散防止膜を形成するほか、キャップ層を形成せずにポリシリコン層をエッチングしてダミーゲートの露出表面を酸化することも可能である。この場合、ダミーゲートの側壁のほか、上面にも拡散防止膜が形成されるようになる。このようにして拡散防止膜を形成した場合には、メタルゲート電極からのA1の拡散防止に加え、さらに、メタルゲート電極の、Si基板表面に対して水平方向の微細化とともに垂直方向の微細化も可能になる。

#### 【0046】

また、上記の説明では、ダミーゲートを酸化することによって拡散防止膜を形成するようにしたが、A1の拡散防止を目的とする限りは、ダミーゲートの表面に緻密な酸化膜や窒化膜を形成することにより、拡散防止膜を形成することも可能である。

#### 【0047】

また、以上の説明では、A1を用いてメタルゲート電極を形成した場合を例にして述べたが、本発明は、白金(Pt)などの他の金属を用いた場合も同様に適用することが可能である。また、ダミーゲートとしては、ポリシリコンのほか、アモルファスシリコン、シリコンゲルマニウム(SiGe)も同様に用いることが可能である。

#### 【0048】

(付記1) ダミーゲートを形成して前記ダミーゲートの露出する表面に拡散防止膜を形成する工程と、

前記ダミーゲートに接触するように金属からなるメタル層を形成する工程と、前記メタル層の前記金属と前記ダミーゲートとを置換してメタルゲート電極を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

#### 【0049】

(付記2) 前記ダミーゲートを形成して前記ダミーゲートの露出する表面に前記拡散防止膜を形成する工程においては、前記ダミーゲートの露出する表面を酸化することにより前記拡散防止膜を形成することを特徴とする付記1記載の半導体装置の製造方法。

#### 【0050】

(付記3) 前記ダミーゲートの露出する表面を酸化することにより前記拡散防止膜を形成する際には、形成すべき前記メタルゲート電極の寸法に応じて、形成する前記拡散防止膜の膜厚を変化させることを特徴とする付記2記載の半導体装置の製造方法。

#### 【0051】

(付記4) 前記メタルゲート電極の寸法が前記ダミーゲートの寸法より小さくなるように前記拡散防止膜を形成することを特徴とする付記2または3に記載の半導体装置の製造方法。

#### 【0052】

(付記5) 前記ダミーゲートを形成して前記ダミーゲートの露出する表面に前記拡散防止膜を形成する工程の後に、層間絶縁膜を形成する工程を有し、

前記層間絶縁膜上に、前記ダミーゲートに接触するように前記メタル層を形成し、前記メタル層の前記金属と前記ダミーゲートとを置換して前記メタルゲート電極を形成することを特徴とする付記1記載の半導体装置の製造方法。

#### 【0053】

(付記6) 前記ダミーゲートを形成して前記ダミーゲートの露出する表面に前記拡散防止膜を形成する工程の後に、前記拡散防止膜をマスクの一部にして半導体基板にソース領域およびドレイン領域を形成する工程を有することを特徴とする付記1記載の半導体装置の製造方法。

#### 【0054】

10

20

30

40

50

(付記7) 金属からなるメタルゲート電極を有する半導体装置において、前記メタルゲート電極の表面の一部に、前記メタルゲート電極からの前記金属の拡散を防止するための拡散防止膜を有していることを特徴とする半導体装置。

【0055】

(付記8) 前記拡散防止膜によって前記メタルゲート電極と層間絶縁膜とが隔離されていることを特徴とする付記7記載の半導体装置。

【0056】

【発明の効果】

以上説明したように本発明では、ダミーゲートの形成後にその露出表面に拡散防止膜を形成し、そのダミーゲートに接触するようにメタル層を形成し、金属とそのダミーゲートとを置換してメタルゲート電極を形成するようにした。これにより、形成時あるいは形成後のメタルゲート電極からの層間絶縁膜への金属の拡散を防止することができるようになるので、低抵抗なメタルゲート電極を有する高耐圧の半導体装置を実現することができる。

10

【図面の簡単な説明】

【図1】半導体装置の一製造フローの概略を説明する図である。

【図2】レジストパターニング工程を示す図である。

【図3】層間絶縁膜形成工程を示す図である。

【図4】メタル層形成工程を示す図である。

【図5】メタルゲート電極形成工程を示す図である。

20

【図6】比較試料のレジストパターニング工程を示す図である。

【図7】比較試料の層間絶縁膜形成工程を示す図である。

【図8】比較試料のメタル層形成工程を示す図である。

【図9】比較試料のメタルゲート電極形成工程を示す図である。

【図10】ダミーゲートの設計寸法と側壁酸化前後のダミーゲートの実寸法との関係を示す図である。

【符号の説明】

1, 2 1 Si 基板

2, 2 2 素子分離層

3, 2 3 ゲート絶縁膜

4, 2 4 ポリシリコン層

30

4 a, 2 4 a ダミーゲート

5, 2 5 キャップ層

6, 2 6 レジストパターン

7 拡散防止膜

8, 2 8 層間絶縁膜

9, 2 9 開口部

10, 3 0 メタル層

11, 3 1 メタルゲート電極

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

F ターム(参考) 4M104 AA01 BB01 BB02 BB06 BB36 CC05 DD02 DD04 DD06 DD16

DD26 DD37 DD43 DD71 DD78 DD83 DD86 DD89 EE05 EE14

EE17 GG09 GG10 GG14 HH05 HH14 HH16 HH20

5F140 AA00 AA01 BA01 BD07 BD09 BD11 BE13 BF01 BF05 BG03

BG04 BG08 BG12 BG26 BG33 BG36 BG37 BG49 BG50 BH14

BK02 CB04 CC02 CC04 CC10 CC12 CC16 CE07