US010304623B2

## (12) United States Patent

### Song et al.

#### (54) INTEGRATED DEVICE PACKAGE COMPRISING A TUNABLE INDUCTOR

(71) Applicant: **QUALCOMM Incorporated**, San

Diego, CA (US)

(72) Inventors: Young Kyu Song, San Diego, CA (US);

John Jong Hoon Lee, San Diego, CA (US); Sangjo Choi, San Diego, CA

(US)

(73) Assignee: QUALCOMM Incorporated, San

Diego, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 15/002,174

(22) Filed: Jan. 20, 2016

(65) Prior Publication Data

US 2017/0207022 A1 Jul. 20, 2017

(51) Int. Cl.

G06F 1/16 (2006.01)

H01F 29/02 (2006.01)

G05B 19/10 (2006.01)

H01F 27/29 (2006.01)

H01F 27/42 (2006.01)

H05K 7/14 (2006.01)

(52) U.S. Cl.

(Continued)

(Continued)

### (10) Patent No.: US 10,304,623 B2

(45) **Date of Patent:**

May 28, 2019

#### (58) Field of Classification Search

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

6,573,822 B2 6/2003 Ma et al. 7,012,323 B2 3/2006 Warner et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

EP 2662870 A1 11/2013 JP 2013110351 A 6/2013

#### OTHER PUBLICATIONS

International Search Report and Written Opinion—PCT/US2017/013997—ISA/EPO—dated Apr. 3, 2017.

Primary Examiner — William H. Mayo, III Assistant Examiner — Hiram E Gonzalez (74) Attorney, Agent, or Firm — Loza & Loza, LLP/Qualcomm

#### (57) ABSTRACT

Some features pertain to a package substrate that includes at least one dielectric layer, an inductor in the at least one dielectric layer, a first terminal coupled to the inductor, a second terminal coupled to the inductor, and a third terminal coupled to the inductor. The first terminal is configured to be a first port for the inductor. The second terminal is configured to be a second port for the inductor. The third terminal is a dummy terminal. In some implementations, the package substrate includes a solder resist layer over the dielectric layer, where the solder resist layer covers the third terminal. In some implementations, the package substrate includes a solder interconnect over the third terminal, such that the solder resist layer is between the third terminal and the solder interconnect. In some implementations, the package substrate is coupled to a die comprising a plurality of switches.

#### 20 Claims, 19 Drawing Sheets

# US 10,304,623 B2 Page 2

| (51) | Int. Cl.<br>H01L 23/498 (2006.01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          | 7,336,147      | B2*   | 2/2008  | Watanabe H01F 17/0006<br>257/531           |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------|-------|---------|--------------------------------------------|

|      | <b>H01L 23/64</b> (2006.01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          | 7,365,628      | B2    | 4/2008  | Sato et al.                                |

|      | H01L 23/31 (2006.01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          | 7,460,001      | B2    | 12/2008 | Jessie                                     |

| (52) | U.S. Cl.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          | 7,531,407      | B2    | 5/2009  | Clevenger et al.                           |

| ()   | CPC <i>H01L 2224/16227</i> (2013.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 01); <i>H01L</i>         | 7,598,838      | B2 *  | 10/2009 | Hargrove H01F 17/0013                      |

|      | 2224/16265 (2013.01); H01L 22<br>(2013.01); H01L 2224/73204 (2013.01); H01L 22 | 01); <i>H01L</i>         | 7,868,409      | B2*   | 1/2011  | 333/174<br>Sasaki H01L 23/49822<br>257/491 |

|      | 2224/92125 (2013.01); H01L 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          | 8,441,334      | B2    | 5/2013  | Kawano                                     |

|      | (2013.01); H01L 2924/19011 (2013.01); H01L 2924/19042 (2013.01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          | 9,806,694      | B2    | 10/2017 | Reedy et al.                               |

|      | 2924/19042                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (2013.01)                | 2011/0260819   | A1    | 10/2011 | Yeh et al.                                 |

| (56) | References Cited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          | 2012/0038025   | A1    | 2/2012  | Teggatz et al.                             |

| ` ′  | U.S. PATENT DOCUMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          | 2013/0242499   | A1*   | 9/2013  | Kang G06K 19/07732<br>361/679.32           |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          | 2014/0246753   | A1    | 9/2014  | Song et al.                                |

|      | 7,064,645 B2* 6/2006 Kobayashi H0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1F 17/0006               | 2014/0333391   |       |         | 2                                          |

|      | 7,202,768 B1 * 4/2007 Harvey I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57/E23.114<br>H01F 21/08 | 2017/0207293   | A1    | 7/2017  | Song et al.                                |

|      | 7,202,700 B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 333/174                  | * cited by exa | miner | •       |                                            |

(PRIOR ART) FIG. 1

PLAN VIEW

FIG. 2

FIG. 3

FIG. 4

FIRST CONFIGURATION

FIG. 5

FIG. 6

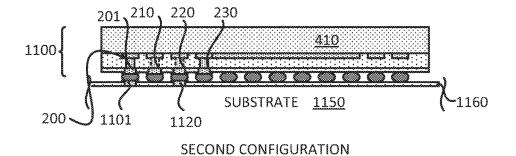

SECOND CONFIGURATION

FIG. 7

FIG. 8

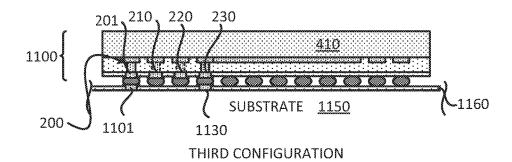

THIRD CONFIGURATION

FIG. 9

FIG. 10

FIRST CONFIGURATION

FIG. 11

FIG. 12

FIG. 13

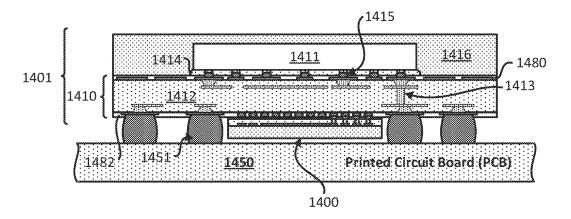

FIG. 14

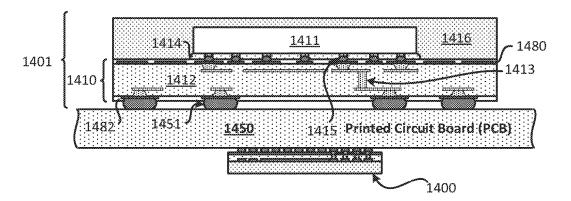

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22

FIG. 24

FIG. 25A

FIG. 25B

FIG. 26

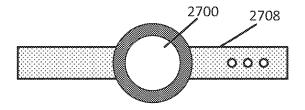

FIG. 27

#### INTEGRATED DEVICE PACKAGE COMPRISING A TUNABLE INDUCTOR

#### BACKGROUND

Field

Various features relate generally to an integrated device package, and more specifically to an integrated device package that includes a tunable inductor implemented in a package substrate.

Background

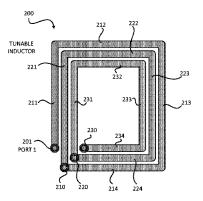

FIG. 1 illustrates a configuration of an integrated device package that includes a die. Specifically, FIG. 1 illustrates an integrated device package 100 that includes a first die 102 and a package substrate 106. The package substrate 106 15 includes a dielectric layer and a plurality of interconnects 110. The package substrate 106 is a laminated substrate. The plurality of interconnects 110 includes traces, pads and/or vias. The first die 102 is coupled to the package substrate **106** through a first plurality of solder balls **112**. The package 20 substrate 106 is coupled to a printed circuit board (PCB) 108 through a second plurality of solder balls 116. FIG. 1 illustrates that an inductor 120 is mounted on the PCB 108. The inductor 120 is located externally of the integrated device package 100, and takes up a lot real estate on the PCB 25 108. The inductor is a surface mounted inductor 120 is mounted on the PCB 108.

A drawback of the inductor 120 is that the property of the inductor 120 is fixed and cannot be tuned and/or configured to meet changing operational conditions of the first die 102. 30 That is, for example, the inductor 120 has a fixed inductance value, which cannot be changed during the operation of the first die 102.

Another drawback of the inductor 120 shown in FIG. 1 is that it creates a device with a form factor that may be too 35 large for the needs of mobile computing devices and/or wearable computing devices. This may result in a device that is either too large and/or too thick. That is, the combination of the integrated device package 100, the inductor 120 and the PCB 108 shown in FIG. 1 may be too thick and/or have 40 a surface area that is too large to meet the needs of mobile computing devices and/or wearable computing devices.

Therefore, there is a need for an integrated device package with a tunable inductor. Ideally, such an integrated device package will include a compact form factor, while at the 45 same time meeting the needs of mobile devices, Internet of Things (IoT) devices, computing devices and/or wearable computing devices.

#### **SUMMARY**

Various features relate generally to an integrated device package, and more specifically to an integrated device package that includes a tunable inductor implemented in a package substrate.

For example, a package substrate includes at least one dielectric layer, an inductor in the at least one dielectric layer, a first terminal coupled to the inductor, a second terminal coupled to the inductor, and a third terminal coupled to the inductor. The first terminal is configured to be 60 device (IPD) that includes a tunable inductor. a first port for the inductor. The second terminal is configured to be a second port for the inductor. The third terminal is a dummy terminal.

For example, a package substrate includes at least one dielectric layer, a means for inductance in the at least one 65 dielectric layer, a first terminal coupled to the means for inductance, a second terminal coupled to the means for

2

inductance, and a third terminal coupled to the means for inductance. The first terminal is configured to be a first port for the means for inductance. The second terminal is configured to be a second port for the means for inductance. The third terminal is a dummy terminal.

In another example, a method for tuning an inductor includes specifying a first inductance for an inductor coupled to a first terminal, a second terminal, and a third terminal, where the first terminal is configured to be a first port for the inductor. The method closes a first switch coupled to the second terminal such that the second terminal is configured to be a second port for the inductor. The method opens a second switch coupled to the third terminal such that the third terminal is configured as a first dummy terminal for the inductor. The method of closing the first switch and opening the second switch configures the inductor to comprise the first inductance when a current traverses through the inductor between the first port and the second

In another example, a processor readable storage medium that includes code for specifying a first inductance for an inductor coupled to a first terminal, a second terminal, and a third terminal, where the first terminal is configured to be a first port for the inductor. The processor readable storage medium further includes code for closing a first switch coupled to the second terminal such that the second terminal is configured to be a second port for the inductor. The processor readable storage medium also includes code for opening a second switch coupled to the third terminal such that the third terminal is configured as a first dummy terminal for the inductor. The processor readable storage medium that includes code for closing the first switch and opening the second switch configures the inductor to comprise the first inductance when a current traverses through the inductor between the first port and the second port.

#### **DRAWINGS**

Various features, nature and advantages may become apparent from the detailed description set forth below when taken in conjunction with the drawings in which like reference characters identify correspondingly throughout.

FIG. 1 illustrates a profile view of an integrated device package and an inductor mounted on a printed circuit board (PCB).

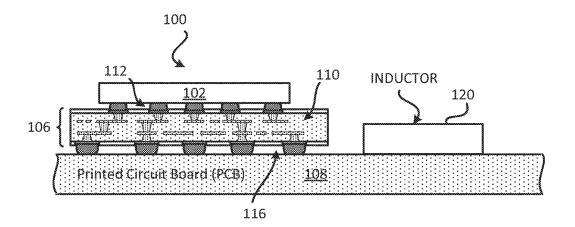

FIG. 2 illustrates a plan view of a tunable inductor.

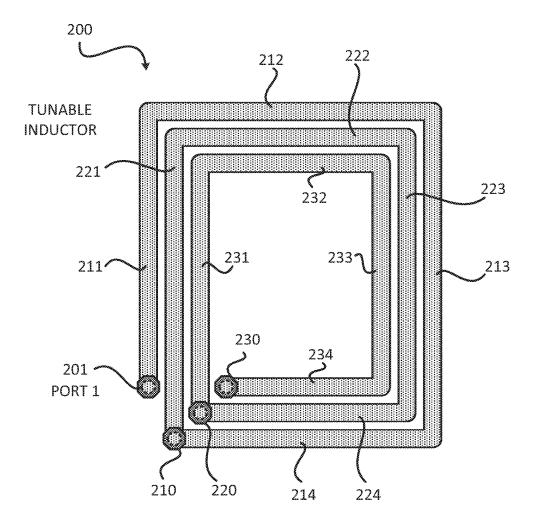

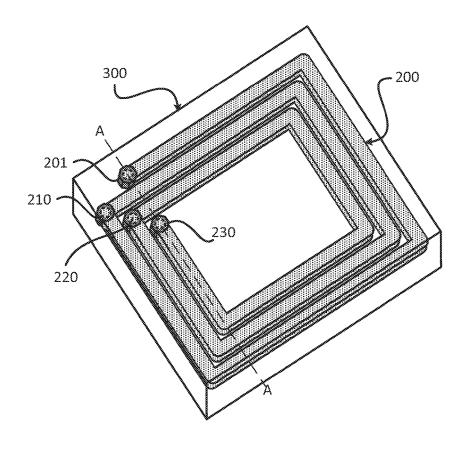

FIG. 3 illustrates a view of an integrated passive device 50 (IPD) that includes a tunable inductor.

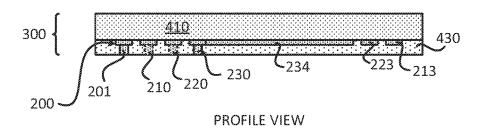

FIG. 4 illustrates a profile view of an integrated passive device (IPD) that includes a tunable inductor.

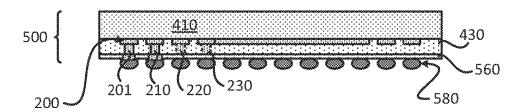

FIG. 5 illustrates a profile view of an integrated passive device (IPD) that includes a tunable inductor.

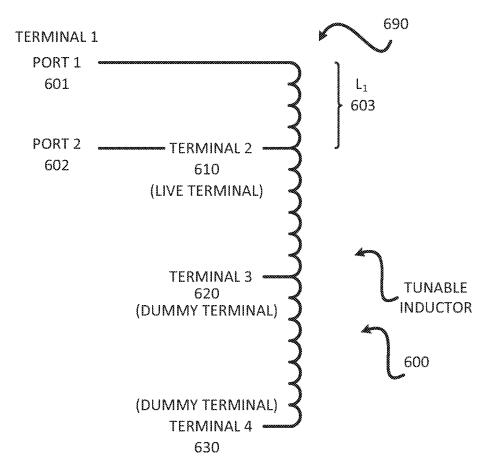

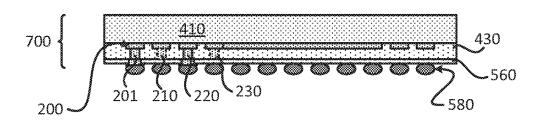

FIG. 6 illustrates a circuit diagram of a tunable inductor. FIG. 7 illustrates a profile view of an integrated passive device (IPD) that includes a tunable inductor.

FIG. 8 illustrates a circuit diagram of a tunable inductor. FIG. 9 illustrates a profile view of an integrated passive

FIG. 10 illustrates a circuit diagram of a tunable inductor. FIG. 11 illustrates a profile view of an integrated passive device (IPD) that includes a tunable inductor, coupled to a

substrate. FIG. 12 illustrates a profile view of an integrated passive device (IPD) that includes a tunable inductor, coupled to a substrate.

FIG. 13 illustrates a profile view of an integrated passive device (IPD) that includes a tunable inductor, coupled to a substrate

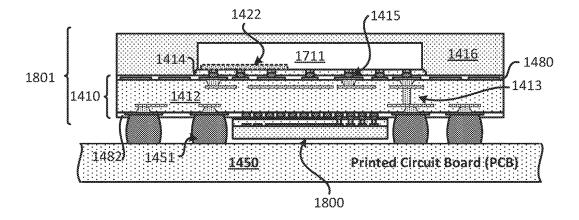

FIG. **14** illustrates a profile view of an integrated passive device (IPD) that includes a tunable inductor, coupled to a package.

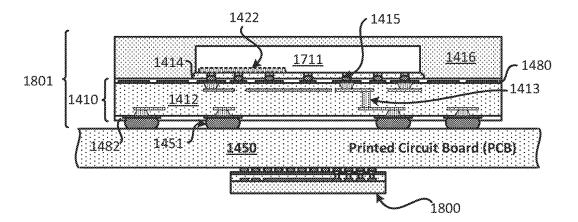

FIG. 15 illustrates a profile view of an integrated passive device (IPD) that includes a tunable inductor, coupled to a printed circuit board (PCB).

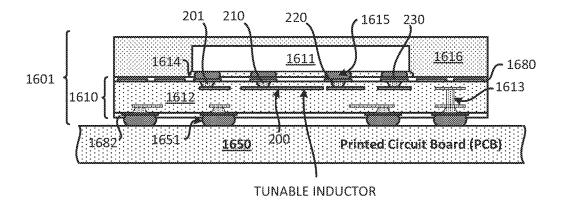

FIG. 16 illustrates a profile view of a tunable inductor in 10 a package substrate.

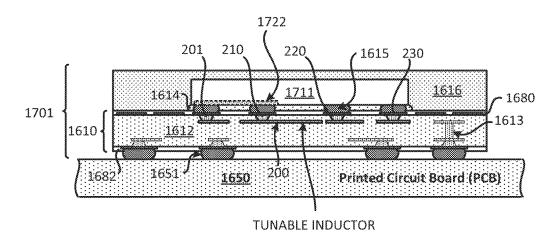

FIG. 17 illustrates a profile view of a real time tunable inductor in a package substrate.

FIG. 18 illustrates a profile view of an integrated passive device (IPD) that includes a real time tunable inductor, 15 coupled to a package.

FIG. 19 illustrates a profile view of an integrated passive device (IPD) that includes a real time tunable inductor, coupled to a printed circuit board (PCB).

FIG. **20** illustrates a circuit diagram of a real time tunable 20 inductor with all the switches open.

FIG. 21 illustrates various means implemented in a package substrate and a die to form a real time tunable inductor.

FIG. 22 illustrates a flow diagram of an exemplary method for providing real time tuning of inductor imple- 25 mented in a package substrate.

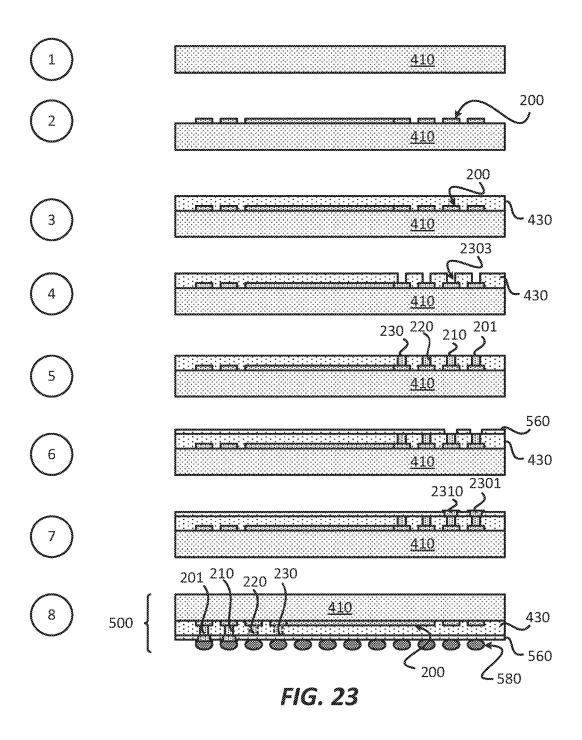

FIG. 23 illustrates a sequence for fabricating an integrated passive device (IPD) that includes a tunable inductor.

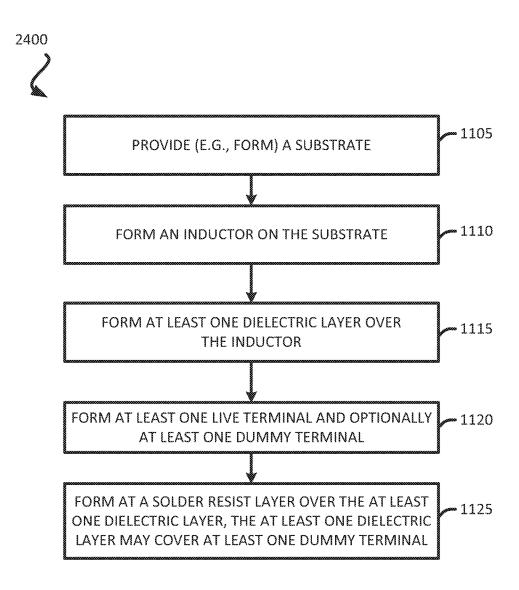

FIG. **24** illustrates a flow diagram of an exemplary method for fabricating an integrated passive device (IPD) <sup>30</sup> that includes a tunable inductor.

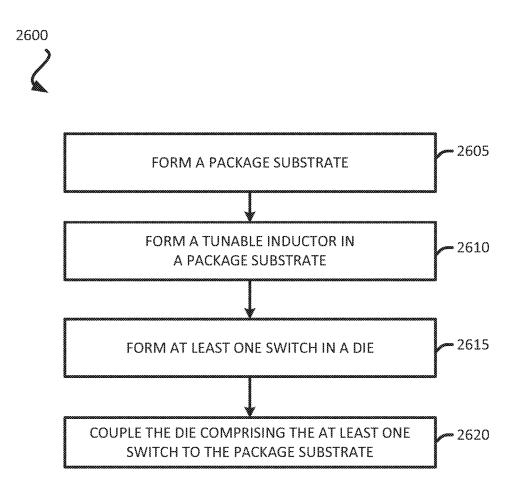

FIG. 25 (which includes FIGS. 25A-25B) illustrates a flow diagram of an exemplary method for fabricating an integrated device package that includes a real time tunable inductor implemented in a package substrate.

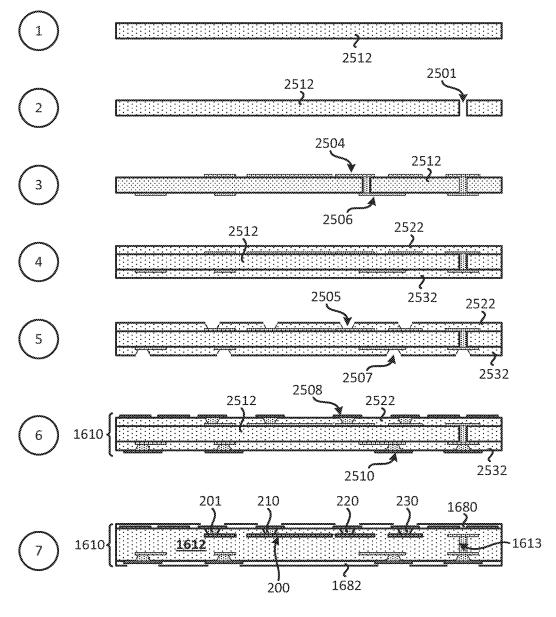

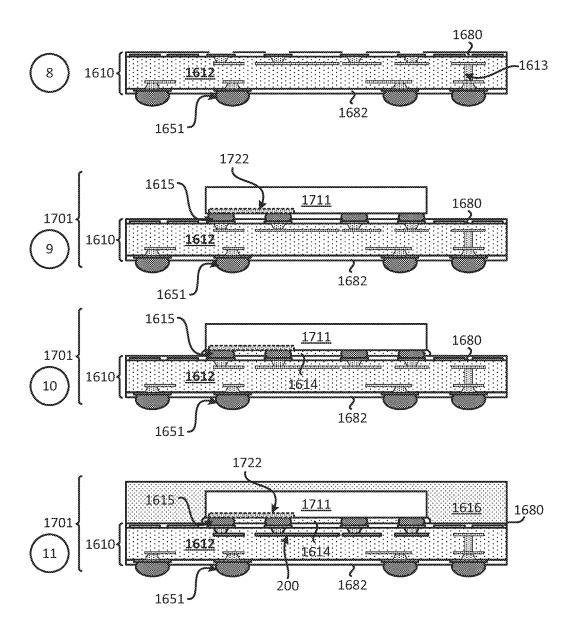

FIG. 26 illustrates an example of a sequence for fabricating an integrated device package that includes a real time tunable inductor implemented in a package substrate.

FIG. 27 illustrates various electronic devices that may include the various integrated devices, integrated device <sup>40</sup> packages, semiconductor devices, dies, integrated circuits, and/or packages described herein.

#### DETAILED DESCRIPTION

In the following description, specific details are given to provide a thorough understanding of the various aspects of the disclosure. However, it will be understood by one of ordinary skill in the art that the aspects may be practiced without these specific details. For example, circuits may be 50 shown in block diagrams in order to avoid obscuring the aspects in unnecessary detail. In other instances, well-known circuits, structures and techniques may not be shown in detail in order not to obscure the aspects of the disclosure.

Some features pertain to a package substrate that includes at least one dielectric layer, an inductor in the at least one dielectric layer, a first terminal coupled to the inductor, a second terminal coupled to the inductor, and a third terminal coupled to the inductor. The first terminal is configured to be a first port for the inductor. The second terminal is configured to be a second port for the inductor. The third terminal is a dummy terminal. In some implementations, the package substrate includes a solder resist layer over the dielectric layer, where the solder resist layer covers the third terminal. In some implementations, the package substrate includes a 65 solder interconnect over the third terminal, such that the solder resist layer is between the third terminal and the

4

solder interconnect. In some implementations, the package substrate is coupled to a die comprising a plurality of switches

In some implementations, an interconnect is an element or component of a device or package that allows or facilitates an electrical connection between two points, elements and/or components. In some implementations, an interconnect may include a trace, a via, a pad, a pillar, a redistribution metal layer, and/or an under bump metallization (UBM) layer. In some implementations, an interconnect is an electrically conductive material that may be configured to provide an electrical path for a signal (e.g., data signal, ground signal, power signal). An interconnect may be part of a circuit. An interconnect may include more than one element or component.

Exemplary Tunable Inductor

FIG. 2 illustrates an example of a tunable inductor 200. In some implementations, the tunable inductor 200 is implemented as an integrated passive device (IPD). Examples of a tunable inductor implemented as an integrated passive device (IPD) are further described in at least FIGS. 4-5, 7, 9, 11-15 and 18-19. In some implementations, the tunable inductor 200 is at least partially implemented in a package substrate. Examples of a tunable inductor at least partially implemented in a package substrate are further described in at least FIGS. 16-17. The tunable inductor may be a tunable inductive means or means for tunable inductance.

In some implementations, the tunable inductor 200 is configurable (e.g., tunable) to have different inductance, through the use of dummy interconnects and/or dummy terminals. The use of dummy interconnects and/or dummy terminals with a tunable inductor, is further described below in at least FIGS. 4-17.

In some implementations, the tunable inductor 200 is configurable to have different inductances, through the use of one or more switches. The use of switches with a tunable inductor, is further described below in at least FIGS. 18-23.

As shown in FIG. 2, the tunable inductor 200 includes one or more interconnects (e.g., interconnect 211, interconnect 212, interconnect 213, interconnect 221, interconnect 222, interconnect 223, interconnect 224, interconnect 231, interconnect 233, interconnect 234). In some implementations, one interconnect may collectively be defined by one or more of the interconnect 211, the interconnect 212, the interconnect 213, the interconnect 214, the interconnect 222, the interconnect 223, the interconnect 223, the interconnect 231, and the interconnect 232, the interconnect 233, and the interconnect 234. An interconnect (e.g., interconnect 211) may include a trace and/or pad.

The tunable inductor 200 includes a first terminal 201, a second terminal 210, a third terminal 220, and a fourth terminal 230. The first terminal 201 may include at least one interconnect (e.g., trace, pad, via). The first terminal 201 may be a first port for the tunable inductor 200.

The second terminal 210 may include at least one interconnect (e.g., trace, pad, via). The third terminal 220 may include at least one interconnect (e.g., trace, pad, via). The fourth terminal 230 may include at least one interconnect (e.g., trace, pad, via). In some implementations, the tunable inductor 200 may be configured (e.g., tuned) to have different inductances, by selecting the second terminal 210, the third terminal 220, or the fourth terminal 230, as the second port for the tunable inductor 200.

As will be further described below in FIGS. 5-10, the tunable inductor 200 that includes the first terminal 201 (e.g., first port) and the second terminal 210 (e.g., second

port), may be a one turn inductor with a first inductance  $(L_1)$ . The tunable inductor 200 that includes the first terminal 201 (e.g., first port) and the third terminal 220 (e.g., second port), may be a two turn inductor with a second inductance  $(L_2)$ . The tunable inductor 200 that includes the first terminal 201 (e.g., first port) and the fourth terminal 230 (e.g., second port), may be a three turn inductor with a third inductance  $(L_3)$ .

Different implementations may use different terminals as the ports for the tunable inductor 200. For example, in some implementations, the second terminal 210 and the third terminal 220 may respectfully correspond to the first port and the second port for the tunable inductor 200.

In some implementations, terminals that are used as ports are live terminals and terminals that are not used as ports are dummy terminals. In some implementations, a dummy terminal may include one or more interconnects that is an end point for an electrical path, where a signal cannot traverse through the dummy terminal.

As shown in FIG. 2, the tunable inductor 200 is a spiral inductor that includes three turns. However, in different implementations, the tunable inductor 200 may include a different number of turns (e.g., 1, 2, 4).

Exemplary Integrated Passive Device (IPD) Comprising 25 Tunable Inductor

As mentioned above, in some implementations, the tunable inductor 200 is implemented as an integrated passive device (IPD). FIGS. 3 and 4 illustrate an example of an integrated passive device (IPD) 300 that include the tunable inductor 200. The tunable inductor may be a tunable inductive means or means for tunable inductance.

FIG. 4 illustrates a profile view of the integrated passive device (IPD) 300 across the cross-section AA of FIG. 3. The integrated passive device (IPD) 300 includes a substrate 35 410, a dielectric layer 430, the tunable inductor 200, the first terminal 201, the second terminal 210, the third terminal 220, and the fourth terminal 230. The tunable inductor 200 includes at least the interconnects 213, 223, and the 234. The tunable inductor 200 is formed over the substrate 410. The 40 substrate 410 may include a substrate (e.g., silicon substrate, glass substrate, ceramic substrate). The dielectric layer 430 is formed over the substrate 410 and the tunable inductor 200.

As shown in FIG. 4, the first terminal 201 includes at least 45 one interconnect (e.g., trace, pad, via) formed in the dielectric layer 430; the second terminal 210 includes at least one interconnect (e.g., trace, pad, via) formed in the dielectric layer 430; the third terminal 220 includes at least one interconnect (e.g., trace, pad, via) formed in the dielectric layer 430; and the fourth terminal 230 includes at least one interconnect (e.g., trace, pad, via) formed in the dielectric layer 430.

As will be further described below in FIGS. **5-10**, the tunable inductor **200** may be configured (e.g., tuned) to have 55 different inductances by using two terminals as ports, and leaving two terminals as dummy terminals. In some implementations, the two dummy terminals may be covered by a solder resist layer, which prevents an electrical connection with the dummy terminals of the tunable inductor **200**.

FIG. 5 illustrates an example of a first configuration of the integrated passive device (IPD) 500. The integrated passive device (IPD) 500 includes the substrate 410, the dielectric layer 430, the tunable inductor 200, the first terminal 201, the second terminal 210, the third terminal 220, the fourth 65 terminal 240, the solder resist layer 560, and a plurality of solder interconnects 580 (e.g., solder balls).

6

As shown in FIG. 5, the first terminal 201 and the second terminal 210 are live terminals (e.g., first port, second port), and the third terminal 220 and the fourth terminal 230 are dummy terminals. The first terminal 201 includes interconnects (e.g., pad, trace, via) that are coupled to a first solder interconnect from the plurality of solder interconnects 580. The second terminal 210 includes interconnects (e.g., pad, trace, via) that are coupled to a second solder interconnect from the plurality of solder interconnects 580.

The dummy terminals (e.g., third terminal 220, fourth terminal 230) are covered by the solder resist layer 560. The dummy terminals are not coupled (e.g., electrically coupled) to solder interconnects from the plurality of solder interconnects 580. Thus, there is a solder interconnect underneath the dummy terminals, but no electrical coupling or direct coupling between the solder interconnect and the dummy terminals

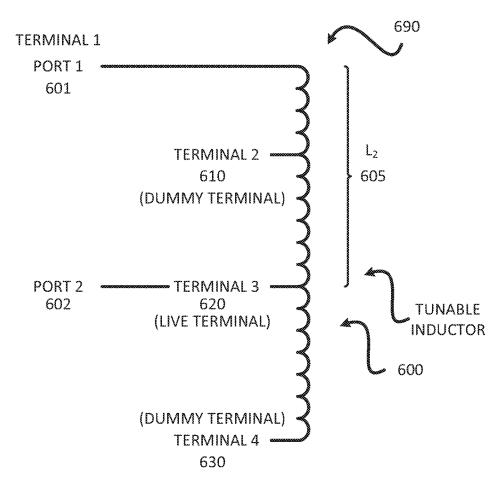

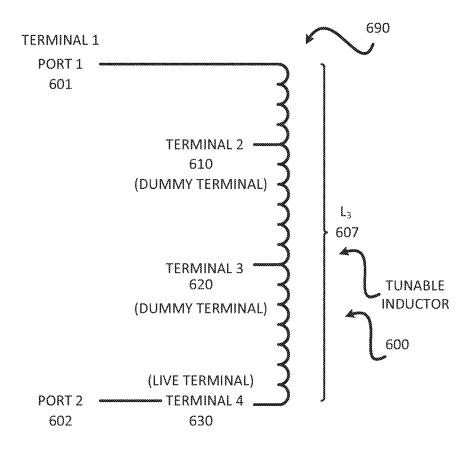

FIG. 6 illustrates a circuit diagram 690 of the inductor 600. The inductor 600 of FIG. 6 may correspond to the integrated passive device (IPD) 500 that includes the tunable inductor 200 of FIG. 5. The inductor 600 includes a first terminal 601, a second terminal 610, a third terminal 620, a fourth terminal 630. The first terminal 601 may correspond to the first terminal 201 of FIG. 5, the second terminal 610 may correspond to the second terminal 210 of FIG. 5, the third terminal 620 may correspond to the third terminal 220 of FIG. 5, and the fourth terminal 630 may correspond to the fourth terminal of FIG. 5.

As shown in FIG. 6, when the inductor 600 includes the first terminal 601 as the first port, and the second terminal 610 as the second port, the inductor 600 has a first inductance (L<sub>1</sub>) 603. The first terminal 601 and the second terminal 610 are live terminals, and the third terminal 620 and the fourth terminal 630 are dummy terminals.

FIG. 7 illustrates an example of a second configuration of the integrated passive device (IPD) 700. FIG. 7 is similar to FIG. 5, except that different terminals are live. As shown in FIG. 7, the first terminal 201 and the third terminal 220 are live terminals (e.g., first port, second port), and the second terminal 210 and the fourth terminal 230 are dummy terminals. The first terminal 201 includes interconnects (e.g., pad, trace, via) that are coupled to a first solder interconnect from the plurality of solder interconnects (e.g., pad, trace, via) that are coupled to a second solder interconnect from the plurality of solder interconnect from the plurality of solder interconnect from the plurality of solder interconnects 580.

The dummy terminals (e.g., second terminal 210, fourth terminal 230) are covered by the solder resist layer 560. The dummy terminals are not coupled (e.g., electrically coupled) to solder interconnects from the plurality of solder interconnects 580. Thus, there is a solder interconnect underneath the dummy terminals, but no electrical coupling or direct coupling between the solder interconnect and the dummy terminals.

FIG. 8 illustrates the circuit diagram 690 of the inductor 600. The inductor 600 of FIG. 8 may correspond to the integrated passive device (IPD) 700 that includes the tunable inductor 200 of FIG. 7. As shown in FIG. 8, when the inductor 600 includes the first terminal 601 as the first port, and the third terminal 620 as the second port, the inductor 600 has a second inductance ( $L_2$ ) 605. The first terminal 601 and the third terminal 620 are live terminals, and the second terminal 610 and the fourth terminal 630 are dummy terminals.

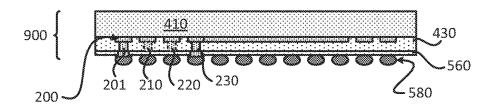

FIG. 9 illustrates an example of a second configuration of the integrated passive device (IPD) 900. FIG. 9 is similar to FIG. 5, except that different terminals are live. As shown in

FIG. 9, the first terminal 201 and the fourth terminal 230 are live terminals (e.g., first port, second port), and the second terminal 210 and the third terminal 220 are dummy terminals. The first terminal 201 includes interconnects (e.g., pad, trace, via) that are coupled to a first solder interconnect from 5 the plurality of solder interconnects 580. The fourth terminal 230 includes interconnects (e.g., pad, trace, via) that are coupled to a second solder interconnect from the plurality of solder interconnects 580.

The dummy terminals (e.g., second terminal 210, third 10 terminal 220) are covered by the solder resist layer 560. The dummy terminals are not coupled (e.g., electrically coupled) to solder interconnects from the plurality of solder interconnects 580. Thus, there is a solder interconnect underneath the dummy terminals, but no electrical coupling or direct coupling between the solder interconnect and the dummy terminals.

FIG. 10 illustrates the circuit diagram 690 of the inductor 600. The inductor 600 of FIG. 10 may correspond to the integrated passive device (IPD) 900 that includes the tunable 20 inductor 200 of FIG. 9. As shown in FIG. 10, when the inductor 600 includes the first terminal 601 as the first port, and the fourth terminal 630 as the second port, the inductor 600 has a third inductance ( $L_3$ ) 607. The first terminal 601 and the fourth terminal 630 are live terminals, and the 25 second terminal 610 and the third terminal 620 are dummy terminals.

Thus, FIGS. **5-10** illustrate that by covering different terminals of an inductor with a solder resist layer, the inductor can be configured to have different inductances. <sup>30</sup> The integrated passive devices (IPDs) of the present disclosure may be coupled to a substrate (e.g., package substrate, laminated substrate) and/or a printed circuit board (PCB).

FIGS. 11-13 illustrate how an integrated passive device (IPD) that includes an inductor may be coupled to a package 35 substrate, a laminate substrate and/or a printed circuit board (PCB).

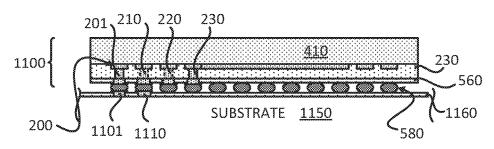

FIG. 11 illustrates a first configuration of an integrated passive device (IPD) 1100 that is coupled to a substrate 1150. The substrate 1100 includes a dielectric layer, a solder 40 resist layer 1160, a first interconnect 1101, and a second interconnect 1110. The substrate 1150 may be a package substrate, a laminated substrate or a printed circuit board (PCB).

The integrated passive device (IPD) 1100 includes the 45 substrate 410, the dielectric layer 430, the tunable inductor 200, the first terminal 201, the second terminal 210, the third terminal 220, the fourth terminal 240, the solder resist layer 560, and a plurality of solder interconnects 580 (e.g., solder balls). In some implementations, the first terminal 201, the 50 second terminal 210, the third terminal 220, the fourth terminal 240 are coupled to a solder interconnect from the plurality of solder interconnects 580.

The integrated passive device (IPD) 1100 is coupled to the substrate 1150 such that the first terminal 201 is coupled to 55 the first interconnect 1101, and the second terminal 210 is coupled to the second interconnect 1110. Thus, the first terminal 201 and the second terminal 210 are live terminals. The third terminal 220 and the fourth terminal 230 are dummy terminals, as they are coupled to the solder resist 60 layer 1160 of the substrate 1150.

FIG. 12 illustrates a second configuration of the integrated passive device (IPD) 1100 that is coupled to a substrate 1150. As shown in FIG. 12, the integrated passive device (IPD) 1100 is coupled to the substrate 1150 such that the first 65 terminal 201 is coupled to the first interconnect 1101, and the third terminal 220 is coupled to a third interconnect

8

1120. Thus, the first terminal 201 and the third terminal 220 are live terminals. The second terminal 210 and the fourth terminal 230 are dummy terminals, as they are coupled to the solder resist layer 1160 of the substrate 1150.

FIG. 13 illustrates a third configuration of the integrated passive device (IPD) 1100 that is coupled to a substrate 1150. As shown in FIG. 13, the integrated passive device (IPD) 1100 is coupled to the substrate 1150 such that the first terminal 201 is coupled to the first interconnect 1101, and the fourth terminal 230 is coupled to a fourth interconnect 1130. Thus, the first terminal 201 and the fourth terminal 230 are live terminals. The second terminal 210 and the third terminal 220 are dummy terminals, as they are coupled to the solder resist layer 1160 of the substrate 1150.

FIGS. **14** and **15** illustrate examples of where an integrated passive device (IPD) that includes a tunable inductor may be positioned. The tunable inductor may be a tunable inductive means or means for tunable inductance.

FIG. 14 illustrates an integrated device package 1401 that includes a package substrate 1410, a die 1411 and an integrated passive device (IPD) 1400 that includes a tunable inductor. The integrated passive device (IPD) 1400 may be any of the integrated passive device (IPD) that includes a tunable inductor, described in the present disclosure. The integrated device package 1401 is coupled to a printed circuit board (PCB) 1450 through a plurality of solder balls 1451.

As shown in FIG. 14, the integrated device package 1401 includes the package substrate 1410, the die 1411, an underfill 1414, a plurality of solder balls 1415, and an encapsulation layer 1416.

The package substrate 1410 includes at least one dielectric layer 1412. The at least one dielectric layer 1412 may include a core layer and/or a prepeg layer. The package substrate 1410 also include a plurality of interconnects 1413. The package substrate 1410 may also include a first solder resist layer 1480 and a second solder resist layer 1482. The first solder resist layer 1480 is formed on a first surface of the package substrate 1410, and the second solder resist layer 1482 is formed on a second surface of the package substrate 1410.

The integrated passive device (IPD) 1400 is coupled to the package substrate 1410. The die 1411 is coupled to the package substrate 1410 through the plurality of solder balls 1415. FIG. 14 illustrates that the integrated passive device (IPD) 1400 is coupled to the package substrate 1410 such that the integrated passive device (IPD) 1400 is face to face with the die 1411. That is, the front side of the integrated passive device (IPD) 1400 is facing the front side of the die 1411. In some implementations, a front side is a side that includes solder interconnects and/or solder balls. It is noted that the integrated passive device (IPD) 1400 may be located differently. The die 1411 is configured to be electrically coupled to the tunable inductor (e.g., tunable inductor 200) of the integrated passive device (IPD) 1400.

The encapsulation layer 1416 is coupled to the package substrate 1410 and the die 1411. The encapsulation layer 1416 at least partially encapsulates the die 1411.

FIG. 15 illustrates another example of where an integrated passive device (IPD) may be positioned. FIG. 15 is similar to FIG. 14, except that the integrated passive device (IPD) 1400 is coupled to the printed circuit board (PCB) 1450. FIG. 15 illustrates that the integrated passive device (IPD) 1400 is coupled to the printed circuit board (PCB) 1450 such that the integrated passive device (IPD) 1400 is face to face

with the die 1411. That is, the front side of the integrated passive device (IPD) 1400 is facing the front side of the die 1411.

Exemplary Integrated Device Package Comprising Tunable Inductor Implemented in Package Substrate

As mentioned above, the tunable inductor 200 may be implemented in a package substrate of an integrated device package. FIG. 16 illustrates an example of an integrated device package 1601 that includes a tunable inductor 200 implemented in a package substrate 1610. The tunable inductor 200 may be a tunable inductive means or means for tunable inductance.

FIG. 16 illustrates an integrated device package 1601 that includes a package substrate 1610, a die 1611, an underfill 1614, a plurality of solder interconnects 1615 (e.g., solder 15 balls), and an encapsulation layer 1616. The integrated device package 1601 is coupled to a printed circuit board (PCB) 1650 through a plurality of solder balls 1651.

The package substrate 1610 includes at least one dielectric layer 1612. The at least one dielectric layer 1612 may 20 include a core layer and/or a prepeg layer. The package substrate 1610 also include a plurality of interconnects 1613. The package substrate 1610 may also include a first solder resist layer 1680 and a second solder resist layer 1682. The first solder resist layer 1680 is formed on a first surface of 25 the package substrate 1610, and the second solder resist layer 1682 is formed on a second surface of the package substrate 1610.

The package substrate 1610 includes the tunable inductor 200, the first terminal 201, the second terminal 210, and the 30 third terminal 220. The tunable inductor 200 is located in the at least one dielectric layer 1612. The tunable inductor 200 may include one or more interconnects (e.g., traces, pads). The tunable inductor 200 is coupled to the first terminal 201, the second terminal 210 and the third terminal 220. The first 35 terminal 201 may include at least one interconnect (e.g., trace, pad, via). The second terminal 210 may include at least one interconnect (e.g., trace, pad, via). The third terminal 220 may include at least one interconnect (e.g., trace, pad, via). Two terminals may be live terminals, and 40 one terminal may be a dummy terminal.

As shown in FIG. 16, the first terminal 201 and the third terminal 220 may be live terminals. The first terminal 201 may be a first port, and the third terminal 220 may be a second port. The first terminal 201 and the third terminal 220 as each coupled to a solder interconnect from the plurality of solder interconnects 1615 (e.g., solder balls). The second terminal 210 is not coupled to a solder interconnect. The second terminal 210 is a dummy terminal. The second terminal 210 is covered by the first solder resist layer 1680, which prevents a solder interconnect from the plurality of solder interconnects 1615 from coupling or touching the second terminal 210. Different implementations may have different configurations of live terminals and dummy terminals

The encapsulation layer 1616 is coupled to the package substrate 1610 and the die 1611. The encapsulation layer 1616 at least partially encapsulates the die 1611.

Exemplary Integrated Device Package Comprising Real Time Tunable Inductor Implemented in Package Substrate 60

As mentioned above, the tunable inductor 200 may be implemented by using one or more switches. FIG. 17 illustrates an example of an integrated device package 1701 that includes a tunable inductor 200 implemented in a package substrate 1610. The tunable inductor 200 is a real 65 time tunable inductor that is configurable to have different inductances when the die and/or the integrated device pack-

10

age is operational. The real time tunable inductor may be a real time tunable inductive means or means for real time tunable inductance.

FIG. 17 is similar to FIG. 16, except that the die 1711 includes at least one switch 1722 (e.g., means for switching). The at least one switch 1722 may include transistors. The at least one switch 1722 may include a first switch, a second switch a, and a third switch, as described in FIG. 20. The die 1711 may also include a circuit for controlling the switch 1722.

FIG. 17 illustrates an integrated device package 1701 that includes a package substrate 1610, a die 1711, an underfill 1614, a plurality of solder interconnects 1615 (e.g., solder balls), and an encapsulation layer 1616. The integrated device package 1601 is coupled to a printed circuit board (PCB) 1650 through a plurality of solder balls 1651. The package substrate 1610 includes the tunable inductor 200, the first terminal 201, the second terminal 210, the third terminal 220, and the fourth terminal 230.

As mentioned above, the die 1711 includes at least one switch 1722. The at least one switch 1722 is configured to be electrically coupled to the tunable inductor 200. In some implementations, the at least one switch 1722 may be coupled to the first terminal 201, the second terminal 210, the third terminal 220, and the fourth terminal 230 of the tunable inductor 200.

Each particular switch is coupled to a particular terminal of the tunable inductor **200**. Each particular switch is configured to control whether the terminal is on or off (e.g., whether a current or signal may pass through the terminal). When the switch is open, no current or signal may pass through the corresponding terminal. When the switch is closed, a current or signal may pass through the corresponding terminal.

As will be further described in FIG. 20, the inductance of the tunable inductor 200 may be configured (e.g., tuned) by selectively opening and closing the switches coupled to the terminals of the tunable inductor 200.

Exemplary Integrated Passive Device (IPD) Comprising Real Time Tunable Inductor

FIGS. **18-19** illustrate examples of where integrated passive devices (IPDs) may be implemented.

FIG. 18 illustrates an integrated device package 1801 that includes a package substrate 1410, a die 1711 and an integrated passive device (IPD) 1800 that includes a tunable inductor. The integrated passive device (IPD) 1800 may be any of the integrated passive device (IPD) that includes a tunable inductor, described in the present disclosure. The tunable inductor may be a tunable inductive means or means for tunable inductance. The integrated device package 1801 is coupled to a printed circuit board (PCB) 1450 through a plurality of solder balls 1451.

FIG. 18 is similar to FIG. 14, except that the die 1711 includes at least one switch 1722. The at least one switch 1722 is configured to be electrically coupled to the integrated passive device (IPD) 1800, which includes a tunable inductor (e.g., tunable inductor 200). The die 1711, which includes the at least one switch 1722, may be used to configured the inductance of the tunable inductor in the integrated passive device (IPD) 1800, when the die 1711 and/or the integrated device package 1801 is operational. Thus, the integrated passive device (IPD) 1800 may include a real time configurable tunable inductor.

FIG. 19 illustrates another example of where an integrated passive device (IPD) may be positioned. FIG. 19 is similar to FIG. 15, except that the die 1711 includes at least one switch 1722. The at least one switch 1722 is configured to

be electrically coupled to the integrated passive device (IPD) 1800, which includes a tunable inductor (e.g., tunable inductor 200). The die 1711, which includes the at least one switch 1722, may be used to configured the inductance of the tunable inductor in the integrated passive device (IPD) **1800**, when the die 1711 and/or the integrated device package **1801** is operational. Thus, the integrated passive device (IPD) 1800 may include a real time configurable tunable

Exemplary Circuit Diagram of a Real Time Tunable Induc-

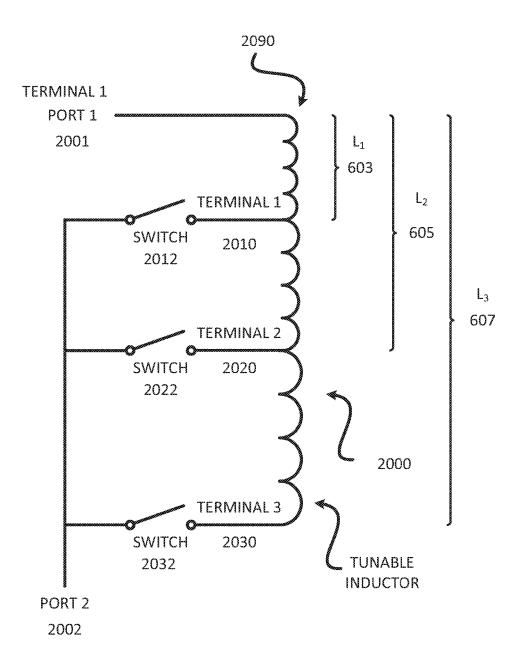

FIG. 20 illustrates an example of a circuit diagram 2090 of a real time tunable inductor. The real time tunable inductor may be a real time tunable inductive means or 15 means for real time tunable inductance. The circuit diagram 2090 includes a tunable inductor 2900, a first terminal 2001, a second terminal 2010, a third terminal 2020, a fourth terminal 2030, a first switch 2012, a second switch 2022, a third switch 2032, and a port 2002.

The tunable inductor 2000 may correspond to the tunable inductor 200 of FIGS. 17-19. The first terminal 2001 may correspond to the first terminal 201. The second terminal 2010 may correspond to the second terminal 210. The third terminal 2020 may correspond to the third terminal 220. The 25 time tuning of an inductor. In some implementations, the fourth terminal 2030 may correspond to the fourth terminal **230**.

The first switch 2012 is coupled to the second terminal 2010. The second switch 2022 is coupled to the third terminal 2020. The third switch 2032 is coupled to the fourth 30 terminal 2030. The first switch 2012, the second switch 2022, and the third switch 2032 are coupled to the port 2002. The first switch 2012, the second switch 2022, and the third switch 2032 may correspond to the at least one switch 1722 of FIGS. 17-19.

The inductance of the tunable inductor 2000 may be configured by selectively opening and closing the first switch 2012, the second switch 2022, and the third switch 2032. For example, when the first switch 2012 is closed and the second switch 2022 and the third switch 2032 are open, 40 then the second terminal 2010 is coupled to the port 602.

When the tunable inductor 2000 includes the first terminal 2001 and the second terminal 2010 as the ports, the tunable inductor 2000 has a first inductance (L<sub>1</sub>) 2003. When the tunable inductor 2000 includes the first terminal 2001 and 45 the third terminal 2020 as the ports (e.g., second switch 2022 is closed, first switch 2012 and third switch 2032 are open). the tunable inductor 2000 has a second inductance (L<sub>2</sub>) 2005. When the tunable inductor 2000 includes the first terminal 2001 and the fourth terminal 2030 as the ports (e.g., 50 third switch 2032 is closed, first switch 2012 and second switch 2022 are open), the tunable inductor 2000 has a third inductance ( $L_3$ ) 2007.

As described above, by selectively opening and closing the switches, the tunable inductor 2000 can be configured in 55 real time to have different inductances, thus providing the tunable inductor 2000 that can be configured in real time during the operation of a die and/or an integrated device package. It is noted that different implementations may use different configurations of switches.

Exemplary Integrated Device Package Comprising a Real Time Tunable Inductor

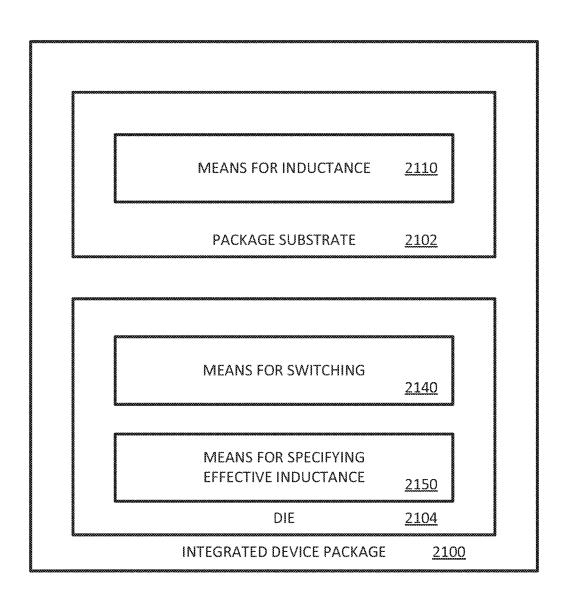

FIG. 21 illustrates a conceptual illustration of an integrated device package 2100 that includes a real time tunable inductor. The integrated device package 2100 includes a 65 package substrate 2102 and a die 2104. The package substrate 2102 includes a means for inductance 2110. The die

12

2104 includes a means for switching 2140 and a means for specifying effective inductance 2150.

In some implementations, a real time tunable inductor is a means for real time tunable inductance that includes the means for inductance 2110, the means for switching 2140 and the means for specifying effective inductance 2150. The means for inductance 2110 may include the tunable inductor

The means for inductance 2110 may include an integrated passive device (IPD) that includes a tunable inductor. The means for inductance 2110 may be located externally of the package substrate 2102. For example, the means for inductance 2110 may be coupled to a printed circuit board (PCB).

The means for switching 2140 may include the switch 1722, the first switch 2012, the second switch 2022, and/or the third switch 2032. The means for switching 2140 is coupled to the means for inductance 2110.

The means for specifying effective inductance 2150 may 20 include circuits that are configured to control the means for switching 2140. The means for specifying effective inductance 2150 is coupled to the means for inductance 2110. Exemplary Method for Real Time Tuning of an Inductor

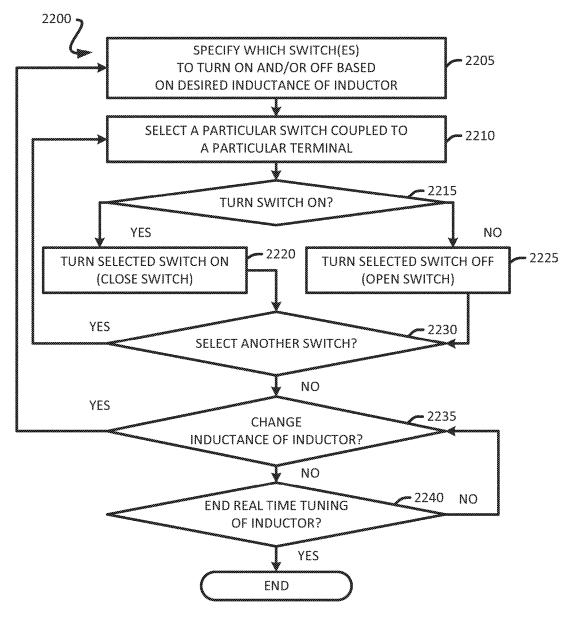

FIG. 22 illustrates an exemplary method 2200 for real tuning of the inductor is performed while a die and/or an integrated device package is operational. In some implementations, the method 2200 may be performed by an integrated device package (e.g., integrated device package 1701) that includes a tunable inductor (e.g., means for inductance) and at least one switch (e.g., means for switching).

In some implementations, the method 2200 is performed when a signal is transmitted through a tunable inductor 35 implemented in a package substrate. In some implementations, the method 2200 is performed when a signal is transmitted through a tunable inductor implemented in an integrated passive device (IPD).

The method specifies (at 2205) which switch(es) (e.g., switch from a plurality of switches) to turn on and/or off based on a desired inductance of the tunable inductor (e.g., tunable inductor 200). Each particular switch (e.g., first switch 2012) is coupled to a particular terminal of the tunable inductor. It is noted that prior to specifying which switch to turn on or off, the switches may be on (e.g., closed switch) or off (e.g., open switch). That is, all the switches may be on, all the switches may be off, or some switches may be on while some switches may be off.

The method selects (at 2210) a particular switch coupled to particular a terminal (e.g., switch from a plurality of switches).

The method determines (at 2215) whether to turn the selected switch on. If so, the method turns the selected switch on (at 2220). In some implementations, turning the selected switch on (at 2220) includes closing the switch, which allows a current or a signal to pass through the terminal that is coupled to the selected switch.

When the method determines (at 2215) not to turn the selected switch on, the method proceeds to turn the selected 60 switch off (at 2225). In some implementations, turning the selected switch off (at 2225) include opening the switch, which does not allow a current or a signal to pass through the terminal that is coupled to the selected switch.

The method determines (at 2230) whether to select another switch. If so, the method proceeds to select (at 2210) another switch coupled to another terminal. In some implementations, the method may iteratively select and turn on

and off several switches, while a die and/or an integrated device package is operational.