(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-78898

(P2004-78898A)

(43) 公開日 平成16年3月11日(2004.3.11)

(51) Int.Cl.<sup>7</sup>G06K 19/07

B42D 15/10

F 1

G06K 19/00

B42D 15/10

G06K 19/00J

521

H

テーマコード(参考)

2C005

5B035

審査請求 未請求 請求項の数 6 O L (全 14 頁)

(21) 出願番号 特願2003-161919 (P2003-161919)

(22) 出願日 平成15年6月6日 (2003.6.6)

(31) 優先権主張番号 特願2002-175189 (P2002-175189)

(32) 優先日 平成14年6月17日 (2002.6.17)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000005108

株式会社日立製作所

東京都千代田区神田駿河台四丁目6番地

(71) 出願人 000233169

株式会社日立超エル・エス・アイ・システムズ

東京都小平市上水本町5丁目22番1号

(74) 代理人 100080001

弁理士 筒井 大和

角田 尚隆

東京都小平市上水本町5丁目22番1号

株式会社日立超エル・エス・アイ・システムズ内

最終頁に続く

(54) 【発明の名称】 ICカード

## (57) 【要約】

【課題】非接触動作時における電源端子間の短絡による誤動作などを防止し、かつセキュリティを大幅に向上する。

【解決手段】非接触／接触動作を兼用するデュアルウェイタイプのICカードにおいて、電源電圧端子VCCと接触電源回路15との間には分離用のトランジスタが設けられている。非接触／接触判定・切り換え部6は、ICカードが非接触動作であることを検出すると、該トランジスタをOFFし、電源電圧端子VCCと接触電源回路15と分離する。これにより、非接触動作時に電源電圧端子VCCとグランド端子GNDとが短絡した際のICカードの誤動作などを確実に防止する。このとき、電源電圧端子VCCが基準電位VSSレベルとなるので、該電源電圧端子VCCの電圧モニタを防止でき、該ICカードのセキュリティを大幅に向上する。

【選択図】 図3

図3

**【特許請求の範囲】****【請求項 1】**

接触タイプと非接触タイプとを兼用したデュアルウェイタイプの I C カードであって、

非接触動作を検出し、制御信号を出力する動作モード検出部と、

前記動作モード検出部の制御信号に基づいて、接触電源端子と内部電源とを切り離す分離

スイッチ手段とを備えたことを特徴とする I C カード。

**【請求項 2】**

請求項 1 記載の I C カードにおいて、前記接触電源端子が、電源電圧が供給される電源電

圧端子、または基準電位が接続される基準電位端子の少なくともいずれかであることを特

徴とする I C カード。

**【請求項 3】**

請求項 1 または 2 記載の I C カードにおいて、前記分離スイッチ手段が、2 つの P チャネ

ル M O S トランジスタを直列接続した構成からなることを特徴とする I C カード。

**【請求項 4】**

請求項 1 ~ 3 のいずれか 1 項に記載の I C カードにおいて、前記分離スイッチ手段を、前

記接触電源端子の近傍に設けたことを特徴とする I C カード。

**【請求項 5】**

請求項 1 ~ 4 のいずれか 1 項に記載の I C カードにおいて、前記 P チャネル M O S トラン

ジスタのトランジスタサイズは、論理用の M O S トランジスタよりも大きいことを特徴と

する I C カード。

**【請求項 6】**

請求項 1 ~ 5 のいずれか 1 項に記載の I C カードにおいて、前記動作モード検出部は、受

信した電波を整流して直流電圧を生成し、その直流電圧を検出して非接触動作を判定する

ことを特徴とする I C カード。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、 I C カードに関し、特に、デュアルウェイタイプの I C カードにおける信頼性

の向上に適用して有効な技術に関するものである。

**【0002】****【従来の技術】**

近年、クレジットカードや電話カードなどの機能を有する I C カードが普及しつつある。

この I C カードは、磁気カードと同じような形状のカードに C P U とメモリとが搭載され

ており、該 C P U によってメモリのリード / ライトが管理され、暗号処理などをカードそれ

自体に持たせ、高セキュリティ機能、および大記憶容量を有している。

**【0003】**

また、 I C カードには、外部装置との情報伝達方式の 1 つとして、たとえば、該外部装置

との間に機械的結合手段を有する接触タイプ、電波などの情報伝送媒体によって情報を伝

達する非接触タイプ、ならびに接触 / 非接触兼用タイプ、いわゆるデュアルウェイタイプ

がある。

**【0004】**

デュアルウェイタイプの I C カードでは、接触タイプの電源入力端子から供給された電力

と、非接触タイプの電波から供給される電力とが共通の電源ラインとなり、内部の電源レ

ギュレータに供給される。

**【0005】**

この場合、電源ラインが共通のために、 I C カードの非接触動作時において、接触動作時

に用いられる電源端子にも電源電圧が印加され、金属の接触などの何らかの理由によ

って電源電圧 ( V D D ) 端子と接地 ( G N D ) 端子とが短絡した際に誤動作などを招いてしま

う恐れがある。

**【0006】**

10

20

30

40

50

このような電源電圧端子と接地端子との短絡によるICカードの誤動作を防止する技術としては、たとえば、特開2000-148961号公報に示されるように、電源ラインの電源電圧VDD側などにダイオードを挿入し、電源電圧端子から接地端子に電流が逆流することを防止することが知られている。

【0007】

【発明が解決しようとする課題】

ところが、上記のようなICカードにおける逆電流防止技術では、次のような問題点があることが本発明者により見い出された。

【0008】

すなわち、ICカードの電源ラインに逆電流防止用のダイオードを挿入した場合、接触動作時に電源端子に供給される電源電圧が該ダイオードの順方向電圧(VF)によりドロップしてしまい、電源動作範囲が狭くなってしまい、ICカードの信頼性などを損ねてしまう恐れがある。

【0009】

また、デュアルウェイタイプのICカードでは、非接触動作時にアンテナから供給されている電力の変化を電源端子からモニタされるという問題がある。電力の変化のモニタは、電源ラインにダイオードが挿入されていても完全に防止できず、この電力の変化を読み取ることにより、ICカードの半導体集積回路装置の内部動作などが解析され、セキュリティホールなってしまう恐れがある。

【0010】

本発明の目的は、非接触動作時における電源端子間の短絡による誤動作などを防止するとともに、電力変化のモニタを防止してセキュリティを大幅に向上することのできるICカードを提供することにある。

【0011】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【0012】

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

1. 接触タイプと非接触タイプとを兼用したデュアルウェイタイプのICカードであって、非接触動作を検出して制御信号を出力する動作モード検出部と、該動作モード検出部の制御信号に基づいて、接触電源端子と内部電源とを切り離す分離スイッチ手段とを備えたものである。

【0013】

また、本願のその他の発明の概要を簡単に示す。

2. 前記第1項において、接触電源端子が、電源電圧端子、または基準電位端子の少なくともいずれかよりなるものである。

3. 前記第1項または前記第2項において、分離スイッチ手段が、2つのPチャネルMOSトランジスタを直列接続した構成からなるものである。

4. 前記第1項～第3項のいずれかにおいて、分離スイッチ手段を、接触電源端子の近傍に設けたものである。

5. 前記第1項～前記第4項のいずれかにおいて、PチャネルMOSトランジスタのトランジスタサイズは、論理用のMOSトランジスタよりも大きいものである。

6. 前記第1項～第5項のいずれかにおいて、動作モード検出部は、受信した電波を整流して直流電圧を生成し、その直流電圧を検出して非接触動作を判定するものである。

【0014】

【発明の実施の形態】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。

【0015】

10

20

30

40

50

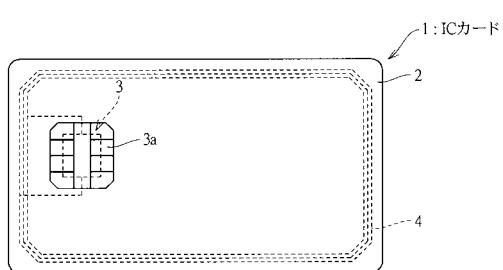

図1は、本発明の一実施の形態によるICカードの説明図、図2は、図1のICカードに内蔵された半導体集積回路装置のブロック図、図3は、図2の半導体集積回路装置に設けられた非接触RF部のブロック図、図4は、図3の非接触RF部に設けられた非接触/接触判定・切り換え部の構成説明図、図5は、図4の非接触RF部における各部の信号タイミングチャート、図6は、図1のICカードに内蔵された半導体集積回路装置におけるチップレイアウトの説明図、図7は、図4の非接触RF部に設けられたトランジスタの断面図、図8は、図7のトランジスタの等価回路図、図9は、図7のトランジスタ論理用のPチャネルMOSトランジスタとのデバイスサイズを比較した説明図である。

## 【0016】

本実施の形態において、ICカード1は、接触型と非接触型とを兼用した、いわゆるデュアルインターフェースICカードからなる。ICカード1は、図1に示すように、磁気カードと同じような形状のプラスティックカード2に半導体集積回路装置3が埋め込まれている。 10

## 【0017】

また、プラスティックカード2の外周部近傍には、アンテナとなるコイル4が埋め込まれている。このコイル4の両端は、半導体集積回路装置2の接続端子LA, LB(図2)に接続されている。

## 【0018】

コイル4は、ICカード1の非接触動作時に、カード端末機からの電波を受け、電力供給や情報通信などを行う。 20

## 【0019】

プラスティックカード2の表面には、半導体集積回路装置3の複数の外部端子3aが露出して設けられている。これら外部端子3aは、ICカード1が接触動作時にカード端末機の外部端子と機械的に接触することにより、電力供給や情報通信などが行われる。

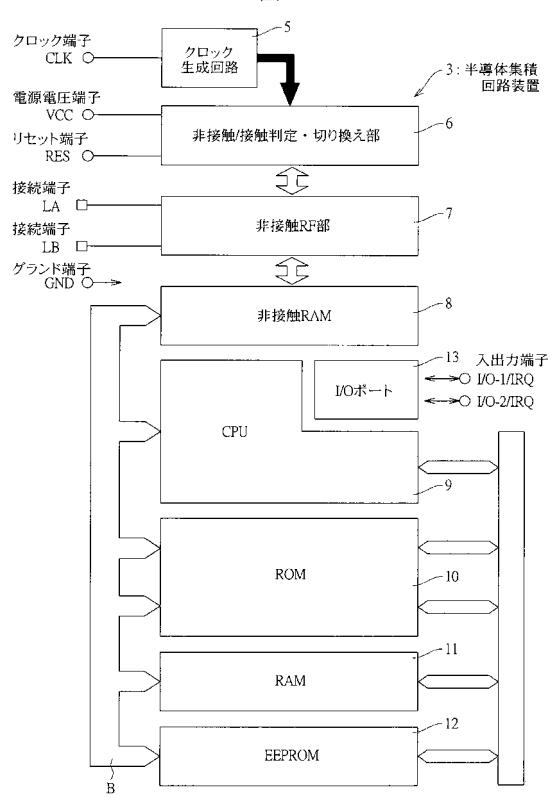

## 【0020】

さらに、半導体集積回路装置3は、図2に示すように、クロック生成回路5、非接触/接触判定・切り換え部(動作モード検出部)6、非接触RF部7、非接触RAM8、CPU9、ROM10、RAM11、EEPROM12、ならびにI/Oポート13などから構成されている。 30

## 【0021】

半導体集積回路装置3は、外部端子3aとして、クロック端子CLK、電源電圧端子(接触電源端子)VCC、リセット端子RES、グランド端子(接触電源端子、基準電位端子)GND、および入出力端子I/O1, I/O2が設けられている。

## 【0022】

クロック端子CLKは、外部クロック信号が供給される。電源電圧端子VCCは、電源電圧が供給され、リセット端子RESは、リセット信号が入力される。グランド端子GNDには基準電位VSSが接続され、入出力端子I/O1, I/O2には、データが入出力される。

## 【0023】

クロック生成回路5は、クロック端子CLKから供給されたクロック信号から内部クロック信号を生成する。非接触/接触判定・切り換え部6は、ICカード1の動作時において、コイル4に電圧があるか否かを検出することによって接触動作か非接触動作かを判定し、内部クロック信号の切り換えなどを制御するとともに、ICカード1が非接触動作時には電源電圧端子VCCを電気的に切断する。 40

## 【0024】

非接触RF部7は、ICカード1が非接触動作する際に用いられる高周波インターフェース機能であり、接続端子LA, LBを介してコイル4の両端部が接続されている。

## 【0025】

また、非接触RAM8、CPU9、ROM10、RAM11、およびEEPROM12は、内部バスBにより相互に接続されている。非接触RAM8は揮発性メモリであり、IC 50

カード1の非接触動作時において、該ICカード1から入出力されるデータを一時的に格納する。

【0026】

CPU9は、ROM10に格納されたプログラムに基づいてICカードにおけるすべての制御を司る。ROM10は読み出し専用メモリであり、ICカード1の制御プログラムなどが格納されている。

【0027】

RAM11は揮発性メモリからなり、ICカード1の接触動作時に該ICカード1から入出力されるデータを一時的に格納する。EEPROM12は電気的に消去／書き換えが可能なメモリであり、非接触RAM8、あるいはRAM11に一時的に格納されたデータなどを格納する。I/Oポート13は、カード端末機からのデータが入出力されるポートである。

【0028】

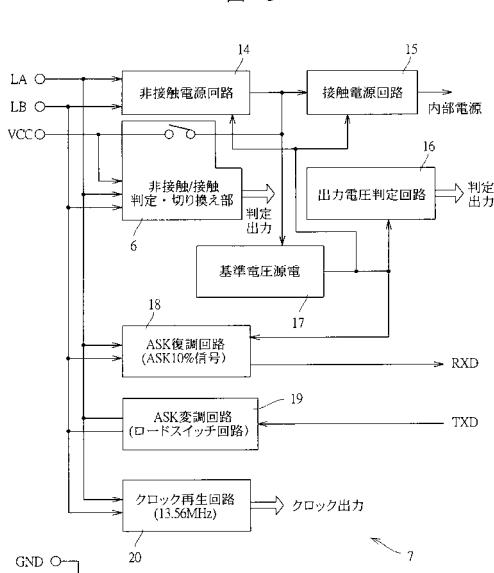

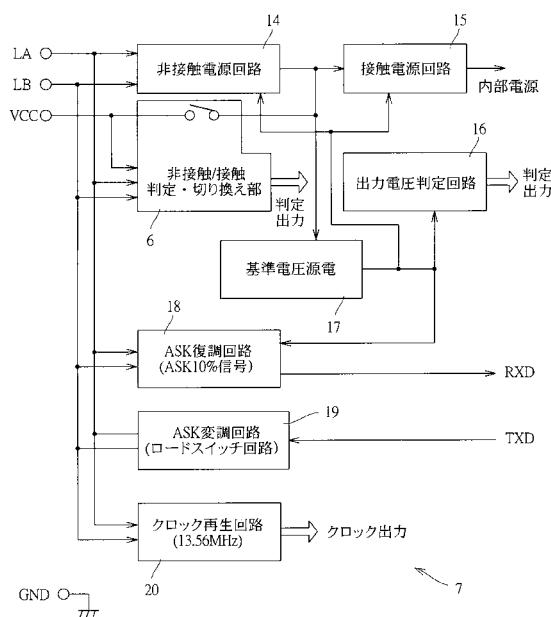

また、非接触RF部7の構成について、図3のブロック図を用いて説明する。

【0029】

非接触RF部7は、非接触電源回路14、接触電源回路15、出力電圧判定回路16、基準電圧電源17、ASK復調回路18、ASK変調回路19、およびクロック再生回路20からなる。

【0030】

非接触電源回路14は、整流回路、レギュレータなどから構成された電源回路であり、ICカード1の動作電圧となる内部電源電圧を生成する。コイル4は、カード端末機から出力された電波から電力を取り出し、その電力を非接触電源回路14に供給する。

【0031】

接触電源回路15はレギュレータなどからなり、ICカード1が接触動作時に電源電圧端子VCCから供給される電源電圧から内部電源電圧を生成する。出力電圧判定回路16は、内部電源電圧の電圧レベルを検出し、ある電圧レベルになるとリセット信号を出力し、半導体集積回路装置3をリセットする。

【0032】

基準電圧電源17は、たとえば、バンドギャップ回路からなり、内部電源電圧から基準電圧を生成し、非接触電源回路14、接触電源回路15、出力電圧判定回路16、およびASK復調回路18などに供給する。

【0033】

ASK復調回路18は、コイル4が受信した搬送波の振幅を入力ディジタル信号に対応させて変化させたASK(Amplitude Shift Keying:振幅シフトキーイング)信号のデータを復調して非接触RAM8に出力する。

【0034】

ASK変調回路19は、非接触RAM8から出力されたデータをASK変調し、コイル4から送信する。クロック再生回路20は、コイル4が受信したクロック信号から、13.56MHz程度の内部クロック信号を生成し、半導体集積回路装置3の動作クロック信号として出力する。

【0035】

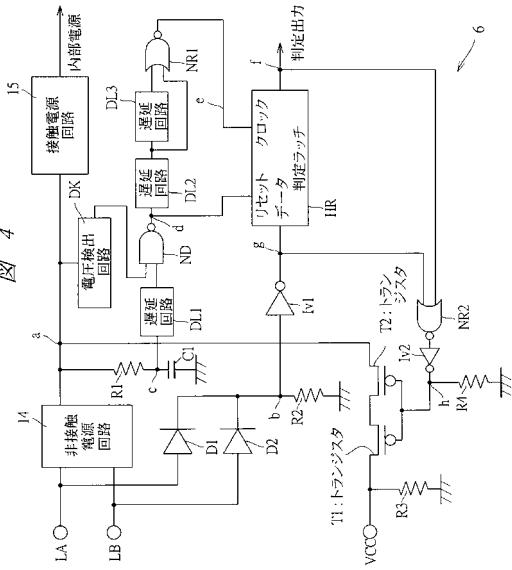

また、非接触／接触判定・切り換え部6の接続構成について、図4を用いて説明する。

【0036】

非接触／接触判定・切り換え部6は、ダイオードD1, D2、抵抗R1～R4、コンデンサC1、PチャネルMOSのトランジスタ(分離スイッチ手段)T1, T2、インバータIV1, IV2、否定論理積回路ND、否定論理和回路NR1, NR2、電圧検出回路DK、遅延回路DL1～DL3、および判定ラッチHRから構成されている。

【0037】

ダイオードD1のアノード、および非接触電源回路14の一方の入力部には、コイル4の一方の端部が接続された接続端子LAがそれぞれ接続されている。ダイオードD2のアノ

10

20

30

40

50

ード、および非接触電源回路 14 の他方の入力部には、コイル 4 の他方の端部が接続された接続端子 L B がそれぞれ接続されている。

【 0 0 3 8 】

ダイオード D 1, D 2 のカソードは、抵抗 R 2 の一方の接続部、ならびにインバータ I v 1 の入力部に接続されており、これらダイオード D 1, D 2 は、コイル 4 から取り込まれた電力を整流して出力する。

【 0 0 3 9 】

非接触電源回路 14 の出力部には、抵抗 R 1 の一方の接続部、トランジスタ T 2 の他方の接続部、電圧検出回路 D K の入力部、および接触電源回路 15 の入力部にそれぞれ接続されている。非接触電源回路 14 は、コイル 4 から取り込まれた電力を整流し、安定化して出力する。

【 0 0 4 0 】

抵抗 R 1 の他方の接続部には、コンデンサ C 1 の一方の接続部、および遅延回路 D L 1 の入力部に接続されており、該コンデンサ C 1 の他方の接続部には、基準電位 V S S が接続されている。これら抵抗 R 1、ならびにコンデンサ C 1 により時定数回路が形成される。

【 0 0 4 1 】

遅延回路 D L 1 の出力部には、否定論理積回路 N D の他方の入力部が接続されており、該否定論理積回路 N D の一方の接続部には、電圧検出回路 D K の電圧検出信号が入力されるように接続されている。

【 0 0 4 2 】

否定論理積回路 N D の出力部には、遅延回路 D L 2 の入力部、およびフリップフロップからなる判定ラッチ H R のリセット端子が接続されている。この遅延回路 D L 2 の出力部には、遅延回路 D L 3 の入力部、および否定論理和回路 N R 1 の他方の入力部が接続されており、該否定論理和回路 N R 1 の一方の入力部には、遅延回路 D L 3 の出力部が接続されている。

【 0 0 4 3 】

否定論理和回路 N R 1 の出力部には、判定ラッチ H R のクロック端子が接続されている。そして、判定ラッチ H R の出力部から出力される信号が、非接触 / 接触判定・切り換え部 6 の判定信号となる。判定ラッチ H R の出力部には、否定論理和回路 N R 2 の他方の入力部が接続されている。

【 0 0 4 4 】

抵抗 R 3 の一方の接続部、およびトランジスタ T 1 の一方の接続部には、電源電圧端子 V C C が接続されている。トランジスタ T 1 の他方の接続部には、トランジスタ T 2 の一方の接続部が接続されており、これらトランジスタ T 1, T 2 のゲートには、抵抗 R 4 の一方の接続部、およびインバータ I v 2 の出力部がそれぞれ接続されている。

【 0 0 4 5 】

これらトランジスタ T 1, T 2 は、電源電圧端子 V C C と接触電源回路 15 などの内部電源ラインとを分離するスイッチである。トランジスタ T 1, T 2 は、I C カード 1 が接触動作する場合に ON となり、該 I C カード 1 が非接触動作時には、トランジスタ T 1, T 2 が OFF となって前述したように電源電圧端子 V C C と内部電源ラインとを電気的に切り離す。

【 0 0 4 6 】

これにより、電源電圧端子 V C C は抵抗 R 3 によって基準電位 V S S レベルに固定される。

【 0 0 4 7 】

また、抵抗 R 3, R 4 の他方の接続部には、基準電位 V S S が接続されており、インバータ I v 2 の入力部には、否定論理和回路 N R 2 の出力部が接続されている。

【 0 0 4 8 】

抵抗 R 2 の他方の接続部には、基準電位 V S S が接続されており、インバータ I v 1 の出力部には、判定ラッチ H R のデータ端子、および否定論理和回路 N R 2 の一方の入力部が

10

20

30

40

50

それぞれ接続されている。

【0049】

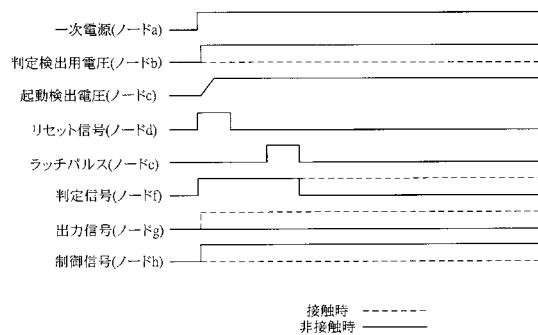

次に、本実施の形態における非接触／接触判定・切り換え部6の動作について、図5のタイミングチャートを用いて説明する。

【0050】

図5においては、上方から下方にかけて、非接触電源回路14から出力される一次電源(図4のノードa)、ダイオードD1,D2に整流された判定検出用電圧(図4のノードb)、遅延回路DL1に入力される起動検出電圧(図4のノードc)、否定論理積回路NDから出力されるリセット信号(図4のノードd)、否定論理和回路NR1から出力されるラッチパルス(図4のノードe)、判定ラッチHRから出力される判定信号(図4のノードf)、インバータIV1から出力される出力信号(図4のノードg)、トランジスタT1,T2を駆動させる制御信号(図4のノードh)における信号のタイミングをそれぞれ示している。

【0051】

また、図5においては、非接触動作時の信号タイミングを実線で示し、接触動作時の信号タイミングを点線により示している。ここでは、ICカード1の非接触動作について説明する。

【0052】

まず、コイル4がカード端末機の電波を受信すると、非接触電源回路14から一次電源が20出力され、ダイオードD1,D2から出力される判定検出用電圧も同様に上昇し、Hiレベルとなる。

【0053】

このとき、否定論理積回路NDからリセット信号(Hiレベル)が出力され、判定ラッチHRをリセットする。遅延回路DL1は、ある時定数で起動検出電圧(ノードc)がHiレベルとなると、そのHiレベルの信号をある時間だけ遅延させて出力する。否定論理積回路NDは、遅延回路DL1から出力されたHiレベル信号を受けてLoレベル信号となる。

【0054】

また、前述のように判定検出用電圧がHiレベルであるので、インバータIV1から出力される信号(ノードg)がLoレベルとなり、インバータIV2から出力される制御信号がHiレベルとなる。

【0055】

そして、否定論理積回路NDから出力されたリセット信号は、遅延回路DL2によってある時間遅延されて、否定論理和回路NR1に他方の入力部に入力され、該遅延回路DL2から出力された信号は遅延回路DL3によりさらに遅延されて、否定論理和回路NR1の一方の入力部に入力される。

【0056】

否定論理和回路NR1は、遅延回路DL2と遅延回路DL3との遅延時間の間、ラッチパルスを出力し、このラッチパルスに基づいて判定ラッチHRはインバータIV1の出力信号(ノードg)をラッチし、判定信号(ノードf)として出力する。ここで、非接触／接触判定・切り換え部6においては、ダイオードD1,D2によって整流した直流電圧を検出信号として用いているので、検出時間を短くすることができる。

【0057】

このとき、インバータIV1の出力はLoレベル、判定信号もLoレベルであるので、インバータIV2の出力部(ノードh)からは、Hiレベルの信号が出力されており、トランジスタT1,T2がOFFとなって電源電圧端子VCCは基準電位VSSレベルとなる。

【0058】

よって、電源電圧端子VCCとグランド端子GNDとが短絡しても、逆電流が流れることが防止されることになる。

## 【0059】

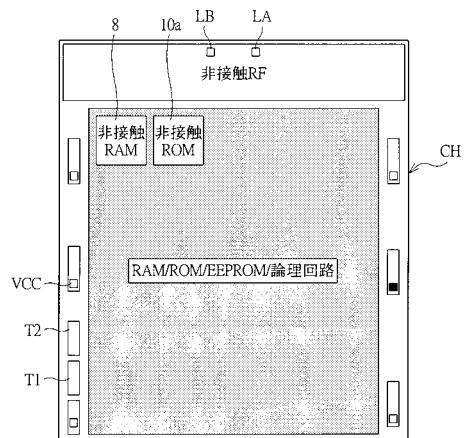

さらに、半導体集積回路装置3のチップレイアウトについて、図6を用いて説明する。

## 【0060】

図6において、半導体チップCHの上方には、非接触RF部7が位置しており、この非接触RF部7の上方には接続端子LA, LBがそれぞれ設けられている。さらに、非接触RF部7に近接する下部には、非接触RAM8とROM10の一部である非接触ROM10aが設けられている。

## 【0061】

図中の網掛けで示した領域には、これら非接触RAM8と非接触ROM10aを含むように、ROM10、RAM11、EEPROM12、CPU9やクロック生成回路5、非接触/接触判定・切り替え部6を含む論理回路が構成されている。

## 【0062】

半導体チップCHの周辺には、クロック端子CLK、電源電圧端子(接触電源端子)VCC、リセット端子RES、グランド端子(接触電源端子、基準電位端子)GND、および入出力端子I/O1, I/O2が設けられている。

## 【0063】

そして、電源電圧端子VCCの近傍には、トランジスタT1, T2が設けられることによってインピーダンスを下げることができ、電圧低下を抑えることができる。

## 【0064】

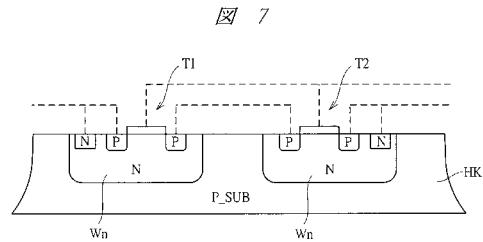

ここで、トランジスタT1, T2の断面図を図7に示す。

10

20

## 【0065】

図7において、たとえば、P形のシリコン単結晶基板からなる半導体基板HK上にHK上N-ウェルWNが形成されており、このN-ウェルWN上にトランジスタT1, T2が形成されている。

## 【0066】

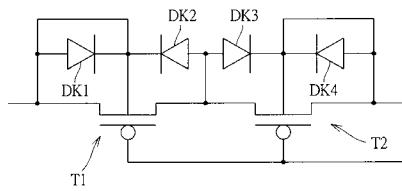

トランジスタT1, T2には、図8に示すように、半導体基板HKに形成される寄生ダイオードDk1～Dk4が形成されるが、これらトランジスタT1, T2を直列接続することによって、トランジスタT1の寄生ダイオードDk1, Dk2がそれぞれ順方向、および逆方向に接続されることになる。

30

## 【0067】

さらに、トランジスタT2の寄生ダイオードDk3, Dk4においても同様に、順方向、および逆方向に接続されることになる。それにより、これら寄生ダイオードDk1～Dk4を介して電源電圧端子VCCに電圧が発生してしまうことを防止することができる。

## 【0068】

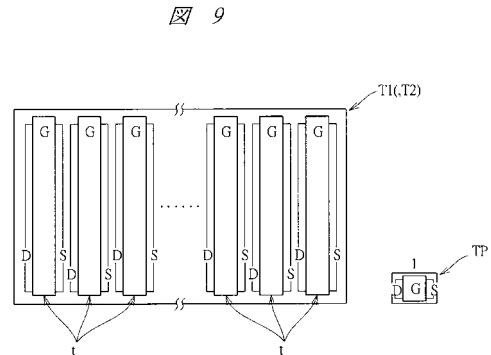

また、図9は、トランジスタT1(, T2)と一般的な論理用のPチャネルMOSトランジスタTpとのデバイスサイズを比較した説明図である。

## 【0069】

図示するように、トランジスタT1(, T2)はON抵抗を下げるために、トランジスタTpに比べ、たとえば、面積比で約700倍程度以上となっている。この場合、n個のPチャネルMOSトランジスタtが並列接続されて1つのトランジスタT1(, T2)が構成されている。

40

## 【0070】

それにより、本実施の形態によれば、ICカード1の非接触動作時には、トランジスタT1, T2がOFFとなり、電源電圧端子VCCが基準電位VSSレベルとなるので、電源電圧端子VCCとグランド端子GNDとが短絡しても、該ICカード1の誤動作などを確実に防止することができる。

## 【0071】

また、ICカード1の非接触動作時には、電源電圧端子VCCは基準電位VSSレベルとなるので、該電源電圧端子VCCをモニタすることによる内部動作の解析を防止することができ、該ICカード1のセキュリティを大幅に向上することができる。

50

## 【0072】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

## 【0073】

たとえば、前記実施の形態では、電源電圧端子を基準電位VSSレベルに固定するトランジスタがPチャネルMOSのトランジスタから構成された場合について記載したが、これらトランジスタは、NチャネルMOSトランジスタであってもよい。

## 【0074】

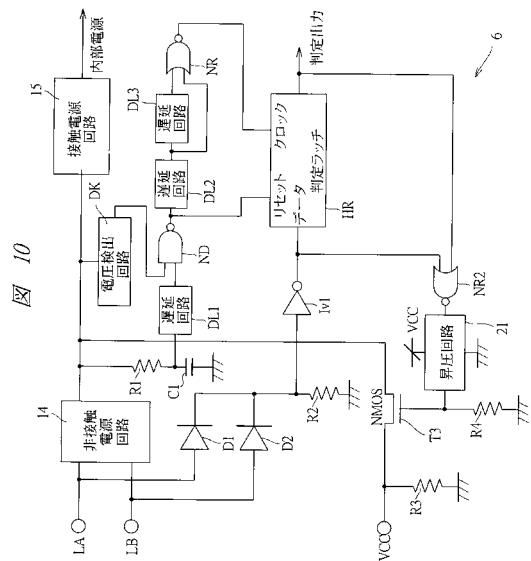

この場合、図10に示すように、非接触／接触判定・切り換え部6には、トランジスタT1, T2(図4)の代わりとしてNチャネルMOSのトランジスタ(分離スイッチ手段)T3が設けられ、該トランジスタT3を駆動させる昇圧回路21が新たに設けられる構成となる。 10

## 【0075】

NチャネルMOSのトランジスタT3を用いることにより、寄生ダイオードの影響をなくすことができる。

## 【0076】

トランジスタT3の一方の接続部には、電源電圧端子VCCが接続されており、該トランジスタT3の他方の接続部には、非接触電源回路14の出力部に接続されている。トランジスタT3のゲートには、抵抗R4を介して基準電位に接続されている。 20

## 【0077】

また、トランジスタT3のゲートには、昇圧回路21が生成した昇圧電圧が入力するよう接続されており、該昇圧回路21の制御端子には、否定論理回路NR2の出力部が接続されている。

## 【0078】

昇圧回路21は、否定論理回路NR2の出力部から出力された信号に基づいて昇圧動作を開始し、生成した昇圧電圧をトランジスタT3のゲートに出力する。

## 【0079】

さらに、その他の非接触／接触判定・切り換え部6における構成、および接続は、図4と同様であるので説明は省略する。 30

## 【0080】

よって、NチャネルMOSのトランジスタT3を用いることにより、トランジスタT1, T2(図4)に比べてON抵抗を小さくすることが可能となる。

## 【0081】

## 【発明の効果】

本願によって開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

## 【0082】

(1) 分離スイッチ手段を設けたことにより、非接触動作時に接触電源端子が短絡しても、ICカードの誤動作などを防止することができる。 40

## 【0083】

(2) また、非接触動作時に接触電源端子と内部電源とを切り離すことにより、非接触動作時におけるICカードのセキュリティを大幅に向上することができる。

## 【0084】

(3) さらに、上記(1)、(2)により、ICカードの信頼性を向上することができる。

## 【図面の簡単な説明】

【図1】本発明の一実施の形態によるICカードの説明図である。

【図2】図1のICカードに内蔵された半導体集積回路装置のブロック図である。

【図3】図2の半導体集積回路装置に設けられた非接触RF部のブロック図である。 50

【図4】図3の非接触RF部に設けられた非接触/接触判定・切り換え部の構成説明図である。

【図5】図4の非接触RF部における各部の信号タイミングチャートである。

【図6】図1のICカードに内蔵された半導体集積回路装置におけるチップレイアウトの説明図である。

【図7】図4の非接触RF部に設けられたトランジスタの断面図である。

【図8】図7のトランジスタの等価回路図である。

【図9】図7のトランジスタ論理用のPチャネルMOSトランジスタとのデバイスサイズを比較した説明図である。

【図10】本発明の他の実施の形態によるICカードに内蔵された半導体集積回路装置に 10 設けられた非接触RF部のブロック図である。

【符号の説明】

- |                   |                          |    |

|-------------------|--------------------------|----|

| 1                 | ICカード                    |    |

| 2                 | プラスティックカード               |    |

| 3                 | 半導体集積回路装置                |    |

| 3 a               | 外部端子                     |    |

| 4                 | コイル                      |    |

| 5                 | クロック生成回路                 |    |

| 6                 | 非接触/接触判定・切り換え部(動作モード検出部) |    |

| 7                 | 非接触RF部                   | 20 |

| 8                 | 非接触RAM                   |    |

| 9                 | CPU                      |    |

| 10                | ROM                      |    |

| 10 a              | 非接触ROM                   |    |

| 11                | RAM                      |    |

| 12                | E PROM                   |    |

| 13                | I/Oポート                   |    |

| 14                | 非接触電源回路                  |    |

| 15                | 接触電源回路                   |    |

| 16                | 出力電圧判定回路                 | 30 |

| 17                | 基準電圧電源                   |    |

| 18                | ASK復調回路                  |    |

| 19                | ASK変調回路                  |    |

| 20                | クロック再生回路                 |    |

| L A , L B         | 接続端子                     |    |

| C L K             | クロック端子                   |    |

| V C C             | 電源電圧端子(接触電源端子)           |    |

| R E S             | リセット端子                   |    |

| G N D             | グランド端子(接触電源端子、基準電位端子)    |    |

| I / O 1 , I / O 2 | 入出力端子                    | 40 |

| D 1 , D 2         | ダイオード                    |    |

| R 1 ~ R 4         | 抵抗                       |    |

| C 1               | コンデンサ                    |    |

| T 1 , T 2         | トランジスタ(分離スイッチ手段)         |    |

| I v 1 , I v 2     | インバータ                    |    |

| N D               | 否定論理積回路                  |    |

| N R 1 , N R 2     | 否定論理和回路                  |    |

| D K               | 電圧検出回路                   |    |

| D L 1 ~ D L 3     | 遅延回路                     |    |

| H R               | 判定ラッチ                    | 50 |

D k 1 ~ D k 4 寄生ダイオード

B 内部バス

【図1】

図1

【図2】

図2

【 図 3 】

3

【図5】

5

【 図 4 】

4

【 义 6 】

図 6

【図7】

【図9】

【図8】

図8

【図10】

## フロントページの続き

(72)発明者 高田 啓祐

東京都小平市上水本町5丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

(72)発明者 渡邊 一希

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

(72)発明者 山本 師久

東京都小平市上水本町5丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

(72)発明者 松下 一浩

東京都小平市上水本町5丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

F ターム(参考) 2C005 MA01 NA02 NA09 NB03 TA21 TA22

5B035 AA00 AA11 BB09 CA12 CA25 CA31 CA38