(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6679317号

(P6679317)

(45) 発行日 令和2年4月15日(2020.4.15)

(24) 登録日 令和2年3月23日(2020.3.23)

(51) Int.Cl.

G09G 3/36 (2006.01)

G09G 3/20 (2006.01)

F 1

G09G 3/36

G09G 3/20

G09G 3/20

G09G 3/20

G09G 3/20

請求項の数 13 (全 29 頁) 最終頁に続く

(21) 出願番号

特願2016-4077 (P2016-4077)

(22) 出願日

平成28年1月13日(2016.1.13)

(65) 公開番号

特開2017-125903 (P2017-125903A)

(43) 公開日

平成29年7月20日(2017.7.20)

審査請求日

平成30年10月30日(2018.10.30)

(73) 特許権者 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74) 代理人 110001737

特許業務法人スズエ国際特許事務所

(72) 発明者 仲尾 貴之

東京都港区西新橋三丁目7番1号 株式会

社ジャパンディスプレイ内

(72) 発明者 島 武弘

東京都港区西新橋三丁目7番1号 株式会

社ジャパンディスプレイ内

審査官 武田 悟

最終頁に続く

(54) 【発明の名称】信号供給回路及び表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の副画素からなる画素にメモリを有する表示装置に用いられ、動作モード制御するモード制御回路を含む信号供給回路であって、

前記モード制御回路により、

前記複数の副画素用のデジタルデータを前記メモリに供給する、第1モードと第2モードとに選択的に切り替えられ、

第1モードは、外部からn個の前記副画素に対応する第1映像データを受け取り、前記第1映像データに基づいてn個の前記副画素用のデジタルデータを前記メモリに供給するモードであり、

第2モードは、外部から前記n個よりも少ないm個の前記副画素に対応する第2映像データを受け取り、前記第2映像データに基づいてn個の前記副画素用のデジタルデータを前記メモリに供給するモードであり、

前記第1映像データ及び前記第2映像データはシリアルデータであり、前記シリアルデータを前記複数の副画素に対応するデジタルデータにパラレル変換するパラレル変換部を有し、

前記パラレル変換部は、n個のラッチ回路と、

前記ラッチ回路のラッチタイミングを制御するn個の制御レジスタと、を備え、

前記第1モードのときn個の前記制御レジスタで、前記制御レジスタの転送データの巡回路を構成し、前記第2モードのときm個の制御レジスタで、前記制御レジスタの転送デ

10

20

ータの巡回路を構成する、信号供給回路。

**【請求項 2】**

前記モード制御回路が、前記第1映像データと前記第2映像データを受け取ることに先行して、モード制御データを受け取る、請求項1記載の信号供給回路。

**【請求項 3】**

前記n個のラッチ回路のパラレル出力データを前記n個の前記複数の副画素用のデジタルデータに変換するラインデータ変換回路と、

を備える、請求項1又は2に記載の信号供給回路。

**【請求項 4】**

前記モード制御回路が、前記第2モードのとき前記nの制御レジスタのうちの一部の制御レジスタの動作を非アクティブに切り替える、請求項1ないし3のいずれか1項に記載の信号供給回路。 10

**【請求項 5】**

前記第1モードの前記第1映像データは、赤、緑、青、白用の映像データから成り、

前記第2モードの前記第2映像データは、赤、緑、青用の映像データから成り、

前記第2モードでは前記ラインデータ変換回路が、前記赤、緑、青用の映像データから、白用の映像データを生成する、請求項3と請求項4のいずれか1項に記載の信号供給回路。

**【請求項 6】**

前記第1モードの前記第1映像データは、赤、緑、青、白用の映像データ又はシアン、マゼンタ、黄、白用の映像データから成る、

請求項1と請求項2のいずれか1項に記載の信号供給回路。 20

**【請求項 7】**

前記第1モード又は前記第2モードにおいて、前記パラレル変換部は、前記n個の前記第1映像データ又は前記m個の前記第2映像データを1個の映像データ単位に変換する、請求項1に記載の信号供給回路。

**【請求項 8】**

画素にメモリを有する表示装置であって、

前記画素を構成する複数の副画素と、

前記複数副画素にデジタルデータを供給する信号供給回路と、

前記デジタルデータが供給される、前記画素に配置されたメモリと、 30

前記メモリに記憶された前記デジタルデータによって電位が供給される画素電極と、を備え、

前記信号供給回路は、第1モードと第2モードとを有し、

第1モードは、外部からn個の前記副画素の第1映像データを受け取り、前記第1映像データに基づいてn個の前記副画素用のデジタルデータを前記メモリに供給するモードであり、

第2モードは、外部から前記n個よりも少ないm個の前副画素に対応する第2映像データを受け取り、前記第2映像データに基づいてn個の前記複数の副画素用のデジタルデータを前記メモリに供給するモードであり、 40

前記第1映像データ及び前記第2映像データはシリアルデータであり、前記シリアルデータを前記複数の副画素に対応するデジタルデータにパラレル変換するパラレル変換部を有し、

前記パラレル変換部は、n個のラッチ回路と、

前記ラッチ回路のラッチタイミングを制御するn個の制御レジスタと、を備え、

前記第1モードのときn個の前記制御レジスタで巡回路を構成し、前記第2モードのときm個の制御レジスタで巡回路を構成する、

表示装置。

**【請求項 9】**

前記複数の副画素としての第1副画素と第2副画素と第3副画素と第4副画素と、を備 50

え、

前記第1モードは、前記第1副画素と前記第2副画素と前記第3副画素と前記第4副画素に対応した前記第1映像データを受け取り、前記第1映像データに基づいて前記第1副画素と前記第2副画素と前記第3副画素と前記第4副画素用のデジタルデータを前記メモリに供給するモードであり、

前記第2モードは、前記第1副画素と前記第2副画素と前記第3副画素に対応した前記第2映像データを受け取り、前記第2映像データに基づいて前記第1副画素と前記第2副画素と前記第3副画素と前記第4副画素用のデジタルデータを前記メモリに供給するモードである、請求項8に記載の表示装置。

#### 【請求項10】

10

前記複数の副画素に対応するデジタルデータを前記メモリに供給する第3モードをさらに有し、

前記第3モードは、外部から前記第2映像データを受け取り、前記第2映像データに基づいてm個の前記副画素のデジタルデータを前記メモリに供給するモードである、請求項8と請求項9のいずれかに記載の表示装置。

#### 【請求項11】

前記複数の副画素に対応するデジタルデータを前記メモリに供給する第3モードをさらに有し、

前記第3モードは、外部から前記第2映像データを受け取り、前記第2映像データに基づいて一部の前記複数の副画素のデジタルデータを供給するモードであり、

20

前記第3モードは、前記第1副画素と前記第2副画素と前記第3副画素に対応した前記第2映像データを受け取り、前記第2映像データに基づいて前記第1副画素と前記第2副画素と前記第3副画素用のデジタルデータを前記メモリに供給するモードである、請求項8又は9に記載の表示装置。

#### 【請求項12】

外部からのビット制御信号によって、前記第2モードと前記第3モードとを切り替える、請求項10乃至11のいずれかに記載の表示装置。

#### 【請求項13】

外部からのラッチ数制御信号によって、前記第1モードと前記第2モードとを切り替える、請求項8乃至12のいずれかに記載の表示装置。

30

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

この実施形態は、信号供給回路及び表示装置に関する。

##### 【背景技術】

##### 【0002】

色表示可能な液晶表示装置において、表示パネルは、複数の画素が行方向（以下X方向と称する）と列方向（以下Y方向と称する）とに配列されている。X方向は、Y方向と交差する方向である。各画素は、それぞれカラーフィルタを備えており、赤色（R）副画素、緑色（G）副画素、及び青色（B）副画素として動作する。

40

##### 【0003】

近年、表示パネルにおいて、表示輝度を向上する手法が提案されている。一例として、R副画素、G副画素、B副画素、及び、白色（W）副画素が行方向に沿って所定の順番で配置され、この1セットが1つの画素を構成しているものがある。白色（W）副画素は、R副画素、G副画素、B副画素と比べて光の利用効率が高く、その透過率はR副画素、G副画素、B副画素の透過率の約3倍である。このために複合色単位画素の中に、白色画素（W）が利用されると、表示装置の表示輝度を上げることができる。

##### 【0004】

一方、表示パネルに映像データ（画像データと称してもよい）を供給する外部装置としては、R、G、B映像信号を出力するものが多い。つまり従来の外部装置は、W副画素の

50

ためのW映像信号を出力しない。これは、一般的には映像信号がR、G、B映像信号で構成されるからである。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2013-186294号公報

【特許文献2】特開2014-186283号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上記した新型の表示パネルと前記外部装置とを一体化した液晶表示装置が制作される場合、以下のような新たな課題が生じる。

(1) W映像信号を生成するために新たな変換回路を必要とする。また

(2) 変換回路を設けた場合1画素を構成する副画素が、3個(R、G及びB副画素)から4個(R、G、B及びW副画素)に増えるために、駆動に必要なデータ数が増加する。この結果、データの送信時間が長くなるとともに、消費電力も増大する。

(3) 勿論、データ処理プロセスも煩雑となる。

【0007】

そこで、本実施形態によれば、外部装置の性能に応じて、表示パネルに対するデータ供給方法を工夫することで、データ転送速度の高速化、消費電力の低減化を実現する信号供給回路及び表示装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

一実施形態は、画素にメモリを有する表示装置に用いられ、動作モードを制御するモード制御回路を含む信号供給回路であって、前記モード制御回路により、

前記画素を構成する複数の副画素用のデジタルデータを前記メモリに供給する、第1モードと第2モードとに選択的に切り替えられ、

第1モードは、外部からn個の前記副画素に対応する第1映像データを受け取り、前記第1映像データに基づいてn個の前記副画素のためのデジタルデータを前記メモリに供給するモードであり、

第2モードは、外部から前記n個よりも少ないm個の前記副画素に対応する第2映像データを受け取り、前記第2映像データに基づいてn個の前記副画素のためのデジタルデータを前記メモリに供給するモードである、信号供給回路を提供するものである。

【図面の簡単な説明】

【0009】

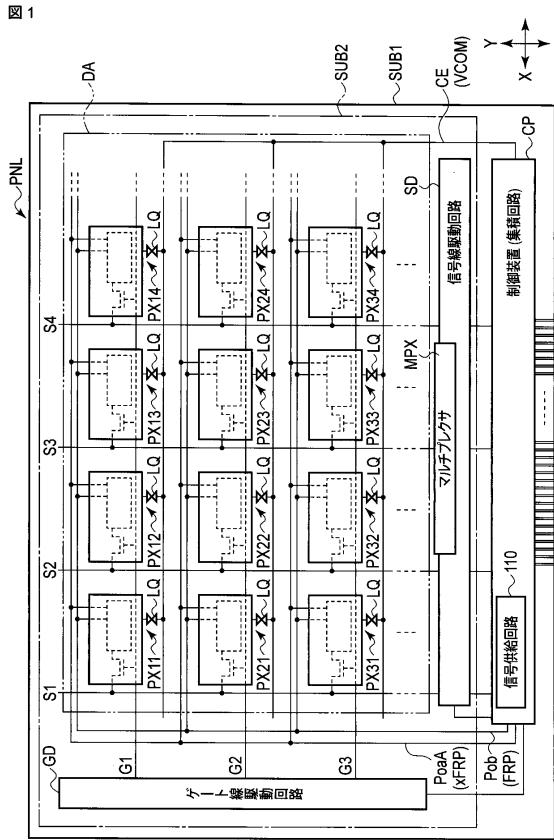

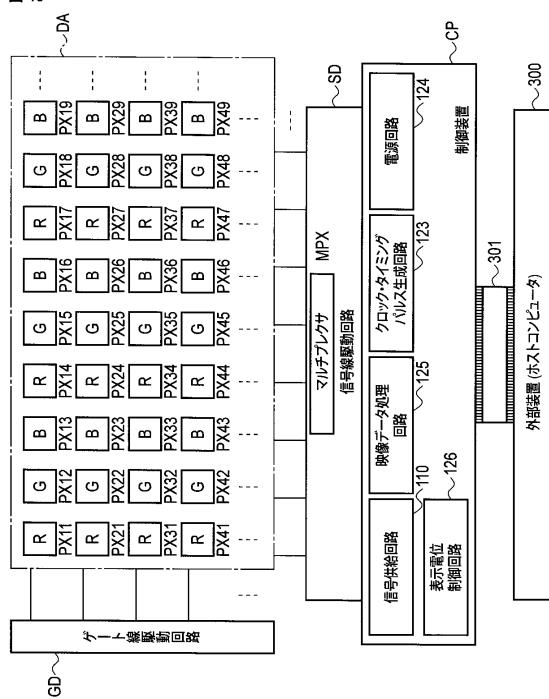

【図1】図1は一実施形態である信号供給回路及び表示装置の全体的構成を概略的に示す図である。

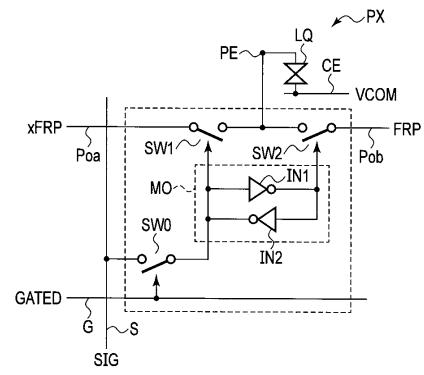

【図2A】図2Aはメモリを有する画素の基本構成を示す回路図である。

【図2B】図2Bはメモリを有する画素において、メモリにデータが書き込まれる際の動作例を示す図である。

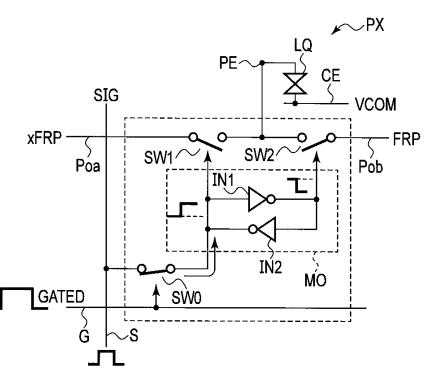

【図3】図3はメモリを有する画素にデータが保持された期間(表示期間)の状態例を示す図である。

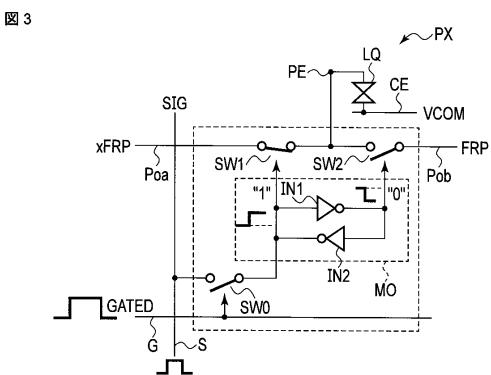

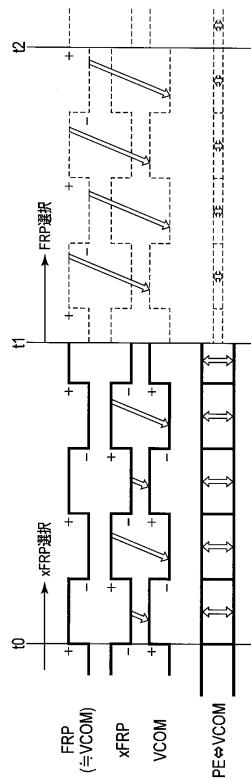

【図4】図4はメモリを有する画素にデータが保持された期間(表示期間)の動作例を説明するために示した波形及び保持データの例を示す図である。

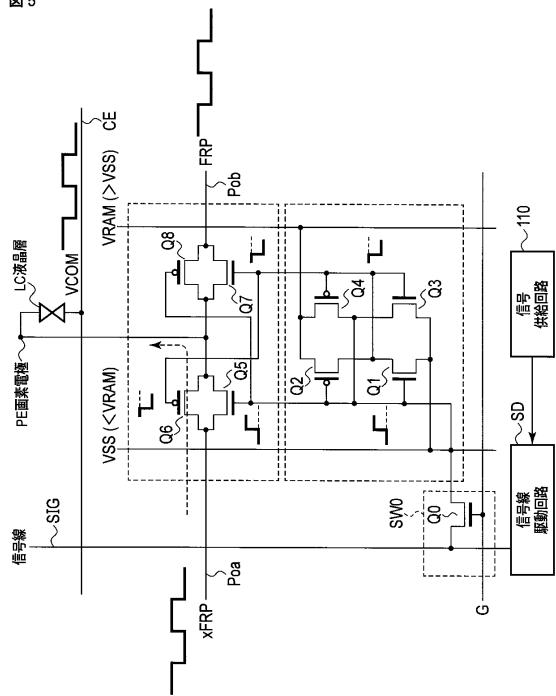

【図5】図5は図2Aの回路構成をさらに具体化して示す回路図である。

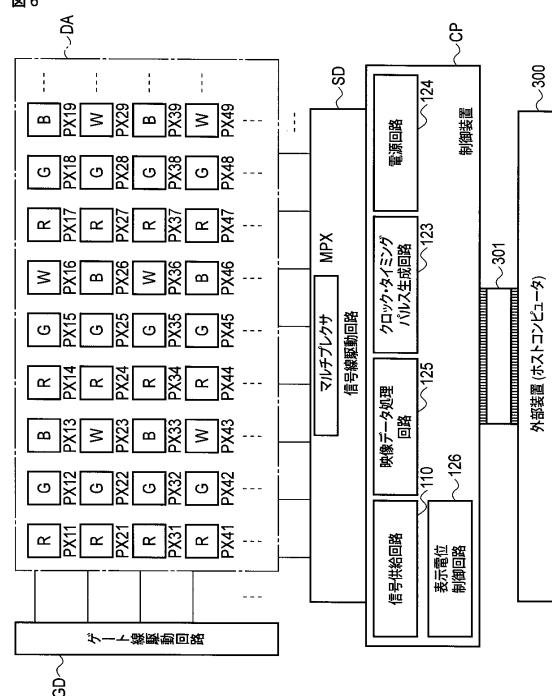

【図6】図6は、一実施形態である信号供給回路及び表示装置において、特に制御装置内の構成要素を示す図である。

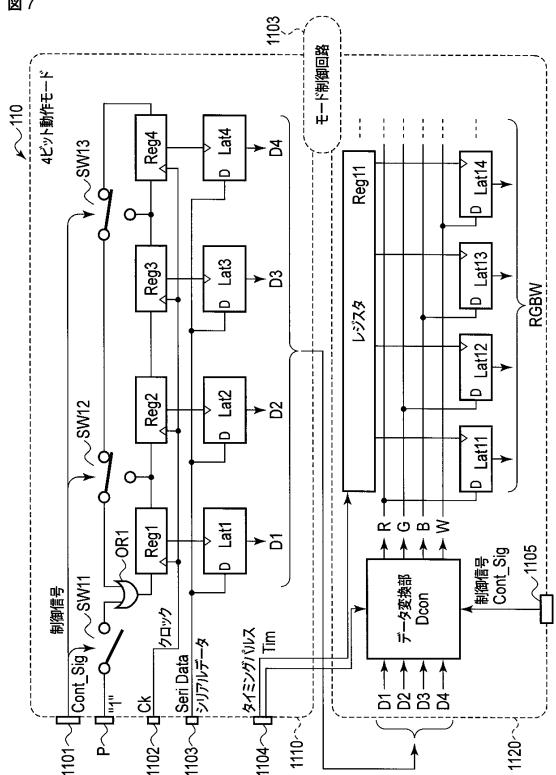

【図7】図7は、制御装置内の信号供給回路の第1の動作形態を示す図である。

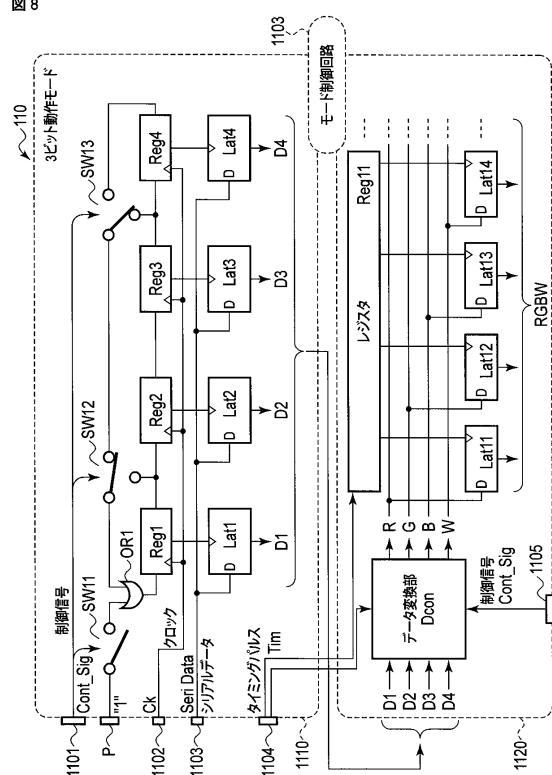

【図8】図8は、制御装置内の信号供給回路の第2の動作形態を示す図である。

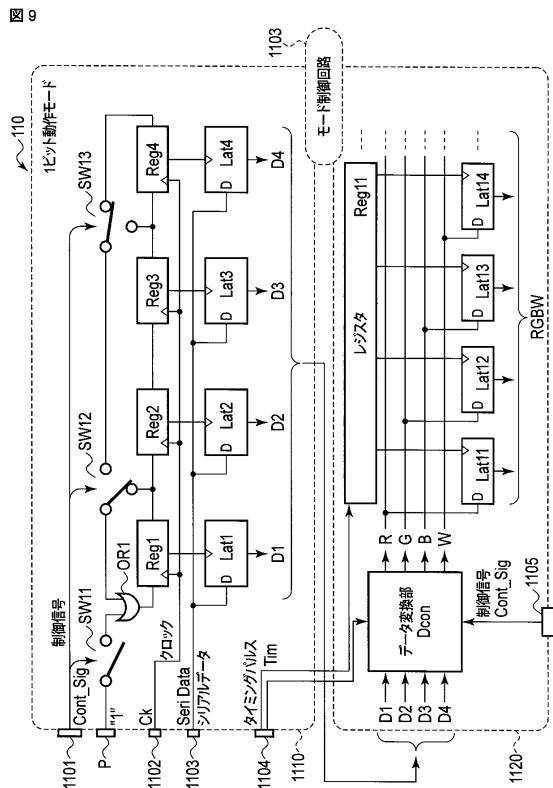

【図9】図9は、制御装置内の信号供給回路の第3の動作形態を示す図である。

10

20

30

40

50

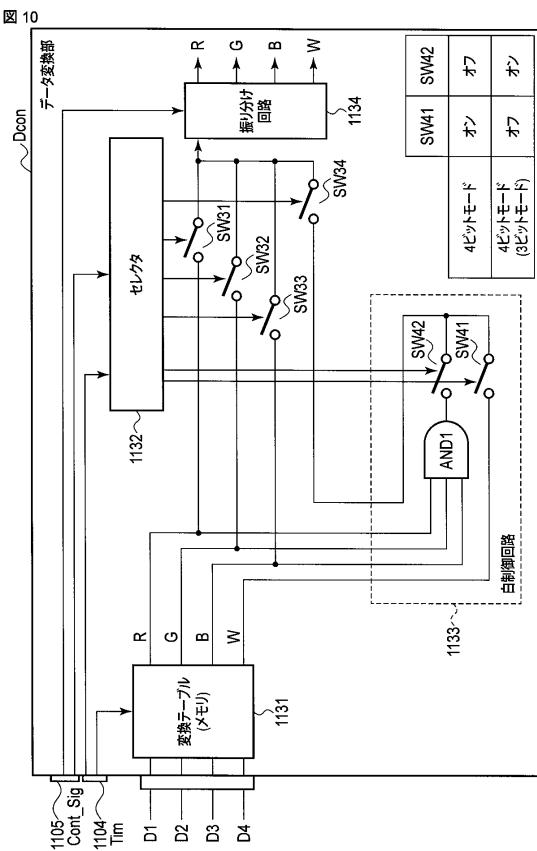

【図10】図10は、ライン変換回路内のデータ変換部の構成例を示す図である。

【図11A】図11Aは、信号供給回路が4ビットモード、3ビットモード、1ビットモード、その他で動作する場合の、シリアルパラレル変換されたデータD1に対する各スイッチSW31, SW32, SW33, SW34のオンオフ状態を示す図である。

【図11B】図11Bは、信号供給回路が4ビットモード、3ビットモード、1ビットモード、その他で動作する場合の、シリアルパラレル変換されたデータD2に対する各スイッチSW31, SW32, SW33, SW34のオンオフ状態を示す図である。

【図11C】図11Cは、信号供給回路が4ビットモード、3ビットモード、1ビットモード、その他で動作する場合の、シリアルパラレル変換されたデータD3に対する各スイッチSW31, SW32, SW33, SW34のオンオフ状態を示す図である。 10

【図11D】図11Dは、信号供給回路が4ビットモード、3ビットモード、1ビットモード、その他で動作する場合の、シリアルパラレル変換されたデータD1に対する各スイッチSW31, SW32, SW33, SW34のオンオフ状態を示す図である。

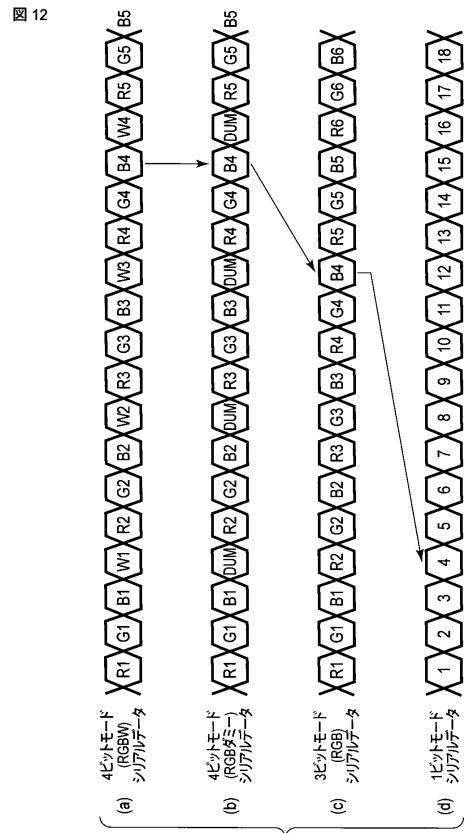

【図12】図12a - 図12dは、信号供給回路が4ビットモード、3ビットモード、1ビットモード、で動作する場合の、シリアルデータの転送速度を説明するために示した説明図である。

【図13】図13は、シリアルパラレル変換回路で用いられる制御データの一例を示す図である。

【図14A】図14Aは、ラインデータ生成回路1120で用いられる制御データの一例を示す図である。 20

【図14B】図14Bは、ラインデータ生成回路1120で用いられる制御データの他の例を示す図である。

【図15】図15は、表示装置の全体構成の他の実施形態を示し、図6の実施形態とはカラーフィルタの配列が異なる図である。

【図16】図16は、8ビット単位シリアル伝送方式の一例でありデータ配置例を示す図である。

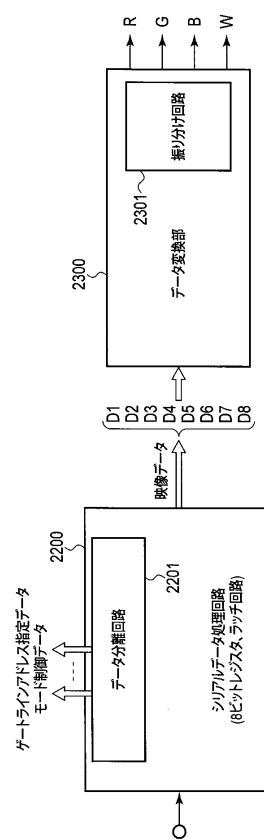

【図17】図17は、8ビット単位シリアル伝送方式のデータ入力に対応できるように構成した本発明（信号供給回路並びに表示装置）の他の実施形態を示すブロック構成図である。

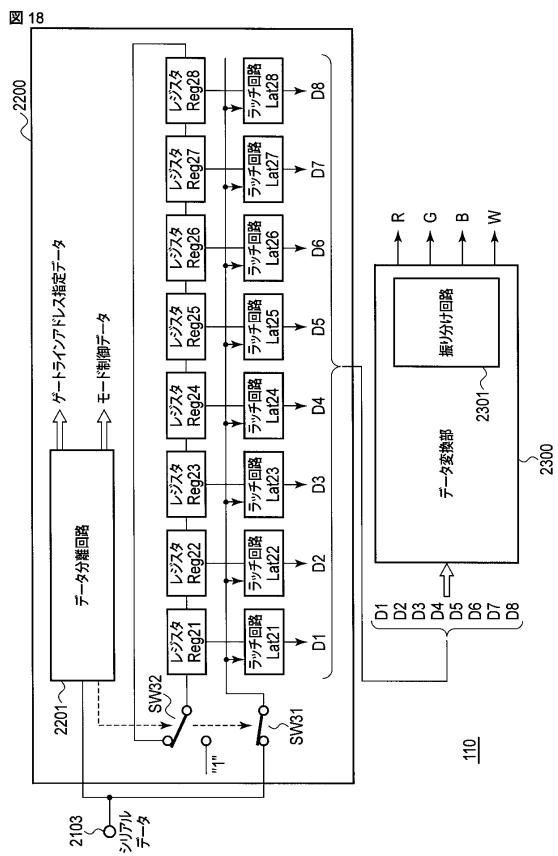

【図18】図18は、図17に示したシリアルデータ処理回路のシリアルパラレル変換回路の具体的な例を示す図である。 30

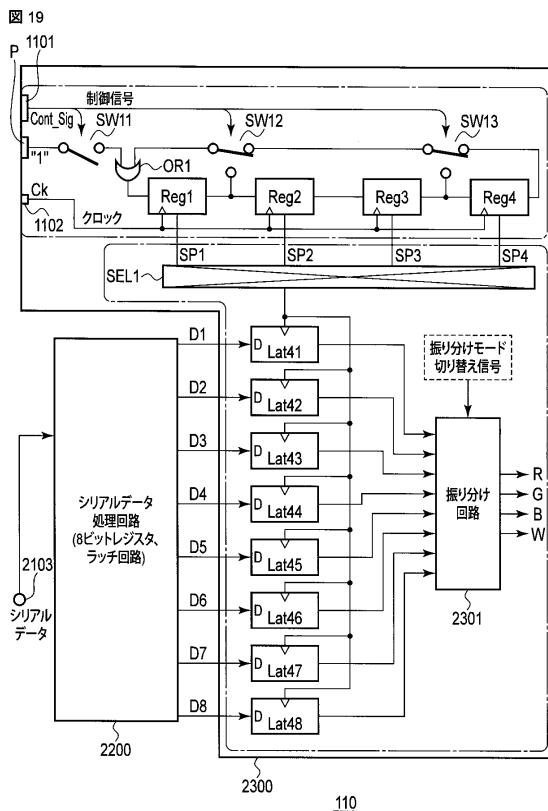

【図19】図19は、図17に示したデータ変換部の具体例を示す図であり、図8の変形例に相当する。

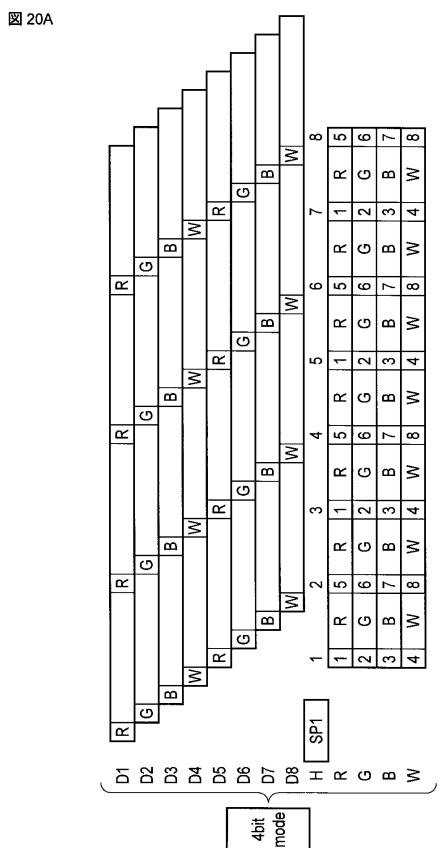

【図20A】図20Aは、図19に示したデータ変換部が4ビットモードで動作する際のデータラッチタイミングとラッチデータとの関係を示すタイミング説明図である。

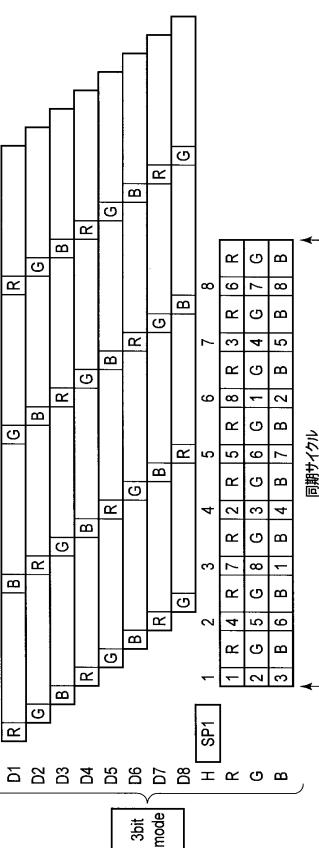

【図20B】図20Bは、図19に示したデータ変換部が3ビットモードで動作する際のデータラッチタイミングとラッチデータとの関係を示すタイミング説明図である。

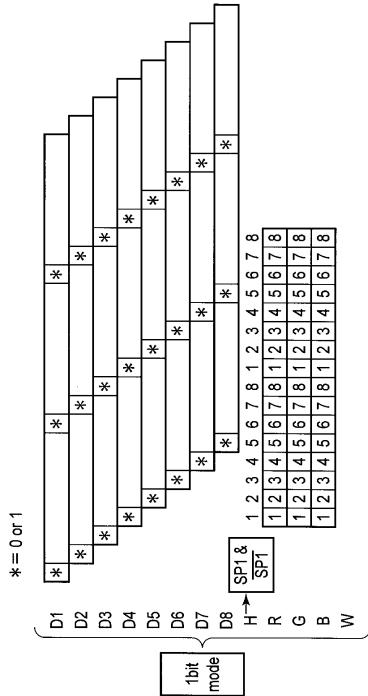

【図20C】図20Cは、図19に示したデータ変換部が1ビットモードで動作する際のデータラッチタイミングとラッチデータとの関係を示すタイミング説明図である。

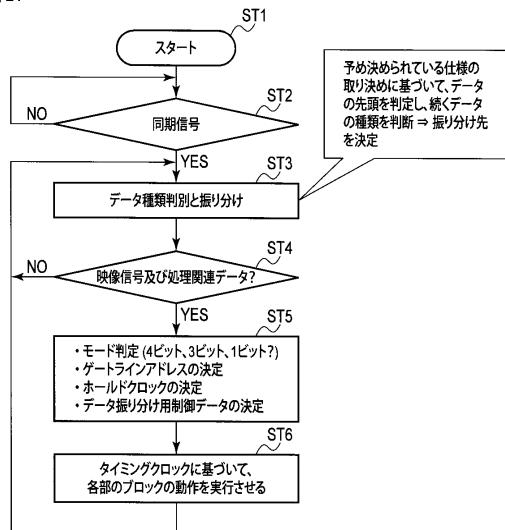

【図21】図21は、図17及び図18に示した信号供給回路の動作フローを簡単に示す図である。 40

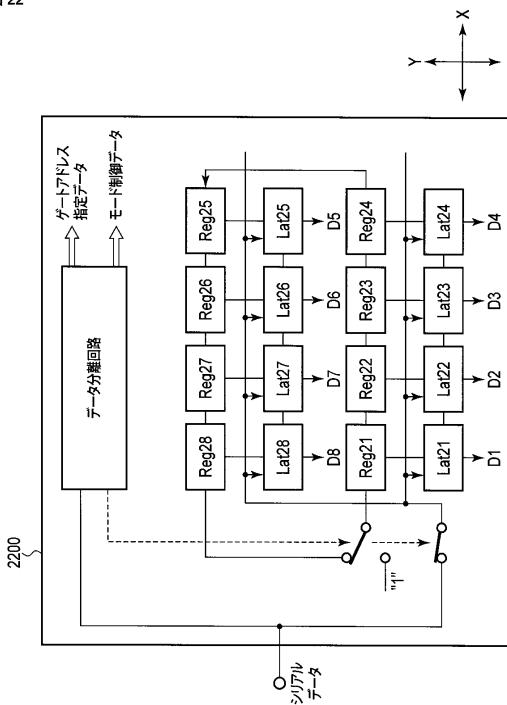

【図22】図22は、図18に示したシリアルデータ処理回路の他の構成例を示す図である。

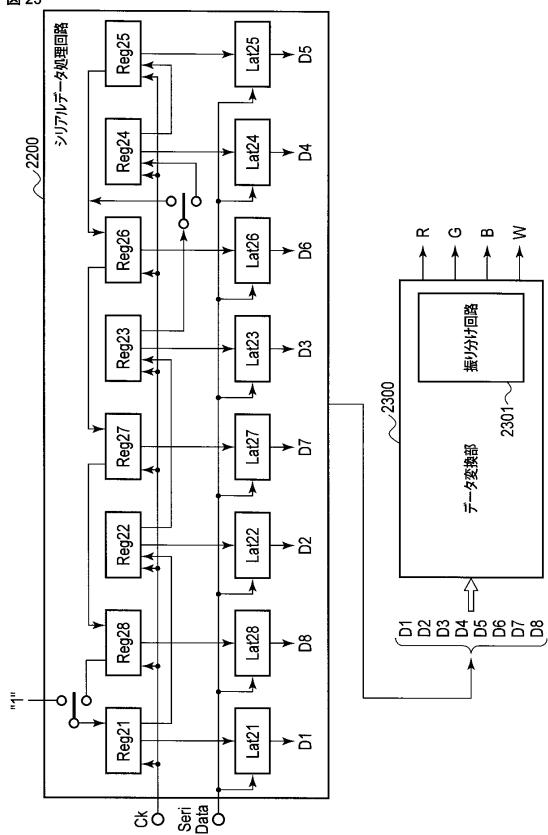

【図23】図23は、図18に示したシリアルデータ処理回路のさらに他の構成例を示す図である。

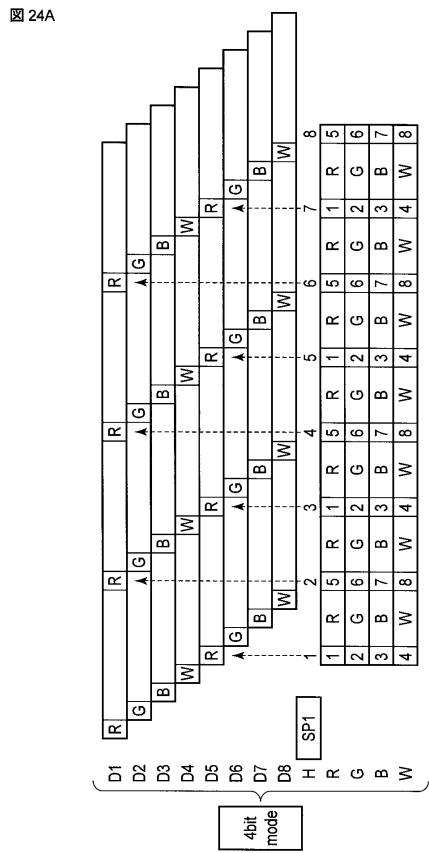

【図24A】図24Aは、図23に示したデータ変換部が4ビットモード（又は1ビットモード）で動作する際のデータラッチタイミングとラッチデータとの関係を示すタイミング説明図である。

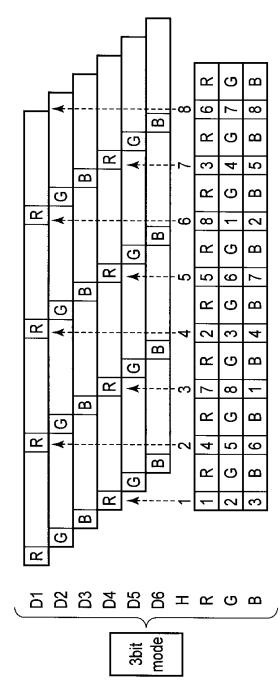

【図24B】図24Bは、図23に示したデータ変換部が3ビットモードで動作する際のデータラッチタイミングとラッチデータとの関係を示すタイミング説明図である。 50

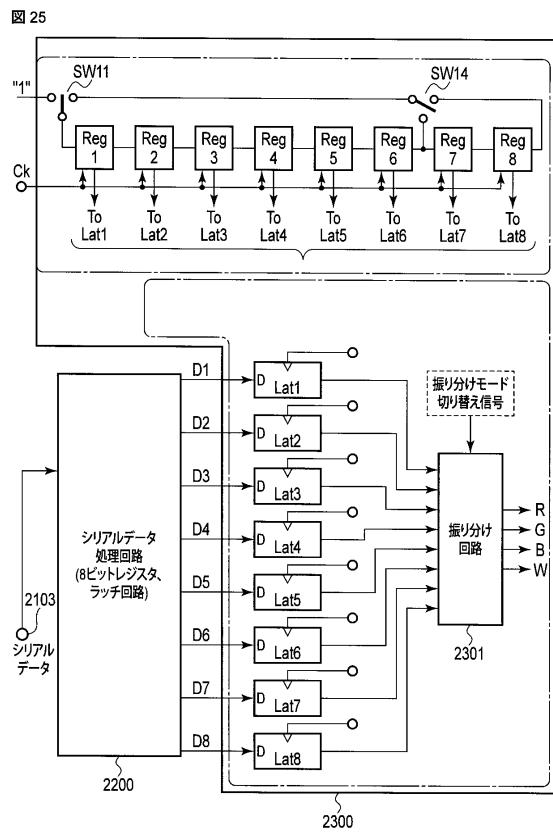

【図25】図25は、データ変換部のさらに他の実施形態を示す図である。

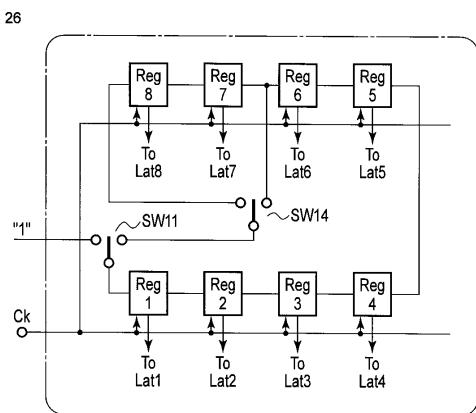

【図26】図26は、図25に示したラッチパルス生成部のさらに他の実施形態を示す図である。

**【発明を実施するための形態】**

**【0010】**

以下、実施の形態について図面を参照して説明する。実施形態の開示はあくまで一例に過ぎず、当業者において、発明の主旨を保っての適宜変更について容易に想到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は、説明をより明確にするため、実際の様子に比べて、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同一又は類似した機能を發揮する構成要素には同一の参照符号を付し、重複する詳細な説明を適宜省略することがある。また本明細書の以後の説明において、色フィルタR、G、B、W、副画素R、G、B、W、映像データR、G、B、色フィルタR、G、B、W、出力ラインR、G、B、W、信号R、G、B、Wを用いている。色フィルタR、G、B、Wは、赤、緑、青、及び白のフィルタを意味し、副画素R、G、B、Wは、色フィルタR、G、B、Wを有する副画素を意味する。また出力ラインR、G、B、Wは、副画素R、G、B、Wに振り分けられるべき映像データが出力されるラインを意味する。映像データR、G、Bは、副画素R、G、B、Wに振り分けられるべき映像データを意味する。

**【0011】**

図1は、表示パネルPNLの構成一例を概略的に示す図である。表示装置は、アクティブマトリクスタイルの表示パネルPNLを備えている。表示パネルPNLは、第1基板SUB1と、第1基板SUB1に対向配置された第2基板SUB2と、第1基板SUB1と第2基板SUB2との間に保持された液晶層LQと、を備える。第2基板SUB2は、一点鎖線で示している。

表示エリアDAは、第1基板SUB1と第2基板SUB2との間に液晶層LQが保持された領域に相当し、例えば、四角形状であり、この領域にはマトリクス状に配置された複数の副画素PX(PX11, PX12, ...)が配置されている。

**【0012】**

第1基板SUB1は、表示エリアDAにおいて、第1方向Xに沿って延出した複数のゲート線G(G1～Gn)、第1方向Xのゲート線Gに交差し、第2方向Yに沿って延出した複数の信号線S(S1～Sm)を備えている。

各ゲート線G(G1～Gn)は、表示エリアDAの外側に引き出され、ゲート線駆動回路(第1駆動回路)GDに接続されている。各信号線S(S1～Sm)は、表示エリアDAの外側に引き出され、ソース線駆動回路(第2駆動回路)SDに接続されている。第1駆動回路GD及び第2駆動回路SDは、例えばその少なくとも一部が第1基板SUB1上に形成され、制御装置(駆動ICチップ或いは液晶ドライバと称される場合もある)CPと接続されている。

**【0013】**

第2駆動回路SDは、制御装置CPから受け取った画素信号を、この画素信号が対応する信号線を介して対応する副画素に供給するために、マルチプレクサMPXを備えている。つまりマルチプレクサMPXは、受け取った画素信号を適切な信号線に出力する。

制御装置CPは、第1駆動回路GD及び第2駆動回路SDを制御するために、クロック及びタイミングパルス生成回路(コントローラ或いはシーケンサと称してもよい)を内蔵し、表示パネルPNLを駆動するのに必要な信号を供給する信号供給源として機能する。制御装置CPは、信号供給回路110を含む。信号供給回路110は、第2駆動回路SDに映像データを与えるとき、映像データのタイプに応じて、動作モードを切り替えるモード制御回路(後述する)を含む。映像データのタイプとは、後で詳しく説明するが、映像データが例えば、赤(R)、緑(G)、青(B)の映像データである場合、赤(R)、緑(G)、青(B)の映像データである場合、赤(R)、緑(G)、青(B)

10

20

30

40

50

、ダミー( D U M )の映像データである場合、或いは単なる1ビットの映像データである場合などがある。

図示した例では、制御装置 C P は、表示パネル P N L の表示エリア D A の外側において、第1基板 S U B 1 上に実装されている。

#### 【 0 0 1 4 】

共通電極 C E は、第2基板 S U B 2 に透明材質で形成され、表示エリア D A の全域に対応しており、例えば、複数の副画素 P X に対して共通に形成されている。共通電極 C E は、表示エリア D A の外側に引き出され、制御装置 C P 内部の給電部に接続されている。給電部には、一定の共通電圧を出力する。

#### 【 0 0 1 5 】

複数の副画素 P X には、色フィルタが所定の規則で配列されている。色フィルタは、液晶層 L Q を挟むように画素電極に対向し、第2基板 S U B 2 に形成されている。

図 2 A は、メモリを有する前記副画素 P X (又は画素)の構成を示している。この副画素 P X において、信号線 S にスイッチ S W 0 の一端が接続され、このスイッチ S W 0 の他端がメモリ M 0 に接続されている。メモリ M 0 は、例えばインバータ I N 1、I N 2 を有し、このインバータ I N 1、I N 2 は逆方向に並列接続されている。インバータ I N 1 の入力端子(インバータ I N 2 の出力端子)は、スイッチ S W 1 の制御端子に接続されている。またインバータ I N 1 の出力端子(インバータ I N 2 の入力端子)は、スイッチ S W 2 の制御端子に接続されている。スイッチ S W 1 の入力端子は、第1の信号ライン P o a に接続され、出力端子は、液晶層に形成された表示素子の画素電極 P E に接続されている。またスイッチ S W 2 の入力端子は、第2の信号ライン P o b に接続され、出力端子は、前記画素電極 P E に接続されている。第1の信号ライン P o a には、第1の信号(表示用信号) × F R P が供給され、第2の信号ライン P o b には、第2の信号(非表示用信号) F R P が入力している。これらの第1の信号 × F R P と第2の信号 F R P は、互いに逆位相の関係となる交流信号であり、図 1 で説明した制御装置 C P で生成されている。前記画素電極 P E に対向する共通電極 C E には、制御装置 C P から共通信号 V C O M が供給されている。共通信号 V C O M は、第2の信号 F R P と同位相の信号交流信号である。

#### 【 0 0 1 6 】

図 2 B は、上記した副画素 P X のメモリ M 0 にデータ“1”が書き込まれる際の動作例を示している。ゲート線 G にゲートパルス G A T E D が供給されるとスイッチ S W 0 がオンし、またこのとき信号線 S に信号 S I G (データ“1”)が出力されると、メモリ M 0 にデータ“1” (= ハイレベル) が書き込まれ保持される。この時、インバータ I N 1 は、入力を反転するので、このインバータ I N 1 の出力は“0” (= ローレベル) となる。インバータ I N 2 の入力はローレベルであるからこのインバータ I N 2 の出力はハイレベルとなる。ここで、スイッチ S W 0 がオフされると、メモリ M 0 は、データ“1”を保持する。

#### 【 0 0 1 7 】

即ち、図 3 に示すように、スイッチ S W が 0 オフし、メモリ M 0 にデータ“1”が保持されると、メモリ M 0 の出力によりスイッチ S W 1 がオン、スイッチ S W 2 がオフとなる。この結果、表示素子(液晶層) L Q の画素電極 P E には、第1の信号 × F R P が印加され、共通電極 C E には共通信号 V C O M が印加される。

#### 【 0 0 1 8 】

図 4 は上記した副画素 P X において、画素電極 P E と共通電極 C E と間に生じる電位差の変化を示している。図 4 の時間 t 0 ~ t 1 では、画素電極 P E に第1の信号 × F R P が印加され、共通電極 C E に共通信号 V C O M が印加されている様子を示している。第1の信号 × F R P と共に共通信号 V C O M とは、逆位相の関係にあるから、画素電極 P E と共通電極 C E の間には、高い電位差が生じている。この時、表示素子は表示状態を形成する。ここで、メモリ M 0 にデータ“0”が保持されたとする。すると、スイッチ S W 1 がオフし、スイッチ S W 2 がオンする。このため、図 4 の時間 t 1 ~ t 2 に示すように、画素電極 P E に第2の信号 F R P が印加され、共通電極 C E に共通信号 V C O M が印加される。

10

20

30

40

50

このときは第2の信号F R Pと共に信号V C O Mとは、同位相の関係にあるから、画素電極P Eと共に電極C Eの間は、低い電位差となる。この時、表示素子は非表示状態を形成する。

#### 【0019】

図5は、図2A、図2B、図3に示した副画素の回路構成をさらに詳しく示している。スイッチS W 0は、例えば薄膜トランジスタQ 0で構成されている。またメモリM 0は、薄膜トランジスタQ 1、Q 2、Q 3及びQ 4で構成されている。スイッチS W 1は、薄膜トランジスタQ 5、Q 6で構成され、スイッチS W 2は、薄膜トランジスタQ 7、Q 8で構成されている。メモリM 0にデータ“1”が書き込まれると、薄膜トランジスタQ 1、Q 4がオンし、薄膜トランジスタQ 2、Q 3がオフする。メモリM 0の出力により、薄膜トランジスタQ 5、Q 6がオンし、薄膜トランジスタQ 7、Q 8がオフする。メモリM 0にデータ“0”が書き込まれると、薄膜トランジスタQ 2、Q 3がオフし、薄膜トランジスタQ 1、Q 4がオフする。メモリM 0の出力により、薄膜トランジスタQ 5、Q 6がオフし、薄膜トランジスタQ 7、Q 8がオンする。

#### 【0020】

図6は、一実施形態である信号供給回路及び表示装置において、特に制御装置C P内の構成要素を示している。また表示パネルP N Lの表示エリアD Aには、副画素P Xに対応する色フィルタの配置例を示している。なお色フィルタの配置例は、図に示す配置順序だけでなく種々の配置例があることは勿論である。この配置例は、例えば第1列が色フィルタR、第2列が色フィルタGである。そして第3の列は色フィルタBとWが交互に配置されている。さらに第4列がR、第5列がGである。そして第6の列は色フィルタWとBが交互に配置されている。このような色フィルタ配置例が、X方向へ繰り返し配置されている。ここで第3列、第6列、第9列を行方向(X方向)へ見ると、色フィルタW、B、W、B、…のように色フィルタWとBが繰り返し配列されている。

#### 【0021】

副画素の好みの他の配置例としては、4色の副画素R、G、B、Wをスクウェア状に配列したものである。具体的にはP X 1 1、P X 3 1、P X 1 3をRとし、P X 2 1、P X 4 1、P X 2 3をGとし、P X 1 2、P X 3 2、P X 1 4をBとし、P X 2 2、P X 4 2、P X 2 4をWとしても良い。

#### 【0022】

制御装置C Pは、信号供給回路1 1 0の他に、電源回路1 2 4、クロック及びタイミングパルス生成回路1 2 3、映像データ処理回路1 2 5、表示電位制御回路1 2 6などを含む。電源回路1 2 4は、外部のバッテリーから受け取った電源電圧を用いて種々の電圧を生成する。クロック及びタイミングパルス生成回路1 2 3は、制御装置C P内部及びゲート線駆動回路G D、信号線駆動回路S Dなどで用いる各種のクロック、種々のタイミング信号を生成する。

#### 【0023】

制御装置C Pは、外部装置(ホストコンピュータと称してもよい)3 0 0からフレキシブル基板3 0 1に形成された接続ラインを介して映像信号、同期信号、制御データ等を受け取る。映像データ、同期信号は映像データ処理回路1 2 5に入力されて、表示パネルP N Lに供給するための映像データに変換される。制御データは、クロック及びタイミングパルス生成回路1 2 3に取り込まれ、表示装置の動作を制御するために用いられる。制御装置C P内の表示電位制御回路1 2 6は、白、黒反転点灯やネガ、ポジ反転点灯などの特殊表示状態を得る際に、図2A、図2B、図3で説明した第1の信号×F R P又は第2の信号F R Pを変化させて画素電極に印加してもよい。

#### 【0024】

図7は、信号供給回路1 1 0の具体的構成例を示している。信号供給回路1 1 0は、シリアルデータとして入力する映像データをパラレル変換するシリアルパラレル変換回路1 1 1 0と、パラレル変換された映像データを収集して、例えば1ライン分の映像データを準備するラインデータ生成回路1 1 2 0とを有する。上記したシリアルパラレル変換回

10

20

30

40

50

路 1110 は、その動作モードが切り替わることが可能であり、このシリアルパラレル変換回路 1110 の動作モードを切り替える回路としてモード制御回路 1103 が備えられている。

#### 【0025】

シリアルパラレル変換回路 1110 は、モード制御回路 1103 からの第 1 の制御データ Cont\_Sig が入力する入力端子 1101 を有する。また、ラインデータ生成回路 1120 もモード制御回路 1103 からの第 2 の制御データ Cont\_Sig が入力する入力端子 1105 を有する。

シリアルパラレル変換回路 1110 は、スイッチ SW11、オア回路 OR1 を有する。初期値入力端子 P からデータ “1” が入力され、スイッチ SW11 が制御データ Cont\_Sig によりオンされた場合、レジスタ Reg1 にデータ “1” がラッチされる。レジスタ Reg1 にデータ “1” がラッチされた後は、スイッチ SW11 はオフされる。レジスタ Reg1 の出力は、レジスタ Reg2 に入力可能であり、レジスタ Reg2 の出力は、レジスタ Reg3 に入力可能であり、レジスタ Reg3 の出力は、レジスタ Reg4 に入力可能に構成されている。レジスタ Reg1 に入力されたデータ “1” は、入力端子 1102 に入力するクロックにより、順次レジスタ Reg2、レジスタ Reg3、レジスタ Reg4 に順次転送される。なお複数のレジスタが直列接続された回路は、レジスタ直列回路或いはカウンタ回路と称されてもよい。

#### 【0026】

しかし、このシリアルパラレル変換回路 1110 は、スイッチ SW12、SW13 を有し、転送データの巡回路が変更可能となっている。スイッチ SW12 は、スイッチ SW13 の出力又はレジスタ Reg1 の出力のいずれか一方を選択し、オア回路 OR1 に入力することができる。スイッチ SW13 は、レジスタ Reg3 の出力、又はレジスタ Reg4 の出力のいずれかを選択して、スイッチ SW12 に入力することができる。スイッチ SW12、SW13 の選択状態は、モード制御回路 1103 からの制御データ Cont\_Sig により制御される。

#### 【0027】

レジスタ Reg1、Reg2、Reg3、Reg4 の出力は、それぞれラッチ回路 Lat1、Lat2、Lat3、Lat4 のラッチタイミングを決めるラッチパルス入力端子に供給される。ラッチ回路 Lat1、Lat2、Lat3、Lat4 のデータ入力端子には、入力端子 1103 からシリアル映像データが入力される。このシリアル映像データは、図 6 に示した画像データ処理回路 125 から与えられる。図 7 のスイッチ SW12、SW13 の状態の場合、この信号出力回路 110 は、動作モードが 4 ビットモードである。

#### 【0028】

今、シリアルデータが、赤 (R)、緑 (G)、青 (B)、白 (W) の映像データであるとすると、これらの映像データは、ラッチ回路 Lat1、Lat2、Lat3、Lat4 に順次ラッチされ、赤 (R) がデータ D1、緑 (G) がデータ D2、青 (B) がデータ D3、白 (W) がデータ D4 として並列データとして出力される。シリアルデータは、赤 (R)、緑 (G)、青 (B)、白 (W) の映像データが繰り返して入力するので、レジスタ Reg1、Reg2、Reg3、Reg4 の出力により、それぞれラッチ回路 Lat1、Lat2、Lat3、Lat4 に赤 (R)、緑 (G)、青 (B)、白 (W) の映像データが順次ラッチされ、このラッチ動作が巡回される。

ラッチ回路 Lat1、Lat2、Lat3、Lat4 の出力データ D1、データ D2、データ D3、データ D4 は、ラインデータ生成回路 1120 のデータ変換部 Dcon に入力されて、R、G、B、W 信号に変換される。

#### 【0029】

なお副画素が 1 ビット記憶メモリを有するものであれば、データ変換部 Dcon は省略、或いはタイミングを調整するための単なるバッファ回路として存在する。

ラインデータ生成回路 1120 のデータ変換部 Dcon 及びレジスタ Reg11 は、入力端子 1104 からのタイミングパルス Tim によりデータの出力タイミング及びデータの

10

20

30

40

50

転送タイミングが制御される。データ変換部 D<sub>con</sub> から出力された、R、G、B、W 信号は、レジスタ R<sub>eg 11</sub>からのラッチパルスに基づいて、ラッチ回路 L<sub>at 11</sub>、L<sub>at 12</sub>、L<sub>at 13</sub>、L<sub>at 14</sub>・・・にラッチされる。図 7 では 4 つのラッチ回路 L<sub>at 11</sub>、L<sub>at 12</sub>、L<sub>at 13</sub>、L<sub>at 14</sub>を示しているが、実際には、1 水平ライン分のデータをラッチするラッチ回路が設けられている。

#### 【0030】

図 7 は、動作モードが 4 ビットモードであるが、この動作モードは、例えば、外部装置 300 が赤 (R)、緑 (G)、青 (B)、白 (W) の映像データを出力する場合に有効である。または、外部装置 300 或いは映像データ処理回路 125 が白 (W) 或いはダミーの映像データを生成して出力する場合に有効である。

10

#### 【0031】

図 8 は、信号供給回路 110 が、モード制御回路 1103 の制御に基づいて、動作モードが 3 ビットモードに切り替わったときの状態を示している。図 7 と同一部分には同一符号を付している。図 8 の状態が図 7 の状態と異なる部分は、スイッチ SW13 が、レジスタ R<sub>eg 3</sub> の出力を選択してレジスタ R<sub>eg 1</sub> にフィードバックしている点である。この動作モードは、例えば、外部装置 300 が赤 (R)、緑 (G)、青 (B) の映像データを出力する場合に有効である。この場合、データ D<sub>4</sub> が例えばオールゼロであるために、オールゼロを利用し、データ変換部 D<sub>con</sub> で白 (W) の映像データに代わる W データを生成することができる。データ変換部 D<sub>con</sub> は、入力端子 1105 から入力する制御データ C<sub>ont\_Sig</sub> により、現在の入力映像データのモードを判断することができる。このモードではレジスタ R<sub>eg 4</sub> が非アクティブである。

20

#### 【0032】

図 9 は、動作モードが 1 ビットモードに切り替わったときの状態を示している。図 7、図 8 と同一部分には同一符号を付している。図 9 の状態が、図 7、図 8 の状態と異なる部分は、スイッチ SW12 が、レジスタ R<sub>eg 1</sub> の出力を選択してレジスタ R<sub>eg 1</sub> にフィードバックしている点である。つまり、パラレル変換部は、外部からのデータを 1 ビット単位のデータにパラレル変換をしている。この場合、データ変換部 D<sub>con</sub> に入力するデータ D<sub>2</sub>、D<sub>3</sub>、D<sub>4</sub> は、ゼロである。データ変換部 D<sub>con</sub> は、動作モードを制御する制御データ C<sub>ont\_Sig</sub> に基づいて、任意に D<sub>2</sub>、D<sub>3</sub>、D<sub>4</sub> に関連した G、B、W の映像データを出力することができる。例えば、全画面が黒、或いは白、或いはグレー、或いは単色になるようなデータを出力することができる。この出力データに基づく表示形態は、データ変換部 D<sub>con</sub> に内蔵可能なデータ変換テーブルと、制御データ C<sub>ont\_Sig</sub> により任意に設定可能である。このモードではレジスタ R<sub>eg 2</sub>、R<sub>eg 3</sub>、R<sub>eg 4</sub> が非アクティブである。

30

#### 【0033】

図 10 には、先のデータ変換部 D<sub>con</sub> の内部構成の一例を示している。データ変換部 D<sub>con</sub> は、変換テーブル (メモリ) 1131 を有し、変換テーブル (メモリ) 1131 は、入力データ D<sub>1</sub>、D<sub>2</sub>、D<sub>3</sub>、D<sub>4</sub> をそれぞれ表示部の設計に対応したビット数の映像データ R、G、B、W に変換することができる。またこの変換テーブル 1131 は交換できるように構成されてもよい。図 2A - 図 3 で示したように副画素が 1 ビットのデータを保持する動作を行う場合、入力データ D<sub>1</sub>、D<sub>2</sub>、D<sub>3</sub>、D<sub>4</sub> に対応する出力もそれぞれ 1 ビットとなる。

40

#### 【0034】

変換テーブル (メモリ) 1131 から出力された、映像データ R、G、B、W は、それぞれスイッチ SW31、SW32、SW33、SW34 にて選択されて、振り分け回路 1134 に入力される。振り分け回路 1134 は、入力端子 1105 からの制御データに基づき、映像データ R、G、B、W が適切な信号線に出力 (適切なカラーフィルタに割り当てる) されるように信号を振り分ける。この処理により、例えば、図 6 に示したようなカラーフィルタ R、G、B、W を有する副画素のメモリに対して、対応する映像データ R、G、B、W が入力される。したがって、振り分け回路 1134 は一時的にデータを保持

50

するバッファを含む場合もある。映像データR、G、Bは、それぞれ、図9に示したラッチ回路Lat11、Lat12、Lat13、Lat14……のデータ入力端子に供給される。

#### 【0035】

変換テーブル1131から出力した映像データR、G、Bは、白制御回路1133にも入力される。この白制御回路1133には、変換テーブル1131から出力されたW映像データも入力される。白制御回路1133は、映像データR、G、Bを用いて、白の映像データWを生成する合成回路AND1に入力される。この合成回路AND1の出力(映像データW)は、スイッチSW42、スイッチSW34を介して、振り分け回路1134に入力される。

10

#### 【0036】

白制御回路1133は、データ変換部Dconから、データD4に基づく白用の映像データWが入力しているときは、この映像データWをスイッチSW41、スイッチSW34を介して、振り分け回路1134に入力することもできる。

スイッチSW41、スイッチSW42のいずれか一方がオンされるが、そのオンオフ制御は、セレクタ1132からの切り替え信号により実施される。また、各スイッチSW31、SW32、SW33、SW34のオン及びオフに関してもセレクタ1132からの切り替え信号により実施される。

#### 【0037】

基本的には、4ビットモードのときは、スイッチSW41がオン、スイッチSW42がオフされる。スイッチSW34は、省略しても構わない。変換テーブル1131への入力が3ビットモードであってR、G、B映像データが入力し、W映像データが存在せず、表示部としては4ビットモードで動作させたい場合は、スイッチSW41がオフ、スイッチSW42がオンされる。このときは、映像データR、G、Bから作成した疑似映像データWが使用される。

20

#### 【0038】

上記のセレクタ1132は、入力端子1105からの制御データCont\_Sigに基づいて、スイッチSW31-SW34、SW41、SW42などを制御する。また振り分け回路1134も制御データCont\_Sigに基づいて、映像データR、G、B、Wを適切なカラーフィルタに割り当てる。

30

#### 【0039】

図11A-図11Dは、4ビットモード、3ビットモード、1ビットモード、その他の場合に、各データD1、D2、D3、D4に対する各スイッチSW31、SW32、SW33、SW34のオンオフ状態を示している。

#### 【0040】

図11Aは、データD1(赤用データ)に対する信号処理回路110のスイッチ動作状態を示している。4ビットモードのときは、データD1に対して、スイッチSW31がオン、SW32、SW33及びSW34はオフである。3ビットモード及び1ビットモードのときも、データD1に対して、スイッチSW31がオン、SW32、SW33及びSW34はオフである。

40

なお、図11Aにおいて、(\*1)で示している記述は、次の事を意味する。外部から赤表示のためのデータが入力している1ビットモードにおいては、赤のみの表示が可能である。或いは色フィルタとして白があるときは白のみの表示も可能である。さらにまた表示パネルの色フィルタが、シアン、マゼンタ、黄のフィルタで構成されている場合もある。このような場合、1ビットモードにおいては、マゼンタのみの表示、黄のみの表示を可能とすることができます。このときは、スイッチSW31の出力が、振り分け回路1134において振り分けられ、マゼンタ、或いは黄のフィルタを有する副画素に供給される。

#### 【0041】

図11Bは、データD2(緑用データ)に対する信号処理回路110のスイッチ動作状態を示している。4ビットモードのときは、データD2に対して、スイッチSW31が

50

オフ , SW3 2 がオン , SW3 3 及び SW3 4 はオフである。3 ビットモードときは、データ D 2 に対して、スイッチ SW3 1 がオフ , SW3 2 がオン , SW3 3 及び SW3 4 はオフである。1 ビットモードときは、データ D 2 に対して、スイッチ SW3 1 がオン , SW3 2 , SW3 3 及び SW3 4 はオフである。

なお、図 11 B において、(\* 2) で示している記述は、次の事を意味する。外部から緑表示のためのデータが入力している 1 ビットモードにおいては、緑のみの表示が可能である。或いは色フィルタとして白があるときは白のみの表示も可能である。さらにまた表示パネルの色フィルタが、シアン、マゼンタ、黄のフィルタで構成されている場合もある。このような場合、1 ビットモードにおいては、シアンのみの表示、黄のみの表示を可能とすることができます。このときは、スイッチ SW3 1 の出力が、振り分け回路 1134 において振り分けられ、シアン、或いは黄のフィルタを有する副画素に供給される。10

#### 【 0042 】

図 11 C は、データ D 3 (青用データ) に対する信号処理回路 110 のスイッチ動作状態を示している。4 ビットモードのときは、データ D 3 に対して、スイッチ SW3 1 , SW3 2 がオフ , SW3 3 がオン、SW3 4 はオフである。3 ビットモードときは、データ D 3 に対して、スイッチ SW3 1 , SW3 2 がオフ , SW3 3 がオン、SW3 4 はオフである。1 ビットモードときは、データ D 3 に対して、スイッチ SW3 1 がオン , SW3 2 , SW3 3 及び SW3 4 はオフである。

なお、図 11 C において、(\* 3) に示している記述は、次の事を意味する。外部から青表示のためのデータが入力している 1 ビットモードにおいては、青のみの表示が可能である。或いは色フィルタとして白があるときは白のみの表示も可能である。さらにまた表示パネルの色フィルタが、シアン、マゼンタ、黄のフィルタで構成されている場合もある。このような場合、1 ビットモードにおいては、シアンのみの表示、マゼンタのみの表示を可能とすることができます。このときは、スイッチ SW3 1 の出力が、振り分け回路 1134 において振り分けられ、シアン、或いはマゼンタのフィルタを有する副画素に供給される。20

#### 【 0043 】

図 11 D は、データ D 4 (白用データ) に対する信号処理回路 110 のスイッチ動作状態を示している。4 ビットモードのときは、データ D 4 に対して、スイッチ SW3 1 , SW3 2 , SW3 3 がオフ、SW3 4 はオンである。3 ビットモードときは、データ D 4 に対して、スイッチ SW3 1 , SW3 2 , SW3 3 がオフ、SW3 4 はオンである。1 ビットモードときは、データ D 4 に対して、スイッチ SW3 1 がオン , SW3 2 , SW3 3 及び SW3 4 はオフである。30

なお、図 11 D において、(\* 4) で示している記述は、次の事を意味する。外部から白表示のためのデータが入力している 1 ビットモードにおいては、白のみの表示が可能である。色フィルタを有する表示パネルが使用されている場合は、振り分け回路 1134 が白フィルタの位置にデータを出力する。さらにまた表示パネルの色フィルタが、R、G、B であったり、或いはシアン、マゼンタ、黄のフィルタで構成されている場合は、振り分け回路 1134 がそれぞれのフィルタに対して、例えばすべてデータ “1” を出力する。40

#### 【 0044 】

上記した図 11 A - 図 11 D のスイッチ状態は、データ D 1 - D 4 毎に示しているので、モード毎に分類されていない。実際の動作は、モードが切り替わるので、4 ビットモードにおける各スイッチの状態、3 ビットモードにおける各スイッチの状態、1 ビットモードにおける各スイッチの状態をそれぞれ集合して図に示してもよい。

#### 【 0045 】

図 12 (a) - 図 12 (b) は、それぞれ、シリアルデータの転送速度を、ビットモード毎に示している。今、例えば 1 種類の映像データをレジスタの 1 段をシフトさせるのに、1 クロックが必要であるとする。

4 ビットモードでは、シリアルデータには映像データ R , G , B , W が含まれる。よって、4 ビットモードでは、映像データ R , G , B , W を 4 サイクル分シフトさせるためには50

、16個のクロックを必要とする(図12(a))。

#### 【0046】

映像データR,G,Bが外部装置から与えられたとしても、映像データ処理回路125において、映像データWとしてダミーデータを生成する場合もある。この場合は、信号供給回路110は、4ビットモードで動作する。この場合シリアルデータには映像データR,G,B,ダミーデータ(DUM)が含まれる。よって、この4ビットモードでも、映像データR,G,B,DUMを4サイクル分シフトさせるためには、16個のクロックを必要とする(図12(b))。

#### 【0047】

3ビットモードでは、シリアルデータには映像データR,G,Bが含まれる(映像データWが存在しない)。よって、3ビットモードでは、映像データR,G,Bを4サイクル分シフトさせるためには、12個のクロックが必要である(図12(c))。このときは、シリアルパラレル変換回路1110は図8に示すスイッチ状態である。

#### 【0048】

1ビットモードでは、シリアルデータには例えば映像データRのみが送られてくる。よって、1ビットモードでは、映像データRを4サイクル分シフトさせるためには、4個のクロックで十分である(図12(d))。このときは、シリアルパラレル変換回路1110は図9に示すスイッチ状態である。

上記したように実施形態によると、副画素にメモリ出力が供給される表示装置に用いられる信号供給回路110が特徴的な機能を備えている。この信号供給回路110は、動作モード制御するモード制御回路1103を含む。

#### 【0049】

そして、モード制御回路1103により、信号供給回路110は、複数の副画素用のデジタルデータを前記メモリに供給する、第1モードと第2モードとに選択的に切り替えられる。ここで、第1モードは、外部からn個の前記副画素に対応する第1映像データを受け取り、前記第1映像データに基づいてn個の前記副画素用のデジタルデータを前記メモリに供給するモードであり、第2モードは、外部から前記n個よりも少ないm個の前記副画素に対応する第2映像データを受け取り、前記第2映像データに基づいてn個の前記副画素用のデジタルデータを前記メモリに供給するモードである。ここでモード制御回路1103が、前記第1映像データと前記第2映像データを受け取ることに先行して、モード制御データを受け取っている。また第1映像データ及び前記第2の映像データはシリアルデータであり、前記シリアルデータを前記複数の副画素に対応するデジタルデータにパラレル変換するパラレル変換回路1110と、前記パラレル変換部の出力データを前記全ての前記複数の副画素用のデジタルデータに変換するラインデータ生成回路1120と備えている。

#### 【0050】

第2モードのときラインデータ生成回路1120は、複数の前記副画素のうち白色のための副画素に供給するデータを生成することができる。

図13は、図10に示したセレクタ1132に与えられる制御データCont\_Sigと複数のビットモードとの関係を示している。制御データCont\_Sigは、例えば2ビットM1,M2を含み、第1の4ビットモード(R,G,B,W)のときは、(M1,M2)=(0,0)である。第2の4ビットモード(R,G,B,DUM)のときは、(M1,M2)=(0,1)である。3ビットモード(R,G,B)のときは、(M1,M2)=(1,0)である。1ビットモード(R or G or B or W)のときは、(M1,M2)=(1,1)である。

#### 【0051】

図14Aは、図10に示した振り分け回路1134に与えられる制御データCont\_Sigと振り分け先(各色=色フィルタ)との関係を示している。制御データCont\_Sigは、例えば3ビットC1,C2,C3を含む。振り分け回路1134は、(C1,C2,C3)=(0,0,0)のときは黒と判断する。この時は、出力ラインR,G,

10

20

30

40

50

B、Wに対してすべて0を出力する。振り分け回路1134は、(C1, C2, C3) = (1, 0, 0)のときは赤と判断する。この時は、出力ラインR、G、B、Wに対して(1, 0, 0, 0)を出力する。振り分け回路1134は、(C1, C2, C3) = (0, 1, 0)のときは緑と判断する。この時は、出力ラインR、G、B、Wに対して(0, 1, 0, 0)を出力する。振り分け回路1134は、(C1, C2, C3) = (0, 0, 1)のときは青と判断する。この時は、出力ラインR、G、B、Wに対して(0, 0, 1, 0)

)を出力する。振り分け回路1134は、(C1, C2, C3) = (1, 1, 1)のときは白と判断する。この時は、出力ラインR、G、B、Wに対して(1, 1, 1, 1) )を出力する。

10

#### 【0052】

上記のように振り分けられる各データを、図9に示したラッチ回路Lat11、Lat12、Lat13、Lat14、Lat15、・・・は、レジスタReg11の制御に基づいて、順次ラッチする。振り分け回路1134は、(C1, C2, C3) = (1, 1, 1)のときは白と判断する。この時は、出力ラインR、G、B、Wに対してすべて1を出力する。上記の構成にすることで、R, G, Bの3ビットデータに基づいて、4画素駆動を行うことが可能となる。

#### 【0053】

なお、(C1, C2, C3) = (0, 1, 1)のときはシアンと判断し、(C1, C2, C3) = (1, 0, 1)のときはマゼンタと判断し、(C1, C2, C3) = (1, 1, 0)のときはイエローと判断する。この場合、Wの出力ラインには0を出力する。

20

#### 【0054】

上記した説明は、映像データが赤(R)、緑(G)、青(B)、白(W)であることを前提として説明した。しかし、本発明の考え方とは、映像データがシアン、マゼンタ、黄の場合でも適用できる。つまり本発明の考え方とは、表示パネルの色フィルタが、シアン、マゼンタ、黄で構成されている場合も適用できる。

#### 【0055】

図14Bは、表示パネルの色フィルタが、シアン、マゼンタ、黄で構成され、制御データがR、G、Bの場合の振り分け回路1134が制御データを判定する判定例を示している。振り分け回路1134は、(C1, C2, C3) = (1, 1, 1)のときは白と判断する。このときは、出力ラインR、G、B、Wに対してすべて1を出力する。振り分け回路1134は、(C1, C2, C3) = (0, 1, 1)のときはシアンと判断する。このときは、シアンフィルタへデータ出力するラッチ回路が接続された出力ラインを1とする。振り分け回路1134は、(C1, C2, C3) = (1, 0, 1)のときはマゼンタと判断する。このときは、マゼンタフィルタへデータ出力するラッチ回路が接続された出力ラインを1とする。振り分け回路1134は、(C1, C2, C3) = (1, 1, 0)のときは黄と判断する。このときは、黄フィルタへデータ出力するラッチ回路が接続された出力ラインを1とする。振り分け回路1134は、(C1, C2, C3) = (0, 0, 0)のときは黒と判断する。この時は、出力ラインR、G、B、Wに対してすべて0を出力する。

30

#### 【0056】

なお、(C1, C2, C3) = (1, 1, 1)の白データが入力された場合、C1、C2、C3から選択されるいずれかの2つを1として出力し、Wを合わせて1として出力しても良い。

#### 【0057】

本発明は上記した実施形態に限定されるものではない。表示装置は、図15に示すように、R、G、Bの3副画素を縦方向に配列した画素構造を有していても良い。他の構成は図6に示した構成と同じである。このような表示装置が、R、G、Bのカラー画像表示モードの他に、黒(B1)、白(ホワイトWh)のモノクロモードを有している場合にも、本実施形態における発明を適用できる。具体的には、モノクロモードの場合は、外部から

40

50

入力される制御データを B 1、W h のいずれかを指定する制御データとする。すると振り分け回路 1 1 3 4 は、制御データが例えれば W h であると判断すれば、R、G、B の出力ラインすべてに 1 (白表示) を出力する。一方で、振り分け回路 1 1 3 4 は、制御データが例えれば B 1 であると判断すれば、R、G、B の出力ラインすべてに 0 (黒表示) を出力する。このような構成とすることで、モノクロモードは 1 ビットで 3 副画素駆動が可能となり、データ転送の高速化と消費電力の低減が可能となる。

#### 【 0 0 5 8 】

なお、本明細書における実施形態の表示装置は、ノーマリーブラックモードを採用していることを前提に記載をしている。しかし、ノーマリーホワイトモードを採用している表示装置にも、本発明は適用可能である。

10

#### 【 0 0 5 9 】

上記の説明において、図 7 乃至図 9 に示した信号供給回路 1 1 0 の入力端子 1 1 0 3 にはシリアルデータが入力するものとして説明した。

ところで一般にデジタルデバイスで処理されるデータは、バイト単位（例えは 8 ビット単位、16 ビット単位、32 ビット単位等）で取り扱われることが多い。このため、入力端子 1 1 0 3 に入力するシリアルデータも 8 ビット単位で区分することができる。

図 16 には、伝送ラインなどで各種のシリアルデータを伝送する伝送形態の一例を示している。伝送ラインにおいて、映像データ、制御データ、アドレスデータ、ダミーデータなどが一定のルールで伝送される。S C S は、あるまとまったシリアルデータが伝送される期間を指定する期間指定信号（同期信号と称してもよい）である。S I は、シリアルデータであり、モード制御データ（M 0、M 1 … M 5）、ゲートラインアドレス指定データ（A G 9、A G 8、A G 7、… A G 0）、映像データ（D 1 R、D 1 G, D 1 B … D n B）、ダミーデータ（…）、その他などが含まれる。さらにデータの境界を示す同期クロック、エラー訂正コードなどが含まれてもよい。S C L K は、シリアルロック（或いはシステムクロック）であり、シリアルデータに同期しており、シリアルデータをサンプリングすることができる。上記のシリアルデータを受け取るシリアルデータ処理部では、8 ビット単位のシリアルデータを判断し、映像データ、制御データ、アドレス指定データなどを分離する。映像データは、後述するデータ変換部（データ制御部と称してもよい）に伝送される。制御データ、アドレス指定データなどは、制御装置 C P 内で出力タイミングなどが調整され、信号供給回路 1 1 0 、ゲート線駆動回路 G D などに送られる。

20

#### 【 0 0 6 0 】

図 17 は、図 16 に示したシリアルデータを受信して処理する信号供給回路の他の実施形態を示している。入力端子 2 1 0 3 には、シリアルデータ処理回路 2 2 0 0 で必要な各種の信号がシリアルデータとして入力する。シリアルデータ処理回路 2 2 0 0 は、例えは予め取り決められている同期パルスのパターンを判断する。そして同期パルスのパターン判定結果に基づいて、内部クロックを利用してシリアルロック S C L K 、同期信号 S C S を生成している。

30

シリアルデータ処理回路 2 2 0 0 の内部には、データ分離回路 2 2 0 1 が設けられている。データ分離回路 2 2 0 1 は、同期信号 S C S 及びシリアルロック S C L K を利用して、モード制御データ（M 0、M 1 … M 5）、ゲートラインアドレス指定データ（A G 9、A G 8、A G 7、… A G 0）、映像データ（D 1 R、D 1 G, D 1 B … D n B）、ダミーデータ（…）、などを分離する。

40

モード制御データ（M 0、M 1 … M 5）は、4 ビットモード、3 ビットモード、1 ビットモードなどを指定するデータであり、シリアルデータ処理回路 2 2 0 0 及びデータ変換部 2 3 0 0 における映像データの処理形態を決定するために利用される。ゲートラインアドレス指定データ（A G 9、A G 8、A G 7、… A G 0）は、映像データが副画素に書き込まれる際に、ゲート線駆動回路 G D (図 1 に示した) がゲート線 G (G 1 ~ G n ) のいずれかを選択するために利用される。

シリアルデータ処理回路 2 2 0 0 においては、シリアルで入力される映像データが、パ

50

ラレルデータ D 1 ~ D 8 (データには、モードに応じてダミーデータが含まれる場合もある) に変換されて出力される。パラレルデータ D 1 ~ D 8 は、データ変換部 2300 に入力され一旦ラッチされる。データ変換部 2300 は、振り分け回路 2301 を含む。振り分け回路 2301 は、データ変換部 2300 内部にラッチされた各データを、適切なカラーの副画素に振り分けて、後段の水平ライン分を保持するラッチ回路に出力する。即ち、図 7、図 8、図 9 に示したように、振り分けられた各データは、1 水平ライン分の副画素データを保持するラッチ回路群に出力される。

#### 【 0 0 6 1 】

図 18 は、図 17 に示したシリアルデータ処理回路 2200 の内部のシリアルパラレル変換回路の一例を示している。シリアルデータ処理回路 2200 は、8 ビット単位の入力データを処理するために、直列接続された例えば 8 つのレジスタ Reg 21 - Reg 28 を含み、8 連続ラッチパルスをサイクリックに発生することができる。また、シリアルデータ処理回路 2200 は、8 連続するシリアルデータ(映像データ)を順次ラッチできるように 8 つのラッチ回路 Lat 21 - Lat 28 を含む。8 つのラッチ回路 Lat 21 - Lat 28 は、8 つのレジスタ Reg 21 - Reg 28 からのラッチパルスに基づいて、入力端子 2103 からの映像データを次々とラッチすることができる。ラッチ回路 Lat 21 - Lat 28 がラッチした、データ D 1 ~ D 8 は、データ変換部 2300 に入力する。

入力端子 2103 は、ラッチ回路 Lat 21 - Lat 28 のデータ入力端子に対して、スイッチ SW 31 を介して接続されている。このスイッチ SW 31 は、図 16 に示した映像データ(D1R, D1G, D1B, ..., DnB)が入力端子 2103 に入力したときにオンとなる。またスイッチ SW 32 は、レジスタ Reg 21 に初期値 “1” を入力するためと、8 ビット単位のサイクルでレジスタの出力 “1” を巡回させるために利用される。レジスタ Reg 21 - Reg 28 は、シリアルクロック SCLK と同相のクロックで駆動されるが、図 18 では省略している。

#### 【 0 0 6 2 】

図 19 は、図 17、図 18 に示したデータ変換部 2300 の内部構成の一例を示している。データ変換部 2300 には、シリアルデータ処理部 2200 からシリアルパラレル変換されたデータ D 1 - D 8 が入力する。これらのデータ D 1 - D 8 は、ラッチ回路 Lat 41 - Lat 48 でラッチされることが可能である。ラッチ回路 Lat 41 - Lat 48 のラッチパルスは、複数のレジスタ Reg 1 - Reg 4 により生成される巡回サンプリングパルス(ラッチパルスと称してもよい) SP1 - SP4 の中からセレクタ SEL が選択することで、決定されている。巡回パルス SP1 - SP4 を生成する回路構成は、図 7 から図 9 において説明したレジスタ Reg 1 - Reg 4、スイッチ SW11、SW12、SW13、オア回路 OR1 による回路と同じ回路構成を採用することができる。ラッチ回路 Lat 41 - Lat 48 によりラッチされたデータは、振り分け回路 2301 に入力される。振り分け回路 2301 は、振り分け回路 2301 は、ラッチ回路 Lat 41 - Lat 48 にラッチされた各データを、適切なカラーの副画素に振り分けて、後段の水平ライン分を保持するラッチ回路に出力する。即ち、図 7、図 8、図 9 に示したように、振り分けられた各データは、1 水平ライン分の副画素データを保持するラッチ回路群に出力される。

#### 【 0 0 6 3 】

図 20A は、映像データ R、G、B 及び W が入力する場合の動作例を示している。この映像データが入力したときは、制御装置 CP 及び又は信号供給回路 110 及び又はモード制御回路 1103 及び又はデータ分離回路 2201 などのモード判定部が、モード制御信号を判定し、4 ビットモードであることを決定する。4 ビットモードのときは、レジスタ Reg 1 - Reg 4 から順次巡回サンプリングパルス SP1 - SP4 が得られる。このときのスイッチ SW13 はレジスタ Reg 4 の出力を選択し、スイッチ SW12 は、スイッチ SW3 の出力を選択するように切り替えられる。

一方、セレクタ SEL1 は、サンプリングパルス SP1 を選択するように制御される。

10

20

30

40

50

したがって、レジスタ Reg 1 からのサンプリングパルス SP 1 が採用され、4つのシリアルクロック SCLK 毎に、ラッチ回路 Lat 41 - Lat 48 にラッチパルスが供給される。また、シリアルデータ処理回路 2200 から出力されるデータは、データ D1、D2、D3、D4、D5、D6、D7、D8、D1、D2、D3、D4、D5、D6、D7、D8、…と順次8ビット単位が繰り返しでラッチされ、そのデータ内容も R、G、B、W、R、G、B、W、R、G、B、W、…の繰り返しである。よって、4つのリアルクロック SCLK 毎に、データがラッチされた場合、各ラッチタイミング毎に、(1回目) R、G、B、W、(2回目) R、G、B、W、…と8ビットシリアル伝送に同期した映像データを得ることができる。

## 【0064】

10

図20Bは、3ビットモードによる映像データ R、G 及び B が入力する場合の動作例を示している。この映像データが入力したときは、上記モード判定部が、モード制御信号を判定し、4ビットモードであることを決定する。4ビットモードのときは、レジスタ Reg 1 - Reg 4 から順次巡回サンプリングパルス SP 1 - SP 4 が得られる。このときのスイッチ SW13 はレジスタ Reg 3 の出力を選択し、スイッチ SW12 は、スイッチ SW3 の出力を選択するように切り替えられる。

一方、セレクタ SEL1 は、このときもサンプリングパルス SP 1 を選択するように制御される。したがって、レジスタ Reg 1 からのサンプリングパルス SP 1 が採用され、この場合は3つのシリアルクロック SCLK 毎に、ラッチ回路 Lat 41 - Lat 48 にラッチパルスが供給される。また、シリアルデータ処理回路 2200 から出力されるデータは、データ D1、D2、D3、D4、D5、D6、D7、D8、D1、D2、D3、D4、D5、D6、D7、D8、…と順次8ビット単位が繰り返しでラッチされ、そのデータ内容は、R、G、B、R、G、B、R、G、B、R、G、B、…の繰り返しである。そして、3つのシリアルクロック SCLK 毎に、データがラッチされた場合、各ラッチタイミング毎に、(1回目) R、G、B、(2回目) R、G、B、…の映像データを得ることができる。ここで、8ビット単位でシリアル伝送される映像データと、ラッチ回路 Lat 41 - Lat 48 でラッチされるデータ D1、D2、D3、D4、D5、D6、D7、D8との関係は、次のような関係にある。3つの映像データ R、G、B に対して伝送単位が8ビットであると、その最少公倍数 24、つまり 24 ビット(8ビットの3サイクル)が同期サイクルとなる。つまり、例えばデータ D1、D2、D3、D4、D5、D6、D7、D8 に同じパターンの映像データ R、G、B、R、G、B、R、G が現れるのは、24ビットサイクルとなる。

20

したがって、3ビットモードのときは、データ振り分け回路 2301 の動作モードは、24ビットサイクルが考慮されて、データ D1、D2、D3、D4、D5、D6、D7、D8 をそれぞれ R、G、B の出力端子へ振り分けるモードが採用される。図20Bの例では、例えば R 出力端子の場合、D4、D7、D2、D5、D8、D3、D6、D1、…の順で R 出力端子へデータが選択されて出力される。

30

## 【0065】

40

図20Cは、1ビットモードによる映像データ\*(\*=R、G、B、W、ダミーデータのいずれでもよい)が入力する場合の動作例を示している。この映像データが入力したときは、上記モード判定部が、モード制御信号を判定し、1ビットモードであることを決定する。1ビットモードのときは、レジスタ Reg 1 からのサンプリングパルス SP 1 とその反転パルス /SP 1 が採用される。このときのスイッチ SW12 はレジスタ Reg 1 の出力を選択するように切り替えられる。このときは、レジスタ Reg 1 のサンプリングパルス SP 1 は、“1”、“0”、“1”、“0”、…を繰り返す。

1ビットモードの場合は、シリアルデータ処理回路 2200 から出力されるデータは、データ D1、D2、D3、D4、D5、D6、D7、D8 の何れかが 1 でもよいが、例えばデータ D1 が伝送データ “1” とされ、他は “0” として取り決められる。これにより、振り分け回路 2301 は、データ D1 を選択する。振り分け回路 2301 は、白モード或いは黒モードに応じて、すべての出力端子 R、G、B に “0” 又は “1” 同時に出力す

50

る。或いは、振り分け回路 2301 は、1 ビットモードとカラー指定情報がある場合、カラー指定情報に応じて、出力端子 R、又は G、又は B に “1” を出力する。

#### 【 0066 】

図 21 は、図 17、図 18、図 19 に示した信号供給回路の動作を概略的に説明するためのフローチャートである。まずモード判定部は、同期信号を検出して 8 ビット単位シリアルデータに対する同期状態となる (ST1、ST2)。この同期状態において、予め仕様書などで取り決められているデータ配列に基づいて、シリアルデータ処理回路 2200 は、入力データのデータ種類判別及び各種データの振り分けを行う (ST3)。またデータ分離部 2201 或いはモード判定部は、映像データ及び処理関連データの判定を行う。処理関連データは、図 16 で説明したモード制御データ、ゲートアドレス指定データなどである (ST4)。モード判定が決定すると、先に説明したように 4 ビットモード或いは 3 ビットモード或いは 1 ビットモードが設定される (ST5)。そしてタイミングクロックに基づいて、各ブロックの動作が実行される (ST6)。

#### 【 0067 】

この発明は上記の実施形態に限定されるものではない。図 22 は、さらに他の実施形態を示している。図 18 に示した実施形態では、レジスタ Reg 21 - Reg 28 及びラッチ回路 Lat 21 - Lat 28 は、信号供給回路 110 内において、ゲート線と同じ方向 (X 方向) へ配列される構成であった。しかし、制御装置 CP において、配列方向の面積に制限があるような場合、或いは配列方向と交差する信号線と同じ方向 (Y 方向) の面積に余裕がある場合、図 22 に示すように、配列してもよい。即ち、複数のレジスタ及び複数のラッチ回路が、それぞれ 2 行になるように分けて配列してもよい。なお、図 18 に示した実施形態と同じ部分には同じ符号を付して具体的な説明は省略する。

#### 【 0068 】

この発明は上記の実施形態に限定されるものではない。図 23 は、さらに他の実施形態を示している。図 18 に示した実施形態において、シリアルデータ処理回路 2200 では、レジスタ Reg 21 - Reg 28 が直列接続されており、この直列回路は、ビット転送の途中でビットリターンすることができない。しかし図 23 のレジスタ直列回路では、レジスタ Reg 23 の出力がレジスタ Reg 24 に転送される途中に、スイッチ SW41 が設けられている。そのために、このレジスタ直列回路は、レジスタ Reg 23 の出力をスイッチ SW41 を介して、レジスタ Reg 26 に転送することができるし、またスイッチ SW41 を介して、レジスタ Reg 24 に転送することができる。スイッチ SW42 は、最終段のレジスタ Reg 28 の出力を初段のレジスタ Reg 21 にフィードバックするか、または初期値 “1” をレジスタ Reg 21 に入力するかを決めるスイッチである。各レジスタ Reg 21 - Reg 28 から出力される状態出力 (“1” または “0”) は、ラッチパルスとして対応するラッチ回路 Lat 21 - Lat 28 のラッチパルス入力端子に供給される。ラッチ回路 Lat 21 - Lat 28 はそれぞれラッチパルスが与えられたタイミングでシリアル入力しているデータをラッチし、データ D1 - D8 として出力する。

上記の構成によると、レジスタ直列回路が、データ “1” を転送する場合、8 段系路又は 6 段系路をスイッチ切り替えにより得ることができる。即ち、レジスタ Reg 21 - レジスタ Reg 28 - レジスタ Reg 21 . . . の順でデータ “1” が巡回する 8 段系路、又は、レジスタ Reg 21 - レジスタ Reg 23 - レジスタ Reg 26、Reg 27、Reg 28、Reg 21、. . . の順でデータ “1” が巡回する 6 段系路である。レジスタの 8 段は、4 の倍数であるから、4 ビットモードのときに利用すると便利である。またレジスタの 6 段は、3 の倍数であるから、3 ビットモードのときに利用すると便利である。

#### 【 0069 】

図 24A は、図 23 に示した信号供給回路 110 が基本 4 ビットモード (8 ビットモードと称してもよい) で動作しているとき、ラッチ回路 Lat 21 - Lat 28 からの出力データ D1 - D8 と、データ変換部 2300 におけるデータラッチタイミングとラッチデ

10

20

30

40

50

ータとの関係を示している。1回のラッチにより4つのデータD1-D4がラッチされ、次のラッチにより4つのデータD5-D8がラッチされる。また次のラッチにより4つのデータD1-D4がラッチされ、この次のラッチにより4つのデータD5-D8がラッチされ、このような動作が繰り替えされる。4ビットモードは、映像データR、G、B、W(又はWがダミーデータ)の入力に対して適用される。

図24Bは、図23に示した信号供給回路110が基本3ビットモード(6ビットモードと称してもよい)で動作しているとき、ラッチ回路Lat21-Lat26からの出力データD1-D6と、データ変換部2300におけるデータラッチャタイミングとラッチデータとの関係を示している。1回のラッチにより3つのデータD1-D3がラッチされ、次のラッチにより3つのデータD4-D6がラッチされる。また次のラッチにより3つのデータD1-D3がラッチされ、この次のラッチにより3つのデータD4-D6がラッチされ、このような動作が繰り替えされる。3ビットモードは、映像データR、G、Bの入力に対して適用される。10

シリアルデータ処理回路が1ビットモードで動作するときは、例えば振り分け回路2301は、制御信号(振り分けモード切替信号、カラー指定情報も含む)に応じて、自動的にR、G、B、Wの何れか1つ、又は複数の組み合わせ出力に切り替わる。このとき、レジスタReg21-Reg28、Lat21-Lat28は、電源節約のために停止してもよい。

上記した実施形態によると、振り分け回路2301における振り分け処理の制御が簡単となる。20

#### 【0070】

図25は、データ変換部2300の他の実施形態を示している。図19に示したデータ変換部2300では、サンプリングクパルス(ラッチャパルスと称してもよい)を生成するレジスタは、4個で構成されてサンプリングSP1-SP4を生成した。しかし、図25に示すようにサンプリングパルス生成回路が8つのレジスタReg1-Reg8により構成されてもよい。この場合、先の実施形態で説明したように、4ビットモード、3ビットモード、1ビットモードに対応した適切なサンプリングクロックが生成されることが好ましい。そこで、このサンプリングパルス生成回路は、スイッチSW11、SW14が設けられている。スイッチSW14は、レジスタReg7の出力又はレジスタReg8の出力のいずれかを選択することができる。そしてスイッチSW11は、スイッチSW14の出力または、初期設定時に取り込むためのデータ“1”の入力端子のいずれかを選択することができる。30

レジスタReg1-レジスタReg8から出力される各サンプリングクパルス(ラッチャパルス)は、ラッチ回路Lat1-ラッチ回路Lat8のラッチャパルス入力端子に供給される。ラッチ回路Lat1-ラッチ回路Lat8のデータ入力端子には、それぞれシリアルデータ処理部2200で取り出された映像データD1-D8がそれぞれ入力される。

#### 【0071】

上記のサンプリングパルス生成回路は、基本4ビットモード(8ビットモードと称してもよい)のときは、スイッチSW14はレジスタReg8の出力を選択し、スイッチSW11はスイッチSW14の出力を選択した状態となる。40

このときは、ラッチ回路Lat1-Lat8からの出力データD1-D8と、データ変換部2300におけるデータラッチャタイミングとラッチデータとの関係は、先の図24Aで示した関係と同じである。1回のラッチにより4つのデータD1-D4がラッチされ、次のラッチにより4つのデータD5-D8がラッチされる。また次のラッチにより4つのデータD1-D4がラッチされ、この次のラッチにより4つのデータD5-D8がラッチされ、このような動作が繰り替えされる。4ビットモードは、映像データR、G、B、W(又はWがダミーデータ)の入力に対して適用される。

#### 【0072】

次にサンプリングパルス生成回路が、基本3ビットモード(6ビットモードと称しても50

よい)のときは、スイッチ SW14 はレジスタ Reg6 の出力を選択し、スイッチ SW13 はスイッチ SW14 の出力を選択した状態となる。

このときは、ラッチ回路 Lat1 - Lat8 からの出力データ D1 - D8 と、データ変換部 2300 におけるデータラッチャタイミングとラッチデータとの関係は、先の図 24B で示した関係と同じである。1 回のラッチにより 3 つのデータ D1 - D3 がラッチされ、次のラッチにより 3 つのデータ D4 - D6 がラッチされる。また次のラッチにより 3 つのデータ D1 - D3 がラッチされ、この次のラッチにより 3 つのデータ D4 - D6 がラッチされ、このような動作が繰り替えされる。3 ビットモードは、映像データ R、G、B の入力に対して適用される。

信号供給回路 110 が 1 ビットモードで動作するときは、例えば振り分け回路 2301 10 は、制御信号(振り分けモード切替信号、カラー指定情報も含む)に応じて、自動的に R、G、B、W の何れか 1 つ、又は複数の組み合わせ出力状態に切り替わる。このとき、データ変換部 2300 は、電源節約のために停止してもよい。

上記した実施形態によると、振り分け回路 2301 における振り分け処理の制御が簡単となる。

#### 【0073】

図 26 は、上記したサンプリングパルス生成回路の他の実施形態を示している。図 25 に示す実施形態は、レジスタ Reg1 - Reg8 を X 方向へ直線的に配列した構成である。しかし、配列パターンは、図 25 の配列パターンに限定されるものではなく、例えば図 26 に示すように、8 つのレジスタ Reg1 - Reg8 を 4 個ずつ分けて、2 行に配列したパターンでもよい。なお図 25 と同じ回路には同じ符号を付して説明は省略する。このような配列パターンであると、X 方向の配列長さ短くすることができる。

#### 【0074】

上記したように外部装置の性能に応じて、表示パネルに対するデータ供給方法を工夫することで、データ転送速度の高速化、消費電力の低減化を実現することができる。上記した実施形態は、画素電極が外部光を反射する反射型の表示装置、バックライトを有した透過型の表示装置のいずれでも採用可能である。

#### 【0075】

(1) 上記したように実施形態によると、基本的には、副画素がマトリックス状に配列された表示パネルに対して、前記副画素にデジタルデータを供給する信号供給回路であって、前記信号供給回路は、

第 1 モードでは、外部から n 個の副画素に対応する第 1 映像データを受け取り、前記第 1 映像データに基づいて n 個の前記副画素のためのデジタルデータを前記表示パネルに供給するモードの動作状態を形成し、

第 2 モードは、外部から前記 n 個よりも少ない m 個の前記副画素に対応する第 2 映像データを受け取り、前記第 2 映像データに基づいて n 個の前記副画素のためのデジタルデータを前記表示パネルに供給するモードの動作状態を形成するものである。

(2) 前記第 1 及び第 2 の映像データはシリアルデータであり、上記(1)記載の信号供給回路は、前記シリアルデータをパラレルデータに変換するためのラッチャパルスを生成するために、複数のレジスタを直列接続したレジスタ直列回路を有する(例えば図 7、図 8、図 9、図 18、図 19、図 22、図 23、図 25、図 26)。

(3) 上記(2)記載の前記レジスタ直列回路は、前記第 1 モードにおけるラッチャパルスと、前記第 2 モードにおけるラッチャパルスを選択的に得るために、最終段のレジスタ出力を初段のレジスタのデータ入力端子に帰還する第 1 の系路と、最終段よりも前の段のレジスタ出力を前記初段のレジスタのデータ入力端子に帰還する第 2 の系路とを切り替えるスイッチを備える(例えば図 7、図 8、図 9、図 19、図 22、図 23、図 25、図 26)。

(4) 上記(2)記載の前記レジスタ直列回路から出力される複数のラッチャパルスは、それぞれ前記シリアルデータをラッチする複数のラッチ回路のラッチャパルス入力端子に供給される(図 7 - 図 9、図 18、図 19、図 23、図 25、図 26)。

10

20

30

40

50

(5) 上記(2)記載のレジスタ直列回路は、8ビット単位で入力するシリアルデータをパラレルデータに変換するためのシリアルデータ処理回路に設けられている(例えば図18、図22、図23)。

(6) 上記(2)記載のレジスタ直列回路は、8ビット単位で入力するシリアルデータをパラレルデータに変換した後の任意のデータを、ラッチするためのラッチパルスを生成するラッチパルス生成回路に用いられる(図19、図25、図26)。

(7) 上記(5)又は(6)記載の8ビット単位で入力するシリアルデータは、さらに、映像データの他にアドレス指定データ、モード制御データを含む。

(8) 上記(7)記載の前記信号供給回路は、前記モード制御データに基づいて前記第1モード、前記第2モードを切り替える。 10

(9) 上記(1)記載のシリアルデータは、R、G、B、Wの映像データ又はR、G、Bの映像データのいずれかを含む。

(10) 上記(1)記載の信号供給回路は、さらに、自動的にダミーデータを生成する回路を含む。

#### 【0076】

本発明のいくつかの実施形態を説明したが、これらの実施形態は例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。さらにまた、請求項の各構成要素において、構成要素を分割して表現した場合、或いは複数を合わせて表現した場合、或いはこれらを組み合わせて表現した場合であっても本発明の範疇である。また請求項を制御ロジックとして表現した場合、コンピュータを実行させるインストラクションを含むプログラムとして表現した場合、及び前記インストラクションを記載したコンピュータ読み取り可能な記録媒体として表現した場合でも本発明の装置を適用したものである。 20

#### 【符号の説明】

#### 【0077】

P N L . . . 表示パネル、S U B 1 . . . 第1基板、S U B 2 . . . 第2基板、L Q . . . 液晶層、D A . . . 表示エリア、P X ( P X 1 1 , P X 1 2 , . . . ) . . . 副画素、

G ( G 1 ~ G n ) . . . ゲート線、S ( S 1 ~ S m ) . . . 信号線、G D . . . ゲート線

駆動回路(第1駆動回路)、S D . . . ソース線駆動回路(第2駆動回路)、C P . . . 制御装置、1 1 0 . . . 信号供給回路、M 0 . . . メモリ、1 2 3 . . . 電源回路、1 2

4 . . . 黒及びタイミングパルス生成回路、1 2 5 . . . 映像データ処理回路、1 2 6 . . . 表示電位制御回路1 2 6、P E . . . 画素電極、C E . . . 共通電極、3 0 0 . . . 外部装置、1 1 0 1 . . . シリアルパラレル変換回路、1 1 2 0 . . . ラインデータ生成回路、1 1 0 3 . . . モード制御回路、2 2 0 0 . . . シリアルデータ処理回路、2 2 0 1 . . . データ分離回路、2 3 0 0 . . . データ変換部、2 3 0 1 . . . 振り分け回路。 30

【図1】

【図2 A】

【図2 B】

【図3】

【図4】

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図 9】

【図 10】

【図 11A】

図 11A

| データ D1 (R)  | SW31 | SW32 | SW33 | SW34 |

|-------------|------|------|------|------|

| 4ビットモード     | オン   | オフ   | オフ   | オフ   |

| 3ビットモード     | オン   | オフ   | オフ   | オフ   |

| 1ビットモード(*1) | オン   | オフ   | オフ   | オフ   |

| その他         | オフ   | オフ   | オフ   | オフ   |

(\*1)赤、マゼンタ、黄、白

【図 11B】

図 11B

| データ D2 (G)  | SW31 | SW32 | SW33 | SW34 |

|-------------|------|------|------|------|

| 4ビットモード     | オフ   | オン   | オフ   | オフ   |

| 3ビットモード     | オフ   | オン   | オフ   | オフ   |

| 1ビットモード(*2) | オン   | オフ   | オフ   | オフ   |

| その他         | オフ   | オフ   | オフ   | オフ   |

(\*2)緑、シアン、黄、白

【図 11C】

図 11C

| データ D3 (B)  | SW31 | SW32 | SW33 | SW34 |

|-------------|------|------|------|------|

| 4ビットモード     | オフ   | オフ   | オン   | オフ   |

| 3ビットモード     | オフ   | オフ   | オン   | オフ   |

| 1ビットモード(*3) | オン   | オフ   | オフ   | オフ   |

| その他         | オフ   | オフ   | オフ   | オフ   |

(\*3)青、シアン、マゼンタ、白

【図 11D】

図 11D

| データ D4 (W)  | SW31 | SW32 | SW33 | SW34 |

|-------------|------|------|------|------|

| 4ビットモード     | オフ   | オフ   | オフ   | オン   |

| 3ビットモード     | オフ   | オフ   | オフ   | オン   |

| 1ビットモード(*4) | オン   | オフ   | オフ   | オフ   |

| その他         | オフ   | オフ   | オフ   | オフ   |

(\*4)白

【図 12】

【図13】

図13

| 動作モード                     | M1 | M2 |

|---------------------------|----|----|

| 4ビットモード<br>(R, G, B, W)   | 0  | 0  |

| 4ビットモード<br>(R, G, B, DUM) | 0  | 1  |

| 3ビットモード                   | 1  | 0  |

| 1ビットモード                   | 1  | 1  |

【図14A】

図14A

| 色 | C1 | C2 | C3 |

|---|----|----|----|

| 黒 | 0  | 0  | 0  |

| 赤 | 1  | 0  | 0  |

| 緑 | 0  | 1  | 0  |

| 青 | 0  | 0  | 1  |

| 白 | 1  | 1  | 1  |

【図14B】

図14B

| 色    | C1 | C2 | C3 |

|------|----|----|----|

| 白    | 1  | 1  | 1  |

| シアン  | 0  | 1  | 1  |

| マゼンタ | 1  | 0  | 1  |

| 黄    | 1  | 1  | 0  |

| 黒    | 0  | 0  | 0  |

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

【図19】

【図20A】

【図20B】

【図 20C】

図 20C

【図 21】

図 21

【図 22】

図 22

【図 23】

図 23

【図 24A】

【図 24B】

【図 25】

【図 26】

---

フロントページの続き

(51)Int.Cl.

| F I     |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 3 J |

| G 0 9 G | 3/20 | 6 3 1 H |

| G 0 9 G | 3/20 | 6 5 0 M |

(56)参考文献 特開2013-57853(JP,A)

特開2008-227609(JP,A)

特開2012-194582(JP,A)

米国特許出願公開第2011/0084990(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8