(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5619152号

(P5619152)

(45) 発行日 平成26年11月5日(2014.11.5)

(24) 登録日 平成26年9月26日(2014.9.26)

(51) Int.Cl.

F 1

|                    |                  |            |      |

|--------------------|------------------|------------|------|

| <b>H01L 29/78</b>  | <b>(2006.01)</b> | H01L 29/78 | 652C |

| <b>H01L 29/12</b>  | <b>(2006.01)</b> | H01L 29/78 | 652T |

| <b>H01L 29/06</b>  | <b>(2006.01)</b> | H01L 29/78 | 652P |

| <b>H01L 21/336</b> | <b>(2006.01)</b> | H01L 29/78 | 652H |

|                    |                  | H01L 29/78 | 652Q |

請求項の数 16 (全 25 頁) 最終頁に続く

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2012-512749 (P2012-512749) |

| (86) (22) 出願日 | 平成23年4月7日(2011.4.7)          |

| (86) 国際出願番号   | PCT/JP2011/058805            |

| (87) 国際公開番号   | W02011/135995                |

| (87) 国際公開日    | 平成23年11月3日(2011.11.3)        |

| 審査請求日         | 平成24年8月23日(2012.8.23)        |

| (31) 優先権主張番号  | 特願2010-195358 (P2010-195358) |

| (32) 優先日      | 平成22年9月1日(2010.9.1)          |

| (33) 優先権主張国   | 日本国(JP)                      |

| (31) 優先権主張番号  | 特願2010-100553 (P2010-100553) |

| (32) 優先日      | 平成22年4月26日(2010.4.26)        |

| (33) 優先権主張国   | 日本国(JP)                      |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号 |

| (74) 代理人  | 100088672<br>弁理士 吉竹 英俊                     |

| (74) 代理人  | 100088845<br>弁理士 有田 貴弘                     |

| (72) 発明者  | 三浦 成久<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内       |

| (72) 発明者  | 中田 修平<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内       |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電型の半導体基板と、

前記半導体基板表面上に形成された、第1導電型のドリフト層と、

前記ドリフト層表面に選択的に複数形成された、第2導電型の第1ウェル領域と、

各前記第1ウェル領域表面に選択的に形成された第1導電型のソース領域と、

前記第1ウェル領域上から前記ドリフト層上に渡って、絶縁膜を介して形成されたゲート電極と、

前記ゲート電極下の前記ドリフト層内部において互いに隣り合う各前記第1ウェル領域のそれぞれに接続して形成された第2導電型の第2ウェル領域と、

前記ソース領域に接続されて形成されたソース電極と、

前記半導体基板裏面に形成されたドレイン電極と、を備え、

前記第2ウェル領域の第2導電型の不純物濃度の最大値が前記ドリフト層の表面よりも深い位置にある、

ことを特徴とする半導体装置。

## 【請求項 2】

前記最大値は、前記ドリフト層の表面からの深さが0.3μm~1.0μmまでの間に存在することを特徴とする請求項1記載の半導体装置。

## 【請求項 3】

第1導電型の半導体基板と、

10

20

前記半導体基板表面上に形成された、第1導電型のドリフト層と、

前記ドリフト層表面に選択的に複数形成された、第2導電型の第1ウェル領域と、

各前記第1ウェル領域表面に選択的に形成された第1導電型のソース領域と、

前記第1ウェル領域上から前記ドリフト層上に渡って、絶縁膜を介して形成されたゲート電極と、

前記ゲート電極下の前記ドリフト層内部において互いに隣り合う各前記第1ウェル領域のそれぞれに接続して形成された第2導電型の第2ウェル領域と、

前記ソース領域に接続されて形成されたソース電極と、

前記半導体基板裏面に形成されたドレイン電極と、を備え、

前記第2ウェル領域上に第1導電型層が形成された、

ことを特徴とする半導体装置。

10

**【請求項4】**

前記第2ウェル領域は、隣接する複数の前記第1ウェル領域の間を接続する、

請求項1乃至3の何れか1項に記載の半導体装置。

**【請求項5】**

前記第2ウェル領域は、自身が接続する複数の前記第1ウェル領域との距離の総和が最小となる平面視上の位置を含むように形成される、

請求項1乃至4の何れか1項に記載の半導体装置。

**【請求項6】**

前記ドリフト層表面に、前記複数の第1ウェル領域を含むセル領域を平面視包囲して選択的に形成され、前記ソース電極と接続された第2導電型の周縁領域をさらに備える、

請求項1乃至5の何れか1項に記載の半導体装置。

20

**【請求項7】**

前記第1ウェル領域と前記第2ウェル領域とは、第2導電型の不純物濃度分布が異なる、

請求項1乃至6の何れか1項に記載の半導体装置。

**【請求項8】**

前記第2ウェル領域を複数備え、

前記複数の第1ウェル領域の前記ドリフト層内部に埋没しつつ、互いに隣り合う各前記第2ウェル領域のそれぞれと接続して形成された、第2導電型の第3ウェル領域をさらに備える、

請求項1乃至7の何れか1項に記載の半導体装置。

30

**【請求項9】**

前記第3ウェル領域の上面は、前記第1ウェル領域の下面よりも下方に形成される、

請求項8に記載の半導体装置。

**【請求項10】**

前記第2ウェル領域および前記第3ウェル領域は、平面視で前記複数の第1ウェル領域の領域を全て覆うように形成される、

請求項8に記載の半導体装置。

**【請求項11】**

前記第2ウェル領域および/または前記第3ウェル領域の下方に形成された、前記ドリフト層の不純物濃度よりも高い不純物濃度を有する第1導電型の第1不純物領域をさらに備える、

請求項8に記載の半導体装置。

40

**【請求項12】**

前記ゲート電極下の前記ドリフト層表面において、前記ドリフト層の不純物濃度よりも高い不純物濃度を有する第1導電型の第2不純物領域をさらに備える、

請求項1乃至5の何れか1項に記載の半導体装置。

**【請求項13】**

前記第1ウェル領域と前記ソース領域との間隙が前記ドリフト層表面の至るところで同

50

一である、

請求項 1 乃至 3 の何れか 1 項に記載の半導体装置。

【請求項 1 4】

前記第 1 ウェル領域は円形である、

請求項 1 2 記載の半導体装置。

【請求項 1 5】

前記半導体基板はワイドバンドギャップ半導体により構成される、

請求項 1 乃至 1 4 の何れか 1 項に記載の半導体装置。

【請求項 1 6】

前記ワイドバンドギャップ半導体は炭化珪素である請求項 1 5 に記載の半導体装置。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に関し、特に炭化珪素半導体装置の帰還容量、オン損失、スイッチング損失の低減に関する。

【背景技術】

【0002】

炭化珪素半導体装置においては、通電時における損失（オン損失）を低減すると共に、装置のスイッチング時に発生する損失（スイッチング損失）を低減することが従来から求められている。 20

【0003】

この解決方法として、ドレイン電極とゲート電極の対向面積に依存する帰還容量を低減することが挙げられる。すなわち特許文献 1 に示すように、各単位セルを構成する p ベース層と p ベース層の間（J F E T 領域）の面積を、 p 抜き取り領域の挿入により減らす手法がある。

【0004】

なお特許文献 1 に示される炭化珪素半導体装置である n チャネル D M O S ( D o u b l e D i f f u s e d M O S ) は、各単位セルを構成する p ベース層を、部分的に p 抜き取り領域にてセル相互間を接続させ、 p 抜き取り領域を介してソース電極と短絡されている。このような構造を有することによって、素子に印加されたノイズを p 抜き取り領域を介してソース電極へ抜ける通路にも流すことができ、素子の破壊耐量が向上することも可能である。さらに、素子全体において p 領域は連続して 1 つの領域を形成するため、局所的な p ベース層の電位上昇が抑えられ、素子の破壊耐量が向上することも可能である。 30

【先行技術文献】

【特許文献】

【0005】

【特許文献 1】特開平 5 - 102487 号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記の p 抜き取り領域は p ベース層の表面近傍で接続され、なおかつドリフト層表面からドリフト層奥の方向に延伸されているため、各単位セルの実効的なチャネル幅が減少し、かつ J F E T 領域の一部が減少し、 p 抜き取り領域を設置しない場合に比べて、帰還容量は減少させることができるものの、チャネル抵抗及び J F E T 抵抗の増加を招くという問題があった。

【0007】

本発明は上記のような問題を解決するためになされたものであり、チャネル抵抗、 J F E T 抵抗の増加を招かずに帰還容量を低減し、オン損失、スイッチング損失を低減することが可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

10

20

30

40

50

## 【0008】

本発明にかかる半導体装置は、第1導電型の半導体基板と、前記半導体基板表面上に形成された、第1導電型のドリフト層と、前記ドリフト層表面に選択的に複数形成された、第2導電型の第1ウェル領域と、各前記第1ウェル領域表面に選択的に形成された第1導電型のソース領域と、前記第1ウェル領域上から前記ドリフト層上に渡って、絶縁膜を介して形成されたゲート電極と、前記ゲート電極下の前記ドリフト層内部において互いに隣り合う各前記第1ウェル領域のそれぞれに接続して形成された第2導電型の第2ウェル領域と、前記ソース領域に接続されて形成されたソース電極と、前記半導体基板裏面に形成されたドレイン電極と、を備え、前記第2ウェル領域の第2導電型の不純物濃度の最大値が前記ドリフト層の表面よりも深い位置にある。

10

## 【発明の効果】

## 【0009】

本発明にかかる半導体装置によれば、ゲート電極下のドリフト層内部において互いに隣り合う各第1ウェル領域のそれぞれに接続して形成された第2導電型の第2ウェル領域を備え、第2ウェル領域の第2導電型の不純物濃度の最大値がドリフト層の表面よりも深い位置にあることにより、オン抵抗の大きな増大を生じさせること無く帰還容量を低減することが可能となる。

## 【0010】

この発明の目的、特徴、局面、および利点は、以下の詳細な説明と添付図面とによって、より明白となる。

20

## 【図面の簡単な説明】

## 【0011】

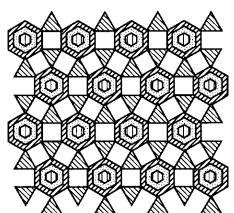

【図1】実施の形態1における炭化珪素半導体装置の上面図である。

【図2】実施の形態1における炭化珪素半導体装置の基板内部の表面近傍の上面図である。

【図3】実施の形態1における炭化珪素半導体装置の基板内部の上面図である。

【図4】実施の形態1における炭化珪素半導体装置の素子端面における縦断面図である。

【図5】実施の形態1における炭化珪素半導体装置の素子端面における縦断面図である。

【図6】実施の形態1における炭化珪素半導体装置の製造方法における縦断面図である。

【図7】実施の形態1における炭化珪素半導体装置の製造方法における変形例の縦断面図である。

30

【図8】実施の形態1における炭化珪素半導体装置の製造方法における変形例の縦断面図である。

【図9】実施の形態1における炭化珪素半導体装置の製造方法における縦断面図である。

【図10】実施の形態1における炭化珪素半導体装置の製造方法における変形例の縦断面図である。

【図11】実施の形態1における炭化珪素半導体装置の製造方法における縦断面図である。

【図12】実施の形態1における炭化珪素半導体装置の製造方法における変形例の縦断面図である。

40

【図13】実施の形態1における炭化珪素半導体装置の製造方法における変形例の縦断面図である。

【図14】実施の形態1における炭化珪素半導体装置の製造方法における縦断面図である。

【図15】実施の形態1における炭化珪素半導体装置の製造方法における縦断面図である。

【図16】実施の形態1における炭化珪素半導体装置の上面図である。

【図17】実施の形態1における炭化珪素半導体装置の変形例の上面図である。

【図18】実施の形態1における炭化珪素半導体装置の変形例の上面図である。

【図19】実施の形態1における炭化珪素半導体装置の変形例の上面図である。

50

- 【図20】実施の形態1における炭化珪素半導体装置の変形例の上面図である。

- 【図21】実施の形態1における炭化珪素半導体装置の変形例の上面図である。

- 【図22】実施の形態1における炭化珪素半導体装置の変形例の上面図である。

- 【図23】実施の形態1における炭化珪素半導体装置の上面図である。

- 【図24】実施の形態1における炭化珪素半導体装置の変形例の上面図である。

- 【図25】実施の形態1における炭化珪素半導体装置の変形例の上面図である。

- 【図26】実施の形態1における炭化珪素半導体装置の変形例の上面図である。

- 【図27】実施の形態1における炭化珪素半導体装置の上面図である。

- 【図28】実施の形態1における炭化珪素半導体装置の変形例の上面図である。

- 【図29】実施の形態1における炭化珪素半導体装置の変形例の上面図である。 10

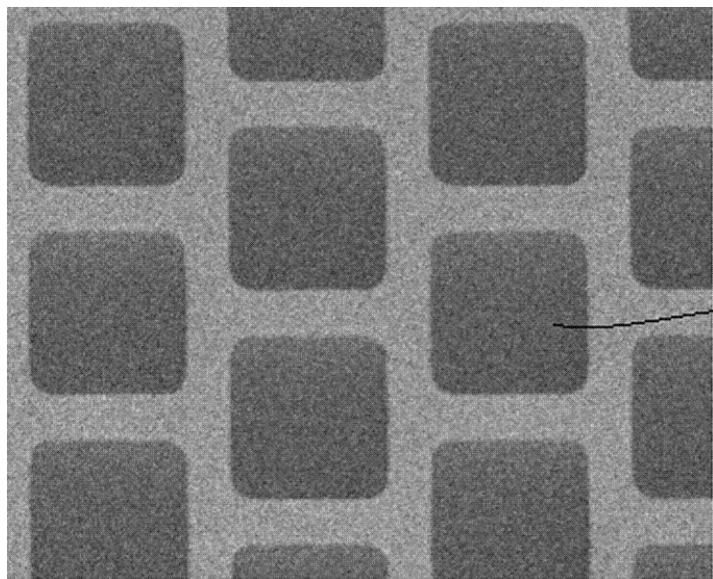

- 【図30】実施の形態1における炭化珪素半導体装置の上面の電子顕微鏡写真である。

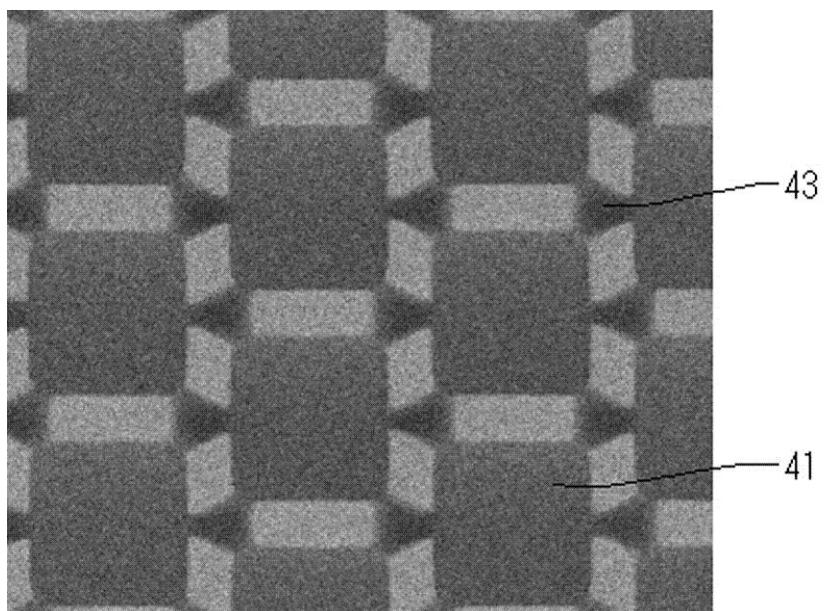

- 【図31】実施の形態1における炭化珪素半導体装置の上面の電子顕微鏡写真である。

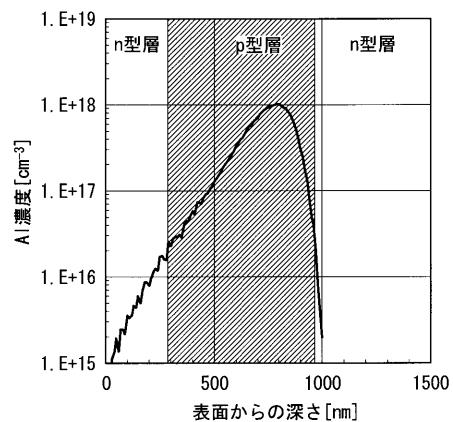

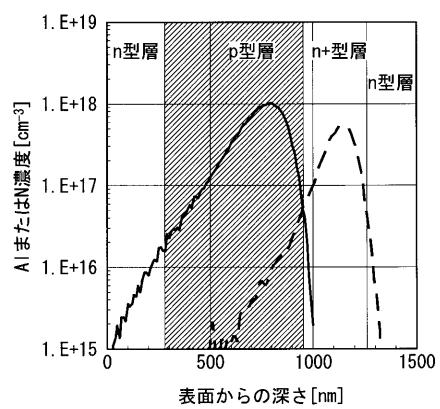

- 【図32】実施の形態1によって作製される炭化珪素半導体装置における不純物濃度分布を示す図である。

- 【図33】実施の形態2における炭化珪素半導体装置の上面図である。

- 【図34】実施の形態2における炭化珪素半導体装置の変形例の上面図である。

- 【図35】実施の形態2における炭化珪素半導体装置の変形例の上面図である。

- 【図36】実施の形態2における炭化珪素半導体装置の上面図である。

- 【図37】実施の形態2における炭化珪素半導体装置の変形例の上面図である。 20

- 【図38】実施の形態2における炭化珪素半導体装置の変形例の上面図である。

- 【図39】実施の形態2における炭化珪素半導体装置の変形例の上面図である。

- 【図40】実施の形態2における炭化珪素半導体装置の変形例の上面図である。

- 【図41】実施の形態3における炭化珪素半導体装置の上面図である。

- 【図42】実施の形態3における炭化珪素半導体装置の変形例の上面図である。

- 【図43】実施の形態3における炭化珪素半導体装置の変形例の上面図である。

- 【図44】実施の形態3における炭化珪素半導体装置の上面図である。

- 【図45】実施の形態3における炭化珪素半導体装置の変形例の上面図である。

- 【図46】実施の形態3における炭化珪素半導体装置の変形例の上面図である。

- 【図47】実施の形態3における炭化珪素半導体装置の製造方法における縦断面図である。 30

- 。 【図48】実施の形態3における炭化珪素半導体装置の製造方法における縦断面図である。

- 。 【図49】実施の形態3における炭化珪素半導体装置の製造方法における縦断面図である。

- 。 【図50】実施の形態4における炭化珪素半導体装置の製造方法における縦断面図である。

- 。 【図51】実施の形態4によって作製される炭化珪素半導体装置における不純物濃度分布を示す図である。

#### 【発明を実施するための形態】

##### 【0012】

以下の記載では、不純物の導電型に関して、n型を「第1導電型」と、p型を「第2導電型」として一般的に定義するが、その逆の定義でも構わない。

##### 【0013】

< A . 実施の形態1 >

< A - 1 . 構成 >

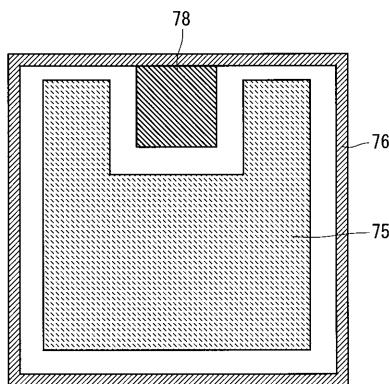

図1は、本実施の形態1に係る炭化珪素半導体装置、具体的には、セル構造からなるMOS構造を備えたスイッチング素子を有する炭化珪素MOSFETの上面構成を模式的に示す上面図である。

##### 【0014】

本装置の4つの側面の内の1側面の上端中央部には、外部の制御回路(図示せず)から

ゲート電圧が印加されるゲートパッド 7 8 が形成されている。また、MOSFET の最小単位構造であるユニットセルが複数個並列配置された活性領域に、ユニットセルのソース電極を並列接続したソースパッド 7 5 が形成されている。そして、ソースパッド 7 5 の周囲に、ゲート配線 7 6 がゲートパッド 7 8 と接続して形成されている。各ユニットセルのゲート電極（図示せず）には、ゲートパッド 7 8 に印加されるゲート電圧が、ゲートパッド 7 8 およびゲート配線 7 6 を通じて供給される。

#### 【0015】

なお、通常の製品では、温度センサー及び電流センサー用の電極が半導体素子に形成されている場合が多いが、それらの電極の形成の有無は、後述する本素子の効果に何らの影響を及ぼすものでは無い。加えて、ゲートパッド 7 8 の位置、個数及びソースパッド 7 5 の形状等も MOSFET によっては多種多様のケースが有り得るが、それらも、上記の電流センサー用電極等と同様に、後述する本装置の効果に何らの影響を及ぼすものでは無い。10

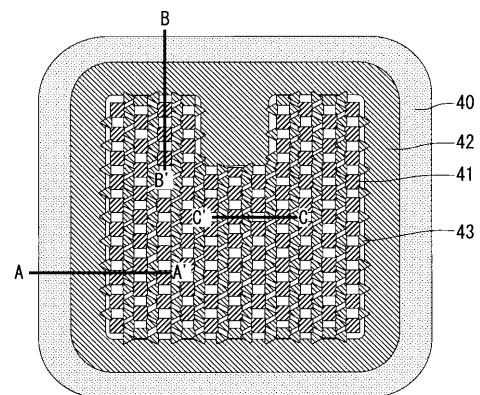

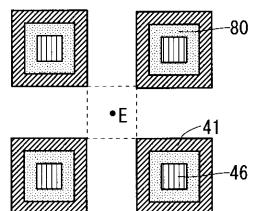

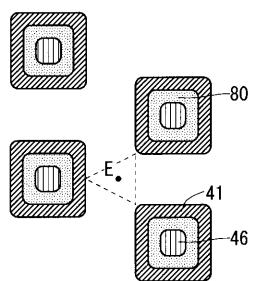

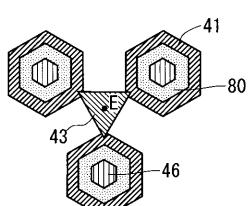

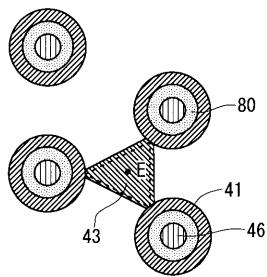

#### 【0016】

図 2 は、本実施の形態 1 に係る炭化珪素 MOSFET の、炭化珪素内部の最表面近傍を模式的に示す上面図である。互いに孤立した第 2 導電型の第 1 ウェル領域 4 1 内に、第 1 導電型のソース領域 8 0 と第 2 導電型のウェルコンタクト領域 4 6 が設置されている。

#### 【0017】

第 1 ウェル領域 4 1 群はそれを取り囲むように第 2 導電型の周縁領域 4 2 で取り囲まれておあり、さらに該周縁領域 4 2 は素子終端の第 2 導電型の JTE 領域 4 0 で取り囲まれておいる。周縁領域 4 2 には、ソース電極（図示せず）とオーミック接続させるための第 2 導電型のウェルコンタクト領域 4 7 が設置されている。20

#### 【0018】

第 1 ウェル領域 4 1 のギャップ領域に存在するのが JFET 領域であり、装置のオン動作時にオン電流が流れる経路の一つであり、またこのギャップ領域が、この上方に形成されるゲート電極（図示せず）と裏面に形成されるドレイン電極（図示せず）との間の容量（帰還容量）の大きさを決定する要素の一つである。

#### 【0019】

なお、本実施の形態 1 においては、図 2 に示すようにユニットセルが四角形で列に対して半周期ずらして互い違いに配列されている形態を記載するが、これに限らず、ユニットセルが長方形や六角形でも良いし、縦横に等ピッチで配列されていても、本発明の効果は何ら変わらない。30

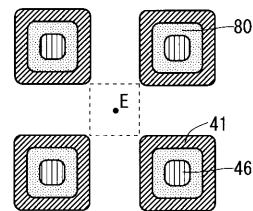

#### 【0020】

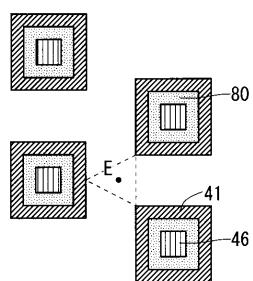

図 3 は、本実施の形態 1 に係る炭化珪素 MOSFET の、炭化珪素表面からある距離、すなわち、第 1 ウェル領域 4 1 程度の深さのところを模式的に示す上面図である。ここでは、第 1 ウェル領域 4 1 を互いに接続するように、第 2 導電型の第 2 ウェル領域 4 3 が形成されている。

#### 【0021】

第 2 ウェル領域 4 3 は、半導体基板内部にのみ設置され、JFET 領域の一部に設置されている。第 2 ウェル領域 4 3 を設置することで、JFET 領域の開口面積が減少するため帰還容量が低減される。なお、第 2 ウェル領域 4 3 は、素子に逆バイアスが印加されたときに、その基板表面への投影面上で最もゲート電界強度が高くなる位置を少なくとも覆うように配置され、さらにその平面構造は後述するように多様な形態があり得る。40

#### 【0022】

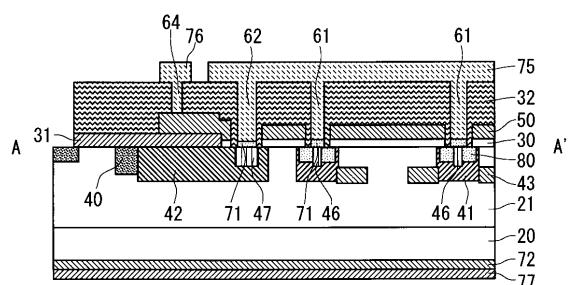

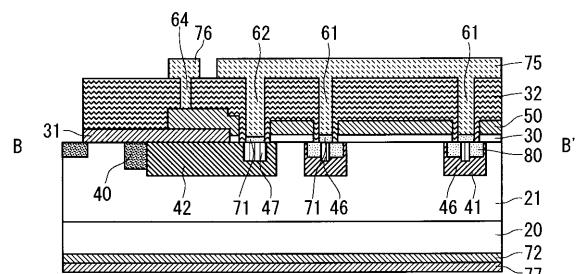

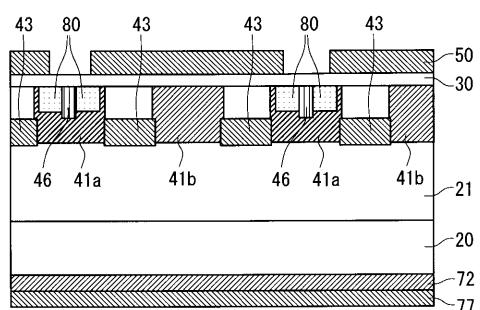

図 4 は図 3 に示す A - A' 間の断面、図 5 は図 3 に示す B - B' 間の断面を模式的に示す縦断面図である。

#### 【0023】

図 4 に示すように、本発明にかかる炭化珪素 MOSFET は、第 1 導電型の半導体基板 2 0 表面上に形成された第 1 導電型のドリフト層 2 1 と、半導体基板 2 0 の裏面側に形成された、オーミック電極 7 2 およびドレイン電極 7 7 と、ドリフト層 2 1 表面上に選択的に50

複数形成された第2導電型の第1ウェル領域41と、第1ウェル領域41表面に選択的に形成された領域であって、当該領域とドリフト層21とで挟まれた第1ウェル領域41表面をチャネル領域として規定する第1導電型のソース領域80と、第1ウェル領域41およびソース領域80内に形成された第2導電型のウェルコンタクト領域46と、ゲート電極50下のドリフト層21内部において埋没しあつ、互いに隣り合う第1ウェル領域41のそれぞれと接続して形成された第2導電型の第2ウェル領域43と、ドリフト層21表面において、第1ウェル領域41を含むセル領域を平面視包囲して選択的に形成され、ソース電極(ソースパッド75)と接続された第2導電型の周縁領域42と、周縁領域42表面に形成された第2導電型のウェルコンタクト領域47と、ドリフト層21表面において周縁領域42を囲むように形成された第2導電型のJTE領域40と、ドリフト層21表面に、第1ウェル領域41および周縁領域42の一部を覆うように形成されたゲート絶縁膜30と、ゲート絶縁膜30が形成されないドリフト層21表面に形成されたフィールド酸化膜31と、チャネル領域上からドリフト層21上に渡って、ゲート絶縁膜30およびフィールド酸化膜31を介して形成されたゲート電極50と、ゲート電極50およびフィールド酸化膜31上に形成された層間絶縁膜32と、層間絶縁膜32を貫通して、ゲート電極50に到達するゲートコンタクトホール64と、ゲートコンタクトホール64上に形成されたゲート配線76と、層間絶縁膜32およびゲート電極50を貫通して、ウェルコンタクト領域47上に形成されたオーミック電極71に到達するウェルコンタクトホール62と、層間絶縁膜32およびゲート電極50を貫通して、ウェルコンタクト領域46上に形成されたオーミック電極71にそれぞれ到達するソースコンタクトホール61と、ソースコンタクトホール61上に形成されたソースパッド75とを備える。このソースパッド75は、換言すれば、ソース領域80と接続されるとともに、第1ウェル領域41と周縁領域42とのみ直接接続されて形成されたソース電極である。

10

#### 【0024】

第2ウェル領域43は、第1導電型のドリフト層21の表面から離れた位置で第1ウェル領域41と周縁領域42と接続している。そして、図2に示すユニットセルの配置に対しては、その断面方向によって図4及び図5に示すように異なった断面形状を有する。

#### 【0025】

なお図5に示す場合は、図4に示す場合と断面方向が異なるが、第2ウェル領域43が断面に現れないことを除けば、ほぼ同様であるので、詳細な説明は省略する。

30

#### 【0026】

##### < A - 2 . 製造方法 >

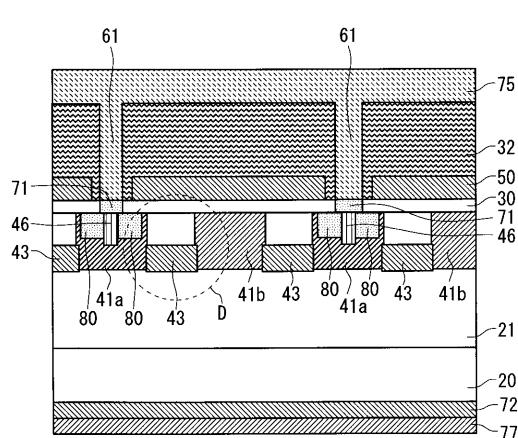

次に、図6～図15に示す模式的な縦断面図を参照して、本実施の形態1に係る炭化珪素半導体装置、具体的には炭化珪素MOSFETの製造方法について記載する。なお、図6～15に示す縦断面図は、素子終端部を含まない、ユニットセルが多数配列された任意の位置で、例えば図3のC-C'の位置の縦断面図を示したものである。

#### 【0027】

先ず、第1導電型の炭化珪素から成る半導体基板20を用意する。半導体基板20には炭化珪素のほか、珪素に比べてバンドギャップの大きい他のワイドバンドギャップ半導体を用いても良い。ワイドバンドギャップ半導体としては、炭化珪素の他、例えばGaNやダイヤモンド等がある。半導体基板20は、c軸方向に対して8°以下に傾斜されていても良いし、或いは、傾斜していないくとも良く、どの様な面方位を有していても、本実施の形態1の効果に影響を及ぼさない。

40

#### 【0028】

半導体基板20の上方にはエピタキシャル結晶成長層(不純物濃度は例えば $1 \times 10^{13}$  cm<sup>-3</sup>～ $1 \times 10^{18}$  cm<sup>-3</sup>の範囲内であり、厚みは4μm～200μmである)より成る第1導電型のドリフト層21を有する。

#### 【0029】

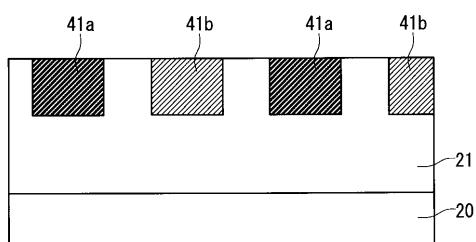

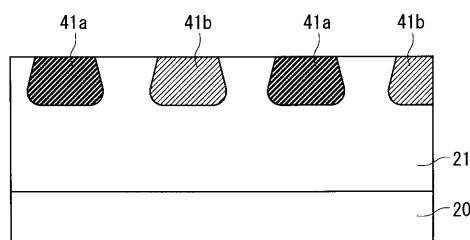

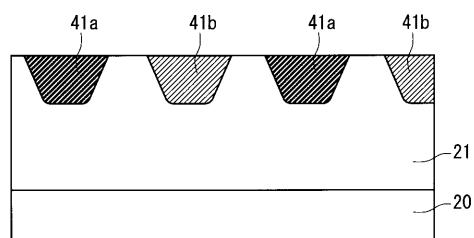

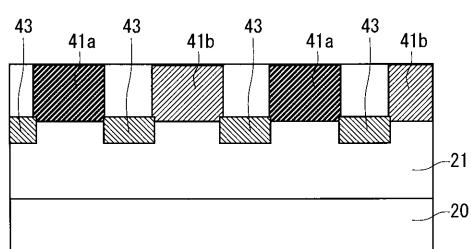

その後、図6を参照して、フォトリソグラフィーにより加工されたレジストマスクまたは酸化膜マスクなどをを利用して不純物のイオン注入を行い、第2導電型の第1ウェル領域

50

4 1 a を形成する。なお、図 6 には、該断面とはユニットセル列が半周期ずれたところに存在する第 1 ウェル領域 4 1 b を理解を助けるために記載している。

#### 【 0 0 3 0 】

注入時の半導体基板 2 0 は積極的に加熱を行わなくても良いし、2 0 0 ~ 8 0 0 で加熱して行っても良い。また注入不純物としては、導電型が n 型の場合には窒素又はリンが好適であり、導電型が p 型の場合にはアルミニウム又は硼素が好適である。

#### 【 0 0 3 1 】

また第 1 ウェル領域 4 1 a の深さは、ドリフト層 2 1 の底面を超えない様に設定する必要があり、例えば 0 . 3  $\mu\text{m}$  ~ 2 . 0  $\mu\text{m}$  の範囲内の値とする。また、第 1 ウェル領域 4 1 a の不純物濃度はドリフト層 2 1 の不純物濃度を超えており、かつ、例えば  $1 \times 1 0 1 5 \text{ cm}^{-3}$  ~  $1 \times 1 0 1 9 \text{ cm}^{-3}$  の範囲内に設定される。但し、ドリフト層 2 1 の最表面近傍に限っては、炭化珪素半導体装置のチャネル領域における導電性を高めるために、第 1 ウェル領域 4 1 a の不純物濃度がドリフト層 2 1 の不純物濃度を下回っていても良い。

#### 【 0 0 3 2 】

なお、第 1 ウェル領域 4 1 a の分布は、図 7 に示すように深さ方向に横方向広がりが多い形状であっても（逆テーパー形状）、図 8 に示すように深さ方向に横方向広がりが少ない形状であっても（テーパー形状）よい。特に、第 1 ウェル領域 4 1 a の分布として最表面側の不純物濃度を薄く、奥側を濃くなるように不純物のイオン注入によって形成した場合、奥側における注入不純物の横方向への散乱が大きくなるため、図 7 のような構造が容易に得られる。

#### 【 0 0 3 3 】

次に、図示しないが第 2 導電型の周縁領域 4 2 、第 2 導電型の J T E 領域 4 0 を同様に不純物のイオン注入によって形成する。なお、第 1 ウェル領域 4 1 と周縁領域 4 2 の不純物濃度及び注入深さは、同一であれば 1 度の写真製版処理によってパターニングしても良く、その場合、処理工数の削減やチップコストの低減に繋がるが、同一でなくとも良い。すなわち、チャネルの伝導に寄与しない周縁領域 4 2 においては、素子のスイッチングによって誘起される電荷による電位発生による素子破壊を防ぐために第 2 導電型の導電率を高くする目的で、より高濃度で第 2 導電型の不純物を注入しても良い。

#### 【 0 0 3 4 】

なお図 4 に示すように、周縁領域 4 2 と J T E 領域 4 0 とは、ドリフト層 2 1 内で接続されている。また図 4 に示すように、第 1 ウェル領域 4 1 と周縁領域 4 2 とは、ドリフト層 2 1 内で直接接続されていない。

#### 【 0 0 3 5 】

続いて、図 9 に示すように、フォトリソグラフィーにより加工されたレジストマスクまたは酸化膜マスクなどを利用して不純物のイオン注入を行い、第 2 導電型の第 2 ウェル領域 4 3 を形成する。第 2 ウェル領域 4 3 の深さは、ドリフト層 2 1 の底面を超えない様に設定し、例えば 0 . 3  $\mu\text{m}$  ~ 3 . 0  $\mu\text{m}$  の範囲内の値とする。第 2 ウェル領域 4 3 の不純物濃度は、ドリフト層 2 1 の不純物濃度を超えており、且つ、例えば  $1 \times 1 0 1 5 \text{ cm}^{-3}$  ~  $1 \times 1 0 2 1 \text{ cm}^{-3}$  の範囲内に設定され、より好ましくは、 $1 \times 1 0 1 6 \text{ cm}^{-3}$  ~  $1 \times 1 0 1 9 \text{ cm}^{-3}$  の範囲内に設定される。第 2 ウェル領域 4 3 の不純物濃度は、第 1 ウェル領域 4 1 の不純物濃度とは異なっていてもよい。第 2 ウェル領域 4 3 は、図 9 に示すように、第 1 ウェル領域 4 1 と同じ深さに形成されていても良く、図 1 0 に示すように、第 1 ウェル領域 4 1 a よりも深く形成されていても良い。但し図 1 0 においても、第 1 ウェル領域 4 1 a と第 2 ウェル領域 4 3 とは、第 1 ウェル領域 4 1 a の下部で接続されている。

#### 【 0 0 3 6 】

なお、第 2 ウェル領域 4 3 は、第 1 ウェル領域 4 1 a 、4 1 b 間の J F E T 領域に形成されるが、その平面配置及び構造については後述する。

#### 【 0 0 3 7 】

第 2 ウェル領域 4 3 は第 1 ウェル領域 4 1 a とは同時に形成されない。また、第 2 ウェル領域 4 3 は、第 1 ウェル領域 4 1 a と周縁領域 4 2 とを接続するように形成される。

10

20

30

40

50

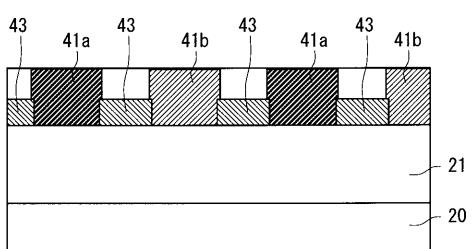

## 【0038】

次に、図11に示すように、フォトリソグラフィーにより加工されたレジストマスクまたは酸化膜マスクなどを利用して不純物のイオン注入を行い、第1導電型のソース領域80、第1導電型のフィールドストッパー領域（図示せず）を形成する。第1導電型のソース領域80の深さに関しては、その底面が第1ウェル領域41の底面を超えない様に設定され、その不純物濃度の値は、第1ウェル領域41の不純物濃度の値を超えており、且つ、その値は例えば $1 \times 10^{17} \text{ cm}^{-3}$ ～ $1 \times 10^{21} \text{ cm}^{-3}$ の範囲内の値に設定されている。

## 【0039】

さらに、第1ウェル領域41、周縁領域42とソースパッド75との良好な金属接触を実現するために、第1ウェル領域41、周縁領域42の不純物濃度よりも高い第2導電型の不純物濃度を有するウェルコンタクト領域46、ウェルコンタクト領域47（図示せず）をイオン注入により形成する。尚、該イオン注入は、150以上に基板温度で実行されることが望ましい。このような温度範囲にすることで、シート抵抗の低い第2導電型の層が形成される。なお、図11から図15までにおいて、第1ウェル領域41bにおいても第1ウェル領域41aと同様にソース領域80及びウェルコンタクト領域46が形成されるが、ここでは理解を助けるために図示していない。

## 【0040】

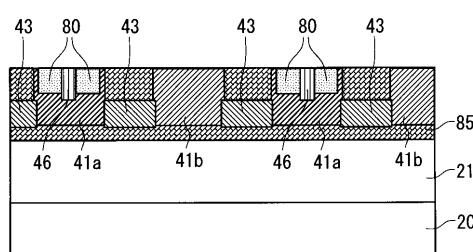

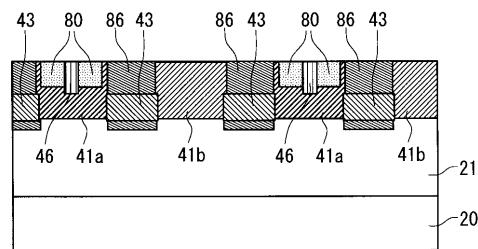

なお、この直後、もしくはこれまでの注入工程のどこかで、もしくはこれまでの注入工程の始めに、図12に示すように基板全面に第1導電型の不純物をイオン注入して、ゲート電極50下のドリフト層21表面において、ドリフト層21の不純物濃度よりも高い不純物濃度を有する第1導電型の第2不純物領域としての高濃度層85を形成しても良いし、図13に示すように、フォトリソグラフィーにより加工されたレジストマスクまたは酸化膜マスクなどを利用してJFET領域に第1導電型の不純物のイオン注入を行い、第1導電型の第2不純物領域としての電流制御層86を形成しても良い。これらはいずれもJFET領域の抵抗を低減することができるため、本装置のオン抵抗を低減することができる。

## 【0041】

なお高濃度層85及び電流制御層86の不純物濃度は、第1ウェル領域41内の第2導電型の最大不純物濃度よりも低く、第2ウェル領域43内の第2導電型の最大不純物濃度よりも低く、ドリフト層21内の第1導電型の不純物濃度よりも高い。その値は例えば $1 \times 10^{16} \text{ cm}^{-3}$ ～ $1 \times 10^{18} \text{ cm}^{-3}$ の範囲内に設定されており、その深さ方向の濃度分布は一様でなくても良い。さらに、高濃度層85及び電流制御層86は、第2ウェル領域43の最表面深さよりも浅くてもJFET抵抗の低減効果を奏するが、図12及び図13に示すように第1ウェル領域41の深さよりも深くまで形成されていても構わない。この場合は、JFET抵抗の減少と共に、JFET領域の広がり抵抗が減少することで、炭化珪素半導体装置のオン抵抗が減少する。特に、図12に示す高濃度層85が第1ウェル領域41の深さよりも深く形成されている構造によれば、逆バイアス印加時における第1ウェル領域41とドリフト層21との間のアバランシェ降伏をより安定に起こさせる効果もある。

## 【0042】

なお、高濃度層85は、図6で示すイオン注入を行う前に、ドリフト層21上にエピタキシャル成長されたものであっても良い。さらに、高濃度層85と電流制御層86との両方を形成しても良い。

## 【0043】

その後、アルゴン又は窒素等の不活性ガス雰囲気、若しくは、真空中に於いて1500～2200の範囲内の温度で0.5分～60分の範囲内の時間で熱処理を行うことで、注入された不純物が電気的に活性化する。該熱処理時においては、ドリフト層21の表面、もしくはドリフト層21の表面と半導体基板20の裏面と端面とを、炭素からなる膜で覆われた状態で行っても良い。このようにすることで、熱処理時における装置内の残留水分や残留酸素などによるエッチングによるドリフト層21の表面荒れ発生を防ぐことが

10

20

30

40

50

出来る。

**【0044】**

次に、熱酸化によるシリコン酸化膜の形成及びフッ酸による該酸化膜の除去によって表面変質層を除去して清浄な面を得た後に、活性領域のみを開口してそれ以外の領域をシリコン酸化膜で覆うフィールド酸化膜31をCVD法などによって堆積し、パターニングを行う(図示せず)。フィールド酸化膜31の膜厚は、0.5μm~2μmあれば良い。

**【0045】**

次に、図14に示すように、例えば熱酸化法又は堆積法又はそれらの後にNOやN<sub>2</sub>Oなどの窒化ガス雰囲気やアンモニア雰囲気における熱処理によって、ゲート絶縁膜30を形成する。

10

**【0046】**

そして、ゲート電極材料となるポリシリコンをCVD法により堆積し、フォトリソグラフィー及びドライエッチングによってゲート電極50をパターニングし、図に示す構造を得る。このポリシリコンには、リンや硼素が含まれて低シート抵抗であることが望ましい。リンや硼素は、ポリシリコンの製膜中に取り込まれても良いし、イオン注入とその後の熱処理によって活性化することによっても良い。さらに、このゲート電極はポリシリコンと金属及び金属間化合物の多層膜であっても良い。

**【0047】**

次に図15に示すように、層間絶縁膜32をCVD法などによって堆積した上で、例えばドライエッティング法によって、ソースパッド75によりその後に充填されるべきソースコンタクトホール61、ウェルコンタクトホール62(図示せず)を形成する。ここで、ゲート配線76(図示せず)により、その後に充填されるべきゲートコンタクトホール64(図示せず)を同時に形成しても良い。このようにすることでプロセス工程を簡略化でき、チップ製造時のコストを削減できる。

20

**【0048】**

次に、層間絶縁膜32が開口されているソースコンタクトホール61、ウェルコンタクトホール62(図示せず)の、炭化珪素が現れている部分にオーミック電極71を形成する。オーミック電極71は、ソース領域80とウェルコンタクト領域46、ウェルコンタクト領域47(図示せず)とのオーミック接触形成に用いられる。このオーミック電極71の形成方法としては、基板全面にNiを主とした金属膜を製膜したあとに、600~1100℃での熱処理によって炭化珪素との間にシリサイドを形成し、層間絶縁膜32上に残留したNiを主とした金属膜を、硝酸や硫酸や塩酸やそれらの過酸化水素水との混合液などを用いたウェットエッティングにより除去することで形成できる。

30

**【0049】**

なお、オーミック電極71を形成する過程で、半導体基板20の裏面に同様の金属膜を製膜した後に、熱処理を行って裏面のオーミック電極72を形成しても良い。このようにすることで、炭化珪素の半導体基板20と後に製膜するドレイン電極77間で良好なオーミック接触が形成される。

**【0050】**

なお、オーミック電極71はいたる所で同一の金属間化合物からなっていても良いし、p型n型のそれぞれに適した別々の金属間化合物からなっていても良い。すなわち、オーミック電極71は第1導電型のソース領域80に対して十分低いオーミックコンタクト抵抗を有していることが、作製されるMOSFETのオン抵抗低減に重要であるが、同時に第2導電型のウェルコンタクト領域46、ウェルコンタクト領域47(図示せず)に対しても、MOSFETに内蔵して作製されるボディーダイオードの順方向特性改善のために低コンタクト抵抗であることが求められるためである。これは、写真製版技術を用いて金属膜のパターニングをそれぞれで行うことで実現可能である。

40

**【0051】**

なお、層間絶縁膜32上に残留したNiを主とした金属膜を除去した後に、再度熱処理を行っても良い。ここでは先の熱処理よりも高温で行うことで、さらに低コンタクト抵抗

50

なオーミック接触が形成される。

**【0052】**

なお、先の工程でゲートコンタクトホール64(図示せず)が形成されいたら、ゲートコンタクトホール64の底面に存在するゲート電極50にシリサイド層が形成される。先の工程でゲートコンタクトホール64を形成していなければ、引き続いて写真製版とエッチングによって、ゲート配線76(図示せず)によりその後に充填されるべきゲートコンタクトホール64を形成する。

**【0053】**

引き続いて、Al、Cu、Ti、Ni、Mo、W、Taやそれらの窒化物やそれらの積層膜やそれらの合金から成る配線金属をスパッタ法や蒸着法によって形成し、その後にパターニングを行うことで、ゲート配線76、ゲートパッド78(図1参照)、ソースパッド75を形成する。更に、裏面のオーミック電極72上にTiやNiやAgやAuなどの金属膜を形成してドレイン電極77を形成することにより、図15で示される炭化珪素MOSFETが完成される。

**【0054】**

なお、本工程における終端領域を含む断面構造が図4及び図5である。また図示しないが、表面側をシリコン窒化膜やポリイミドなどの保護膜で覆っていても良い。それらは、ゲートパッド78及びソースパッド75のしかるべき位置で開口され、外部の制御回路と接続できるようになっている。

**【0055】**

< A - 3 . 動作 >

次に、本実施の形態により作製される炭化珪素半導体装置の動作と、第2ウェル領域43の平面配置について記載する。

**【0056】**

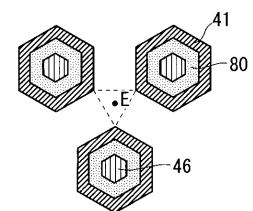

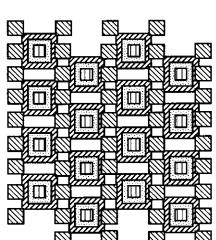

本実施の形態1の炭化珪素半導体装置は、MOSFETを構成する複数のユニットセルと、それらを取り囲むpnダイオードが電気的に並列に接続されている。このユニットセルの平面的な配置は、例えば図2で示したものを含めて図16～18に示す。図16～18はドリフト層21の最表面近傍の一部を表しており、図16は図1～5で示した四角形セルが互い違いに配置されたもの、図17は四角形セルが等間隔で配置されたもの、図18は六角形セルが最密充填で配置されたものである。

**【0057】**

第1ウェル領域41のギャップにはドリフト層21が存在しており、その直上には、ゲート絶縁膜30及びゲート電極50が存在している(図4参照)。

**【0058】**

ところで、ゲート電極とドレイン電極間の帰還容量は、該ギャップ領域の面積に概比例し、また、帰還容量が大きいほどMOSFETのスイッチング動作時における損失(スイッチング損失)が大きくなることが知られている。図15のDで囲む領域を見ると、対となる第1ウェル領域41a、41bの間隙に第2ウェル領域43が存在することによって、実効的な該ギャップ領域の面積が減少し、帰還容量が小さくなる効果がある。すなわち、スイッチング損失を低減させることが可能となる。

**【0059】**

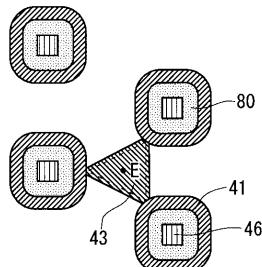

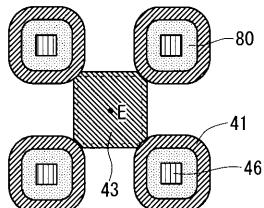

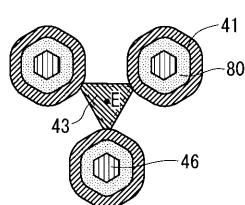

この第2ウェル領域43の平面配置について述べる。図2及び図16～18に示すセル構造をユニットセルに持つ縦型のMOSFETにおいて、ドレイン電極77に逆バイアスが印加されたオフ状態を保持するとき、JFET領域直上に存在するMOS構造のゲート絶縁膜30に高電界が誘起される。最も高電界となる箇所は、第1ウェル領域41からJFET領域に伸びる空乏層による遮蔽効果が弱くなる、図16～18にそれぞれEで示す地点である。すなわち、隣接する複数の第1ウェル領域41との距離の総和が最小となる平面視上の位置を覆うような地点である。

**【0060】**

特に、実際の製造プロセスにおいては、写真製版におけるレジストパターン精度に依存

10

20

30

40

50

して、図19～21にそれぞれ示すように、第1ウェル領域41などのパターンの角が丸みを帯びることがしばしばである。従って、地点Eにおける電界強度は、図16～18に示す場合よりもさらに高まることになる。

#### 【0061】

その様子を図30に示す。図30は、第1ウェル領域41を形成するA1注入直後の炭化珪素半導体表面の電子顕微鏡写真である。角がとがった正方形のクロムマスク(抜き)パターンを用いているが、写真製版後のレジストパターンにおいて角に半径0.5μm程度の丸みを帯びるために、第1ウェル領域41もこれを反映して、丸みを帯びた構造が形成されている様子がわかる。

#### 【0062】

従って、Eを含む近傍を第2導電型の層で覆うことが、ゲート絶縁膜30に印加される電界を弱めることになり、ゲート絶縁膜30の信頼性確保の観点からも好ましい。

#### 【0063】

その地点Eを覆いつつ、第1ウェル領域41を相互に接続させる第2ウェル領域43の平面的な配置(基板表面への投影図)を図22～25に示す。これらに対応する実際の配置を図26～29にそれぞれ示す。

#### 【0064】

図22、図23に示す四角形セルが交互配置されている場合は、第1ウェル領域41のセルの隣接する2つの領域の頂点と対向するセルの中央を結ぶ三角形の重心位置Eを含むように、図22で示す四角形や図23で示す三角形の第2ウェル領域43が挙げられる。第2ウェル領域43の面積が図22の方が大きいために、帰還容量の低減効果が大きく、一方図23においてはJFET領域を遮蔽する領域が少ないので、JFET領域のオン動作時の抵抗増を抑止できる。

#### 【0065】

図24の四角形セル及び図25の六角形セルにおいては、第1ウェル領域41のセルの隣接する4つないし3つの領域の頂点を結ぶ四角形ないし三角形の重心位置を含むように、図24で示す四角形や図25で示す三角形が挙げられる。

#### 【0066】

図31に、図27の構造を実際に作製した炭化珪素半導体表面の電子顕微鏡写真を示す。丸みを帯びた四角形の第1ウェル領域41に対して、隣接する第1ウェル領域41間に三角形の第2ウェル領域43が形成され、第2ウェル領域43が第1ウェル領域41を相互に接続させている。第2ウェル領域43を配置することで、第1ウェル領域41の角が丸みを帯びることによる地点E(図23参照)における電界強度上昇を抑え、かつ帰還容量を低減することができる。

#### 【0067】

本発明の特徴的な点は、図22～図25に図示したように、第1ウェル領域41を第2ウェル領域43によって接続することで、帰還容量の低減やゲート絶縁膜30への高電界印加抑止による信頼性向上、さらには、ボディーダイオードの接合面積増加による順方向電流の増加などの効果を奏することである。さらに、図4、図5や図15に示すように、第2ウェル領域43がドリフト層21の最表面に存在していないことで、オン抵抗の大きな増大を生じさせること無く帰還容量の低減を行えることである。

#### 【0068】

図22～図25に示す第2ウェル領域43がドリフト層21の最表面まで延在していると、第1ウェル領域41とソース領域80及びJFET領域によって表面に形成されるチャネルの一部を第2導電型領域で閉塞してしまうことで、単位セル面積当たりのチャネル幅を減少させ、更には、JFET領域にオン動作時にゲート電界によって誘起されるキャリアの生成領域を奪うことで、オン抵抗を増加させる。

#### 【0069】

本発明は第2ウェル領域43がドリフト層21の表面に存在しないために、このような不具合を発生させないことから、オン抵抗の大きな増大を生じさせること無く帰還容量の

10

20

30

40

50

低減を行える特徴がある。

#### 【0070】

このような第2ウェル領域43の構造は、図32の数値計算結果に示すように、炭化珪素からなるドリフト層21に例えばA1の700keV注入を行うことで、JFET領域のn型層を持ちつつ、およそ深さ0.3μm~1.0μmまでをp型層、さらに1.0μmから奥側でn型層という構造を作製できる。ここで、図の縦軸はA1濃度を示し、横軸は表面からの深さ(nm)を示す。ドリフト層21の最表面まで延在しないように、p型層が形成される。なお、本計算ではドリフト層の不純物濃度を $2 \times 10^{16} \text{ cm}^{-3}$ とした。特に炭化珪素中の不純物の熱拡散が従来のシリコン中の熱拡散に比べて少なく、高温の活性化熱処理を施しても注入時の分布をほぼ保ち、熱拡散による不純物濃度の平滑化が抑止されるため、図1~5や図6~15で示した第2ウェル領域43の構造が容易に作製される。10

#### 【0071】

##### < A - 4 . 効果 >

本発明にかかる実施の形態1によれば、半導体装置において、第1導電型の半導体基板20と、半導体基板20表面上に形成された、第1導電型のドリフト層21と、ドリフト層21表面に選択的に複数形成された、第2導電型の第1ウェル領域41と、各第1ウェル領域41表面に選択的に形成された領域であって、当該領域とドリフト層21とで挟まれた各第1ウェル領域41表面をチャネル領域として規定する第1導電型のソース領域80と、チャネル領域上からドリフト層21上に渡って、絶縁膜であるゲート絶縁膜30を介して形成されたゲート電極50と、ゲート電極50下のドリフト層21内部において埋没しあつ、互いに隣り合う各第1ウェル領域41のそれぞれと接続して形成され、平面視で複数の第1ウェル領域41間の領域の一部を覆う複数の第2導電型の第2ウェル領域43と、ソース領域80と接続されるとともに、第1および第2ウェル領域41、43のうち第1ウェル領域41とのみ直接接続されて形成されたソース電極と、半導体基板20裏面に形成されたドレイン電極77とを備えることで、チャネル領域とならない位置に第2ウェル領域43を形成し、チャネル幅の減少によるチャネル抵抗、JFET抵抗の増加を招かずに帰還容量を低減し、半導体装置のオン損失、スイッチング損失を低減することが可能となる。20

#### 【0072】

また、本発明にかかる実施の形態1によれば、半導体装置において、第1ウェル領域41と第2ウェル領域43とは、第2導電型の不純物濃度分布が異なることで、チャネル特性に影響を与えずに帰還容量を低減することが可能となる。30

#### 【0073】

また、本発明にかかる実施の形態1によれば、半導体装置において、第2ウェル領域43は、自身が接続する複数の第1ウェル領域41との距離の総和が最小となる平面視上の位置を覆うように形成されることで、逆バイアス時におけるゲート絶縁膜30への高電界印加が抑制されて、ゲート絶縁膜30の信頼性が向上する。

#### 【0074】

また、本発明にかかる実施の形態1によれば、半導体装置において、ゲート電極50下のドリフト層21表面において、ドリフト層21の不純物濃度よりも高い不純物濃度を有する第1導電型の第2不純物領域である高濃度層85、電流制御層86をさらに備えることで、JFET領域の抵抗を低減することが可能となる。40

#### 【0075】

また、本発明にかかる実施の形態1によれば、半導体装置において、半導体基板20がワイドバンドギャップ半導体により構成されることにより、耐電圧性が向上し、許容電流密度が高くなるため、半導体装置の小型化が可能となる。また電力損失が低くなるため、半導体装置の高効率化が可能である。

#### 【0076】

##### < B . 実施の形態2 >

50

20

30

40

50

## &lt; B - 1 . 構成 &gt;

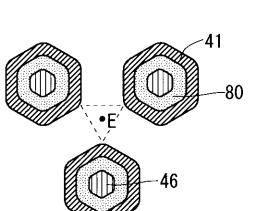

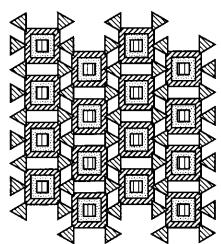

図 3 3 ~ 3 5 は、本実施の形態 2 に係る炭化珪素半導体装置、具体的には炭化珪素 M O S F E T のユニットセルを示す図であり、図 3 6 ~ 4 0 は、本実施の形態 2 に係る炭化珪素半導体装置、具体的には炭化珪素 M O S F E T のユニットセルと第 2 ウェル領域 4 3 の平面配置を示す図（基板表面への投影図）である。

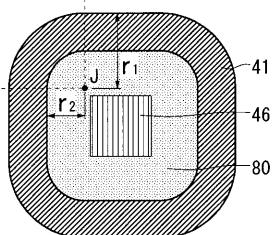

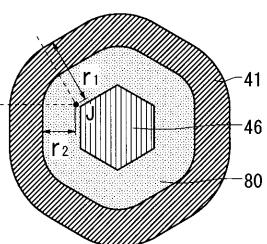

## 【 0 0 7 7 】

本実施の形態 2 においては、ドリフト層 2 1 表面における第 1 ウェル領域 4 1 とソース領域 8 0 の間隙で定義されるチャネル長がユニットセル内の至るところで同一である。

## 【 0 0 7 8 】

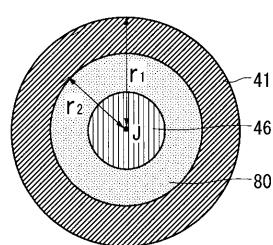

すなわち、図 3 3 に示す四角形のユニットセルの角部においては、地点 J を中心とする 90° の円弧パターン（半径 r 1 及び半径 r 2 ）によってそれぞれ第 1 ウェル領域 4 1 及びソース領域 8 0 が形成される。 10

## 【 0 0 7 9 】

また、図 3 4 に示す六角形のユニットセルの角部においては、地点 J を中心とする 60° の円弧パターン（半径 r 1 及び半径 r 2 ）によってそれぞれ第 1 ウェル領域 4 1 及びソース領域 8 0 が形成される。

## 【 0 0 8 0 】

さらに、図 3 5 に示す円形のユニットセルにおいては、ユニットセルの中心となる地点 J を中心とする円弧パターン（半径 r 1 及び半径 r 2 ）によってそれぞれ第 1 ウェル領域 4 1 及びソース領域 8 0 が形成される。 20

## 【 0 0 8 1 】

## &lt; B - 2 . 動作 &gt;

このような第 1 ウェル領域 4 1 及びソース領域 8 0 を形成することで、ユニットセル内におけるチャネル長が均一化される。従来の例えば図 1 6 に示す正方形のユニットセルの角部においては、角部以外の場所に比べて第 1 ウェル領域 4 1 及びソース領域 8 0 の間隙が最大で 1.41 倍長くなっている。この部分でのチャネル抵抗が高くなっていた。さらには、角の頂点近傍では、角を形成する二辺（二方向）からの距離が最短となって電流集中が発生していた。すなわち、角部においてはオン電流の分布が不均一であり、素子信頼性の観点からは問題であった。本実施の形態によるユニットセル構造においては、チャネル長がユニットセル内の至る所で一定であるために、過度の電流集中が発生せず、素子の信頼性を向上する効果を奏する。 30

## 【 0 0 8 2 】

なお、このような第 1 ウェル領域 4 1 及びソース領域 8 0 の形成方法については、それ別々のマスクを用いた不純物のイオン注入によてもよいが、第 1 ウェル領域 4 1 のマスクを用いたウェル注入処理後に、マスクをチャネル長の分だけ太らせてソース注入のマスクとしても良いし、ソース領域 8 0 のマスクを用いたソース注入処理後に、チャネル長の分だけ細らせてウェル注入のマスクとしても良い。例えば多結晶シリコンを用いたウェル注入マスクに対して、注入処理後に酸化処理を施して多結晶シリコンの周囲に熱酸化膜を形成して複合マスクとしてソース注入を行うことで、体積増加分に対応したチャネル長を実現することができる。また、シリコン酸化膜やフォトレジストを用いたソース注入マスクに対して、注入処理後に酸化膜やレジストの等方性エッチングを行った後にウェル注入を行うことで、体積減少分に対応したチャネル長を実現することができる。 40

## 【 0 0 8 3 】

このようなチャネル長決定のセルファアライン手法は、ユニットセルの中心に対して対称性の優れた図 3 5 に示す円形のユニットセル構造において、一定のチャネル長を実現する上でより効果を奏する。これは、酸化やエッチングなどの化学的な手法によって注入マスクの構造変形を行う場合、角部と直線部分とでは反応速度が異なることがしばしば発生するため、必ずしも全方位に同じ長さだけ体積増加分または体積減少するわけではなく、結果としてチャネル長のアンバランスを招くためである。

## 【 0 0 8 4 】

50

20

30

40

50

なお、図33と図34に示す四角形及び六角形の角部の曲率半径は、第1ウェル領域41よりも小さいソース領域80において0.5μm以上あれば、従来の写真製版技術によって十分解像される。また、曲率半径を大きくし過ぎると、四角形及び六角形の元々のチャネル幅に比較して減少幅が大きくなり、チャネル抵抗を増大させるため、ソース領域80の曲率半径として2.0μm程度あればよい。

#### 【0085】

ところで、チャネル長を一定にするには、四角形のソース領域80の角部を90°、または六角形のソース領域の角部を120°のままにして丸みを持たせず、第1ウェル領域41の角部のみに丸みを持たせるユニットセル構造も考えられる。しかしながら、実施の形態1で示したように、上記のような鋭角パターンを注入マスクとして作製することは容易ではなく、図30に示すように丸みを帯びることがしばしばであり、結果としてチャネル長一定とはならない。例え鋭角パターンの注入マスクが形成できたとしても、オン電流はソース領域80の角部に集中することになり、信頼性の観点からは好ましくない。

10

#### 【0086】

ところで、図33～35に示す第1ウェル領域41のような角部に丸みを持たせたユニットセル構造においては、図36～40に示すように、丸みがない構造と比べて第1ウェル領域の間隙（JFET長）が一部で増加し、JFET開口領域にかかる電界が増加する懸念がある。ここで、本発明で示す第2ウェル領域43を配することで高電界印加を抑制し、ゲート酸化膜の信頼性劣化を抑制する効果を奏する。本構造によって帰還容量が低減され、またボディーダイオードの接合面積が増加することで、ボディーダイオードの順方向電流の増加がはかられることは言うまでもない。

20

#### 【0087】

##### <B-3.効果>

本発明にかかる実施の形態2によれば、半導体装置において、第1ウェル領域41とソース領域80との間隙がドリフト層21表面の至るところで同一であるので、オン動作時におけるチャネル領域のオン電流分布が均一化され、素子の信頼性が向上する。

#### 【0088】

また、本発明にかかる実施の形態2によれば、半導体装置において、第1ウェル領域41が円形である場合ユニットセルの中心に対して対称性が優れているので、セルファーライン手法を用いたマスクの形成により一定のチャネル長を実現することができる。

30

#### 【0089】

##### <C.実施の形態3>

##### <C-1.構成>

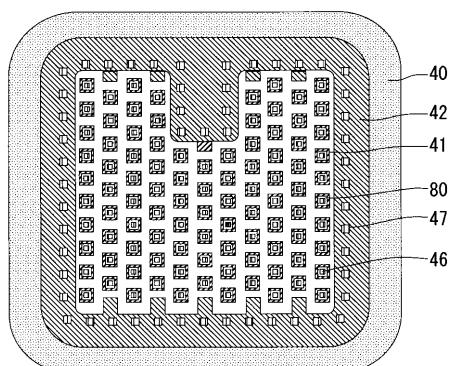

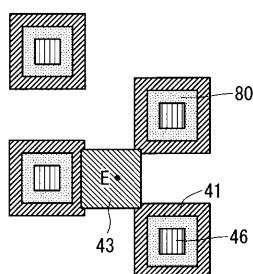

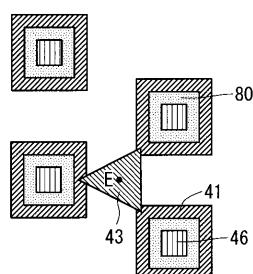

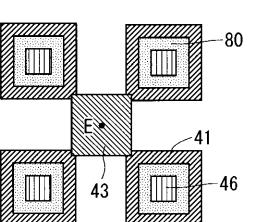

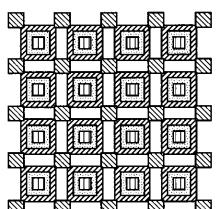

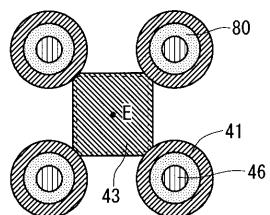

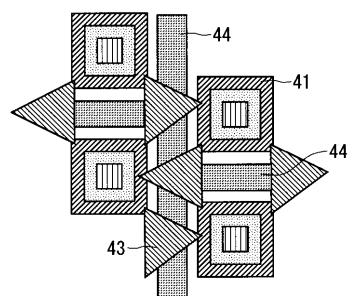

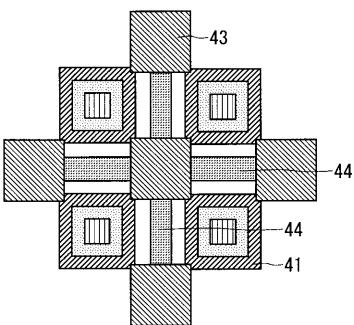

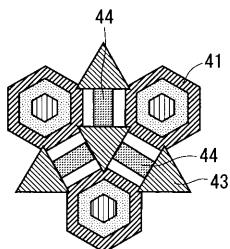

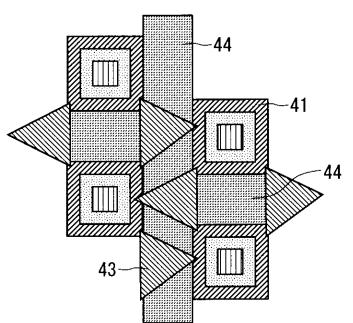

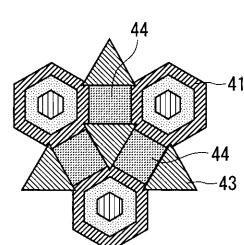

図41～43は、本実施の形態3に係る炭化珪素半導体装置、具体的には炭化珪素MOSFETのユニットセルの平面配置を示す図（基板表面への投影図）である。

#### 【0090】

本実施の形態3においては、孤立した複数の第2ウェル領域43間のドリフト層21内部に埋没しつつ、互いに隣り合う各第2ウェル領域43のそれぞれと接続して形成された第3ウェル領域44をさらに備える。

40

#### 【0091】

ここで、第3ウェル領域44はJFET領域もしくはその下方に存在し、ドリフト層21表面には存在していない。また、第2ウェル領域43と同じ深さ、または第2ウェル領域43よりも深く存在している。

#### 【0092】

すなわち、第3ウェル領域44は第1ウェル領域41とは直接接続していない。さらに、第3ウェル領域44は周縁領域42とは直接接続していない。

#### 【0093】

##### <C-2.動作>

このような第3ウェル領域44を形成することで、帰還容量の更なる低減によるスイッチング損失の低減が図られる。また、ボディーダイオードの接合面積がさらに増加するこ

50

とで、順方向電流の増加がはかられる。

**【0094】**

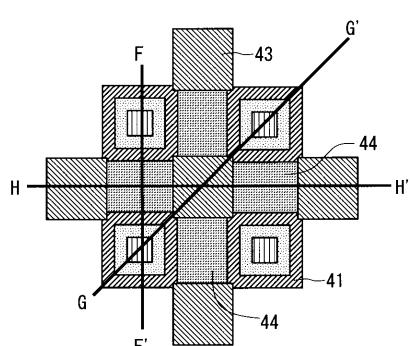

また、第2ウェル領域43が第1ウェル領域41と底面近傍で接し、第3ウェル領域44が第2ウェル領域43の底面近傍で接するような構造とすることで、第3ウェル領域44を挿入したことによるJFET領域の狭窄化が緩和される。すなわち、第1ウェル領域41と第3ウェル領域44のギャップが基板奥方向に広がるために、JFET抵抗の大幅な増加を防ぐことが出来る。さらに、図44～46に示す基板表面への投影図で見たときの第3ウェル領域44の配置、すなわち、JFET領域が第3ウェル領域44で全て埋められた構造とすることも、帰還容量の更なる低減のために効果的である。

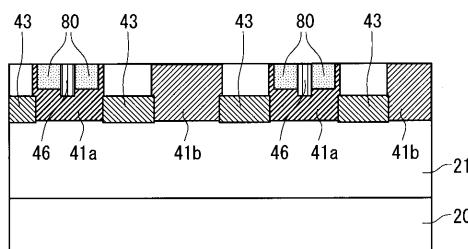

**【0095】**

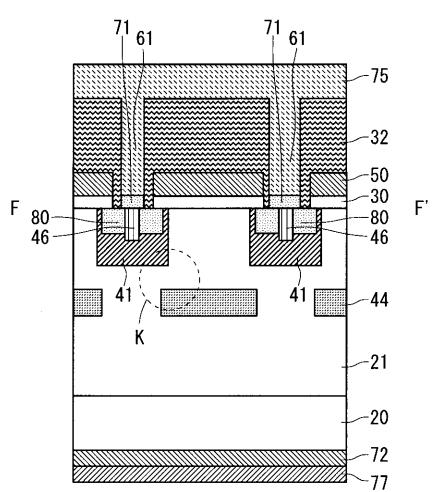

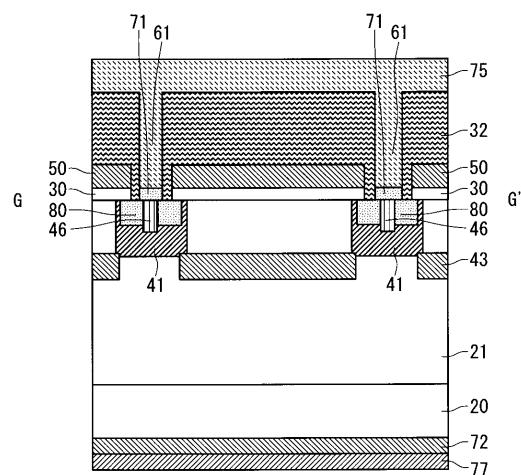

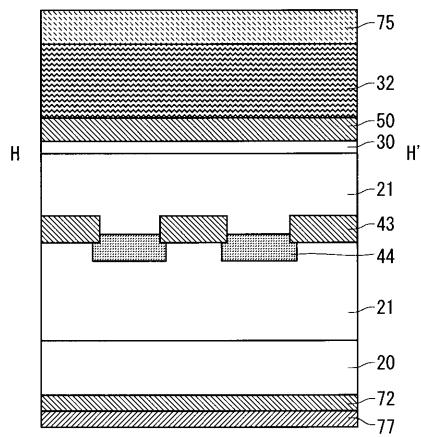

図45の平面構造について、図47～49にその詳細に説明する。図47～49は、図45におけるF-F'間、G-G'間、H-H'間の断面構造を示している。すなわち、第2ウェル領域43は図48に示すように、第1ウェル領域41とこの下方において接続されている。第3ウェル領域44は図49に示すように、第2ウェル領域43とこの下方において接続されている。図47に示すように、JFET開口領域はその下方の第3ウェル領域44によってその投影面が覆われているが、図47のKで示すように、第1ウェル領域41と第3ウェル領域44との間にギャップを設けて配置することもできる。このようにすることで、該ギャップをオン電流が流れるために、素子がオンしなくなる不具合を生じさせることなく、帰還容量の大幅な低減が行える。また、JFET領域の開口領域を立体的に広げることになり、オン抵抗を低減できる。なお、図47～49において示す構成は、第3ウェル領域44を有することを除いては実施の形態1に示した構成と同様であるので、他の構成の詳細な説明を省略する。

10

**【0096】**

< C - 3 . 効果 >

本発明にかかる実施の形態3によれば、半導体装置において、第2ウェル領域43を複数備え、複数の第1ウェル領域41間のドリフト層21内部に埋没しあつ、互いに隣り合う各第2ウェル領域43のそれぞれと接続して形成された、第2導電型の第3ウェル領域44をさらに備えることで、帰還容量とスイッチング損失の低減が可能となり、またボディーダイオードのオン電流を大きくできる。

20

**【0097】**

また、本発明にかかる実施の形態3によれば、半導体装置において、第3ウェル領域44の上面は、第1ウェル領域41の下面よりも下方に形成されることで、JFET領域の開口領域を立体的に広げることが出来るので、オン抵抗を低減できる。

30

**【0098】**

また、本発明にかかる実施の形態3によれば、半導体装置において、第2ウェル領域43および第3ウェル領域44は、平面視で複数の第1ウェル領域41間の領域を全て覆うように形成されることで、帰還容量の更なる低減が可能となる。

**【0099】**

< D . 実施の形態4 >

< D - 1 . 構成 >

40

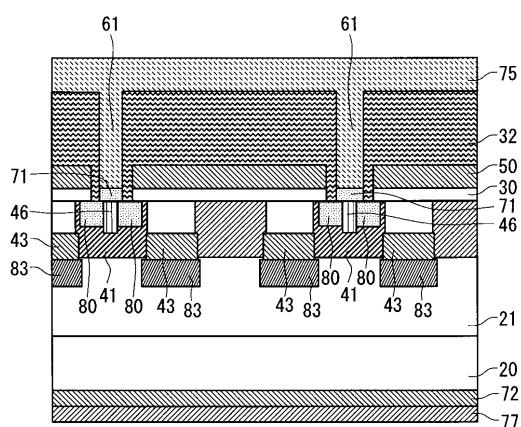

図50は、本実施の形態4に係る炭化珪素半導体装置、具体的には炭化珪素MOSFETのユニットセルの断面構造を示す図である。

**【0100】**

本実施の形態4においては、第2ウェル領域43を不純物の注入で形成したときに、ここで用いた注入マスクをそのまま用いて第1導電型の不純物を連続的に注入して、第1導電型の第1不純物領域としての電流広がり層83を設けたことに特徴がある。電流広がり層83は、ドリフト層21よりも高い不純物濃度を持ち、具体的には例えば $2 \times 10^{13} \text{ cm}^{-3}$ ～ $2 \times 10^{18} \text{ cm}^{-3}$ の範囲内であり、その深さはドリフト層21を超えず、せいぜい $1 \mu\text{m}$ である。なお、図50において示す構成は、電流広がり層83を有することを除いては実施の形態1に示した構成と同様であるので、他の構成の詳細な説明を省略する。

50

## 【0101】

&lt; D - 2 . 動作 &gt;

第2ウェル領域43の形成と同じマスクを用いた自己整合的な手法によって電流広がり層83を設けることによって、オン動作時にJFET領域を抜けた電流が低抵抗な電流広がり層83の存在する横方向へ広がりやすくなるため、JFET広がり抵抗を低減することができる。特に、電流広がり層83を第1導電型の不純物の注入によって形成することにより、注入時の横方向広がりの効果によって、同じ注入マスクを用いていても第2ウェル領域43よりもより横方向に広がった領域を作製できるため、JFET抵抗の低減効果はより顕著になる。

## 【0102】

10

なお、この第1導電型の不純物の注入時に、基板表面に対して鉛直方向から水平方向に若干傾斜した角度で注入（斜め注入）することによって、横方向広がりをさらに持たせて電流広がり層83を作製しても良い。

## 【0103】

20

このような電流広がり層83の広がり構造は、図51の数値計算結果に示すように、炭化珪素からなるドリフト層21に、例えばアルミニウムの700keV注入によるp型層と窒素の1.3MeV注入によるn+型層形成を行うことで、およそ深さ0.3μm~1.0μmまでの第2ウェル領域43の形成と、そこから1.3μm程度までの電流広がり層83という縦構造が作製できる。ここで、図の縦軸はA1またはN濃度を示し、横軸は表面からの深さ（nm）を示す。特に炭化珪素中の不純物の熱拡散が従来のシリコン中の熱拡散に比べて少なく、高温の活性化熱処理を施しても注入時の分布をほぼ保ち、熱拡散による不純物濃度の平滑化が抑止されるため、図51で示したような構造が容易に作製される。

## 【0104】

また、実施の形態3で示した第3ウェル領域44を形成時に、同様の自己整合的な手法によって、第3ウェル領域44の下方に第1導電型の電流広がり層83を形成しても、同様の効果を奏する。

## 【0105】

30

&lt; D - 3 . 効果 &gt;

本発明にかかる実施の形態4によれば、半導体装置において、第2ウェル領域43および/または第3ウェル領域44の下方に形成された、ドリフト層21の不純物濃度よりも高い不純物濃度を有する第1導電型の第1不純物領域である電流広がり層83をさらに備えることで、JFET領域の広がり抵抗を低減できる。

## 【0106】

尚、本実施の形態1、2、3、4で示される上記効果は、その構造を形成するための製造方法により効果に影響が出ることはない。従って、本実施の形態1、2、3、4で一例として記載した製造方法以外の製造方法を用いて本装置を作製したとしても、既述した効果に影響を与えるものではない。

## 【0107】

40

以上、本発明の実施の形態を詳細に開示し記述したが、以上の記述は本発明の適用可能な局面を例示したものであって、本発明はこれに限定されるものではない。即ち、記述した局面に対する様々な修正や変形例を、この発明の範囲から逸脱することの無い範囲内で考えることが可能である。

## 【0108】

また、本発明に於いては、半導体素子が縦型のMOSFETである場合を開示しているが、例えば図4に示す半導体基板20と裏面側のオーミック電極72との間に第2導電型からなるコレクタ層を設けることで、IGBTのセル領域を有する半導体素子を構成しても既述した本発明の効果が同様に奏される。従って、本発明の効力が及ぶ射程範囲は、MOSFET或いはIGBT等のMOS構造を有するスイッチング素子としての半導体素子であると言える。

50

## 【0109】

また、本発明に於いては、実施の形態1、2、3、4で記載したMOS構造を有する半導体素子自体を狭義の意味で「半導体装置」と定義する他、例えば、当該半導体素子を、当該半導体素子に対して逆並列に接続されるフリー・ホイール・ダイオード及び当該半導体素子のゲート電圧を生成・印加する制御回路等と共にリードフレームに搭載して封止して成るインバータモジュールの様な、当該半導体素子を組み込んで応用して成るパワーモジュール自体をも、広義の意味で「半導体装置」と定義する。

## 【0110】

この発明は詳細に説明されたが、上記した説明は、全ての局面において、例示であって、この発明がそれに限定されるものではない。例示されていない無数の変形例が、この発明の範囲から外れることなく想定され得るものと解される。

10

## 【産業上の利用可能性】

## 【0111】

この発明は、例えばインバータの様な電力変換器に適用して好適である。

## 【符号の説明】

## 【0112】

20 半導体基板、21 ドリフト層、30 ゲート絶縁膜、31 フィールド酸化膜、32 層間絶縁膜、40 JTE領域、41, 41a, 41b 第1ウェル領域、42 周縁領域、43 第2ウェル領域、44 第3ウェル領域、46, 47 ウェルコンタクト領域、50 ゲート電極、61 ソースコンタクトホール、62 ウェルコンタクトホール、64 ゲートコンタクトホール、71, 72 オーミック電極、75 ソースパッド、76 ゲート配線、77 ドレイン電極、78 ゲートパッド、80 ソース領域、83 電流広がり層、85 高濃度層、86 電流制御層。

20

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図11】

【図12】

【図13】

【図8】

【図9】

【図10】

【図14】

【図15】

【図16】

【図17】

【図18】

【図22】

【図23】

【図19】

【図20】

【図21】

【図24】

【図25】

【図26】

【図 2 7】

【図 2 8】

【図 2 9】

【図 3 2】

【図 3 3】

【図 3 4】

【図 3 5】

【図 3 6】

【図 3 7】

【図 3 8】

【図 3 9】

【図40】

【図41】

【図42】

【図43】

【図44】

【図46】

【図45】

【図47】

【図48】

【図49】

【図50】

【図51】

【図30】

【図31】

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 5 8 A |

| H 01 L | 29/78 | 6 5 2 J |

| H 01 L | 29/78 | 6 5 8 F |

| H 01 L | 29/78 | 6 5 2 F |

| H 01 L | 29/78 | 6 5 2 S |

(72)発明者 大塚 健一

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 渡辺 昭裕

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 渡邊 寛

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 杏 哲次

(56)参考文献 特開2008-258313(JP,A)

特開2007-150142(JP,A)

特開2007-281034(JP,A)

特開平05-102487(JP,A)

特開2011-211020(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 78

H 01 L 21 / 336

H 01 L 29 / 06

H 01 L 29 / 12