#### (19) 日本国特許庁(JP)

# 再 公 表 特 許(A1)

(11) 国際公開番号

W02011/036745

発行日 平成25年2月14日 (2013.2.14)

(43) 国際公開日 平成23年3月31日(2011.3.31)

| (51) Int.Cl.  |      |           | FΙ    |      |      | テーマコード (参考) |

|---------------|------|-----------|-------|------|------|-------------|

| H04L          | 9/10 | (2006.01) | H04 L | 9/00 | 621A | 5 J 1 O 4   |

| H <b>04</b> L | 9/08 | (2006.01) | H04 L | 9/00 | 601E |             |

| G09C          | 1/00 | (2006.01) | GO9C  | 1/00 | 610A |             |

#### 審査請求 有 予備審査請求 未請求 (全 28 頁)

出願番号 特願2011-532824 (P2011-532824) (21) 国際出願番号 PCT/JP2009/066536 平成21年9月24日 (2009.9.24) (22) 国際出願日 AP (BW, GH, GM, KE, LS, MW, MZ, NA, SD, (81) 指定国 SL, SZ, TZ, UG, ZM, ZW), EA (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), EP (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, F1, FR, GB, GR, HR, HU , IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, S K, SM, TR), OA (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE , SN, TD, TG) , AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC , EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, I S. JP. KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE , PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, S Y, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW

(71) 出願人 000003078 株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100089118

弁理士 酒井 宏明

(74)代理人 100112656

弁理士 宮田 英毅

(72) 発明者 川端 健

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 藤崎 浩一

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

## (54) 【発明の名称】 鍵スケジュール装置および方法

## (57)【要約】

検算を行う鍵を格納するレジスタの規模を小さくする。拡大鍵が分割されて拡大鍵生成回路に入力される。拡大鍵が分割された1の部分鍵に対して非線形変換が行われると共に、部分鍵のそれぞれに対して非線形変換の出力を用いて線形変換が行われ、変換された部分鍵が拡大鍵レジスタに格納された部分鍵のうち、非線形変換の出力を直接的に用いて線形変換が行われる部分鍵が検算用拡大鍵レジスタに格納される。それ以外の部分鍵は、拡大鍵レジスタに接続される線形変換回路で、拡大鍵生成回路における線形変換を施される。検算用拡大鍵レジスタに格納される部分鍵と、線形変換回路で拡大鍵生成回路における線形変換を施された各部分鍵とにおける線形変換とは逆の線形変換を施された各部分鍵とを結合して、検算用拡大鍵が生成される。検算用拡大鍵レジスタは、1の部分鍵が格納可能な容量があればよい。

151 REGISTER

#### 【特許請求の範囲】

#### 【請求項1】

入力データに対して実行される演算に用いる第 1 の鍵を出力する鍵スケジュール装置であって、

拡大鍵を分割した各部分鍵のうち少なくとも 1 の部分鍵に対して非線形変換を施す非線 形変換部と、

複数の線形変換回路を含み、該複数の線形変換回路の一部が前記非線形変換部の変換結果を直接用いて前記部分鍵の線形変換を行う第1の線形変換部と、

前記第1の線形変換部で前記線形変換を行われた前記部分鍵をそれぞれ格納する第1の 格納部と、

前記第1の格納部に格納された前記部分鍵のうち前記非線形変換部の変換結果を直接用いて前記線形変換回路で線形変換が行われた部分鍵以外の部分鍵のそれぞれに対して、前記第1の線形変換部による変換に対して逆の線形変換を行う第2の線形変換部と、

前記複数の線形変換回路のうち前記非線形変換部の変換結果に対して直接的に前記線形変換を行う線形変換回路に対する入力のうち1を格納する第2の格納部と、

前記第2の線形変換部で前記逆の線形変換を施された部分鍵のそれぞれと、前記第2の格納部に格納された前記入力とを結合して、前記演算に対する検算を行う際に用いる第2の鍵として出力する出力部と

#### を備える

ことを特徴とする鍵スケジュール装置。

#### 【請求項2】

前記第1の線形変換部および前記第2の線形変換部は、排他的論理和回路、ビットシフト回路、加算回路および減算回路のうち少なくとも1を用いて構成されることを特徴とする請求項1に記載の鍵スケジュール装置。

#### 【請求項3】

前記第2の格納部は、前記入力部から前記非線形変換部の変換結果に対して直接的に線形変換を行う線形変換回路に入力される前記部分鍵を格納する

ことを特徴とする請求項2に記載の鍵スケジュール装置。

#### 【請求項4】

前記第2の格納部は、前記非線形変換部の前記変換結果を格納し、

前記第2の線形変換部は、さらに、前記第2の格納部に格納される前記変換結果に対して逆の線形変換を行う

ことを特徴とする請求項2に記載の鍵スケジュール装置。

## 【請求項5】

入力データに対して実行される演算に用いる第1の鍵を出力する鍵スケジュール方法であって、

拡大鍵を分割した各部分鍵のうち少なくとも1の部分鍵に対して非線形変換を施す非線 形変換ステップと、

複数の線形変換回路の一部が前記非線形変換ステップの変換結果を直接用いて前記部分鍵の線形変換を行う第1の線形変換ステップと、

前記第1の線形変換ステップで前記線形変換を行われた前記部分鍵をそれぞれ第1の格納部に格納する第1の格納ステップと、

前記第1の格納ステップに格納された前記部分鍵のうち前記非線形変換ステップの変換結果を直接用いて前記線形変換回路で線形変換が行われた部分鍵以外の部分鍵のそれぞれに対して、前記第1の線形変換ステップによる変換に対して逆の線形変換を行う第2の線形変換ステップと、

前記複数の線形変換回路のうち前記非線形変換ステップの変換結果に対して直接的に前記線形変換を行う線形変換回路に対する入力のうち1を第2の格納部に格納する第2の格納ステップと、

前記第2の線形変換ステップで前記逆の線形変換を施された部分鍵のそれぞれと、前記

10

20

30

40

第 2 の格納部に格納された前記入力とを結合して、前記演算に対する検算を行う際に用いる第 2 の鍵として出力する出力ステップと

を備える

ことを特徴とする鍵スケジュール方法。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、暗号化処理または復号処理の検算に用いる鍵の生成に関する。

【背景技術】

[0002]

近年で一般的に用いられる暗号化方式の一つとして、AES(Advanced Encryption Standard)などのブロック暗号を用いたものがある。ブロック暗号は、鍵を入力として複数個の拡大鍵を出力する鍵スケジューラと、入力データの撹拌を行うスクランブラとで構成され、さらに、スクランブラが複数のラウンドぞれぞれで拡大鍵を用いて入力データの置換や転置などの演算処理を行う構成になっているものが多い。

[00003]

このような複数のラウンド毎に演算処理を行う場合、ラウンド毎に検算を行うことでエラーを検出する方法が適用できる。ラウンド毎に検算を行う場合、検算用の回路を備えれば演算処理と検算処理とを並列化することが可能であり、1ラウンド分のオーバヘッドで演算結果が確定し、検算を含めた暗号化や復号処理を高速に行うことが可能である。非特許文献1には、ブロック暗号に適用するための様々なエラー検出方法が報告されている。

【先行技術文献】

【非特許文献】

[0004]

【非特許文献 1】 "Concurrent Error Detection Schemes for Fault-based Side-Channel Cryptanalysis of Symmetric Block Cipher", IEEE Transactions on Computer-Added Design of Integrated circuit and Systems. VO.21 No.12, December 2002

【発明の概要】

【発明が解決しようとする課題】

[00005]

暗号化装置や復号装置は、処理速度が高速であると共に、回路規模が小さいことが望ましい。暗号化や復号の演算中のエラーに対する対策である検算を行うには、検算結果に対する比較対象となる演算結果を保持または生成するためのレジスタが必要である。それと共に、検算に用いる拡大鍵を格納するため、拡大鍵格納用レジスタと同じ大きさのレジスタが必要となり、回路の小規模化を妨げていた。

[0006]

本発明は、上記に鑑みてなされたものであって、検算を行う鍵を格納するレジスタの規模が小さい鍵スケジュール装置および方法を提供することを目的とする。

【課題を解決するための手段】

[0007]

上述した課題を解決し、目的を達成するために、本発明は、入力データに対して実行される演算に用いる第1の鍵を出力する鍵スケジュール装置であって、拡大鍵を分割した各部分鍵のうち少なくとも1の部分鍵に対して非線形変換を施す非線形変換部と、複数の線形変換回路の一部が非線形変換部の変換結果を直接用いて部分鍵の線形変換を行う第1の線形変換部と、第1の線形変換部で線形変換を行われた部分鍵をそれぞれ格納する第1の格納部と、第1の格納部に格納された部分鍵のうち非線形変換部の変換結果を直接用いて線形変換回路で線形変換が行われた部分鍵以外の部分鍵のそれぞれに対して、第1の線形変換部による変換に対して逆の線形変換を行う第2の線形変換部と、複数の線形変換回路のうち非線形変換部の変換結果に対して直接的に線形変換を

10

20

20

30

40

行う線形変換回路に対する入力のうち1を格納する第2の格納部と、第2の線形変換部で逆の線形変換を施された部分鍵のそれぞれと、第2の格納部に格納された入力とを結合して、演算に対する検算を行う際に用いる第2の鍵として出力する出力部とを備えることを特徴とする。

#### 【発明の効果】

#### [00008]

本発明によれば、検算を行う鍵を格納するレジスタの規模を小さくできるという効果を 奏する。

#### 【図面の簡単な説明】

[0009]

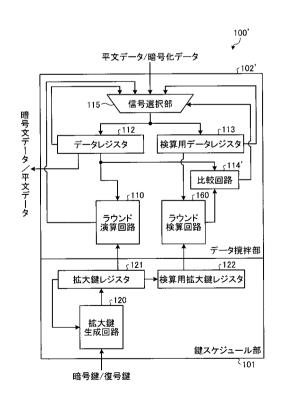

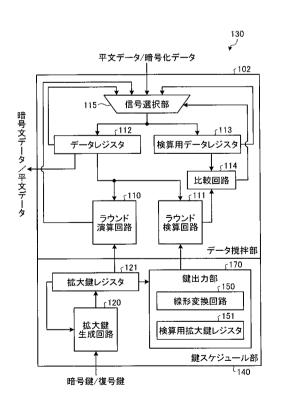

【図1】検算を異種処理で行う場合の演算装置の基本的な構成の例を示す図。

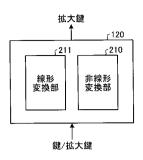

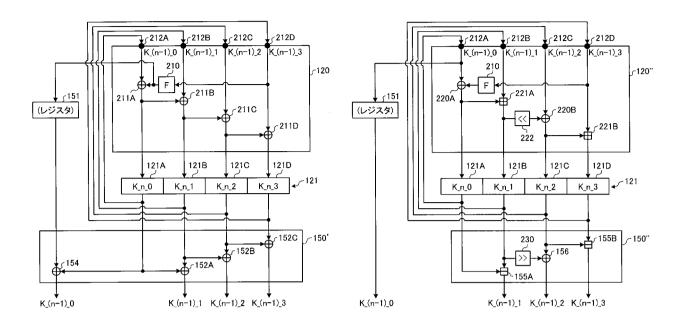

- 【図2】拡大鍵生成回路を概略的に示す図。

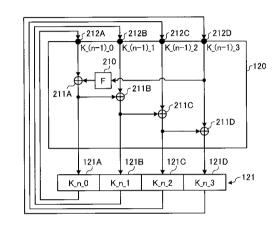

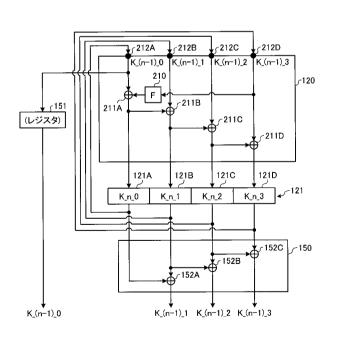

- 【図3】拡大鍵生成回路の構成を示す図。

- 【図4】検算を異種処理で行う場合の処理を示すフローチャート。

- 【図5】検算を同種処理で行う場合の演算装置の基本的な構成を示す図。

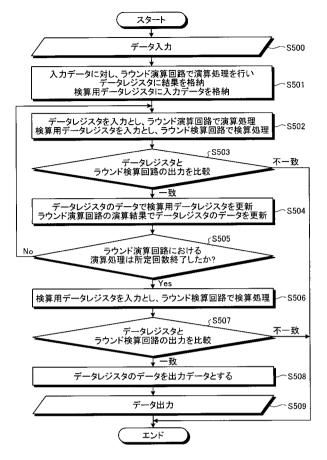

- 【図6】検算を同種処理で行う場合の処理を示すフローチャート。

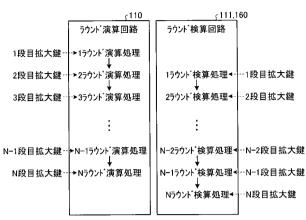

- 【図7】演算処理と検算処理との関係について説明するための図。

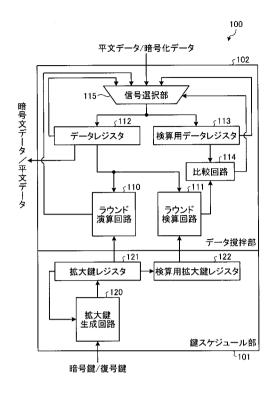

- 【図8】実施の形態による鍵スケジュール部の構成を示す図。

- 【図9】実施の形態による鍵スケジュール部を演算装置に適用させた例を示す図。

- 【 図 1 0 】 実 施 の 形 態 の 第 1 の 変 形 例 に よ る 鍵 ス ケ ジ ュ ー ル 部 の 構 成 を 示 す 図 。

- 【図11】実施の形態の第2の変形例による鍵スケジュール部の構成を示す図。

#### 【発明を実施するための形態】

#### [0010]

以下に添付図面を参照して、本発明に係る演算装置、方法およびプログラムの実施の形態を詳細に説明する。なお、本実施の形態では、暗号化および復号を、AES(Advanced Encryption Standard)に代表される、ブロック暗号を用いた暗号化方式で行う。また、本実施の形態に適用されるブロック暗号化方式では、暗号化装置および復号装置は、鍵を入力として複数個の拡大鍵を出力する鍵スケジューラ部と、入力データの撹拌を行うデータ撹拌部とで構成される。そして、データ撹拌部が複数のラウンドぞれぞれで拡大鍵を用いて入力データの置換や転置などの演算処理を行う。

#### [0011]

<暗号化および復号処理に対する検算の概略>

先ず、本実施の形態に適用可能な、暗号化処理および復号処理で演算された演算データに対するエラー検出について、概略的に説明する。

#### [0012]

暗号化装置および復号装置における演算データのエラーを検出する方法として、演算中のデータにパリティを付加してエラー検出を行う方法や、検算を行う方法がある。これらのうち、パリティを付加する方法は、入力ビット長が長くなるため、既存システムに対してパリティ付加によるエラー検出を行う暗号化装置や復号装置を適用する場合には、既存システムの変更が必要になる。

# [ 0 0 1 3 ]

一方、検算によりエラー検出を行う方法は、入力ビット長の変更が無く、検算機能を付加した暗号化装置や復号装置を既存のシステムに適用することが比較的容易である。本実施の形態では、暗号化処理や復号処理で演算された演算データのエラー検出に、この検算方式を採用する。

## [0014]

検算方式では、さらに、暗号装置または復号装置において全体の演算処理が終わってから検算を行う方法と、ラウンド毎に検算を行う方法が考えられる。これらのうち、全体の演算処理が終わってから検算する方法は、1ブロックの入力に対して演算処理と検算処理とを行うため、演算結果が確定するまでの時間が検算を行わない場合に比べて2倍必要と

10

20

30

40

なる。そのため、高速な処理が要求されるシステムには適していない。

#### [0015]

一方、ラウンド毎に検算処理を行う方法は、暗号化処理や復号処理を行う演算回路とは別個に検算用の回路を備えれば、データ演算処理と検算処理とを並列的に行うことができる。この場合、1ラウンド分のオーバヘッドで演算結果が確定し、検算を含めた暗号化処理または復号処理の高速化が可能である。

#### [0016]

ところで、一般に、暗号化処理または復号処理の演算に対する検算は、演算と異なる処理により行う異種処理と、演算と同種の処理により行う同種処理とがある。

#### [0017]

異種処理では、暗号化処理の演算に対する検算は、暗号化処理に対応する復号処理の演算により行う。同様に、復号処理の演算に対する検算は、暗号化処理の演算により行う。 検算を異種処理により行う場合には、暗号化装置または復号装置は、暗号処理回路および 復号処理回路の2種類の回路を備える。したがって、検算を異種処理により行う場合、1 の装置で暗号化処理および復号処理の両方を実行可能に構成することができる。

#### [0018]

これに対して、同種処理では、暗号化処理の演算に対する検算は、同じ暗号化処理の演算により行う。同様に、復号処理の演算に対する検算は、同じ復号処理の演算により行う。検算を同種処理により行う場合には、暗号化装置または復号装置は、暗号化処理回路または復号処理回路のうち装置の目的に即した1種類の回路を複数、備える。したがって、検算を同種処理により行う場合、検算を利用しない状態においてスループットを向上させるように構成できる。

## [0019]

先ず、検算を異種処理により行う場合について説明する。図1は、検算を異種処理により行う場合の、検算機能付き暗号化装置または復号装置の基本的な構成の例を示す。なお、暗号化装置と復号装置は、同一の構成で実現可能であるので、以下では、特に記載のない限り、暗号化装置および復号装置を纏めて演算装置と呼ぶ。

#### [0020]

図1に例示される演算装置100は、同じ演算処理を複数回繰り返し実行して、平文データの暗号化または暗号データの復号を行う。演算装置100は、暗号化装置として機能する場合には、所定長の平文データと所定長の暗号鍵とが入力され、入力された平文データを暗号鍵を用いて暗号化して所定長の暗号文データを出力する。復号装置として機能する場合には、所定長の暗号文データと所定長の復号鍵とが入力され、入力された暗号文データを復号して所定長の平文データを出力する。また、演算装置100は、暗号化または復号に対する検算機能を有する。

# [0021]

なお、演算装置100に対して入力される平文または暗号データ、暗号鍵または復号鍵、ならびに、演算処理の繰り返し回数は、演算装置100に適用される暗号化または復号方式によって定まるものとする。また、演算装置100は、演算装置100の各部に作用して全体の動作を制御するための制御部を備える(図示しない)。

# [0022]

演算装置100は、鍵スケジュール部101とデータ撹拌部102とを有する。鍵スケジュール部101は、外部から入力された暗号鍵または復号鍵(以下では、特に記載のない限り、これらを纏めて「鍵」と呼ぶ)に基づき拡大鍵を生成する。また、鍵スケジュール部101は、自ら生成した拡大鍵に基づき、新たな拡大鍵を生成する。

# [0023]

データ撹拌部102は、外部から入力データとして入力された平文または暗号化データに対して、鍵スケジュール部101で生成された拡大鍵を用いて演算を行い、当該入力データを撹拌する(演算装置100が暗号化装置の場合)。演算装置100が復号装置の場合には、データ撹拌部102は、拡大鍵を用いて暗号化の際と逆の演算を行うことで、撹

10

20

30

40

拌されたデータを元に戻すことになる。また、データ撹拌部 1 0 2 は、拡大鍵を用いた演算を検算する機能を有する。

# [0024]

以降、特に記載のない限り、この暗号化の際のデータ撹拌と、復号の際の撹拌されたデータを元に戻す処理を、纏めてデータ撹拌と呼ぶ。

## [0025]

鍵スケジュール部101およびデータ撹拌部102は、互いに同期的に動作し、鍵スケジュール部101において新たな拡大鍵が生成される毎に、当該拡大鍵を用いてデータ撹拌部102において1回のデータ撹拌が行われる。この、鍵スケジュール部101において新たな拡大鍵が生成され、当該拡大鍵を用いてデータ撹拌部102がデータ撹拌を行う1回分の処理を、1ラウンドとする。演算装置100におけるラウンド毎の動作は、例えば上述した制御部により制御される。

#### [0026]

先ず、鍵スケジュール部101について説明する。鍵スケジュール部101は、この基本的な構成においては、拡大鍵生成回路120、拡大鍵レジスタ121および検算用拡大鍵レジスタ122を有する。

#### [0027]

拡大鍵生成回路 1 2 0 は、例えば図 2 に概略的に示されるように、線形変換を行う線形変換部 2 1 1 と、非線形変換を行う非線形変換部 2 1 0 とを有し、入力された鍵または拡大鍵に対して線形変換および非線形変換を行い、新たな拡大鍵を生成する。

#### [0028]

なお、線形は、本来は重ね合わせが可能なことをいい、ある関数 f (x)を考えたときに、関数 f (a x + b y) = a f (x) + b f (y)を満たす場合、その関数 f (x)は、線形である。例えば、加減算による変換は、線形である。また例えば、排他的論理和による変換は、変換の順序を入れ替えても同じ出力値が得られるため上述の条件を満たし、線形である。一方、ランダムに値を割り当てたテーブルを、入力値をインデクスとして参照して出力値を得るような変換は、入力値と出力値との関係が一定ではなく、例えば変換の順序を入れ替えると異なる出力値が得られ、上述の条件を満たさないため、非線形である。

# [0029]

拡大鍵生成回路120は、外部から供給された鍵または拡大鍵レジスタ121に格納される拡大鍵に対して線形処理および非線形処理を施し、拡大鍵を生成する。拡大鍵生成回路120で生成された拡大鍵は、拡大鍵レジスタ121に格納され、拡大鍵レジスタ121が更新される。検算用拡大鍵レジスタ122は、拡大鍵レジスタ121と同一のビット長を格納可能とされ、拡大鍵レジスタ121から供給された拡大鍵が格納されることで更新される。

#### [0030]

図3は、拡大鍵生成回路120の一例の構成を示すプロック図である。この図3に例示される拡大鍵生成回路120は、AESによる拡大鍵生成を、拡大鍵生成回路と拡大鍵レジスタとで構成する場合の例である。拡大鍵生成回路120は、非線形変換を行う非線形変換回路210(図3の例では「F」と記述)と、線形変換を行う排他的論理和回路211A、211B、211Cおよび211Dが、図2で説明した線形変換部211に相当する。

# [0031]

n - 1 ラウンド目の拡大鍵が 4 分割されて、拡大鍵生成回路 1 2 0 の入力端 2 1 2 A 、 2 1 2 B、 2 1 2 C および 2 1 2 D にそれぞれ入力される。ここで、初期状態の鍵(暗号鍵または復号鍵)を、 0 ラウンド目の拡大鍵(すなわち n = 1 )であるものとする。この例では、ビット長が 1 2 8 ビットの n - 1 ラウンド目の拡大鍵が、ビット長が 3 2 ビットの部分に 4 分割される。ここで、 n - 1 ラウンド目の拡大鍵の値を値K\_(n-1)と表し、当該拡大鍵が 4 分割された各部分鍵の値を、それぞれ値K\_(n-1)\_0、値K\_(n-1)\_1、値K\_(n-1

10

20

30

40

)\_2および値K\_(n-1)\_3と表すものとする。

#### [0032]

これら値K\_(n-1)\_0、値K\_(n-1)\_1、値K\_(n-1)\_2および値K\_(n-1)\_3が、拡大鍵生成回路 120の入力端212A、212B、212Cおよび212Dを介して排他的論理和回路 211A、211B、211Cおよび211Dそれぞれ一方の入力端に入力される。また 、値K\_(n-1)\_3が非線形変換回路210に入力される。値K\_(n-1)\_3は、非線形変換回路2 10で非線形変換されて排他的論理和回路211の他方の入力端に入力される。

#### [0033]

ここで、非線形変換回路 2 1 0 は、入力されたデータに対して非線形変換処理を施しデータを非線形に攪乱する。非線形変換回路 2 1 0 としては、例えば予め与えられたテーブルである S - B O X (Substitution Box)が用いられる。 S - B O X は、典型的な例では、入力データのデータ長を 1 6 ビットとしたとき、 M S B 側の 8 ビットと L S B 側の 8 ビットとでテーブルを参照し、入力データを、当該入力データとは異なる 1 6 ビットの出力データに変換する。この S - B O X は、一般的には、演算装置 1 0 0 の構成の大きな部分を占める大規模なものとなる。

#### [0034]

排他的論理和回路 2 1 1 A は、一方の入力端に入力された値K\_(n-1)\_0と、他方の入力端に入力された、値K\_(n-1)\_3が非線形変換されたデータとの排他的論理和を取り、値K\_n\_0を出力する。この値K\_n\_0は、拡大鍵レジスタ 1 2 1 の領域 1 2 1 A に格納されると共に、排他的論理和回路 2 1 1 B の他方の入力端に入力される。

#### [0035]

排他的論理和回路 2 1 1 B は、一方の入力端に入力された値 $K_{-}(n-1)_{-}1$ と、他方の入力端に入力された値 $K_{-}n_{-}0$ との排他的論理和を取り、値 $K_{-}n_{-}1$ を出力する。この値 $K_{-}n_{-}1$ は、拡大鍵レジスタ 1 2 1 の領域 1 2 1 B に格納されると共に、排他的論理和回路 2 1 1 C の他方の入力端に入力される。排他的論理和回路 2 1 1 C は、一方の入力端に入力された値 $K_{-}(n-1)_{-}2$ と、他方の入力端に入力された値 $K_{-}n_{-}1$ との排他的論理和を取り、値 $K_{-}n_{-}2$ を出力する。この値 $K_{-}n_{-}2$ は、拡大鍵レジスタ 1 2 1 の領域 1 2 1 C に格納されると共に、排他的論理和回路 2 1 1 D の他方の入力端に入力される。排他的論理和回路 2 1 1 D は、一方の入力端に入力された値 $K_{-}n_{-}2$ との排他的論理和を取り、値 $K_{-}n_{-}3$ と、他方の入力端に入力された値 $K_{-}n_{-}3$ との排他的論理和を取り、値 $K_{-}n_{-}3$ を出力する。この値 $K_{-}n_{-}3$ は、拡大鍵レジスタ 1 2 1 の領域 1 2 1 D に格納される。

# [0036]

このように、拡大鍵レジスタ121の各領域121A、121B、121Cおよび121Dには、各排他的論理和回路211A、211B、211Cおよび211Dそれぞれから出力された値 $K_n_0$ 、値 $K_n_1$ 、値 $K_n_2$ および値 $K_n_3$ が格納される。すなわち、n ラウンド目の拡大鍵の値 $K_n$ は、値 $K_n=\{K_n_0,K_n_1,K_n_2,K_n_3\}$ として、値 $K_n$ 0、値 $K_n_1$ 、値 $K_n_2$ および値 $K_n_3$ のビット結合で表すことができる。換言すれば、 $K_n_n$ 0、位 $K_n_n$ 1、値 $K_n_n$ 2および値 $K_n_n$ 3が結合されて生成される。

#### [0037]

拡大鍵レジスタ121に格納される値 $K_n_0$ 、値 $K_n_1$ 、値 $K_n_2$ および値 $K_n_3$ は、入力端212A、212B、212Cおよび212Dに対し、それぞれ値 $K_n_1$ 0、値 $K_n_1$ 1) $K_n_1$ 1、値 $K_n_1$ 1、値 $K_n_1$ 2および値 $K_n_1$ 1、位の は大鍵が生成される。

#### [0038]

説明は図1に戻り、鍵スケジュール部101の動作について、概略的に説明する。最初に、鍵(暗号鍵または復号鍵)が拡大鍵生成回路120に供給される。拡大鍵生成回路120は、第1ラウンド目の処理として、供給された鍵に対して上述のようにして排他的論理和回路211A~211Dによる線形変換と、非線形変換回路210による非線形変換を施し、拡大鍵の各値K\_n\_0、値K\_n\_1、値K\_n\_2および値K\_n\_3を生成する。生成された値

10

20

30

K\_n\_0、値K\_n\_1、値K\_n\_2および値K\_n\_3は、それぞれ拡大鍵レジスタ121の領域121 A~121Dに格納され、拡大鍵レジスタ121が更新される。

## [0039]

次のラウンドにおいて、拡大鍵レジスタ121に格納される拡大鍵(値K\_n\_0、値K\_n\_1、値K\_n\_2および値K\_n\_3)が、検算用の拡大鍵として検算用拡大鍵レジスタ122に格納され、検算用拡大鍵レジスタ122が更新される。その後、拡大鍵生成回路120は、拡大鍵レジスタ121に格納される拡大鍵に対して線形変換および非線形変換を施し、第2ラウンド目の拡大鍵を生成する。拡大鍵レジスタ121に格納される第1ラウンド目の拡大鍵により検算用拡大鍵レジスタ122が更新され、次いで、拡大鍵生成回路120により生成された第2ラウンド目の拡大鍵により拡大鍵レジスタ121が更新される。

[0040]

以降、拡大鍵生成回路120による拡大鍵レジスタ121に格納された拡大鍵を用いた拡大鍵の生成、拡大鍵レジスタ121に格納される1ラウンド前の拡大鍵による検算用拡大鍵レジスタ122の更新、拡大鍵生成回路120により生成された現在のラウンドの拡大鍵による拡大鍵レジスタ121の更新が、所定のラウンド数だけ繰り返される。すなわち、検算用拡大鍵レジスタ122には、拡大鍵レジスタ121に格納される拡大鍵に対して1ラウンド前の拡大鍵が検算用の拡大鍵として格納される。

#### [0041]

次に、データ撹拌部102について説明する。データ撹拌部102は、ラウンド演算回路110、ラウンド検算回路111、データレジスタ112、検算用データレジスタ11 3、比較回路114および信号選択部115を有する。

[0042]

信号選択部115は、暗号化の対象となる平文データ、または、復号の対象となる暗号化データ(以下、纏めて処理対象データと呼ぶ)が入力されると共に、ラウンド演算回路110、データレジスタ112および検算用データレジスタ113の出力がそれぞれ入力される。信号選択部115は、比較回路114の出力信号に応じて、入力されたデータから、後述するデータレジスタ112および検算用データレジスタ113を更新するためのデータを選択する。

[0043]

データレジスタ112および検算用データレジスタ113は、信号選択部115から出力されたデータにより更新される。詳細は後述するが、検算用データレジスタ113は、データレジスタ112に保持される1ラウンド前のデータにより更新される。データレジスタ112の更新は、検算用データレジスタ113の更新が行われた後に行われる。すなわち、検算用データレジスタ113は、データレジスタ112に格納されるデータに対して1ラウンド前のデータが格納される。

[0044]

ラウンド演算回路110は、上述した鍵スケジュール部101の拡大鍵レジスタ121から拡大鍵を読み出して、データレジスタ112に保持されるデータに対して1ラウンドの所定の演算処理を行う。演算結果は、信号選択部115に供給される。

[0045]

ここで、この演算装置100が暗号化装置として機能する場合には、ラウンド演算回路 110は、拡大鍵レジスタ121から読み出した拡大鍵を用いて、所定の暗号化方式に従い、データレジスタ112に格納されるデータに対する1ラウンドの暗号化処理を行う。 【0046】

一方、この演算装置100が復号装置として機能する場合には、ラウンド演算回路11 0は、拡大鍵レジスタ121から読み出した拡大鍵を用いて、所定の暗号化方式に従い、 データレジスタ112に格納されるデータに対する1ラウンドの復号処理を行う。以下で は、特に記載のない限り、ラウンド演算回路110で行われる暗号化処理および復号処理 の演算を纏めて、演算処理と呼ぶ。

[0047]

10

20

30

ラウンド検算回路111は、上述した鍵スケジュール部101の検算用拡大鍵レジスタ 122から拡大鍵を読み出して、データレジスタ112に格納されるデータに対して1ラウンドの検算処理を行う。検算結果は、比較回路114に供給される。

#### [ 0 0 4 8 ]

ここで、ラウンド検算回路111の検算処理は、ラウンド演算回路110の逆の演算により行われる。すなわち、この演算装置100が暗号化装置として機能する場合には、ラウンド検算回路111は、検算用拡大鍵レジスタ122から読み出した検算用拡大鍵を用いて、上述のラウンド演算回路110でなされる所定の暗号化方式に対応する演算により、データレジスタ112に格納されるデータに対する1ラウンドの復号処理の演算を行い、検算とする。

[0049]

一方、この演算装置100が復号装置として機能する場合には、ラウンド検算回路11 1は、検算処理として、上述のラウンド演算回路110でなされる復号処理が対応する所定の暗号化方式に従い、データレジスタ112に格納されるデータに対する1ラウンドの暗号化処理の演算を行う。以下では、特に記載のない限り、ラウンド検算回路111で行われる復号処理および暗号化処理の演算を纏めて、検算処理と呼ぶ。

[0050]

このように、ラウンド検算回路111では、ラウンド演算回路110で行った演算処理 結果を1ラウンド分戻す演算処理を行うことで、検算とする。

[0051]

比較回路114は、ラウンド検算回路111の出力と検算用データレジスタ113に格納されるデータとを比較する。比較の結果、両者が一致すれば、比較回路114は、ラウンド演算回路110による演算処理が正しいと判断し、次のラウンドの演算を行うように信号選択部115を制御する。一方、比較の結果、両者が一致しなければ、比較回路114は、ラウンド演算回路110による演算処理にエラーが発生したと判断し、以降のラウンドの演算を停止するように信号選択部115を制御する。

[0052]

図4は、検算を異種処理で行う場合の、データ撹拌部102による演算および検算処理を示す一例のフローチャートである。なお、図4に例示される処理は、暗号化方式または復号方式によって定められるラウンド回数がR回(R>2)である場合の例である。現在のラウンド数は、例えばデータ撹拌部102が備える図示されないカウンタによりカウントされる。

[0053]

最初のステップS400で、処理対象データが演算装置100に入力され、信号選択部115に供給される。また、図示しないが、鍵が演算装置100に入力され、拡大鍵生成回路120に供給される。拡大鍵生成回路120は、入力された鍵に対して上述した線形変換および非線形変換を施して拡大鍵を生成する。この拡大鍵が拡大鍵レジスタ121に格納される。

[0054]

次のステップS401で、信号選択部115は、処理対象データをデータレジスタ11 2 および検算用データレジスタ113にそれぞれ格納する。そして、ラウンド演算回路1 1 0 がデータレジスタ112に格納される処理対象データに対して、拡大鍵レジスタ12 1 に格納される拡大鍵を用いて1ラウンド目の演算処理を施す。ラウンド演算回路110 による演算結果が信号選択部115を介してデータレジスタ112に格納され、データレジスタ112が更新される。

[0055]

鍵スケジュール部101において、拡大鍵レジスタ121に格納される拡大鍵が検算用拡大鍵レジスタ122に検算用拡大鍵として格納されると共に、拡大鍵生成回路120が拡大鍵レジスタ121に格納される拡大鍵を用いて新たな拡大鍵を生成する。生成された新たな拡大鍵は、拡大鍵レジスタ121に格納され、拡大鍵レジスタ121が更新される

10

20

30

40

10

20

30

40

50

[0056]

次のステップS402で、ラウンド演算回路110は、データレジスタ112に格納されるデータを入力として、拡大鍵レジスタ121に格納される拡大鍵を用いて、2ラウンド目の演算処理を行う。それと共に、ステップS402で、ラウンド検算回路111は、データレジスタ112に格納されるデータを入力として、検算用拡大鍵レジスタ122に格納される拡大鍵を用いて検算処理を行う。

[0057]

ラウンド検算回路111で行われる検算処理は、ラウンド演算回路110で行われる演算処理と逆の処理である。また、検算用拡大鍵レジスタ122に格納される拡大鍵は、拡大鍵レジスタ121に格納される拡大鍵に対して1ラウンド前の状態の拡大鍵である。したがって、ラウンド検算回路111での検算により、入力とされるデータレジスタ112に格納されるデータ1ラウンド前の状態に戻されることになる。ラウンド検算回路111による検算結果は、比較回路114に供給される。

[0058]

次のステップS403で、比較回路114は、ラウンド検算回路111から供給された 検算結果と、検算用データレジスタ113に格納されるデータとを比較して、両者が一致 するか否かを判定する。若し、一致しないと判定されたら、演算処理にエラーがあったと され、一連の処理が終了される。一方、両者が一致すると判定されたら、処理はステップ S404に移行される。

[0059]

ステップS404で、信号選択部115は、データレジスタ112のデータを検算用データレジスタ113に格納し、検算用データレジスタ113を更新すると共に、上述のステップS402で行われたラウンド演算回路110による演算結果をデータレジスタ112に格納し、データレジスタ112を更新する。

[0060]

また、鍵スケジュール部101において、拡大鍵レジスタ121に格納される拡大鍵が 検算用拡大鍵レジスタ122に検算用拡大鍵として格納される。また、拡大鍵生成回路1 20は、拡大鍵レジスタ121に格納される拡大鍵を用いて新たな拡大鍵を生成する。こ の新たな拡大鍵は、拡大鍵レジスタ121に格納され、拡大鍵レジスタ121が更新され る。

[0061]

次のステップS405で、例えば図示されないカウンタにより、ラウンド演算回路11 0における演算処理が所定回数(この例ではR-1回)を終了したか否かが判定される。 若し、終了していないと判定されたら、処理がステップS402に戻され、次のラウンドの処理がなされる。

[0062]

一方、ステップS405で、ラウンド演算回路110における演算処理が所定回数を終了したと判定されたら、処理はステップS406に移行される。ステップS406では、ラウンド検算回路111は、データレジスタ112に格納されるデータを入力として、検算用拡大鍵レジスタ122に格納される検算用拡大鍵を用いて検算処理を行う。検算処理の結果は、比較回路114に供給される。

[0063]

次のステップS407で、比較回路114は、ラウンド検算回路111から供給された 検算結果と、検算用データレジスタ113に格納されるデータとを比較して、両者が一致 するか否かを判定する。若し、一致しないと判定されたら、演算処理にエラーがあったと され、一連の処理が終了される。一方、両者が一致すると判定されたら、処理はステップ S408に移行される。

[0064]

ステップS408では、データレジスタ112に格納されるデータが出力データに決定

され、ステップS409で、当該出力データが演算装置100から出力される。

#### [0065]

なお、この図4のフローチャートによる処理は、演算装置100が平文データの暗号化を行う暗号化装置あるいは暗号化データの復号を行う復号装置の何れであっても適用可能である。すなわち、ラウンド演算回路110が暗号化の演算を行い、ラウンド検算回路110が復号の演算を行い、ラウンド検算回路111が対応する暗号化の演算を行う場合であっても、図4のフローチャートによる処理を適用することができる。またこの場合、鍵スケジュール部101の動作は、演算装置100が暗号化装置あるいは復号装置の何れの場合であっても同一である。

[0066]

次に、検算を同種処理により行う場合について説明する。図5は、検算を同種処理により行う場合の、検算機能付き暗号化装置または復号装置の基本的な構成の例を示す。なお、検算を同種処理により行う場合でも、暗号化装置と復号装置は、同一の構成で実現可能であるので、以下では、特に記載のない限り、暗号化装置および復号装置を纏めて演算装置と呼ぶ。

#### [0067]

図5に例示される演算装置100′は、図1に例示した演算装置100と同様に、同じ演算処理を複数回繰り返し実行して、平文データの暗号化または暗号データの復号を行う。演算装置100′は、図1に例示した演算装置と同様に、暗号化または復号に対する検算機能を有する。なお、図5において、上述の図1と共通する部分には同一の符号を付し、詳細な説明を省略する。

[0068]

演算装置100′は、鍵スケジュール部101とデータ撹拌部102′とを有する。鍵スケジュール部101は、図1~図3を用いて説明した異種処理の場合の例と全く同じ構成および動作を適用できるので、ここでの説明を省略する。

[0069]

データ撹拌部102′において、ラウンド検算回路160は、検算用拡大鍵レジスタ122から拡大鍵が供給されると共に、データレジスタ112に格納されるデータを入力として、ラウンド演算回路110と同一の演算を行う。すなわち、この演算装置100′が暗号化装置として機能する場合には、ラウンド検算回路160は、検算用拡大鍵レジスタ122から供給される検算用拡大鍵を用いて、ラウンド演算回路110でなされる演算処理と同一の、所定の暗号化方式による演算を行う。

[0070]

また、この演算装置100′が復号装置として機能する場合にも、ラウンド検算回路160は、検算用拡大鍵レジスタ122から供給される検算用拡大鍵を用いて、ラウンド演算回路110でなされる演算処理と同一の、所定の暗号化方式による復号処理の演算を行う。

[0071]

ラウンド検算回路160の検算結果は、比較回路114′に供給される。比較回路114′は、ラウンド検算回路160から供給された検算結果と、データレジスタ112に格納されるデータとを比較する。比較の結果、両者が一致すれば、比較回路114′は、ラウンド演算回路110による演算処理が正しいと判断し、次のラウンドの演算を行うように信号選択部115を制御する。一方、比較の結果、両者が一致しなければ、比較回路114′は、ラウンド演算回路110による演算処理にエラーが発生したと判断し、以降のラウンドの演算を停止するように信号選択部115を制御する。

[0072]

図 6 は、検算を同種処理で行う場合の、データ撹拌部 1 0 2 'による演算および検算処理を示す一例のフローチャートである。なお、図 5 に例示される処理は、暗号化方式または復号方式によって定められるラウンド回数が R 回( R > 2 )である場合の例である。現

10

20

30

40

在のラウンド数は、例えばデータ撹拌部 1 0 2 ′が備える図示されないカウンタによりカウントされる。

## [0073]

最初のステップS500で、処理対象データが演算装置100′に入力され、信号選択部115に供給される。また、図示しないが、鍵が演算装置100′に入力され、拡大鍵生成回路120に供給される。拡大鍵生成回路120は、入力された鍵に対して上述した線形変換および非線形変換を施して拡大鍵を生成する。この拡大鍵が拡大鍵レジスタ121に格納される。

## [0074]

次のステップS501で、信号選択部115は、処理対象データをデータレジスタ11 2 および検算用データレジスタ113にそれぞれ格納する。そして、ラウンド演算回路1 1 0 がデータレジスタ112に格納される処理対象データに対して、拡大鍵レジスタ12 1 に格納される拡大鍵を用いて1ラウンド目の演算処理を施す。ラウンド演算回路110 による演算結果が信号選択部115を介してデータレジスタ112に格納され、データレジスタ112が更新される。

#### [0075]

鍵スケジュール部101において、拡大鍵レジスタ121に格納される拡大鍵が、検算用拡大鍵レジスタ122に検算用拡大鍵として格納される。そして、拡大鍵生成回路120は、拡大鍵レジスタ121に格納される拡大鍵を用いて新たな拡大鍵を生成する。生成された新たな拡大鍵は、拡大鍵レジスタ121に格納され、拡大鍵レジスタ121が更新される。

#### [0076]

次のステップS502で、ラウンド演算回路110は、データレジスタ112に格納されるデータを入力として、拡大鍵レジスタ121に格納される拡大鍵を用いて、2ラウンド目の演算処理を行う。それと共に、ステップS502で、ラウンド検算回路160は、検算用データレジスタ113に格納されるデータを入力として、検算用拡大鍵レジスタ122に格納される拡大鍵を用いて検算処理を行う。

#### [0077]

ラウンド検算回路160で行われる検算処理は、ラウンド演算回路110で行われる演算処理と同一の処理である。一方、検算用拡大鍵レジスタ122に格納される検算用拡大鍵は、拡大鍵レジスタ121に格納される拡大鍵に対して1ラウンド前の状態の拡大鍵である。また、検算用データレジスタ113には、1ラウンド前のデータが格納されている。したがって、ラウンド検算回路160での検算により、ラウンド演算回路110で1ラウンド前に行われた演算と同一の演算が行われることになる。ラウンド検算回路160による検算結果は、比較回路114、に供給される。

#### [0078]

次のステップS503で、比較回路114′は、ラウンド検算回路160から供給された検算結果と、データレジスタ112に格納されるデータとを比較して、両者が一致するか否かを判定する。この場合、データレジスタ112は、ステップS502によるラウンド演算回路110による演算結果による更新が行われていないので、1ラウンド目の演算結果が格納されていることになる。若し、一致しないと判定されたら、演算処理にエラーがあったとされ、一連の処理が終了される。一方、両者が一致すると判定されたら、処理はステップS504に移行される。

# [0079]

ステップS504で、信号選択部115は、データレジスタ112のデータを検算用データレジスタ113に格納し、検算用データレジスタ113を更新する。それと共に、ステップS504で、上述のステップS502で行われたラウンド演算回路110による演算結果が信号選択部115に供給される。信号選択部115は、供給された演算結果をデータレジスタ112に格納し、データレジスタ112を更新する。

# [0800]

50

10

20

30

10

20

30

40

50

また、鍵スケジュール部101において、拡大鍵レジスタ121に格納される拡大鍵が、検算用拡大鍵レジスタ122に検算用拡大鍵として格納される。また、拡大鍵生成回路120は、拡大鍵レジスタ121に格納される拡大鍵を用いた新たな拡大鍵を生成する。この新たな拡大鍵は、拡大鍵レジスタ121が更新される。

[0081]

次のステップS505で、例えば図示されないカウンタにより、ラウンド演算回路110における演算処理が所定回数(この例ではR-1回)を終了したか否かが判定される。若し、終了していないと判定されたら、処理がステップS502に戻され、次のラウンドの処理が行われる。

[0082]

一方、ステップS505で、ラウンド演算回路110における演算処理が所定回数を終了したと判定されたら、処理はステップS506に移行される。ステップS506では、ラウンド検算回路160は、検算用データレジスタ113に格納されるデータを入力として、検算用拡大鍵レジスタ122に格納される検算用拡大鍵を用いて検算処理を行う。検算処理の結果は、比較回路114<sup>°</sup>に供給される。

[0083]

次のステップS507で、比較回路114′は、ラウンド検算回路160から供給された検算結果と、データレジスタ112に格納されるデータとを比較して、両者が一致するか否かを判定する。若し、一致しないと判定されたら、演算処理にエラーがあったとされ、一連の処理が終了される。一方、両者が一致すると判定されたら、処理はステップS508に移行される。

[0084]

ステップ S 5 0 8 では、データレジスタ 1 1 2 に格納されるデータが出力データに決定され、ステップ S 5 0 9 で、当該出力データが演算装置 1 0 0 'から出力される。

[0085]

なお、この図6のフローチャートによる処理は、演算装置100′が平文データの暗号化を行う暗号化装置あるいは暗号化データの復号を行う復号装置の何れであっても適用可能である。すなわち、ラウンド演算回路110およびラウンド検算回路160が暗号化の演算を行う場合であっても、ラウンド演算回路110およびラウンド検算回路160が復号の演算を行う場合であっても、図6のフローチャートによる処理を適用することができる。またこの場合、鍵スケジュール部101の動作は、演算装置100′が暗号化装置あるいは復号装置の何れの場合であっても同一である。

[0086]

<本実施の形態による検算機能付き演算装置>

次に、本実施の形態による検算機能付き演算装置について説明する。上述した鍵スケジュール部101の動作と、図4および図6のフローチャートを用いて説明したデータ撹拌部102′)の動作から分かるように、ラウンド演算回路110における演算処理と、ラウンド検算回路111(またはラウンド検算回路160)における検算処理は、1ラウンド分ずれて実行される。そのため、演算装置100(または演算装置100′)は、2ラウンド分の拡大鍵をレジスタに保持する必要がある。

[0087]

なお、図4および図6を用いて既に説明したように、検算を異種処理で行う演算装置1000と、同種処理で行う演算装置1000、とでは、演算処理と検算処理とが互いに対応するタイミングで行われる。そのため、煩雑さを避けるため、以下では、特に記載のない限り、演算装置100および演算装置100、について、演算装置100で代表させて説明する。

[0088]

図 7 を用いて、演算処理と検算処理との関係についてより具体的に説明する。先ず、1ラウンド目の処理では、ラウンド演算回路 1 1 0 において、1段目の拡大鍵を用いて1ラ

10

20

30

40

50

ウンド目の演算処理が行われる。次に、2ラウンド目の処理では、ラウンド演算回路110において、2段目の拡大鍵を用いて2ラウンド目の演算処理が行われると共に、ラウンド検算回路111において、1段目の拡大鍵を用いて1ラウンド目の演算処理結果に対して検算処理が行われる。すなわち、2ラウンド目の処理では、演算装置100は、検算用の1段目の拡大鍵と、演算用の2段目の拡大鍵とを保持している必要がある。

[0089]

3 ラウンド目の処理では、ラウンド演算回路 1 1 0 において 3 段目の拡大鍵を用いて 3 ラウンド目の演算処理が行われると共に、ラウンド検算回路 1 1 1 において、 2 段目の拡大鍵を用いて 2 ラウンド目の演算結果に対して検算処理が行われる。すなわち、 3 ラウンド目の処理では、演算装置 1 0 0 は、検算用の 2 段目の拡大鍵と、演算用の 3 段目の拡大鍵とを保持している必要がある。

[0090]

以降、同様にして、 n ラウンド目の処理(図示しない)では、ラウンド演算回路 1 1 0 において n ラウンド目の拡大鍵を用いて n ラウンド目の演算処理が行われると共に、ラウンド検算回路 1 1 1 において、検算用の n - 1 段目の拡大鍵を用いて n - 1 ラウンド目の検算処理が行われる。このように、ラウンド演算回路 1 1 0 およびラウンド検算回路 1 1 では、1 ラウンド分ずれた拡大鍵を用いてそれぞれ演算および検算が行われる。

[0091]

最終ラウンドのNラウンド目の処理では、ラウンド演算回路110においてNラウンド目の拡大鍵を用いてNラウンド目の演算処理が行われると共に、ラウンド検算回路111において、N-1段目の拡大鍵を用いてN-1ラウンド目の検算処理が行われる。そして、最終的に、ラウンド検算回路111において、Nラウンド目の演算結果に対してN段目の拡大鍵を用いて検算処理を行い、検算結果が正しければ、Nラウンド目の演算結果が正しい暗号化データまたは平文データとして演算装置100から出力される。

[0092]

このように、演算装置 1 0 0 は、 1 ラウンド目および最終ラウンドの N ラウンド目を除いて、各ラウンド毎に 2 の拡大鍵をレジスタに保持する必要がある。

[0093]

本実施の形態では、図1または図5に例示される演算装置100または演算装置100 の鍵スケジュール部101に対して、拡大鍵生成回路120が有する線形変換部200 の逆の処理を行う線形変換回路を追加する。これにより、拡大鍵を保持するレジスタの容量を削減している。

[0094]

図8は、本実施の形態による、線形変換回路が追加された鍵スケジュール部140の一例の構成を示す。この本実施の形態による鍵スケジュール部140は、拡大鍵生成回路120の構成、ならびに、拡大鍵生成回路120と拡大鍵レジスタ121との接続は、図3を用いて説明した構成をそのまま適用できる。なお、図8において、上述した図3を共通する部分には同一の符号を付し、詳細な説明を省略する。

[0095]

n - 1 ラウンド目の拡大鍵が 4 分割された各値K\_(n-1)\_0、値K\_(n-1)\_1、値K\_(n-1)\_2 および値K\_(n-1)\_3が、拡大鍵生成回路 1 2 0 の入力端 2 1 2 A 、 2 1 2 B 、 2 1 2 C および 2 1 2 D にそれぞれ入力され、拡大鍵の生成処理が行われる。処理の結果、新たな拡大鍵の各値K\_n\_0、値K\_n\_1、値K\_n\_2および値K\_n\_3が生成され、拡大鍵レジスタ 1 2 1 の領域 1 2 1 A 、 1 2 1 B 、 1 2 1 C および 1 2 1 D にそれぞれ格納される。

[0096]

図8において、拡大鍵レジスタ121から拡大鍵生成回路120の入力端212A、212B、212Cおよび212Dに遡った演算を行うことができれば、n-1ラウンド目の演算が可能となる。これにより、nラウンド目において、n-1ラウンド目の拡大鍵の全てを保持していなくても、n-1ラウンド目の拡大鍵を検算用拡大鍵として用いた検算処理を行うことができるようになる。

#### [0097]

そこで、本実施の形態では、鍵スケジュール部101に対して、拡大鍵レジスタ121に格納される各値K\_n\_0、値K\_n\_1、値K\_n\_2および値K\_n\_3を前段の値に復元可能な回路を設ける。このとき、この回路として、回路規模の小さい可逆演算回路が選択される。

#### [0098]

より具体的には、図8に例示されるように、排他的論理和回路152A、152Bおよび152Cを有する線形変換回路150を設ける。そして、拡大鍵レジスタ121の領域121A、121B、121Cおよび121Dに格納される各値K\_n\_0、値K\_n\_1、値K\_n\_2および値K\_n\_3を、排他的論理和回路152A、152Bおよび152Cの各入力端にそれぞれ入力する。

#### [0099]

より詳細には、排他的論理和回路152Aの一方および他方の入力端に、拡大鍵レジスタ121の領域121Aに格納される値 $K_n_0$ と、領域121Bに格納される値 $K_n_1$ とがそれぞれ入力される。また、排他的論理和回路152Bの一方および他方の入力端に、拡大鍵レジスタ121の領域121Bに格納される値 $K_n_1$ と、領域121Cに格納される値 $K_n_2$ とがそれぞれ入力される。さらに、排他的論理和回路152Cの一方および他方の入力端に、拡大鍵レジスタ121の領域121Cに格納される値 $K_n_2$ と、領域121Dに格納される値 $K_n_3$ とがそれぞれ入力される。

## [0100]

ここで、図 8 の構成から、領域 1 2 1 B に格納される値 $K_n_1$ は、領域 1 2 1 A に格納される値 $K_n_0$ と入力端 2 1 2 B に入力された値 $K_n_1$ との排他的論理和と見做すことができる。したがって、排他的論理和の性質から、値 $K_n_1$ と値 $K_n_0$ との排他的論理和を取ることで、入力端 2 1 2 B に入力された値 $K_n_1$ 1を得ることができる。

#### [0101]

#### [0102]

このように、 n-1 ラウンド目の拡大鍵を構成する値 $K_-(n-1)_-1$ 、値 $K_-(n-1)_-2$ および値 $K_-(n-1)_-3$ については、拡大鍵レジスタ1 2 1 の各領域1 2 1 A ~ 1 2 1 D に格納される n ラウンド目の拡大鍵の各値 $K_-n_-0$ 、値 $K_-n_-1$ 、値 $K_-n_-2$ および値 $K_-n_-3$ に対して排他的論理和を取ることで得ることができる。

#### [0103]

一方、入力端 2 1 2 A に入力された値 $K_{-}$ (n-1)\_0は、非線形回路 2 1 0 による非線形変換が含まれた演算が行われる。この場合、拡大鍵レジスタ 1 2 1 に格納される各値から値 $K_{-}$ (n-1)\_0を求めるためには、非線形回路 2 1 0 の逆変換を行うための回路を設ける必要がある。非線形回路 2 1 0 の逆変換を行う回路は、非線形回路 2 1 0 と同等の構成となり、回路規模も同等となるため、本実施の形態の主旨にそぐわない。

#### [0104]

そこで、本実施の形態では、検算用拡大鍵レジスタ151を設けて、非線形回路210の変換結果に対して直接的に線形変換を行う排他的論理和回路211Aの入力のうち一方に、当該検算用拡大鍵レジスタ151を接続する。図8の例では、検算用拡大鍵レジスタ151を、排他的論理和回路211Aの一方の入力端すなわち入力端212Aに接続する。そして、n・1ラウンド目に入力端212Aに入力された値K\_(n-1)\_0を、この検算用拡大鍵レジスタ151に格納する。したがって、検算用拡大鍵レジスタ151は、値K\_(n

10

20

30

40

-1)\_0が格納可能なだけの容量を有すればよい。この例では、検算用拡大鍵レジスタ 1 5 1 は、拡大鍵レジスタ 1 2 1 の 1 / 4 の容量があればよいことになる。

## [0105]

n ラウンド目に、この検算用拡大鍵レジスタ 1 5 1 に格納される値 $K_{-}(n-1)_{-}0$ と、線形変換回路 1 5 0 の排他的論理和回路 1 5 2 A ~ 1 5 2 C それぞれの出力である値 $K_{-}(n-1)_{-}1$ 、値 $K_{-}(n-1)_{-}2$ および値 $K_{-}(n-1)_{-}3$ とをビット結合して、値 $K_{-}(n-1)$ である  $E_{-}(n-1)$ である  $E_{-}(n-1)$ 0 が大鍵すなわち  $E_{-}(n-1)$ 0 が生成される。

#### [0106]

なお、図8では、検算用拡大鍵レジスタ151が拡大鍵生成回路120の入力側に接続されるように説明したが、これは、検算用拡大鍵レジスタ151が拡大鍵レジスタ121における領域121Aに対して接続されることと等価である。この場合、例えば、拡大鍵レジスタ121から拡大鍵が読み出されるタイミングで、拡大鍵レジスタ121の領域121Aのデータが検算用拡大鍵レジスタ151に格納され、検算用拡大鍵レジスタ151が更新される。

#### [0107]

図9は、図8に例示した本実施の形態による鍵スケジュール部140を、上述した図1に例示される演算装置100に対して鍵スケジュール部101に代えて適用させた例を示す。なお、図9において、上述した図1と共通する部分には同一の符号を付し、詳細な説明を省略する。

## [0108]

図9に例示される演算装置130は、データ撹拌部102と鍵スケジュール部140とを有する。なお、鍵スケジュール部140において、線形変換回路150および検算用拡大鍵レジスタ151を纏めて鍵出力部170と呼ぶ。すなわち、鍵出力部170は、検算用拡大鍵レジスタ151に格納される値K\_(n-1)\_0と、線形変換回路150の出力である値K\_(n-1)\_1、値K\_(n-1)\_2および値K\_(n-1)\_3とをビット結合して、検算用拡大鍵として出力する。

## [0109]

データ撹拌部102のラウンド演算回路110は、鍵スケジュール部140の拡大鍵レジスタ121から n ラウンド目の拡大鍵を読み出して1ラウンド分の演算処理を行う。また、ラウンド検算回路111は、検算用拡大鍵レジスタ151に格納される値K\_(n-1)\_0と、線形変換回路150の出力である値K\_(n-1)\_1、値K\_(n-1)\_2および値K\_(n-1)\_3とがビット結合された値K\_(n-1)を、n ラウンド目の検算用拡大鍵として用いて検算処理を行う。

## [0110]

データ撹拌部102は、これら拡大鍵レジスタ121から読み出した拡大鍵と、検算用拡大鍵レジスタ151および線形変換回路150から供給される検算用拡大鍵とを用いて、図4のフローチャートを用いて説明した処理により、演算処理および検算処理を行う。

#### [0111]

上述では、演算装置130が、暗号化処理または復号処理の演算に対する検算を異種処理で行う例について説明したが、これはこの例に限定されるものではない。すなわち、本実施の形態は、暗号化処理また復号処理の演算に対する検算を同種処理で行う場合にも、同様に適用することができる。これは、検算を異種処理により行う図1の構成と、検算を同種処理により行う図5の構成とで鍵スケジュール部101の構成が共通していることから明らかである。

# [0112]

このように、本実施の形態によれば、検算用拡大鍵レジスタ151は、拡大鍵の一部分を格納可能な容量を有すればよく、図1および図5を用いて説明したような、拡大鍵レジスタ121と同じ容量の検算用拡大鍵レジスタ122を持つ場合に比べて、遙かに回路規模を小さくすることができる。

# [0113]

50

10

20

30

なお、本実施の形態によれば、線形変換回路 1 5 0 が新たに追加されているが、この線形変換回路 1 5 0 は高々 3 の排他的論理和回路 1 5 2 A、 1 5 2 B および 1 5 2 C で構成されるものである。周知のように、排他的論理和回路は、非常に小規模な構成で実現され、検算用拡大鍵レジスタの容量が削減された効果を相殺するようなものではない。

#### [0114]

< 本実施の形態の第1の変形例 >

図10は、本実施の形態の第1の変形例による鍵スケジュール部141の一例の構成を示す。なお、図10において、上述した図8と共通する部分には同一の符号を付し、詳細な説明を省略する。本実施の形態の第1の変形例においては、検算用拡大鍵レジスタ151を、非線形回路210の変換結果に対して直接的に線形変換を行う排他的論理和回路211Aの他方の入力端、すなわち、非線形変換回路210の出力に接続する。

[ 0 1 1 5 ]

ここで、拡大鍵生成回路120では、非線形変換回路210の出力と入力端212Aに入力されたn-1ラウンド目の拡大鍵における値K\_(n-1)\_0との排他的論理和を取ることで、拡大鍵における値K\_n\_0を生成している。したがって、検算用拡大鍵レジスタ151に格納されるデータを1ラウンド前の状態に戻すには、当該データに対して同等の処理を施す必要がある。

#### [0116]

そこで、本実施の形態の第1の変形例における線形変換回路150′は、上述の実施の形態による線形変換回路150に対して排他的論理和回路154をさらに設けた構成とする。そして、排他的論理和回路154により、検算用拡大鍵レジスタ151に保持されるデータと、拡大鍵レジスタ121の領域121Aに格納される値K\_n\_0との排他的論理和を取る。これにより、拡大鍵生成回路120内の排他的論理和回路211Aと同等の処理を行うことができ、排他的論理和回路154から、値K\_n\_0が1ラウンド分戻された値K\_(n-1)\_0が出力される。

# [0117]

したがって、 n ラウンド目に、この検算用拡大鍵レジスタ 1 5 1 に格納される値K\_(n-1)\_0と、線形変換回路 1 5 0 の排他的論理和回路 1 5 2 A ~ 1 5 2 C それぞれの出力である値K\_(n-1)\_1、値K\_(n-1)\_2および値K\_(n-1)\_3とをビット結合して、値K\_(n-1)である n - 1 ラウンド目の拡大鍵すなわち n ラウンド目の検算用拡大鍵が生成される。

[0118]

このように、本第1の実施の形態の第1の変形例においても、検算用拡大鍵レジスタ151は、非線形変換回路210の出力が格納可能なだけの容量を有すればよいことになる。この場合も、上述と同様に、検算用拡大鍵レジスタ151は、拡大鍵レジスタ121の114の容量があればよい。

[0119]

本実施の形態の第1の変形例によれば、検算用拡大鍵レジスタ151にデータが格納されるタイミングが、拡大鍵レジスタ121の各領域121A、121B、121Cおよび121Dに値K\_n\_0、値K\_n\_1、値K\_n\_2および値K\_n\_3がそれぞれ格納されるタイミングと一致している。そのため、拡大鍵の各値K\_n\_0、値K\_n\_1、値K\_n\_2および値K\_n\_3が線形変換回路150′から出力されるタイミングの同時性の点で、上述の実施の形態による図8の構成に対して有利である。

[0120]

本実施の形態の第1の変形例による鍵スケジュール部141も、 n ラウンド目の拡大鍵と n - 1 ラウンド目の検算用拡大鍵とを同時に得ることができるため、上述した実施の形態による鍵スケジュール部140と同様に、図1に例示される演算装置100における鍵スケジュール部101に代えて適用可能である。勿論、本実施の形態の第1の変形例による鍵スケジュール部141は、暗号化処理また復号処理の演算に対する検算を同種処理で行う場合にも、同様に適用することができる。

# [0121]

10

20

30

#### < 本実施の形態の第2の変形例 >

次に、本実施の形態の第2の変形例について説明する。上述では、拡大鍵生成回路120における線形変換を、排他的論理和回路を用いて行っているが、これはこの例に限定されない。例えば、拡大鍵生成回路において、当該線形変換を他の構成で実現した場合であっても、本実施の形態を適用することができる。

# [0122]

図11は、本実施の形態の第2の変形例による鍵スケジュール部142の一例の構成を示す。この鍵スケジュール部142は、拡大鍵生成回路120 "における線形変換を、加算回路とビットシフト回路とを用いて実現した例である。なお、図11において、上述した図8と共通する部分には同一の符号を付し、詳細な説明を省略する。

#### [ 0 1 2 3 ]

すなわち、拡大鍵生成回路120″に対し、n-1ラウンド目の拡大鍵を4分割した各値K\_(n-1)\_0、値K\_(n-1)\_1、値K\_(n-1)\_2および値K\_(n-1)\_3が、入力端212A、212B、212Cおよび212Dを介して排他的論理和回路220A、加算回路221A、排他的論理和回路220Bおよび加算回路221Bそれぞれの一方の入力端に入力される。また、値K\_(n-1)\_3が非線形変換回路210に入力される。値K\_(n-1)\_3は、非線形変換回路210で非線形変換されて排他的論理和回路220Aの他方の入力端に入力される。

#### [0124]

排他的論理和回路 2 2 0 A は、一方の入力端に入力された値K\_(n-1)\_0と、他方の入力端に入力された、値K\_(n-1)\_3が非線形変換されたデータとの排他的論理和を取り、値K\_n\_0を出力する。この値K\_n\_0は、拡大鍵レジスタ 1 2 1 の領域 1 2 1 A に格納されると共に、加算回路 2 2 1 A の他方の入力端に入力される。

#### [ 0 1 2 5 ]

加算回路 2 2 1 A は、一方の入力端に入力された値 $K_{-}(n-1)_{-}1$ と、他方の入力端に入力された値 $K_{-}n_{-}0$ とを加算し、値 $K_{-}n_{-}1$ を出力する。この値 $K_{-}n_{-}1$ は、拡大鍵レジスタ 1 2 1 の領域 1 2 1 B に格納されると共に、ビットシフト回路 2 2 2 で左ビットシフトされて排他的論理和回路 2 2 0 B の他方の入力端に入力される。排他的論理和回路 2 2 0 B は、一方の入力端に入力された値 $K_{-}(n-1)_{-}2$ と、他方の入力端に入力された値 $K_{-}n_{-}1$ との排他的論理和を取り、値 $K_{-}n_{-}2$ を出力する。この値 $K_{-}n_{-}2$ は、拡大鍵レジスタ 1 2 1 の領域 1 2 1 C に格納されると共に、加算回路 2 2 1 B の他方の入力端に入力された値 $K_{-}n_{-}2$ とを加算し、値 $K_{-}n_{-}3$ を出力する。この値 $K_{-}n_{-}3$ は、拡大鍵レジスタ 1 2 1 の領域 1 2 1 D に格納される。

## [0126]

ここで、図11の構成から、領域121Bに格納される値 $K_n_1$ は、領域121Aに格納される値 $K_n_0$ と入力端212Bに入力された値 $K_n_1$ とを加算したものと見做すことができる。そのため、値 $K_n_1$ から値 $K_n_1$ のを減ずることで、入力端212Bに入力された値 $K_n_1$ 1を得ることができる。

# [0127]

領域121Cに格納される値 $K_n_2$ は、領域121Bに格納される値 $K_n_1$ と入力端212Cに入力された値 $K_n_1$ 2との排他的論理和と見做すことができる。そのため、値 $K_n_2$ 2と値 $K_n_1$ 2との排他的論理和を取ることで、入力端212Cに入力された値 $K_n_1$ 2を得ることができる。同様に、また、領域121Dに格納される値 $K_n_1$ 3は、領域121Cに格納される値 $K_n_1$ 2と入力端212Dに入力された値 $K_n_1$ 3とを加算したものと見做すことができる。そのため、値 $K_n_1$ 3から値 $K_n_1$ 2を減ずることで、入力端212Dに入力された値 $K_n_1$ 3を得ることができる。

#### [0128]

したがって、本実施の形態の第2の変形例では、拡大鍵レジスタ121に格納される拡大鍵を1ラウンド分戻すための線形変換回路150″を、減算回路155A、右ビットシフトを行うビットシフト回路230、排他的論理和回路156および減算回路155Bを

10

20

30

40

順次接続して構成する。

#### [0129]

このような構成において、減算回路155Aの減算入力端に拡大鍵レジスタ121の領域121Aに格納される値K\_n\_0を入力し、領域121Bに格納される値K\_n\_1を減算回路155Aの被減算入力端に入力する。減算回路155Aで、値K\_n\_1から値K\_n\_0を減じて n - 1ラウンド目の拡大鍵を構成する値K\_(n-1)\_1を得る。また、排他的論理和回路156の一方の入力端に、拡大鍵レジスタ121の領域121Bに格納される値K\_n\_1をビットシフト回路230で右ビットシフトさせて入力し、領域121Cに格納される値K\_n\_2を排他的論理和回路156の他方の入力端に入力する。排他的論理和回路156で、値K\_n\_1と値K\_n\_2との排他的論理和を取って、n - 1ラウンド目の拡大鍵を構成する値K\_(n-1)\_2を得る。さらに、減算回路155Bの減算入力端に拡大鍵レジスタ121の領域121Cに格納される値K\_n\_2を入力し、領域121Dに格納される値K\_n\_3を減算回路155Bの被減算入力端に入力する。減算回路155Bで、値K\_n\_1から値K\_n\_0を減じてn - 1ラウンド目の拡大鍵を構成する値K\_(n-1)\_3を得る。

#### [0130]

# [0131]

一方、入力端212Aに入力された値K\_(n-1)\_0は、非線形回路210による非線形変換が含まれた演算が行われる。そのため、上述した実施の形態と同様にして、n-1ラウンド目に入力端212Aに入力された値K\_(n-1)\_0を、この検算用拡大鍵レジスタ151に格納する。検算用拡大鍵レジスタ151は、値K\_(n-1)\_0が格納可能なだけの容量、すなわち拡大鍵レジスタ121の1/4の容量があればよい。

#### [0132]

n ラウンド目に、この検算用拡大鍵レジスタ151に格納される値 $K_-$ (n-1)\_0と、線形変換回路150"の減算回路155A、排他的論理和回路156および減算回路155Bそれぞれの出力である値 $K_-$ (n-1)\_1、値 $K_-$ (n-1)\_2および値 $K_-$ (n-1)\_3とをビット結合して、値 $K_-$ (n-1)であるn - ラウンド目の拡大鍵すなわちn ラウンド目の検算用拡大鍵が生成される。

# [0133]

このように、拡大鍵生成回路 1 2 0 "内で行われる線形変換を、排他的論理和以外の手段、例えば加算およびビットシフトを用いて行った場合でも、検算用拡大鍵レジスタの容量を削減することができる。

#### [0134]

なお、図11の例では、検算用拡大鍵レジスタ151を拡大鍵生成回路120″の入力端212Aに対して接続しているが、これはこの例に限定されない。例えば、図10を用いて説明した実施の形態の第1の変形例の如く、非線形変換回路210の出力に対して検算用拡大鍵レジスタ151を接続する構成とすることも可能である。この場合には、図10と同様に、検算用拡大鍵レジスタ151に格納されるデータと、領域121Aに格納される値K\_n\_0との排他的論理和を取ることで、出力すべき値K\_(n-1)\_0を得る。

# [ 0 1 3 5 ]

本実施の形態の第2の変形例による鍵スケジュール部142も、nラウンド目の拡大鍵とn-1ラウンド目の検算用拡大鍵とを同時に得ることができるため、上述した実施の形態による鍵スケジュール部140と同様に、図1に例示される演算装置100における鍵スケジュール部101に代えて適用可能である。勿論、本実施の形態の第2の変形例による鍵スケジュール部142は、暗号化処理また復号処理の演算に対する検算を同種処理で行う場合にも、同様に適用することができる。

# [0136]

10

20

30

< 本実施の形態の第3の変形例>

次に、本実施の形態の第3の変形例について説明する。上述の実施の形態では、拡大鍵 生成回路120における線形変換を、排他的論理和回路を用いて行っているが、当該線形 変換を、他の演算回路、例えば加算回路、減算回路、ビットシフト回路のうち1を用いて 行うことも考えられる。

[0137]

線形変換を加算回路により行う場合、図8の拡大鍵生成回路120における排他的論理 和 回 路 2 1 1 A 、 2 1 1 B 、 2 1 1 C お よ び 2 1 1 D を 、 そ れ ぞ れ 加 算 回 路 に 置 き 換 え る 。この場合には、線形変換回路150における排他的論理和回路152A、152Bおよ び1520を、それぞれ減算回路に置き換えればよいことになる。

[0138]

線形変換を減算回路により行う場合、図8の拡大鍵生成回路120における排他的論理 和回路211A、211B、211Cおよび211Dを、それぞれ減算回路に置き換える 。この場合には、線形変換回路150における排他的論理和回路152A、152Bおよ び152Cを、それぞれ加算回路に置き換えればよいことになる。

[0139]

拡大鍵生成回路120における線形変換を、ビットシフト回路のみを用いて行うことも 可能である。この場合には、線形変換回路150では、拡大鍵生成回路120で用いられ たビットシフト回路と逆向きのビットシフトを行うビットシフト回路を、拡大鍵生成回路 120のビットシフト回路と対応する位置に設ける。

【符号の説明】

[0140]

100,100, 演算装置

- 101 鍵スケジュール部

- 102,102 データ撹拌部

- 1 1 0 ラウンド演算回路

- 1 1 1 1 1 6 0 ラウンド検算回路

- データレジスタ 1 1 2

- 1 1 3 検算用データレジスタ

- 1 1 4 , 1 1 4 ' 比較回路

- 信号選択部 1 1 5

- 120 拡大鍵生成回路

- 1 2 1 拡大鍵レジスタ

- 1 2 2 検算用拡大鍵レジスタ

- 150,150',150" 線形変換回路

- 151 検算用拡大鍵レジスタ

- 1 5 2 A , 1 5 2 B , 1 5 2 C 排他的論理和回路

- 1 7 0 鍵出力部

- 2 1 0 非線形回路

- 2 1 1 A , 2 1 1 B , 2 1 1 C , 2 1 1 D 排他的論理和回路

- 212A,212B,212C,212D 入力端

10

20

30

#### 【図2】 【図1】

#### 【図3】

# 【図4】

# スタート データ入力 ~S400 入力データに対し、ラウンド演算回路で演算処理を行い データレジスタに結果を格納 検算用データレジスタに入力データを格納 S401 データレジスタを入力とし、ラウンド演算回路で演算処理 データレジスタを入力とし、ラウンド検算回路で検算処理 ~S402 検算用データレジスタと ラウンド検算回路の出力を比較 不一致 ↓一致 データレジスタのデータで検算用データレジスタを更新 ラウンド演算回路の演算結果でデータレジスタを更新 ~S404 ラウンド演算回路における 演算処理は所定回数終了したか? **↓** Yes データレジスタを入力とし、ラウンド検算回路で検算処理 S406 検算用データレジスタと ラウンド検算回路の出力を比較 ↓一致 データレジスタのデータを出力データとする S408 データ出力 S409 エンド

# 【図5】

【図6】 【図7】

【図8】 【図9】

【図10】

# 【図11】

# 【国際調査報告】

|                                                                | INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                            | International application No.                                                                                                                                                                                                                                                                                                       |                                       |                                              |  |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------|--|

|                                                                |                                                                                                                                                                                                                                        | PCT/JP2                                                                                                                                                                                                                                                                                                                             | 009/066536                            |                                              |  |

| A. CLASSIFICATION OF SUBJECT MATTER<br>H04L9/06(2006.01)i      |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                     |                                       |                                              |  |

| According to Inte                                              | ernational Patent Classification (IPC) or to both national                                                                                                                                                                             | d classification and IP                                                                                                                                                                                                                                                                                                             | С                                     |                                              |  |

| B. FIELDS SE                                                   | ARCHED                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                     |                                       |                                              |  |

| Minimum docun<br>H04L9/06                                      | nentation searched (classification system followed by cl                                                                                                                                                                               | assification symbols)                                                                                                                                                                                                                                                                                                               |                                       |                                              |  |

| Jitsuyo                                                        |                                                                                                                                                                                                                                        | ent that such document<br>tsuyo Shinan T<br>roku Jitsuyo S                                                                                                                                                                                                                                                                          | oroku Koho                            | ne fields searched<br>1996–2009<br>1994–2009 |  |

|                                                                | vase consulted during the international search (name of \$/JMEDPlus/JST7580 (JDreamII)                                                                                                                                                 | data base and, where                                                                                                                                                                                                                                                                                                                | practicable, search t                 | terms used)                                  |  |

| C. DOCUMEN                                                     | ITS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                     |                                       |                                              |  |

| Category*                                                      | Citation of document, with indication, where app                                                                                                                                                                                       | propriate, of the releva                                                                                                                                                                                                                                                                                                            | ant passages                          | Relevant to claim No.                        |  |

| A                                                              | JP 8-30195 A (Nippon Telegraph And Telephone Corp.), 02 February 1996 (02.02.1996), paragraphs [0014] to [0018]; fig. 1 (Family: none)                                                                                                 |                                                                                                                                                                                                                                                                                                                                     |                                       | 1-5                                          |  |

| A                                                              | JP 10-154976 A (Toshiba Corp.),<br>09 June 1998 (09.06.1998),<br>paragraphs [0070] to [0085]; fig. 10 to 12<br>(Family: none)                                                                                                          |                                                                                                                                                                                                                                                                                                                                     |                                       | 1-5                                          |  |

| A                                                              | JP 2005-503069 A (ST Microel<br>27 January 2005 (27.01.2005),<br>paragraphs [0032] to [0047];<br>& US 2005/0021990 A1 & EP<br>& WO 2003/024017 A2                                                                                      | fig. 1, 2                                                                                                                                                                                                                                                                                                                           | A.),                                  | 1-5                                          |  |

| × Further do                                                   | cuments are listed in the continuation of Box C.                                                                                                                                                                                       | See patent fan                                                                                                                                                                                                                                                                                                                      | nily annex.                           |                                              |  |

| "A" document de<br>be of particu<br>"E" carlier applie<br>date | gories of cited documents:  fining the general state of the art which is not considered to lar relevance  cation or patent but published on or after the international filing  thich may throw doubts on priority claim(s) or which is | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention document of particular relevance; the claimed invention cannot be considered novel or cannot be considered novel or state alone |                                       |                                              |  |

| special reaso<br>"O" document re                               | blish the publication date of another citation or other<br>in (as specified) ferring to an oral disclosure, use, exhibition or other means<br>iblished prior to the international filing date but later than the<br>claimed            | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art "&" document member of the same patent family                                      |                                       |                                              |  |

| 26 Oct                                                         | al completion of the international search obser, 2009 (26.10.09)                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                     | ne international sear<br>aber, 2009 ( |                                              |  |

|                                                                | ng address of the ISA/<br>se Patent Office                                                                                                                                                                                             | Authorized officer                                                                                                                                                                                                                                                                                                                  |                                       |                                              |  |

| Facsimile No.                                                  |                                                                                                                                                                                                                                        | Telephone No.                                                                                                                                                                                                                                                                                                                       |                                       |                                              |  |

Facsimile No.

Form PCT/ISA/210 (second sheet) (April 2007)

# INTERNATIONAL SEARCH REPORT

International application No.

PCT/JP2009/066536

|                |                                                                        | PCT/JP2      | 009/066536                |

|----------------|------------------------------------------------------------------------|--------------|---------------------------|

| C(Continuation | a). DOCUMENTS CONSIDERED TO BE RELEVANT                                |              |                           |

| Category*      | Citation of document, with indication, where appropriate, of the relev | ant passages | Relevant to claim No.     |

|                |                                                                        | S.A.),       | Relevant to claim No. 1-5 |

|                |                                                                        |              |                           |

Form PCT/ISA/210 (continuation of second sheet) (April 2007)

# 国際調査報告

国際出願番号 PCT/JP2009/066536

発明の属する分野の分類(国際特許分類(IPC))

Int.Cl. H04L9/06(2006.01) i

B. 調査を行った分野

調査を行った最小限資料(国際特許分類(IPC))

Int,Cl. H04L9/06

最小限資料以外の資料で調査を行った分野に含まれるもの

日本国実用新案公報 1922-1996年 日本国公開実用新案公報 1971-2009年 1996-2009年 日本国実用新案登録公報 日本国登録実用新案公報 1994-2009年

国際調査で使用した電子データベース(データベースの名称、調査に使用した用語)

JSTPlus/JMEDPlus/JST7580(JDreamII)

| ( | ο. | 関連す | ると | 部め | られる | 文献 |

|---|----|-----|----|----|-----|----|

|   |    |     |    |    |     |    |

| - 170727        | 2 日本の 5年                                 |                |

|-----------------|------------------------------------------------------------------------------|----------------|

| 引用文献の<br>カテゴリー* | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                            | 関連する<br>請求項の番号 |

| A               | JP 8-30195 A (日本電信電話株式会社) 1996.02.02,<br>段落【0014】-【0018】,【図1】 (ファミリーなし)      | 1 – 5          |

| A               | JP 10-154976 A (株式会社東芝) 1998.06.09,<br>段落【0070】-【0085】,【図10】-【図12】 (ファミリーなし) | 1-5            |

#### C欄の続きにも文献が列挙されている。

パテントファミリーに関する別紙を参照。

- \* 引用文献のカテゴリー

- 「A」特に関連のある文献ではなく、一般的技術水準を示す 「T」国際出願日又は優先日後に公表された文献であって もの

- 「E」国際出願目前の出願または特許であるが、国際出願目 以後に公表されたもの

- 「L」優先権主張に疑義を提起する文献又は他の文献の発行 日若しくは他の特別な理由を確立するために引用す る文献(理由を付す)

- 「O」口頭による開示、使用、展示等に言及する文献

- 「P」国際出願目前で、かつ優先権の主張の基礎となる出願

- の日の後に公表された文献

- 出願と矛盾するものではなく、発明の原理又は理論 の理解のために引用するもの

- 「X」特に関連のある文献であって、当該文献のみで発明 の新規性又は進歩性がないと考えられるもの

- 「Y」特に関連のある文献であって、当該文献と他の1以 上の文献との、当業者にとって自明である組合せに よって進歩性がないと考えられるもの

- 「&」同一パテントファミリー文献

国際調査を完了した日

26. 10. 2009

国際調査報告の発送日

02.11.2009

国際調査機関の名称及びあて先

日本国特許庁([SA/JP) 郵便番号100-8915 特許庁審査官(権限のある職員)

5 S 3146

松平 英

電話番号 03-3581-1101 内線 3546

様式PCT/ISA/210 (第2ページ) (2007年4月)

東京都千代田区霞が関三丁目4番3号

国際調査報告

国際出願番号 PCT/JP2009/066536

C (続き). 関連すると認められる文献 引用文献の 関連する 請求項の番号 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示 カテゴリー\* JP 2005-503069 A (エステーミクロエレクトロニクス ソシエテ ア 1 - 5Α ノニム) 2005.01.27, 段落【0032】-【0047】,【図1】,【図2】 & US 2005/0021990 A1 & EP 1423937 A & WO 2003/024017 A2 JP 2005-522912 A (オベルトゥル カード システムズ ソシエテ 1 - 5Α アノニム) 2005.07.28, 段落【0009】-【0030】,【図1】-【図3】 & US 2006/0104438 A1 & EP 1493242 A & WO 2003/085881 A1

様式PCT/ISA/210 (第2ページの続き) (2007年4月)

## フロントページの続き

# (72)発明者 新保 淳

東京都港区芝浦一丁目1番1号 株式会社東芝内

F ターム(参考) 5J104 AA16 AA18 AA32 EA04 JA03 NA37

(注)この公表は、国際事務局(WIPO)により国際公開された公報を基に作成したものである。なおこの公表に係る日本語特許出願(日本語実用新案登録出願)の国際公開の効果は、特許法第184条の10第1項(実用新案法第48条の13第2項)により生ずるものであり、本掲載とは関係ありません。