(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6181844号

(P6181844)

(45) 発行日 平成29年8月16日(2017.8.16)

(24) 登録日 平成29年7月28日(2017.7.28)

|                      |                   |

|----------------------|-------------------|

| (51) Int.Cl.         | F 1               |

| G06F 13/14 (2006.01) | G06F 13/14   310A |

| G06F 9/52 (2006.01)  | G06F 9/46   472Z  |

| G06F 13/12 (2006.01) | G06F 13/12   340D |

| G06F 3/08 (2006.01)  | G06F 3/08   H     |

| G06F 3/06 (2006.01)  | G06F 3/06   301F  |

請求項の数 17 (全 20 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-500857 (P2016-500857)  |

| (86) (22) 出願日 | 平成26年3月7日(2014.3.7)           |

| (65) 公表番号     | 特表2016-512361 (P2016-512361A) |

| (43) 公表日      | 平成28年4月25日(2016.4.25)         |

| (86) 国際出願番号   | PCT/US2014/021834             |

| (87) 国際公開番号   | W02014/164310                 |

| (87) 国際公開日    | 平成26年10月9日(2014.10.9)         |

| 審査請求日         | 平成28年11月28日(2016.11.28)       |

| (31) 優先権主張番号  | 13/798,803                    |

| (32) 優先日      | 平成25年3月13日(2013.3.13)         |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                                         |

|-----------|-----------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サンディエゴ モアハウス ドラ<br>イブ 5775   |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                  |

| (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                                  |

| (72) 発明者  | アサフ・シャチャム<br>アメリカ合衆国・カリフォルニア・921<br>21・サン・ディエゴ・モアハウス・ドラ<br>イブ・5775・クアルコム・インコーポ<br>レイテッド |

最終頁に続く

(54) 【発明の名称】デュアルホスト組込み共有デバイスコントローラ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のプロセッサを第2のプロセッサによりプリエンプトするための方法であって、直接アクセスによって前記第1のプロセッサおよび第2のプロセッサと共有される共有不揮発性メモリデバイスから前記第1のプロセッサによりデータアクセスを実施するステップと、

前記第1のプロセッサによる前記共有不揮発性メモリデバイスへの前記第1のプロセッサによる操作のプリエンプションを要求するために、前記第1のプロセッサにドアベル割込みを発行するステップと、

前記第1のプロセッサによる前記データアクセスをプリエンプトし、前記第2のプロセッサによるメモリアクセスを開始するステップと、

を含み、

前記第1のプロセッサは、シャドーレジスタの第1のセットに対する排他的アクセス権を有し、シャドーレジスタの前記第1のセットにアクセスするように構成され、シャドーレジスタの前記第1のセットの各シャドーレジスタは、アドレスマップされたレジスタが共有アドレススペースにマップされるように前記共有アドレススペースにリンクされるよう構成された前記アドレスマップされたレジスタを含み、

前記第2のプロセッサは、シャドーレジスタの第2のセットに対する排他的アクセス権を有し、シャドーレジスタの前記第2のセットにアクセスするように構成され、シャドーレジスタの前記第2のセットの各シャドーレジスタは、アドレスマップされたレジスタが共

10

20

有アドレススペースにマップされるように前記共有アドレススペースにリンクされるよう

に構成された前記アドレスマップされたレジスタを含み、

前記第1のプロセッサにより前記データアクセスを実施するステップは、シャドーレジ

スタの前記第1のセットにアクセスするステップを含み、

前記第2のプロセッサにより前記メモリアクセスを開始するステップは、シャドーレジ

スタの前記第2のセットにアクセスするステップを含む、

方法。

#### 【請求項 2】

前記共有不揮発性メモリデバイスはフラッシュドライブまたはディスクドライブである

請求項1に記載の方法。 10

#### 【請求項 3】

前記第1のプロセッサと前記第2のプロセッサにより共有される別個のメモリが、データ

に正しくアクセスするために前記共有不揮発性メモリデバイスへのアクセスを与えられた

前記第1のプロセッサと前記第2のプロセッサにより要求されるメモリパラメータを格納す

る、請求項1に記載の方法。

#### 【請求項 4】

前記第2のプロセッサにより前記アクセスを完了するステップと、

前記第1のプロセッサにより前記データアクセスを再開するステップと、

をさらに備える請求項1に記載の方法。

#### 【請求項 5】

前記共有不揮発性メモリデバイスへの前記メモリアクセスを開始するために、前記第2

のプロセッサにセマフォロックを認可するステップと、

前記第2のプロセッサが前記メモリアクセスを完了した後に、前記データアクセスを再

開するために、前記第1のプロセッサにセマフォロックを認可するステップと

をさらに備える請求項1に記載の方法。 20

#### 【請求項 6】

2つのプロセッサが共有デバイスへ独立にアクセスできるようにする装置であって、

共有アドレススペースと、

シャドーレジスタの第1のセットであって、シャドーレジスタの前記第1のセットの各

シャドーレジスタは、アドレスマップされたレジスタが共有アドレススペースにマップさ

れるように前記共有アドレススペースにリンクされるように構成された前記アドレスマッ

プされたレジスタを含む、シャドーレジスタの第1のセットと。 30

シャドーレジスタの第2のセットであって、シャドーレジスタの前記第2のセットの各

シャドーレジスタは、アドレスマップされたレジスタが共有アドレススペースにマップさ

れるように前記共有アドレススペースにリンクされるように構成された前記アドレスマッ

プされたレジスタを含む、シャドーレジスタの第2のセットと、

を備える、共有デバイスコントローラと、

前記共有デバイスコントローラを介して共有デバイスに接続され、シャドーレジスタの

第1のセットに対して排他的アクセス権を有するように構成された、第1のプロセッサと、

前記共有デバイスコントローラを介して前記共有デバイスに接続され、シャドーレジス

タの第2のセットに対して排他的アクセス権を有するように構成された、第2のプロセッサ

と、

を備え、

前記共有デバイスコントローラは、セマフォを前記第1のプロセッサに認可すると、シ

ャドーレジスタの前記第1のセットを前記共有アドレススペースにマップし、前記セマフ

オを前記第2のプロセッサに認可すると、シャドーレジスタの前記第2のセットを前記共有

アドレススペースにマップするように構成されたセマフォ状態マシンを有する、

を備える装置。

#### 【請求項 7】

前記セマフォ状態マシンは、前記共有デバイス上の前記第1のプロセッサの操作のプリ

50

エンプト要求に応答して、前記第1のプロセッサの前記操作をプリエンプトするために前記第2のプロセッサへの前記アクセスを認可して、前記第2のプロセッサが前記共有デバイスにアクセスできるようにする、請求項6に記載の装置。

【請求項8】

前記第1のプロセッサにより要求されたトランザクションが、シャドーレジスタの前記第1のセットに記憶されている情報を使用し、前記第2のプロセッサにより要求されたトランザクションが、シャドーレジスタの前記第2のセットに記憶されている情報を使用する、請求項6に記載の装置。

【請求項9】

シャドーレジスタの前記第1のセットとシャドーレジスタの前記第2のセットを、前記セマフォの認可により制御されるように同一の共有アドレススペースにマップするように構成された共有アドレスマルチプレクサをさらに備える請求項6に記載の装置。 10

【請求項10】

前記第1のプロセッサの前記共有デバイスに関連付けられている操作は、前記共有デバイスに関連付けられている前記操作を開始するために前記第2のプロセッサにセマフォロックを認可することによってプリエンプトされ、前記第2のプロセッサによる操作が完了すると、前記共有デバイスに対する前記操作を再開するために前記セマフォロックが前記第1のプロセッサに返される、請求項6に記載の装置。

【請求項11】

2つのプロセッサが共有デバイスへ独立にアクセスできるようにするための方法であつて、 20

第1のアドレスマップされたレジスタへのアクセスが共有アドレスにマップされるように前記共有アドレスにリンクされるように構成された前記第1のアドレスマップされたレジスタを含む、第1のシャドーレジスタを、第1のプロセッサによるセマフォの取得に応答して、前記共有アドレスにマップするステップであって、前記第1のプロセッサが、第1の値を前記共有アドレスにおいて前記第1のシャドーレジスタに書き込む、ステップと、

前記第1のプロセッサによる共有デバイスへの第1の操作の完了時の前記セマフォの解放に応答して、前記第1のシャドーレジスタを前記共有アドレスからリンク除去するステップと、

第2のアドレスマップされたレジスタへのアクセスが共有アドレスにマップされるように前記共有アドレスにリンクされるように構成された前記第2のアドレスマップされたレジスタを含む、第2のシャドーレジスタを、第2のプロセッサによるセマフォの取得に応答して、前記共有アドレスにマップするステップであって、前記第2のプロセッサが、第2の値を前記共有アドレスにおいて前記第2のシャドーレジスタに書き込む、ステップと、 30

前記第2のプロセッサによる前記共有デバイスへの第2の操作の完了時の前記セマフォの解放に応答して、前記第2のシャドーレジスタを前記共有アドレスからリンク除去するステップであって、前記第2の操作の完了時に、前記第1の値は前記第1のシャドーレジスタ内で不变であり、前記第2の値は前記第2のシャドーレジスタ内で不变である、ステップとを備える方法。

【請求項12】

前記第1の操作は、前記第1の値に従った前記共有デバイスから前記第1のプロセッサへのデータ転送である請求項11に記載の方法。 40

【請求項13】

前記第2の操作は、前記第2の値に従った前記共有デバイスから前記第2のプロセッサへのデータ転送である請求項11に記載の方法。

【請求項14】

前記第1の操作は、前記第2の操作を達成するために前記第2のプロセッサによってプリエンプトされる前記第1のプロセッサ操作への操作の一部であり、前記第2の操作が完了すると、前記第1のプロセッサは、以前に書き込まれた前記第1の値を用いて前記操作を完了するために前記セマフォを再度取得する、請求項11に記載の方法。 50

## 【請求項 15】

コンピュータ可読プログラムデータおよびコードにより符号化されたコンピュータ可読非一時的記憶媒体であって、前記プログラムデータおよびコードは、プロセッサによって実行されるとき、

第1のアドレスマップされたレジスタへのアクセスが共有アドレスにマップされるように前記共有アドレスにリンクされるように構成された前記第1のアドレスマップされたレジスタを含む、第1のシャドーレジスタを、第1のプロセッサによるセマフォの取得に応答して、前記共有アドレスにマップするステップであって、前記第1のプロセッサが、第1の値を前記共有アドレスにおいて前記第1のシャドーレジスタに書き込む、ステップと、

前記第1のプロセッサによる共有デバイスへの第1の操作の完了時の前記セマフォの解放に応答して、前記第1のシャドーレジスタを前記共有アドレスからリンク除去するステップと、

第2のアドレスマップされたレジスタへのアクセスが共有アドレスにマップされるように前記共有アドレスにリンクされるように構成された前記第2のアドレスマップされたレジスタを含む、第2のシャドーレジスタを、第2のプロセッサによるセマフォの取得に応答して、前記共有アドレスにマップするステップであって、前記第2のプロセッサが、第2の値を前記共有アドレスにおいて前記第2のシャドーレジスタに書き込む、ステップと、

前記第2のプロセッサによる前記共有デバイスへの第2の操作の完了時の前記セマフォの解放に応答して、前記第2のシャドーレジスタを前記共有アドレスからリンク除去するステップであって、前記第2の操作の完了時に、前記第1の値は前記第1のシャドーレジスタ内で不变であり、前記第2の値は前記第2のシャドーレジスタ内で不变である、ステップとを実施するように動作可能である、コンピュータ可読非一時的記憶媒体。

## 【請求項 16】

コンピュータ可読プログラムデータおよびコードにより符号化されたコンピュータ可読非一時的記憶媒体であって、前記プログラムデータおよびコードは、プロセッサによって実行されるとき、

直接アクセスによって第1のプロセッサおよび第2のプロセッサと共有される共有不揮発性メモリデバイスから前記第1のプロセッサによりデータアクセスを実施するステップと、

前記第1のプロセッサによる前記共有不揮発性メモリデバイスへの前記第1のプロセッサによる操作のプリエンプションを要求するために、前記第1のプロセッサにドアベル割込みを発行するステップと、

前記第1のプロセッサによる前記データアクセスをプリエンプトし、前記第2のプロセッサによるメモリアクセスを開始するステップと、

を実施するように動作可能であり、

前記第1のプロセッサは、シャドーレジスタの第1のセットに対する排他的アクセス権を有し、シャドーレジスタの前記第1のセットにアクセスするように構成され、シャドーレジスタの前記第1のセットの各シャドーレジスタは、アドレスマップされたレジスタが共有アドレススペースにマップされるように前記共有アドレススペースにリンクされるように構成された前記アドレスマップされたレジスタを含み、

前記第2のプロセッサは、シャドーレジスタの第2のセットに対する排他的アクセス権を有し、シャドーレジスタの前記第2のセットにアクセスするように構成され、シャドーレジスタの前記第2のセットの各シャドーレジスタは、アドレスマップされたレジスタが共有アドレススペースにマップされるように前記共有アドレススペースにリンクされるように構成された前記アドレスマップされたレジスタを含み、

前記第1のプロセッサにより前記データアクセスを実施するステップは、シャドーレジスタの前記第1のセットにアクセスするステップを含み、

前記第2のプロセッサにより前記メモリアクセスを開始するステップは、シャドーレジスタの前記第2のセットにアクセスするステップを含む、

コンピュータ可読非一時的記憶媒体。

10

20

30

40

50

**【請求項 17】**

2つのプロセッサが共有デバイスへ独立にアクセスできるようにする装置であって、

第1のプロセッサが共有デバイスにアクセスし、シャドーレジスタの第1のセットへの排他的アクセス権を有するための手段であって、シャドーレジスタの前記第1のセットの各シャドーレジスタは、アドレスマップされたレジスタが共有アドレススペースにマップされるように前記共有アドレススペースにリンクされるように構成された前記アドレスマップされたレジスタを含む、手段と、

第2のプロセッサが共有デバイスにアクセスし、シャドーレジスタの第2のセットへの排他的アクセス権を有するための手段であって、シャドーレジスタの前記第2のセットの各シャドーレジスタは、アドレスマップされたレジスタが共有アドレススペースにマップされるように前記共有アドレススペースにリンクされるように構成された前記アドレスマップされたレジスタを含む、手段と、

共有デバイスコントローラが、セマフォを前記第1のプロセッサに認可すると、シャドーレジスタの前記第1のセットを前記共有アドレススペースにマップし、前記セマフォを前記第2のプロセッサに認可すると、シャドーレジスタの前記第2のセットを前記共有アドレススペースにマップするための手段と、

を備える装置。

**【発明の詳細な説明】****【技術分野】****【0001】****優先権出願**

本出願は、参照により全体が本明細書に組み込まれる、2013年3月13日に出願した「DUAL HOST EMBEDDED SHARED DEVICE CONTROLLER」と題する米国特許出願第13/798,803号の優先権を主張するものである。

**【0002】**

本開示は一般に、マイクロプロセッサの分野に関し、詳細には、デュアルホスト共有デバイスコントローラによって提供される機能に関する。

**【背景技術】****【0003】**

携帯電話、ラップトップコンピュータ、携帯情報端末(PDA)などのような、多くのポータブル製品は、通信およびマルチメディアプログラムのようなプログラムを実行する処理システムを使用する。そのような製品の処理システムは、複数のプロセッサ、命令およびデータを記憶するための多重レベルのキャッシュを含む複合メモリシステム、コントローラ、通信インターフェースのような周辺デバイス、ならびに、たとえばシングルチップ上に構成された固定機能論理ブロックを含むことができる。

**【0004】**

スマートフォン、タブレットなどを含む、マルチプロセッサポータブルシステムにおいて、アプリケーションプロセッサは、多数の組込み型プロセッサの間の操作を調整するために使用され得る。ホストアプリケーションプロセッサはまた、組込み型または取外し可能な不揮発性メモリモジュールおよびディスクドライブのようなストレージ要素にアクセスポートを提供することもできる。他の組込み型プロセッサは、モデム制御プロセッサ、音声信号プロセッサなどのような、固有のリアルタイム操作に専用であってもよい。組込み型プロセッサの各々は、その専用の機能に関連付けられている固有の時間の制約を有することもある各自のファイルシステムを操作することができる。そのようなマイクロプロセッサシステムはまた、組込み型メモリおよび取外し可能不揮発性メモリモジュールまたはディスクドライブのような、メモリストレージを共有することが求められる場合もある。しかし、共有不揮発性メモリストレージデバイスが各々、ホスト制御プロセッサを通じてアクセス可能な単一のポートを有するシステムにおいては、サブシステム間の相互依存性およびプロセス間通信(IPC)のオーバーヘッドの増大が原因となって、固有のプロセッサにおいて専用機能からのメモリアクセスに過剰な待ち時間が生じることもあり得る。ま

10

20

30

40

50

た、そのようなシステムのデバッグは、容認しがたいほど複雑になる可能性もある。

【発明の概要】

【課題を解決するための手段】

【0005】

本開示は、その複数の態様の中で、各組込み型プロセッサが、アプリケーションプロセッサを通じてアクセスを集中化することなく、独立して不揮発性メモリに直接アクセスできるようにするための、さらに効率的な方法および装置を提供することが有利であると認識する。また、1つのプロセッサの操作を第2のプロセッサによりハンドシェークおよびプリエンプトしてタイムクリティカルなイベントを処理するための、さらに効率的な方法および装置を提供することは有利である。そのような目的のため、本発明の実施形態は、第1のプロセッサを第2のプロセッサによりプリエンプトするための方法を扱う。データのブロックは、第1のプロセッサおよび第2のプロセッサによる直接アクセスによって共有される共有不揮発性メモリデバイスから、第1のプロセッサによってアクセスされる。ドアベル割込みは、共有不揮発性メモリデバイス上の第1のプロセッサによる操作のプリエンプションを要求するために第1のプロセッサに発行される。第1のプロセッサによるデータブロックアクセスは、第2のプロセッサによるメモリアクセスを開始するようにプリエンプトされる。10

【0006】

別の実施形態は、2つのプロセッサが、共有デバイスに独立してアクセスできるようにする装置を扱う。第1のプロセッサは共有デバイスに結合され、シャドーレジスタの第1のセットへの排他的アクセス権を有するように構成される。第2のプロセッサは共有デバイスに結合され、シャドーレジスタの第2のセットへの排他的アクセス権を有するように構成される。セマフォー状態マシンを有する共有デバイスコントローラは、セマフォーを第1のプロセッサに認可すると、シャドーレジスタの第1のセットを、共有アドレススペースにマップし、セマフォーを第2のプロセッサに認可すると、シャドーレジスタの第2のセットを、共有アドレススペースにマップするように構成される。20

【0007】

別の実施形態は、2つのプロセッサが、共有デバイスに独立してアクセスするための方法を扱う。第1のシャドーレジスタは、第1のプロセッサによるセマフォーの取得に応答して、共有アドレスにマップされ、第1のプロセッサは、第1の値を、共有アドレスにおいて第1のシャドーレジスタに書き込む。第1のプロセッサによる共有デバイスへの第1の操作の完了時にセマフォーが解放されたことに応答して、第1のシャドーレジスタは、共有アドレスへのそのリンクから除去される。第2のシャドーレジスタは、第2のプロセッサによるセマフォーの取得に応答して、共有アドレスにマップされ、第2のプロセッサは、第2の値を、共有アドレスにおいて第2のシャドーレジスタに書き込む。第2のプロセッサによる共有デバイスへの第2の操作の完了時にセマフォーが解放されたことに応答して、第2のシャドーレジスタは、共有アドレスへのそのリンクから除去され、第2の操作の完了時に、第1の値は第1のシャドーレジスタ内で不变であり、第2の値は第2のシャドーレジスタ内で不变である。30

【0008】

別の実施形態は、電力制御のための方法を扱う。第1のプロセッサの制御下にあり、複数のプロセッサによって共有されているメモリデバイスへの供給電圧は、メモリデバイスへのアクセスの欠如を示す指示を受信したことに応答して低減される。供給電圧は、複数のプロセッサのうちの別のプロセッサによりメモリアクセス要求を受信したことに応答して、第1のプロセッサの制御下の作動レベルに戻される。40

【0009】

別の実施形態は、コンピュータ可読プログラムデータおよびコードにより符号化されたコンピュータ可読非一時的媒体を扱う。第1のシャドーレジスタは、第1のプロセッサによるセマフォーの取得に応答して、共有アドレスにマップされ、第1のプロセッサは、第1の値を、共有アドレスにおいて第1のシャドーレジスタに書き込む。第1のプロセッサによる50

共有デバイスへの第1の操作の完了時にセマフォーが解放されたことに応答して、第1のシャドーレジスタは、共有アドレスへのそのリンクから除去される。第2のシャドーレジスタは、第2のプロセッサによるセマフォーの取得に応答して、共有アドレスにマップされ、第2のプロセッサは、第2の値を、共有アドレスの第2のシャドーレジスタに書き込む。第2のプロセッサによる共有デバイスへの第2の操作の完了時にセマフォーが解放されたことに応答して、第2のシャドーレジスタは、共有アドレスへのそのリンクから除去され、第2の操作の完了時に、第1の値は第1のシャドーレジスタ内で不变であり、第2の値は第2のシャドーレジスタ内で不变である。

#### 【0010】

別の実施形態は、コンピュータ可読プログラムデータおよびコードにより符号化されたコンピュータ可読非一時的媒体を扱う。データのブロックは、第1のプロセッサおよび第2のプロセッサによる直接アクセスによって共有される共有不揮発性メモリデバイスから、第1のプロセッサによってアクセスされる。ドアベル割込みは、共有不揮発性メモリデバイス上の第1のプロセッサによる操作のプリエンプションを要求するために第1のプロセッサに発行される。第1のプロセッサによるデータブロックアクセスは、第2のプロセッサによるメモリアクセスを開始するようにプリエンプトされる。

#### 【0011】

さらなる実施形態は、2つのプロセッサが、共有デバイスに独立してアクセスできるようにする装置を扱う。第1のプロセッサが共有デバイスにアクセスし、シャドーレジスタの第1のセットへの排他的アクセス権を有するようにするための手段が使用される。第2のプロセッサが共有デバイスにアクセスし、シャドーレジスタの第2のセットへの排他的アクセス権を有するようにするための手段が使用される。共有デバイスコントローラが、セマフォーを第1のプロセッサに認可すると、シャドーレジスタの第1のセットを、共有アドレススペースにマップし、セマフォーを第2のプロセッサに認可すると、シャドーレジスタの第2のセットを、共有アドレススペースにマップするようにするための手段が使用される。

#### 【0012】

本発明の他の実施形態は、本発明の様々な実施形態が例示により示され説明される後段の詳細な説明から当業者には容易に明らかとなることを理解されたい。理解されるように、本発明は、他の異なる実施形態が可能であり、その複数の詳細は、本発明の精神および範囲をすべてが逸脱することなく、様々な他の点において変更が可能である。したがって、図面および詳細な説明は、限定的ではなく、事実上例示的なものと見なされるべきである。

#### 【0013】

本発明の様々な態様は、添付の図面において、限定としてではなく、一例として示される。

#### 【図面の簡単な説明】

#### 【0014】

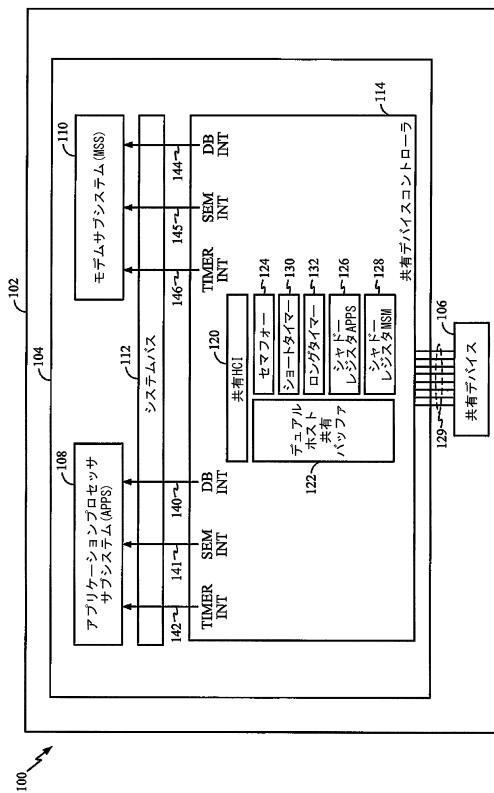

【図1】有利に採用され得るモデルサブシステムにおいてリアルタイム制約を満足するマルチプロセッササブシステムの実施形態を示す図である。

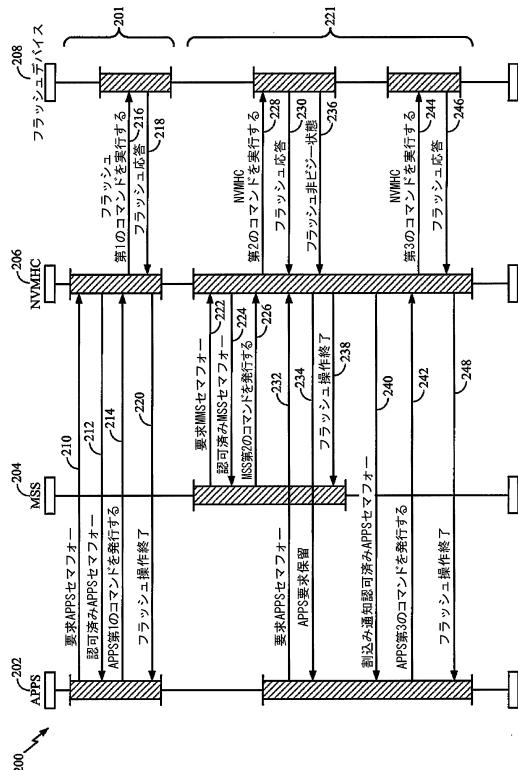

【図2A】マルチプロセッサデータトランザクションにおいてデータにアクセスするプロセスの実施形態を示す図である。

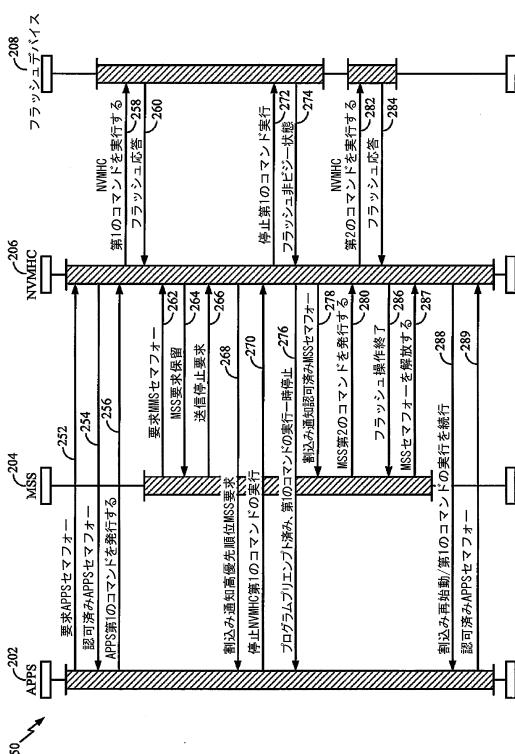

【図2B】リアルタイムタスクにサービスを提供するために、マルチプロセッササブシステムにおいてデータトランザクションをプリエンプトするプロセスの実施形態を示す図である。

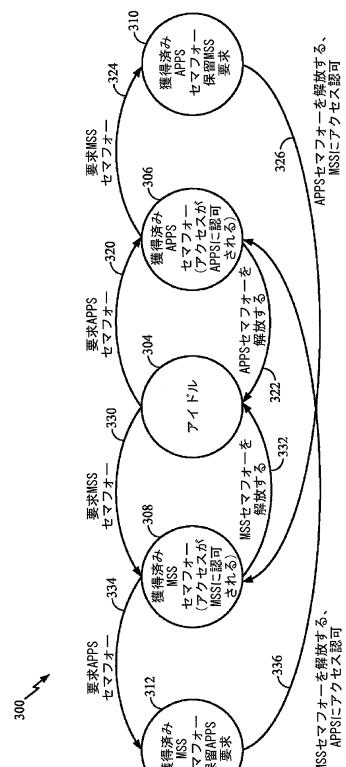

【図3】リアルタイムタスクにサービスを提供するためにデータトランザクションのプリエンプションをサポートするセマフォー状態マシンの実施形態を示す図である。

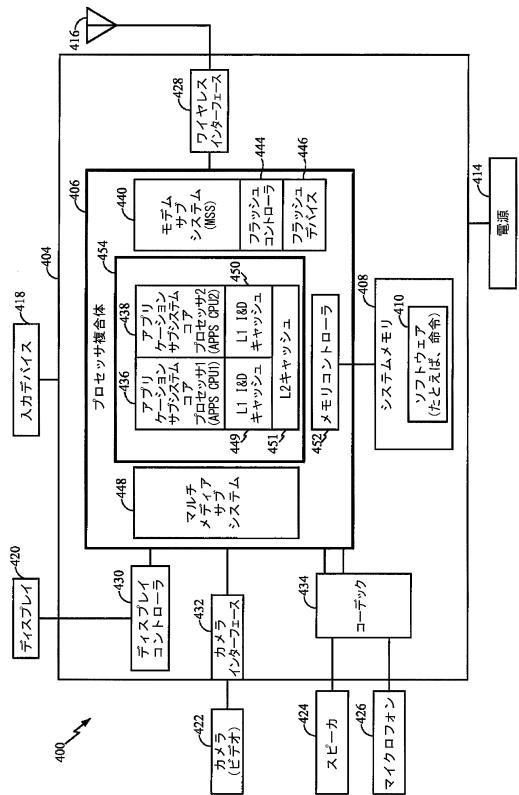

【図4】モデルサブシステムのリアルタイム要求を満足するように構成されるプロセッサ複合体を有するポータブルデバイスを示す図である。

#### 【発明を実施するための形態】

10

20

30

40

50

## 【0015】

添付の図面と併せて後段に示される詳細な説明は、本発明の様々な例示的な実施形態の説明であることを意図されており、本発明が実施され得る実施形態のみを表すことを意図されてはいない。詳細な説明は、本発明の十分な理解をもたらすことを目的として具体的な詳細を含む。しかし、本発明が、それらの具体的な詳細を伴うことなく実施され得ることが、当業者には明らかとなろう。場合によっては、よく知られた構造およびコンポーネントは、本発明の概念を不明瞭にすることを避けるため、ブロック図の形態で示される。

## 【0016】

専用機能固有のプロセッサからのメモリアクセスにおける過剰な待ち時間のような問題に対処するため、マルチポートメモリのソフトウェアおよびハードウェア設計が、共有不揮発性メモリモジュールに実施されてもよい。たとえば、モデム制御プロセッサのような、重要な待ち時間要求を伴う専用のプロセッサは、ホスト制御プロセッサのメモリアクセスポートとは別の第2のメモリポートにアクセスすることができてもよい。単一アクセスポート設計においてホスト制御プロセッサを通じてアクセスをパイプするようにモデム制御プロセッサに要求しないことによって、マルチポート設計は、共有不揮発性メモリモジュールからデータにアクセスする待ち時間を低減し、ひいてはプロセス間通信(IPC)手順に費やす時間を回避する。

## 【0017】

加えて、要求時ページングおよび他のそのような高速アクセス技法は、メモリモジュールを共有する複数プロセッサによって使用されてもよい。たとえば、システム操作のシナリオは、モデムプロセッサにおいてタイムクリティカルなイベントが発生するときに、ホスト制御プロセッサが取外し可能メモリモジュールから大きいデータブロックにアクセスする場合を含むことができる。マルチポートメモリシステムにおいて、モデムプロセッサは、ホスト制御プロセッサをプリエンプトして、モデムプロセッサが取外し可能メモリモジュールのデータに迅速にアクセスできるようにし、それによりタイムクリティカルなイベントのメモリアクセス時間を低減することができる。プリエンプションは、アクセスを求めるプロセッサによって要求され、プリエンプトされるプロセッサにおいて開始されるドアベル割込みを有利に使用することができる。ドアベル割込みの使用により、ドアベル割込みを伴わない場合に要求される大量のIPCと比較すると、アプリケーションプロセスからのはるかに迅速な応答が可能になる。また、デバイスステータスおよび操作モード情報のような共有不揮発性メモリパラメータは、アクセスが認可された後の使用のためにアクセスを求めるプロセッサによってアクセス可能な別個のメモリに記憶されてもよい。プリエンプションの後、アクセス権は、アプリケーション(ホスト制御)プロセッサに戻され、ホスト制御プロセッサは、大きいデータブロックのアクセスを再開することができるか、またはアクセスを再始動することができる。プロセッサによるアクセス制御は、後段においてさらに詳細に説明されるように、ハードウェアにサポートされるセマフォーアトミック制御メカニズムを使用する。

## 【0018】

複数のプロセッサ間のアクセス要求はまた、たとえば、先入れ先出し(FIFO)メモリまたは優先キューを使用してバッファに入れられてもよく、メモリアクセスのためのプロセッサ間のより迅速な切替えにハードウェアサポートを提供する。共有不揮発性メモリモジュールの電力制御は、共有不揮発性メモリモジュールへの供給電圧がいつ安全に低減され得るかまたはオフにされ得るかを指示するための少なくとも1つの非アクティブタイマーを含む。電力は、メモリを共有するプロセッサのいずれかによって再始動されて、データへの迅速なアクセスを可能にすることができる。異なる長さの第2の非アクティブタイマーは、エラー回復手順をサポートするために使用されてもよい。マルチプロセッサシステムにおいて、セマフォーロックを有するプロセッサが共有不揮発性メモリデバイスにアクセスし、第2の非アクティブタイマーがタイムアウトしたこと示す指示が制御プロセッサにおいて受信されると、制御プロセッサは、不揮発性メモリコントローラに対してエラー回復手順を開始して、共有不揮発性メモリデバイスへのアクセスを解放する。セマフォー

10

20

30

40

50

ロックを有するプロセッサがリセットされて、セマフォーロックは解放され、オプションで、共有不揮発性メモリデバイスは再初期化される。

#### 【0019】

本発明の実施形態は、モデルサブシステムを有するプロセッサにおいて適切に採用されてもよい。図1は、モデルサブシステムにおいてリアルタイム制約を満足するマルチプロセッササブシステム100の実施形態を示す。マルチプロセッササブシステム100は、サブシステムコントローラ104と、フラッシュメモリ、ディスクドライブ、または2つ以上のプロセッサ間で共有される他のデバイスのような、共有デバイス106とを含むデバイスシステムコア102を含む。サブシステムコントローラ104は、アプリケーションプロセッササブシステム(APPS)108と、MSSプロセッサで構成されたモデルサブシステム(MSS)110と、システムバス112と、フラッシュコントローラのような共有デバイスコントローラ114とを含む。APPS108は、製品の要件に従って、1つ、2つ、またはそれ以上のプロセッサで構成されてもよい。APPS108およびMSS110は、システムバス112を介して共有デバイス106にアクセスし、共有デバイスコントローラ114によって制御される。共有デバイス106はまた、取外し可能フラッシュメモリを含むことができるか、または組込み型メモリであってもよい。共有デバイス106が、デバイスシステムコア102においてサブシステムコントローラ104と統合されてもよいことに留意されたい。10

#### 【0020】

共有デバイスコントローラ114は、共有ホストコントローラインターフェース(HCI)120と、デュアルホスト共有バッファ122と、複数のアトミックアクセスセマフォー124と、APSシャドーレジスタ126と、MSSシャドーレジスタ128と、共有デバイス106へのアクセスパス129と、ショートタイマー130と、ロングタイマー132とを含み、これらについては後段においてさらに詳細に説明される。APPSの割込み(INT)信号は、ドアベル割込み(DB INT)140と、セマフォー割込み(SEM INT)141と、タイマー割込み(TIM INT)142とを含む。MSSの割込み(INT)信号は、ドアベル割込み(DB INT)144と、セマフォー割込み(SEM INT)145と、タイマー割込み(TIM INT)146とを含む。共有HCI120は、単一のアドレス領域を使用して、共有レジスタのセット、および2つのシャドーレジスタセット(126および128)へのアクセスを提供する。セマフォーは、どちらのシャドーレジスタセットが任意の所与の時点においてHCIアドレス領域にマップされるかを管理する。各プロセッサは、同じアドレススペースを使用してトランザクションを発行する。20

#### 【0021】

アプリケーションプロセッササブシステム(APPS)108は、APPSシャドーレジスタ126に排他的アクセス権を有し、モデルサブシステム(MSS)110は、MSSシャドーレジスタ128に排他的アクセス権を有する。たとえば、APPS108およびMSS110におけるアクセス制御は、排他的アクセス権を強制するための手段を提供するようにセットアップされてもよい。代替の実施形態において、APPSシャドーレジスタ126は、APPS108のみへのアクセスパスで構成されてもよく、MSSシャドーレジスタ128は、MSS110のみへのアクセスパスで構成されてもよいので、排他的アクセス権を強制するための手段を提供することができる。いずれの場合においても、手段は、APPS108がMSSシャドーレジスタ128にアクセスすることができないように、およびMSS110がAPPSシャドーレジスタ126にアクセスすることができないように提供される。セマフォーは、シャドーレジスタへのアクセスを管理するこのルールをさらに強制する。有利なことに、不揮発性メモリのような共有デバイス106への直接アクセスを有する各プロセッサは、排他的アクセス権を保証するために対応するアクセス制御メカニズムで構成される。30

#### 【0022】

ショート非アクティブタイマー130は、APPS108またはMSS110からの予想される応答が過剰に遅延する場合に、エラー回復のための割込みを生成するために使用される。たとえば、APPS108がセマフォーを取得しようと試みるが、MSS110が、100msのようなある時間後にセマフォーを解放できない場合、予想される応答の受信がないということは、MSSソフトウェアが現在のタスクに応答していないことの指示である。その場合、ショート非アクテ40

イブタイマー130は満了して、エラー回復手順が必要であることをAPPS108に指示する。ロング非アクティブタイマー132は、共有デバイスコントローラ114が、5秒のような長いカウント期間にわたる非ビジー状態を指示する場合、電力制御の割込みを生成するために使用される。共有デバイスコントローラ114がビジー状態になるときは常に、ロング非アクティブタイマーはリセットされ、カウント期間が再始動される。ロングカウント期間に到達した後、共有デバイスコントローラ114および共有デバイス106は、低電力状態におかれる。APPS108またはMSS110のいずれかによるアクセスは、共有デバイスコントローラ114および共有デバイス106の電力を上げて元の状態に戻す。

#### 【 0 0 2 3 】

図2Aは、マルチプロセッサデータトランザクションにおいてデータにアクセスするプロセス200の実施形態を示す。プロセス200は、アプリケーションプロセッササブシステム(APPS)202と不揮発性メモリホストコントローラ(NVMHC)206との間、モデムサブシステム(MSS)204とNVMHC206との間、およびNVMHC206とフラッシュデバイス208との間のトランザクションのシーケンスにおいて示される。APPS202は、共有レジスタおよびAPPSシャドーレジスタ126を通じてNVMHC206にアクセスし、MSS204は、共有レジスタおよびMSSシャドーレジスタ128を通じてNVMHC206にアクセスする。一般に、制御アクセスは、シャドーレジスタを通じて達成されるが、一部のモードにおいては、データがシャドーレジスタを通じて同様に転送されてもよい。図2Aおよび図2Bに示されるトランザクションの場合、デバイスが初期化されており、動作可能であって、低減電力モードにないことが想定される。また、共有バッファ122には、後続のトランザクションに必要とされ得る初期化済みデータが取り込まれる。フラッシュデバイス208は、組込み型フラッシュメモリか、または組込み型フラッシュメモリを備える取外し可能セキュアデータカードのいずれかである。

10

#### 【 0 0 2 4 】

トランザクションの第1のセット201は、APPS202とフラッシュデバイス208との間のデータトランザクションについて示される。トランザクション210において、APPS202は、セマフォーを取得するよう求める要求をNVMHC206に送信する。トランザクション212において、NVMHC206は、セマフォー要求を認可し、セマフォーが取得されたことを指示する応答をAPPS202に送信する。トランザクション214において、APPS202は、フラッシュデバイス208での操作を開始するための第1のコマンド(1st CMD)をNVMHC206に送信する。トランザクション216において、NVMHC206は、データ読み取りコマンドのような、第1のコマンドを、フラッシュデバイス208で実行する。トランザクション218において、フラッシュデバイス208は、要求されたデータで、NVMHC206への応答を開始する。トランザクション220において、すべての要求されたデータが読み取られた後、NVMHC206は、フラッシュ操作終了メッセージをAPPS202に送信する。

20

#### 【 0 0 2 5 】

トランザクションの第2のセット221は、MSS204とフラッシュデバイス208との間のデータトランザクションについて示され、APPS202が優先順位の低いコマンドのアクセスセマフォーを取得しようと試みるが、MSS204のトランザクションが発生している。トランザクション222において、MSS204は、セマフォーを取得するよう求める要求をNVMHC206に送信する。トランザクション224において、NVMHC206は、セマフォー要求を認可し、セマフォーが取得されたことを指示する応答をMSS204に送信する。トランザクション226において、MSS204は、フラッシュデバイス208での操作を開始するための第2のコマンド(2nd CMD)をNVMHC206に送信する。トランザクション228において、NVMHC206は、データ読み取りコマンドのような、第2のコマンドを、フラッシュデバイス208で実行する。トランザクション230において、フラッシュデバイス208は、要求されたデータで、NVMHC206への応答を開始する。トランザクション232において、APPS202は、セマフォーを取得するよう求める優先順位の低い要求をNVMHC206に送信する。トランザクション234において、MSS204が優先順位の低いAPPS要求よりも高い優先権を有するのでセマフォーに対するAPPS要求が現在認可されず、保留状態にあることを指示するAPPSメッセージがAPPS202に送信され、この場合、MSS204はプリエンプトされ得ない。トランザクション236において、要求されたデータ

30

40

50

を完了したフラッシュデバイス208は、非ビジー状態メッセージでNVMHC206に応答する。トランザクション238において、すべての要求されたデータが読み取られた後、NVMHC206は、フラッシュデバイス操作終了メッセージをMSS204に送信する。トランザクション240において、NVMHC206は、保留APPSセマフォー要求を認可し、割込みを発行して、保留APPSアクセスセマフォーが取得されたことをAPPS202に通知する。トランザクション242において、APPSは、第3のコマンド(3rd CMD)をNVMHC206に送信する。トランザクション244において、NVMHC206は、データ読み取りコマンドのような、第3のコマンドを、フラッシュデバイス208に実行する。トランザクション246において、フラッシュデバイスは、要求されたデータで、NVMHC206への応答を開始する。トランザクション248において、すべての要求されたデータが読み取られた後、NVMHC206は、フラッシュ操作終了メッセージをAPPS202に送信する。

10

#### 【0026】

図2Bは、リアルタイムタスクにサービスを提供するために、マルチプロセッササブシステムにおいてデータトランザクションをプリエンプトするプロセス250の実施形態を示す。プロセス250は、アプリケーションプロセッササブシステム(APPS)202とセキュアデジタルカードまたは不揮発性メモリホストコントローラ(NVMHC)206と、モデムサブシステム(MS)204によって優先順位の高い要求により割込みされるフラッシュデバイス208との間のトランザクションのシーケンスにおいて示される。これらのトランザクションの場合、デバイスが初期化されており、動作可能であって、低減電力モードにないことが想定される。フラッシュデバイス208は、組込み型フラッシュメモリか、または組込み型フラッシュメモリを備える取外し可能セキュアデータカードのいずれかである。トランザクション252において、APPS202は、セマフォーを取得するよう求める要求をNVMHC206に送信する。トランザクション254において、NVMHC206は、セマフォー要求を認可し、セマフォーが取得されたことを指示する応答をAPPS202に送信する。トランザクション256において、APPS202は、フラッシュデバイス208での操作を開始するための第1のコマンド(1st CMD)をNVMHC206に送信する。トランザクション258において、NVMHC206は、データ読み取りコマンドのような、第1のコマンドを、フラッシュデバイス208で実行する。トランザクション260において、フラッシュデバイス208は、要求されたデータで、NVMHC206への応答を開始する。

20

#### 【0027】

トランザクション262において、およびAPPSデータトランザクションを完了する前に、MS204は、セマフォーを取得するよう求める要求をNVMHC206に送信する。トランザクション264において、セマフォーに対するMSS要求が現在認可されず、保留状態にあることを指示するメッセージがMSS204に送信される。トランザクション266において、MSS204がフラッシュデバイス208の優先順位の高いアクセスを試みているので、MSS204は停止要求をNVMHC206に送信する。トランザクション268において、NVMHC206は、ドアベル割込みと称される優先順位の高い割込みをAPPS202に送信して、優先順位の高いMSS要求について通知する。トランザクション270において、APPS202は、ドアベル割込みに応答し、第1のコマンドの実行を停止するためのメッセージをNVMHC206に送信する。トランザクション272において、NVMHC206は、第1のコマンドの実行を停止する。トランザクション274において、フラッシュデバイス208は、ビジー状態ではないことを指示する。トランザクション276において、NVMHC206は、プログラムがプリエンプトされて、第1のコマンドの実行が一時停止されたというメッセージをAPPS202に送信する。トランザクション278において、NVMHC206は、ドアベル割込みをMSS204に発行して、保留中のセマフォーを取得したことをMSS204に通知する。トランザクション280において、MSS204は、第2のコマンド(2nd CMD)をNVMHC206に送信する。トランザクション282において、NVMHC206は、データ読み取りコマンドのような、第2のコマンドを、フラッシュデバイス208で実行する。トランザクション284において、フラッシュデバイス208は、要求されたデータで、NVMHC206への応答を開始する。トランザクション286において、要求されたデータトランザクションを完了した後、NVMHC206は、フラッシュ操作終了メッセージをMSS204に送信し、トランザクション287において、MSSはセマフォーを解放する。トランザクション288において、NVMHC206は、第1のコマンド

30

40

50

ドの実行を再始動するかまたは続行すべきであるという割込みをAPPS202に発行する。トランザクション289において、APPS202は、認可されたセマフォーに応答し、1つの実施形態において、APPS202は第1のコマンドを最初から再始動し、別の実施形態においては、APPSは、トランザクション276においてプリエンプトされたポイントから第1のコマンドの実行を続行する。

#### 【0028】

図3は、リアルタイムタスクにサービスを提供するためにデータトランザクションのプリエンプションをサポートするセマフォー状態マシン300の実施形態を示す。セマフォー状態マシン300は、APPS108およびMSS110による共有デバイスコントローラ114へのアクセスを管理する。状態マシン300がIDLE状態304にあるとき、APPS108またはMSS110が、状態マシン300への制御アクセスを取得することができ、それにより共有デバイスコントローラ114へのアクセスを獲得することができる。状態マシン300は、APPS108またはMSS110のいずれかから要求を受信することによって、獲得済みAPPSセマフォー状態306または獲得済みMSSセマフォー状態308のような獲得済み状態に遷移する。たとえば、状態マシン300が、状態306または状態308にあり、他のホストがその他のホストでの既存の操作をプリエンプトするための取得を試みる場合、状態マシン300は、獲得済みAPPSセマフォーと保留MSS要求状態310、または獲得済みMSSセマフォーと保留APPS要求状態312のような獲得済みと保留状態に遷移する。たとえば、状態マシン300が獲得済みAPPSセマフォー状態306にある場合、MSSからの要求を受け入れると、状態マシン300は、対応する獲得済みAPPSセマフォーと保留MSS要求状態310に遷移する。その状態310において、セマフォーを保持しているAPPSがセマフォーを解放すると、状態マシン300は、獲得済みMSSセマフォー状態308に遷移する326。この状態マシン300は、2つのホスト間の制御のハンドオフを加速するために採用される。

#### 【0029】

図2Bのトランザクションは、図3の状態マシン300において示される状態遷移と相関関係があつてもよい。たとえば、APPS202がセマフォーを要求するトランザクション252は、トランザクション320に対応し、APPS202が認可済みAPPSセマフォーによって指示されるセマフォーを取得するトランザクション254は、状態306に対応する。MSS204は、遷移324に対応する、MSSセマフォーを要求するトランザクション262の取得を試みる。要求は即座には容認されないので、MSS要求保留トランザクション264が発生し、これは状態310に対応する。セマフォーは、トランザクション278においてMSS204に認可され、これは遷移326に対応する。引き続き、トランザクション287においてMSS204がセマフォーを解放することはアイドル状態304に戻る遷移332に対応する。トランザクション289においてAPPS202が認可済みセマフォーに応答することは獲得済みAPPSセマフォー状態306への遷移320に対応する。同様の方法で、MSS204がアイドル状態304にセマフォーを要求することは遷移330に対応し、MSS204がセマフォーを取得することは状態308に対応する。APPS202は、遷移334に対応する取得を試みる。要求が即座には容認されない場合、システムは、状態312においてAPPS要求を保留して獲得済みMSSセマフォーに留まる。APPS要求が認可される場合、MSS204はセマフォーを解放し、アクセスがAPPS202に認可され、これはAPPS202がセマフォーを獲得したことを指示する状態306への遷移336に対応する。

#### 【0030】

シャドーレジスタに関して、NVMHC206は、ソフトウェアが、たとえばアプリケーションの初期化時点で、1回構成することを予想する多数のレジスタを含み、それらの値がアプリケーションの動作中に不变のままであることに依存する。複数ホストプロセッサのシナリオにおいて、各ホストプロセッサは、同一のレジスタに異なる値を割り当てようとする場合もあるが、レジスタがそれらの値を保持することを期待している。そのようなストレージ容量の提供に対処するため、シャドーレジスタのセットが各ホストに割り当てられる。シャドーレジスタの各ホストのセットは、セマフォーによって制御されるように单一のアドレススペースにマップされる。セマフォーがホストAに認可される場合、レジスタAのシャドーセットは、ホストAソフトウェアでアクセス可能にされ、値はホストAによってあ

らかじめ構成されている。その後になって、セマフォーがホストBに認可される場合、レジスタBのシャドーセットは、ホストBソフトウェアでアクセス可能にされるが、レジスタAのシャドーセットは将来の使用のために記憶される。たとえば、シャドーレジスタのAPP SセットおよびシャドーレジスタのMSSセットは、同じ初期状態にリセットされる。読み取りアクセスと書き込みアクセスの両方についてソフトウェアでアクセス可能にされるシャドーレジスタのセットは、セマフォーの状態によって決定される。APPSがセマフォーを取得すると、APPSシャドーレジスタの値は、共有デバイスコントローラ114内のハードウェアマルチプレクサのような多重化の手段によってAPPSソフトウェアで可視のアドレススペースにマップされる。APPSがセマフォーを取得すると、マルチプレクサがAPPSシャドーレジスタをAPPSソフトウェアで可視にし、MSSがセマフォーを取得すると、MSSシャドーレジスタをMSSソフトウェアで可視にするための手段がハードウェアマルチプレクサによって提供されるというように、セマフォーはハードウェアマルチプレクサを制御する。したがって、共有デバイスにアクセスし、シャドーレジスタの第1のセットへの排他的アクセス権を有するようにするための手段が、第1のプロセッサ、APPSに提供され、共有デバイスにアクセスし、シャドーレジスタの第2のセットへの排他的アクセス権を有するようにするための手段が、第2のプロセッサ、MSSに提供される。APPSソフトウェアは、値を読み取り、任意の値を再構成することができるか、または値をそのAPPSシャドーレジスタ内で不变のままにしておくことができる。MSSソフトウェアが後にセマフォーを取得すると、MSSシャドーレジスタの記憶されている値は、MSSソフトウェアで可視のアドレススペースにマップされ、APPSシャドーレジスタはアクセス不能になる。したがって、共有デバイスコントローラが、セマフォーを第1のプロセッサ、APPS、に認可すると、シャドーレジスタの第1のセットを、共有アドレススペースにマップし、セマフォーを第2のプロセッサ、MSS、に認可すると、シャドーレジスタの第2のセットを、共有アドレススペースにマップするようになるための手段が提供される。セマフォーがアイドル状態にある場合、APPSシャドーレジスタはアドレススペースにマップされてもよく、デフォルト設定としてAPPSソフトウェアでアクセス可能にされてもよい。

### 【0031】

次の表は、最初にAPPSがデータを転送することで始まり、第2にMSSがデータを転送することが続き、次いで第3にAPPSがデータを転送する、という3つのデータ転送のシナリオにおいてシャドーレジスタの使用を示す。

### 【0032】

10

20

30

【表1】

|    |                                                                                                                         |    |

|----|-------------------------------------------------------------------------------------------------------------------------|----|

| 1  | APPSはセマフォーを取得する                                                                                                         |    |

| 2  | APPSは、DMAチャネルを#5に設定するためにアドレスにマップされたレジスタに書き込む、アドレスにマップされたレジスタは APPS シャドーレジスタである                                          | 10 |

| 3  | APPSは、DMAチャネル#5を使用するデータ転送トランザクションを実行する                                                                                  |    |

| 4  | APPSはセマフォーを解放する                                                                                                         |    |

| 5  | MSSはセマフォーを取得する                                                                                                          |    |

| 6  | MSSは、DMAチャネルを#7に設定するために同じアドレスにマップされたレジスタに書き込む、アドレスにマップされたレジスタは MSS シャドーレジスタである                                          |    |

| 7  | MSSは、DMAチャネル#7を使用するデータ転送トランザクションを実行する                                                                                   |    |

| 8  | MSSはセマフォーを解放する                                                                                                          |    |

| 9  | APPSはセマフォーを取得する                                                                                                         |    |

| 10 | APPSは、DMAチャネル#5を使用するデータ転送トランザクションを実行する、APPSは、DMAチャネルが引き続きチャネル#5に設定されていると仮定して、アドレスにマップされたレジスタへの書き込みを行わないか、またはその読み取りを行わない | 20 |

| 11 | APPSはセマフォーを解放する                                                                                                         |    |

## 【0033】

上記のシナリオにおいて、MSSがステップ11の後にセマフォーを再取得する場合、DMAチャネル#7を記憶しているMSSシャドーレジスタは、共有アドレススペースにマップされ、MSSソフトウェアがDMAチャネルを変更するようにプログラムされていない限り、MSSソフトウェアはDMAチャネルを再書き込みする必要はなくなる。ホスト固有の設定のこの保存は、同じアドレススペースにマップされた他のシャドーレジスタと共に保持される。そのような制御レジスタは、不揮発性メモリまたは2つのホストプロセッサ間で共有される任意の他のデバイスとのすべてのトランザクションについて再構成される必要はない。

## 【0034】

図4は、モデムサブシステムのリアルタイム要求を満足するように構成されるプロセッサ複合体を有するポータブルデバイス400を示す。ポータブルデバイス400は、ワイヤレス電子デバイスであってもよく、ソフトウェア命令410を有するシステムメモリ408に結合されたプロセッサ複合体406を含むシステムコア404を含むことができる。ポータブルデバイス400は、電源414と、アンテナ416と、キーボードのような入力デバイス418と、液晶ディスプレイLCDのようなディスプレイ420と、ビデオ機能を備える1つまたは2つのカメラ422と、スピーカ424と、マイクロフォン426とを備える。システムコア404はまた、ワイヤレスインターフェース428と、ディスプレイコントローラ430と、カーラインインターフェース432と、コードック434とを含む。プロセッサ複合体406は、ローカルレベル1命令およびデータ(L1 I&D)キャッシュ449を有するAPPS CPU1 436と、ローカルレベル1命令およびデータ(L1 I&D)キャッシュ450を有するAPPS CPU2 438という2つの中央演算処理装置を含むプリケーションプロセッササブシステム(APPS)454のデュアルコア配列を含むことができる。APPS454は、図1のAPPS108に対応することができる。プロセッサ複合体406はまた、モデムサブシステム440と、フラッシュコントローラ444と、フラッシュデバイス446と、マルチメディアサブシステム448と、レベル2キャッシュ451と、メモリコントローラ452とを含むことができる。フラッシュデバイス446は、取外し可能フラッシュメモリを含むことができるか、または組込み型メモリであってもよい。モデムサブシステム440は図1のMSS1 30 40 50

10に対応することができ、フラッシュコントローラ444は図1の共有デバイスコントローラ114に対応することができ、フラッシュデバイス446は図1の共有デバイス106に対応することができる。

#### 【0035】

説明に役立つ例において、システムコア404は、図1、図2A、図2B、および図3において、またはこれらに関連して説明される実施形態のいずれかに従って動作する。たとえば、図4に示されるように、APPS454デュアルコアプロセッサは、図2Aおよび図2Bに示されるデータトランザクションを提供するために、関連するデュアルコアプロセッサのL1 I&Dキャッシュのメモリ、L2キャッシュ451、およびシステムメモリ408に記憶されているデータまたはプログラム命令にアクセスするように構成される。

10

#### 【0036】

ワイヤレスインターフェース428は、アンテナ416およびワイヤレスインターフェース428を介して受信されたワイヤレスデータがMSS440に提供されてAPPS454と共有され得るように、プロセッサ複合体406およびワイヤレスアンテナ416に結合されてもよい。カメラインターフェース432は、プロセッサ複合体406に結合され、さらにビデオ機能を備えるカメラ422のような1つまたは複数のカメラに結合される。ディスプレイコントローラ430は、プロセッサ複合体406、およびディスプレイデバイス420に結合される。コーダ/デコーダ(CODEC)434もまた、プロセッサ複合体406に結合される。ステレオスピーカのペアを備えることができるスピーカ424、およびマイクロフォン426は、CODEC434に結合される。周辺デバイスおよびそれらの関連するインターフェースは、例示的なものであり、数量または容量において限定されることはない。たとえば、入力デバイス418は、ユニバーサルシリアルバス(USB)インターフェースなど、QWERTYスタイルキーボード、英数字キーボード、および特定のデバイスまたは異なるデバイスでの組合せで個別に実装され得る数値パッドを含むことができる。

20

#### 【0037】

APPS454は、システムメモリ408のような非一時的コンピュータ可読媒体に記憶され、デュアルコアプロセッサ436および438のようなコンピュータに、プログラムを実行させて図2Aおよび図2Bに示されるデータトランザクションを提供させるために実行可能である、ソフトウェア命令410を実行するように構成される。APPS CPU1 436およびAPPS CPU2 438は、異なるレベルのキャッシュメモリおよびシステムメモリ408からアクセスされるソフトウェア命令410を実行するように構成される。

30

#### 【0038】

特定の実施形態において、システムコア404は、システムインパッケージ内、またはシステムオンチップデバイス上に物理的に編成されてもよい。特定の実施形態において、システムオンチップデバイスとして編成されたシステムコア404は、図4に示されるように、電源414と、ワイヤレスアンテナ416と、入力デバイス418と、ディスプレイデバイス420と、カメラまたは複数のカメラ422と、スピーカ424と、マイクロフォン426とに物理的に結合され、取外し可能フラッシュデバイス446に結合されてもよい。

#### 【0039】

本明細書において説明される実施形態によるポータブルデバイス400は、セットトップボックス、エンターテイメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定ロケーションデータユニット、モバイルロケーションデータユニット、携帯電話、セルラー電話、コンピュータ、ポータブルコンピュータ、タブレット、モニタ、コンピュータモニタ、テレビジョン、チューナ、ラジオ、衛星ラジオ、音楽プレイヤー、デジタル音楽プレイヤー、ポータブル音楽プレイヤー、ビデオプレイヤー、デジタルビデオプレイヤー、デジタルビデオディスク(DVD)プレイヤー、ポータブルデジタルビデオプレイヤー、データまたはコンピュータ命令を記憶または取り出す任意の他のデバイスのような、多種多様な電子デバイス、もしくはその任意の組合せに組み込まれてもよい。

40

#### 【0040】

50

本明細書において開示される実施形態に関連して説明される様々な例示的な論理プロック、モジュール、回路、要素、またはコンポーネントは、汎用プロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)または他のプログラマブル論理コンポーネント、ディスクリートゲートまたはトランジスタ論理、ディスクリートハードウェアコンポーネント、または本明細書において説明される機能を実行するように設計されたこれらの任意の組合せにより実装または実行されてもよい。汎用プロセッサは、マイクロプロセッサであってもよいが、代替策において、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、または状態マシンであってもよい。プロセッサはまた、たとえばDSPとマイクロプロセッサの組合せのようなコンピューティングコンポーネントの組合せ、複数のマイクロプロセッサ、DSPコアと併せた1つまたは複数のマイクロプロセッサ、または望ましいアプリケーションに適した任意の他のそのような構成として実装されてもよい。10

#### 【0041】

たとえば、図1のAPPS108または図4のデュアルコアプロセッサ436および438は、たとえば、プログラムの制御下でリアルタイムタスクにサービスを提供するために、マルチプロセッサシステムにおいてデータトランザクションをプリエンプトできるようにする命令を実行するように構成されてもよい。プロセッサ複合体406にローカルに直接関連付けられているコンピュータ可読非一時的ストレージ媒体上に記憶されているプログラムは、たとえば命令キャッシュを通じて使用可能であっても、または特定の入力デバイス418またはワイヤレスインターフェース428を通じてアクセス可能であってもよい。たとえば、入力デバイス418またはワイヤレスインターフェース428はまた、プロセッサローカルデータキャッシュのようなプロセッサにローカルに直接関連付けられているか、またはシステムメモリ408からアクセス可能なメモリデバイスに存在するデータにアクセスすることもできる。本明細書において開示される様々な実施形態に関連して説明される方法は、ハードウェアにおいて、プロセッサによって実行される1つまたは複数のプログラムを有するソフトウェアモジュールにおいて、またはこの2つの組合せにおいて直接具現されてもよい。20

ソフトウェアモジュールは、ランダムアクセスメモリ(RAM)、ダイナミックランダムアクセスメモリ(DRAM)、同期ダイナミックランダムアクセスメモリ(SDRAM)、フラッシュメモリ、読み取り専用メモリ(ROM)、消去可能プログラマブル読み取り専用メモリ(EPROM)、電気的消去可能プログラマブル読み取り専用メモリ EEPROM)、ハードディスク、取外し可能ディスク、コンパクトディスク(CD)-ROM、デジタルビデオディスク(DVD)、または当技術分野において知られている任意の他の形態の非一時的ストレージ媒体に存在することができる。非一時的ストレージ媒体は、プロセッサがストレージ媒体から情報を読み取り、ストレージ媒体に情報を書き込むことができるように、プロセッサに結合されてもよい。代替策において、ストレージ媒体は、プロセッサに組込み型であってもよい。30

#### 【0042】

本発明は、プロセッサシステムにおいて使用される例示的な実施形態のコンテキストにおいて開示されるが、上記の説明および以下に続く特許請求の範囲と一致する、多岐にわたる実施態様が、当業者によって採用され得ることが理解されるであろう。たとえば、固定機能の実装態様はまた、本発明の様々な実施形態を使用することもできる。40

#### 【符号の説明】

#### 【0043】

- 100 マイクロプロセッササブシステム

- 102 デバイスシステムコア

- 104 サブシステムコントローラ

- 106 共有デバイス

- 108 アプリケーションプロセッササブシステム(APPS)

- 110 モデムサブシステム(MSS)

- 112 システムバス

- 114 共有デバイスコントローラ

|     |                        |    |

|-----|------------------------|----|

| 120 | 共有HCl                  |    |

| 122 | デュアルホスト共有バッファ          |    |

| 124 | セマフォー                  |    |

| 126 | シャドーレジスタAPPS           |    |

| 128 | シャドーレジスタMSM            |    |

| 130 | ショートタイマー               |    |

| 132 | ロングタイマー                |    |

| 208 | フラッシュデバイス              |    |

| 406 | プロセッサ複合体               | 10 |

| 408 | システムメモリ                |    |

| 410 | ソフトウェア(たとえば、命令)        |    |

| 414 | 電源                     |    |

| 418 | 入力デバイス                 |    |

| 420 | ディスプレイ                 |    |

| 422 | カメラ(ビデオ)               |    |

| 424 | スピーカ                   |    |

| 426 | マイクロフォン                |    |

| 428 | ワイヤレスインターフェース          |    |

| 430 | ディスプレイコントローラ           |    |

| 432 | カーラインインターフェース          | 20 |

| 434 | コーデック                  |    |

| 436 | アプリケーションサブシステムコアプロセッサ1 |    |

| 438 | アプリケーションサブシステムコアプロセッサ2 |    |

| 440 | モデムサブシステム(MSS)         |    |

| 444 | フラッシュコントローラ            |    |

| 446 | フラッシュデバイス              |    |

| 448 | マルチメディアサブシステム          |    |

| 449 | L1 I&Dキャッシュ            |    |

| 450 | L1 I&Dキャッシュ            |    |

| 451 | メモリコントローラ              | 30 |

【 図 1 】

【図2A】

【 図 2 B 】

【 図 3 】

【図4】

---

フロントページの続き

(72)発明者 アミット・ジル

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5・クアルコム・インコーポレイテッド

(72)発明者 エレツ・ツィードン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5・クアルコム・インコーポレイテッド

(72)発明者 ヤンル・リ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5・クアルコム・インコーポレイテッド

(72)発明者 アゼディン・トウズニ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5・クアルコム・インコーポレイテッド

審査官 井上 宏一

(56)参考文献 特開2009-277007(JP,A)

特開2011-232956(JP,A)

特開2001-216284(JP,A)

特開2002-189705(JP,A)

米国特許出願公開第2010/0095089(US,A1)

(58)調査した分野(Int.Cl., DB名)

G06F 13/14

G06F 13/12

G06F 3/06

G06F 3/08

G06F 9/52