(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第6454065号 (P6454065)

(45) 発行日 平成31年1月16日(2019.1.16)

(24) 登録日 平成30年12月21日 (2018.12.21)

(51) Int. Cl. FL

HO3K 5/08 (2006, 01) нозк 5/08

> 請求項の数 4 (全 19 頁)

(21) 出願番号 特願2013-233408 (P2013-233408) (22) 出願日 平成25年11月11日 (2013.11.11) (65) 公開番号 特開2015-95727 (P2015-95727A)

(43) 公開日 平成27年5月18日 (2015.5.18) 平成28年9月16日 (2016.9.16) 審查請求日

||(73)特許権者 715010864

エイブリック株式会社

Т

千葉県千葉市美浜区中瀬一丁目8番地

||(72)発明者 有山 稔

千葉県千葉市美浜区中瀬1丁目8番地 セ

イコーインスツル株式会社内

審査官 白井 亮

最終頁に続く

# (54) 【発明の名称】比較回路

## (57)【特許請求の範囲】

## 【請求項1】

前置審查

第一容量及び第二容量と、

第一入力電圧が前記第一容量を介して入力される第一入力端子と、第二入力電圧が前記 第二容量を介して入力される第二入力端子と、出力端子とを備えた比較器と、

基準電圧が入力される基準電圧端子と、

一端が前記第一入力端子に接続され、サンプルフェーズでオンして前記第一入力端子の 電圧を前記出力端子の電圧にする第一スイッチと、

一端が前記第二入力端子に接続され、前記サンプルフェーズでオンして前記第二入力端 子の電圧を前記基準電圧にする第二スイッチと、

前記第一スイッチの他端と前記第二スイッチの他端の間に設けられ、比較フェーズでオ ンして前記第一スイッチの他端と前記第二スイッチの他端の電圧を等しくする第三スイッ チと、

を備えたことを特徴とする比較回路。

## 【請求項2】

前記第二スイッチの他端と前記基準電圧端子の間に設けられ、サンプルフェーズでオン する第四スイッチを備え、

前記第三スイッチは、前記第一スイッチの他端と前記第二スイッチの他端の電圧を前記 出力端子の電圧にする、

ことを特徴とする請求項1に記載の比較回路。

#### 【請求項3】

前記第一スイッチの他端と前記出力端子の間に設けられ、サンプルフェーズでオンする 第四スイッチを備え、

前記第三スイッチは、前記第一スイッチの他端と前記第二スイッチの他端の電圧を前記基準電圧にする、

ことを特徴とする請求項1に記載の比較回路。

#### 【請求項4】

前記比較器は、

前記第一入力端子と前記第二入力端子に接続された第一増幅器と、

第三入力端子と第四入力端子に接続された第二増幅器と、

前記第一増幅器の出力端子と前記第二増幅器の出力端子に接続され、出力端子が前記比較器の出力端子に接続された加算器と、を備え、

前記第三入力端子に第二の基準電圧が入力され、前記第四入力端子に第三の基準電圧が入力された、

ことを特徴とする請求項1から3のいずれかに記載の比較回路。

#### 【発明の詳細な説明】

## 【技術分野】

### [0001]

本発明は、電圧の大小を比較する比較回路に関し、特に高温時の回路素子のリーク電流やノイズによる影響を抑え、高精度な電圧比較を行う回路に関する。

#### 【背景技術】

#### [0002]

電子回路一般において、複数の電圧を比較し、その大小を判定する回路として比較回路が用いられている(例えば、特許文献 1 参照)。

#### [0003]

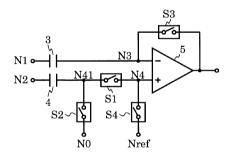

従来の比較回路の一例の回路図を図りに示す。従来の比較回路は、比較器(コンパレータ)を用い、2つの入力電圧の差分の電圧が所定の電圧よりも大きいかまたは小さいかを判定している。この比較において、比較器が持つオフセット電圧(入力オフセット電圧)やノイズが誤差の要因となり、精度が低下するという問題がある。上記の入力オフセット電圧は、一例としては比較器の入力回路を構成する素子の特性ばらつきにより発生する。また上記のノイズは、回路を構成する単体トランジスタが持つフリッカ雑音や、単体トランジスタや抵抗素子が持つ熱雑音により発生する。

#### [0004]

前述の比較器が持つオフセット電圧の影響を低減するため、図9に示した比較回路は以下の構成となっている。比較器5と、比較器5の反転入力端子N3と出力端子との間に接続されるスイッチS3と、比較器5の反転入力端子N3と入力端子N1との間に接続される容量3と、比較器5の非反転入力端子N4と比較電圧入力端子Nrefとの間に接続されるスイッチS1と、入力端子N2と接続点N41との間に接続される容量4と、接続点N41と比較電圧入力端子N0との間に接続されるスイッチS2とを有する。ここで、比較電圧入力端子N0の電圧をV0、比較電圧入力端子Nrefの電圧をVref、入力端子N1の電圧をV1、入力端子N2の電圧をV2、比較器5の反転入力端子N3の電圧をV3、比較器5の非反転入力端子N4の電圧をV2、比較器5の出力端子の電圧をVoとする。また、比較器5の入力オフセット電圧をVoaとする。

#### [0005]

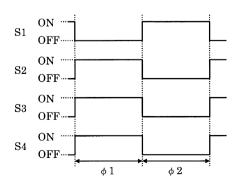

図9の比較回路は、図10に示すようにスイッチS1~S4が制御されて動作する。動作の一周期は、サンプルフェーズ 1と比較フェーズ 2からなる。サンプルフェーズ 1では、スイッチS1がオフ、スイッチS2~S4がオンする。比較フェーズ 2では、スイッチS1がオン、スイッチS2~S4がオフする。また、各接続点や端子の電圧の末尾に付する 1または 2は、それぞれサンプルフェーズ 1または比較フェーズ 2に

10

20

30

40

おける電圧を表すものとする。

[0006]

サンプルフェーズ 1では、スイッチS1がオフ、スイッチS2がオンし、容量4にVC4 1 = V0 - V2 1が充電される。スイッチS4がオンしているのでV4 1 = Vrefとなる。比較器5は、スイッチS3がオンしているので、ボルテージフォロワ回路として動作し、入力オフセット電圧Voaを有するためVo 1 = V4 1 + Voaとなる。また、スイッチS3がオンしているのでV3 1 = Vo 1であり、すなわちV3 1 = Vref + Voaとなり、容量3に VC3 1 = V3 1 - V1 1 = Vref + Voa - V1 1が充電される。サンプルフェーズ 1での容量3と容量4に蓄積される電荷をまとめると次のようになる。

10

[0007]

$VC3 1 = Vref + Voa - V1 1 \cdot \cdot \cdot (43)$

$V C 4 1 = V 0 - V 2 1 \cdot \cdot \cdot (4 4)$

比較フェーズ 2 では、スイッチ S 2 ~ S 4 がオフし、スイッチ S 1 がオンする。容量 3 には式 ( 4 3 ) で示す V C 3 1 が保持されているので、電圧 V 3 は次のようになる

0

[0008]

$V 3 2 = V 1 2 + V C 3 1 \cdots (45)$

一方、容量 4 には式(44)で示す VC4 1 が保持されているので、電圧 V4 は次のようになる。

20

[0009]

$V 4 2 = V 2 2 + V C 4 1 \cdot \cdot \cdot (46)$

最終的に、式(45)で表される電圧V3と式(46)で表される電圧V4が比較器5において比較され、出力端子からハイレベルまたはローレベルが出力される。

比較器 5 の入力オフセット電圧 V o a を考慮すると、比較器 5 で比較される電圧は次のようになる。

[0010]

$(V4 2 + Voa) - V3 2 = {(V2 2 - V1 2) - (V2 1 - V1 1)} - (Vref - V0) \cdot \cdot \cdot (47)$

式(47)には、比較器5の入力オフセット電圧Voaが含まれておらず、オフセット電圧が相殺されていることが示されている。従って、比較フェーズ 2 で比較器5において、入力電圧成分{(V2 2 - V1 2) - (V2 1 - V1 1)}と基準電圧成分(Vref - V0)が比較される。以上により、誤差要因となる比較器のオフセット電圧成

分の影響が取り除かれ、誤差の少ない高精度な出力の比較回路を実現することができる。

【先行技術文献】

【特許文献】

[0011]

【特許文献1】特開2008-236737号公報

【発明の概要】

【発明が解決しようとする課題】

40

30

[0012]

しかしながら、自動車等に搭載される回路においては、近年、より高温での動作が求められ、また更なる高精度化が求められる傾向にある。前述したような従来の比較回路では、比較フェーズにおいて、高温時に顕著になるスイッチのオフリーク電流により容量に電荷が注入され、比較の結果に誤差を生じるという課題があった。具体的には、図9の比較回路においては、比較フェーズ 2にて、容量3にはスイッチS3のみのリーク電流が流れ込むのに対して、容量4にはスイッチS2およびS4のリーク電流が流れ込むため、比較器の入力における電圧の変動量が反転入力端子N3側と非反転入力端子N4側で異なり、比較結果に誤差を生じていた。一般的に、スイッチを構成するトランジスタのリーク電流は高温になるに従い増加するため、誤差は高温になるほど顕著になる。また、トランジ

スタがMOSトランジスタの場合、チャネル間のリーク電流はドレイン・ソース間の電圧 差に依存するため、オフしているスイッチにおいて容量に接続されていない側の電圧によ り、スイッチのリーク電流の流れる向きや大きさが異なり、比較結果に誤差を生じていた

## [0013]

また、従来の比較回路では、スイッチを構成するトランジスタ素子がオンからオフに遷 移する際に発生するノイズ成分(例えば、チャネルチャージインジェクションやクロック フィードスルー)の影響についても、各容量へのスイッチの接続が非対称であるために、 スイッチのノイズ成分による比較器の入力における電圧の変動量が反転入力端子N3側と 非反転入力端子N4側で異なっており、誤差発生の要因であるという課題があった。

[0014]

本発明はこのような点に鑑みてなされたものであり、簡便な回路構成で比較器の入力オ フセット電圧の影響を取り除くと共に、スイッチのオフリーク電流やノイズ成分による誤 差の影響を抑制し、高精度な比較判定結果を得ることが可能な比較回路を提供することを 目的とする。

【課題を解決するための手段】

[0015]

従来のこのような問題点を解決するために、本発明の比較回路は以下のような構成とし た。

[0016]

第一入力電圧が第一容量を介して入力される第一入力端子と、第二入力電圧が第二容量 を介して入力される第二入力端子と、出力端子とを備えた比較器と、一端が第一入力端子 に接続され、サンプルフェーズでオンして第一入力端子の電圧を出力端子の電圧にする第 ースイッチと、一端が第二入力端子に接続され、サンプルフェーズでオンして第二入力端 子の電圧を基準電圧にする第二スイッチと、比較フェーズでオンして第一スイッチの他端 と第二スイッチの他端の電圧を等しくする第三スイッチを備えた比較回路。

## 【発明の効果】

[0017]

本発明の比較回路によれば、スイッチと容量と比較器を有効的に活用することにより、 比較器において発生するオフセット成分やスイッチのオフリーク電流成分やスイッチのノ イズ成分によって生じる誤差を簡便な回路構成で取り除き、広範な温度領域にわたって高 精度な比較を行うことが可能となる。

【図面の簡単な説明】

[0018]

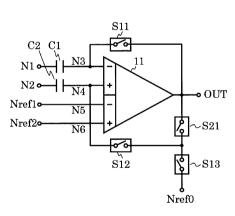

- 【図1】第1の実施形態の比較回路の回路図である。

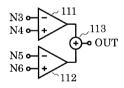

- 【図2】第1の実施形態の各スイッチの動作を示す図である。

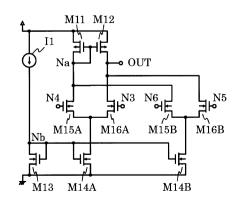

- 【図3】本発明の比較回路に用いる比較器の一例を示す回路図である。

- 【図4】本発明の比較回路に用いる比較器の他の例を示す回路図である。

- 【図5】第2の実施形態の比較回路の回路図である。

- 【図6】第2の実施形態の各スイッチの動作を示す図である。

- 【図7】第3の実施形態の比較回路の回路図である。

- 【図8】第4の実施形態の比較回路の回路図である。

- 【図9】従来の比較回路の回路図である。

- 【図10】従来の比較回路の各スイッチの動作を示す図である。

【発明を実施するための形態】

[0019]

本発明の比較回路は、半導体回路における高精度な比較回路として幅広く利用されうる 。以下、本発明の比較回路について図面を参照して説明する。

< 第 1 の実施形態 >

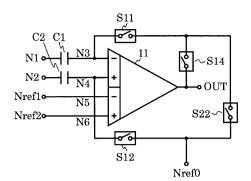

図1は、第1の実施形態の比較回路の回路図である。第1の実施形態の比較回路は、比

10

20

30

40

較器11と、容量C1、C2と、スイッチS11、S12、S13、S21を備える。 【0020】

比較器11は、4つの入力端子と1つの出力端子とを有し、詳しくは、第一差動入力対 の第一入力端子N3と、第一差動入力対の第二入力端子N4と、第二差動入力対の第一入 力端子N5と、第二差動入力対の第二入力端子N6と出力端子OUTを有する。容量C1 は、2つの端子を有し、一方の端子は比較器11の第一差動入力対の第一入力端子N3に 接続され、他方の端子は入力端子N1に接続される。容量C2は、2つの端子を有し、一 方の端子は比較器11の第一差動入力対の第二入力端子N4に接続され、他方の端子は入 力端子N2に接続される。スイッチS11は、2つの端子を有し、一方の端子は比較器1 1の第一差動入力対の第一入力端子N3に接続され、他方の端子は比較器11の出力端子 OUTに接続される。スイッチS12は、2つの端子を有し、一方の端子は比較器11の 第一差動入力対の第二入力端子N4に接続される。スイッチS13は、2つの端子を有し 、一方の端子は基準電圧入力端子Nref0に接続される。スイッチS21は、2つの端 子を有し、一方の端子は比較器11の出力端子OUTに接続される。スイッチS12、S 13、S21のそれぞれの他方の端子は共通に接続される。スイッチS11、S12、S 13、S21は、スイッチ制御信号(回路図には図示しない)により、オンまたはオフが 制御される。比較器11の第二差動入力対の第一入力端子N5には第一基準電圧入力端子 Nref1が接続され、比較器11の第二差動入力対の第二入力端子N6には第二基準電 圧入力端子Nref2が接続される。

[0021]

次に、第1の実施形態の比較回路の動作を説明する。

まず、比較器11の動作を説明する。比較器11は、一対の入力電圧の差を増幅した値と、もう一対の入力電圧の差を増幅した値と、の和を出力する機能を有する。この増幅機能を概念的に表した図を図3に示す。

[0022]

図3は、比較器11の機能を表す概念図である。

図3の比較器11は、差動増幅器111、112と加算器113を有し、以下のように接続されて構成される。比較器11の第一差動入力対の第一入力端子N3が差動増幅器111の反転入力端子に接続され、第一差動入力対の第二入力端子N4が差動増幅器111の非反転入力端子に接続され、第二差動入力対の第一入力端子N5が差動増幅器112の反転入力端子に接続され、第二差動入力対の第二入力端子N6が差動増幅器112の非反転入力端子に接続される。差動増幅器111の出力と差動増幅器112の出力は加算器113の入力にそれぞれ接続され、加算器113の出力が比較器11の出力端子OUTに接続される。

[0023]

比較器11は以上のように接続されており、次のように動作する。

差動増幅器 1 1 1 は 2 つの入力端子 N 3 と N 4 の電圧の差を増幅して加算器 1 1 3 に入力し、差動増幅器 1 1 2 は 2 つの入力端子 N 5 と N 6 の電圧の差を増幅して加算器 1 1 3 に入力する。加算器 1 1 3 は差動増幅器 1 1 1 と差動増幅器 1 1 2 の出力の和を出力する。この増幅機能を式で表すと、

$V \circ = A \ 1 \times (V \ 4 - V \ 3) + A \ 2 \times (V \ 6 - V \ 5) \cdot \cdot \cdot (1)$

となる。ここに A 1 および A 2 はそれぞれ差動増幅器 1 1 1 および 1 1 2 の増幅率である。また、各端子 N 3 ~ N 6 および O U T の電圧をそれぞれ V 3 ~ V 6 および V o とした。

[0024]

図1の比較回路では、図3に示した比較器11の第一差動入力対の第一入力端子N3と出力端子OUTはスイッチS11の両端に接続されている。スイッチS11がオンしている状態では、VoとV3は概等しい電圧になるから、Voは式(1)から次のように表される。

Vo=A1/(1+A1) x V 4 + A 2 / (1 + A 1) x ( V 6 - V 5 ) ・・・(2) 説明の便宜上、増幅率 A 1 および A 2 は十分に大きいとすると、次式を得る。 10

20

30

40

#### [0025]

$Vo = V4 + (A2/A1) \times (V6 - V5) \cdot \cdot \cdot (3)$

すなわちスイッチS11がオンしている状態では、比較器11の出力端子OUTと、第一差動入力対の第一入力端子N3すなわち差動比較器111の反転入力端子が電気的に接続されており、フィードバックループが形成され、出力電圧Voは入力電圧V4に追従するだけでなく、入力V6とV5の電圧の差分を増幅率A2とA1の比で増幅した電圧との和をも出力する、一種のボルテージフォロワのような動作をする。

## [0026]

一方、スイッチS11がオフしている状態では比較器11にフィードバックループが形成されないことから、比較器11は比較器(コンパレータ)そのものとして動作する。式(1)から

Vo=A1×{(V4-V3)+(A2/A1)×(V6-V5)}・・・(4)であるから、すなわち比較器11は、スイッチS11がオフしている状態では、V4とV3の差分の電圧と、V6とV5の差分を増幅率A2とA1の比で増幅した電圧と、の和の電圧を、十分に大きな増幅率A1で増幅して、出力端子OUTからハイレベル信号(一般に正の電源電圧レベル)またはローレベル信号(一般に負の電源電圧レベル、またはGNDレベル)を出力する比較動作を行う。

### [0027]

ここで、比較器 1 1 の入力オフセット電圧を第一差動入力対の第二入力端子 N 4 において V o a 1、第二差動入力対の第二入力端子 N 6 において V o a 2 とすると、入力オフセット電圧を考慮した比較器 1 1 の動作を表す式は、スイッチ S 1 1 がオンしているときとオフしているときで、それぞれ式(3)、式(4)から次のようになる。

#### [0028]

スイッチS11がオンしているとき

$Vo = (V4 + Voa1) + (A2/A1) \times (V6 + Voa2 - V5) \cdot \cdot \cdot (5)$  スイッチS11がオフしているとき

V o = A 1 x { ( V 4 + V o a 1 - V 3 ) + ( A 2 / A 1 ) x ( V 6 + V o a 2 - V 5 ) } · · · ( 6 )

以上が図3に示した比較器11の動作説明である。

## [0029]

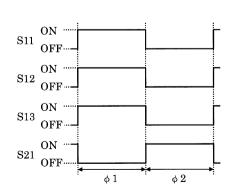

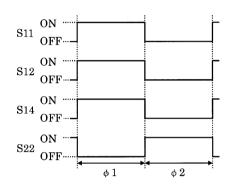

図2は各スイッチの動作を示す図である。

比較動作の一周期は、サンプルフェーズ 1 と比較フェーズ 2 の 2 つのフェーズからなる。スイッチ S 1 1 、 S 1 2 、 S 1 3 、 S 2 1 は、図 2 のスイッチ制御信号により制御される。スイッチ S 1 1 、 S 1 2 、 S 1 3 は、サンプルフェーズ 1 でオンし、比較フェーズ 2 でオフする。また、スイッチ S 2 1 は、サンプルフェーズ 1 でオフし、比較フェーズ 2 でオンする。

## [0030]

図1の比較回路の各フェーズでの動作の概略を説明する。サンプルフェーズ 1は、入力端子N1の電圧V1、入力端子N2の電圧V2、第一基準電圧入力端子Nref1の電圧Vref1、第二基準電圧入力端子Nref2の電圧Vref2と、比較器11のオフセット電圧とを容量C1およびC2に記憶するフェーズである。比較フェーズ 2は、サンプルフェーズ 1における比較器11のオフセット成分を相殺しつつ、入力端子N1と入力端子N2の間の電圧差と、第一基準電圧Vref1と第二基準電圧Vref2の間の電圧差の比較を行うフェーズである。

#### [0031]

以下に、サンプルフェーズ 1と比較フェーズ 2について、詳細に説明する。

サンプルフェーズ 1では、スイッチS11、S12、S13はオンしており、スイッチS21はオフする。従って、比較器11の各入力端子には、次の電圧が供給される。比較器11の第一差動入力対の第一入力端子N3には出力端子OUTの電圧Voが与えられ、第一差動入力対の第二入力端子N4には基準電圧Vref0が与えられ、第二差動入力

10

20

30

40

対の第一入力端子N5には第一基準電圧Vref1が与えられ、第二差動入力対の第二入 力端子N6には第二基準電圧Vref2が与えられる。スイッチS11がオンしていると き、比較器11は式(5)で示したように動作するから、第一差動入力対の第一入力端子 N3の電圧は次のように表される。

## [0032]

V3 1 = Vref0 1 + Voa1 1 + (A2/A1) x (Vref2 1 + Vo a 2 1 - V r e f 1 1)  $\cdot \cdot \cdot (7)$

各電圧の末尾の 1は、サンプルフェーズ 1における電圧である事を示す。これ以降 では、他の電圧、また比較フェーズ 2についても同様に表記する。

#### [0033]

容量 С 1 には電圧 V 3 と電圧 V 1 の差分 V С 1 1 が充電される

$VC1 1 = V3 1 - V1 1 \cdot \cdot \cdot (8)$

上式に式(7)を代入すると、次式を得る。

## [0034]

$VC1 1 = -V1 1 + Vref0 1 + Voa1 1 + (A2/A1) \times (Vr$ ef2 1+Voa2 1-Vref1 1) · · · (9)

一方、容量 C 2 には電圧 V 4 と電圧 V 2 の差分 V C 2 1 が充電される  $VC2 1 = V4 1 - V2 1 \cdot \cdot \cdot (10)$

第一差動入力対の第二入力端子N4には基準電圧Vref0が与えられているから、式( 10)から次式を得る。

#### [0035]

$VC2 1 = Vref0 1 - V2 1 \cdot \cdot \cdot (11)$

一方、比較フェーズ 2では、スイッチS11、S12、S13はオフしており、スイ ッチS21はオンする。スイッチS11がオフし、容量C1には VC1 1が充電され ているので、電圧V3は電圧V1と VC1 1で定まり、次式で表される。

$V 3 2 = V 1 2 + V C 1 1 \cdots (12)$

上式に容量 C 1 に充電された VC1 1 を表す式(9)を代入すると次のようになる。

## [0036]

V3 2 = V1 2 - V1 1 + Vref0 1 + Voa1 1 + (A2/A1) x ( Vref2 1 + Voa 2 1 - Vref1 1) · · · (13)

また、スイッチS12がオフし、容量C2には VC2 1が充電されているので、電圧 V4は電圧V2と VC2 1で定まり、次式で表される。

$2 = V 2 2 + V C 2 1 \cdot \cdot \cdot (14)$

上式に容量C2に充電された VC2 1を表す式(11)を代入すると次のようになる

## [0037]

$V4 2 = V2 2 - V2 1 + Vref0 1 \cdot \cdot \cdot (15)$

また、スイッチS11がオフしているとき、比較器11は式(6)で示したように動作す るから、比較器11の出力端子OUTの電圧Voは次のように表される。

## [0038]

2 = A 1 x { ( V 4 2 + V o a 1 2 - V 3 2 ) + ( A 2 / A 1 ) x ( V r 2 + Voa 2 2 - Vref 1 2) } · · · (16)

上式に式(13)で表されるV3 2、式(15)で表されるV4 2を代入すると次式 を得る。

## [0039]

2 = A 1 x [ { ( V 2 2 - V 1 2 ) - ( V 2 1 - V 1 1 ) + ( V o a 1 2 - Voa 1 1) } - (A 2 / A 1) x { (Vref 2 1 - Vref 1 1) - ( 2 - V r e f 1 2) - (Voa2 2 - Voa2 1) } ] • • • (17 )

式(17)を分かりやすくするために、入力端子N1および入力端子N2から供給され

10

20

30

40

10

20

30

40

50

る電圧成分を Vinとおき、第一基準電圧入力端子Nref1および第二基準電圧入力端子Nref2から供給される電圧成分を Vrefとおくと、式(17)は次のように表せる。

## [0040]

Vin=(V2 2-V1 2)-(V2 1-V1 1)・・・(19)

Vref=(Vref2 1-Vref1 1)-(Vref2 2-Vref1

2)・・・(20)

である。

#### [0041]

ここで、比較器 1 1 の入力オフセット電圧 V o a 1 、 V o a 2 は、厳密には経時変化や温度変化(温度ドリフト)を示すため、一定の値ではないが、サンプルフェーズ 1 および比較フェーズ 2 の時間が、入力オフセット電圧の経時変化や温度変化に対して十分に短い時間であれば、入力オフセット電圧の値は、サンプルフェーズ 1 と比較フェーズ 2 で概等しい値であるとみなす事ができる。従って、式(18)において、 V o a 1 2 ・ V o a 1 1、 V o a 2 2 ・ V o a 2 1 は、ほぼゼロの値となり、比較フェーズ 2 の比較器 1 1 における比較動作時に、比較器 1 1 のオフセット成分は取り除かれる。よって式(18)は次のように表せる。

#### [0042]

Vo  $2 = A 1 \times \{ Vin - (A 2 / A 1) \times Vref \} \cdot \cdot \cdot (2 1)$ 従って、入力端子N1および入力端子N2から供給される電圧成分 Vinと、第一基準 電圧入力端子Nref1および第二基準電圧入力端子Nref2から供給される電圧成分 Vrefを比較した結果が、十分に大きな増幅率A1で増幅され、最終的に比較器11 の出力端子OUTからハイレベル信号またはローレベル信号として出力されることになる 。例として、 Vinを決める入力端子N1および入力端子N2に印加する電圧を挙げる と、例えば、V1 2=V2 1=V1′、V1 1=V2 2=V2′となるように外 部から電圧を入力した場合には、式(19)から Vin=2x(V2'-V1')とな り、V1′とV2′の差を2倍した電圧が入力電圧成分として比較器11に入力されるこ とになる。また一方で、 Vrefを決める第一基準電圧Vref1および第二基準電圧 Vref2は、例えば、Vref2 1=Vref1 1=Vref2 2=Vref2 '、Vref1 2=Vref1'となるように外部から基準電圧を印加した場合には、 式(20)から Vref=Vref1'-Vref2'となり、Vref1'とVre f 2 'の差の電圧が比較器11に基準電圧成分として入力されることになる。間便のため 、A1=A2となるように差動増幅器111、112を設計したとすると、この例の場合 には式(21)は、

Vo 2 = A1 x { 2 x ( V 2 ' - V 1 ' ) - ( V r e f 1 ' - V r e f 2 ' ) } · · ( 2 2 )

となり、入力電圧成分 2 x ( V 2 ' - V 1 ') と基準電圧成分 ( V r e f 1 ' - V r e f 2 ') の比較結果が得られることになる。

#### [0043]

10

20

30

40

50

2 の電圧が、比較器 1 1 の同相入力電圧範囲外の電圧であったとしても、本実施形態の比較回路磁気センサ装置では、基準電圧入力端子 N r e f 0 の電圧を比較器 1 1 の同相入力電圧範囲内になるように選択することで、高精度な比較が可能であるという利点を有する。別の表現をすると、比較器 1 1 に要求される同相入力電圧範囲を著しく緩和できるという利点を有しているといえる。

## [0044]

次に、スイッチS13とS21による効果を説明する。比較フェーズ 2 では、スイッチS13がオフし、スイッチS21がオンすることで、スイッチS12の他方の端子の電圧を比較器11の出力端子OUTの電圧Voに等しくするように動作させている。従って、オフ状態にあるスイッチS11とS12のそれぞれの他方の端子の電圧は比較器11の出力端子OUTの電圧Voに等しくなる。

#### [0045]

仮に、スイッチS13が比較フェーズ 2でサンプルフェーズ 1と同じくオンのまま であり、スイッチS21が比較フェーズ 2 でサンプルフェーズ 1 と同じくオフのまま である場合、言い換えるとスイッチS13とS21が存在せず、スイッチS12の他方の 端子が基準電圧入力端子Nref0に直接接続されている場合、を考える。この場合には 、比較フェーズ 2 では、スイッチS11の他方の電圧は比較器11の出力端子OUTの 電圧Voに等しくなり、比較結果に応じてハイレベル信号(一般に正の電源電圧レベル) またはローレベル信号(一般に負の電源電圧レベル、またはGNDレベル)の電圧になる 。一方、スイッチS12の他方の電圧は基準電圧入力端子Nref0の電圧に等しくなる 。前述のとおり、基準電圧入力端子Nref0の電圧は、比較器11の同相入力電圧範囲 内になるように選択することが好ましく、一般的には正の電源電圧レベルと負の電源電圧 レベル(またはGNDレベル)の間の電圧、例としては、中間の電圧に設定される。従っ て、比較フェーズ 2では、スイッチS11の他方の端子の電圧とスイッチS21の他方 の端子の電圧は、非常に差の大きい電圧となる。一方、スイッチS11とS12の一方の 端子の電圧は、それぞれ式(13)および式(15)で表される電圧であり、必ずしも等 しい電圧ではないが、いずれも基準電圧入力端子Nref0のサンプルフェーズ 1にお ける電圧を基準とした電圧となり、特に比較器11の比較判定結果が切り替わる境界条件 近傍において、概ね近い電圧となる(少なくとも、片方が正または負の電源電圧になり、 もう片方が正と負の電源電圧の中間電圧となるほどの電圧差は生じない)。以上から、オ フ状態にあるスイッチS11の両端子間の電圧差と、スイッチS12の両端子間の電圧差 は大きく異なることになる。オフ状態のスイッチの理想的な特性としては、両端子間の電 圧差によらず端子間に電流が流れないことが挙げられるが、実際の回路においては、スイ ッチの端子間にはリーク電流が流れ、また両端子間の電圧差によりリーク電流が変化する ,このためにリーク電流を低減させるスイッチ回路の構成が多々挙げられているが、リー ク電流はゼロにはならず有限の値をとる。スイッチS12においては、一方の端子の電圧 は式(15)で表されるVref0 1を基準とした電圧であり、他方の端子の電圧はV 1の電圧であるため、リーク電流が流れるものの、比較的小さいリーク電流と なる。スイッチS11においては、一方の端子の電圧は式(13)で表されるVref0 1を基準とした電圧であり、他方の端子の電圧は比較器11の出力端子OUTの電圧V oに等しく、ハイレベル信号(一般に正の電源電圧レベル)またはローレベル信号(一般 に負の電源電圧レベル、またはGNDレベル)の電圧であるため、スイッチS12のリー ク電流よりも大きい電流リーク電流が流れることになる。従って、容量C1と容量C2に 流れ込むリーク電流が異なり、第一差動入力対の第一入力端子N3の電圧の変動量と、第 一差動入力対の第二入力端子N4の電圧の変動量が異なり、結果として比較結果に誤差を 生じる要因となる。一般に、リーク電流は高温であるほど増加する傾向にあるため、高温 になるほど比較回路の誤差は増大する。

## [0046]

上述した仮の場合に対して、本実施形態においては、比較フェーズ 2 では、スイッチS 1 3 がオフし、スイッチS 2 1 がオンすることで、スイッチS 1 2 の他方の端子の電圧

10

20

30

40

50

を比較器11の出力端子OUTの電圧Voに等しくするように制御しているため、スイッチS11の両端子間の電圧差と、スイッチS12の両端子間の電圧差と、の差が小さくなるように改善され、リーク電流の差が小さくなり、容量C1と容量C2に流れ込むリーク電流の差を小さくするよう改善され、結果として比較結果に生じる誤差を小さくすることが可能となる。従って、スイッチS13とS21により、スイッチのリーク電流によって発生する誤差の影響を抑制し、高精度な比較判定結果を得ることが可能となる。

#### [0047]

また、スイッチの非理想成分としては、上述のリーク電流の他に、スイッチを構成するトランジスタ素子がオンからオフに遷移する際に発生するノイズ成分、例えば、チャネルチャージインジェクションやクロックフィードスルーが挙げられる。本実施形態においては、容量C1の一方の端子と比較器11の第一差動入力対の第一入力端子N3の接続点、にそれぞれ対称となるようにスイッチS11,S12を接続しているため、スイッチのノイズ成分によって発生する電荷は各接続点にほぼ等しく注入され、第一差動入力対の第一入力端子N3の電圧と第一差動入力対の第二入力端子N4の電圧はそれぞれ変動するものの、その変動量はほぼ等しくなるように動作する。従って、スイッチがオン状態からオフ状態に遷移する際に発生するノイズ成分による誤差の影響を抑制し、高精度な比較判定結果を得ることが可能となる。

## [0048]

ここで、図1の磁気センサ装置を構成する要素である比較器11の回路構成の一例について示しておく。図3の概念図で示した比較器11の機能は、さらに具体的には、例えば図4に示すような回路構成で実現することができる。

#### [0049]

図4は、比較器11の回路構成の一例である。

比 較 器 11は、 定 電 流 回 路 I 1と、 NMOSトランジス 夕 M 1 3、 M 1 4 A、 M 1 4 B 、M15A、M16A、M15B、M16Bと、PMOSトランジスタM11、M12を 有し、次のように接続されて構成される。定電流回路I1の一方は電源電圧端子VDDに 接続され、もう一方はNMOSトランジスタM13のドレインおよびゲートに接続される 。この接続点をNbとする。NbはNMOSトランジスタM14AのゲートとNMOSト ランジスタM14Bのゲートに接続される。NMOSトランジスタM13、M14A、M 14Bのソースはグランド端子VSSに接続される。NMOSトランジスタM15AとM 16AのソースはM14Aのドレインに接続され、NMOSトランジスタM15BとM1 6 BのソースはM14Bのドレインに接続される。NMOSトランジスタM15AとM1 5BのドレインはPMOSトランジスタM11のドレインに接続される。この接続点をN aとする。NMOSトランジスタM16AとM16BのドレインはPMOSトランジスタ M12のドレインに接続される。この接続点は、比較器11の出力端子OUTに接続され る。PMOSトランジスタM11とM12のゲートは接続点Naに接続され、ソースは電 源電圧端子VDDに接続される。NMOSトランジスタM15A、M16Aのゲートは、 それぞれ第一差動入力対の第二入力端子N4、第一入力端子N3に接続され、NMOSト ランジスタM15B、M16Bのゲートは、それぞれ第二差動入力対の第二入力端子N6 、第一入力端子N5に接続される。

#### [0050]

比較器11は以上のように接続されており、次のように動作する。

定電流回路I1は、定電流を発生しNMOSトランジスタM13に供給する。NMOSトランジスタM13、M14A、M14Bはカレントミラー回路を構成しており、NMOSトランジスタM14A、M14Bのドレイン ソース間には、M13のドレイン ソース間に流れる電流に基づいた電流が流れる。NMOSトランジスタM14A、M15A、M16A、PMOSトランジスタM11、M12からなる5つのトランジスタは、差動増幅器を構成しており、第一差動入力対を構成するNMOSトランジスタM15A、M16Aのゲート電圧の差、すなわち、第一差動入力対の第二入力端子N4と第一差動入力対の

第一入力端子N3の電圧差を増幅して、出力端子OUTに出力するように動作する。この増幅率をA1とする。ここで、カレントミラー回路構成および差動増幅器構成の動作にいいては、CMOSアナログ回路の文献等にて詳細に記載されており、ここでは誤細ならいの文献等にて詳細に記載されており、ここでは説細ならいのでは割愛する。また、NMOSトランジスタM14B、M15B、M16B、PMOSトランジスタM115B、M16Bのゲート電圧のままを増幅しており、第二差動入力対を構成するNMOSトランジスタM15B、M16Bのゲート電圧のののの第二入力端子N6と第二差動入力対の第一入力端子N5と第二差動入力対の第一入力端子N5と第二差動入力対の第一次とする。この増幅率をA2とするる、なわち、第一差動入力対を構成するNMOSトランジスタM15Bのドレインと第二差動入力対を構成するNMOSトランジスタM16Bのドレインに接続され、第一差動入力対を構成するNMOSトランジスタM16Bのドレインと第二差動入力対を構成するNMOSトランジスタM16Bのドレインと第二差動入力対を構成するNMOSトランジスタM16Bのドレインと第二差動入力対を構成するNMOSトランジスタM16Bのドレインと第二差動入力対を構成するNMOSトランジスタM16Bのドレインと第二差動入力対を構成するNMOSトランジスタM16Bのドレインと第二差動入力対を構成するNMOSトランジスタM16Bのドレインと第二差動入力対を構成するNMOSトランジスタM16Bのドレインに接続されていることにあり、この接続点Naおよび出力端子OUTにて、第一差動入力対と第二差動入力対の特に表すと、

Vo = A1 x (V4 - V3) + A2 x (V6 - V5)・・・(23) となる。すなわち、式(1)と同等の動作を行う。

## [0051]

以上により、第1の実施形態の比較回路の動作を説明し、簡便な回路構成で比較器の入力オフセット電圧の影響を取り除くと共に、スイッチのオフリーク電流やノイズ成分による誤差の影響を抑制し、高精度な比較判定結果を得ることが可能であることを示した。

#### [0052]

本説明においては、比較器11についての具体的な回路構成およびスイッチ制御のタイミングチャートを示したが、本説明内で記載した動作を行う構成であれば、必ずしもこの構成に制限されるものではない。例えば、図2では、サンプルフェーズ 1から比較フェーズ 2への遷移時、または逆の遷移時にスイッチのオンまたはオフが切り替わるタイミングが同時になるように記載しているが、スイッチS11がオフしてからスイッチS12をオフし、さらにその後にS13をオフ、S21をオンするようにタイミングをずらして制御しても良い。比較器11の過渡応答特性が良い場合や、比較器11の第一差動入力対の第一入力端子N3と第一差動入力対の第二入力端子N4の間の寄生容量が無視できないの第一入力端子N3に伝播し、次十一差動入力対の第二入力端子N3に伝播し、容量C1に充電する電圧に無視できない誤差を発生させる場合がある。このような場合には、スイッチS11がオフするタイミングを遅らせると、より好適である。

#### [0053]

また本説明においては、入力端子N1と入力端子N2に印加される入力電圧の一例、および、第一基準電圧入力端子Nref1と第二基準電圧入力端子Nref2に印加する電圧の一例を挙げたが、必ずしも、この例に制限されるものではない。例えば、従来技術に示されるように、センサ素子に印加される物理量の強度に応じて論理出力を行う信号検出回路に本実施形態の比較回路を適用する場合、入力電圧成分の例は次のようになる。

#### [0054]

V 1 1 = V c m 1 + V s i g 1 + V o f f 1

V 2 1 = V c m 1 - V s i g 1 - V o f f 1

V1 2 = V cm 2 - V sig 2 + V off 2

V2 2 = V cm 2 + V sig 2 - V o f f 2

ここで、Vcmはセンサ素子の信号電圧の同相電圧成分、Vsigはセンサ素子の信号電圧成分、Voffはセンサ素子のオフセット電圧成分(誤差要因)である。以上の各入力電圧を式(19)に代入すると、

$Vin = 2 \times (Vsig 2 + Vsig 1) - 2 \times (Voff 2 - Voff 1)$

10

20

30

40

#### $\cdot \cdot \cdot (24)$

となる。センサ素子のオフセット電圧成分はサンプルフェーズ 1と比較フェーズ 2で概等しい値を示すので相殺される。従って、センサ素子の信号電圧成分のみが入力電圧成分として比較器11に入力されることになる。このような入力電圧成分の場合においても、本発明の趣旨である、比較器の入力オフセット電圧の影響を取り除くと共に、スイッチのオフリーク電流やノイズ成分による誤差の影響を抑制し、高精度な比較判定結果を得るという点から逸脱するものではない。

## [0055]

## <第2の実施形態>

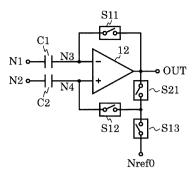

図5は、第2の実施形態の比較回路の回路図である。図1に示した第1の実施形態との違いは、スイッチS13とS21を削除し、スイッチS14とS22を追加した点である。追加した要素は次のように構成され接続される。また削除した要素により次の接続が第1の実施形態と異なる。

## [0056]

スイッチS12の他方の端子は、基準電圧入力端子Nref0に接続される。スイッチS14は、2つの端子を有し、一方の端子は比較器11の出力端子OUTに接続され、他方の端子はスイッチS11の他方の端子に接続される。スイッチS22は、2つの端子を有し、一方の端子はスイッチS11の他方の端子に接続され、他方の端子はスイッチS12の他方の端子に接続される。この他の接続および構成については、第1の実施形態と同じである。

#### [0057]

次に、第2の実施形態の比較回路の動作を説明する。

スイッチ S 1 4 、 S 2 2 は、スイッチ S 1 1 、 S 1 2 と同様にスイッチ制御信号(回路図には図示しない)により、オンまたはオフが制御される。

#### [0058]

図 6 は、第 2 の実施形態の比較回路における各スイッチの動作を示す図である。スイッチ S 1 1 、 S 1 2 、 S 1 4 は、サンプルフェーズ 1 でオンし、比較フェーズ 2 でオフ するように制御される。スイッチ S 2 2 は、サンプルフェーズ 1 でオフし、比較フェーズ 2 でオンするように制御される。

## [0059]

サンプルフェーズ 1では、スイッチS11、S12、S14はオンしており、スイッチS22はオフする。従って、比較器11の各入力端子には、次の電圧が供給される。比較器11の第一差動入力対の第一入力端子N3には出力端子OUTの電圧Voが与えられ、第一差動入力対の第二入力端子N4には基準電圧入力端子Nref0の電圧が与えられ、第二差動入力対の第一入力端子N5には第一基準電圧入力端子Nref1の電圧が与えられ、第二差動入力対の第二入力端子N6には第二基準電圧入力端子Nref2の電圧が与えられる。すなわち、第1の実施形態の比較回路と同様であるから、動作についても第1の実施形態の比較回路と同様になる。

## [0060]

比較フェーズ 2では、スイッチS11、S12、S14はオフしており、スイッチS22はオンする。スイッチS11とS12がオフしているので、電圧V3は電圧V1とVC1 1で定まり、また、電圧V4は電圧V2と VC2 1で定まる。すなわち、第1の実施形態の比較回路と同様であるから、動作についても第1の実施形態の比較回路と同様になる。

#### [0061]

比較フェーズ 2ではスイッチS14がオフし、スイッチS22がオンしているので、スイッチS11とS12の他方の端子の電圧は、基準電圧入力端子Nref0の電圧に等しくなる。第1の実施形態の比較回路の場合には、スイッチS11とS12の他方の端子の電圧は、比較器11の出力端子OUTの電圧Voと等しいので、この点が第1の実施形態と異なる。本実施形態においては、比較フェーズ 2では、スイッチS14がオフし、

10

20

30

40

スイッチS22がオンすることで、スイッチS12の一方の端子の電圧は式(15)で表されるVref0 1を基準とした電圧となり、他方の端子の電圧はVref0 1の電圧となるため、リーク電流が流れるものの、比較的小さいリーク電流となる。スイッチS11については、一方の端子の電圧は式(13)で表されるVref0 1を基準とした電圧となり、他方の端子の電圧はVref0 1の電圧となるため、スイッチS12と同様にリーク電流が流れるものの、比較的小さいリーク電流となる。従って、スイッチS11の両端子間の電圧差と、スイッチS12の両端子間の電圧差と、の差が小さくなるように改善され、第1の実施形態の比較回路の場合と同様に、結果として比較判定結果に生じる誤差を小さくすることが可能となる。従って、スイッチS14とS22により、スイッチのリーク電流によって発生する誤差の影響を抑制し高精度な比較判定結果を得ることが可能となる。

[0062]

また、スイッチの非理想成分としては、上述のリーク電流の他に、スイッチを構成するトランジスタ素子がオンからオフに遷移する際に発生するノイズ成分、例えば、チャルチャージインジェクションやクロックフィードスルーが挙げられる。本実施形態においては、容量 C 1 の一方の端子と比較器 1 1 の第一差動入力対の第一入力端子 N 3 の接続点、 にる量 C 2 の一方の端子と比較器 1 1 の第一差動入力対の第二入力端子 N 4 の接続点、にそれぞれ対称となるようにスイッチ S 1 1 、 S 1 2 を接続しているため、スイッチのノイズ成分によって発生する電荷は各接続点にほぼ等しく注入され、第一差動入力対の第一入入端子 N 3 の電圧と第一差動入力対の第二入力端子 N 4 の電圧はそれぞれ変動するものの、その変動量はほぼ等しくなるように動作する。従って、スイッチがオン状態からオフ状態に遷移する際に発生するノイズ成分による誤差の影響を抑制し高精度な比較判定結果を得ることが可能となる点におても、第 1 の実施形態の場合と同様である。

[0063]

以上により、第2の実施形態の比較回路の動作を説明し、第1の実施形態の場合と同様に簡便な回路構成で比較器の入力オフセット電圧の影響を取り除くと共に、スイッチのオフリーク電流やノイズ成分による誤差の影響を抑制し、高精度な比較判定結果を得ることが可能であることを示した。

[0064]

<第3の実施形態>

図7は、第3の実施形態の比較回路の回路図である。図1に示した第1の実施形態との違いは、比較器11を比較器12で置き換えた点、比較器11の入力に接続されていた第一基準電圧入力端子Nref1と第二基準電圧入力端子Nref2を削除した点である。置き換えた要素は次のように構成され接続される。

[0065]

比較器12は、2つの入力端子と1つの出力端子とを有し、詳しくは、差動入力対の第一入力端子N3と、差動入力対の第二入力端子N4と、出力端子OUTを有する。比較器12の差動入力対の第一入力端子N3は容量C1の一方の端子に接続され、差動入力対の第二入力端子N4は容量C2の一方の端子に接続され、出力端子OUTはスイッチS11の他方の端子に接続される。この他の接続および構成については、第1の実施形態と同じである。スイッチS11、S12、S13、S21は、第1の実施形態の比較回路と同様にスイッチ制御信号(回路図には図示しない)により、オンまたはオフが制御される。

[0066]

次に、第3の実施形態の比較回路の動作を説明する。

まず、比較器12の動作を説明する。比較器12は、入力電圧の差を増幅した値を出力する機能を有する。この増幅機能を式で表すと、

Vo=A3x(V4-V3)・・・(25) となる。ここにA3は比較器12の増幅率である。 10

20

30

40

#### [0067]

図7の比較回路では、差動入力対の第一入力端子N3と出力端子OUTはスイッチS11の両端に接続されている。スイッチS11がオンしている状態では、VoとV3は概等しい電圧になるから、Voは式(25)から次のように表される。

$Vo = A3 / (1 + A3) \times V4 \cdot \cdot \cdot (26)$

説明の便宜上、増幅率A3は十分に大きいとすると、次式を得る。

[0068]

$V \circ = V \cdot \cdot \cdot \cdot (27)$

すなわちスイッチS11がオンしている状態では、比較器12の出力端子OUTと、差動入力対の第一入力端子N3が電気的に接続されており、フィードバックループが形成され、出力電圧Voは入力電圧V4に追従し、ボルテージフォロワ動作をする。

[0069]

一方、スイッチS11がオフしている状態では比較器12にフィードバックループが形成されないことから、比較器11は比較器(コンパレータ)そのものとして動作する。このときの動作は式(24)と等しく、

$V \circ = A \ 3 \times (V \ 4 - V \ 3) \cdot \cdot \cdot (2 \ 8)$

であるから、すなわち比較器 1 2 は、スイッチ S 1 1 がオフしている状態では、 V 4 と V 3 の差分の電圧を十分に大きな増幅率 A 3 で増幅して、出力端子 O U T からハイレベル信号(一般に正の電源電圧レベル)またはローレベル信号(一般に負の電源電圧レベル、または G N D レベル)を出力する比較動作を行う。

[0070]

ここで、比較器 1 2 の入力オフセット電圧を差動入力対の第二入力端子 N 4 において V o a 3 とすると、入力オフセット電圧を考慮した比較器 1 2 の動作を表す式は、スイッチ S 1 1 がオンしているときとオフしているときで、それぞれ式(2 7)、式(2 8)から次のようになる。

[0071]

スイッチS11がオンしているとき

$Vo = V4 + Voa 3 \cdot \cdot \cdot (29)$

スイッチS11がオフしているとき

$V \circ = A \ 3 \times \{ (V \ 4 + V \circ a \ 3 - V \ 3) \} \cdot \cdot \cdot (3 \ 0)$

以上が図7に示した比較器12の動作説明である。

[0072]

スイッチの動作についても第1の実施形態と同様に制御され、図2の各スイッチの動作を示す図に従って動作される。各フェーズでの図7の比較回路の動作の概略を説明すると、サンプルフェーズ 1は、入力端子N1、入力端子N2の各端子電圧と、比較器12のオフセット電圧とを容量C1およびC2に記憶するフェーズであり、比較フェーズ 2は、サンプルフェーズ 1における比較器12のオフセット成分を相殺しつつ、入力端子N1と入力端子N2の間の電圧差の比較を行うフェーズである。以下に詳細を説明する。

[0073]

サンプルフェーズ 1では、スイッチS11、S12、S13はオンしており、スイッチS21はオフする。従って、比較器12の差動入力対の第一入力端子N3には出力端子OUTの電圧Voが与えられ、差動入力対の第二入力端子N4には基準電圧入力端子Nref0の電圧が与えられる。スイッチS11がオンしているとき、比較器12は式(29)で示したように動作するから、差動入力対の第一入力端子N3の電圧は次のように表される。

[0074]

$V3 1 = V r e f 0 1 + V o a 3 1 \cdot \cdot \cdot (31)$

容量 C 1 には電圧 V 3 と電圧 V 1 の差分 V C 1 1 が充電される

$VC1 1 = V3 1 - V1 1 \cdot \cdot \cdot (32)$

上式に式(31)を代入すると、次式を得る。

20

10

30

40

[0075]

VC1 1 = - V1 1 + Vref0 1 + Voa3 1 · · · (33)

一方、容量C2には電圧V4と電圧V2の差分 VC2 1が充電される

$VC2 1 = V4 1 - V2 1 \cdot \cdot \cdot (34)$

差動入力対の第二入力端子N4には基準電圧入力端子Nref0の電圧が与えられているから、式(34)から次式を得る。

[0076]

$VC2 1 = Vref0 1 - V2 1 \cdot \cdot \cdot (35)$

一方、比較フェーズ 2 では、スイッチS 1 1、S 1 2、 S 1 3 はオフしており、スイッチS 2 1 はオンする。スイッチS 1 1 がオフし、容量 C 1 には V C 1 1 が充電されているので、電圧 V 3 は電圧 V 1 と V C 1 1 で定まり、次式で表される。

10

[0077]

$V 3 2 = V 1 2 + V C 1 1 \cdot \cdot \cdot (36)$

上式に容量 С 1 に充電された VС 1 1 を表す式(33)を代入すると次のようになる

0

V3 2 = V1 2 - V1 1 + Vref0 1 + Voa3 1 · · · · (37)また、スイッチS12がオフし、容量C2には VC2 1 が充電されているので、電圧V4は電圧V2と VC2 1で定まり、次式で表される。

[0078]

$V 4 2 = V 2 2 + V C 2 1 \cdot \cdot \cdot (38)$

20

$V4 2 = V2 2 + Vref0 1 - V2 1 \cdots (39)$

また、スイッチS11がオフしているとき、比較器12は式(30)で示したように動作するから、比較器12の出力端子OUTの電圧Voは次のように表される。

[0079]

Vo 2 = A3 x { (V4 2 + Voa3 2 - V3 2 ) } ・・・(40)

上式に式(37)で表されるV3 2、式(39)で表されるV4 2を代入すると次式を得る。

[0080]

30

50

$Vo 2 = A3 \times \{ (V2 2 - V2 1) - (V1 2 - V1 1) + (Voa 3 2 - Voa 3 1) \} \cdot \cdot \cdot (41)$

ここで、比較器 1 2 の入力オフセット電圧 V o a 3 は、第 1 の実施形態と同様に、サンプルフェーズ 1 および比較フェーズ 2 の時間が、入力オフセット電圧の経時変化や温度変化に対して十分に短い時間であれば、サンプルフェーズ 1 と比較フェーズ 2 で概等しい値であるとみなす事ができる。従って、式(4 1)において、 V o a 3 2 - V o a 3 1 は、ほぼゼロの値となり、比較フェーズ 2 の比較器 1 2 における比較動作時に、比較器 1 2 のオフセット成分は取り除かれる。よって式(4 1)は次のように表せる。

[0081]

$V \circ 2 = A 3 \times \{ (V 2 2 - V 2 1) - (V 1 2 - V 1 1) \} \cdot \cdot \cdot (4 2 40)$

[0082]

式(42)には、Vref0の項は含まれていない。このことは、第1の実施形態と同様に、入力端子N1および入力端子N2の電圧が比較器12の同相入力電圧範囲外であっても、基準電圧入力端子Nref0の電圧を比較器12の同相入力電圧範囲内になるように選択することで、高精度な比較が可能であるという利点を有する。別の表現をすると、比較器12に要求される同相入力電圧範囲を著しく緩和できるという利点を有しているといえる。

[0083]

また、スイッチS13とS21は、比較フェーズ 2 では、スイッチS13がオフし、

スイッチS21がオンすることで、スイッチS11およびスイッチS12の他方の端子の電圧を比較器11の出力端子OUTの電圧Voに等しくするように動作させている。従って、第1の実施形態と同様に、スイッチS13とS21により、スイッチのリーク電流によって発生する誤差の影響を抑制し高精度な比較判定結果を得ることが可能となる。

## [0084]

また、スイッチS11、S12の非理想成分についても、第1の実施形態と同様に、スイッチがオン状態からオフ状態に遷移する際に発生するノイズ成分による誤差の影響を抑制し高精度な比較判定結果を得ることが可能となる。

## [0085]

以上により、第3の実施形態の比較回路の動作を説明し、簡便な回路構成で比較器の入力オフセット電圧の影響を取り除くと共に、スイッチのオフリーク電流やノイズ成分による誤差の影響を抑制し、高精度な比較判定結果を得ることが可能であることを示した。

#### [0086]

## <第4の実施形態>

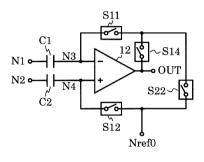

図8は、第4の実施形態の比較回路の回路図である。図7に示した第3の実施形態との違いは、スイッチS13とS21を削除し、スイッチS14とS22を追加した点である。追加した要素は次のように構成され接続される。また削除した要素により次の接続が第3の実施形態と異なる。

## [0087]

スイッチS12の他方の端子は、基準電圧入力端子Nref0に接続される。スイッチS14は、2つの端子を有し、一方の端子は比較器12の出力端子OUTに接続され、他方の端子はスイッチS11の他方の端子に接続される。スイッチS22は、2つの端子を有し、一方の端子はスイッチS11の他方の端子に接続され、他方の端子はスイッチS12の他方の端子に接続される。この他の接続および構成については、第3の実施形態と同じである。

## [0088]

また、本実施形態と図5に示した第2の実施形態との違いは、図7に示した第3の実施 形態と図1に示した第1の実施形態との違いと同様に、比較器11を比較器12で置き換 えた点、比較器11の入力に接続されていた第一基準電圧入力端子Nref1と第二基準 電圧入力端子Nref2を削除した点である。

### [0089]

次に、第4の実施形態の比較回路の動作を説明する。

スイッチS14、S22は、スイッチS11、S12と同様にスイッチ制御信号(回路図には図示しない)により、オンまたはオフが制御される。スイッチの動作については第 2の実施形態と同様に制御され、図6の各スイッチの動作を示す図に従って動作する。

## [0090]

サンプルフェーズ 1では、スイッチS11、S12、S14はオンしており、スイッチS22はオフする。従って、比較器12の各入力端子には、次の電圧が供給される。比較器12の差動入力対の第一入力端子N3には出力端子OUTの電圧Voが与えられ、差動入力対の第二入力端子N4には基準電圧入力端子Nref0の電圧が与えられる。すなわち、第3の実施形態の比較回路と同様であるから、動作についても第3の実施形態の比較回路と同様になる。

## [0091]

比較フェーズ 2では、スイッチS11、S12、S14はオフしており、スイッチS22はオンする。スイッチS11とS12がオフしているので、電圧V3は電圧V1とVC1 1で定まり、また、電圧V4は電圧V2と VC2 1で定まる。すなわち、第3の実施形態の比較回路と同様であるから、動作についても第3の実施形態の比較回路と同様になり、比較器12のオフセット成分を取り除き、比較器12に要求される同相入力電圧範囲を著しく緩和できるという利点を有した、高精度な比較判定結果を得ることが可能な比較回路となる。

10

20

30

## [0092]

また、比較フェーズ 2 ではスイッチS14がオフし、スイッチS22がオンしているので、スイッチS11とS12の他方の端子の電圧は、基準電圧入力端子Nref0の電圧に等しくなる。すなわち、第2の実施形態の比較回路と同様であるから、スイッチS11とS12のリーク電流による誤差の影響を抑制し、高精度な比較判定結果を得ることが可能な比較回路となる。

#### [0093]

以上により、第4の実施形態の比較回路の動作を説明し、第3実施形態の場合と同様に 簡便な回路構成で比較器の入力オフセット電圧の影響を取り除くと共に、スイッチのオフ リーク電流やノイズ成分による誤差の影響を抑制し、高精度な比較判定結果を得ることが 可能であることを示した。

#### [0094]

本説明においては、説明のために具体的な例を示して説明したが、必ずしもこの構成やスイッチ制御タイミングに制限されるものではない。これは第 1 ,第 2 ,第 3 の実施形態の比較回路の場合についても同様である。

#### 【符号の説明】

## [0095]

11、12 比較器

1 1 1 、 1 1 2 差動増幅器

1 1 3 加算器

I 1 定電流回路

【図1】

【図3】

【図4】

## 【図2】

10

# 【図5】

# 【図7】

# 【図6】

【図8】

# 【図9】

【図10】

## フロントページの続き

(56)参考文献 国際公開第2013/161571(WO,A1)

特開2010-226234(JP,A) 特開2008-236737(JP,A)

国際公開第2006/085503(WO,A1)

(58)調査した分野(Int.CI., DB名)

H 0 3 K 5 / 0 8