(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3871883号

(P3871883)

(45) 発行日 平成19年1月24日(2007.1.24)

(24) 登録日 平成18年10月27日(2006.10.27)

(51) Int.C1.

F 1

GO 6 F 9/38 (2006.01)

GO 6 F 9/38 330 B

請求項の数 23 (全 23 頁)

(21) 出願番号 特願2000-571339 (P2000-571339)

(86) (22) 出願日 平成11年4月2日 (1999.4.2)

(65) 公表番号 特表2002-525741 (P2002-525741A)

(43) 公表日 平成14年8月13日 (2002.8.13)

(86) 國際出願番号 PCT/US1999/007266

(87) 國際公開番号 WO2000/017745

(87) 國際公開日 平成12年3月30日 (2000.3.30)

審査請求日 平成18年2月7日 (2006.2.7)

(31) 優先権主張番号 09/157,721

(32) 優先日 平成10年9月21日 (1998.9.21)

(33) 優先権主張国 米国(US)

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVI

CES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベイル、ビイ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・プレイス、メイル・ストップ

・68 (番地なし)

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

最終頁に続く

(54) 【発明の名称】間接分岐ターゲットを計算するための方法

## (57) 【特許請求の範囲】

## 【請求項 1】

マイクロプロセッサであって、

命令バイトを受取り記憶するよう構成される命令キャッシュを含み、命令キャッシュは、

フェッチアドレスを受取り、それに応答してフェッチアドレスに対応する命令バイトの

1つ以上を出力するよう構成され、さらに、

複数個の選択子ビットを記憶するよう構成される分岐選択子アレイを含み、各選択子ビ

ットは、命令キャッシュに記憶される特定の命令バイトに対応し、分岐選択子アレイは、

フェッチアドレスを受取り、それに応答して予測される次のフェッチアドレスのためのソ

ースを示す1つ以上の対応する選択子ビットを出力するよう構成され、さらに、

フェッチアドレスをフェッチブロックサイズと合計して次のシーケンシャルなアドレス

を生成するよう構成されるシーケンシャルアドレス加算器と、

命令キャッシュに記憶される間接分岐命令のための予測される分岐ターゲットアドレス

を記憶するよう構成される間接分岐ターゲットキャッシュとを含み、間接分岐ターゲット

キャッシュは、フェッチアドレスを受取り、対応する間接分岐アドレスを出力するよう構

成され、さらに、

フェッチアドレスを、命令キャッシュによって出力される命令バイトからのオフセット

と合計して直接分岐アドレスを計算するよう構成される直接分岐加算器と、

分岐選択子アレイから1つ以上の対応する選択子ビットを受取るよう構成されるマルチ

プレクサとを含み、マルチプレクサは、選択子ビットに基づいて次のシーケンシャルなア

10

20

ドレス、直接分岐アドレス、または間接分岐アドレスのいずれかを選択するよう構成される、マイクロプロセッサ。

**【請求項 2】**

シーケンシャルアドレス加算器、直接分岐加算器、および間接分岐ターゲットキャッシュは各々、次のシーケンシャルなアドレス、直接分岐アドレス、および間接分岐アドレスをそれぞれ並列に計算するよう構成される、請求項1に記載のマイクロプロセッサ。

**【請求項 3】**

命令キャッシュによって出力される命令バイトからのオフセットを計算するよう構成されるオフセット計算論理ユニットをさらに含み、オフセット計算論理ユニットは、選択子ビットに基づいてオフセットを計算するよう構成される、請求項2に記載のマイクロプロセッサ。10

**【請求項 4】**

前記選択子ビットの2つが、前記命令キャッシュに記憶される各命令バイトに対応し、前記2バイトは、対応する命令が、(i) 分岐命令ノットティクン、(ii) 直接分岐命令ティクン、(iii) 間接分岐アドレステイクン、または(iv) リターンアドレステイクンであるかを示す、請求項3に記載のマイクロプロセッサ。

**【請求項 5】**

命令キャッシュは、命令バイトについてのプリデコード情報を記憶するよう構成され、プリデコード情報は、命令開始バイトを示すプリデコードビットを含む、請求項4に記載のマイクロプロセッサ。20

**【請求項 6】**

フェッチブロックサイズは定数である、請求項5に記載のマイクロプロセッサ。

**【請求項 7】**

前記マルチプレクサに結合され、コール命令のすぐ後に続く命令に対する命令ポインタを記憶するよう構成されるリターンスタックをさらに含む、請求項6に記載のマイクロプロセッサ。

**【請求項 8】**

前記分岐選択子アレイおよび前記間接分岐ターゲットキャッシュは各々、セットアソシエティブであり、もしあれば、どの記憶された選択子ビットおよび間接分岐ターゲットアドレスがフェッチアドレスに対応するかを決定するためにフェッチアドレスと比較されるタグを記憶するよう構成される、請求項2に記載のマイクロプロセッサ。30

**【請求項 9】**

マイクロプロセッサにおける予測される次のフェッチアドレスを生成するための方法であって、

現在のフェッチアドレスを受取るステップと、

命令キャッシュから現在のフェッチアドレスに対応するプリデコード情報および命令バイトを出力するステップと、

分岐選択子アレイから現在のフェッチアドレスに対応する選択子ビットを出力するステップと、

現在のフェッチアドレスをフェッチブロック定数に加算して次のシーケンシャルなアドレスを生成するステップと、40

間接分岐ターゲットアドレスキャッシュから記憶された間接分岐アドレスを出力するステップと、

リターンスタックから記憶されたリターンアドレスを出力するステップと、

オフセットを計算するステップと、

現在のフェッチアドレスをオフセットに合計して次の直接分岐アドレスを生成するステップと、

予測される次のフェッチアドレスとして、(i) 次のシーケンシャルなアドレス、(ii) 出力間接分岐アドレス、(iii) 出力リターンアドレス、および(iv) 次の直接分岐アドレスのいずれかを選択するステップとを含み、前記現在のフェッチアドレスを前記出力

するステップと、前記記憶された間接分岐アドレスを前記出力するステップと、前記記憶されたリターンアドレスを前記出力するステップと、現在のフェッチアドレスをオフセットに加算して次の直接分岐アドレスを生成する前記ステップとは、すべて並列に行なわれる、方法。

**【請求項 10】**

命令キャッシュに記憶される命令バイトについての選択子ビットを生成し記憶するステップと、

選択子ビットに基づいて予測される次のフェッチアドレスを選択するステップとをさらに含む、請求項9に記載の方法。

**【請求項 11】**

命令キャッシュに記憶される分岐命令の結果に基づいて選択子ビットを更新するステップをさらに含む、請求項10に記載の方法。

**【請求項 12】**

前記計算するステップは、

現在のフェッチアドレスから、ティクンであると予測される命令キャッシュからの第1の直接分岐命令への第1の特定のオフセットを決定するステップと、

第1の直接分岐命令内に即値データとして記憶される第2の特定のオフセットを検出するステップとを含み、

前記合計するステップは、現在のフェッチアドレスと第1のオフセットと第2のオフセットとを合計するステップを含む、請求項11に記載の方法。

**【請求項 13】**

タグを用いて選択子ビットにアクセスするステップをさらに含む、請求項12に記載の方法。

**【請求項 14】**

タグを用いて間接分岐ターゲットキャッシュにアクセスするステップをさらに含む、請求項13に記載の方法。

**【請求項 15】**

複数個のプリデコードビットを命令キャッシュに記憶するステップをさらに含み、プリデコードビットは、分岐命令の存在と、直接分岐命令に即値データとして記憶されるオフセットバイトの存在とを示す、請求項14に記載の方法。

**【請求項 16】**

コンピュータシステムであって、

命令バイトを記憶するよう構成される命令キャッシュ手段を含み、命令キャッシュ手段は、フェッチアドレスを受取り、それに応答してフェッチアドレスに対応する命令バイトの1つ以上を出力するよう構成され、さらに、

複数個の選択子ビットを記憶するよう構成される分岐選択子アレイ手段を含み、各選択子ビットは、命令キャッシュ手段に記憶される特定の命令バイトに対応し、分岐選択子アレイ手段は、フェッチアドレスを受取り、それに応答して予測される次のフェッチアドレスのためのソースを示す1つ以上の対応する選択子ビットを出力するよう構成され、さらに、

フェッチアドレスをフェッチブロックサイズと合計して次のシーケンシャルなアドレスを生成するよう構成されるシーケンシャルアドレス加算器手段と、

命令キャッシュ手段に記憶される間接分岐命令のための予測される分岐ターゲットアドレスを記憶するよう構成される間接分岐ターゲットキャッシュ手段とを含み、間接分岐ターゲットキャッシュ手段は、フェッチアドレスを受取り、対応する間接分岐アドレスを出力するよう構成され、さらに、

フェッチアドレスを、命令キャッシュ手段によって出力される命令バイトからのオフセットと合計して直接分岐アドレスを計算するよう構成される直接分岐加算器手段と、

分岐選択子アレイ手段から1つ以上の対応する選択子ビットを受取るよう構成される選択子手段とを含み、選択子手段は、選択子ビットに基づいて次のシーケンシャルなアドレ

10

20

30

40

50

ス、直接分岐アドレス、または間接分岐アドレスのいずれかを選択するよう構成される、コンピュータシステム。

**【請求項 17】**

シーケンシャルアドレス加算器手段、直接分岐加算器手段、および間接分岐ターゲットキャッシュ手段は各々、次のシーケンシャルなアドレス、直接分岐アドレス、および間接分岐アドレスをそれぞれ並列に計算するよう構成される、請求項16に記載のコンピュータシステム。

**【請求項 18】**

命令キャッシュ手段によって出力される命令バイトからのオフセットを計算するよう構成されるオフセット計算論理ユニットをさらに含み、オフセット計算論理ユニットは、選択子ビットに基づいてオフセットを計算するよう構成される、請求項17に記載のコンピュータシステム。10

**【請求項 19】**

前記選択子ビットの2つが、前記命令キャッシュ手段に記憶される各命令バイトに対応し、前記2バイトは、対応する命令が、(i) 分岐命令ノットティクン、(ii) 直接分岐命令ティクン、(iii) 間接分岐アドレスティクン、または(iv) リターンアドレスティクンであるかを示す、請求項18に記載のコンピュータシステム。

**【請求項 20】**

命令キャッシュ手段は、命令バイトについてのプリデコード情報を記憶するよう構成され、プリデコード情報は、命令開始バイトを示すプリデコードビットを含む、請求項19に記載のコンピュータシステム。20

**【請求項 21】**

フェッチブロックサイズは定数である、請求項20に記載のコンピュータシステム。

**【請求項 22】**

前記選択子手段に結合され、コール命令のすぐ後に続く命令に対する命令ポインタを記憶するよう構成されるリターンスタックをさらに含む、請求項21に記載のコンピュータシステム。

**【請求項 23】**

前記分岐選択子アレイ手段および前記間接分岐ターゲットキャッシュ手段は各々、セットアソシアティブであり、もしあれば、どの記憶された選択子ビットおよび間接分岐ターゲットアドレスがフェッチアドレスに対応するかを決定するためにフェッチアドレスと比較されるタグを記憶するよう構成される、請求項17に記載のコンピュータシステム。30

**【発明の詳細な説明】**

**【0001】**

**【発明の背景】**

**1. 技術分野**

この発明は、マイクロプロセッサにおける分岐ターゲットアドレスを記憶することに関する、特に、間接分岐ターゲットアドレスをキャッシュするための方法に関する。

**【0002】**

**2. 背景技術**

Sakamoto M et alによる、「スーパースカラプロセッサにおける分岐ペナルティを低減するためのマイクロアーキテクチャサポート」(“Microarchitecture Support for Reducing Branch Penalty in a Superscalar Processor”)と題する、1996年10月7日、オースティンにおける、コンピュータおよびプロセッサにおけるコンピュータ設計ICC VLSIに関する国際会議議事録(Proceedings of the International Conference on Computer Design. ICC VLSI in Computers and Processors)の第208から216頁は、動的分岐予測方式を実現し分岐履歴テーブルを有するマイクロプロセッサを開示する。

分岐ターゲットバッファが、先に実行されたティクンのジャンプ命令の結果を維持する。ジャンプ命令は、無条件ジャンプ命令、条件付き分岐命令および間接ジャンプ命令を含む。

40

50

Chang P-Y et alによる「間接ジャンプのためのターゲット予測」(“Target Prediction for Indirect Jumps”)と題する、コンピュータ・アーキテクチャ・ニュース(Computer Architecture News)、第25巻、第2号、1997年5月1日、第274頁から283頁は、間接ジャンプターゲットを予測するためにターゲットキャッシュを有する予測メカニズムを採用するスーパースカラプロセッサアーキテクチャを開示する。

WO 98/22873は、分岐予測を選択するために分岐選択子を採用する分岐予測メカニズムを開示する。分岐予測：シーケンシャル、リターンスタック、分岐予測1および分岐予測2のための分岐選択子が開示される。

今日のマイクロプロセッサ設計者は、絶えず製品の性能を向上させようとしている。マイクロプロセッサの性能を増大させる方法の1つは、それが動作するクロック周波数を増大させることである。しかしながら、クロック周波数が増大すると、マイクロプロセッサ内の各機能ユニットは、その指定されたタスクを行なうのにかかる時間が少なくなる。したがって、所与のクロック周波数で性能をさらに増大させるために他の方法が採用される。並列実行はそのような方法の1つである。並列実行は、各クロックサイクル中2つ以上の命令を実行することを伴う。並列実行を実現するために、多くのマイクロプロセッサは、各自が独立に並列して実行する構成された並列機能ユニットを用いる。10

#### 【0003】

所定のクロックサイクルでマイクロプロセッサの性能を増大させるための別の中間方法は、アウトオブオーダ実行である。たいていのプログラムは、特定の順序で実行する命令に依存する。しかしながら、プログラム内のある種の命令は、所望の機能がなお達成されるのであればプログラム順序を飛越して実行してもよい。アウトオブオーダで実行可能な命令は、そのまわりの命令に「依存」しない命令である。アウトオブオーダ実行を実現するマイクロプロセッサは、どの命令が他の命令に依存しないか、すなわちアウトオブオーダ実行が可能であるかを決定することができる。20

#### 【0004】

命令をアウトオブオーダで実行するには、いくつかの潜在的な欠点がある。特に、欠点の1つは、分岐命令の使用である。分岐命令は、条件付きジャンプ命令(JCC)、無条件ジャンプ命令(JMP)、リターン命令(RET)、およびサブルーチンコール命令(CALL)を含む。マイクロプロセッサは分岐命令後の命令が実行されるべきかどうかを決定できないことがあるので、これらの命令は、アウトオブオーダ実行を特に困難にする。30

#### 【0005】

所定のクロックサイクルでマイクロプロセッサの性能を増大させるのに使用される別の中間方法は、パイプライン化である。パイプライン化は、命令を実行するためにマイクロプロセッサが完了しなければならないタスクを分割することを伴う。タスクは、命令処理「パイプライン」を形成する複数のステージに分割される。ステージは、典型的には、一般的な連続処理形式になる。たとえば、第1のステージは、命令キャッシュに記憶された命令を「フェッチ」することかもしれないし、第2の段階は、命令を整列させ、それをデコードユニットに運んでデコードするか、または機能ユニットに運んで実行することかもしれない。パイプラインによって、命令の長いストリームが、より少ないクロックサイクルで実行されることが可能になる。パイプライン化されたマイクロプロセッサの利点は、一度に2つ以上の命令を処理する能力による。たとえば、第2の命令が命令キャッシュからフェッチされているのと同時に、第1の命令をデコードすることが可能である。40

#### 【0006】

しかしながら、アウトオブオーダ実行と同様、パイプライン化されたマイクロプロセッサにおいて、分岐命令の結果として性能が後退することがある。分岐命令はパイプラインを「ストール」させてしまうことがある、なぜなら、パイプライン処理は、分岐命令が実行されてしまう後までどの命令をフェッチするべきかを決定することができないからである。たとえば、条件付き分岐命令は、「テイクン」または「ノットテイクン」のいずれかである。分岐命令がノットテイクンであれば、プログラム順序で分岐命令のすぐ後に続く命50

令が実行される。代わりに、分岐命令がティクンであれば、分岐ターゲットアドレス相対するあるオフセットの異なった命令が実行される。パイプライン化されたマイクロプロセッサにおいては、分岐命令が実行を完了するまで、パイplineの初期ステージまたはフェッチステージにおいては、「ティクン」または「ノットティクン」に従ったターゲット命令をフェッチするかどうかを決定するのが困難である。したがって、マイクロプロセッサのパイpline処理は、初期ステージが分岐命令の結果を待つ間、ストールするか、または「バブル」（すなわち、パイplineを介して伝搬するアイドルクロックサイクル）を形成してしまうことがある。

#### 【0007】

パイplineにおいてストールまたはバブルを形成するのを防ぐために、多くのプロセッサは、分岐予測方式を実現する。分岐予測は、分岐命令が実際に実行を完了する前に、各分岐命令がティクンまたはノットティクンのいずれであるかを予測することを伴う。複数の異なったアルゴリズムが使用され得るが、多くは、特定の分岐命令のティクン／ノットティクン履歴を記憶することに依存する。たとえば、分岐命令が実行されティクンである場合、分岐予測ハードウェアは、その情報を記憶し、その結果、分岐命令が次にフェッチされるとき、パイplineは、その先行のパフォーマンスに基づいて命令がティクンであると自動的に推測するであろう。

#### 【0008】

分岐予測情報を記憶することは、ストールまたはバブルの形成の確立を低減するが、それは不利益も有する。不利益の1つは、分岐履歴情報を維持し更新するのに必要とされる複雑なハードウェアである。第2の不利益は、分岐履歴情報を記憶するのに必要とされるスペースである。マイクロプロセッサのダイスペースは、比較的乏しい資源であるので、分岐予測を記憶するために多量のスペースを用いることは不利益である。命令キャッシュのサイズが大きくなると、そこにより多くの分岐命令を記憶することが可能である。これは代わりに、分岐履歴予測情報の記憶空間をより多く必要とする。さらに、現在のソフトウェアは、高集中の分岐命令（たとえば、4命令ごとに1つ）を有する傾向がある。この高集中は、いくつの分岐が命令キャッシュに記憶されるかを正確に知ることができないということと合わせて、典型的には、分岐履歴情報を記憶するのに充てられるダイスペースの量を多くしてしまう。

#### 【0009】

これらの理由のために、分岐予測および履歴情報を効率的に記憶するための方法が所望される。特に、分岐履歴および予測情報をために必要とされる記憶空間の量を低減するための方法が特に望ましい。

#### 【0010】

##### 【発明の開示】

上述した課題は、この発明に従うマイクロプロセッサおよび分岐予測ユニットによって部分的に解決可能である。ある実施例では、分岐予測情報を効率的に記憶するよう構成されたマイクロプロセッサは、命令キャッシュおよび分岐予測ユニットを含み得る。分岐予測ユニットは、命令キャッシュに結合されてもよく、間接分岐ターゲットキャッシュ、直接分岐加算器、および分岐選択子アレイを含んでもよい。間接分岐ターゲットアレイは、間接分岐命令のための予測される分岐ターゲットアドレスを記憶するよう構成可能であり、直接分岐加算器は、直接分岐命令のための分岐ターゲットアドレスを計算するよう構成可能である。分岐選択子アレイは、間接分岐ターゲットキャッシュに結合されてもよく、複数個の選択子ビットを記憶するよう構成されてもよい。ある実施例では、選択子ビットは、命令キャッシュに記憶される特定の命令バイトに対応してもよい。選択子ビットは、特定の命令バイトと関連づけられる予測される次のフェッチアドレスのためのソースを示す。

#### 【0011】

別の実施例では、分岐予測ユニットは、直接分岐加算器、間接分岐ターゲットキャッシュ、または別のソースのいずれかから予測される次のフェッチアドレスを選択するよう構成

10

20

30

40

50

されるマルチプレクサをさらに含んでもよい。マルチプレクサは、現在のフェッチアドレスに対応する選択子ビットの値に基づいてその選択をするよう構成可能である。分岐予測ユニットは、マルチプレクサに結合されるシーケンシャルアドレス加算器も含んでもよい。シーケンシャルアドレス加算器は、現在のフェッチアドレスの一部と、命令キャッシュのフェッチブロックまたはキャッシュラインサイズに対応する定数とを合計することにより、予測される次のシーケンシャルなフェッチアドレスを生成するよう構成可能である。コール命令のすぐ後に続く命令に対応するフェッチアドレスを記憶するために、リターンスタックを利用してよい。

#### 【0012】

マイクロプロセッサにおいて予測される次のフェッチアドレスを記憶するための方法も企図される。ある実施例では、方法は、間接分岐命令のための予測される分岐ターゲットアドレスを間接分岐ターゲットキャッシュに記憶することを含み得る。加えて、特定の命令バイトに対応する選択子ビットが、分岐選択子アレイに記憶される。直接分岐命令については、予測される直接分岐ターゲットアドレスは、「オンザフライ」で計算される。一旦、予測される間接分岐アドレスが参照され、予測される直接分岐アドレスが計算されると、予測される次のフェッチアドレスは選択子ビットに基づいて選択される。

10

#### 【0013】

ある実施例では、プリデコードビットが、命令バイトとともに計算され記憶される。プリデコードビットは、予測される直接分岐ターゲットアドレスを計算するために使用されてもよく、これは、現在のフェッチアドレスからティクンであると予測される第1の直接分岐命令への第1のオフセットを決定し、直接分岐命令内に即値データとして記憶される第2のオフセットを検出し、次に現在のフェッチアドレスと第1のオフセットと第2のオフセットとを合計することによって計算されてもよい。

20

#### 【0014】

別の実施例では、予測されるシーケンシャルなアドレスは、現在のフェッチアドレスの一部を、命令キャッシュのキャッシュラインサイズまたはフェッチブロックサイズを表わす定数と合計することにより計算されてもよい。

#### 【0015】

分岐予測情報を効率的に記憶するよう構成されるコンピュータシステムも企図される。ある実施例では、コンピュータシステムは、上述したようなマイクロプロセッサとバスブリッジとを含む。バスブリッジは、高速C P Uバスを介してマイクロプロセッサに結合されてもよい。モデムなどの周辺装置がバスブリッジを介してマイクロプロセッサに結合されてもよい。別の実施例では、コンピュータシステムは、C P Uバスを介して第1のマイクロプロセッサに結合される第2のマイクロプロセッサを含んでもよい。

30

#### 【0016】

この発明の他の目的および利点は、添付の図面を参照し以下の詳細な説明を読むと明らかになるであろう。

#### 【0017】

この発明は、さまざまな変形および代替の形を許すが、その具体的な実施例が図に例として示され、ここに詳細に記載される。しかしながら、図面およびその詳細な説明は、この発明を開示される特定の形に制限するものではなく、反対に、その意図は、前掲の特許請求の範囲によって定義されるこの発明の精神および範囲内にあるすべての変形、等価および代替を含むものであることが理解される。

40

#### 【0018】

##### 【発明を実施する態様】

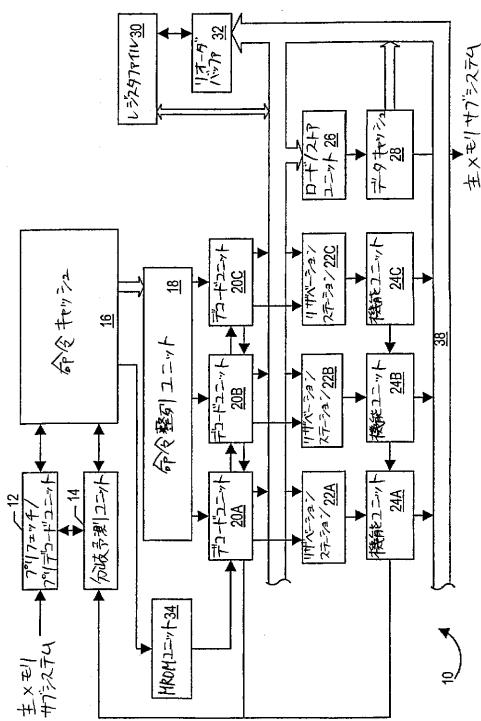

ここで図1を参照して、例のマイクロプロセッサ10のある実施例のブロック図が示される。マイクロプロセッサ10は、プリフェッチ/プリデコードユニット12と、分岐予測ユニット14と、命令キャッシュ16と、命令整列ユニット18と、複数個のデコードユニット20A～20Cと、複数個のリザベーションステーション22A～22Cと、複数個の機能ユニット24A～24Cと、ロード/ストアユニット26と、データキャッシュ

50

28と、レジスタファイル30と、リオーダバッファ32と、MROMユニット34とを含む。文字が後に付された特定の参照番号とともに参照される要素は、参照番号のみにより集合的に参照されることがある。たとえば、リザベーションステーション22A～22Cは、リザベーションステーション22として集合的に参照されることがある。

#### 【0019】

プリフェッチ／プリデコードユニット12は、主メモリサブシステム（図示せず）から命令を受けるよう結合され、命令キャッシュ16および分岐予測ユニット14にさらに結合される。同様に、分岐予測ユニット14は、命令キャッシュ16に結合される。分岐予測ユニット14は、命令整列ユニット18および機能ユニット24A～Cにも結合される。命令キャッシュ16はさらに、MROMユニット34および命令整列ユニット18に結合される。命令整列ユニット18は、ロード／ストアユニット26およびそれぞれのデコードユニット20A～Cに結合される。デコードユニット20A～Cはそれぞれリザベーションステーション22A～Cに結合され、これはさらにそれぞれの機能ユニット24A～Cに結合される。加えて、命令整列ユニット18およびリザベーションステーション22は、レジスタファイル30およびリオーダバッファ32に結合される。機能ユニット24は、ロード／ストアユニット26、レジスタファイル30、およびリオーダバッファ32にも結合される。データキャッシュ28は、ロード／ストアユニット26および主メモリサブシステムに結合される。最後に、MROMユニット34は、命令整列ユニット18に結合される。

#### 【0020】

命令は、プリフェッチ／プリデコードユニット12によって主メモリからプリフェッチされる。プリフェッチ／プリデコードユニット12は、可変長の命令を固定長の命令にプリデコードし、これは次に命令キャッシュ16に記憶される。命令は、プリフェッチ方式を用いることによって実際に必要とされるより前にプリフェッチおよびプリデコードされてもよい。さまざまなプリフェッチ方式がプリフェッチ／プリデコードユニット12によって採用され得る。

#### 【0021】

マイクロプロセッサ10は、条件付き分岐命令の後の命令を投機的にフェッチするために分岐予測を採用してもよい。分岐予測ユニット14は、分岐予測動作を行なうために含まれる。プリフェッチ／プリデコードユニット12は、特定の命令ラインがプリデコードされるとき初期分岐ターゲットを決定する。キャッシュラインに対応する分岐ターゲットへのその後の更新は、キャッシュライン内の命令の実行のために生じ得る。命令キャッシュ16は、分岐予測ユニット14にフェッチされる命令アドレスの表示を与える。これにより、分岐予測ユニット14は、分岐予測を形成するとき、どの分岐ターゲットアドレスを選択すべきかを決定することが可能になる。命令整列ユニット18および機能ユニット24は、分岐予測ユニット14に更新情報を与える。命令整列ユニット18は、分岐予測ユニット14によって予測されなかった分岐命令を検出するよう構成され得る。機能ユニット24は、分岐命令を実行し、予測された分岐方向が予測誤りでなかったかどうかを決定する。分岐方向は「テイクン」であるかもしれません、その場合にはその後の命令は分岐命令のターゲットアドレスからフェッチされる。反対に、分岐方向は「ノットテイクン」であるかもしれません、その場合にはその後の命令は、分岐命令に連続したメモリ場所からフェッチされる。予測誤りされた分岐命令が検出されると、予測誤りされた分岐の後の命令は、マイクロプロセッサ10のさまざまなユニットから廃棄される。さまざまな好適な分岐予測アルゴリズムが分岐予測ユニット14によって採用され得る。分岐予測ユニット14および命令キャッシュ16とのその相互作用のさらなる詳細を記載する前に、例示のマイクロプロセッサ10の一般的局面および可能な実施例を記載する。

#### 【0022】

命令キャッシュ16は、プリフェッチ／プリデコードユニット12から受取られる命令を記憶するために設けられる高速キャッシュメモリである。記憶された命令は次に、命令キャッシュ16からフェッチされ、命令整列ユニット18に転送される。ある実施例では、

10

20

30

40

50

命令キャッシュ 16 は、セットアソシティブ構造としてもよい。命令キャッシュ 16 は、アクセス時間を速めるためにウェイ予測方式をさらに採用してもよい。たとえば、命令の各ラインを特定するタグにアクセスし、タグをフェッチアドレスと比較してウェイを選択する代わりに、命令キャッシュ 16 は、アクセスされるウェイを予測してもよい。この態様では、ウェイは、アレイにアクセスするより前に投機的に選択される。ウェイ予測を用いると、命令キャッシュ 16 のアクセス時間は、ダイレクトマップドのキャッシュと同様になり得る。命令バイトが読み出された後、ベリファイのためにタグ比較が行なわれる。ウェイ予測が正しくなければ、正しい命令バイトがフェッチされ、正しくない命令バイト（処理パイプラインのさらに下にある）は廃棄される。なお、命令キャッシュ 16 は、フルアソシティブ構成、セットアソシティブ構成、またはダイレクトマップド構成で実現可能である。

#### 【 0023 】

M ROM ユニット 34 は、「高速経路」(fast-path) 命令のシーケンスを記憶するよう構成されるリードオンリーメモリである。高速経路命令は、デコーダ 20A～C および機能ユニット 24A～C によってデコードおよび実行可能である命令である。対照的に、「M ROM 命令」は、デコーダ 20A～C および機能ユニット 24A～C によって直接デコードおよび実行されるには複雑すぎる命令である。命令キャッシュ 16 が M ROM 命令を出力すると、M ROM ユニット 34 は、高速経路命令のシーケンスを出力することによって応答する。より具体的には、M ROM ユニット 34 は、M ROM 命令を構文解析し定義された高速経路命令のサブセットに変換して、所望の演算を実行する。M ROM ユニット 34 は、高速経路命令のサブセットをデコードユニット 20A～C にディスパッチする。

#### 【 0024 】

命令バイトが一旦命令キャッシュ 16 からフェッチされると、それらは命令整列ユニット 18 に運ばれる。命令整列ユニット 18 は、命令をデコードユニット 20A～C の 1 つに経路付ける。レジスタオペランド情報も検出されレジスタファイル 30 およびリオーダバッファ 32 に経路付けられる。加えて、命令が 1 つ以上のメモリ操作を行なわれることを必要とする場合、命令整列ユニット 18 は、メモリ操作をロード / ストアユニット 26 にディスパッチする。各デコードされた命令は、命令とともに含まれ得る変位または即値データおよびオペランドアドレス情報とともに、リザベーションステーション 22 にディスパッチされる。

#### 【 0025 】

マイクロプロセッサ 10 は、アウトオブオーダ実行をサポートし、したがって以下のタスクのためにリオーダバッファ 32 を採用する。タスクは、レジスタ読出動作およびレジスタ書き込み動作のために元のプログラムシーケンスを追跡し、レジスタリネーミングを実現し、投機的命令実行および分岐予測誤り復旧を可能にし、正確な例外を容易にするものである。リオーダバッファ 32 内の一時的記憶場所は、レジスタの更新を伴う命令のデコードの際に確保される。一時的記憶場所は、命令の投機的実行から生じる投機的レジスタ状態を記憶する。分岐命令が正しくなければ、予測誤りされた経路に沿った、投機的に実行された命令から生ずる結果は、それらがレジスタファイル 30 に書き込まれる前に、リオーダバッファ 32 において無効化可能である。同様に、特定の命令が例外を引き起こした場合、例外を引き起こした命令の後の命令が廃棄され得る。この態様では、例外は「正確」である（すなわち、例外を引き起こした命令の後の命令は、例外より前に完了されない）。なお、特定の命令は、プログラム順序でその特定の命令に先行する命令より前にそれが実行されるならば、投機的に実行される。先行する命令は、分岐命令または例外を引き起こす命令であり得、その場合には投機的結果はリオーダバッファ 32 によって廃棄され得る。

#### 【 0026 】

命令整列ユニット 18 の出力において与えられる即値または変位データおよびデコードされた命令は、それぞれのリザベーションステーション 22 に直接経路づけられる。ある実施例では、各リザベーションステーション 22 は、対応する機能ユニットへの発行を待つ

10

20

30

40

50

ている最大3つのペンドィング命令についての命令情報（すなわち、デコードされた命令ならびにオペランド値、オペランドタグおよび／または即値データ）を保持することができる。なお、図面に示す実施例では、各リザベーションステーション22は、専用の機能ユニット24と関連づけられる。したがって、3つの専用の「発行位置」がリザベーションステーション22および機能ユニット24によって形成される。言い換えれば、発行位置0は、リザベーションステーション22Aおよび機能ユニット24Aによって形成される。リザベーションステーション22Aに整列されディスパッチされる命令は、機能ユニット24Aによって実行される。同様に、発行位置1は、リザベーションステーション22Bおよび機能ユニット24Bによって形成され、発行位置2は、リザベーションステーション22Cおよび機能ユニット24Cによって形成される。

10

#### 【0027】

特定の命令のデコードの際、必要とされるオペランドがレジスタ場所であるならば、レジスタアドレス情報はリオーダバッファ32およびレジスタファイル30に同時に経路づけられる。 $\times 8$ 6レジスタファイルは、8個の32ビット実レジスタ（すなわち、典型的には、EAX、EBX、ECX、EDX、EBP、ESI、EDIおよびESPと呼ばれる）を含む。 $\times 8$ 6マイクロプロセッサーアーキテクチャを採用するマイクロプロセッサ10のある実施例では、レジスタファイル30は、32ビットの実レジスタの各々について記憶場所を含む。さらなる記憶場所が、MRROMユニット34によって使用されるレジスタファイル30内に含められてもよい。リオーダバッファ32は、これらのレジスタの内容を変更する結果のための一時的記憶場所を含み、それによりアウトオブオーダ実行を可能にする。リオーダバッファ32の一時的記憶場所は、デコードされると、実レジスタの1つの内容を変更するよう決定される各命令のために確保される。したがって、特定のプログラムの実行中のさまざまな時点で、リオーダバッファ32は、所定のレジスタの、投機的に実行された内容を含む1つ以上の場所を含み得る。

20

#### 【0028】

所定の命令のデコードの後に、リオーダバッファ32が所定の命令におけるオペランドとして用いられたレジスタに割当てられた先の場所を有していることが決定されれば、リオーダバッファ32は、対応するリザベーションステーションに、1)最も最近に割当てられた場所の値、または2)値が、やがて先の命令を実行するであろう機能ユニットによってまだ発生されていなければ、最も最近に割当てられた場所についてのタグ、のいずれかを転送する。リオーダバッファ32が所与のレジスタのために確保された場所を有していれば、オペランド値（またはリオーダバッファタグ）は、レジスタファイル30からではなくリオーダバッファ32から与えられる。リオーダバッファ32中に、必要とされるレジスタのために確保された場所がなければ、値はレジスタファイル30から直接とられる。オペランドがメモリ場所に対応していれば、オペランド値はロード／ストアユニット26を介してリザベーションステーションに与えられる。

30

#### 【0029】

ある特定の実施例では、リオーダバッファ32は、ユニットとして、同時にデコードされた命令を記憶し操作するよう構成される。この構成を、ここでは「ライン志向の」と呼ぶ。いくつかの命令を併せて操作することによって、リオーダバッファ32内に採用されるハードウェアは簡素化され得る。たとえば、この実施例に含まれるライン志向のリオーダバッファは、1つ以上の命令が命令整列ユニット18によってディスパッチされるたびに、3つの命令に属する命令情報のために十分な記憶場所を割当てる。対照的に、実際にディスパッチされる命令の数に依存して、可変量の記憶装置が、従来のリオーダバッファにおいては割当てられる。可変量の記憶装置を割当てるには、比較的多数の論理ゲートが必要とされ得る。同時にデコードされた命令の各々が実行すると、命令結果は同時にレジスタファイル30に記憶される。記憶装置は、同時にデコードされた命令の別のセットへの割当てのために解放される。加えて、制御論理はいくつかの同時にデコードされた命令にわたって償却されるので、命令当り採用される制御論理回路の量は低減される。特定の命令を特定するリオーダバッファタグは、2つのフィールドである：ラインタグおよびオフ

40

50

セットタグに分割されてもよい。ラインタグは、特定の命令を含む同時にデコードされた命令のセットを特定し、オフセットタグは、セット内のどの命令が特定の命令に対応するかを特定する。なお、命令結果をレジスタファイル30に記憶し対応する記憶装置を解放することを、命令を「リタイア」するという。さらになお、いかなるリオーダバッファ構成をマイクロプロセッサ10のさまざまな実施例において採用してもよい。

#### 【0030】

前述したように、リザベーションステーション22は、命令が対応する機能ユニット24によって実行されるまで命令を記憶する。(i)命令のオペランドが与えられ、かつ(ii)同じリザベーションステーション22A～22C内にあり、かつプログラム順序で命令より先にある命令についてオペランドがまだ与えられていなければ、命令が実行のために選択される。なお、命令が機能ユニット24の1つによって実行されると、その命令の結果は、その結果を待っているリザベーションステーション22のいずれかに直接送られ、同時に結果はリオーダバッファ32を更新するために送られる(この技術は、一般的には、「結果転送」と言われる)。命令は、関連づけられた結果が転送されるクロックサイクル中に、実行のために選択され機能ユニット24A～24Cに送られることが可能である。リザベーションステーション22は、この場合には、転送された結果を機能ユニット24に経路付ける。

#### 【0031】

ある実施例では、各機能ユニット24A～Cは、加算および減算、ならびにシフト、ロード、論理演算、および分岐動作を行なうよう構成される。なお、浮動小数点演算を可能にするために浮動小数点ユニット(図示せず)を採用してもよい。浮動小数点ユニットは、コプロセッサとして動作し、MRROMユニット34から命令を受取り、その後にリオーダバッファ32と交信して命令を完了し得る。さらに、機能ユニット24は、ロード/ストアユニット26によって行なわれるロードメモリ操作およびストアメモリ操作のためにアドレス生成を行なうよう構成され得る。

#### 【0032】

機能ユニット24の各々はまた、条件付き分岐命令の実行に関する情報を分岐予測ユニット14に与える。分岐予測が正しくなかったならば、分岐予測ユニット14は、命令処理パイプラインに入った予測誤りされた分岐の後の命令をフラッシュ(flush)し、命令キャッシュ16または主メモリからの必要とされる命令のフェッチをもたらす。なお、そのような状況では、投機的に実行され、ロード/ストアユニット26およびリオーダバッファ32に一時的に記憶されたものを含む、予測誤りされた分岐命令の後に起こる元のプログラムシークエンスにおける命令の結果は廃棄される。

#### 【0033】

機能ユニット24によって発生された結果は、レジスタ値が更新されているならばリオーダバッファ32に、メモリ場所の内容が変更されているならばロード/ストアユニット26に送られる。結果がレジスタに記憶されるべきものであれば、リオーダバッファ32は、命令がデコードされたとき、レジスタの値のために確保された場所に結果を記憶する。複数個の結果バス38が、機能ユニット24およびロード/ストアユニット26からの結果の転送のために含まれる。結果バス38は、生成された結果、および実行された命令を特定するリオーダバッファタグを運ぶ。

#### 【0034】

ロード/ストアユニット26は、機能ユニット24とデータキャッシュ28との間のインターフェイスを与える。ある実施例では、ロード/ストアユニット26は、ペンディングのロードまたはストアについてのデータおよびアドレス情報のために8個の記憶場所を有するロード/ストアバッファで構成される。バッファが一杯になると、命令整列ユニット18は、ロード/ストアユニット26がペンディングのロードまたはストア要求情報のための空きを有するまで待つ。ロード/ストアユニット26はまた、ペンディングのストアメモリ操作に対するロードメモリ操作の依存性チェックを行ない、データコヒーレンシが確実に維持されるようにする。メモリ操作は、マイクロプロセッサ10と主メモリサブシ

10

20

30

40

50

システムとの間のデータの転送である。メモリ操作は、メモリに記憶されるオペランドを利用する命令の結果であってもよく、データ転送をもたらすが他の操作をもたらさないロード／ストア命令の結果であってもよい。加えて、ロード／ストアユニット26は、セグメントレジスタと、 $\times 8$ 6マイクロプロセッサーアーキテクチャによって定義されるアドレス変換メカニズムに関連する他のレジスタなどの特殊レジスタのための特有のレジスタ記憶場所とを含み得る。

#### 【0035】

ある実施例では、ロード／ストアユニット26は、ロードメモリ操作を投機的に行なうよう構成される。ストアメモリ操作は、プログラム順序で行なわれてもよいが、予測されたウェイに記憶されてもよい。予測されたウェイが正しくなければ、ストアメモリ操作の前のデータは、その後に、予測されたウェイにリストアされ、ストアメモリ操作は正しいウェイに行なわれる。別の実施例では、ストアは投機的に実行されてもよい。投機的に実行されたストアは、更新の前のキャッシュラインのコピーとともに、ストアバッファ内に置かれる。投機的に実行されたストアが、分岐予測誤りまたは例外のために後に廃棄されるならば、キャッシュラインはバッファに記憶された値にリストアされてもよい。なお、ロード／ストアユニット26は、投機的実行なしを含む、いかなる投機的実行を行なうようにも構成されてよい。

10

#### 【0036】

データキャッシュ28は、ロード／ストアユニット26と主メモリサブシステムとの間で転送されるデータを一時的に記憶するために設けられる高速キャッシュメモリである。ある実施例では、データキャッシュ28は、8ウェイのセットアソシアティブ構造で最大16キロバイトを記憶する容量を有する。命令キャッシュ16と同様に、データキャッシュ28は、ウェイ予測メカニズムを採用し得る。データキャッシュ28は、セットアソシアティブ構成およびダイレクトマップ構成を含む、さまざまな特有のメモリ構成で実現可能であることが理解される。

20

#### 【0037】

$\times 8$ 6マイクロプロセッサーアーキテクチャを採用するマイクロプロセッサ10のある特定の実施例では、命令キャッシュ16およびデータキャッシュ28は線形にアドレスされる。線形アドレスは、命令によって特定されるオフセットと、 $\times 8$ 6アドレス変換メカニズムのセグメント部分によって特定されるベースアドレスとから形成される。線形アドレスは、任意で、主メモリにアクセスするために物理的アドレスに変換されてもよい。線形から物理への変換は、 $\times 8$ 6アドレス変換メカニズムのページング部分によって特定される。なお、線形アドレスのキャッシュは、線形アドレスタグを記憶する。1組の物理的タグ（図示せず）を採用して、線形アドレスを物理的アドレスにマッピングし、かつ変換エンティアスを検出してもよい。加えて、物理的タグロックが、線形から物理へのアドレス変換を行なってよい。

30

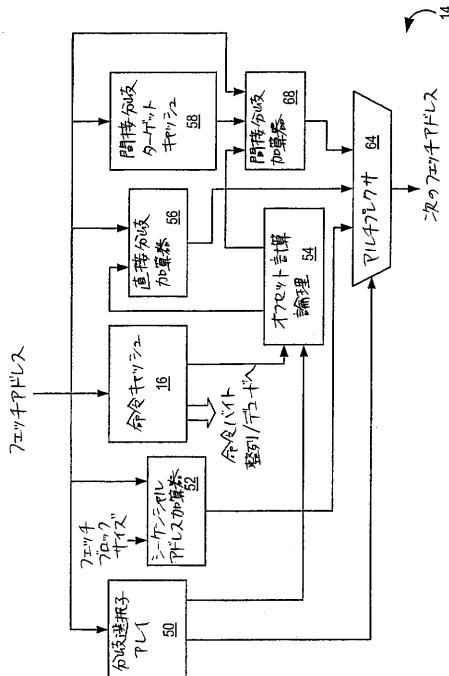

#### 【0038】

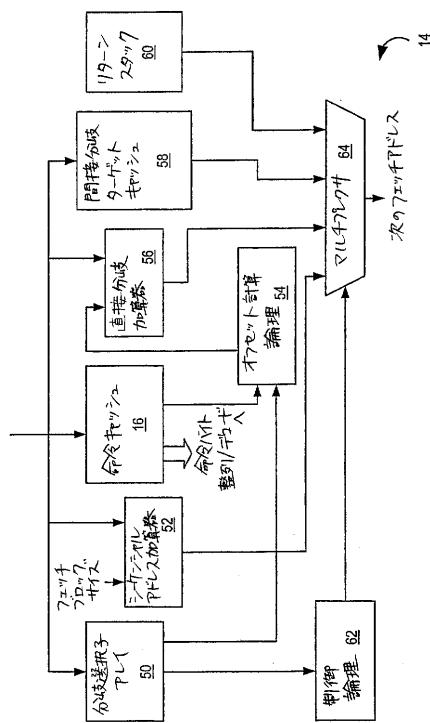

##### 分岐予測ユニット

ここで図2を参照すると、分岐予測ユニット14のある実施例の詳細が示される。図が示すとおり、この実施例では、分岐予測ユニット14は、分岐選択子アレイ50と、シーケンシャルアドレス加算器52と、オフセット計算論理54と、直接分岐加算器56と、間接分岐ターゲットキャッシュ58と、リターンスタック60と、制御論理回路62と、マルチプレクサ64とを含む。

40

#### 【0039】

一般的には、分岐予測ユニット14は、機能ユニット24A～Cからフェッチアドレスを受取り、これに応答して予測される次のフェッチアドレスを出力する。予測される次のフェッチアドレスは次に、命令キャッシュ16に経路付けられる。予測される次のフェッチアドレスが命令キャッシュ16をミスすれば、予測される次のフェッチアドレスはプリフェッチ／プリデコードユニット12に経路付けられる。プリフェッチ／プリデコードユニット12は、主メモリサブシステムにアクセスし、予測された次のフェッチアドレスに存

50

在する予め定められた数の命令バイトを命令キャッシュ 16 に記憶するプロセスを開始する。

#### 【 0 0 4 0 】

分岐予測ユニット 14 の動作中、受取られたフェッチアドレスのすべてまたは一部は、複数の異なった場所に並列に経路付けられる。たとえば、図に例示される実施例では、フェッチアドレスは、分岐選択子アレイ 50、シーケンシャルアドレス加算器 52、命令キャッシュ 16、直接分岐加算器 56、および間接分岐ターゲットキャッシュ 58 に運ばれる。

#### 【 0 0 4 1 】

分岐選択子アレイ 50 は、各々が命令キャッシュ 16 内の特定の命令バイトに対応する、複数個の選択ビットを記憶するよう構成される。ある実施例では、分岐選択アレイ 50 は、命令キャッシュ 16 の構造をミラーリングするよう構成される。たとえば、命令キャッシュ 16 が 4 ウェイセットアソシアティブキャッシュとして構成される場合、分岐選択子アレイ 50 も、4 ウェイのセットアソシアティブとして構成されてもよい。分岐選択子アレイ 50 と命令キャッシュ 16 とはどちらも、フェッチアドレスの同じタグまたは部分を用いてアクセス可能である。分岐選択子アレイ 50 によって出力される選択子ビットは、制御論理回路 62 に経路付けられる。選択子ビットに基づいて、制御論理回路 62 は、4 個の潜在的に可能なソースの 1 つから次の予測されるフェッチアドレスを選択するようマルチプレクサ 64 を制御する。ある実施例では、マルチプレクサ 64 は、以下の可能性がある 4 つのアドレス、(1) 計算されたシーケンシャルなアドレス、(2) 計算された直接分岐ターゲットアドレス、(3) 記憶された間接分岐ターゲットアドレス、および(4) 記憶されたリターンアドレス、から予測される次のフェッチアドレスを選択する。これらの 4 個の潜在的に可能なアドレスの各々を個別に以下に記載する。ここに使用されるフェッチブロックという言葉は、命令キャッシュ 16 中でヒットするフェッチアドレスを受取るのに応答して命令キャッシュ 16 によって出力される命令バイトのブロックのことを行う。いくつかの実現化例では、フェッチブロックはキャッシュラインに等しくてもよい。別の実現化例では、命令キャッシュ 16 は、キャッシュラインの一部（たとえば、キャッシュラインの半分）を出力してもよく、その場合は、キャッシュラインは複数のフェッチブロックを含み得る。

#### 【 0 0 4 2 】

4 つの潜在的に可能なアドレスの第 1、すなわち計算されたシーケンシャルなアドレスは、選択子ビットが、フェッチされたキャッシュライン内のフェッチアドレスの後にティクンの分岐がないということを示す場合、選択される。たとえば、フェッチされたキャッシュラインが分岐命令を有していないなければ、プログラムは、現在のフェッチされたキャッシュラインの終わりを超えて次のシーケンシャルなキャッシュラインへ実行を続けるであろう。次のシーケンシャルなキャッシュラインのフェッチアドレスは、シーケンシャルアドレス加算器 52 によって計算される。シーケンシャルアドレス加算器 52 は、フェッチアドレス（またはその一部）を受取りそれを定数 66 に加算するよう構成される。定数 66 は、命令キャッシュ 16 のフェッチブロックサイズに等しい。たとえば、ヒットするフェッチアドレスが受取られるたびに、16 個の命令バイトのブロックが命令キャッシュ 16 によって出力されるならば、定数 66 は 16 に等しいであろう。フェッチアドレスにフェッチブロックサイズを加算することにより、次のシーケンシャルなフェッチブロックのアドレスを計算することが可能である。いくつかの実施例では、フェッチアドレスの下位ビット（たとえば、フェッチブロック内のバイトオフセットを示すインデックスビット）は、合計が行なわれるより前または後にゼロにされ得ることに注目されたい。これにより、次のシーケンシャルアドレスは確実に、キャッシュライン（または、キャッシュライン内に複数のフェッチブロックがある場合フェッチブロック）の始まりに対応するようになる。

#### 【 0 0 4 3 】

4 つの潜在的に可能なアドレスの第 2、すなわち計算された直接分岐ターゲットアドレス

10

20

30

40

50

は、制御論理回路 6 2 によって受取られる選択子ビットが、ティクンであると予測される直接分岐命令の存在を示す場合、マルチプレクサ 6 4 によって選択される。直接分岐命令は、オフセット（すなわち、ジャンプするバイトの数）が即値データとして命令内に含まれている分岐命令である。たとえば、 $\times 8$  6 命令セットでは、即値オフセットを備える無条件ニアジャンプ命令（たとえば、JMP 014C）が直接分岐命令の一例である。即値オフセット（先の例では 014C）は、分岐命令のすぐ後に続く命令の命令ポインタ（EIP）に加算される、またはそれから減算されるバイトの数を示す。直接分岐加算器 5 6 は、直接分岐ターゲットアドレスを計算する。ある実施例では、予測される直接分岐アドレスを生成するために、直接分岐加算器 5 6 は、以下の 3 つの構成要素、（1）フェッチアドレス、（2）現在のフェッチアドレスから、直接分岐命令のすぐ後に続く命令へのオフセット、および（3）直接分岐命令内に即値データとして記憶されるオフセット、を合計する。フェッチアドレスは、計算のための開始点としての役割を果たす。現在のフェッチアドレスから直接分岐アドレスのすぐ後に続く命令へのオフセットは、開始点に加算され、有効な EIP 値を形成する。即値データとして記憶されるオフセットは次に、有効 EIP 値に加算され、予測される直接分岐ターゲットアドレスを生成する。加算器 5 6 は、任意の数の異なったタイプの加算器（たとえば、桁上げ伝搬加算器または桁上げ保存加算器）の 1 つとして、または異なる加算器のタイプの組合せとして実現されてもよいことに注目されたい。さらに、加算演算は、いかなる順序でまたは並列に行なわれてもよい。直接分岐加算器 5 6 によって使用される 2 つのオフセット値は、命令キャッシュ 1 6 から受取られる命令バイトからのオフセット値を決定する計算論理ユニット 5 4 によって計算される。この計算を以下により詳細に記載する。

#### 【0044】

4 つの潜在的に可能なアドレスの第 3、すなわち記憶された間接分岐ターゲットアドレスは、制御論理回路 6 2 によって受取られる選択子ビットが、ティクンであると予測される間接分岐命令の存在を示す場合、マルチプレクサ 6 4 によって選択される。間接分岐命令は、オフセットが即値データとして記憶されない分岐命令である。たとえば、オフセットがメモリ（たとえば、JMP [9912]）またはレジスタ（たとえば、JMP AX）に記憶される無条件ジャンプ命令が、間接分岐であると考えられる。直接分岐命令とは対照的に、メモリまたはレジスタから所望のオフセットを取出すのに必要とされる余分な時間のために、間接分岐について、予測される分岐ターゲットアドレスを「オンザフライ」（またはプログラム順序を飛越して）計算することはより困難であるかもしれない。したがって、予測される間接分岐アドレスは、間接分岐ターゲットキャッシュ 5 8 に記憶される。間接分岐ターゲットキャッシュ 5 8 は、現在のフェッチアドレスを受取り、応答して予測される間接分岐ターゲットアドレスをマルチプレクサ 6 4 に出力するよう構成される。制御論理回路 6 2 が、ティクンであると予測される間接分岐命令を検出すると、それは、間接分岐ターゲットキャッシュ 5 8 によって出力される予測される間接分岐ターゲットアドレスを選択するようにマルチプレクサ 6 4 を向ける。

#### 【0045】

第 4 の潜在的に可能なアドレスは、記憶されたリターンアドレスである。記憶されたリターンアドレスは、制御論理 6 2 によって受取られる選択子ビットがリターン命令の存在を示す場合、マルチプレクサ 6 4 によって選択される。リターン命令（たとえば、 $\times 8$  6 命令セットにおける RET および RETF）は、先行するコール命令の前にそれが保持する値に EIP をリストアする。コール命令およびリターン命令は、典型的には、プロシージャまたはサブルーチンにジャンプしつつそれからリターンするために使用される。コール命令は、メモリにスタックへの現在の命令ポインタを記憶（またはプッシュ）し、リターン命令は、メモリスタックから記憶された命令ポインタを読み出す（またはポップする）ことにより、最終コール命令の前からのその値に命令ポインタをリストアする。図示の実施例では、リターンスタック 6 0 は、コール命令に対応する命令ポインタを記憶するよう構成される。制御論理回路 6 2 によって受取られる選択子ビットがリターン命令を示す場合、制御論理回路 6 2 は、マルチプレクサ 6 4 に、リターンスタック 6 0 の最上部の予測さ

れたリターンアドレスを選択させる。リターンスタック 60 は、予測されるリターンアドレスがマルチプレクサ 64 によって選択されるたびにスタックポインタのその最上部をインクリメントして適切なスタック動作を可能にするよう構成され得る。同様に、コール命令が検出され、対応する命令ポインタがリターンスタック 60 に記憶されると、スタックポインタの最上部がデクリメントされ得る。

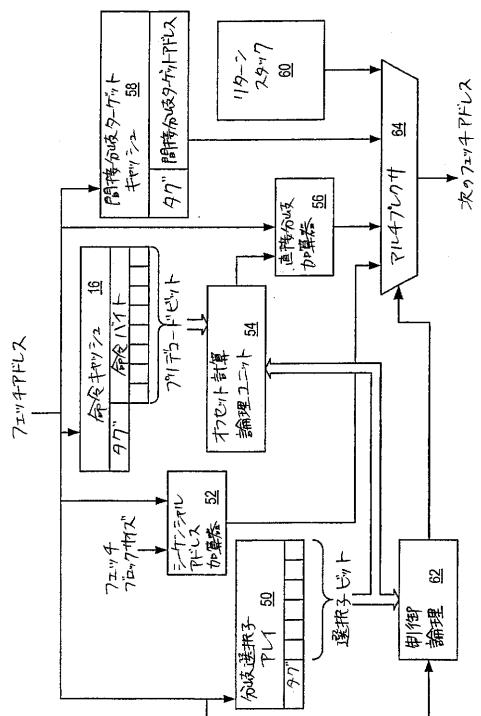

#### 【 0 0 4 6 】

ここで図 3 を参照して、分岐予測ユニット 14 のある特定の実施例のさまざまな特徴が示される。図が例示するように、分岐選択子アレイ 50 、命令キャッシュ 16 、および間接分岐ターゲットキャッシュ 58 は各々、記憶された情報に対応するタグを記憶してもよい。間接分岐ターゲットキャッシュは、命令キャッシュ 16 の構造を鏡映し、キャッシュラインまたはフェッチブロック当たり 1 つ以上の間接分岐ターゲットアドレスを記憶してもよい。別の実施例では、間接分岐ターゲットキャッシュ 58 は、フルアソシアティブであってもよく、予測される間接分岐ターゲットアドレスの予め定められた数まで記憶してもよい。たとえば、間接分岐ターゲットキャッシュ 58 は、予め定められた数の、最も最近のティクンの間接分岐ターゲットアドレスを記憶するために、先入れ先出し (FIFO) 置換方式を用いるよう構成されてもよい。いくつかの実施例では、間接分岐ターゲットキャッシュ 58 は、間接分岐ターゲットアドレスのみを記憶してもよく、これは、間接分岐ターゲットキャッシュ 58 を、間接分岐ターゲットアドレスに加えてターゲットアドレスの他のタイプを記憶する他の分岐ターゲットキャッシュよりも小さくし得る。さらに、間接分岐は直接分岐ほど頻繁に行なわれないので、これはさらに、記憶場所がより少ない分岐ターゲットキャッシュを実現するのに関連するいかなる潜在的不利益を軽減し得る。10

20

#### 【 0 0 4 7 】

図がまた例示するように、オフセット計算ユニット 54 は、命令キャッシュ 16 からプリデコードビットを受取るよう構成されてもよい。前述のとおり、プリデコードビットは、プリデコードユニット 12 によって生成され、命令キャッシュ 16 に記憶される命令の整列およびデコーディングに関連する情報を記憶するために使用されてもよい。オフセット計算ユニット 54 はまた、分岐選択子アレイ 50 から選択子ビットを受取るよう構成されてもよい。ある実施例では、分岐選択子アレイ 50 は、フェッチアドレスの後に生じる選択子ビットのみを出力するよう構成されてもよい。別の実施例では、分岐選択子アレイ 50 は、命令キャッシュ 16 内の選択されたキャッシュラインまたはフェッチブロックの各バイトに対応する選択子ビットのすべてを出力するよう構成されてもよい。さらに、制御論理回路 62 およびオフセット計算ユニット 54 はどちらも、分岐選択子アレイ 50 によって出力される選択子ビットのすべてまたは一部のみを受取るよう構成されてもよい。ある実施例では、分岐選択子アレイは、フェッチアドレスに対応する選択子ビットを、マルチプレクサ 64 の制御入力に直接出力し、それにより制御論理回路 62 の複雑さを低減するように（または完全になくすように）構成されてもよい。30

#### 【 0 0 4 8 】

分岐予測誤りが検出されると、機能ユニット 24 は、正しい分岐ターゲットアドレス（および対応するティクンまたはノットティクン情報）を、分岐予測ユニット 14 に与え得る。分岐予測ユニット 14 は次に、分岐選択子アレイ 50 および間接分岐ターゲットキャッシュ 58 中の対応する情報を更新するよう構成され得る。分岐予測ユニット 14 および分岐選択子アレイ 50 はまた、命令キャッシュ 16 内の置換されたキャッシュラインまたはフェッチブロックに対応するいかなる選択子ビットをモリセットするよう構成され得る。リターンスタック 60 は、そのエントリの各々に関連付けられる有効ビットを有してもよい。さらに、さらなる記憶アレイを用いて、間接分岐ターゲットアレイ 58 に間接分岐ターゲットアドレス全体を記憶する代わりに、オフセットの異なるサイズ（たとえば、別個の、 8 、 16 、および 32 ビットのアレイ）を記憶することが可能である。しかし、この実施例は、記憶されたオフセットを用いて間接分岐ターゲットアドレス計算を行なうためにさらなる加算器を使用する可能性がある。40

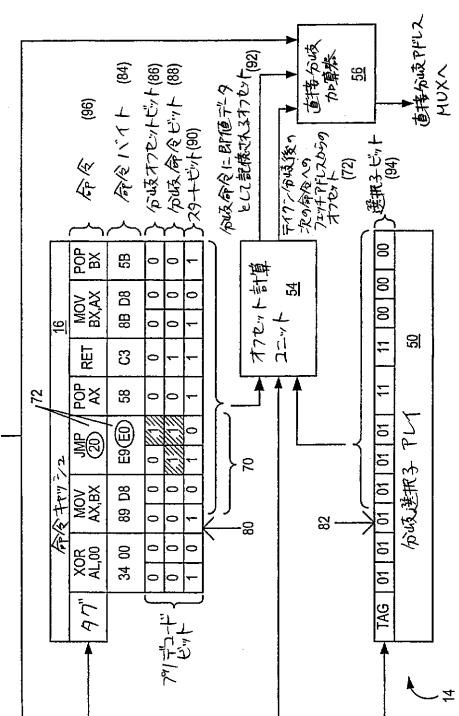

#### 【 0 0 4 9 】

ここで図4を参照して、分岐予測ユニット14のある実施例の動作のさらなる詳細が示される。図が例示するように、ある実施例では、命令キャッシュ16は、命令バイト84と、分岐オフセットビット86と、分岐命令バイト88と、スタートビット90とを記憶可能である。なお、アセンブルされていない命令96が説明のためにのみ示され、命令キャッシュ16内に實際には記憶されていない。分岐オフセットビット86、分岐命令バイト88、およびスタートビット90はすべて、プリデコードユニット12によって生成されるプリデコードビットである。各プリデコードビットは、例示に示されるように1命令バイトに対応する。分岐オフセットビット86は、対応する命令バイトが直接分岐命令の即値オフセットの一部を含む場合、アサートされる。たとえば、命令JMP20は、次の命令(すなわちPOP AX)の開始の20バイト後のアドレスへの無条件ジャンプを表わす。命令JMP20は、E9 E0として16進数マシンコードにアセンブルされる。ただし、E9は、即値8ビットオフセットを備える無条件ジャンプについての操作コードであり、E0は、オフセット(20)の2の補数表現である。オフセットは、図の円72によって示される。バイトE0は、直接分岐命令についての即値オフセットデータを表すので、対応する分岐オフセットビット86はセットされる(影付きのブロックによって表わされる)。

#### 【0050】

同様に、対応する命令バイトが分岐命令の一部であるとき、分岐命令ビット88はアサートされる。たとえば、命令JMP 20およびRETはどちらも分岐命令である。したがって、その対応する分岐命令ビット86はアサートされる。前述のとおり、スタートビット90は、対応する命令バイトが命令の第1のバイトである場合にのみアサートされる。

#### 【0051】

図はまた、選択子ビット94についての符号化のあるタイプの一例を例示する。図において使用される符号化は、命令キャッシュ16内に記憶される各命令バイトについて2つの選択子ビットを利用する。なお、他の実施例では、選択子ビット94は、命令キャッシュ16中の命令バイトのサブセットについて記憶されてもよく、たとえば命令バイト1つおきに2つの選択子ビットであってもよい。表1は、図に示す例に使用される符号化を例示する。

#### 【0052】

#### 【表1】

表1-選択子ビット符号化

|    |                                            |

|----|--------------------------------------------|

| 00 | 分岐命令ノットテイクン、<br>シーケンシャルなアドレスを選択する          |

| 01 | 直接分岐命令テイクン<br>計算された直接分岐アドレスを選択する           |

| 10 | 間接分岐テイクン、間接分岐ターゲットキャッシュ<br>から間接分岐アドレスを選択する |

| 11 | リターン命令、リターンスタックからリターン<br>アドレスを選択する         |

#### 【0053】

図では、矢印80および82は例としてのフェッチアドレスを表わす。例のフェッチアドレスを用いて、分岐予測ユニット14の動作が例示され得る。フェッチアドレスは、命令キャッシュ16、オフセット計算ユニット54、直接分岐加算器56、および分岐選択子アレイ50によって受取られる。応答して、命令キャッシュ16は、MOV AX, BX命令で始まる命令バイト84を命令整列ユニット18に出力する。並列に、対応するプリデコードビット(これも選択的に整列ユニット18に経路付けされ得る)は、オフセット計算ユニット54に運ばれる。並列してまた、分岐選択子アレイ50は、選択子ビット94(命令キャッシュ16によって出力される命令バイトに対応する)をオフセット計算ユ

10

20

30

40

50

ニット 54 に運ぶ。

#### 【0054】

フェッチアドレス、プリデコードビット、および選択子ビットを受取った後、オフセット計算ユニット 54 は 2 つのオフセットを計算する。第 1 のオフセットは、フェッチアドレス 80 から、(図の範囲 70 によって表わされる) 第 1 のティクンの分岐命令の終わりまでのバイトの数である。これは、複数の方法で、たとえば、アサートされる対応する選択子ビットを有する第 1 のセットの分岐命令ビットに対してスキャンすることによって決定可能である。このオフセットは、直接分岐加算器 56 に運ばれる。第 2 のオフセットは、(円 72 によって表わされる) 直接ジャンプ命令内の即値データとして記憶されるオフセットである。ある実施例では、オフセット計算ユニット 54 は、プリデコードビットに加えて計算キャッシュ 16 から命令バイトを受取ってもよい。オフセット計算ユニット 54 は次に、フェッチアドレスの後の第 1 のティクンの分岐命令に対応するアサートされた分岐オフセットビット 86 に対してスキャンすることによって、命令バイトから即値オフセットデータ 72 を選択してもよい。オフセット計算ユニット 54 は、第 1 の「ティクン」の分岐命令に対してスキャンし、「ノットティクン」である分岐命令が予測に悪影響を与えないようにし得る。さらに、複数の命令バイトに対応する選択子ビットがオフセット計算ユニット 54 に運ばれ得るが、ある実施例では、フェッチアドレスに対応する選択子のみが制御論理回路 62 (またはマルチブレクサ 64) に運ばれることに注目されたい。上に使用された例では、値 01 を有する選択子ビット (フェッチアドレス 80 および 82 の命令バイトに対応する) は、マルチブレクサ 64 に出力され、直接分岐加算器 56 からの出力が選択されるべきであることを示すであろう。10

#### 【0055】

代わりに、フェッチアドレスが命令 POP BX のそれであったとすると、(値 00 を有する) 選択子ビットの最終の対は、マルチブレクサ 64 に運ばれ、(シーケンシャルアドレス加算器 52 によって生成される) 次のシーケンシャルなフェッチアドレスが選択されるべきであることを示すであろう。同様に、フェッチアドレスが命令 RET のそれであつた場合、値 11 を有する選択子ビットは、マルチブレクサ 64 に運ばれ、リターンスタック 60 の最上部に記憶されたリターンアドレスが選択されるべきであることを示すであろう。20

#### 【0056】

なお、選択子ビット 94 の他の構成もまた企図される。たとえば、ある実施例では、分岐予測ユニットは、リターンスタック 60 なしに実現されてもよい。同様に、他のプリデコード情報が、上述のプリデコード情報に加えてまたはその代わりに記憶されてもよく、たとえば、対応する分岐予測情報が有効であるかどうかを示す有効ビットが記憶されてもよい。同様に、リセットが発生する場合、分岐選択子アレイ 50 は、すべての選択子ビット 94 をクリアする (たとえば 00) よう構成されてもよい。命令キャッシュは、キャッシュラインが上書きされているときプリデコードユニット 12 に制御信号をアサートするよう構成されてもよい。分岐選択子アレイ 50 が命令キャッシュ 16 の構造をミラーリングする構造を有するならば、分岐選択子アレイ 50 は、上書きされたキャッシュラインに対応するすべての選択子ビット 94 をクリアしてもよい。30

#### 【0057】

ここで図 5 を参照すると、分岐予測ユニット 14 の別の実施例が例示される。この実施例では、分岐選択子アレイ 50 からの選択子ビットは、マルチブレクサ 64 に直接経路付けされ、どのソースが次の予測されるフェッチアドレスを与えるかを選択する。選択子ビットが正しくなければ、または (後に機能ユニット 24A ~ C によって検出されるように) 記憶されたアドレスの 1 つが正しくなければ、正しくない情報は、機能ユニット 24A ~ C から受取られた正しい情報で更新される。たとえば、選択子ビット 94 が、特定の命令がティクンであると誤って表すならば、機能ユニット 24A ~ C は、分岐予測誤りを検出すると、選択子ビットが誤っており更新される必要があるということを分岐予測ユニット 14 に通知するであろう。40

**【0058】**

この実施例のさらなる特徴は、間接分岐ターゲットがオフセットの形で記憶されることである。オフセットは次に、間接分岐加算器 68 によってフェッチアドレスに加算される。この計算は、直接分岐加算器 56 によって行なわれる計算と同様に行なわれ得る。さらになお、この実施例はリターンスタック 60 を使用しない。

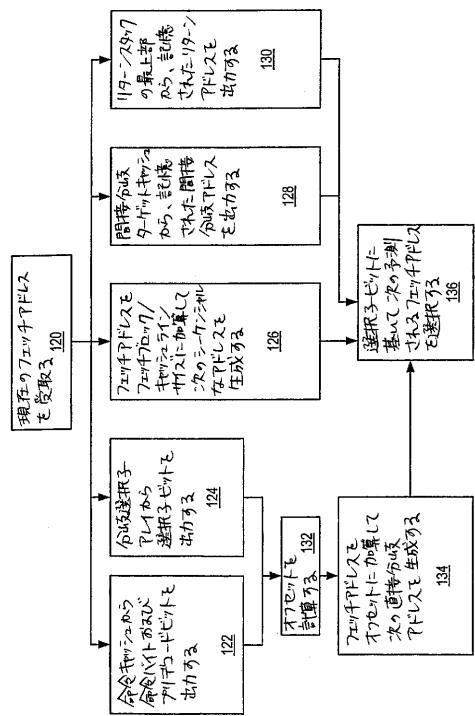

**【0059】**

次に図 6 を参照して、マイクロプロセッサにおける予測される次のフェッチアドレスを記憶するための方法のある実施例を例示するフローチャートが示される。この実施例では、現在のフェッチアドレスが受取られた後（ステップ 120）、以下の複数の機能が並列に行なわれ得る。（1）命令バイトおよびプリデコードビットが命令キャッシュ 16 から出力される（ステップ 122）。 （2）選択子ビットが分岐選択子アレイ 50 から出力される（ステップ 124）。 （3）フェッチアドレスがフェッチブロック / キャッシュラインサイズに加算され、次のシーケンシャルなフェッチアドレスが生成される（ステップ 126）。 （4）記憶された間接分岐命令アドレスが間接分岐ターゲットキャッシュ 58 から出力される。 （5）リターンスタック 60 の最上部からのリターンアドレスが出力される。 次に、オフセット計算ユニット 54 は、フェッチアドレスから第 1 の予測されるティクンの直接分岐命令へのオフセットを計算し、直接分岐命令内に即値データとして記憶されたオフセットを検出する（ステップ 132）。一旦計算されると、オフセットは次にフェッチアドレスに加算され、予測される次の直接分岐命令を生成する（ステップ 134）。最後に、次の予測されるフェッチアドレスは、分岐選択子アレイ 50 からの選択子ビットに基づいて選択される（ステップ 136）。

10

20

30

**【0060】**

なお、例示されるステップのいくつかはオプションである（たとえばステップ 130）。さらになお、ステップの順番は変動可能であり、ステップ内の異なった機能を異なったシーケンスで行なってもよい。たとえば、プリデコードビットは、命令バイトより前に命令キャッシュの出力から利用可能であってもよい（ステップ 122）。したがって、各オフセットについての計算は、異なったときに開始され得る。さらになお、さらなるステップが異なった実施例においては加えられてもよい。たとえば、前述のように、いくつかの実施例は、アドレス全体の代わりにオフセットとして間接分岐ターゲットアドレスを記憶してもよい。そのような実施例では、記憶されたオフセットをフェッチアドレスおよびオフセット計算論理 54 によって生成されたオフセットに加算するさらなるステップが利用されてもよい。

30

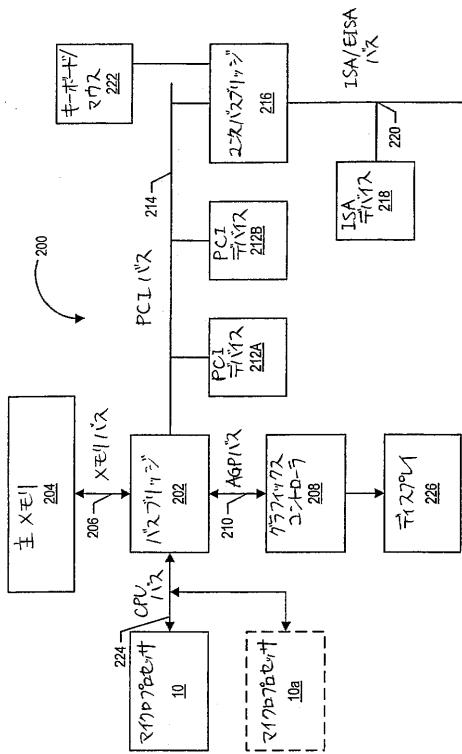

**【0061】****コンピュータシステムへの通用例**

ここで図 7 を参照すると、マイクロプロセッサ 10 および分岐予測ユニット 14 のある実施例を利用する構成されたコンピュータシステム 200 のある実施例のブロック図が示される。図示のシステムでは、主メモリ 204 がメモリバス 206 を介してバスブリッジ 202 に結合され、グラフィックスコントローラ 208 が AGP バス 210 を介してバスブリッジ 202 に結合される。最後に、複数個の PCI デバイス 212A ~ 212B が PCI バス 214 を介してバスブリッジ 202 に結合される。2 次バスブリッジ 216 が、EISA / ISA バス 220 を介して 1 つ以上の EISA または ISA デバイス 218 への電気的インターフェイスを収容するよう設けられてもよい。マイクロプロセッサ 10 は、CPU バス 224 を介してバスブリッジ 202 に結合される。

40

**【0062】**

バスブリッジ 202 は、マイクロプロセッサ 10 と主メモリ 204 とグラフィックスコントローラ 208 と PCI バス 214 につながれるデバイスとの間のインターフェイスとして機能する。演算がバスブリッジ 202 に接続されるデバイスの 1 つから受取られると、バスブリッジ 202 は演算のターゲット（たとえば、特定のデバイスまたは、PCI バス 214 の場合には、ターゲットは PCI バス 214 にある）を特定する。バスブリッジ 202 は、ターゲットとされたデバイスに演算を経路付ける。バスブリッジ 202 は、一般

50

的には、ソースデバイスまたはバスによって使用されるプロトコルからターゲットデバイスまたはバスによって使用されるプロトコルに演算を変換する。

#### 【0063】

P C I バス 2 1 4 に対して I S A / E I S A バスへのインターフェイスを与えることに加えて、2 次バスブリッジ 2 1 6 はさらに、所望に応じて、さらなる機能を組込んでもよい。たとえば、ある実施例では、2 次バスブリッジ 2 1 6 は、P C I バス 2 1 4 の使用の優先順位を決定するためのマスタ P C I アービタ（図示せず）を含む。外部からの、または 2 次バスブリッジ 2 1 6 と一体化されるかのいずれかの、入力／出力コントローラ（図示せず）をもコンピュータシステム 2 0 0 内に含めて、所望により、キーボードおよびマスク 2 2 0 のための、ならびにさまざまなシリアルポートおよびパラレルポートのための動作サポートを与えてよい。外部キャッシュユニット（図示せず）が、他の実施例では、マイクロプロセッサ 1 0 とバスブリッジ 2 0 2 との間の C P U バス 2 2 4 にさらに結合されてもよい。代替的に、外部キャッシュはバスブリッジ 2 0 2 に結合されてもよく、外部キャッシュのためのキャッシュ制御論理回路がバスブリッジ 2 0 2 に一体化されてもよい。10

#### 【0064】

主メモリ 2 0 4 は、アプリケーションプログラムがこれに記憶されマイクロプロセッサ 1 0 が主にここから実行するメモリである。好適な主メモリ 2 0 4 は、D R A M （ダイナミック・ランダム・アクセス・メモリ）、および好ましくは S D R A M （シンクロナス D R A M ）の複数個のバンクを含む。20

#### 【0065】

P C I デバイス 2 1 2 A ~ 2 1 2 B は、たとえば、ネットワークインターフェイスカード、ビデオアクセラレータ、オーディオカード、ハードまたはフロッピイディスクドライブまたはドライブコントローラ、S C S I （スマート・コンピュータ・システムズ・インターフェイス）アダプタおよび電話機能カードなどのさまざまな周辺デバイスを例示するものである。同様に、I S A デバイス 2 1 8 は、モデム、サウンドカード、または G P I B もしくはフィールドバスインターフェイスカードなどのさまざまなデータ収集カードなどのさまざまなタイプの周辺デバイスを例示するものである。

#### 【0066】

ディスプレイ 2 2 6 上のテキストおよび画像のレンダリングを制御するためにグラフィックスコントローラ 2 0 8 が設けられる。グラフィックスコントローラ 2 0 8 は、主メモリ 2 0 4 およびそれから有効にシフト可能である 3 次元データ構造をレンダリングするために、一般的に公知の典型的なグラフィックスアクセラレータを採用してもよい。グラフィックスコントローラ 2 0 8 は、したがって、それがバスブリッジ 2 0 2 内のターゲットインターフェイスへのアクセスを要求し受取り、それにより主メモリ 2 0 4 へのアクセスを獲得することができるという点で、A G P バス 2 1 0 のマスタであり得る。専用のグラフィックスバスが、主メモリ 2 0 4 からの高速のデータ取出を可能にする。ある種の動作では、グラフィックスコントローラ 2 0 8 は、A G P バス 2 1 0 での P C I プロトコルトランザクションを生成するようさらに構成されてもよい。バスブリッジ 2 0 2 の A G P インターフェイスは、したがって、A G P プロトコルトランザクションも P C I プロトコルターゲットおよびイニシエータトランザクションもサポートする機能を含み得る。ディスプレイ 2 2 6 は、画像またはテキストを表わすことのできるいかなる電子ディスプレイでもある。好適なディスプレイ 2 2 6 は、陰極線管（「C R T」）、液晶ディスプレイ（「L C D」）などを含む。30

#### 【0067】

なお、A G P バス、P C I バスおよびI S A またはE I S A バスが上の記載では例として使用されたが、所望によりいかなるバスアーキテクチャが置換されてもよい。さらにお、コンピュータシステム 2 0 0 は、さらなるマイクロプロセッサを含むマルチプロセッシングコンピュータシステムであってもよい。

#### 【0068】

10

20

30

40

50

さらになお、この説明はさまざまな信号のアサーションに言及することがある。信号が特定の条件を示す値を運ぶ場合、信号が「アサートされる」とここでは用いられる。反対に、信号が特定の条件の欠如を示す値を運ぶ場合、信号は「デアサートされる」または「アサートされない」。信号は、論理 0 値を運ぶとき、または反対に、論理 1 値を運ぶときアサートされるものと定義され得る。加えて、上の記載では廃棄されるものとしてさまざまな値が記載された。値は複数の態様で廃棄され得るが、一般的には、値を受取る論理回路によってそれが無視されるように値を変更することを伴う。たとえば、値が 1 ビットを含む場合、値の論理状態は、値を廃棄するよう反転され得る。値が  $n$  ビットの値である場合、 $n$  ビットの符号化の 1 つが、値が無効であることを示し得る。値を無効の符号化にセットすることにより、値が廃棄されるようになる。加えて、 $n$  ビットの値は、セットされたと  $n$  ビットの値が有効であることを示す有効ビットを含み得る。有効ビットをリセットすることは、値を廃棄することを含み得る。値を廃棄する他の方法が同様に使用されてもよい。

#### 【0069】

##### 産業上の適用性

この発明は、一般的には、マイクロプロセッサおよびコンピュータシステムに適用可能であろう。

#### 【0070】

さまざまな変形および変更が、上の記載を完全に理解すると当業者には明らかとなるであろう。前掲の特許請求の範囲はそのようなすべての変形および変更を含むものと解釈されるべきであることが意図される。

##### 【図面の簡単な説明】

【図 1】 マイクロプロセッサのある実施例の例示の図である。

【図 2】 図 1 のマイクロプロセッサからの分岐予測ユニットのある実施例の例示の図である。

【図 3】 図 2 からの分岐予測ユニットのある実施例のさらなる詳細を例示する図である。

【図 4】 図 2 からの分岐予測ユニットのある実施例のさらなる詳細を例示するブロック図である。

【図 5】 図 2 からの分岐予測ユニットの別の実施例を例示するブロック図である。

【図 6】 マイクロプロセッサにおける予測される次のフェッチアドレスを記憶するための方法のある実施例を例示する流れ図である。

【図 7】 図 1 からのマイクロプロセッサのある実施例を使用するよう構成されたコンピュータシステムのある実施例のブロック図である。

10

20

30

【 四 1 】

【 四 2 】

【図3】

【 図 4 】

【図5】

【図6】

【図7】

---

フロントページの続き

(74)代理人 100083703

弁理士 仲村 義平

(74)代理人 100091409

弁理士 伊藤 英彦

(74)代理人 100096781

弁理士 堀井 豊

(74)代理人 100096792

弁理士 森下 八郎

(72)発明者 ロバーツ, ジェイムズ・エス

アメリカ合衆国、78746 テキサス州、オースティン、タマロン・ブルバード、3050、

ナンバー・1205

審査官 後藤 彰

(56)参考文献 特開平8-320786 (JP, A)

特開平6-168120 (JP, A)

特開平5-120013 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 9/38