## (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2020/038125 A1

(51) International Patent Classification: G09G 3/3208 (2016.01) G11C 19/28 (2006.01)

(21) International Application Number:

PCT/CN20 19/094395

(22) International Filing Date:

02 July 2019 (02.07.2019)

(25) Filing Language:

English

(26) **Publication Language:**

English

CN

(30) Priority Data:

201810966800.7

23 August 2018 (23.08.2018)

(71) Applicants: BOE TECHNOLOGY GROUP CO., LTD. [CN/CN]; No. 10 Jiuxianqiao Rd, Chaoyang District, Beijing 100015 (CN). HEFEI BOE JOINT TECHNOLOGY CO., LTD. [CN/CN]; Block 15 Group-A Zone-E of Indus-

trial Park in Hefei New Station, Xinzhan District, Hefei, Anhui 230012 (CN).

- (72) Inventors: FENG, Xuehuan; No.9 Dize Rd., BDA, Beijing 100176 (CN). LI, Yongqian; No.9 Dize Rd., BDA, Beijing 100176 (CN). ZHANG, Xing; No.9 Dize Rd., BDA, Beijing 100176 (CN).

- (74) Agent: TEE&HOWE INTELLECTUAL PROPERTY ATTORNEYS; Yuan CHEN, 10th Floor, Tower D, Minsheng Financial Center, 28 Jianguomennei Avenue, Dongcheng District, Beijing 100005 (CN).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP,

(54) Title: SHIFT-REGISTER UNIT, GATE-DRIVING CIRCUIT, DISPLAY APPARATUS, AND DRIVING METHOD

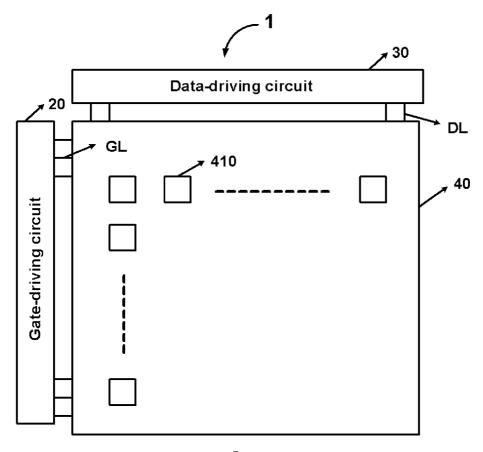

FIG. 1

(57) Abstract: A shift-register unit (10) includes a first sub-unit (100) including a first input circuit (110) coupled via a first node (Ql) to a first output circuit (120). The first input circuit (110) is configured to control a voltage level of the first node (Ql) in response to a first input signal (STU1) and the first output circuit (120) is configured to output a shift-register signal (CR) and a first output signal (OUT1) in response to the voltage level of the first node (Ql). Additionally, the shift-register unit (10) includes a second sub-unit (200) including a second input circuit (210) coupled via a second node (Q2) to a second output circuit (220). The second input circuit (210) is configured to control a voltage level of the second node (Q2) in response to the first input signal (STU1) and the second output circuit (220) is configured to output a second output signal (OUT2) in response to the voltage level of the second node (Q2).

##

KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

### **Published:**

— with international search report (Art. 21(3))

# SHIFT-REGISTER UNIT, GATE-DRIVING CIRCUIT, DISPLAY APPARATUS, AND DRIVING METHOD

## CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application claims priority to Chinese Patent Application No. 201810966800.7, August 23, 2018, the contents of which are incorporated by reference in the entirety.

## TECHNICAL FIELD

[0002] The present invention relates to display technology, more particularly, to a shift-register unit, a gate-driving circuit, a display apparatus, and driving method.

### **BACKGROUND**

[0003] In a display panel, especially for one based on Organic Light-Emitting Diode (OLED), the driving circuit is typically integrated in a Gate Integrated Circuit (Gate IC). When designing a chip of the Gate IC, the cost of the chip is mainly depended on the area of the chip. Existing OLED gate-driving circuit includes three sub-circuits, i.e., a sense unit circuit, a scan unit circuit, and a connection circuit or a gate circuit for outputting signals from both the sense unit circuit and the scan unit circuit, making the Gate IC to be a very complex circuit structure and hard to meet more and more stringent requirement to produce a high resolution OLED display panel with a narrow frame boarder. Therefore, an improved circuitry design for the shift-register unit to form a gate-driving circuit of the display panel is desired.

## **SUMMARY**

[0004] In an aspect, the present disclosure provides a shift-register unit. The shift-register unit includes a first sub-unit including a first input circuit coupled via a first node to a first output circuit. The first input circuit is configured to control a voltage level of the first node in response to a first input signal and the first output circuit is configured to output a shift-register signal and a first output signal in response to the voltage level of the first node. The shift-register circuit further includes a second sub-unit including a second input circuit

coupled via a second node to a second output circuit. The second input circuit is configured to control a voltage level of the second node in response to the first input signal and the second output circuit is configured to output a second output signal in response to the voltage level of the second node.

[0005] Optionally, the shift-register unit further includes a blank-input sub-unit coupled to the first node and the second node and configured to receive a select-control signal to control respective voltage levels of the first node and the second node.

[0006] Optionally, the blank-input sub-unit includes a common-input circuit, a first transport circuit, and a second transport circuit. The common-input circuit is configured to control a voltage level of a third node in response to the select-control signal and to control a voltage level of a fourth node. The first transport circuit is coupled to the first node and the fourth node, and is configured to control the voltage level of the first node in response to the voltage level of the fourth node or a first transport signal. The second transport circuit is coupled to the second node and the fourth node, and is configured to control the voltage level of the second node in response to the voltage level of the fourth node or a second transport signal.

[0007] Optionally, the common-input circuit further includes a select-control circuit and a third input circuit. The select-control circuit is configured to use a second input signal to control the voltage level of the third node in response to the select-control signal, and to maintain the voltage level of the third node. The third input circuit is configured to control the voltage level of the fourth node in response to the voltage level of the third node.

**[0008]** Optionally, the select-control circuit includes a first transistor and a first capacitor. The first transistor has a gate terminal configured to receive the select-control signal, a first terminal configured to receive the second input signal, and a second terminal coupled to the third node. The first capacitor has a first terminal coupled to the third node.

[0009] Optionally, the third input circuit includes a second transistor having a gate coupled to the third node, a first terminal configured to receive a first clock signal, and a second terminal coupled to the fourth node.

[0010] Optionally, the first transport circuit includes a third transistor and the second transport circuit includes a fourth transistor. The third transistor has a gate terminal coupled

the fourth node, and a first terminal configured to receive a first voltage, and a second terminal coupled to the first node. The fourth transistor has a gate terminal coupled to the fourth node, a first terminal configured to receive the first voltage, and a second terminal coupled to the second node.

[0011] Optionally, the first input circuit includes a fifth transistor and the first output circuit includes a sixth transistor, a seventh transistor, and a second capacitor. The fifth transistor has a gate terminal configured to receive the first input signal, a first terminal configured to receive a first voltage, and a second terminal coupled to the first node. The sixth transistor has a gate terminal coupled to the first node, a first terminal configured to receive a second clock signal as a shift-register signal, and a second terminal configured to output the shift-register signal. The seventh transistor has a gate terminal coupled to the first node, a first terminal configured to receive a third clock signal as the first output signal, and a second terminal configured to output the first output signal. The second capacitor has a first terminal coupled to the first node and a second terminal coupled to the second terminal of the seventh transistor.

[0012] Optionally, the second input circuit includes an eighth transistor and the second output circuit includes a ninth transistor and a third capacitor. The eighth transistor has a gate terminal configured to receive the first input signal, a first terminal configured to receive the first voltage, and a second terminal coupled to the second node. The ninth transistor has a fate terminal coupled to the second node, a first terminal configured to receive a fourth clock signal as the second output signal, and a second terminal configured to output the second output signal. The third capacitor has a first terminal coupled to the second node and a second terminal coupled to the second terminal of the ninth transistor.

[0013] Optionally, the first sub-unit further includes a first control circuit, a first reset circuit, a second reset circuit, a shift-register output terminal, and a first output terminal. The first control circuit is configured to control a voltage level of a fifth node in response to the voltage level at the first node and a second voltage. The first reset circuit is configured to reset voltage levels at the first node, the shift-register output terminal, and the first output terminal in response to the voltage level at the fifth node. The second reset circuit is configured to reset voltage levels at the first node, the shift-register output terminal, and the first output terminal in response to a voltage level at a sixth node.

[0014] Optionally, the second sub-unit further includes a second control circuit, a third reset circuit, a fourth reset circuit, and a second output terminal. The second output terminal is configured to output the second output signal. The second control circuit is configured to control the voltage level of the sixth node in response to the voltage level at the second node and a third voltage. The third reset circuit is configured to reset voltage levels at the second node and the second output terminal in response to the voltage level of the sixth node. The fourth reset circuit is configured to reset voltage levels at the second node and the second output terminal in response to the voltage level of the fifth node.

[0015] Optionally, the blank-input sub-unit further includes a common-reset circuit coupled to the fourth node, the fifth node, and the sixth node, and is configured to reset the voltage level of the fourth node in response to the voltage level at the fifth node or the sixth node.

[0016] Optionally, the common-reset circuit includes a tenth transistor and an eleventh transistor. The tenth transistor has a gate terminal coupled to the fifth node, a first terminal coupled to the fourth node, and a second terminal configured to receive a fourth voltage. The eleventh transistor has a gate terminal coupled to the sixth node, a first terminal coupled to the fourth node, and a second terminal configured to receive the fourth voltage.

[0017] Optionally, the first control circuit includes a twelfth transistor and a thirteenth transistor. The first reset circuit includes a fourteenth transistor, a fifteenth transistor, and a sixteenth transistor. The second reset circuit includes a seventeenth transistor, an eighteenth transistor, and a nineteenth transistor. The twelfth transistor has a gate terminal and a first terminal commonly configured to receive the second voltage, and a second terminal coupled to the fifth node. The thirteenth transistor has a gate terminal coupled to the first node, a first terminal coupled to the fifth node, and a second terminal configured to receive a fourth voltage. The fourteenth transistor has a gate terminal coupled to the fifth node, a first terminal coupled to the first node, and a second terminal configured to receive the fourth voltage. The fifteenth transistor has a gate terminal coupled to the fifth node, a first terminal coupled to the shift-register output terminal, and a second terminal configured to receive the fourth voltage. The sixteenth transistor has a gate terminal coupled to the fifth node, a first terminal coupled to the first output terminal, and a second terminal configured to receive a fifth voltage. The seventeenth transistor has a gate terminal coupled to the sixth node, a first terminal coupled to the first node, and a second terminal configured to receive the fourth voltage. The eighteenth transistor has a gate terminal coupled to the sixth node, a first

terminal coupled to the shift-register output terminal, and a second terminal configured to receive the fourth voltage. The nineteenth transistor has a gate terminal coupled to the sixth node, a first terminal coupled to the first output terminal, and a second terminal configured to receive the fifth voltage.

[0018] Optionally, the second control circuit includes a twentieth transistor and a twentyfirst transistor. The third reset circuit includes a twenty-second transistor and a twenty-third transistor; and the fourth reset circuit includes a twenty-fourth transistor and a twenty-fifth transistor. The twentieth transistor has a gate terminal and a first terminal commonly configured to receive the third voltage, and a second terminal coupled to the sixth node. The twenty-first transistor has a gate terminal coupled to the second node, a first terminal coupled to the sixth node, and a second terminal configured to receive a fourth voltage. The twentysecond transistor has a gate terminal coupled to the sixth node, a first terminal coupled to the second node, and a second terminal configured to receive the fourth voltage. The twentythird transistor has a gate terminal coupled to the sixth node, a first terminal coupled to the second output terminal, and a second terminal configured to receive a fifth voltage. The twenty-fourth transistor has a gate terminal coupled to the fifth node, a first terminal coupled to the second node, and a second terminal configured to receive the fourth voltage. The twenty-fifth transistor has a gate terminal coupled to the fifth node, a first terminal coupled to the second output signal, and a second terminal configured to receive the fifth voltage.

[0019] Optionally, the first sub-unit further includes a third output terminal configured to output a third output signal. The second sub-unit further includes a fourth output terminal configured to output a fourth output signal. The first reset circuit and the second reset circuit are configured to reset a voltage level at the third output terminal. The third reset circuit and the fourth reset circuit are configured to reset a voltage level at the fourth output terminal.

[0020] Optionally, the first sub-unit further includes a third control circuit and a fourth control circuit. The third control circuit is configured to control the voltage level of the fifth node in response to the first clock signal and the fourth control circuit is configured to control the voltage level of the fifth node in response to the first input signal. The second sub-unit further includes a fifth control circuit and a sixth control circuit. The fifth control circuit is configured to control the voltage level of the sixth node in response to the first clock signal and the sixth control circuit is configured to control the voltage level of the sixth node in response to the first input signal.

[0021] Optionally, the first sub-unit further includes a fifth reset circuit and a sixth reset circuit. The fifth reset circuit is configured to reset the voltage level at the first node in response to a display-reset signal and the sixth reset circuit is configured to reset the voltage level at the first node in response to a full-scale reset signal. The second sub-unit further includes a seventh reset circuit and an eighth reset circuit. The seventh reset circuit is configured to reset the voltage level at the second node in response to the display-reset signal and the eighth reset circuit is configured to reset the voltage level at the second node in response to the full-scale reset signal.

[0022] Optionally, the shift-register unit further includes a common anti-leak circuit, a first anti-leak circuit, and a second anti-leak circuit. The common anti-leak circuit is connected to the first node and a seventh node, and configured to control a voltage level at the seventh node in response to the voltage level at the first node. The first anti-leak circuit is connected to the seventh node, the first reset circuit, the second reset circuit, the fifth reset circuit, and the sixth reset circuit, and configured to prevent the first node from leaking in response to the voltage level of the seventh node. The second anti-leak circuit is connected to the seventh node, the third reset circuit, the fourth reset circuit, the seventh reset circuit, and the eighth reset circuit, and configured to prevent the second node from leaking in response to the voltage level at the seventh node.

[0023] In another aspect, the present disclosure provides a gate-driving circuit including multiple shift-register units cascaded in series. Each of the multiple shift-register units is the shift-register unit described herein including a pair of first sub-unit in an odd stage and a second sub-unit in a next even stage respectively controlled by voltage levels of a first node and a second node. The voltage levels of the first node and the second node are respective controlled by a first transport circuit and a second transport circuit coupled commonly from a common-input circuit. A first sub-unit of a respective shift-register unit outputs a shift-register signal as a first input signal to drive both the first sub-unit and the second sub-unit in a next shift-register unit or as a display-reset signal to drive both the first sub-unit and the second sub-unit in one before a previous shift-register unit.

[0024] In yet another aspect, the present disclosure provides a display apparatus including a gate-driving circuit described herein and multiple subpixel units arranged in an array. A first output signal and a second output signal respectively outputted from a first output circuit and

a second output circuit of a respective one shift-register unit in the gate-driving circuit are provided respectively to subpixel units in different rows of the array.

[0025] In still another aspect, the present disclosure provides a method of driving the shift-register unit described herein. The method includes a step of inputting a first input signal to a first input circuit of a first sub-unit of the shift-register unit and a second input circuit of a second sub-unit of the same shift-register unit. The method further includes a step of driving the first sub-unit to control a voltage level of a first node of the first sub-unit based on the first input signal. The method also includes a step of coupling a first output circuit to the first node. Additionally, the method includes driving the first sub-unit to control the first output circuit to output a shift-register signal and a first output signal in response to the voltage level of the first node and driving the second sub-unit to control a voltage level of a second node of the second sub-unit based on the first input signal. Furthermore, the method includes coupling a second output circuit to the second node. Moreover, the method includes a step of driving the second sub-unit to control the second output circuit to output a second output signal in response to the voltage level of the second node.

[0026] Optionally, the step of driving the first sub-unit to control a voltage level of the first node includes employing a blank-input circuit having a common input circuit to receive a second input signal and a first clock signal to determine a voltage level of a third node and a fourth node and a first transport circuit to control the voltage level of the first node in response to the voltage level of the fourth node. The step of driving the second sub-unit to control a voltage level of the second node includes employing the blank-input circuit further having a second transport circuit to control the voltage level of the second node in response to the voltage level of the fourth node.

[0027] Optionally, the step of driving the first sub-unit to control the first output circuit includes using at least a first reset circuit and a second reset circuit to reset voltage levels at a shift-register output terminal and a first output terminal, and controlling a second clock signal outputted as a shift-register signal and a third clock signal outputted as the first output signal in response to the voltage of the first node. The step of driving the second sub-unit to control the second output circuit includes using at least a third reset circuit to reset a voltage level at a second output terminal, and controlling a fourth clock signal outputted as the second output signal in response to the voltage level of the second node.

### BRIEF DESCRIPTION OF THE FIGURES

- [0028] The following drawings are merely examples for illustrative purposes according to various disclosed embodiments and are not intended to limit the scope of the present invention.

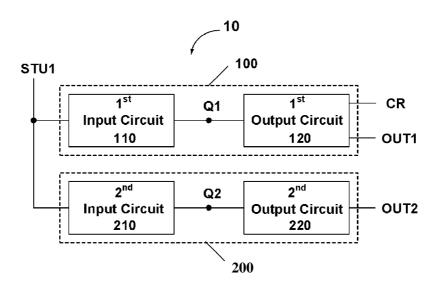

- [0029] FIG. 1 is a block diagram of a shift-register unit according to an embodiment of the present disclosure.

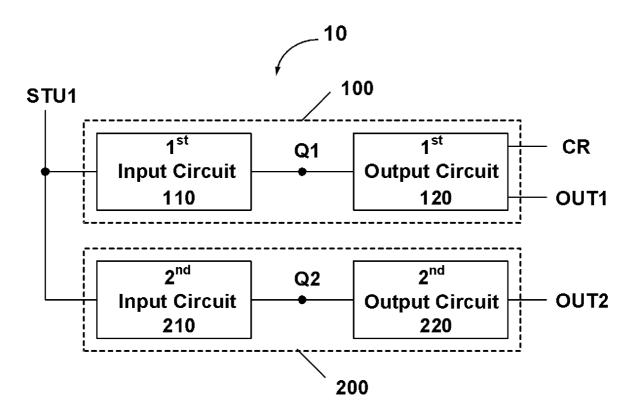

- [0030] FIG. 2 is a block diagram of a shift-register unit according to another embodiment of the present disclosure.

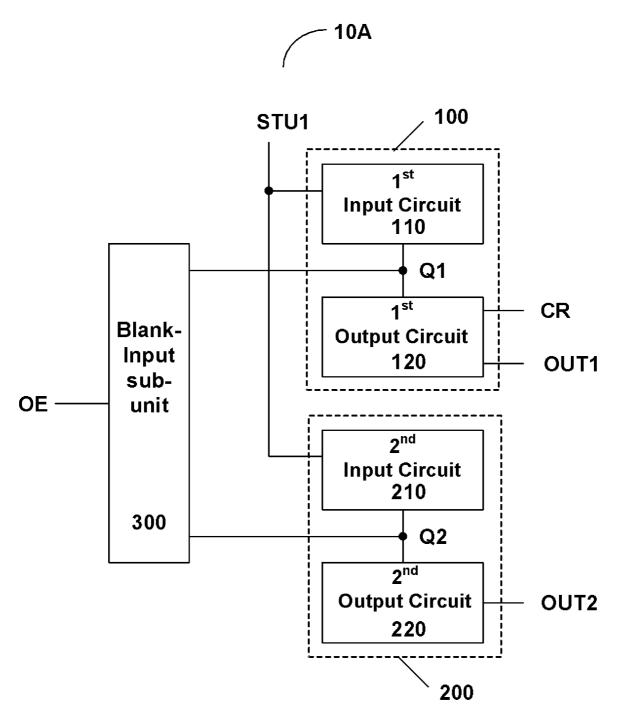

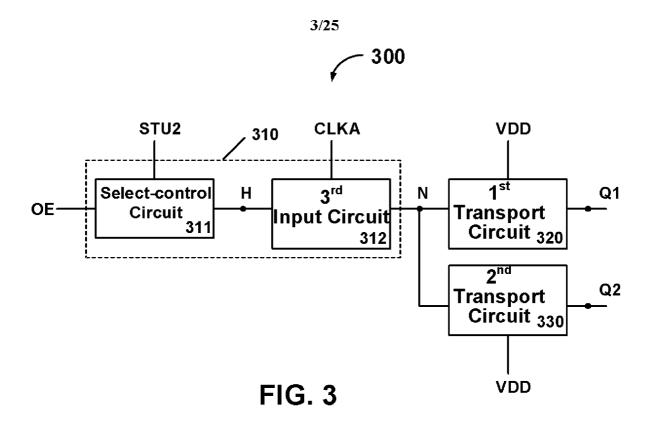

- [0031] FIG. 3 is a block diagram of a blank-input sub-unit of the shift-register unit according to an embodiment of the present disclosure.

- [0032] FIG. 4 is a circuit diagram of a blank-input sub-unit according to an embodiment of the present disclosure.

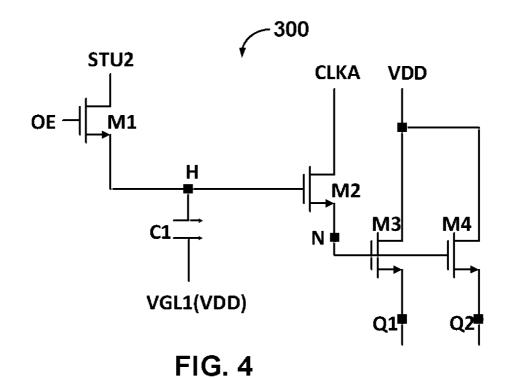

- [0033] FIG. 5A through FIG. 5F are circuit diagrams of blank-input sub-units according to an embodiment of the present disclosure.

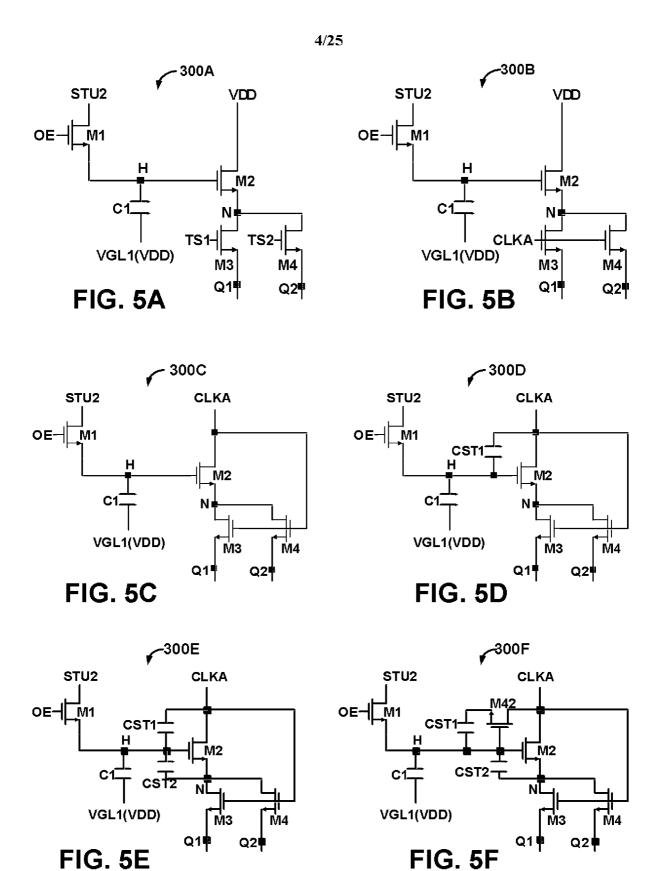

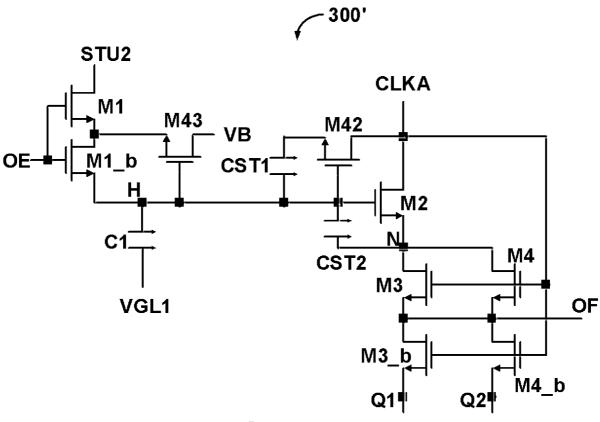

- [0034] FIG. 6 is a circuit diagram of a blank-input sub-unit including an anti-leak structure according to an embodiment of the present disclosure.

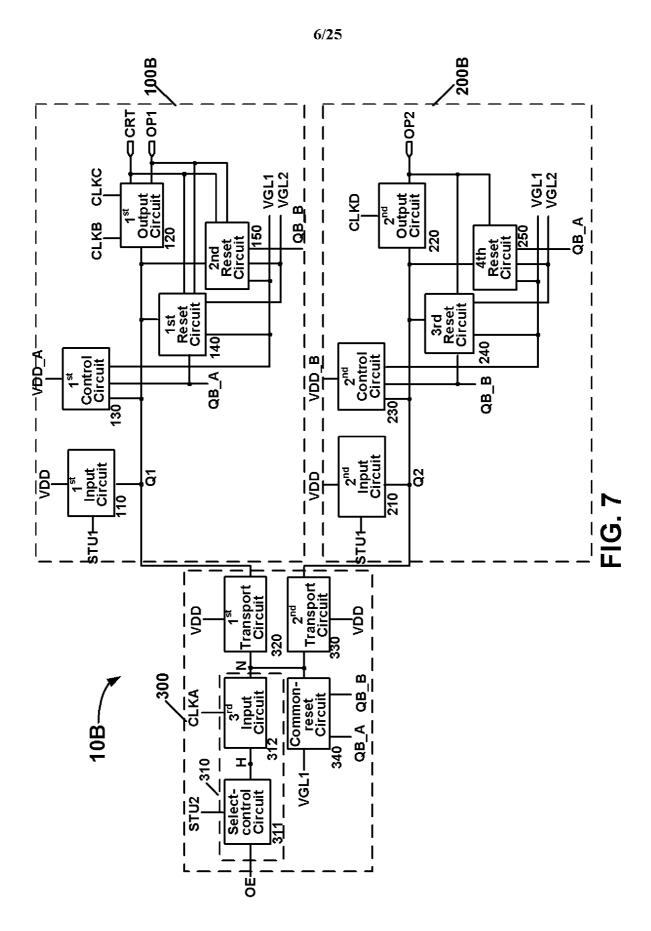

- [0035] FIG. 7 is a block diagram of a shift-register unit according to yet another embodiment of the present disclosure.

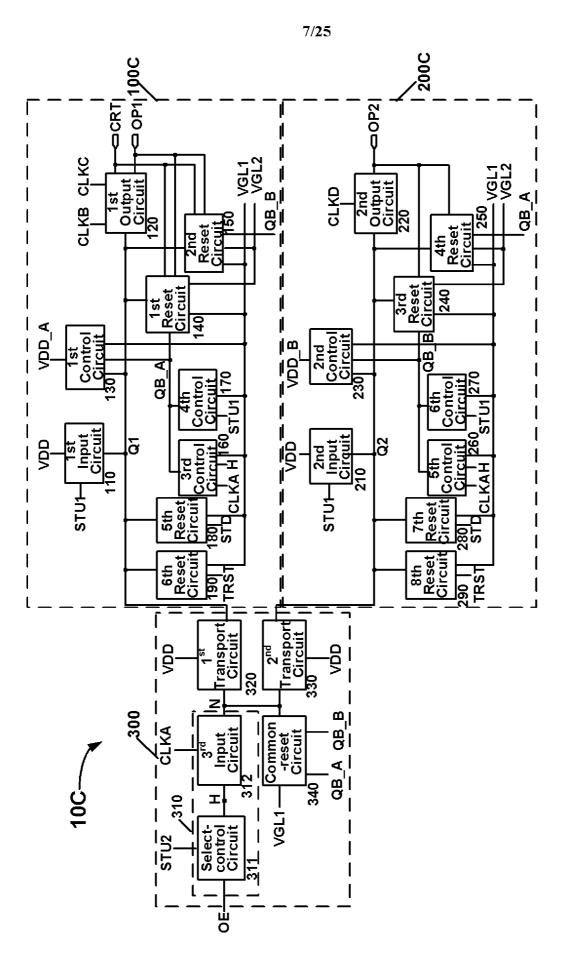

- [0036] FIG. 8 is a block diagram of a shift-register unit according to still another embodiment of the present disclosure.

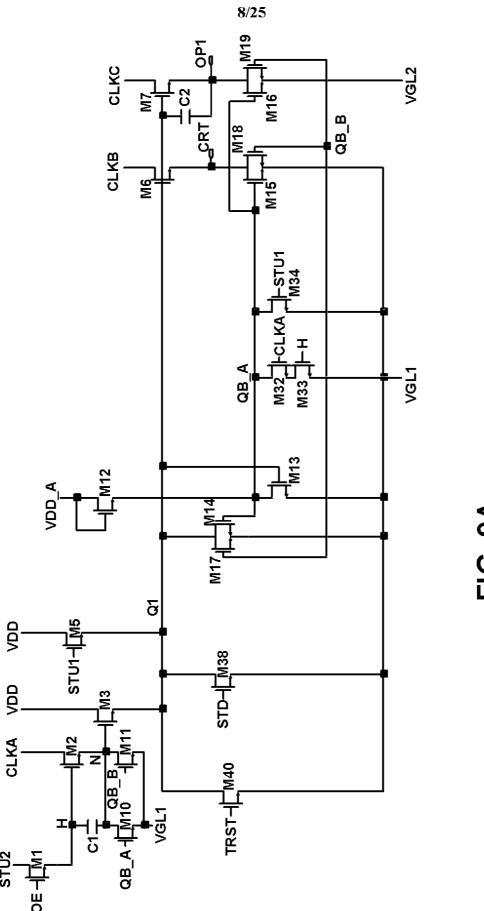

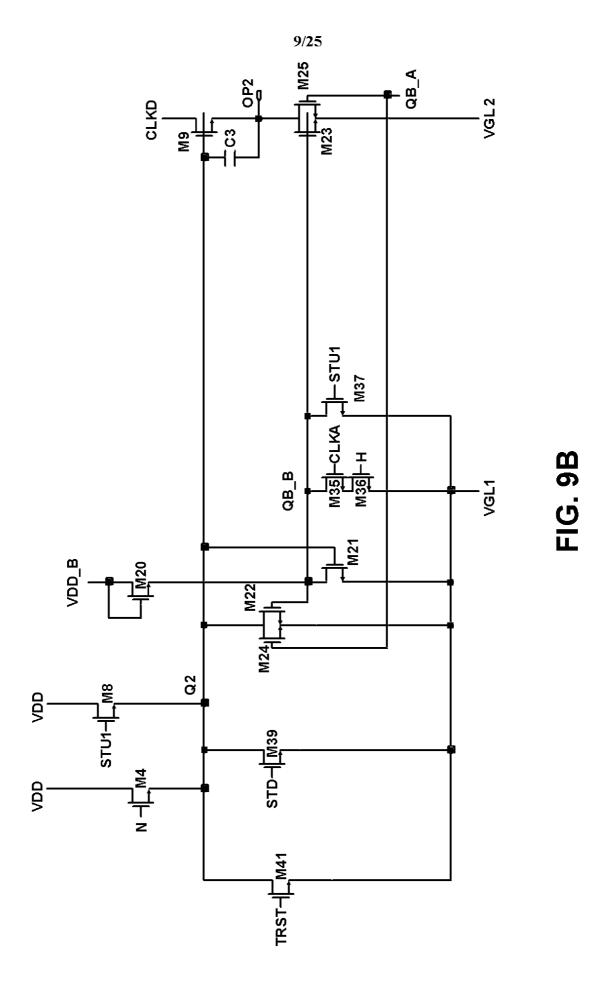

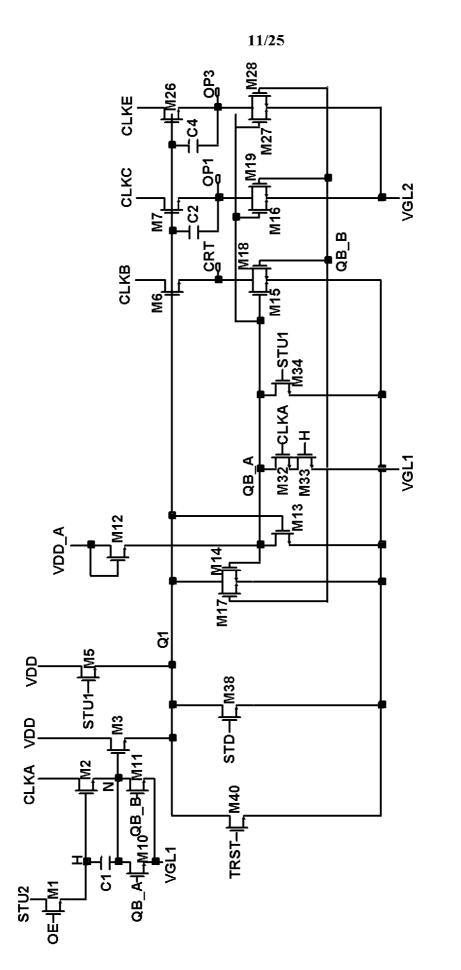

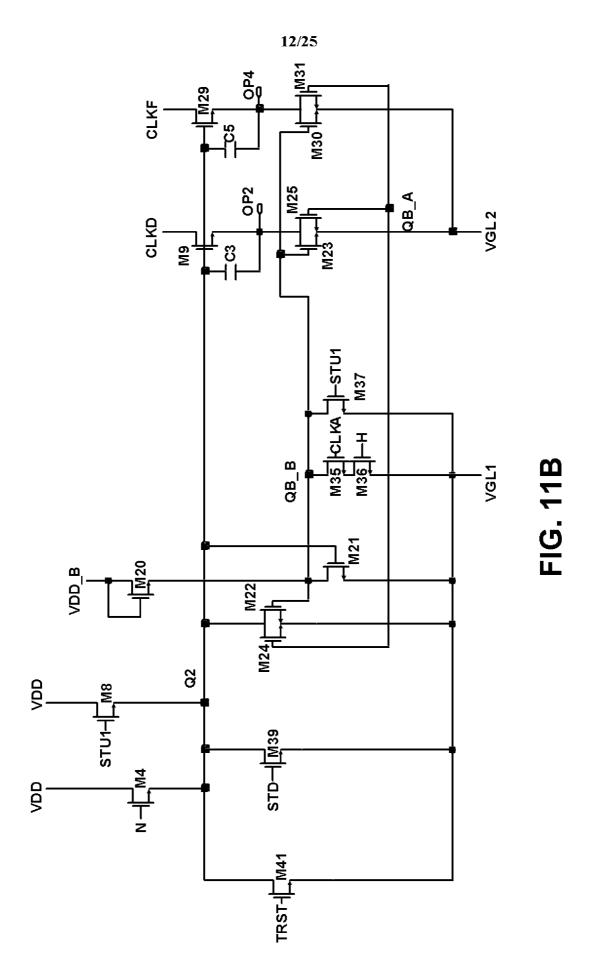

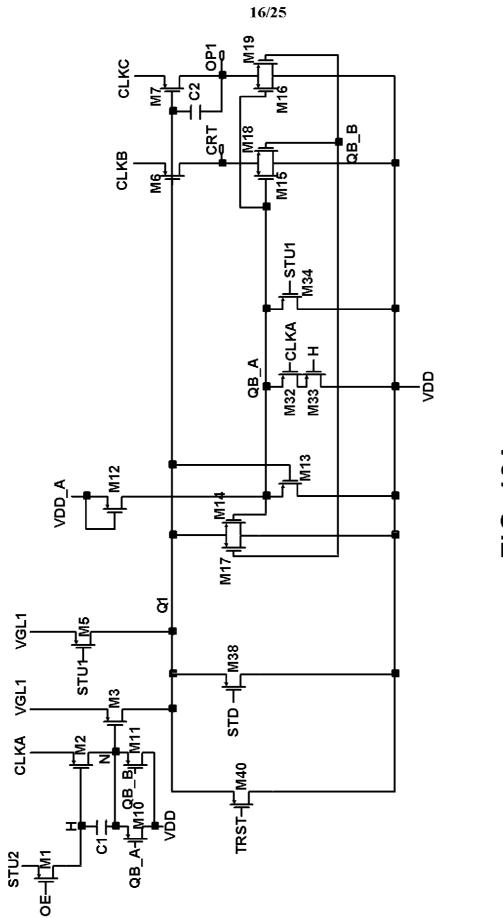

- [0037] FIG. 9A and FIG. 9B are circuit diagrams of respective a first sub-unit and a second sub-unit of a shift-register unit according to an embodiment of the present disclosure.

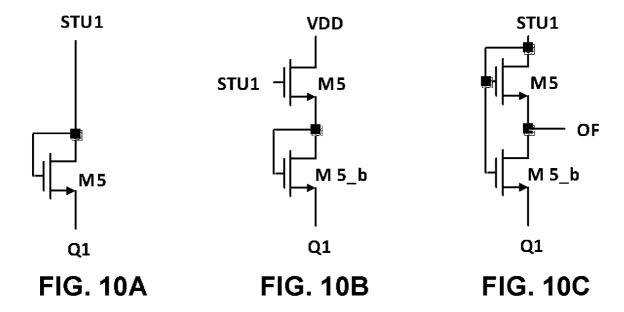

- [0038] FIG. 10A through FIG. 10C are circuit diagrams of three kinds of a first input circuit of a shift-register unit according to an embodiment of the present disclosure.

- [0039] FIG. 11A and FIG. 11B are circuit diagrams of respective a first sub-unit and a second sub-unit of a shift-register unit according to another embodiment of the present disclosure.

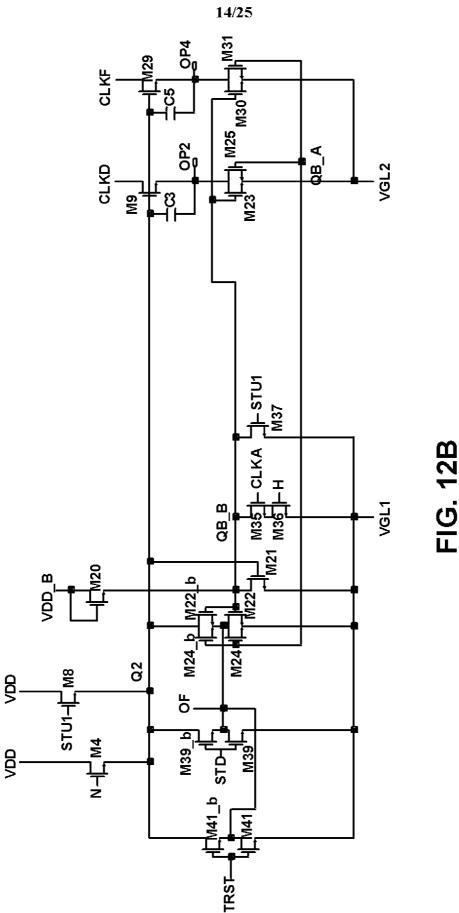

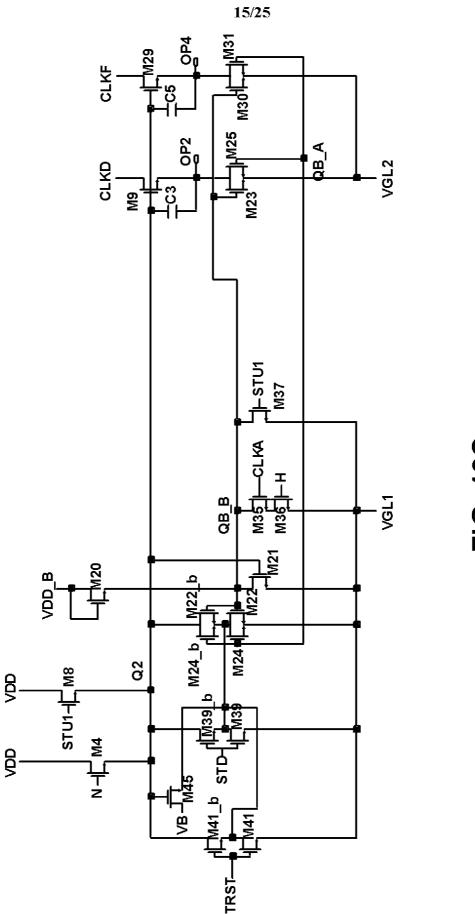

[0040] FIG. 12A through FIG. 12C are circuit diagrams of a shift-register unit with antileak circuitry structures according to some embodiments of the present disclosure.

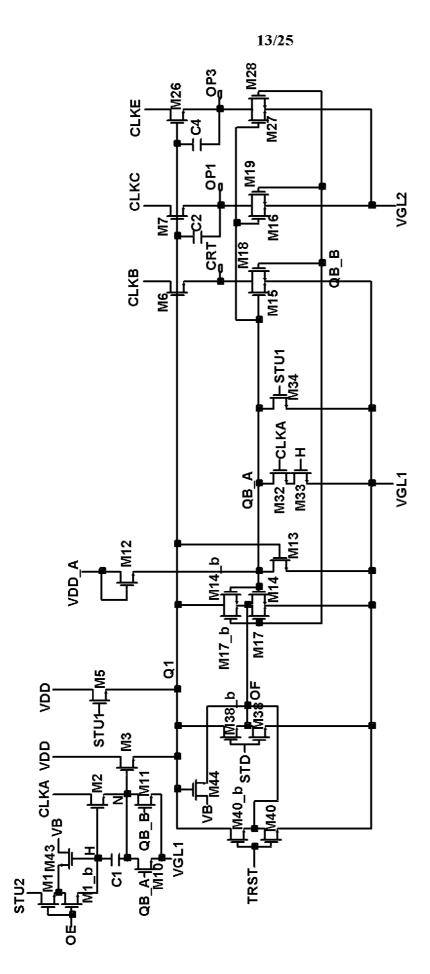

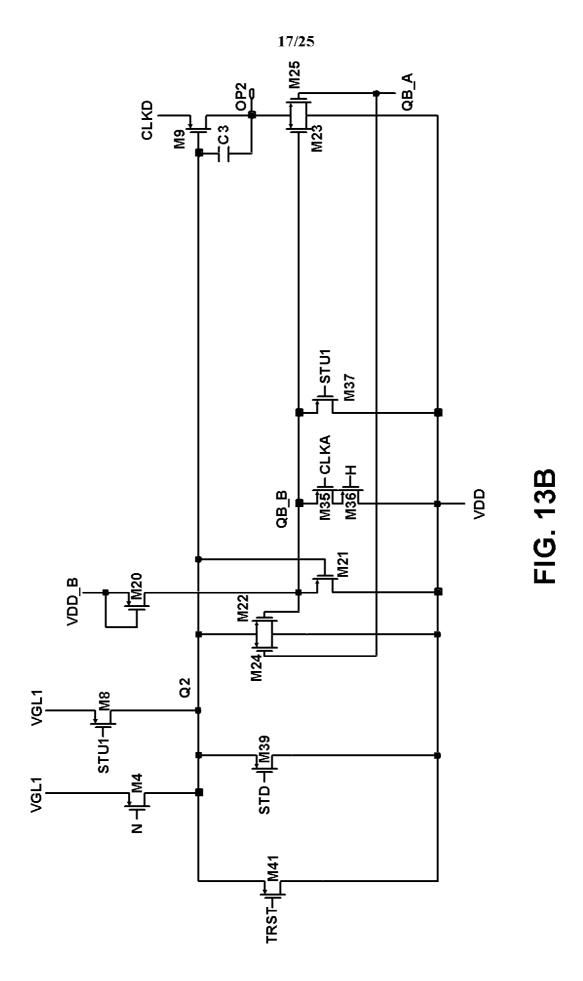

- [0041] FIG. 13A and FIG. 13B are circuit diagrams of respective a first sub-unit and a second sub-unit of a shift-register unit according to yet another embodiment of the present disclosure.

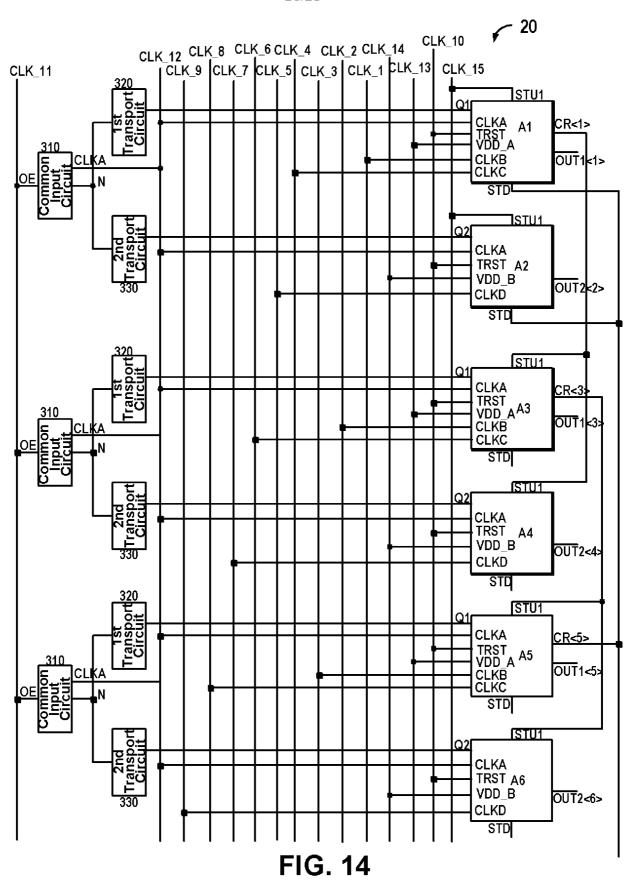

- [0042] FIG. 14 is a schematic diagram of a gate-driving circuit according to an embodiment of the present disclosure.

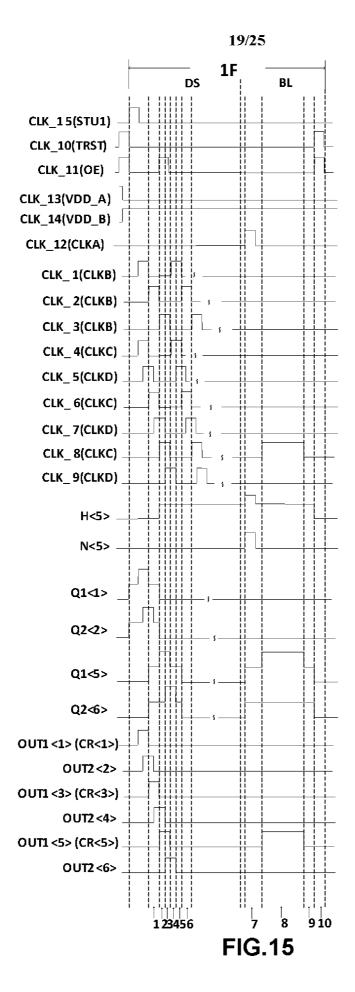

- [0043] FIG. 15 is a timing diagram of operating a gate-driving circuit of FIG. 14 according to an embodiment of the present disclosure.

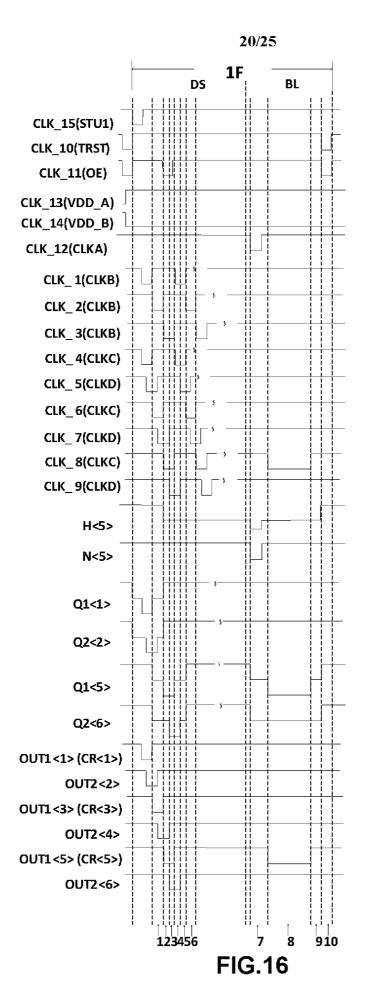

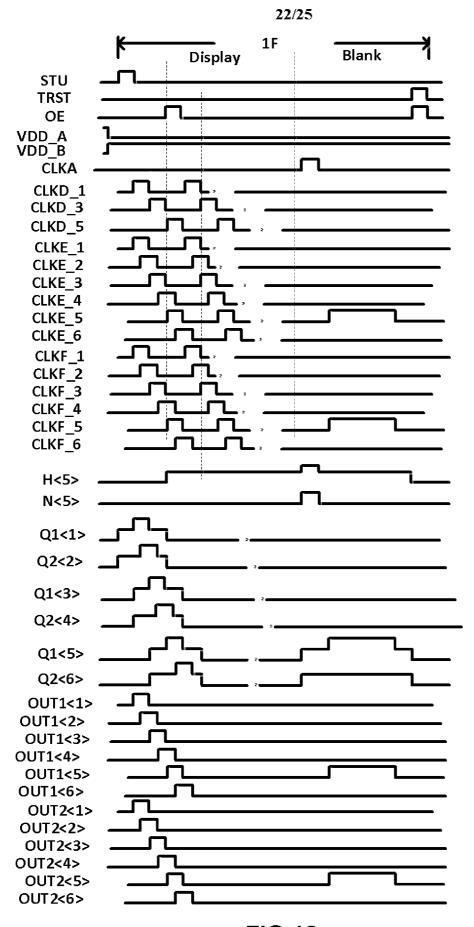

- [0044] FIG. 16 is a timing diagram of operating a gate-driving circuit of FIG. 14 according to another embodiment of the present disclosure.

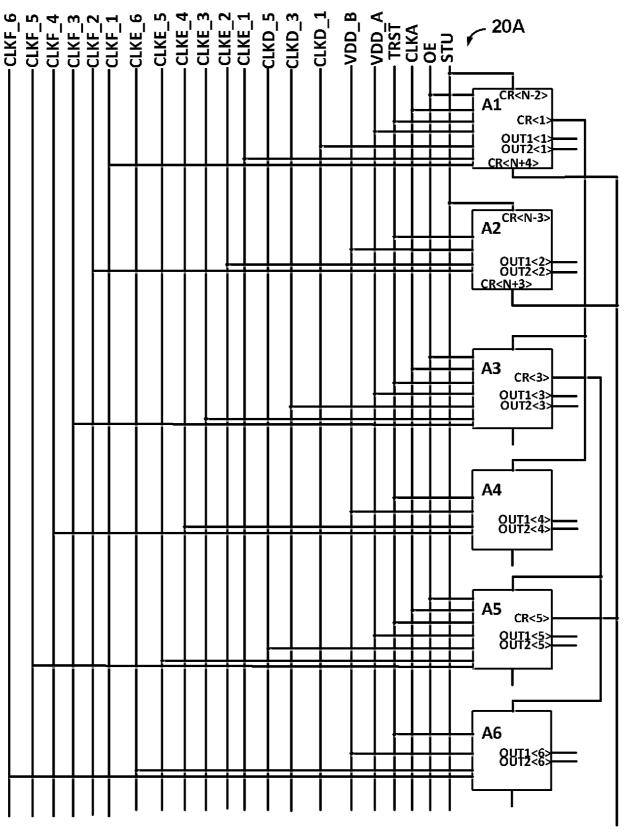

- [0045] FIG. 17 is a schematic diagram of a gate-driving cirucit according to another embodiment of the present disclosure.

- [0046] FIG. 18 is a timing diagram of operating a gate-driving circuit of FIG. 17 according to an embodiment of the present disclosure.

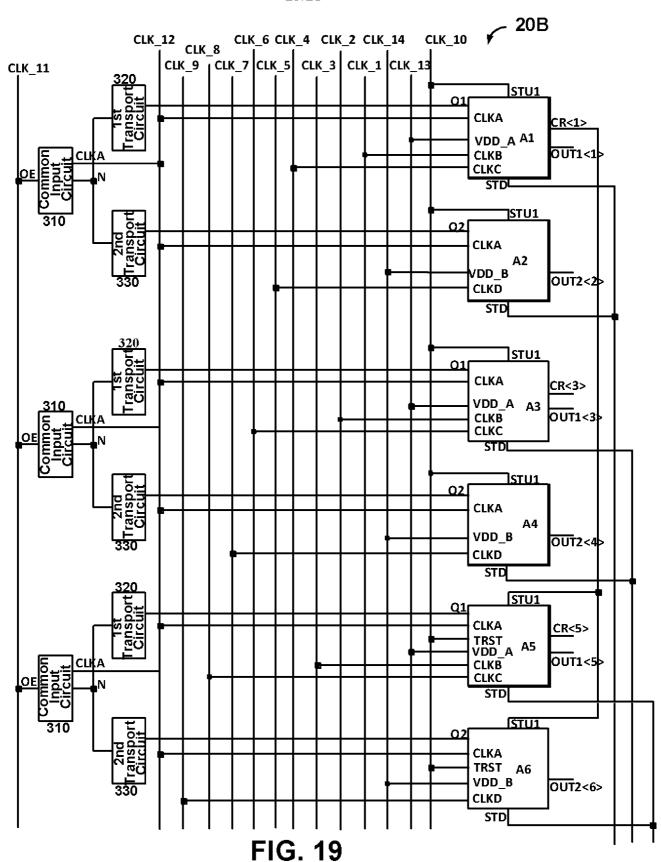

- [0047] FIG. 19 is a schematic diagram of a gate-driving circuit according to another embodiment of the present disclosure.

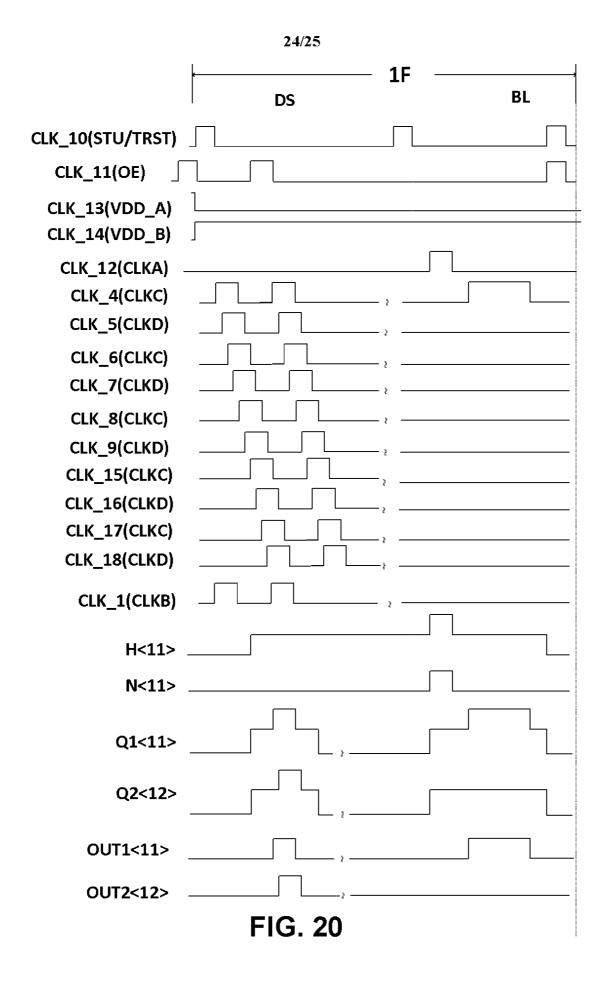

- [0048] FIG. 20 is a timing diagram of operating a gate-driving circuit of FIG. 19 according to an embodiment of the present disclosure.

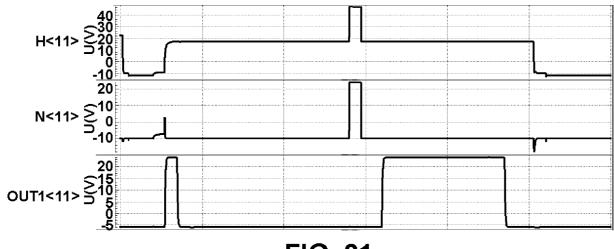

- [0049] FIG. 21 is a signal diagram for simulated voltage signals at circuit nodes and output terminal of a gate-driving circuit according to an embodiment of the present disclosure.

- [0050] FIG. 22 is a schematic diagram of a display apparatus according to an embodiment of the present disclosure.

## DETAILED DESCRIPTION

[0051] The disclosure will now be described more specifically with reference to the following embodiments. It is to be noted that the following descriptions of some

embodiments are presented herein for purpose of illustration and description only. It is not intended to be exhaustive or to be limited to the precise form disclosed.

[0052] In the following detailed description, numerous specific details are set forth in order to provide a more thorough understanding of the present disclosure. However, it will be apparent to one skilled in the art that the present disclosure may be practiced without necessarily being limited to these specific details. In other instances, well-known structures devices, and circuits are shown in block diagram form, rather than in detail, in order to avoid obscuring the present invention.

[0053] The reader's attention is directed to all papers and documents which are filed concurrently with this specification and which are open to public inspection with this specification, and the contents of all such papers and documents are incorporated herein by reference. All the features disclosed in this specification, (including any accompanying claims, abstract, and drawings) may be replaced by alternative features serving the same, equivalent or similar purpose, unless expressly stated otherwise. Thus, unless expressly stated otherwise, each feature disclosed is one example only of a generic series of equivalent or similar features.

[0054] Furthermore, any element in a claim that does not explicitly state "means for" performing a specified function, or "step for" performing a specific function, is not to be interpreted as a "means" or "step" clause as specified in 35 U.S.C. Section 112, Paragraph 6. In particular, the use of "step of" or "act of" in the Claims herein is not intended to invoke the provisions of 35 U.S.C. 112, Paragraph 6.

[0055] Please note, the words "first," "second," and similar terms used in the present disclosure do not denote any order, quantity, or importance, but are used to distinguish different components. Similarly, the words "comprising" or "comprising" or "comprising" or "an" or "an" The words "coupled" or "connected" and the like are not limited to physical or mechanical connections, but may include electrical connections, whether direct or indirect. "Upper", "lower", "left", "right", etc. are only used to indicate the relative positional relationship, and when the absolute position of the object to be described is changed, the relative positional relationship may also change accordingly.

[0056] The words "a", "an", "the" and "the" In general, the terms "comprising" and "comprising" are intended to include only the steps and elements that are specifically

identified, and the steps and elements do not constitute an exclusive list, and the method or device may also include other steps or elements.

[0057] When compensating the sub-pixel unit in the OLED display panel, in addition to setting the pixel compensation circuit for internal compensation in the sub-pixel unit, external compensation can also be performed by setting the sensing transistor. When external compensation is performed, the gate driving circuit composed of the shift register unit needs to supply respective driving signals for the scanning transistor and the sensing transistor to the sub-pixel units in the display panel. For example, in a display period of one cycle of displaying one frame of image, a scanning driving signal for the scanning transistor is provided; while in a blank period of the cycle, a sensing driving signal for the sensing transistor is provided.

[0058] In an external compensation method, the sensing driving signals output by the gate-driving circuit are sequentially scanned line by line. For example, a sensing driving signal is outputted to a first row of sub-pixel units in the display panel during a blanking period of a cycle of displaying a first frame, and another sensing driving signal is outputted to a second row of sub-pixel units in the display panel during a blanking period of a cycle of displaying a second frame, and so on. Thus, outputting the sensing driving signal to corresponding one row of the sub-pixel units per frame leads to completion of the line-by-line sequential compensation of the display panel.

[0059] Accordingly, the present disclosure provides, *inter alia*, a shift-register unit configured to be cascaded in series to form a gate-driving circuit that can output a scanning driving signal during a display period of one cycle of displaying one frame and output a sensing driving signal during a blank period of the cycle, a display apparatus, and a driving method that substantially obviate one or more of the problems due to limitations and disadvantages of the related art. In one aspect, the present disclosure provides a shift-register unit suitable for being adopted in a display apparatus with reduced frame size and increased pixels per inch (PPI) of the panel and allowing random compensation to avoid brightness non-uniformity during display operation.

[0060] For the purpose of explanation, definition of "one frame", "per frame" or "a certain frame" includes a display period and a blank period which are sequentially performed. For example, the gate-driving circuit outputs a gate-driving signal during the display period, and

the gate-driving signal can be used to drive the display panel by scanning from a first row to a last row to complete a display of one frame. In the blanking period, the gate-driving circuit outputs a sense-driving signal, and the sense-driving signal can be used to drive sensing transistors in a row of sub-pixel units in the display panel to complete external compensation of the row of sub-pixel units.

**[0061]** FIG. 1 is a block diagram of a shift-register unit according to an embodiment of the present disclosure. Referring to FIG. 1, the shift-register unit 10 includes a first sub-unit 100 and a second sub-unit 200. Multiple such shift-register units 10 can be cascaded to form a gate-driving circuit according to some embodiments of the present disclosure. The gate-driving circuit can be applied in a display apparatus to provide scanning signals to display one frame of image therein during a display operation.

[0062] The first sub-unit 100 includes a first input circuit 110 and a first output circuit 120 coupled to each other via a first node Ql. The first input circuit 110 is configured to control a voltage level at the first node Ql in response to a first input signal STU1 received. For example, the first input circuit 110 is able to charge the first node Ql. Optionally, the first input circuit 110 is configured to receive the first input signal STU1 and a first voltage VDD. Optionally, the first input circuit 110 is turned to a conduction state in response to the first input signal STU1 so that the first voltage VDD is utilized for charging the first node Ql. Optionally, the voltage level at the first node Ql is charged to the level of the first voltage VDD at least within 10% of error. Optionally, the first voltage VDD is set to be a high voltage provided from a power supply.

[0063] The first output circuit 120 is configured to output a shift-register signal CR and a first output signal OUT1 in response to the voltage level at the first node Ql. For example, the first output circuit 120 can be configured to receive a second clock signal CLKB and a third clock signal CLKC. The first output circuit 120 is turned to a conduction state in response to the voltage level at the first node Ql so that the second clock signal CLKB cab be outputted as the shift-register signal CR and the third clock signal CLKC can be outputted as the first output signal OUT1.

[0064] Optionally, in a display period of one cycle of displaying one frame of image or simply one frame, the shift-register signal CR outputted from the first output circuit 120 may be provided as a first input signal STU 1 to other shift-register unit (in the gate-driving circuit)

to complete a line-by-line shift scanning during display operation. The first output signal OUT1 outputted from the first output circuit 120 can drive one row of subpixel units of a display panel to perform display scanning. Optionally, in a blank period of one frame, the first output signal OUT1 outputted from the first output circuit 120 can be used to drive sensing transistors in one row of subpixel units of the display panel to complete external compensations to the one row of subpixel units.

[0065] Optionally, during the display period of the frame, the shift-register signal outputted from the first output circuitl20 can have a same, or a different, waveform compared with the first output signal OUT1 outputted from the same first output circuit 120.

[0066] Referring to FIG. 1, the second sub-unit 200 includes a second input circuit 210 and a second output circuit 220 coupled to each other via a second node Q2. The second input circuit 210 is configured to control a voltage level at the second node Q2 in response to the first input signal STU1. For example, the second input circuit 210 is to charge the second node Q2. Optionally, the second input circuit 210 can be configured to receive the first input signal STU11 and the first voltage VDD and is turned on by the first input signal STU1 so that it uses the first voltage VDD to charge the second node Q2.

[0067] Optionally, the second output circuit 220 is configured to output a second output signal OUT2 in response to the voltage level at the second node Q2. For example, the second output circuit 220 is configured to receive a fourth clock signal CLKD. The second output circuit 220 is then turned on by the voltage level at the second node Q2 so that it can output the fourth clock signal CLKD as a second output signal OUT2.

**[0068]** In a display period of one frame, the second output circuit 220 outputs the second output signal OUT2 to drive a row of subpixel units of a display panel to perform display scanning. In a blank period of one frame, the second output circuit 220 outputs the second output signal OUT2 to drive sensing transistors in one row of subpixel units of the display panel to complete an external compensation for the one row of subpixel units.

**[0069]** When multiple such shift-register units 10 are cascaded in series to form a gate-driving circuit, some shift-register units 10 can be connected with a clock signal line so as to receive the first input signal STU 1 provided with the clock signal line. Optionally, some shift-register units 10 can receive the shift-register signal CR outputted from other stages of shift-register units 10 in the same gate-driving circuit as the first input signal STU1.

**[0070]** Optionally, controlling the level of a node (e.g., first node Ql, second node Q2, etc.), including charging the node to raise the voltage level of the node, or discharging the node to lower the voltage level of the node. Optionally, a capacitor can be electrically connected to the node, and charging the node means charging the capacitor electrically connected to the node. Similarly, discharging the node means discharging the capacitor electrically connected to the node. Discharge. The capacitor can maintain the high or low level of the node.

[0071] The shift-register unit 10 of the present disclosure can perform charging to multiple sub-units (such as the first sub-unit 100 and the second sub-unit 200) at the same time. FIG. 1 only shows two sub-units in the shift-register unit. Optionally, the shift-register unit can include three, or four, or more sub-units in similar circuitry structures depending on actual setup in different applications. Only one of the multiple sub-units (e.g., the first sub-unit 100) needs to output a shift-register signal at a time, while others of the multiple sub-units (e.g., the second sub-unit 200) need not to output the shift-register signal. Therefore, the number of clock signal lines and transistors in the gate-driving circuit can be saved, reducing border frame size of a display apparatus that adopts the shift-register units 10 thereby enhancing PPI of the display apparatus.

[0072] FIG. 2 is a block diagram of a shift-register unit according to another embodiment of the present disclosure. Referring to FIG. 2, the shift-register unit 10A includes a blank-input sub-unit 300 respectively coupled to the first sub-unit 100 via the first node Q1 and coupled to the second sub-unit 200 via the second node Q2 and configured to receive a select-control signal OE. The blank-input sub-unit 300 is configured to control the voltage levels of the first node Q1 and the second node Q2 in response to the select-control signal OE. For example, the blank-input sub-unit 300 is configured to charge respectively the first node Q1 and the second node Q2.

[0073] Optionally, in a display period of one frame, the blank-input sub-unit 300 can charge the first node Q1 and also can charge the second node Q2. The first output circuit 120 then can output a first output signal OUT1 in response to the voltage level charged to the first node Q1, or the second output circuit 220 then can output a second output signal OUT2 in response to the voltage level charged to the second node Q2. The first output signal OUT1 or the second output signal OUT2 can be used to drive sensing transistors in one row of subpixel units of a display panel to complete an external compensation to the one row of subpixel units.

[0074] FIG. 3 is a block diagram of a blank-input sub-unit of the shift-register unit according to an embodiment of the present disclosure. In an embodiment, referring to FIG. 3, the blank-input sub-unit 300 includes a common-input circuit 310 coupled to a first transport circuit 320 and a second transport circuit 330 via a fourth node N. The common-input circuit 310 further includes a select-control circuit 311 coupled via a third node H to a third input circuit 312. The common-input circuit 310 is configured to control a voltage level of the third node H in response to the select-control signal OE and further to control a voltage level of the fourth node N. The select-control circuit 311 is configured to use a second input signal STU2 to charge the third node H in response to the select-control signal OE and to maintain the voltage level at the third node H. For example in a display period of a frame, the select-control circuit 311 is turned on by the select-control signal OE so that the second input signal STU2 can be used to charge the third node H. The voltage level (e.g., a high voltage level) at the third node H can be maintained throughout the display period until a blank period following the display period of the same frame.

[0075] When multiple shift-register units 10A cascaded in a multi-stage series to form a gate-driving circuit, one-stage of shift-register unit 10A can receive a shift-register signal CR outputted from other stages of shift-register units 10A as the second input signal STU2. For example, when one stage of shift-register unit 10A is selected to output a driving signal in a blank period of one frame, it is preferred to provide both the select-control signal OE and the second input signal STU2 with a same timing-waveform to the stage of shift-register unit 10A so that the select-control circuit 311 in the stage of shift-register unit 10A can be turned on and to perform corresponding charging operation described above.

[0076] Additionally, the third input circuit 312 is configured to control a voltage level at the fourth node N in response to the voltage level charged to the third node H. Optionally, the third input circuit 312 is configured to receive a first clock signal CLKA. As the third input circuit 312 is in conduction state controlled by the voltage level at the third node H, the first clock signal CLKA can be passed to the fourth node N to control the voltage level of the fourth node N. For example, in a blank period of one frame, when the first clock signal CLKA is provided with a high voltage level, the third input circuit 312 can pass the high voltage level to the fourth node N to make the fourth node N to a high voltage level.

[0077] Referring to FIG. 3, the first transport circuit 320 is connected to the first node Q1 and the fourth node N and is configured to control a voltage level at the first node Q1 in

response to the voltage level of the fourth node N or a first transport signal TS1 (not shown) received by the first transport circuit 320. In some embodiments, the first transport circuit 320 can receive the first voltage VDD at a high voltage level. When the first transport circuit 320 is turned to a conduction state by the voltage level at the fourth node N, the high voltage level of the first voltage VDD can be used to charge the first node Ql. Optionally, the voltage level at the first node Ql is charged to the level of the first voltage VDD at least within 10% of error. In some other embodiments, the first transport circuit 320 can be turned to the conduction state by the first transport signal TS1 (not shown) to establish an electrical connection between the fourth node N and the first node Ql so that the third input circuit 312 can charge the first node Ql.

[0078] Furthermore, the second transport circuit 330 is connected to the second node Q2 and the fourth node N and is configured to control the voltage level at the second node Q2 in response to the voltage level at the fourth node N or a second transport signal TS2 (not shown) received by the second transport circuit 330. In some embodiments, the second transport circuit 330 can receive a high voltage level first voltage VDD. When the second transport circuit 330 is turned to a conduction state by the voltage level at the fourth node N, the high voltage level first voltage VDD can be used to charge the second node Q2. Optionally, the voltage level at the second node Q2 is charged to the level of the first voltage VDD at least within 10% of error. In some other embodiments, the second transport circuit 330 can also be turned to conduction state by the second transport signal TS2 (not shown) to establish an electrical connection between the fourth node N and the second node Q2 so that the third input circuit 312 can charge the second node Q2.

[0079] Optionally, the first transport signal TS1 and the second transport signal TS2 can be the same signal, e.g., a first clock signal CLKA or a first voltage VDD. Thus, the number of clock signal lines can be reduced. Optionally, the first transport signal TS1 and the second transport signal TS2 can be provided with different signals for respectively controlling the first transport circuit 320 and the second transport circuit 330. For example, when there is no need to charge the second node Q2, the second transport circuit 330 can be turned off to reduce power consumption.

[0080] Optionally, when the shift-register unit 10A includes three, or four, or more sub-units, there are needs to set three, or four, or more transport circuits to perform function of the blank-input sub-unit 300. The three, or four, or more sub-units in the shift-register unit 10A

can share one blank-input sub-unit 300 to reduce area of the shift-register unit 10A so as to reduce the border frame size of a display apparatus that adopts the shift-register unit 10A and to enhance PPI of the display apparatus. Optionally, the blank-input sub-unit 300 set in the shift-register unit 10A is to allow the shift-register unit to output a driving signal during a blank period of one frame. The "blank" is merely related to the blank period of a frame. The blank-input sub-unit 300 is not restricted to work in the blank period only.

[0081] FIG. 4 is a circuit diagram of a blank-input sub-unit according to an embodiment of the present disclosure. FIG. 5A through FIG. 5F is a circuit diagram of a blank-input sub-unit according to an embodiment of the present disclosure. In some embodiments, the select-control circuit 311 can be realized by including a first transistor M1 and a first capacitor Cl. The first transistor M1 has a gate terminal configured to receive the select-control signal OE. The first transistor M1 has a first terminal configured to receive a second input signal STU2. The first transistor M1 has a second terminal coupled to the third node H. For example, when the select-control signal OE is provided as a high voltage tum-on signal, the first transistor M1 is turned on so that the second input signal STU2 is used to charge the third node H.

[0082] The first capacitor C1 has a first terminal coupled to the third node H and a second terminal configured to receive a fourth voltage VGL1 or a first voltage VDD. By setting the first capacitor Cl, the voltage level at the third node H can be maintained. For example, in a display period of a frame, the select-control circuit 311 can charge the third node H to pull up the voltage level of the third node H to a high voltage level. The first capacitor C1 can maintain the high voltage level at the third node H until a blank period of the frame. In some other embodiments, the first capacitor C1 has a second terminal coupled to the fourth node N. Optionally, the fourth voltage VGL1 is a low voltage level or a tum-off signal.

[0083] Referring to FIG. 4, the third input circuit 312 is achieved by including a second transistor M2. The second transistor M2 has a gate terminal coupled to the third node H, a first terminal configured to receive a first clock signal CLKA, and a second terminal coupled to the fourth node N. When the third node H is set to a high voltage level, the second transistor M2 is turned on so that the first clock signal CLKA can be passed to the fourth node N to pull up the voltage level there to a high voltage level.

[0084] Referring to FIG. 4, the first transport circuit 320 includes a third transistor M3 and the second transport circuit 330 includes a fourth transistor M4. The third transistor M3 has a

gate terminal coupled to the fourth node N, a first terminal configured to receive the first voltage VDD, and a second terminal coupled to the first node Ql. For example, when the fourth node N is set to a high voltage level, the third transistor M3 is turned on so that the first voltage VDD can be used to charge the first node Ql. Optionally, the voltage level at the first node Ql is charged to the level of the first voltage VDD at least within 10% of error. The fourth transistor M4 has a gate terminal coupled to the fourth node N, a first terminal configured to receive the first voltage VDD, and a second terminal coupled to the second node Q2. For example, when the fourth node N is set to a high voltage level, the fourth transistor M4 is turned on so that the first voltage VDD can be used to charge the second node Q2.

[0085] Referring to FIG. 5A, in a specific embodiment, the blank-input sub-unit 300A includes a second transistor M2 having a first terminal configured to receive the first voltage VDD, a third transistor M3 having a gate terminal configured to receive the first transport signal TS1, and a fourth transistor M4 having a gate terminal configured to receive the second transport signal TS2. The third transistor M3 also has a first terminal coupled to the fourth node N and the fourth transistor M4 also has a first terminal coupled to the fourth node N. In a display period of a frame, when it needs to charge the first node Ql, it is an option to provide a high voltage to the first transport signal TS1 to make the third transistor M3 to be turned on. Thus, the high voltage level of the first voltage VDD can pass through the second transistor M2, the fourth node N, and the third transistor M3 to charge the first node Ql. In a blank period of a frame, when it needs to charge the second node Q2, it is an option to provide a high voltage to the second transport signal TS2 to make the fourth transistor M4 in conduction state, so that the high voltage level of the first voltage VDD can be passed through the second transistor M2, the fourth node N, and the fourth transistor M4 to charge the second node Q2.

[0086] Referring to FIG. 5B, in another specific embodiment, the blank-input sub-unit 300B includes a third transistor M3 and a fourth transistor M4. The third transistor M3 as well as the fourth transistor M4 are configured to have their gate terminals respectively receiving a first clock signal CLKA. In other words, TS1 = TS2 = CLKA. For example, in a blank period of a frame, when the first clock signal CLKA is provided with a high voltage level, the third transistor M3 and the fourth transistor M4 are turned on at the same time, the

high voltage level of the first voltage VDD can charge the first node Q1 and the second node Q2 at the same time.

[0087] Referring to FIG. 5C, in yet another specific embodiment, the blank-input sub-unit 300C includes a second transistor M2 having a first terminal configured to receive the first clock signal CLKA. The third transistor M3 as well as the fourth transistor M4 are configured to have their gate terminals respectively connected to the first terminal of the second transistor M2 to receive the first clock signal CLKA. Thus, the first terminal of the second transistor M2 in FIG. 5C can be set to a high voltage level with a less time compared to the second transistor M2 in FIG. 5B whose first terminal is always coupled to the first voltage VDD at the high voltage level. Thus, the second transistor M2 in FIG. 5C may have longer work life to ensure stability of the shift-register unit.

[0088] Referring to FIG. 5D, in still another specific embodiment, the blank-input sub-unit 300D further includes a first coupling capacitor CST1 in addition to the circuit shown in FIG. 5C. The coupling capacitor CST1 has a first terminal configured to receive the first clock signal CLKA and a second terminal coupled to the third node H. When the first clock signal CLKA is changed from a low voltage level to a high voltage level, the first clock signal CLKA can pull up a voltage level at the third node H through a coupling effect of the first coupling capacitor CST1 to push the voltage level of the third node H even higher, ensuring that the second transistor M2 is sufficiently turned on.

[0089] Referring to FIG. 5E, in yet still another specific embodiment, the blank-input subunit 300E further includes a second coupling capacitor CST2 in addition to the circuit shown in FIG. 5D. The second coupling capacitor CST2 has a first terminal coupled to the third node H and a second terminal coupled to the fourth node N. When the first clock signal CLKA is changed from a low voltage level to a high voltage level, if the second transistor M2 is turned on, the high voltage level of the first clock signal CLKA can be passed through the second transistor M2 to the fourth node N. The voltage level at the second terminal of the second coupling capacitor CST2 will be pulled up. By a bootstrap effect of the coupling capacitor, the voltage level at the third node H can be further pushed higher to ensure the second transistor M2 be sufficiently turned on.

[0090] Referring to FIG. 5F, in also another specific embodiment, the blank-input sub-unit 300F further includes a forty-second transistor M42 in addition to the circuit shown in FIG.

5E. The forty-second transistor M42 has a gate terminal coupled to the third node H, a first terminal configured to receive the first clock signal CLKA, and a second terminal coupled to the first terminal of the first coupling capacitor CST1. When the third node H is set to a high voltage level, the forty-second transistor M42 is turned on. Then, the first clock signal CLKA is able to pull up the third node H via a coupling effect of the first coupling capacitor CST1 so that the third node H is pushed to an even higher voltage level, ensuring that the second transistor M2 is sufficiently turned on.

[0091] FIG. 6 is a circuit diagram of a blank-input sub-unit including an anti-leak structure according to an embodiment of the present disclosure. Referring to FIG. 6, in an alternative embodiment, the blank-input sub-unit 300' further includes a forty-third transistor M43 and transistors M1\_b, M3\_b, and M4\_b in addition to the circuit shown in FIG. 5E. The forty-third transistor M43 has a gate terminal coupled to the third node H, a first terminal configured to receive a sixth voltage VB, and a second terminal coupled to the second terminal of the first transistor M1. Transistor M1\_b has a gate terminal configured to receive the select-control signal OE, a first terminal coupled to the second terminal of the first transistor M1, and a second terminal coupled to the third node H. Transistor M3\_b and transistor M4\_b have their gate terminals commonly configured to receive the first clock signal CLKA. Transistor M3\_b and transistor M4\_b have their first terminals commonly coupled to a seventh node OF. Transistor M3\_b also has a second terminal coupled to the second node O2.

[0092] The forty-third transistor M43 and transistor M1\_b are combined to provide an antileak function to prevent current leaking at the third node H. Transistor M3\_b is also able to prevent current leaking at the first node Ql. Transistor M4\_b is also able to prevent current leaking at the second node Q2. Optionally, the sixth voltage VB is set to a high voltage level. Optionally, more details about the anti-leak function achieved in the blank-input sub-unit and its relevance with the seventh node OF will be described in the specification below. Optionally, the transistors employed in the blank-input sub-units shown in FIG. 4, FIG. 5A through FIG. 5F, and FIG. 6 are all N-type transistors as an example.

[0093] FIG. 7 is a block diagram of a shift-register unit according to yet another embodiment of the present disclosure. Referring to FIG. 7, the shift-register unit 10B includes, in addition to the circuit shown in FIG. 2, a first control circuit 130, a first reset circuit 140, a second reset circuit 150, a shift-register output terminal CRT, and a first output

terminal OP1. The shift-register output terminal CRT is provided to output the shift-register signal CR. The first output terminal OP1 is provided to output the first output signal OUT1.

[0094] The first control circuit 1130 is configured to control a voltage level of a fifth node QB\_A in response to the voltage level at the first node Q1 and a second voltage VDD\_A. For example, the first control circuit 130 is connected to the first node Q1 and the fifth node QB\_A and is configured to receive the second voltage VDD\_A and the fourth voltage VGL1. When the first node Q1 is set to a high voltage level (with a 10% error being allowed), the first control circuit 130 can use the fourth voltage VGL1 at a low voltage level to pull down the voltage level of the fifth node QB\_A to a low voltage level. Optionally, when the first node Q1 is set to a low voltage level (with a 10% error being allowed), the first control circuit 130 can use the second voltage level (with a 10% error being allowed), the first control circuit 130 can use the second voltage VDD\_A at a high voltage level to charge the fifth node QB\_A so as to pull up the voltage level of the fifth node QB\_A to a high voltage level.

[0095] The first reset circuit 140 is configured to reset voltage levels at the first node Ql, the shift-register output terminal CRT, and the first output terminal OP1 in response to the voltage level at the fifth node QB\_A. The first reset circuit 140 is connected respectively to the first node Ql, the fifth node QB\_A, the shift-register output terminal CRT, and the first output terminal OP1, and is configured to receive the fourth voltage VGL1 and a fifth voltage VGL2. When the first reset circuit 140 is turned on by the voltage level at the fifth node QB\_A, it can use the fourth voltage VGL1 (at a low voltage level) to pull down or reset the voltage levels of the first node Q1 and the shift-register output terminal CRT to a low voltage level. At the same time, it also can use the fifth voltage VGL2 (also at a low voltage level) to pull down or reset the voltage level of the first output terminal OP1 to a low voltage level. Optionally, the first reset circuit 140 can also use the fourth voltage VGL1 to pull down or reset the voltage level of the first output terminal OP1 to a low voltage level.

[0096] The second reset circuit 150 is configured to reset voltage levels of the first node Ql, the shift-register output terminal CRT, and the first output terminal in response to a voltage level at the sixth node QB\_B. Referring to FIG. 7, the second reset circuit 150 is connected respectively to the first node Ql, the sixth node QB\_B, the shift-register output terminal CRT, and the first output terminal OP1, and is configured to receive the fourth voltage VGL1 and the fifth voltage VGL2. When the second reset circuit 150 is turned on by the voltage level at the sixth node QB\_B, it is an option that the fourth voltage VGL1 (at the low voltage level) is used to pull down or reset the voltage level at the first node Q1 and the shift-register output

terminal CRT to a low voltage level. At the same time, it is an option to use the fifth voltage VGL2 (at the low voltage level) to pull down or reset the voltage level of the first output terminal OP1 to a low voltage level.

[0097] Referring to FIG. 7, the second sub-unit 200B also includes a second control circuit 230, a third reset circuit 240, a fourth reset circuit 250, and a second output terminal OP2. The second output terminal OP2 is to output the second output signal OUT2.

[0098] The second control circuit 230 is configured to control a voltage level of the sixth node QB-B in response to a voltage level at the second node Q2 and a third voltage VDD\_B. Referring to FIG. 7, the second control circuit 230 is connected to the second node Q2 and the sixth node QB\_B, and is configured to receive the third voltage VDD\_B and the fourth voltage VGL1. When the second node Q2 is set to a high voltage level, the second control circuit 230 can use the fourth voltage VGL1 at the low voltage level to pull down the voltage level of the sixth node QB\_B to a low voltage level. When the second node Q2 is set to a low voltage level, the second control circuit 230 also can use the third voltage VDD\_B (at a high voltage level) to charge the sixth node QB\_B so as to pull up the voltage level thereof.

[0099] The third reset circuit 240 is configured to reset the second node Q2 and the second output terminal OP2 to a low voltage level in response to the voltage level at the sixth node QB\_B. For example, the third reset circuit 240 is connected to the second node Q2, the sixth node QB\_B, and the second output terminal OP2, and is configured to receive the fourth voltage VGL1 and the fifth voltage VGL2. When the third reset circuit 240 is turned on by the voltage level at the sixth node QB\_B, it is an option to use the fourth voltage VGL1 to pull down the voltage level at the second node Q2 to a low voltage level. At the same time, it is also an option to use the fifth voltage VGL2 to pull down the voltage level at the second output terminal OP2. Optionally, the fourth voltage VGL1 can also be used to pull down or reset the second output terminal OP2 to a low voltage level.

[0100] The fourth reset circuit 250 is configured to reset the second node Q2 and the second output terminal OP2 in response to the voltage level at the fifth node QB\_A. For example, the fourth reset circuit 250 is connected to the second node Q2, the fifth node QB\_A, and the second output terminal OP2, and is configured to receive the fourth voltage VGL1 and the fifth voltage VGL2. When the fourth reset circuit 250 is turned on by the voltage level at the fifth node QB\_A, it is an option to use the fourth voltage VGL1 (at the

low voltage level) to pull down or reset the second node Q2 to the low voltage level. At the same time, it is also an option to use the fifth voltage VGL2 (at the low voltage level) to pull down or reset the second output terminal OP2 to low voltage level.

[0101] Optionally, the second voltage VDD\_A and the third voltage VDD\_B can be set to two out-of-phase voltage signals, i.e., when the second voltage VDD\_A is given a high voltage level, the third voltage VDD\_B is given a low voltage level, while the second voltage VDD\_A is a low voltage level, the third voltage VDD\_B is a high voltage level. By setting in this way, the first control circuit 130 and the second control circuit 230 can have one circuit be in working mode at one time. This can avoid functional drift of the circuits due to long-time working and enhance the circuit stability.

[0102] Referring to FIG. 7, the blank-input sub-unit 300 of the shift-register unit 10B also includes a common-reset circuit 340. The common-reset circuit 340 is connected respectively to the fourth node N, the fifth node QB\_A, and the sixth node QB\_B, and is configured to reset the voltage level of the fourth node N in response to the voltage level at the fifth node QB\_A or the sixth node QB\_B. For example, the common-reset circuit 340 can be configured to receive the fourth voltage VGL1. When the common-reset circuit 340 is turned on by the voltage level of the fifth node QB\_A or the sixth node QB\_B, it can use the fourth voltage VGL1 to pull down or reset the fourth node N to a low voltage level. By setting up the common-reset circuit 340 in the blank-input sub-unit, it is able to better control the voltage level at the fourth node N. When there is no need to charge the first node Q1 or the second node Q2, the fourth node N can be set to a low voltage level to turn off the first transport circuit 320 and the second transport circuit 330. Thus, the high voltage level from the first voltage VDD is prevented from charging the first node Q1 and the second node Q2. In this way, abnormal signal output can be avoided, enhancing the circuit stability.

[0103] FIG. 8 is a block diagram of a shift-register unit according to still another embodiment of the present disclosure. Referring to FIG. 8, the shift-register unit 10C, in additional to the circuit shown in FIG. 7, is provided with its first sub-unit 100 further including a third control circuit 160 and a fourth control circuit 170. The third control circuit 160 is configured to control a voltage level of the fifth node QB\_A in response to the first clock signal CLKA. The fourth control circuit 170 is configured to control a voltage level of the fifth node QB\_A in response to the first input signal STU1.

[0104] In an embodiment, the third control circuit 160 is connected to the fifth node QB\_A and is configured to receive the first clock signal CLKA and the fourth voltage VGL1. For example, in a display period of a frame, the third control circuit 160 can be turned on in response to the first clock signal CLKA so as to use the fourth voltage VGL1 to pull down the fifth node QB\_A to a low voltage level. In another embodiment, the third control circuit 160 is also connected to the third node H. In a blank period of a frame, when the third node H is set to a high voltage level and the first clock signal CLKA is provided with a high voltage level, the third control circuit 160 is turned on so that the fourth voltage VGL1 at the low voltage level can be used to pull down the fifth node OB A to a low voltage level.

[0105] The fourth control circuit 170 is connected to the fifth node QB\_A and is configured to receive the first input signal STU1 and the fourth voltage VGL1. For example, in a display period of a frame, the fourth control circuit 170 is turned on in response to the first input signal STU1 and the fourth voltage VGL1 can be used to pull down the fifth node QB\_A to a low voltage level. Once the fifth node QB\_A is pull down to the low voltage level, it can avoid its affection to the first node Q1 so that the charging to the first node Q1 during the display period is more sufficient.

[0106] Referring to FIG. 8, the second sub-unit 200, in addition to the circuit shown in FIG. 7, also includes a fifth control circuit 260 and a sixth control circuit 270. The fifth control circuit 260 is configured to control a voltage level of the sixth node QB\_B in response to the first clock signal CLKA. The sixth control circuit 270 is configured to control a voltage level of the sixth node QB\_B in response to the first input signal STU1.

[0107] In an embodiment, the fifth control circuit 260 is connected to the sixth node QB\_B and is configured to receive the first clock signal CLKA and the fifth voltage VGL1. For example, in a blank period of a frame, the fifth control circuit 260 can be turned on in response to the first clock signal CLKA. Thus, the fourth voltage VLG1 at the low voltage level can be used to pull down voltage level at the sixth node QB\_B. In another embodiment, the fifth control circuit 260 is also connected to the third node H. For example, in the blank period of the frame, when the third node H is set to a high voltage level and the first clock signal CLKA is provided with a high voltage level, the fifth control circuit 260 is turned on, so that the fourth voltage VGL1 can be used pull down the sixth node QB\_B to a low voltage level.

[0108] The sixth control circuit 270 is connected to the sixth node QB\_B and is configured to receive the first input signal STU1 and the fourth voltage VGL1. For example, in a display period of a frame, the sixth control circuit 270 is turned on in response to the first input signal STU1. The low fourth voltage VGL1 can be used to pull down the sixth node QB\_B. The sixth node QB\_B is pulled down to a low voltage level to prevent an affection of the sixth node QB\_B on the second node Q2 so that the charging of the second node Q2 during the display period is more sufficient.

- [0109] Referring to FIG. 8, the first sub-unit 100C further includes a fifth reset circuit 180 and a sixth reset circuit 190. The fifth reset circuit 180 is configured to reset the first node Q1 in response to a display-reset signal STD. The sixth reset circuit 190 is configured to reset the first node Q1 in response to a full-scale reset signal TRST.

- [0110] In an embodiment, the fifth reset circuit 180 is connected to the first node Q1 and is configured to receive a display-reset signal STD and the fourth voltage VGL1. In a display period of a frame, the fifth reset circuit 180 is turned on in response to the display-reset signal STD so that the fourth voltage VGL1 at the low voltage level can be used to pull down or reset the first node Q1. For example, when multiple shift-register units 10C are cascaded to form a multi-stage gate-driving circuit, one stage of shift-register unit 10C can receive shift-register signal CR outputted from another stage of shift-register unit as the display-reset signal STD.

- [0111] In an embodiment, the sixth reset circuit 190 is connected to the first node Q1 and is configured to receive a full-scale reset signal TRST and the fourth voltage VGL1. When multiple shift-register units 10C are cascaded to form a multi-stage gate-driving circuit, in a display period of a frame, a sixth reset circuit 190 in a respective one stage of shift-register unit 10C is turned on in response to the full-scale reset signal TRST. Thus, the fourth voltage VGL1 at the low voltage level can be used to pull down or reset the first node Q1 of the respective one stage of shift-register unit 10C and so as to achieve a full-scale reset to the gate-driving circuit.

- **[0112]** Referring to FIG. 8, the second sub-unit 200C also includes a seventh reset circuit 280 and an eighth reset circuit 290. The seventh reset circuit 280 is configured to reset the second node Q2 in response to a display-reset signal STD. The eighth reset circuit 290 is configured to reset the second node Q2 in response to a full-scale reset signal TRST.

[0113] In an embodiment, the seventh reset circuit 280 is connected to the second node Q2 and is configured to receive the display-reset signal STD and the fourth voltage VGL1. For example, in a display period of a frame, the seventh reset circuit 280 is turned on in response to the display-reset signal STD so that the fourth voltage VGL1 at the low voltage level can be used to pull down or reset the second node Q2.

- [0114] In an embodiment, the eighth reset circuit 290 is connected to the second node Q2 and is configured to receive the full-scale reset signal TRST and the fourth voltage VGL1. For example, when multiple shift-register units 10C are cascaded to form a multi-stage gate-driving circuit, in a display period of a frame, an eighth reset circuit 290 of a respective one stage of shift-register unit can be turned on in response to the full-scale reset signal TRST. The fourth voltage VGL1 at the low voltage level thus can be used to pull down or reset the second node Q2 in the respective one stage of shift-register unit 10C to a low voltage level so that a full-scale reset of the gate-driving circuit can be achieved.

- [0115] FIG. 9A and FIG. 9B are circuit diagrams of respective a first sub-unit and a second sub-unit of a shift-register unit according to an embodiment of the present disclosure. In particular, FIG. 9A shows a part of the shift-register unit including a first sub-unit 100 and a blank-input sub-unit 300. FIG. 9B shows a part of the shift-register unit including a second sub-unit 200 and a second transport circuit 330. Referring to FIG. 9A and FIG. 9B, the shift-register unit includes many transistors from M1 through M41, a first capacitor Cl, a second capacitor C2, and a third capacitor C3. All transistors used here are N-type transistors as examples. FIG. 10A through FIG. 10C are circuit diagrams of three kinds of a first input circuit of a shift-register unit according to an embodiment of the present disclosure.

- [0116] In an embodiment, referring to the FIG. 9A, the first input circuit 110 is achieved by including a fifth transistor M5. The fifth transistor M5 has a gate terminal configured to receive the first input signal STU1, a first terminal configured to receive the first voltage VDD, and a second terminal coupled to the first node Ql.

- [0117] In another embodiment, referring to the FIG. 10A, the fifth transistor M5 has its gate terminal and its first terminal commonly configured to receive the first input signal STU 1 so that when the first input signal STU 1 is a high voltage signal, the fifth transistor M5 is able to use the high voltage of the first input signal STU1 to charge the first node Ql.

[0118] In yet another embodiment, referring to the FIG. 10B, the first input circuit 110 also includes a transistor M5\_b. The transistor M5\_b has a gate terminal and a first terminal commonly coupled to the second terminal of the fifth transistor M5. The transistor M5\_b also has a second terminal coupled to the first node Ql. Since the transistor M5\_b uses a diode connection manner, the current can only flow from the first terminal to the second terminal of the transistor M5\_b but not the other way. Thus, the current leaking from the first node Ql via the fifth transistor M5 is prevented.

- [0119] In still another embodiment, referring to FIG. 10C, the transistor M5\_b has a gate terminal coupled to the gate terminal of the fifth transistor M5, which are both configured to receive the first input signal STU1. The transistor M5\_b has a first terminal coupled to a seventh node OF. The first input circuit 110 shown in FIG. 10C adopts an anti-leak circuitry structure to prevent current leaking of the first node OI.

- [0120] Referring to FIG. 9A again, the first output circuit 120 can be achieved by including a sixth transistor M6, a seventh transistor M7, and a second capacitor C2. The sixth transistor M6 has a gate terminal coupled to the first node Ql. The sixth transistor M6 has a first terminal configured to receive a second clock signal CLKB as a shift-register signal CR. The sixth transistor M6 has a second terminal coupled to the shift-register output terminal CRT and configured to output the shift-register signal CR.

- [0121] The seventh transistor M7 has a gate terminal coupled to the first node Ql. The seventh transistor M7 has a first terminal configured to receive a third clock signal CLKC as a first output signal OUT1. The seventh transistor M7 has a second terminal coupled to the first output terminal OP1 and configured to output the first output signal OUT1. The second capacitor C2 has a first terminal coupled to the first node Q1 and a second terminal coupled to the second terminal of the seventh transistor M7 which is also the first output terminal OP1.

- [0122] Referring to FIG. 9B again, the second input circuit 210 can be achieved by including an eighth transistor M8. The eighth transistor M8 has a gate terminal configured to receive the first input signal STU1. The eighth transistor M8 has a first terminal configured to receive the first voltage VDD. The eighth transistor M8 has a second terminal coupled to the second node Q2. Alternatively, the second input circuit 210 can also use similar circuits shown in FIG. 10A through FIG. 10C.

[0123] Referring to FIG. 9B, the second output circuit 220 can be achieved by including a ninth transistor M9 and a third capacitor C3. The ninth transistor M9 has a gate terminal coupled to the second node Q2. The ninth transistor M9 has a first terminal configured to receive the fourth clock signal CLKD as a second output signal OUT2. The ninth transistor M9 has a second terminal coupled to the second output terminal OP2 and configured to output the second output signal OUT2. The third capacitor C3 has a first terminal coupled to the second node Q2 and a second terminal coupled to the second terminal of the ninth transistor M9 which is also the second output terminal OP2.

- [0124] Referring to FIG. 9A, the common-reset circuit 340 can be achieved by including a tenth transistor M10 and an eleventh transistor M11. The tenth transistor M10 has a gate terminal coupled to the fifth node QB\_A. The tenth transistor M10 has a first terminal coupled to the fourth node N. The tenth transistor M10 has a second terminal configured to receive the fourth voltage VGL1. The eleventh transistor M11 has a gate terminal coupled to the sixth node QB\_B. The eleventh transistor M11 has a first terminal coupled to the fourth node N. The eleventh transistor M11 has a second terminal configured to receive the fourth voltage VGL1.

- [0125] Referring to FIG. 9A, the first control circuit 130 is achieved by including a twelfth transistor M12 and a thirteenth transistor M13. The twelfth transistor M12 has a gate terminal and a first terminal commonly configured to receive a second voltage VDD\_A. The twelfth transistor M12 also has a second terminal coupled to the fifth node QB\_A. The thirteenth transistor M13 has a gate terminal coupled to the first node Ql. The thirteenth transistor M13 has a first terminal coupled to the fifth node QB\_A. The thirteenth transistor M13 has a second terminal configured to receive the fourth voltage VGL1.

- **[0126]** Referring to FIG. 9A, the first reset circuit 140 can be achieved by including a fourteenth transistor M14, a fifteenth transistor M15, and a sixteenth transistor M16. The second reset circuit 150 can be achieved by including a seventeenth transistor M17, an eighteenth transistor M18, and a nineteenth transistor M19.

- [0127] The fourteenth transistor M14 has a gate terminal coupled to the fifth node QB\_A, a first terminal coupled to the first node Ql, and a second terminal configured to receive the fourth voltage VGL1. The fifteenth transistor M15 has a gate terminal coupled to the fifth node QB\_A, a first terminal coupled to the shift-register output terminal CRT, and a second

terminal configured to receive the fourth voltage VGL1. The sixteenth transistor M16 has a gate terminal coupled to the fifth node QB\_A, a first terminal coupled to the first output terminal OP1, and a second terminal configured to receive a fifth voltage VGL2.

- [0128] The seventeenth transistor M17 has a gate terminal coupled to the sixth node QB\_B, a first terminal coupled to the first node Ql, and a second terminal configured to receive the fourth voltage VGL1. The eighteenth transistor M18 has a gate terminal coupled to the sixth node QB\_B, a first terminal coupled to the shift-register output terminal CRT, and a second terminal configured to receive the fourth voltage VGL1. The nineteenth transistor M19 has a gate terminal coupled to the sixth node QB\_B, a first terminal coupled to the first output terminal OP1, and a second terminal configured to receive the fifth voltage VGL2.