(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5501851号

(P5501851)

(45) 発行日 平成26年5月28日(2014.5.28)

(24) 登録日 平成26年3月20日(2014.3.20)

(51) Int.Cl.

F 1

H03K 17/695 (2006.01)

H03K 17/687

B

G05F 1/455 (2006.01)

G05F 1/455

B

H02M 1/08 (2006.01)

H02M 1/08 321Z

請求項の数 10 (全 21 頁)

(21) 出願番号

特願2010-109908 (P2010-109908)

(22) 出願日

平成22年5月12日(2010.5.12)

(65) 公開番号

特開2011-239253 (P2011-239253A)

(43) 公開日

平成23年11月24日(2011.11.24)

審査請求日

平成25年3月8日(2013.3.8)

(73) 特許権者 000201467

T O N E 株式会社

大阪府大阪市浪速区湊町2丁目1番57号

(74) 代理人 100066728

弁理士 丸山 敏之

(74) 代理人 100100099

弁理士 宮野 孝雄

(74) 代理人 100111017

弁理士 北住 公一

(74) 代理人 100119596

弁理士 長塚 俊也

(74) 代理人 100141841

弁理士 久徳 高寛

最終頁に続く

(54) 【発明の名称】位相制御装置

## (57) 【特許請求の範囲】

## 【請求項 1】

交流電源に接続された負荷に供給される電力を位相制御又は逆位相制御する位相制御装置において、

ソース又はエミッタが前記交流電源の一端と接続されると共に、ドレイン又はコレクタが前記負荷の一端と接続される第1トランジスタと、

ソース又はエミッタが前記交流電源の他端と接続されると共に、ドレイン又はコレクタが前記負荷の他端と接続される第2トランジスタと、

ダイオードブリッジと、

抵抗と、

ツェナーダイオード及びコンデンサの並列回路とを備えており、

前記ダイオードブリッジの一方の入力端子は、前記交流電源と前記第1トランジスタの接続点に接続され、前記ダイオードブリッジの他方の入力端子は、前記交流電源と前記第2トランジスタの接続点に接続され、前記抵抗の一端は、前記ダイオードブリッジの正側の出力端子に接続され、前記抵抗の他端は、前記ツェナーダイオードのカソードと前記コンデンサの一端と接続され、前記ツェナーダイオードのアノードと前記コンデンサの他端は、前記ダイオードブリッジの負側の出力端子と接続されており、

前記第1トランジスタの制御端子の電位と前記第2トランジスタの制御端子の電位とが、前記抵抗と前記並列回路の接続点の電位と、前記ダイオードブリッジの負側の出力端子の電位との間で切り換えられることを特徴とする位相制御装置。

10

20

**【請求項 2】**

スイッチング素子を更に備えており、

前記第1トランジスタの制御端子及び前記第2トランジスタの制御端子の各々は、前記スイッチング素子の一端とゲート抵抗を介して接続されており、

前記スイッチング素子のオン・オフに応じて、前記スイッチング素子の一端の電位が、前記抵抗と前記並列回路の接続点の電位と、前記ダイオードブリッジの負側の出力端子の電位との間で切り換わる、請求項1に記載の位相制御装置。

**【請求項 3】**

交流電源に接続された負荷に供給される電力を位相制御又は逆位相制御する位相制御装置において、

10

ソース又はエミッタが前記交流電源の一端と接続されると共に、ドレイン又はコレクタが前記負荷の一端と接続される第1トランジスタと、

ソース又はエミッタが前記交流電源の他端と接続されると共に、ドレイン又はコレクタが前記負荷の他端と接続される第2トランジスタと、

ダイオードブリッジと、

抵抗と、

ツェナーダイオード及びコンデンサの並列回路とを備えており、

前記ダイオードブリッジの一方の入力端子は、前記交流電源と前記第1トランジスタの接続点に接続され、前記ダイオードブリッジの他方の入力端子は、前記交流電源と前記第2トランジスタの接続点に接続され、前記抵抗の一端は、前記ダイオードブリッジの負側の出力端子に接続され、前記抵抗の他端は、前記ツェナーダイオードのアノードと前記コンデンサの一端と接続され、前記ツェナーダイオードのカソードと前記コンデンサの他端は、前記ダイオードブリッジの正側の出力端子と接続されており、

20

前記第1トランジスタの制御端子の電位と前記第2トランジスタの制御端子の電位とが、前記抵抗と前記並列回路の接続点の電位と、前記ダイオードブリッジの正側の出力端子の電位との間で切り換えられることを特徴とする位相制御装置。

**【請求項 4】**

スイッチング素子を更に備えており、

前記第1トランジスタの制御端子及び前記第2トランジスタの制御端子の各々は、前記スイッチング素子の一端とゲート抵抗を介して接続されており、

30

前記スイッチング素子のオン・オフに応じて、前記スイッチング素子の一端の電位が、前記抵抗と前記並列回路の接続点の電位と、前記ダイオードブリッジの正側の出力端子の電位との間で切り換わる、請求項3に記載の位相制御装置。

**【請求項 5】**

交流電源に接続された負荷に供給される電力を、前記負荷に直列に設けられるスイッチング手段を用いて位相制御又は逆位相制御する位相制御装置において、

前記スイッチング手段は、

前記交流電源と前記負荷の間に設けられる第1トランジスタと、

前記第1トランジスタと極性が異なると共に、前記第1トランジスタに並列に設けられる第2トランジスタと、

40

前記第1トランジスタに対して順方向に直列に接続される第1ダイオードと、

前記第2トランジスタに対して順方向に直列に接続される第2ダイオードとを備えており、

ダイオードブリッジと、

抵抗と、

第1ツェナーダイオード及び第1コンデンサの第1並列回路と、

第2ツェナーダイオード及び第2コンデンサの第2並列回路とを備えており、

前記第1トランジスタのソース又はエミッタと前記第2トランジスタのソース又はエミッタとは、前記交流電源側に配置されており、

前記ダイオードブリッジの一方の入力端子は、前記交流電源と前記スイッチング手段の

50

接続点に接続され、前記ダイオードブリッジの他方の入力端子は、前記交流電源と前記負荷の接続点に接続され、前記抵抗の一端は、前記第1ツエナーダイオードのカソードと前記第1コンデンサの一端と接続され、前記抵抗の他端は、前記第2ツエナーダイオードのアノードと前記第2コンデンサの一端と接続され、前記第1ツエナーダイオードのアノードと前記第1コンデンサの他端とは、前記ダイオードブリッジの負側の出力端子に接続され、前記第2ツエナーダイオードのカソードと前記第2コンデンサの他端とは、前記ダイオードブリッジの正側の出力端子に接続されており、

前記第1トランジスタの制御端子の電位が、前記抵抗と前記第1並列回路の接続点の電位と、前記ダイオードブリッジの負側の出力端子の電位との間で切り換えられると共に、前記第2トランジスタの制御端子の電位が、前記抵抗と前記第2並列回路の接続点の電位と、前記ダイオードブリッジの正側の出力端子の電位との間で切り換えられることを特徴とする位相制御装置。10

#### 【請求項6】

第1スイッチング素子と、

第2スイッチング素子とを更に備えており、

前記第1トランジスタの制御端子は、前記第1スイッチング素子の一端とゲート抵抗を介して接続されており、

前記第1スイッチング素子のオン・オフに応じて、前記第1スイッチング素子の一端の電位は、前記抵抗と前記第1並列回路の接続点の電位と、前記ダイオードブリッジの負側の出力端子の電位との間で切り換わり。20

前記第2トランジスタの制御端子は、前記第2スイッチング素子の一端とゲート抵抗を介して接続されており、

前記第2スイッチング素子のオン・オフに応じて、前記第2スイッチング素子の一端の電位は、前記抵抗と前記第2並列回路の接続点の電位と、前記ダイオードブリッジの正側の出力端子の電位との間で切り換わる、請求項5に記載の位相制御装置。

#### 【請求項7】

交流電源に接続された負荷に供給される電力を、前記負荷に直列に設けられるスイッチング手段を用いて位相制御又は逆位相制御する位相制御装置において、

前記スイッチング手段は、

前記交流電源と前記負荷の間に設けられる第1トランジスタと、30

前記第1トランジスタと極性が異なると共に、前記第1トランジスタに並列に設けられる第2トランジスタと、

前記第1トランジスタに対して順方向に直列に接続される第1ダイオードと、

前記第2トランジスタに対して順方向に直列に接続される第2ダイオードとを備えており、

ダイオードブリッジと、

第1抵抗と、

第2抵抗と、

第1ツエナーダイオード及び第1コンデンサの第1並列回路と、

第2ツエナーダイオード及び第2コンデンサの第2並列回路とを備えており、40

前記第1トランジスタのソース又はエミッタと前記第2トランジスタのソース又はエミッタとは、前記交流電源側に配置されており、

前記ダイオードブリッジの一方の入力端子は、前記交流電源と前記スイッチング手段の接続点に接続され、前記ダイオードブリッジの他方の入力端子は、前記交流電源と前記負荷の接続点に接続され、前記第1抵抗の一端は、前記第1ツエナーダイオードのカソードと前記第1コンデンサの一端と接続され、前記第2抵抗の一端は、前記第2ツエナーダイオードのアノードと前記第2コンデンサの一端と接続され、前記第2抵抗の他端と、前記第1ツエナーダイオードのアノードと、前記第1コンデンサの他端とは、前記ダイオードブリッジの負側の出力端子に接続され、前記第1抵抗の他端と、前記第2ツエナーダイオードのカソードと、前記第2コンデンサの他端とは、前記ダイオードブリッジの正側の出50

力端子に接続されており、

前記第1トランジスタの制御端子の電位が、前記第1抵抗と前記第1並列回路の接続点の電位と、前記ダイオードブリッジの負側の出力端子の電位との間で切り換えられると共に、前記第2トランジスタの制御端子の電位が、前記第2抵抗と前記第2並列回路の接続点の電位と、前記ダイオードブリッジの正側の出力端子の電位との間で切り換えられることを特徴とする位相制御装置。

**【請求項8】**

第1スイッチング素子と、

第2スイッチング素子とを更に備えており、

前記第1トランジスタの制御端子は、前記第1スイッチング素子の一端とゲート抵抗を介して接続されており、

前記第1スイッチング素子のオン・オフに応じて、前記第1スイッチング素子の一端の電位は、前記第1抵抗と前記第1並列回路の接続点の電位と、前記ダイオードブリッジの負側の出力端子の電位との間で切り換わり、

前記第2トランジスタの制御端子は、前記第2スイッチング素子の一端とゲート抵抗を介して接続されており、

前記第2スイッチング素子のオン・オフに応じて、前記第2スイッチング素子の一端の電位は、前記第2抵抗と前記第2並列回路の接続点の電位と、前記ダイオードブリッジの正側の出力端子の電位との間で切り換わる、請求項7に記載の位相制御装置。

**【請求項9】**

交流電源に接続された負荷に供給される電力を位相制御又は逆位相制御する位相制御装置において、

ソース又はエミッタが前記交流電源の一端と接続されると共に、ドレイン又はコレクタが前記負荷の一端と接続される第1トランジスタと、

ソース又はエミッタが前記交流電源の他端と接続されると共に、ドレイン又はコレクタが前記負荷の他端と接続される第2トランジスタと、

前記交流電源の交流電圧を整流するダイオードブリッジと、

前記ダイオードブリッジの出力を用いて、前記ダイオードブリッジの負側の出力端子の電位に対して一定の高電位を生成するための、又は、前記ダイオードブリッジの出力を用いて、前記ダイオードブリッジの正側の出力端子の電位に対して一定の低電位を生成するためのツェナーダイオード及びコンデンサの並列回路とを備えており、

前記第1トランジスタの制御端子の電位と前記第2トランジスタの制御端子の電位とが、前記高電位と前記ダイオードブリッジの負側の出力端子の電位との間で、又は、前記低電位と前記ダイオードブリッジの正側の出力端子の電位との間で、切り換えられることを特徴とする位相制御装置。

**【請求項10】**

交流電源に接続された負荷に供給される電力を位相制御又は逆位相制御する位相制御装置において、

前記交流電源と前記負荷の間に設けられる第1トランジスタと、

前記第1トランジスタと極性が異なると共に、前記第1トランジスタに並列に配置される第2トランジスタと、

前記第1トランジスタに対して順方向に直列に接続される第1ダイオードと、

前記第2トランジスタに対して順方向に直列に接続される第2ダイオードと、

前記交流電源の交流電圧を整流するダイオードブリッジと、

前記ダイオードブリッジの出力を用いて、前記ダイオードブリッジの負側の出力端子の電位に対して一定の高電位を生成するための第1ツェナーダイオード及び第1コンデンサの第1並列回路と、

前記ダイオードブリッジの出力を用いて、前記ダイオードブリッジの正側の出力端子の電位に対して一定の低電位を生成するための第2ツェナーダイオード及び第2コンデンサの第2並列回路とを備えており、

10

20

30

40

50

前記第1トランジスタのソース又はエミッタと前記第2トランジスタのソース又はエミッタとは、前記交流電源側に配置されており、

前記第1トランジスタの制御端子の電位が、前記高電位と前記ダイオードブリッジの負側の出力端子の電位との間で切り換えられると共に、前記第2トランジスタの制御端子の電位が、前記低電位と前記ダイオードブリッジの正側の出力端子の電位との間で切り換えられることを特徴とする位相制御装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、交流負荷の電力を位相制御又は逆位相制御する位相制御装置に関するものである。10

より詳細には、トランジスタをスイッチング素子として用いて、交流負荷の電力を位相制御又は逆位相制御する位相制御装置に関するものである。

**【背景技術】**

**【0002】**

電動工具や照明器具などの電気機器の分野においては、負荷である交流モータや照明負荷などの電力を位相制御又は逆位相制御することが広く行われている。例えば、特開2009-12149号公報や特開平08-154392号公報には、トライアックやSSRをスイッチング素子として使用して、交流モータの位相制御を行う電動工具や交流モータの制御装置が開示されている。20

**【0003】**

電気機器において交流負荷の位相制御又は逆位相制御がなされる場合、スイッチングの際の急激な電流変化に起因して電磁ノイズが発生する。交流負荷に流れる電流が大きい電動工具のような電気機器では、スイッチングに起因した電磁ノイズが大きくなるので、周辺の電気機器や人体に対する悪影響が特に懸念される。20

**【0004】**

特開平11-161346号公報には、逆方向に直列接続した2個のMOSFETを用いて位相制御又は逆位相制御を行う位相制御装置が開示されている。近年、パワーエレクトロニクス分野において、MOSFETやIGBTなどの大電流を制御可能なトランジスタが普及ってきており、また、トライアックやSSRなどと比較して、トランジスタは、スイッチングの際の電流変化の低減に有利である。故に、電動工具のような、比較的大きな電流が負荷に流れる電気機器の位相制御又逆位相制御においても、大電流を制御可能なトランジスタをスイッチング素子として使用することで、スイッチングの際の電磁ノイズを抑制することが考えられる。30

**【先行技術文献】**

**【特許文献】**

**【0005】**

**【特許文献1】**特開2009-12149号公報

**【特許文献2】**特開平08-154392号公報

**【特許文献3】**特開平11-161346号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

大電流が流れる電気機器において、大電流を制御可能なトランジスタを用いた位相制御又逆位相制御を行う場合、トランジスタのゲート又ベース駆動電圧として使用される比較的大きな定電圧を生成して、トランジスタのゲート又はベースに印加する必要がある。特開平11-161346号公報の図2に示された位相制御装置では、トランジスタを用いたゲート電源部を用いて、交流電圧からゲート駆動電圧を得ているが、このようなゲート電源部は、スペース、コスト高、重量増などの点で好ましくない。

**【0007】**

また、特開平11-161346号公報の図8に示された位相制御装置では、交流電源40

50

と負荷の直列回路がダイオードブリッジの入力端子間に接続されている。これら端子間に印加される交流電圧をダイオードブリッジで全波整流しても、高い直流電圧を安定して得られないことから、このような構成は、大電流を制御可能なトランジスタを用いた位相制御又は逆位相制御には好ましくない。

#### 【0008】

トランジスタのゲート又はベース駆動電圧を、全波整流ではなく半波整流を用いて交流電圧から生成すれば、比較的簡単な回路構成を用いてゲート又はベース駆動電圧を生成できるであろう。しかしながら、位相制御又は逆位相制御を安定且つ正確に行うためには、ゲート又はベース駆動電圧が安定する必要がある。この点を踏まえると、ゲート又はベース駆動電圧は、交流電圧を全波整流して生成されるのが好ましい。

10

#### 【0009】

本発明は、上記の問題を解決するものであり、トランジスタを用いて交流負荷の位相制御又は逆位相制御を行う位相制御装置において、トランジスタの制御端子に与える駆動電圧を、安価、省スペース、軽量で簡単な構成を用いて、全波整流を行うことで生成することを目的とする。

#### 【課題を解決するための手段】

#### 【0010】

本発明の位相制御装置は、交流電源に接続された負荷に供給される電力を位相制御又は逆位相制御する位相制御装置において、ソース又はエミッタが前記交流電源の一端と接続されると共に、ドレイン又はコレクタが前記負荷の一端と接続される第1トランジスタと、ソース又はエミッタが前記交流電源の他端と接続されると共に、ドレイン又はコレクタが前記負荷の他端と接続される第2トランジスタと、ダイオードブリッジと、抵抗と、ツェナーダイオード及びコンデンサの並列回路とを備えており、前記ダイオードブリッジの一方の入力端子は、前記交流電源と前記第1トランジスタの接続点に接続され、前記ダイオードブリッジの他方の入力端子は、前記交流電源と前記第2トランジスタの接続点に接続され、前記抵抗の一端は、前記ダイオードブリッジの正側の出力端子に接続され、前記抵抗の他端は、前記ツェナーダイオードのカソードと前記コンデンサの一端と接続され、前記ツェナーダイオードのアノードと前記コンデンサの他端は、前記ダイオードブリッジの負側の出力端子と接続されており、前記第1トランジスタの制御端子の電位と前記第2トランジスタの制御端子の電位とが、前記抵抗と前記並列回路の接続点の電位と、前記ダイオードブリッジの負側の出力端子の電位との間で切り換えられることを特徴とする。

20

#### 【0011】

さらに、本発明の位相制御装置は、スイッチング素子を更に備えており、前記第1トランジスタの制御端子及び前記第2トランジスタの制御端子の各々は、前記スイッチング素子の一端とゲート抵抗を介して接続されており、前記スイッチング素子のオン・オフに応じて、前記スイッチング素子の一端の電位が、前記抵抗と前記並列回路の接続点の電位と、前記ダイオードブリッジの負側の出力端子の電位との間で切り換わる。

30

#### 【0012】

本発明の位相制御装置は、交流電源に接続された負荷に供給される電力を位相制御又は逆位相制御する位相制御装置において、ソース又はエミッタが前記交流電源の一端と接続されると共に、ドレイン又はコレクタが前記負荷の一端と接続される第1トランジスタと、ソース又はエミッタが前記交流電源の他端と接続されると共に、ドレイン又はコレクタが前記負荷の他端と接続される第2トランジスタと、ダイオードブリッジと、抵抗と、ツェナーダイオード及びコンデンサの並列回路とを備えており、前記ダイオードブリッジの一方の入力端子は、前記交流電源と前記第1トランジスタの接続点に接続され、前記ダイオードブリッジの他方の入力端子は、前記交流電源と前記第2トランジスタの接続点に接続され、前記抵抗の一端は、前記ダイオードブリッジの負側の出力端子に接続され、前記抵抗の他端は、前記ツェナーダイオードのカソードと前記コンデンサの一端と接続され、前記ツェナーダイオードのアノードと前記コンデンサの他端は、前記ダイオードブリッジの正側の出力端子と接続されており、前記第1トランジスタの制御端子の電位と前記第2

40

50

トランジスタの制御端子の電位とが、前記抵抗と前記並列回路の接続点の電位と、前記ダイオードブリッジの正側の出力端子の電位との間で切り換えられることを特徴とする。

#### 【0013】

さらに、本発明の位相制御装置は、スイッチング素子を更に備えており、前記第1トランジスタの制御端子及び前記第2トランジスタの制御端子の各々は、前記スイッチング素子の一端とゲート抵抗を介して接続されており、前記スイッチング素子のオン・オフに応じて、前記スイッチング素子の一端の電位が、前記抵抗と前記並列回路の接続点の電位と、前記ダイオードブリッジの正側の出力端子の電位との間で切り換わる。

#### 【0014】

本発明の位相制御装置は、交流電源に接続された負荷に供給される電力を、前記負荷に直列に設けられるスイッチング手段を用いて位相制御又は逆位相制御する位相制御装置において、前記スイッチング手段は、前記交流電源と前記負荷の間に設けられる第1トランジスタと、前記第1トランジスタと極性が異なると共に、前記第1トランジスタに並列に設けられる第2トランジスタと、前記第1トランジスタに対して順方向に直列に接続される第1ダイオードと、前記第2トランジスタに対して順方向に直列に接続される第2ダイオードとを備えており、ダイオードブリッジと、抵抗と、第1ツエナーダイオード及び第1コンデンサの第1並列回路と、第2ツエナーダイオード及び第2コンデンサの第2並列回路とを備えており、前記第1トランジスタのソース又はエミッタと前記第2トランジスタのソース又はエミッタとは、前記交流電源側に配置されており、前記ダイオードブリッジの一方の入力端子は、前記交流電源と前記スイッチング手段の接続点に接続され、前記ダイオードブリッジの他方の入力端子は、前記交流電源と前記負荷の接続点に接続され、前記抵抗の一端は、前記第1ツエナーダイオードのカソードと前記第1コンデンサの一端と接続され、前記抵抗の他端は、前記第2ツエナーダイオードのアノードと前記第2コンデンサの一端と接続され、前記第1ツエナーダイオードのアノードと前記第1コンデンサの他端とは、前記ダイオードブリッジの負側の出力端子に接続され、前記第2ツエナーダイオードのカソードと前記第2コンデンサの他端とは、前記ダイオードブリッジの正側の出力端子に接続されており、前記第1トランジスタの制御端子の電位が、前記抵抗と前記第1並列回路の接続点の電位と、前記ダイオードブリッジの負側の出力端子の電位との間で切り換えられると共に、前記第2トランジスタの制御端子の電位が、前記抵抗と前記第2並列回路の接続点の電位と、前記ダイオードブリッジの正側の出力端子の電位との間で切り換えられることを特徴とする。

#### 【0015】

さらに、本発明の位相制御装置は、第1スイッチング素子と、第2スイッチング素子とを更に備えており、前記第1トランジスタの制御端子は、前記第1スイッチング素子の一端とゲート抵抗を介して接続されており、前記第1スイッチング素子のオン・オフに応じて、前記第1スイッチング素子の一端の電位は、前記抵抗と前記第1並列回路の接続点の電位と、前記ダイオードブリッジの負側の出力端子の電位との間で切り換わり、前記第2トランジスタの制御端子は、前記第2スイッチング素子の一端とゲート抵抗を介して接続されており、前記第2スイッチング素子のオン・オフに応じて、前記第2スイッチング素子の一端の電位は、前記抵抗と前記第2並列回路の接続点の電位と、前記ダイオードブリッジの正側の出力端子の電位との間で切り換わる。

#### 【0016】

本発明の位相制御装置は、交流電源に接続された負荷に供給される電力を、前記負荷に直列に設けられるスイッチング手段を用いて位相制御又は逆位相制御する位相制御装置において、前記スイッチング手段は、前記交流電源と前記負荷の間に設けられる第1トランジスタと、前記第1トランジスタと極性が異なると共に、前記第1トランジスタに並列に設けられる第2トランジスタと、前記第1トランジスタに対して順方向に直列に接続される第1ダイオードと、前記第2トランジスタに対して順方向に直列に接続される第2ダイオードとを備えており、ダイオードブリッジと、第1抵抗と、第2抵抗と、第1ツエナーダイオード及び第1コンデンサの第1並列回路と、第2ツエナーダイオード及び第2コ

10

20

30

40

50

ンデンサの第2並列回路とを備えており、前記第1トランジスタのソース又はエミッタと前記第2トランジスタのソース又はエミッタとは、前記交流電源側に配置されており、前記ダイオードブリッジの一方の入力端子は、前記交流電源と前記スイッチング手段の接続点に接続され、前記ダイオードブリッジの他方の入力端子は、前記交流電源と前記負荷の接続点に接続され、前記第1抵抗の一端は、前記第1ツェナーダイオードのカソードと前記第1コンデンサの一端と接続され、前記第2抵抗の一端は、前記第2ツェナーダイオードのアノードと前記第2コンデンサの一端と接続され、前記第2抵抗の他端と、前記第1ツェナーダイオードのアノードと、前記第1コンデンサの他端とは、前記ダイオードブリッジの負側の出力端子に接続され、前記第1抵抗の他端と、前記第2ツェナーダイオードのカソードと、前記第2コンデンサの他端とは、前記ダイオードブリッジの正側の出力端子に接続されており、前記第1トランジスタの制御端子の電位が、前記第1抵抗と前記第1並列回路の接続点の電位と、前記ダイオードブリッジの負側の出力端子の電位との間で切り換えられると共に、前記第2トランジスタの制御端子の電位が、前記第2抵抗と前記第2並列回路の接続点の電位と、前記ダイオードブリッジの正側の出力端子の電位との間で切り換えられることを特徴とする。

10

#### 【0017】

さらに、本発明の位相制御装置は、第1スイッチング素子と、第2スイッチング素子とを更に備えており、前記第1トランジスタの制御端子は、前記第1スイッチング素子の一端とゲート抵抗を介して接続されており、前記第1スイッチング素子のオン・オフに応じて、前記第1スイッチング素子の一端の電位は、前記第1抵抗と前記第1並列回路の接続点の電位と、前記ダイオードブリッジの負側の出力端子の電位との間で切り換わり、前記第2トランジスタの制御端子は、前記第2スイッチング素子の一端とゲート抵抗を介して接続されており、前記第2スイッチング素子のオン・オフに応じて、前記第2スイッチング素子の一端の電位は、前記第2抵抗と前記第2並列回路の接続点の電位と、前記ダイオードブリッジの正側の出力端子の電位との間で切り換わる。

20

#### 【0018】

本発明の位相制御装置は、交流電源に接続された負荷に供給される電力を位相制御又は逆位相制御する位相制御装置において、ソース又はエミッタが前記交流電源の一端と接続されると共に、ドレイン又はコレクタが前記負荷の一端と接続される第1トランジスタと、ソース又はエミッタが前記交流電源の他端と接続されると共に、ドレイン又はコレクタが前記負荷の他端と接続される第2トランジスタと、前記交流電源の交流電圧を整流するダイオードブリッジと、前記ダイオードブリッジの出力を用いて、前記ダイオードブリッジの負側の出力端子の電位に対して一定の高電位を生成するための、又は、前記ダイオードブリッジの出力を用いて、前記ダイオードブリッジの正側の出力端子の電位に対して一定の低電位を生成するためのツェナーダイオード及びコンデンサの並列回路とを備えており、前記第1トランジスタの制御端子の電位と前記第2トランジスタの制御端子の電位とが、前記高電位と前記ダイオードブリッジの負側の出力端子の電位との間で、又は、前記低電位と前記ダイオードブリッジの正側の出力端子の電位との間で、切り換えられることを特徴とする。

30

#### 【0019】

本発明の位相制御装置は、交流電源に接続された負荷に供給される電力を位相制御又は逆位相制御する位相制御装置において、前記交流電源と前記負荷の間に設けられる第1トランジスタと、前記第1トランジスタと極性が異なると共に、前記第1トランジスタに並列に配置される第2トランジスタと、前記第1トランジスタに対して順方向に直列に接続される第1ダイオードと、前記第2トランジスタに対して順方向に直列に接続される第2ダイオードと、前記交流電源の交流電圧を整流するダイオードブリッジと、前記ダイオードブリッジの出力を用いて、前記ダイオードブリッジの負側の出力端子の電位に対して一定の高電位を生成するための第1ツェナーダイオード及び第1コンデンサの第1並列回路と、前記ダイオードブリッジの出力を用いて、前記ダイオードブリッジの正側の出力端子の電位に対して一定の低電位を生成するための第2ツェナーダイオード及び第2コンデン

40

サの第2並列回路とを備えており、前記第1トランジスタのソース又はエミッタと前記第2トランジスタのソース又はエミッタとは、前記交流電源側に配置されており、前記第1トランジスタの制御端子の電位が、前記高電位と前記ダイオードブリッジの負側の出力端子の電位との間で切り換えられると共に、前記第2トランジスタの制御端子の電位が、前記低電位と前記ダイオードブリッジの正側の出力端子の電位との間で切り換えられることを特徴とする。

#### 【発明の効果】

#### 【0020】

本発明では、上述したような回路構成を用いて、位相制御又は逆位相制御に用いる2個のトランジスタの制御端子に印加される電位が与えられており、2個のトランジスタのソース又はエミッタの電位と、ダイオードブリッジの出力端子の電位との関係が、交流電圧に応じて変化するように、これらトランジスタが配置されている。これによって、トランジスタなどの電気部品を用いることなく安価、省スペース、軽量で簡単な構成を有すると共に全波整流を行う回路構成を用いて、これらのトランジスタの制御端子に、その制御に必要な安定な電圧を与えることが可能とされている。また、交流電源として、例えば商用交流電源を用いた場合には、本発明により、十分な大きさの電圧を生成できるので、大電流のトランジスタをスイッチング素子として用いた位相制御又は逆位相制御が行える。

10

#### 【図面の簡単な説明】

#### 【0021】

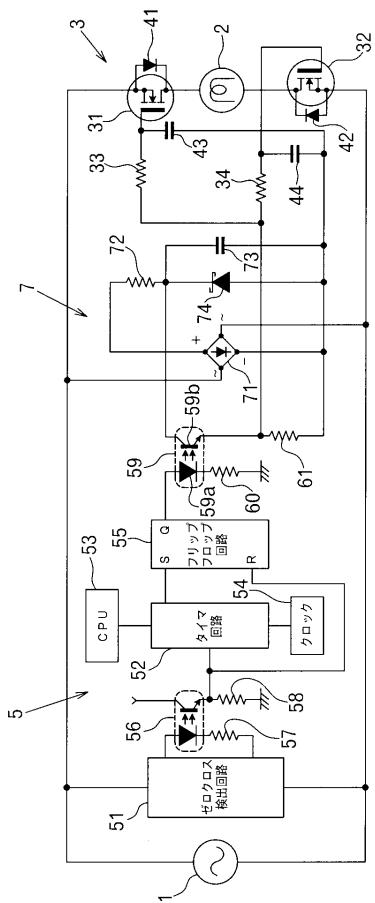

【図1】本発明の位相制御装置の第1実施例を示す回路図である。

20

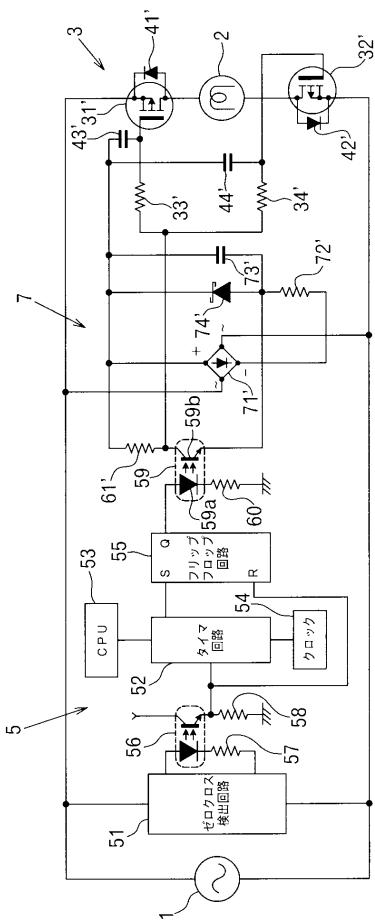

【図2】本発明の位相制御装置の第2実施例を示す回路図である。

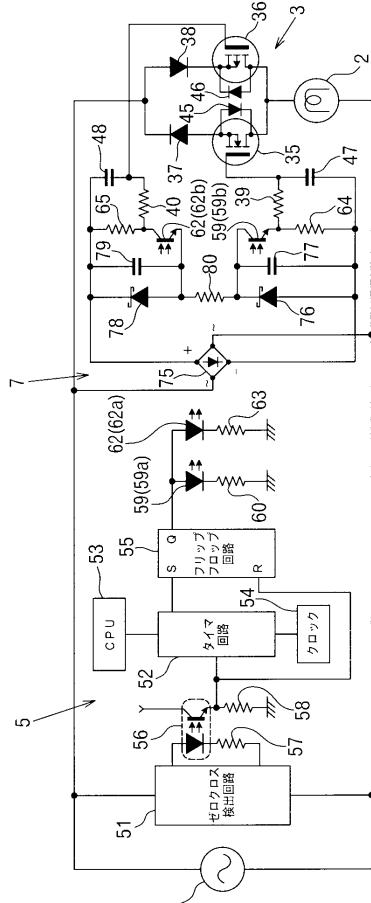

【図3】本発明の位相制御装置の第3実施例を示す回路図である。

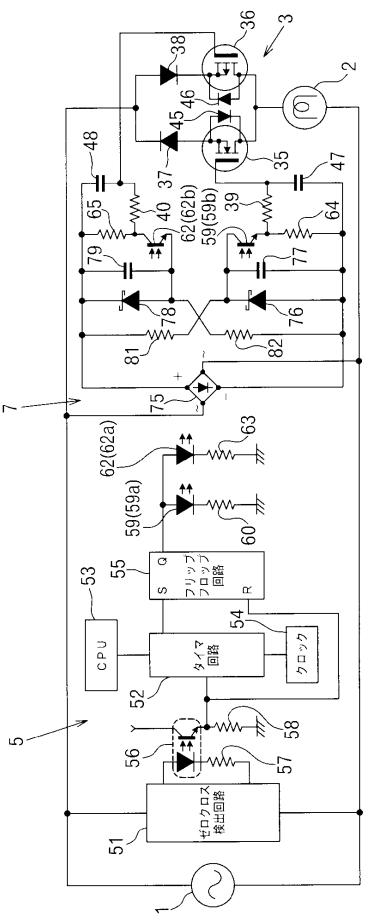

【図4】本発明の位相制御装置の第4実施例を示す回路図である。

#### 【発明を実施するための形態】

#### 【0022】

以下、本発明について図を用いて説明する。図1は、本発明の第1実施例である位相制御装置の構成を示す回路図である。位相制御装置は、交流電源(1)を電源とする交流負荷(2)と、該交流負荷(2)への供給電力をオン又はオフするスイッチング手段(3)と、所定の位相角又は点弧角について交流負荷(2)に電圧が印加されるように、スイッチング手段(3)の動作を制御する制御手段(5)と、スイッチング手段(3)の制御に用いる定電圧を交流電圧から生成する定電圧生成手段(7)とを備えている。

30

#### 【0023】

例えば、交流電源(1)は単相交流の商用交流電源であって、50Hz又は60Hzの100V単相交流電源や、50Hzの220V単相交流電源などが使用されてよい。例えば、本発明の位相制御装置は、ボルト締付機に組み込まれて使用されるものであり、交流負荷(2)は、交流モータであって、ボルトの頭部と、又はボルトに螺合したナットと着脱自在に嵌合するソケットを回転駆動する。本発明の位相制御装置が用いられる電気機器には特段の制限はなく、ボルト締付機以外の電気機器、例えば照明器具において照明負荷の位相制御を行うために、本発明の位相制御装置が使用されてよい。

#### 【0024】

40

スイッチング手段(3)は、交流負荷(2)に直列に接続された2個のNチャネルMOSFET(31)(32)を含んでいる。MOSFET(31)のドレインは、交流負荷(2)の一端に接続されており、MOSFET(31)のソースは、交流電源(1)の一端に接続されている。また、MOSFET(32)のドレインは、交流負荷(2)の他端に接続されており、MOSFET(32)のソースは、交流電源(1)の他端に接続されている。MOSFET(31)のドレイン-ソース間に、電流の逆流を許容するダイオード(41)が設けられている。MOSFET(32)のドレイン-ソース間に、電流の逆流を許容するダイオード(42)が設けられている。スイッチング手段(3)の動作の詳細については後述する。

#### 【0025】

制御手段(5)は、ゼロクロス検出回路(51)と、タイマ回路(52)と、CPU(53)と、クロ

50

ック(54)と、フリップフロップ回路(55)とを含んでいる。ゼロクロス検出回路(51)の出力端子間には、第1フォトカプラ(56)の発光ダイオードと抵抗(57)の直列回路が接続されている。第1フォトカプラ(56)のフォトトランジスタのコレクタは、図示を省略した電源に接続されており、このフォトトランジスタのエミッタは、タイマ回路(52)の入力端子とフリップフロップ回路(55)のリセット端子に接続されると共に、抵抗(58)を介して接地されている。ゼロクロス検出回路(51)の入力端子間には、交流電源(1)の交流電圧が印加されており、ゼロクロス検出回路(51)は、交流電源(1)の交流電圧がゼロになった状態、つまりゼロクロスポイントを検知して、交流電圧のゼロクロスポイントに応じた短時間パルスを、交流電圧の半周期のパルス間隔で有する信号を生成する。生成されたパルス信号は、第1フォトカプラ(56)を介してタイマ回路(52)とフリップフロップ回路(55)に入力される。

10

#### 【 0 0 2 6 】

タイマ回路(52)は、ゼロクロス検出回路(51)から出力されるパルスを受信する毎に、時間のカウントを開始する。そして、所定の設定時間をカウントすると、フリップフロップ回路(55)のセット端子にパルスを出力する。言い換えると、タイマ回路(52)は、ゼロクロス検出回路(51)が出力するパルス信号をこの設定時間だけ遅延させて、フリップフロップ回路(55)に出力する。

#### 【 0 0 2 7 】

クロック(54)は、タイマ回路(52)が時間のカウントに使用するクロック信号を生成する。C P U(53)は、上記の設定時間、つまりパルス信号の遅延時間を設定して、タイマ回路(52)に与える。例えば、本発明の位相制御装置がボルト締付機に用いられる場合、C P U(53)は、使用者が設定した締付トルクの設定値に応じて設定時間を決定して、タイマ回路(52)に与える。

20

#### 【 0 0 2 8 】

ゼロクロス検出回路(51)が出力したパルス信号は、フリップフロップ回路(55)のリセット端子に入力されると共に、設定時間だけ遅延させられてフリップフロップ回路(55)のセット端子に入力される。図1のフリップフロップ回路(55)は、リセット端子へのパルスの入力によってリセット状態になり、そのパルスの入力から設定時間経過後にセット端子にパルスが入力されてセット状態になることで、パルス間隔が交流の半周期であり、パルス幅が交流の半周期から設定時間を引いた時間であるパルス信号を生成する。パルス信号の各パルスのパルス幅は、位相制御の位相角に対応している。

30

#### 【 0 0 2 9 】

フリップフロップ回路(55)の出力端子は、第2フォトカプラ(59)の発光ダイオード(59a)と抵抗(60)を介して接地されている。第2フォトカプラ(59)のフォトトランジスタ(59b)のコレクタは、定電圧生成手段(7)が生成した定電圧を供給する電源ラインと接続されており、第2フォトカプラ(59)のフォトトランジスタ(59b)のエミッタは、ゲート抵抗(33)(34)を介して、M O S F E T(31)(32)の各々のゲートと接続されている。

#### 【 0 0 3 0 】

定電圧生成手段(7)は、交流電圧を全波整流するダイオードブリッジ(71)を備えている。ダイオードブリッジ(71)の一方の入力端子は、M O S F E T(31)と交流電源(1)の接続点に接続されており、ダイオードブリッジ(71)の他方の入力端子は、M O S F E T(32)と交流電源(1)の接続点に接続されている。ダイオードブリッジ(71)の正側の出力端子は、抵抗(72)を介して、コンデンサ(73)及びツェナーダイオード(74)の並列回路と接続されている。コンデンサ(73)の一端とツェナーダイオード(74)のカソードとが、抵抗(72)の一端に接続されており、コンデンサ(73)の他端とツェナーダイオード(74)のアノードは、ダイオードブリッジ(71)の負側の出力端子と接続されている。また、制御手段(5)の第2フォトカプラ(59)のフォトトランジスタ(59b)のエミッタも、抵抗(61)を介して、ダイオードブリッジ(71)の負側の出力端子と接続されている。

40

#### 【 0 0 3 1 】

定電圧生成手段(7)のダイオードブリッジ(71)は、交流電源(1)の交流電圧を全波整流し

50

、コンデンサ(73)は、整流された直流電圧を平滑化する。また、ツェナーダイオード(74)が、平滑化された直流電圧の上限を与えることで、抵抗(72)と、コンデンサ(73)及びツェナーダイオード(74)の並列回路の接続点の電位(以下、「供給電位」)は、ダイオードブリッジ(71)の負側の出力端子の電位(以下、「基準電位」)に対してほぼ一定になり、ダイオードブリッジ(71)の負側の出力端子に対するこの接続点の電圧が、定電圧生成手段(7)が生成する定電圧となっている。

#### 【 0 0 3 2 】

制御手段(5)のフリップフロップ回路(55)から出力されるパルス信号がハイレベルである場合、第2フォトカプラ(59)の発光ダイオード(59a)の光により、第2フォトカプラ(59)のフォトトランジスタ(59b)がオン状態になる。これにより、MOSFET(31)(32)のゲートの電位は、供給電位になる。フリップフロップ回路(55)から出力されるパルス信号がロー・レベルである場合、第2フォトカプラ(59)のフォトトランジスタ(59b)はオフ状態になり、MOSFET(31)(32)のゲートの電位は、基準電位となる。

#### 【 0 0 3 3 】

MOSFET(31)のソースの電位がMOSFET(32)のソースの電位よりも高い状況下で、第2フォトカプラ(59)のフォトトランジスタ(59b)がオン状態になって、MOSFET(31)(32)のゲートの電位が供給電位になる場合を考える。この場合、MOSFET(32)のソースの電位と基準電位(ダイオードブリッジ(71)の負側の出力端子の電位)とがほぼ同じであることから、定電圧生成手段(7)の供給電位(と基準電位の差)が、MOSFET(32)のゲート駆動電圧として、MOSFET(32)のゲートに印加されて、MOSFET(32)がオン状態となる。MOSFET(32)がオン状態となることで、MOSFET(31)がオン状態であるかオフ状態であるかに拘わらず、ダイオード(41)、交流負荷(2)、及びMOSFET(32)のドレイン - ソース間を通じて電流が流れ(つまり、交流負荷(2)及びスイッチング手段(3)からなる回路が導通状態になって)、交流負荷(2)に電力が供給される。なお、MOSFET(31)の寄生ダイオードをダイオード(41)の代わりに利用できる場合には、ダイオード(41)を設ける必要はない。

#### 【 0 0 3 4 】

MOSFET(32)のソースの電位がMOSFET(31)のソースの電位よりも高い状況下で、第2フォトカプラ(59)のフォトトランジスタ(59b)がオン状態になって、MOSFET(31)(32)のゲートの電位が供給電位になる場合を考える。この場合、MOSFET(31)のソースの電位と基準電位とがほぼ同じであることから、定電圧生成手段(7)の供給電位が、MOSFET(31)のゲート駆動電圧として、MOSFET(31)のゲートに印加され、MOSFET(31)がオン状態となる。MOSFET(31)がオン状態となることで、MOSFET(32)がオン状態であるかオフ状態であるかに拘わらず、ダイオード(42)、交流負荷(2)、及びMOSFET(31)のドレイン - ソース間を通じて電流が流れ(つまり、交流負荷(2)及びスイッチング手段(3)からなる回路が導通状態になって)、交流負荷(2)に電力が供給される。なお、MOSFET(32)の寄生ダイオードをダイオード(42)の代わりに利用できる場合には、ダイオード(42)を設ける必要はない。

#### 【 0 0 3 5 】

MOSFET(31)のソースの電位とMOSFET(32)のソースの電位とが、等しい又はほぼ等しい状況下で、第2フォトカプラ(59)のフォトトランジスタ(59b)がオン状態になり、MOSFET(31)(32)のゲートの電位が、定電圧生成手段(7)の供給電位となる場合には、MOSFET(31)(32)が共にオン状態となって、交流負荷(2)とスイッチング手段(3)とからなる回路は導通状態となる。その後の交流電圧の変化に伴って高電位側のMOSFETがオフ状態になったとしても、そのMOSFETに並列に設置されているダイオードを電流が流れ、低電位側のMOSFETはオン状態であるので、交流負荷(2)とスイッチング手段(3)とからなる回路は導通状態のままであり、交流負荷(2)に電力が供給される。

#### 【 0 0 3 6 】

MOSFET(31)のソースの電位がMOSFET(32)のソースの電位よりも高い状況下

10

20

30

40

50

で、第2フォトカプラ(59)のフォトトランジスタ(59b)がオフ状態になり、MOSFET(31)(32)のゲートが基準電位となる場合を考える。この場合、MOSFET(32)のソースの電圧と基準電位とがほぼ同じであるから、MOSFET(32)はオフ状態になる。MOSFET(32)がオフ状態であると共に、それに並列に設けられたダイオード(42)は逆方向バイアスされるので、交流負荷(2)とスイッチング手段(3)とからなる回路は非導通状態となる。故に、MOSFET(31)側からMOSFET(32)側に交流負荷(2)を通って電流が流れないことから、交流負荷(2)に電力は供給されない。

#### 【0037】

MOSFET(32)のソースの電位がMOSFET(31)のソースの電位よりも高い状況下で、第2フォトカプラ(59)のフォトトランジスタ(59b)がオフ状態になり、MOSFET(31)(32)のゲートが基準電位となる場合を考える。この場合、MOSFET(31)のソースの電位と基準電位とがほぼ同じであるから、MOSFET(31)はオフ状態になる。MOSFET(31)がオフ状態であると共に、それに並列に設けられたダイオード(41)は逆方向バイアスされるので、交流負荷(2)とスイッチング手段(3)とからなる回路は非導通状態となる。故に、MOSFET(32)側からMOSFET(31)側に交流負荷(2)を通って電流が流れないことから、交流負荷(2)に電力は供給されない。なお、MOSFET(31)のソースの電位とMOSFET(32)のソースの電位とが、等しい又はほぼ等しい状況下で、MOSFET(31)(32)のゲートに基準電位が印加される場合も、MOSFET(31)(32)が共にオフ状態となり、交流負荷(2)とスイッチング手段(3)とからなる回路は非導通状態になる。その後交流電圧が変化しても、低電位側のMOSFETはオフ状態のままであると共に、それに並列なダイオードは逆方向バイアスされるので、交流負荷(2)とスイッチング手段(3)とからなる回路は非導通状態のままであり、交流負荷(2)には電力が供給されない。

#### 【0038】

以上のように、制御手段(5)がスイッチング手段(3)のMOSFET(31)(32)の動作を制御することで、交流負荷(2)の位相制御が行われる。つまり、交流電圧のゼロクロスポイントに応じて、交流負荷(2)への電力供給を停止し、電力供給を停止してから位相角に対応した時間が経過すると、交流負荷(2)への電力供給を開始することが繰り返される。例えば、本発明の位相制御装置はボルト締付機に用いられ、使用者が設定した締付トルクの設定値に応じた位相角で交流電圧が交流負荷(2)に印加されることで、締付トルクが設定値になるように、交流負荷(2)の電力、具体的には交流モータの電力が位相制御される。

#### 【0039】

交流負荷(2)の位相制御がなされると、MOSFET(31)(32)のゲート抵抗(33)(34)の電位は、定電圧生成手段(7)の供給電位と基準電位との間で繰り返し変化するが、ゲート抵抗(33)と、MOSFET(31)のゲート - ソース間の寄生容量であるゲート容量とが、RC遅延回路として機能することで、MOSFET(31)のゲートにおける電圧の変化は緩やかになる。また、ゲート抵抗(34)と、MOSFET(32)のゲート - ソース間の寄生容量であるゲート容量とが、RC遅延回路として機能することで、MOSFET(32)のゲートにおける電圧の変化が緩やかになる。これによって、MOSFET(31)(32)のドレイン - ソース間を流れる電流の変化が緩和されて、交流負荷(2)の位相制御に伴って発生する電磁ノイズが抑制されている。

#### 【0040】

本実施例では、ダイオードブリッジ(71)の負側の出力端子と、MOSFET(31)のゲートとの間に、コンデンサ(43)が接続されており、ダイオードブリッジ(71)の負側の出力端子とMOSFET(32)のゲートの間に、コンデンサ(44)が接続されている。コンデンサ(43)(44)により、これらゲートにおける電位の変化がより緩やかにされている。ゲート抵抗(33)(34)とMOSFET(31)(32)のゲート容量で、遅延時間が適切に与えられて、MOSFET(31)(32)の電流変化が十分に緩和できる場合には、これらコンデンサ(43)(44)を設ける必要はない。

#### 【0041】

上述したように定電圧生成手段(7)を構成すると共にスイッチング手段(3)を構成する M

10

20

30

40

50

O S F E T (31)(32)の配置を工夫することで、第1実施例の位相制御装置では、M O S F E T (31)(32)のゲートに印加されるゲート駆動電圧が、トランジストなどの電気部品を用いることなく安価、省スペース、軽量で簡単な構成を用いて、且つ、交流電圧を全波整流することで生成されている。また、交流電源(1)として一般的な商用交流電源が使用される場合、大電流のM O S F E Tを駆動するのに必要な程度に、定電圧生成手段(7)の電源ライン電位、つまり供給電位を、基準電位に対して高くできることから(例えば、+12V)、M O S F E T (31)(32)として、大電流を制御可能なM O S F E Tが使用可能となっている。

#### 【 0 0 4 2 】

第1実施例の位相制御装置では、交流電圧が全波整流されているので、交流電圧を半波整流する場合と比較して、より安定したゲート駆動電圧が生成されている。これによって、交流電圧を半波整流する場合と比較して、位相制御によって交流の半周期毎に交流負荷(2)に供給される電力がより安定するので、例えば、交流負荷(2)が交流モータである場合には、モータの不整振動が抑制され、交流負荷(2)が照明負荷である場合には、照明のちらつきが抑制される。定電圧生成手段(7)の供給電位が安定していることから、例えば、M O S F E T (31)(32)のゲート駆動電圧として、例えば5Vの定電圧が求められる場合には、第1実施例において、定電圧生成手段(7)の電源ラインの5Vの定電圧を、制御手段(5)のC P U (53)などの電源電圧として供給してもよい。

#### 【 0 0 4 3 】

図2は、本発明の第2実施例である位相制御装置の構成を示す回路図である。スイッチング手段(3)は、交流負荷(2)に対して直列に配置されており、極性が異なっている一対のM O S F E T (35)(36)、つまり、NチャネルM O S F E T (35)とPチャネルM O S F E T (36)を含んでいる。これらM O S F E T (35)(36)は、並列に配置されており、また、スイッチング手段(3)は、NチャネルM O S F E T (35)に対して順方向に直列に接続されるダイオード(37)と、PチャネルM O S F E T (36)に対して順方向に直列に接続されるダイオード(38)とを含んでいる。

#### 【 0 0 4 4 】

より具体的には、NチャネルM O S F E T (35)のドレインと、PチャネルM O S F E T (36)のドレインとは、交流電源(1)に接続された交流負荷(2)の一端に接続されている。NチャネルM O S F E T (35)のソースは、ダイオード(37)のアノードと接続されており、ダイオード(37)のカソードは、交流電源(1)の一端と接続されている。PチャネルM O S F E T (36)のソースは、ダイオード(38)のカソードと接続されており、ダイオード(38)のアノードは、交流電源(1)の一端と接続されている。NチャネルM O S F E T (35)のドレイン - ソース間には、電流の逆流を許容するダイオード(45)が設けられており、PチャネルM O S F E T (36)のドレイン - ソース間にも、同様なダイオード(46)が設けられている。なお、M O S F E T (35)の寄生ダイオードをダイオード(45)の代わりに利用できる場合には、ダイオード(45)を設ける必要はない。ダイオード(46)についても同様である。

#### 【 0 0 4 5 】

第2実施例の定電圧生成手段(7)は、NチャネルM O S F E T (35)の制御に使用される定電圧と、PチャネルM O S F E T (36)の制御に使用される定電圧とを、交流電圧から生成することを特徴としている。第2実施例の定電圧生成手段(7)に含まれるダイオードブリッジ(75)の一方の入力端子は、交流電源(1)とスイッチング手段(3)の接続点と接続し、ダイオードブリッジ(75)の他方の入力端子は、交流電源(1)と交流負荷(2)の接続点と接続している。ダイオードブリッジ(75)の出力端子の間には、第1ツエナーダイオード(76)と第1コンデンサ(77)が並列に配置された第1並列回路と、第2ツエナーダイオード(78)と第2コンデンサ(79)が並列に配置された第2並列回路とが、抵抗(80)を介して直列に接続されている。第1ツエナーダイオード(76)のアノードと第1コンデンサ(77)の一端とは、ダイオードブリッジ(75)の負側の出力端子に接続されており、第1ツエナーダイオード(76)のカソードと第1コンデンサ(77)の他端とは、抵抗(80)の一端と接続されている。抵抗(80)の他端には、第2ツエナーダイオード(78)のアノードと第2コンデンサ(79)の一端が

10

20

30

40

50

接続されており、第2ツエナーダイオード(78)のカソードと第2コンデンサ(79)の他端とは、ダイオードブリッジ(75)の正側の出力端子に接続されている。

#### 【0046】

ダイオードブリッジ(75)は交流電圧を整流し、ダイオードブリッジ(75)の出力端子間に10

は、全波整流された直流電圧が印加される。第1コンデンサ(77)に印加される電圧を第1

ツエナーダイオード(76)が制限するとともに、第1コンデンサ(77)が電圧を平滑化するこ

とで、第1並列回路と抵抗(80)の接続点の電位(以下、「第1供給電位」)は、ダイオード

ブリッジ(75)の負側の出力端子の電圧(以下、「第1基準電位」)に対してほぼ一定になる

。また、第2コンデンサ(79)に印加される電圧を第2ツエナーダイオード(78)が制限する

とともに、第2コンデンサ(79)が電圧を平滑化することで、第2並列回路と抵抗(80)の接

続点の電位(以下、「第2供給電位」)は、ダイオードブリッジ(75)の正側の出力端子の電

位(以下、「第2基準電位」)に対してほぼ一定になる。第1供給電位は、第1基準電位より

も高く(例えば、第1基準電位に対して+12Vとされる)、第2供給電位は、第2基準電位より

も低い(例えば、第2基準電位に対して-12Vとされる)。

#### 【0047】

第2実施例の制御手段(5)のフリップフロップ回路(55)の出力端子には、第2フォトカ

プラ(59)の発光ダイオード(59a)のアノードに加えて、第3フォトカプラ(62)の発光ダイ

オード(62a)のアノードが接続されており、この発光ダイオード(62a)のカソードは抵抗(6

3)を介して接地されている。その他の点については、第2実施例の制御手段(5)は、第1

実施例の制御手段(5)と同様な構成を有しているので、説明を省略する。

20

#### 【0048】

第2フォトカプラ(59)のフォトトランジスタ(59b)のコレクタは、第1並列回路と抵抗(80)

の接続点と接続されて、このコレクタの電位は第1供給電位となる。フォトトランジ

スタ(59b)のエミッタは、抵抗(64)を介して、ダイオードブリッジ(75)の負側の出力端子

と接続されると共に、ゲート抵抗(39)を介して、NチャネルMOSFET(35)のゲートと接

続される。第3フォトカプラ(62)のフォトトランジスタ(62b)のエミッタは、第2並列

回路と抵抗(80)の接続点と接続されて、このエミッタの電位は第2供給電位となる。フォ

トトランジスタ(62b)のコレクタは、抵抗(65)を介して、ダイオードブリッジ(75)の正側

の出力端子と接続されると共に、ゲート抵抗(40)を介して、PチャネルMOSFET(36)

のゲートと接続される。

30

#### 【0049】

第1実施例で説明したように、フリップフロップ回路(55)から出力されるパルス信号が

ハイレベルになると、第2フォトカプラ(59)のフォトトランジスタ(59b)と第3フォトカ

プラ(62)のフォトトランジスタ(62b)とが共にオン状態になって、NチャネルMOSFET

(35)のゲートは第1供給電位となり、PチャネルMOSFET(36)のゲートは第2供給

電位となる。また、フリップフロップ回路(55)から出力されるパルス信号がロー

レベルになると、フォトトランジスタ(59b)(62b)がオフ状態になって、NチャネルMOSFET(3

5)のゲートは、第1基準電位となり、PチャネルMOSFET(36)のゲートは第2基準電

位となる。

#### 【0050】

交流電源(1)とスイッチング手段(3)とを結ぶライン(以下、「上ライン」)の電位が、交

流電源(1)と交流負荷(2)とを結ぶライン(以下、「下ライン」)の電位よりも高い状況下で

、NチャネルMOSFET(35)のゲートが第1供給電位になり、PチャネルMOSFET

(36)のゲートが第2供給電位になる場合を考える。この場合、PチャネルMOSFET(3

6)のソースの電位が、ダイオードブリッジ(75)の正側の出力端子の電位つまり、第2基準

電位とほぼ同じになるので、第2供給電位(と第2基準電位の差。例えば-12V)がPチャ

ネルMOSFET(36)のゲート駆動電圧として機能して、PチャネルMOSFET(36)

がオン状態になると、PチャネルMOSFET(36)がオン状態になると、NチャネルMOS

FET(35)の状態に拘わらず、ダイオード(38)、PチャネルMOSFET(36)のソース -

ドレイン間、及び交流負荷(2)を通って、上ライン側から下ライン側に電流が流れるので(50

つまり、交流負荷(2)とスイッチング手段(3)とからなる回路が導通状態になるので)、交流負荷(2)に電力が供給される。

#### 【0051】

下ラインの電位が上ラインの電位よりも高い状況下で、NチャネルMOSFET(35)のゲートが第1供給電位になり、PチャネルMOSFET(36)のゲートが第2供給電位になる状況を考える。この場合、NチャネルMOSFET(35)のソースの電位が、ダイオードブリッジ(75)の負側の出力端子の電位つまり、第1基準電位とほぼ同じになるので、第1供給電位(と第1基準電位の差。例えば+12V)がNチャネルMOSFET(35)のゲート駆動電圧として機能して、NチャネルMOSFET(35)がオン状態になる。NチャネルMOSFET(35)がオン状態になると、PチャネルMOSFET(36)の状態に拘わらず、交流負荷(2)、NチャネルMOSFET(35)のドレイン-ソース間、及びダイオード(37)を通って、下ライン側から上ライン側に電流が流れるので(つまり、交流負荷(2)とスイッチング手段(3)とからなる回路が導通状態になるので)、交流負荷(2)に電力が供給される。10

#### 【0052】

上ラインの電位と下ラインの電位が同じ又はほぼ同じ状況下で、NチャネルMOSFET(35)のゲートが第1供給電位になり、PチャネルMOSFET(36)のゲートが第2供給電位になる状況を考える。この場合、2個のMOSFET(35)(36)は共にオン状態になり、交流負荷(2)とスイッチング手段(3)とからなる回路が導通状態になる。その後、上ラインの電位が下ラインの電位に対して上昇しても、PチャネルMOSFET(36)はオン状態のままであり、また、下ラインの電位が上ラインの電位に対して上昇しても、NチャネルMOSFET(35)はオン状態のままであるから、交流負荷(2)とスイッチング手段(3)とからなる回路は導通状態に維持される。20

#### 【0053】

上ラインの電位が下ラインの電位よりも高い状況下で、NチャネルMOSFET(35)のゲートが第1基準電位であり、PチャネルMOSFET(36)のゲートが第2基準電位である場合、PチャネルMOSFET(36)のソースの電位が、第2基準電位とほぼ同じになるので、PチャネルMOSFET(36)がオフ状態になる。ダイオード(37)が設けられているので、PチャネルMOSFET(36)がオフ状態になると、NチャネルMOSFET(35)の状態の如何に拘わらず、交流負荷(2)とスイッチング手段(3)とからなる回路が非導通状態になって、上ライン側から下ライン側に電流が流れないので、交流負荷(2)に電力が供給されない。30

#### 【0054】

下ラインの電位が上ラインの電位よりも高い状況下で、NチャネルMOSFET(35)のゲートが第1基準電位であり、PチャネルMOSFET(36)のゲートが第2基準電位である場合、NチャネルMOSFET(35)のソースの電位が、第1基準電位とほぼ同じになるので、NチャネルMOSFET(35)がオフ状態になる。ダイオード(38)が設けられているので、NチャネルMOSFET(35)がオフ状態になると、PチャネルMOSFET(36)の状態の如何に拘わらず、交流負荷(2)とスイッチング手段(3)とからなる回路が非導通状態になって、下ライン側から上ライン側に電流が流れないので、交流負荷(2)に電力が供給されない。なお、上ラインの電位と下ラインの電位が同じ又はほぼ同じ状況下で、NチャネルMOSFET(35)のゲートが第1基準電位であり、PチャネルMOSFET(36)のゲートが第2基準電位である場合でも、2個のMOSFET(35)(36)は共にオフ状態になり、交流負荷(2)とスイッチング手段(3)とからなる回路は非導通状態になる。その後、上ラインの電位が下ラインの電位に対して上昇してもPチャネルMOSFET(36)はオフ状態のままであり、下ラインの電位が上ラインの電位に対して上昇しても、NチャネルMOSFET(35)はオフ状態のままであるから、交流負荷(2)とスイッチング手段(3)とからなる回路は非導通状態のままであり、交流負荷(2)に電力が供給されない。40

#### 【0055】

以上のように、制御手段(5)がスイッチング手段(3)のMOSFET(35)(36)の動作を制御することで、第1実施例と同様に、第2実施例でも交流負荷(2)の位相制御が行われる50

。交流負荷(2)の位相制御がなされると、NチャネルMOSFET(35)のゲート抵抗(39)に印加される電圧は、定電圧生成手段(7)の第1供給電位と第1基準電位との間で繰り返し変化するが、ゲート抵抗(39)と、MOSFET(35)のゲート-ソース間の寄生容量であるゲート容量とが、RC遅延回路として機能することで、MOSFET(35)のゲートにおける電圧の変化は緩やかになる。また、MOSFET(36)のゲート抵抗(40)に印加される電圧は、定電圧生成手段(7)の第2供給電位と第2基準電位との間で繰り返し変化するが、ゲート抵抗(40)と、PチャネルMOSFET(36)のゲート-ソース間の寄生容量であるゲート容量とが、RC遅延回路として機能することで、MOSFET(36)のゲートにおける電圧の変化が緩やかになる。これによって、MOSFET(35)(36)のドレイン-ソース間を流れる電流の変化が緩和されて、交流負荷(2)の位相制御に伴って発生する電磁ノイズが抑制されている。10

#### 【0056】

第2実施例では、ダイオードブリッジ(75)の負側の出力端子と、NチャネルMOSFET(35)のゲートとの間に、コンデンサ(47)が接続されており、ダイオードブリッジ(75)の正側の出力端子とPチャネルMOSFET(36)のゲートの間に、コンデンサ(48)が接続されている。ゲート抵抗(39)(40)とMOSFET(35)(36)のゲート容量で、遅延時間が適切に与えられて、MOSFET(35)(36)の電流変化が十分に緩和できる場合には、これらコンデンサ(47)(48)を設ける必要はない。

#### 【0057】

上述したように定電圧生成手段(7)を構成すると共にスイッチング手段(3)を構成するMOSFET(35)(36)の配置を工夫することで、第2実施例でも、MOSFET(35)(36)のゲートに印加されるゲート駆動電圧が、トランジスタなどの電気部品を用いることなく安価、省スペース、軽量で簡単な構成を用いて、且つ、交流電圧を全波整流することで生成されている。また、交流電源(1)として一般的な商用交流電源が使用される場合、ゲート駆動電圧は、大電流のMOSFETを駆動するのに必要な程度に、基準電位に対して高く又は低くできることから(例えば、+12V又は-12V)、MOSFET(35)(36)として、大電流を制御可能なMOSFETが使用可能とされている。また、第2実施例でも、交流電圧が全波整流されているので、交流電圧を半波整流する場合と比較して、より安定したゲート駆動電圧が生成されている。20

#### 【0058】

図1に示す第1実施例では、スイッチング手段(3)にNチャネルMOSFET(31)(32)が使用されているが、PチャネルMOSFETが使用されてもよい。図3に示す本発明の第3実施例では、スイッチング手段(3)は、第1実施例のNチャネルMOSFET(31)(32)に夫々対応するPチャネルMOSFET(31')(32')を含んでおり、MOSFET(31')(32')のドレイン-ソース間には、電流の逆流を許容するダイオード(41')(42')が夫々設けられている。MOSFET(31')の寄生ダイオードをダイオード(41')の代わりに利用できる場合には、ダイオード(41')を設ける必要はない。ダイオード(42')についても同様である。

#### 【0059】

第3実施例の定電圧生成手段(7)のダイオードブリッジ(71')の2つの入力端子は、第1実施例と同様に、MOSFET(31')と交流電源(1)の接続点と、MOSFET(32')と交流電源(1)の接続点とに夫々接続されている。ダイオードブリッジ(71')の正側の出力端子は、コンデンサ(73')及びツェナーダイオード(74')の並列回路と接続されている。コンデンサ(73')の一端とツェナーダイオード(74')のカソードとが、ダイオードブリッジ(71')の正側の出力端子に接続されており、コンデンサ(73')の他端とツェナーダイオード(74')のアノードは、抵抗(72')を介してダイオードブリッジ(71')の負側の出力端子と接続されている。40

#### 【0060】

第3実施例では、コンデンサ(73')及びツェナーダイオード(74')の並列回路と抵抗(72')の接続点の電位(「供給電位」)は、ダイオードブリッジ(71')の正側の出力端子の電位(50

以下、「基準電位」)に対してほぼ一定の負の値となる。例えば、供給電位は、基準電位に対して - 12 V とされる。

#### 【 0 0 6 1 】

制御手段(5)の第 2 フォトカプラ(59)のフォトトランジスタ(59b)のコレクタは、抵抗(61')を介して、ダイオードブリッジ(71')の正側の出力端子と接続されている。また、第 2 フォトカプラ(59)のフォトトランジスタ(59b)のコレクタは、ゲート抵抗(33')(34')を介して、MOSFET(31')(32')の各々のゲートと接続されている。ダイオードブリッジ(71')の正側の出力端子と、MOSFET(31')(32')のゲートとの間には、コンデンサ(43')(44')が夫々接続されているが、第 1 実施例で説明したように、MOSFET(31')(32')のゲート容量で足りる場合にはコンデンサ(43')(44')を設ける必要はない。第 2 フォトカプラ(59)のフォトトランジスタ(59b)のエミッタは、コンデンサ(73')及びツェナーダイオード(74')の並列回路と抵抗(72')との接続点に接続されている。10

#### 【 0 0 6 2 】

第 3 実施例の制御手段(5)は、第 1 実施例と同様な構成を有している。フリップフロップ回路(55)から出力されるパルス信号がハイレベルである場合、第 2 フォトカプラ(59)のフォトトランジスタ(59b)がオン状態になり、これにより、MOSFET(31')(32')のゲートの電位は、供給電位になる。フリップフロップ回路(55)から出力されるパルス信号がロー レベルである場合、第 2 フォトカプラ(59)のフォトトランジスタ(59b)はオフ状態になり、MOSFET(31')(32')のゲートの電位は、基準電位となる。20

#### 【 0 0 6 3 】

例えば、MOSFET(31')のソースの電位がMOSFET(32')のソースの電位よりも高い状況下で、第 2 フォトカプラ(59)のフォトトランジスタ(59b)がオン状態になって、MOSFET(31')のゲートの電位が供給電位になる場合、MOSFET(31')のソースの電位と基準電位(ダイオードブリッジ(71')の正側の出力端子の電位)とがほぼ同じであることから、定電圧生成手段(7)の供給電位と基準電位の差である負の電圧(先の例では、- 12 V)が、MOSFET(31')のゲート駆動電圧として、MOSFET(31')のゲートに印加されて、MOSFET(31')がオン状態となる。MOSFET(31')がオン状態となることで、MOSFET(32')がオン状態であるかオフ状態であるかに拘わらず、MOSFET(31')のソース - ドレイン間、交流負荷(2)、及びダイオード(42')を通って電流が流れ(つまり、交流負荷(2)及びスイッチング手段(3)からなる回路が導通状態になって)、交流負荷(2)に電力が供給される。MOSFET(31')のソースの電位がMOSFET(32')のソースの電位よりも高い状況下で、第 2 フォトカプラ(59)のフォトトランジスタ(59b)がオフ状態になって、MOSFET(31')のゲートの電位が基準電位になる場合、MOSFET(31')のソースの電位と基準電位とがほぼ同じであるから、MOSFET(31')はオフ状態になる。MOSFET(31')がオフ状態であると、ダイオード(41')にも電流が流れないことから、交流負荷(2)とスイッチング手段(3)とからなる回路は非導通状態となり、交流負荷(2)に電力は供給されない。30

#### 【 0 0 6 4 】

MOSFET(31')のソースの電位とMOSFET(32')のソースの電位とが、等しい又はほぼ等しい状況下で、第 2 フォトカプラ(59)のフォトトランジスタ(59b)がオン状態になり、MOSFET(31')(32')のゲートの電位が、定電圧生成手段(7)の供給電位となる場合には、MOSFET(31')(32')が共にオン状態となって、交流負荷(2)とスイッチング手段(3)とからなる回路は導通状態となる。その後の交流電圧の変動に伴って低電位側のMOSFET がオフ状態になったとしても、そのMOSFET に並列に設置されているダイオードを電流が流れ、高電位側のMOSFET はオン状態であるので、交流負荷(2)とスイッチング手段(3)とからなる回路は導通状態のままであり、交流負荷(2)に電力が供給される。40

#### 【 0 0 6 5 】

MOSFET(31')(32')の動作に関する上述の説明と、第 1 実施例のMOSFET(31)(32)の動作に関する先の説明とから、第 3 実施例においても、制御手段(5)がスイッチ50

グ手段(3)のMOSFET(31')(32')の動作を制御することで、交流負荷(2)の位相制御が行われることは容易に理解できるであろう。

#### 【0066】

図4は、本発明の第4実施例である位相制御装置の構成を示す回路図である。第4実施例では、第2実施例における抵抗(80)の代わりに、第1抵抗(81)と第2抵抗(82)が設けられている。第1抵抗(81)の一端は、第1ツエナーダイオード(76)のカソードと第1コンデンサ(77)の一端と接続され、第2抵抗(82)の一端は、第2ツエナーダイオード(78)のアノードと第2コンデンサ(79)の一端と接続されている。第2抵抗(82)の他端は、ダイオードブリッジ(75)の負側の出力端子に接続されている。第1抵抗(81)の他端は、ダイオードブリッジ(75)の正側の出力端子に接続されている。

10

#### 【0067】

第1抵抗(81)及び第2抵抗(82)に関する変更点以外は、第4実施例は、第2実施例と同様に構成されている。第2実施例に関する先の説明から、第4実施例においても、制御手段(5)がスイッチング手段(3)のMOSFET(35)(36)の動作を制御することで、交流負荷(2)の位相制御が行われることは容易に理解できるであろう。

#### 【0068】

第1乃至第4実施例の位相制御装置は正論理で動作しているが、負論理で動作するように変更されてもよい。図1に示す第1実施例が負論理で動作するように変更される場合、図1に示す抵抗(61)(及びコンデンサ(43)(44))が、第2フォトカプラ(59)のフォトトランジスタ(59b)のコレクタ側に移動し、MOSFET(31)(32)のゲートが、ゲート抵抗(33)(34)を介してフォトトランジスタ(59b)のコレクタに接続される。つまり、MOSFET(31)(32)のゲートは、図3の第3実施例におけるMOSFET(31')(32')のゲートのように、フォトトランジスタ(59b)のコレクタと接続される。さらに、第1実施例の制御手段(5)が負論理で動作するように変更される。例えば、第1フォトカプラ(56)は、通常オン状態にされて、ゼロクロス検出回路(51)は、交流電源(1)の交流電圧のゼロクロスポイントを検知すると、第1フォトカプラ(56)を短時間オフ状態にする。図3に示す第3実施例が負論理で動作するように変更される場合、MOSFET(31')(32')のゲートは、図1の第1実施例におけるMOSFET(31)(32)のゲートのように、フォトトランジスタ(59b)のエミッタと接続されると共に、制御手段(5)が負論理で動作するように変更される。

20

#### 【0069】

図2に示す第2実施例と図4に示す第4実施例とが負論理で動作するように変更される場合、抵抗(64)(及びコンデンサ(47))が、第2フォトカプラ(59)のフォトトランジスタ(59b)のコレクタ側に移動し、MOSFET(35)のゲートが、ゲート抵抗(39)を介してフォトトランジスタ(59b)のコレクタに接続される。また、抵抗(65)(及びコンデンサ(48))が、第3フォトカプラ(62)のフォトトランジスタ(62b)のエミッタ側に移動し、MOSFET(36)のゲートが、ゲート抵抗(40)を介してフォトトランジスタ(62b)のエミッタに接続される。さらに、制御手段(5)が負論理で動作するように変更される。

30

#### 【0070】

第1乃至第4実施例の位相制御装置では、交流負荷(2)の電力は位相制御されているが、第1実施例において、交流負荷(2)の電力を逆位相制御する場合には、例えば、フリップフロップ回路(55)の出力端子と第2フォトカプラ(59)の間にインバータを配置すればよい(第3実施例も同様)。第2実施例において、交流負荷(2)の電力を逆位相制御する場合には、例えば、フリップフロップ回路(55)の出力端子と、第2フォトカプラ(59)及び第3フォトカプラ(62)の間にインバータを配置すればよい(第4実施例も同様)。なお、インバータを追加することなく、上述したような負論理に対応した変更を第1乃至第4実施例に行うことで、逆位相制御が行われてもよい。

40

#### 【0071】

第1実施例のスイッチング手段(3)では、NチャネルMOSFET(31)(32)が使用されており、第3実施例のスイッチング手段(3)では、PチャネルMOSFET(31')(32')が使用されているが、これらMOSFETの代わりに、IGBTやバイポーラ型トランジス

50

タなどのトランジスタが使用されてもよい。例えば、第1実施例のMOSFET(31)(32)が共にIGBTに置き換えられる場合には、これらIGBTのコレクタが交流負荷(2)に接続され、これらIGBTのエミッタが交流電源(1)に接続される。第1実施例のMOSFET(31)(32)が共に、バイポーラ型トランジスタに置き換えられる場合には、これらバイポーラ型トランジスタのコレクタが交流負荷(2)に接続され、これらバイポーラ型トランジスタのベースが、抵抗(33)(34)を介して、第2フォトカプラ(59)のフォトトランジスタ(59b)のエミッタと接続される。また、第2及び第4実施例では、スイッチング手段(3)に、NチャネルMOSFET(35)とPチャネルMOSFET(36)が使用されているが、これらMOSFETの代わりに、NチャネルIGBTとPチャネルIGBTが使用されてもよく、また、NPNトランジスタとPNPトランジスタが使用されてもよい。

10

## 【0072】

第1乃至4実施例では、制御手段(5)にて第2フォトカプラ(59)、さらには第3フォトカプラ(62)が使用されており、これらフォトカプラ(59)(62)の受光側には、スイッチング素子として機能するフォトトランジスタ(59b)(62b)が使用されているが、フォトカプラ(59)(62)の受光側には、フォトサイリスタやフォトMOSFETなどのスイッチング素子などが使用されてもよい。また、第2フォトカプラ(59)や第3フォトカプラ(62)に代えて、通常のバイポーラトランジスタやMOSFETなどのスイッチング素子を使用し、このスイッチング素子をフリップフロップ回路(55)の出力信号で直接駆動してもよい。

20

上記実施例の説明は、本発明を説明するためのものであって、特許請求の範囲に記載の発明を限定し、或いは範囲を減縮する様に解すべきではない。また、本発明の各部構成は上記実施例に限らず、特許請求の範囲に記載の発明の技術的範囲内で種々の変形が可能であることは勿論である。

## 【符号の説明】

## 【0074】

- (1) 交流電源

- (2) 交流負荷

- (3) スイッチング手段

- (5) 制御手段

- (7) 定電圧生成手段

- (31)(31')(32)(32')(35)(36) MOSFET

- (37)(37')(38)(38')(41)(42) ダイオード

- (59)(62) フォトカプラ

- (71)(71')(75) ダイオードブリッジ

- (72)(72')(80)(81)(82) 抵抗

- (73)(73')(77)(79) コンデンサ

- (74)(74')(76)(78) ツェナーダイオード

30

【 四 1 】

【図3】

【 図 2 】

【図4】

---

フロントページの続き

(72)発明者 小畠 敬良

大阪府大阪市東成区深江北3丁目14番3号 前田金属工業株式会社内

審査官 栗栖 正和

(56)参考文献 特開平11-161346(JP,A)

特開平06-089116(JP,A)

特開平04-349390(JP,A)

特開平09-181656(JP,A)

特開2004-357479(JP,A)

特開平11-161347(JP,A)

特開昭63-238830(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 17/00 - 17/70

G05F 1/455

H02M 1/08