(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6779283号

(P6779283)

(45) 発行日 令和2年11月4日(2020.11.4)

(24) 登録日 令和2年10月15日(2020.10.15)

(51) Int.Cl.

H01S 5/022 (2006.01)

F 1

H01S 5/022

請求項の数 11 (全 9 頁)

(21) 出願番号 特願2018-514853 (P2018-514853)

(86) (22) 出願日 平成28年9月15日 (2016.9.15)

(65) 公表番号 特表2018-527757 (P2018-527757A)

(43) 公表日 平成30年9月20日 (2018.9.20)

(86) 國際出願番号 PCT/EP2016/071847

(87) 國際公開番号 WO2017/050636

(87) 國際公開日 平成29年3月30日 (2017.3.30)

審査請求日 平成30年3月19日 (2018.3.19)

(31) 優先権主張番号 102015116092.7

(32) 優先日 平成27年9月23日 (2015.9.23)

(33) 優先権主張国・地域又は機関

ドイツ (DE)

(73) 特許権者 599133716

オスラム オプト セミコンダクターズ

ゲゼルシャフト ミット ベシュレンクテ

ル ハフツング

Osram Opto Semiconductors GmbH

ドイツ連邦共和国、93055 レーゲン

スブルグ、ライプニッツシュトラーゼ 4

Leibnizstrasse 4, D

-93055 Regensburg,

Germany

(74) 代理人 110002952

特許業務法人鷺田国際特許事務所

最終頁に続く

(54) 【発明の名称】オプトエレクトロニクス部品の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

上面(201)を有するキャリア(200)を設ける工程と、

前記キャリア(200)の前記上面(201)に、前記上面(201)の実装領域(210)に対して凹部をなす凹部領域(220)を作る工程であって、前記実装領域(210)と前記凹部領域(220)との間に段差(230)が形成される工程と、

前記キャリア(200)の前記上面(201)に、前記実装領域(210)および前記凹部領域(220)にわたって延在するメタライゼーション(250)を配置する工程と、

前記メタライゼーション(250)に分離路(270)を作る工程であって、前記メタライゼーション(250)は、少なくとも前記実装領域(210)においては完全に切断されて、前記キャリア(200)の材料が、前記実装領域(210)の前記分離路(270)において少なくとも部分的に露出され、前記凹部領域(220)においては少なくとも完全には切断されず、前記分離路(270)は、直線的に、かつ前記段差(230)に対して垂直に作られる工程と、

オプトエレクトロニクス半導体チップ(110)を前記上面(201)の前記実装領域(210)上に配置する工程であって、前記オプトエレクトロニクス半導体チップ(110)は前記分離路(270)に沿って配置される工程と、を含む、オプトエレクトロニクス部品の製造方法。

## 【請求項 2】

10

20

前記オプトエレクトロニクス半導体チップ(110)は、前記段差(230)から突出するように配置される、請求項1に記載のオプトエレクトロニクス部品の製造方法。

**【請求項3】**

前記分離路(270)に沿って配置する工程は、少なくとも前記実装領域(210)においては完全に切断された前記メタライゼーション(250)と、前記凹部領域(220)においては少なくとも完全には切断されていない前記メタライゼーション(250)との間の境界(280)の位置を光学的に検出する工程を含む、請求項1または2のいずれか1項に記載のオプトエレクトロニクス部品の製造方法。

**【請求項4】**

前記キャリア(200)は、キャリア集合体(300)に設けられ、

前記キャリア集合体(300)は、前記キャリア(200)に個片化するために、前記分離路(270)を作る工程の後に分割され、

前記キャリア(200)の外縁(240)が前記分割によって形成され、

前記凹部領域(220)は、前記外縁(240)に隣接しており、

前記段差(230)は、前記外縁(240)と平行である、請求項1から3のいずれか1項に記載のオプトエレクトロニクス部品の製造方法。

**【請求項5】**

前記分離路(270)を作る工程は、ソーイングまたはレーザによって行われる、請求項1から4のいずれか1項に記載のオプトエレクトロニクス部品の製造方法。

**【請求項6】**

前記分離路(270)は、前記メタライゼーション(250)が前記凹部領域(220)において切断されないように作られる、請求項1から5のいずれか1項に記載のオプトエレクトロニクス部品の製造方法。

**【請求項7】**

前記オプトエレクトロニクス半導体チップ(110)を配置する前に、はんだ(260)が前記上面(201)の前記実装領域(210)の前記メタライゼーション(250)に配置され、

前記オプトエレクトロニクス半導体チップ(110)は、前記はんだ(110)に配置される、請求項1から6のいずれか1項に記載のオプトエレクトロニクス部品の製造方法。

**【請求項8】**

前記オプトエレクトロニクス半導体チップ(110)はレーザチップである、請求項1から7のいずれか1項に記載のオプトエレクトロニクス部品の製造方法。

**【請求項9】**

前記レーザチップは、前記レーザチップの出射面(130)が前記段差(230)から突出するように配置される、請求項8に記載のオプトエレクトロニクス部品の製造方法。

**【請求項10】**

前記レーザチップの電極部(120)が、前記キャリア(200)の前記上面(201)と対向する、請求項8または9のいずれか1項に記載のオプトエレクトロニクス部品の製造方法。

**【請求項11】**

前記分離路(270)は、前記キャリア(200)の前記上面(201)に垂直な方向において、前記メタライゼーション(250)の厚さより大きいが、前記メタライゼーション(250)の厚さと、前記実装領域(210)に対して凹部をなす前記凹部領域(220)の深さとの合計よりは小さい深さを有する、請求項1から10のいずれか1項に記載のオプトエレクトロニクス部品の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、オプトエレクトロニクス部品の製造方法に関する。

10

20

30

40

50

**【背景技術】****【0002】**

レーザチップを、レーザチップの出射面がキャリアの外縁から突出するようにキャリアに配置することは既知である。これにより、出射面のはんだによる望ましくない汚染が防止されうる。しかしながら、この場合、レーザチップの十分な冷却を確保するためには、突出部が過剰なサイズとならないように選択されるべきである。チップの自動実装時における、信頼性あるレーザチップの位置決めが困難であることが分かっている。

**【発明の概要】****【発明が解決しようとする課題】****【0003】**

10

本発明の目的の1つは、オプトエレクトロニクス部品を製造する方法を特定することである。この目的は、請求項1の特徴を備える方法によって達成される。また、様々な発展形態が従属項で特定される。

**【0004】**

20

オプトエレクトロニクス部品を製造する方法は、上面を有するキャリアを設ける工程と、キャリアの上面に、上面の実装領域に対して凹部をなす領域を作る工程であって、実装領域と凹部領域との間に段差が形成される工程と、キャリアの上面に、実装領域および凹部領域にわたって延在するメタライゼーションを配置する工程と、メタライゼーションに分離路 (separating track) を作る工程であって、メタライゼーションは、少なくとも部分的に実装領域においては完全に切断され、凹部領域においては少なくとも完全には切断されない工程と、オプトエレクトロニクス半導体チップを上面の実装領域に配置する工程であって、オプトエレクトロニクス半導体チップは分離路に沿って配置される工程と、を含む。

**【0005】**

この方法によって、分離路の領域において実装領域に露出したキャリアの材料と、分離路の領域において凹部領域で完全には切断されていないメタライゼーションとの間の、明確な光学コントラストがもたらされ有利である。この結果、高コントラストなアラインメントマーク (alignment marking) が形成される。このようなアラインメントマークによって、キャリアの上面の実装領域へのオプトエレクトロニクス半導体チップの信頼性ある自動位置決めが可能となる。

30

**【0006】**

製造方法の一実施形態では、オプトエレクトロニクス半導体チップは、段差から突出するように配置される。このため、オプトエレクトロニクス半導体チップをキャリアの上面の実装領域上に配置する工程時に、突出するように配置されるオプトエレクトロニクス半導体チップの部分が、オプトエレクトロニクス半導体チップをキャリアに接合するための接合材料で汚染されるリスクを低減し有利である。

**【0007】**

40

製造方法の一実施形態では、分離路に沿って配置する工程は、少なくとも部分的に実装領域において完全に切断されたメタライゼーションと、凹部領域において少なくとも完全には切断されていないメタライゼーションとの間の境界の位置を光学的に検出する工程を含む。この方法では、少なくとも実装領域の部分においては完全に切断されたメタライゼーションの領域に露出したキャリアの材料と、凹部領域においては少なくとも完全には切断されていないメタライゼーションとの間に顕著な光学コントラストが生じ有利である。この顕著な光学コントラストは、例えば光学画像認識システムによって、自動化され確実に検出されうる。この結果、境界の位置が正確に検出されうる。同時に、境界の位置は分離路によって正確に決定されるため、わずかなずれのみで全体として正確なオプトエレクトロニクス半導体チップのアラインメントが可能となる。

**【0008】**

製造方法の一実施形態では、分離路は、直線的に、かつ段差に対して垂直に作られる。この結果、とりわけ簡単で正確なオプトエレクトロニクス半導体チップのアラインメント

50

が可能となり有利である。また、直線的に分離路を作ることは、とりわけ簡単な方法によつて可能であり有利である。

#### 【0009】

製造する方法の一実施形態では、キャリアは、キャリア集合体に設けられる。分離路を作る工程後に、キャリアに個片化するためにキャリア集合体は分割される。ここで、キャリアの外縁が分割によって形成される。段差がキャリアの外縁と平行であるように、凹部領域はキャリアの外縁に隣接している。これにより、このような製造方法は、共通の作業工程で複数のキャリアの並行生産を可能とし有利である。この結果、キャリア毎の製造費用が削減されるとともに、キャリア当たりの製造時間が短縮される。さらなる効果として、キャリア集合体で行われる工程が、キャリア集合体の寸法がより大きくなることで、さらに簡単に、かつさらに高精度に行われうる。キャリアの外縁に隣接する凹部領域は、キャリアが、オプトエレクトロニクス半導体チップの正確なアライメントおよび実装をさらに困難とするまたは阻止する骨組みを外縁の領域における上面に含まないことを確実とするので有利である。10

#### 【0010】

製造方法の一実施形態では、分離路を作る工程は、ソーイング（のこ挽き、sawing）またはレーザによって行われる。これらの方法は、正確に定められた深さおよび幅の分離路を迅速に、簡単に、かつ再現性良く作ることを可能とし有利である。

#### 【0011】

製造方法の一実施形態では、分離路は、メタライゼーションが凹部領域において切断されないように作られる。このため、分離路の領域において、少なくとも実装領域の部分において完全に切断されたメタライゼーションと、凹部領域において切断されていないメタライゼーションとの間の、とりわけ明確なコントラストがもたらされ有利である。20

#### 【0012】

製造方法の一実施形態では、オプトエレクトロニクス半導体チップを配置する前に、はんだが上面の実装領域のメタライゼーションに配置される。オプトエレクトロニクス半導体チップはその後、はんだに配置される。ここで、はんだは、オプトエレクトロニクス半導体チップを機械的に固定し、オプトエレクトロニクス半導体チップと電気的に接触する働きをしうる。

#### 【0013】

製造方法の一実施形態では、オプトエレクトロニクス半導体チップはレーザチップである。オプトエレクトロニクス部品は、したがってレーザ部品である。

#### 【0014】

製造方法の一実施形態では、レーザチップは、レーザチップの出射面が段差から突出するように配置される。このため、キャリアの上面の実装領域にレーザチップを配置する工程時に、例えばはんだなどの、レーザチップを固定するために用いられる接合材料がレーザチップの出射面に到達しないことを確実とし有利である。

#### 【0015】

製造方法の一実施形態では、レーザチップのアノードコンタクト部が、キャリアの上面と対向する。このため、レーザチップの出射領域は、キャリアの上面と特に近接して配置されることが可能で、この結果、レーザチップの効果的な冷却が達成されうる。40

#### 【0016】

本発明の上述した特性、特徴、および利点と、これらを達成する方法は、それぞれ図面を参照しながら以下にさらに詳しく説明する例示的な実施形態に関連して、さらに明確かつ容易に理解されるであろう。

#### 【図面の簡単な説明】

#### 【0017】

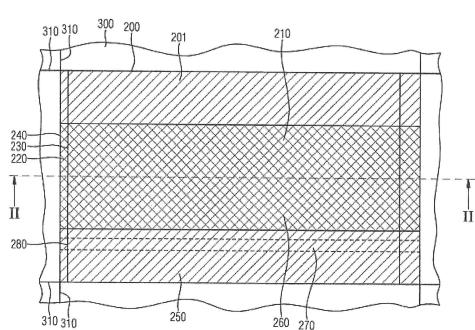

【図1】図1は、キャリア集合体に配置されたキャリアの上面の平面図である。

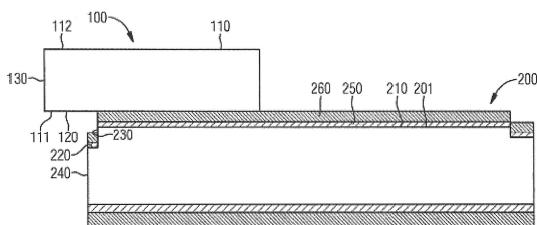

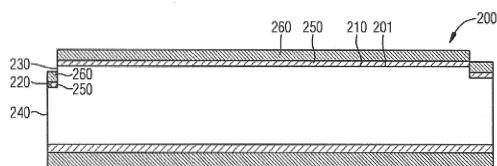

【図2】図2は、キャリアの側断面図である。

【図3】図3は、キャリアとオプトエレクトロニクス半導体チップとを備えるオプトエレ50

クトロニクス部品の側断面図である。

【発明を実施するための形態】

【0018】

図1は、キャリア200の平面図を概略的に示す。図2は、キャリア200の側断面図である。図2におけるキャリア200が切断される断面を図1に示す。キャリア200は、サブマウントとも言及されうる。

【0019】

キャリア200は、上面201を有する実質的に平坦なシートとして形成されている。キャリア200は、例えばケイ素またはセラミックなどの電気絶縁性材料を含みうる。

キャリア200は、キャリア集合体300に設けられうる。キャリア集合体300は、図1に図示されている。キャリア集合体300は、互いに並んで平面に配置され、互いに一体に連続して連結された、同一種類の複数のキャリア200を含む。個々のキャリア200はそれぞれ、例えば長方形で、キャリア集合体300において長方形の格子に配置されうる。

【0020】

キャリア集合体300は、共通の作業工程で複数のキャリアの並行生産を可能とする。共通の加工工程の終了後にのみ、分離面310に沿ってキャリア集合体300が分割されることで、個々のキャリア200に個片化される。分離面310に沿ったキャリア集合体300の分割は、例えばソーイング工程などで行われうる。

【0021】

キャリア200の上面201は、実装領域210と、実装領域210に対して凹んだ凹部領域220とを含んでいる。凹部領域220と実装領域210との間の境界に段差230が形成され、キャリア200の上面201の高さはこの段差で変化している。

【0022】

キャリア200の上面201の凹部領域220は、分離面310に沿ってキャリア集合体300を分割する工程後に、分離面により形成されるキャリア200の外縁240に、隣接するように配置される。つまり、凹部領域220は、キャリア200の上面201の縁領域に配置される。分離面310に形成されるキャリア200の外縁240と、凹部領域220と実装領域210との間に形成される段差230とが、直線的に延び、互いに平行であると都合がよい。

【0023】

凹部領域220は、キャリア200の材料の一部で加工され、凹部領域220において、例えばエッチングまたはソーイングなどの分離法で除去された、キャリア200の上面201で作られうる。ここで、キャリア集合体300の複数のキャリア200の凹部領域220は、同時に作られうる。さらに、キャリア200毎の複数の凹部領域220は、図1および2の例に示すように、例えば各キャリア200の対向する外端に作られうる。

【0024】

凹部領域220を作る工程後に、キャリア200の上面201にメタライゼーション250が配置されている。メタライゼーション250は、キャリア200の上面201の凹部領域220および実装領域210の両方にわたって延在する。メタライゼーション250は、例えば、チタン、白金、および／または金を含みうる。メタライゼーション250は、キャリア200の上面201に対して垂直に測定される厚さが、凹部領域220の深さよりも小さい。メタライゼーション250の厚さは、例えば1μmである。

【0025】

メタライゼーション250をキャリア200の上面201に配置する工程後に、キャリア200の上面201のメタライゼーション250に、分離路270が作られている。分離路270は、直線的に形成され、凹部領域220と実装領域210との間の段差230に垂直に、したがってキャリア集合体300を分割する工程時に形成されるキャリア200の外縁240とも垂直に延在している。ここで分離路270は、キャリア200の上面201の実装領域210および凹部領域220の両方にわたって延在している。

10

20

30

40

50

## 【0026】

キャリア200の上面201の実装領域210では、実装領域210の分離路270の領域においてキャリア200の材料が少なくとも部分的に露出されるように、メタライゼーション250が少なくとも分離路270の領域において完全に切断される。これに対して、キャリア200の上面201の凹部領域220では、分離路270のメタライゼーション250は少なくとも完全には切断されない。この結果、分離路270の領域におけるキャリア200の上面201の凹部領域220で、キャリア200の材料は露出しておらず、依然としてメタライゼーション250で覆われている。

## 【0027】

キャリア200の上面201の凹部領域220において、メタライゼーション250が、分離路270によって全く切断されないように分離路270を作ることが可能である。10

したがって、キャリア200の上面201に垂直な方向において、分離路270の深さが、メタライゼーション250の厚さよりは大きいが、メタライゼーション250の厚さと、実装領域210に対して凹部をなす凹部領域220の深さとの合計よりは小さいと都合がよい。分離路270の深さは、例えば数μmでありうる。

## 【0028】

分離路270は、例えばソーイングまたはレーザによって作られる。分離路270がソーイングで作られる場合、分離路270はソーイングトラックとも言及されうる。

## 【0029】

分離路270を共通の加工工程で、キャリア集合体300の全てのキャリア200に作ることが可能である。20

## 【0030】

図1および2に示す例では、はんだ260がキャリア200の上面201のメタライゼーション250に配置されている。はんだ260を配置する工程は、分離路270を作る工程の前または後に行われる。はんだ260は、キャリア200の上面201の実装領域210の一部に延在し、キャリア200の上面201の凹部領域220の一部にも延在しうる。しかしながら、はんだ260は、分離路270が延びるキャリア200の上面201の部分には延在しない。はんだ260を配置する工程は、後にキャリア200の上面201に配置されるオプトエレクトロニクス半導体チップが他の方法で固定され電気コンタクトされる場合には、省くことが可能である。30

## 【0031】

図3は、図1および2に時間的に続く加工状態にあるキャリア200の概略的な側断面図である。

## 【0032】

オプトエレクトロニクス半導体チップ110が、キャリア200の上面201上に配置されている。キャリア200とオプトエレクトロニクス半導体チップ110とは共に、オプトエレクトロニクス部品100を構成する。オプトエレクトロニクス半導体チップ110は、例えばレーザチップでありうる。この場合、オプトエレクトロニクス部品100はレーザ部品である。

## 【0033】

オプトエレクトロニクス半導体チップ110は、キャリア200の上面201の実装領域210上に配置されている。ここで、キャリア200の上面201におけるオプトエレクトロニクス半導体チップ110の位置および/または向きを定めるために、オプトエレクトロニクス半導体チップ110は、分離路270に沿って配置される。

## 【0034】

オプトエレクトロニクス半導体チップ110を分離路270に対して配置するために、少なくとも部分的に実装領域210において完全に切断されたメタライゼーション250と、キャリア200の上面201の凹部領域220において少なくとも完全には切断されていないメタライゼーション250との間の境界280の位置が検出される。検出は、例えばカメラなどで光学的に行われる。少なくとも実装領域210において完全に切断さ4050

れたメタライゼーション 250 と、凹部領域 220 において少なくとも完全には切断されていないメタライゼーション 250 との間の境界 280 では、メタライゼーション 250 とキャリア 200 の露出した材料との間の光学的に明瞭に識別可能なコントラストが生じる。このようなコントラストは光学検出に好適であり、キャリア 200 の上面 201 の段差 230 に対するコントラストの位置が正確に決定される。

#### 【0035】

オプトエレクトロニクス半導体チップ 110 は、段差 230 から突出するようにキャリア 200 の上面 201 上に配置されている。突出長は、分離路 270 でのアラインメント、特に境界 280 でのアラインメントで正確に決定されうる。

#### 【0036】

オプトエレクトロニクス半導体チップ 110 は、上面 111 と、上面 111 と対向する下面 112 を有する。オプトエレクトロニクス半導体チップ 110 は、オプトエレクトロニクス半導体チップ 110 の上面 111 がキャリア 200 の上面 201 と対向するように、キャリア 200 の上面 201 上に配置されている。オプトエレクトロニクス半導体チップ 110 は、キャリア 200 の上面 201 の実装領域 210 に配置されたはんだ 260 に配置され、はんだ 260 によって固定される。キャリア 200 の上面 201 にはんだを配置する工程を省いて、代わりに例えば、キャリア 200 の上面 201 に配置される前のオプトエレクトロニクス半導体チップ 110 の上面 111 にはんだを配置することも可能である。オプトエレクトロニクス半導体チップ 110 を固定するために、はんだ 260 の代わりに、導電性接着剤などの接着剤、または他の固定材料も用いられうる。

10

#### 【0037】

例えばアノードコンタクト部 120 などの、オプトエレクトロニクス半導体チップ 110 の電気部は、オプトエレクトロニクス半導体チップ 110 の上面 111 に形成されうる。この場合、アノードコンタクト部 120 は、はんだ 260 によって、キャリア 200 のメタライゼーション 250 に導電接続される。これにより、メタライゼーション 250 を介してオプトエレクトロニクス半導体チップ 110 の電気駆動が可能となる。

#### 【0038】

オプトエレクトロニクス半導体チップ 110 がレーザチップである場合、キャリア 200 の上面 201 における、凹部領域 220 と実装領域 210 との間の段差 230 から突出するオプトエレクトロニクス半導体チップ 110 の側面が、オプトエレクトロニクス半導体チップ 110 の出射面 130 を形成する。オプトエレクトロニクス半導体チップ 110 は、動作時に出射面 130 において、出射面 130 と垂直な方向に、レーザビームを出射する。ここで、レーザビームが出てくる箇所は、オプトエレクトロニクス半導体チップ 110 の上面 111 の近傍でありうる。

30

#### 【0039】

キャリア 200 の上面 201 における段差 230 から出射面 130 が突出することで、はんだ 260 が出射面 130 に到達することを阻止し、キャリア 200 の上面 201 にオプトエレクトロニクス半導体チップ 110 を固定する工程時における出射面 130 の汚染を防止する。キャリア 200 の上面 201 に作られた凹部領域 220 によって、キャリア集合体 300 の分割工程時に、オプトエレクトロニクス半導体チップ 110 の固定およびアラインメントに悪影響を及ぼしかねない、キャリア 200 の外縁 240 に形成される骨組みが段差 230 の領域に存在しないことが確実となる。

40

#### 【0040】

好ましい例示的な実施形態に基づき、本発明を図示し、より詳細に説明した。しかしながら、本発明は、開示した例に限定されない。むしろ、当業者であれば、開示した例に基づき、本発明の保護範囲から逸脱することなく、他の変形形態を得ることができる。

#### 【0041】

本特許出願は、独国特許出願第 102015116092.7 号の優先権を主張するものであり、この文書の開示内容は参照により本明細書に援用される。

#### 【符号の説明】

50

## 【0042】

- 100 オプトエレクトロニクス部品

110 オプトエレクトロニクス半導体チップ

111 上面

112 下面

120 アノードコンタクト部

130 出射面

200 キャリア

201 上面

210 実装領域

220 凹部領域

230 段差

240 外縁

250 メタライゼーション

260 はんだ

270 分離路

280 境界

300 キャリア集合体

310 分離面 10

【図1】

【図3】

【図2】

---

フロントページの続き

(72)発明者 ウォルター クリストフ

ドイツ国 レーゲンスブルク ギヒトルガッセ 5

(72)発明者 エンツマン ローラント

ドイツ国 レーゲンスブルク オストハイム 1

(72)発明者 ホルン マルクス

ドイツ国 シュトラウビング ヴォルフヴィーゼンシュトラーセ 4

(72)発明者 ザイデンファーデン ヤン

ドイツ国 ノイマルクト イン テア オーバープファルツ ローレンツ - ヒルトナー - シュトラ

-セ 3

審査官 大西 孝宣

(56)参考文献 特開2003-046181(JP,A)

実開平02-072573(JP,U)

特開2009-026819(JP,A)

特開2009-103915(JP,A)

特開2008-016507(JP,A)

米国特許出願公開第2004/0195297(US,A1)

特開2015-019066(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01S 5/00 - 5/50