(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6720532号

(P6720532)

(45) 発行日 令和2年7月8日(2020.7.8)

(24) 登録日 令和2年6月22日(2020.6.22)

|                     |             |

|---------------------|-------------|

| (51) Int.Cl.        | F 1         |

| HO3B 5/32 (2006.01) | HO3B 5/32 A |

| HO3L 1/02 (2006.01) | HO3B 5/32 H |

|                     | HO3L 1/02   |

請求項の数 15 (全 41 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2016-1318 (P2016-1318)      |

| (22) 出願日  | 平成28年1月6日(2016.1.6)           |

| (65) 公開番号 | 特開2017-123552 (P2017-123552A) |

| (43) 公開日  | 平成29年7月13日(2017.7.13)         |

| 審査請求日     | 平成30年12月18日(2018.12.18)       |

|           |                                              |

|-----------|----------------------------------------------|

| (73) 特許権者 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区新宿四丁目1番6号 |

| (74) 代理人  | 100104710<br>弁理士 竹腰 昇                        |

| (74) 代理人  | 100090479<br>弁理士 井上 一                        |

| (74) 代理人  | 100124682<br>弁理士 黒田 泰                        |

| (72) 発明者  | 米澤 岳美<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内       |

| 審査官       | 橋本 和志                                        |

最終頁に続く

(54) 【発明の名称】回路装置、発振器、電子機器及び移動体

## (57) 【特許請求の範囲】

## 【請求項 1】

恒温槽内に設けられる回路装置の外部に設けられる外部温度センサーからの温度検出電圧が入力される温度センサー入力端子と、

前記温度検出電圧をA/D変換して温度検出データを出力するA/D変換部と、

前記温度検出データに基づいて、周波数制御データを生成する処理部と、

前記周波数制御データ及び前記恒温槽内に設けられる振動子を用いて、前記周波数制御データに対応する発振周波数の発振信号を生成する発振信号生成回路と、

を含み、

前記外部温度センサーは、前記回路装置の位置における温度変化よりも温度変化が大きい位置に設けられることを特徴とする回路装置。

## 【請求項 2】

恒温槽内に設けられる回路装置の外部に設けられる外部温度センサーからの温度検出電圧が入力される温度センサー入力端子と、

前記温度検出電圧をA/D変換して温度検出データを出力するA/D変換部と、

前記温度検出データに基づいて、周波数制御データを生成する処理部と、

前記周波数制御データ及び前記恒温槽内に設けられる振動子を用いて、前記周波数制御データに対応する発振周波数の発振信号を生成する発振信号生成回路と、

を含み、

前記外部温度センサーは、前記恒温槽の外部に設けられることを特徴とする回路装置。

10

20

## 【請求項 3】

請求項 1 又は 2 に記載の回路装置において、

前記温度検出電圧は、前記温度センサー入力端子からプログラマブルゲインアンプを介して前記 A / D 変換部に入力されることを特徴とする回路装置。

## 【請求項 4】

請求項 1 乃至 3 のいずれか一項に記載の回路装置において、

前記 A / D 変換部からの前記温度検出データは、デジタルフィルター部を介して前記処理部に入力されることを特徴とする回路装置。

## 【請求項 5】

請求項 1 乃至 4 のいずれか一項に記載の回路装置において、

内部温度センサーを含み、

前記 A / D 変換部は、

第 1 のモードでは、前記内部温度センサーからの内部温度検出電圧を A / D 変換し、

第 2 のモードでは、前記外部温度センサーからの前記温度検出電圧を A / D 変換することを特徴とする回路装置。

## 【請求項 6】

請求項 1 乃至 5 のいずれか一項に記載の回路装置において、

前記処理部は、

前記温度検出電圧により求められる前記温度検出データに基づいて、エージング変動成分と温度変動成分を含む、前記周波数制御データの変動成分から、前記エージング変動成分を抽出して、抽出した前記エージング変動成分に基づいて前記周波数制御データのエージング補正処理を行うことを特徴とする回路装置。

## 【請求項 7】

請求項 1 乃至 6 のいずれか一項に記載の回路装置において、

前記振動子及び前記回路装置は、前記恒温槽であるシングルオープン内に設けられることを特徴とする回路装置。

## 【請求項 8】

請求項 1 乃至 6 のいずれか一項に記載の回路装置において、

前記振動子及び前記回路装置は、前記恒温槽である第 1 恒温槽と前記第 1 恒温槽を収容する第 2 恒温槽とを含むダブルオープンの前記第 1 恒温槽内に設けられることを特徴とする回路装置。

## 【請求項 9】

請求項 8 に記載の回路装置において、

前記外部温度センサーは、前記第 2 恒温槽の外部に設けられることを特徴とする回路装置。

## 【請求項 10】

請求項 8 に記載の回路装置において、

前記外部温度センサーは、前記第 1 恒温槽と前記第 2 恒温槽の間に設けられることを特徴とする回路装置。

## 【請求項 11】

請求項 1 乃至 10 のいずれか一項に記載の回路装置において、

前記振動子に対応して設けられたヒーターを制御するオープン制御回路を含むことを特徴とする回路装置。

## 【請求項 12】

請求項 1 乃至 11 のいずれか一項に記載の回路装置と、

前記外部温度センサーと、

前記振動子と、

前記振動子に対応して設けられたヒーターと、

を含むことを特徴とする発振器。

## 【請求項 13】

10

20

30

40

50

請求項 1 2 に記載の発振器において、

前記振動子と前記回路装置との間の距離を  $L_1$  とし、前記振動子と、前記外部温度センサーとの距離を  $L_2$  とした場合に、  $L_2 > L_1$  であることを特徴とする発振器。

【請求項 1 4】

請求項 1 乃至 1 1 のいずれか一項に記載の回路装置を含むことを特徴とする電子機器。

【請求項 1 5】

請求項 1 乃至 1 1 のいずれか一項に記載の回路装置を含むことを特徴とする移動体。

【発明の詳細な説明】

【技術分野】

10

【0 0 0 1】

本発明は、回路装置、発振器、電子機器及び移動体等に関する。

【背景技術】

【0 0 0 2】

従来より、OCXO (oven controlled crystal oscillator)、TCXO (temperature compensated crystal oscillator) 等の発振器が知られている。例えばOCXOは、基地局、ネットワークルーター、測定機器等における基準信号源として用いられている。

【0 0 0 3】

このような発振器の従来技術としては、例えば特許文献 1 に開示される技術がある。この従来技術では、発振周波数の高精度化のために、発振周波数のエージング補正を行っている。具体的には、発振周波数の制御電圧の補正值と経過時間との対応関係情報を記憶する記憶部と、経過時間計測部を設ける。そして、記憶部に記憶された補正值と経過時間との対応関係情報を、経過時間計測部により測定された経過時間に基づいて、エージング補正を実行する。

【先行技術文献】

【特許文献】

【0 0 0 4】

【特許文献 1】特開 2015 - 82815 号公報

20

【発明の概要】

【発明が解決しようとする課題】

30

【0 0 0 5】

このように、OCXO、TCXO 等の発振器では、発振信号の発振周波数の高精度化に対する要求がある。

【0 0 0 6】

このような発振器において、より精度の高い発振周波数を得るには、恒温槽により振動子の温度が制御されているOCXOが望ましい。OCXOでは振動子の温度が制御されているが、実際には恒温槽の周囲の環境温度が変動すると、その影響で振動子の温度が変動し、発振周波数がわずかにながら変動する。そのため、更に精度の高い発振周波数を得るには温度補償が必要である。温度補償は、振動子の温度変動による発振周波数の変動を低減するものである。即ち、温度補償では、振動子の温度を温度センサーにより測定し、その測定された温度に基づいて発振周波数が一定になるように制御する。温度センサーは、例えば発振信号を生成する回路装置に設けられているが、振動子の温度を測定できるように回路装置（温度センサー）は恒温槽内に設けられている。

40

【0 0 0 7】

しかしながら、上述したように基本的には恒温槽内は温度が制御されている。そのため、環境温度の影響を受けるとはいえ、回路装置に内蔵の温度センサーだけを用いると環境温度の変動によるセンシング温度の変動範囲は小さくなり、高精度な温度補償ができない。例えば、温度センサーのセンシング電圧は A / D 変換回路により A / D 変換され、その温度検出データが温度補償に用いられる。この場合、センシング電圧の変動範囲が A / D 変換回路の入力フルスケールに対して非常に小さくなるので、A / D 変換回路の分解能が

50

粗くなり（センシング電圧の変動範囲に対応するコード変動範囲が小さくなり）、高精度な温度補償ができないおそれがあった。

#### 【0008】

本発明の幾つかの態様によれば、発振周波数の温度依存性が小さい高安定な発振周波数を得ることができる回路装置、発振器、電子機器及び移動体等を提供できる。

#### 【課題を解決するための手段】

#### 【0009】

本発明の一態様は、温度検出電圧をA/D変換して温度検出データを出力するA/D変換部と、前記温度検出データに基づいて、発振周波数の温度補償の信号処理を行う処理部と、周波数制御データ及び恒温槽内に設けられるオープン型振動子を用いて、前記周波数制御データに対応する前記発振周波数の発振信号を生成する発振信号生成回路と、回路装置の外部に設けられる外部温度センサーからの前記温度検出電圧を入力するための温度センサー入力端子と、を含む回路装置に関係する。10

#### 【0010】

本発明の一態様によれば、回路装置の外部に外部温度センサーを設け、その外部温度センサーからの温度検出電圧を温度センサー入力端子から回路装置に入力し、その入力された温度検出電圧をA/D変換して温度検出データを出力し、その温度検出データに基づいて、発振周波数の温度補償の信号処理を行うことができる。これにより、回路装置に温度センサーを内蔵した場合に比べて、センシング温度の変動範囲を大きくし、温度検出データの温度分解能を向上できる。そして、その高い温度分解能の温度検出データを用いて温度補償処理を行うことで、発振周波数の温度依存性が小さい高安定な発振周波数を得ることができる。20

#### 【0011】

また本発明の一態様では、前記温度検出電圧は、前記温度センサー入力端子からプログラマブルゲインアンプを介して前記A/D変換部に入力されてもよい。

#### 【0012】

外部温度センサーとしては、種々の特性（例えば感度や出力電圧範囲等）が異なる温度センサーが接続される可能性がある。このように、温度センサー入力端子を設けたことによって、多様な特性の温度センサーが接続される可能性がある。この点、本発明の一態様によれば、A/D変換部の前段にプログラマブルゲインアンプを設けたことで、多様な特性の温度センサーに対応してゲイン調整できる。30

#### 【0013】

また本発明の一態様では、前記A/D変換部からの前記温度検出データは、デジタルフィルター部を介して前記処理部に入力されてもよい。

#### 【0014】

外部温度センサーや内部温度センサーからの温度検出電圧にはノイズが含まれている。また、プログラマブルゲインアンプを設けたので、そのゲインによって温度検出電圧のノイズが増幅される。ノイズを含んだ温度検出電圧で温度補償処理を行うと、周波数制御データにもノイズが含まれることになり、発振信号の特性（例えば位相ノイズ）を低下させる。この点、本発明の一態様によれば、デジタルフィルター部により温度検出データをフィルター処理できるので、温度検出データのノイズ（温度検出電圧のノイズ）を低減できる。40

#### 【0015】

また本発明の一態様では、回路装置は、内部温度センサーを含み、前記A/D変換部は、第1のモードでは、前記内部温度センサーからの内部温度検出電圧を、前記温度検出電圧としてA/D変換を行い、第2のモードでは、前記外部温度センサーから前記温度センサー入力端子を介して入力される外部温度検出電圧を前記温度検出電圧としてA/D変換を行ってもよい。

#### 【0016】

このようにすれば、例えば発振器の用途等に応じて適切な温度センサーを選択できる。50

例えば、外部温度センサーを設けずにコスト削減したい場合には内部温度センサーを選択できる。一方、高精度な発振周波数を得たい場合には外部温度センサーを選択できる。そして、本発明の一態様では、プログラマブルゲインアンプを設けたことで、このような種々の温度センサーに対応できる。

#### 【0017】

また本発明の一態様では、前記処理部は、前記温度検出電圧により求められる前記温度検出データに基づいて、エージング変動成分と温度変動成分を含む、前記周波数制御データの変動成分から、前記エージング変動成分を抽出して、抽出した前記エージング変動成分に基づいて前記周波数制御データのエージング補正処理を行ってもよい。

#### 【0018】

本発明の一態様では、温度センサー入力端子を設けたことで外部温度センサーを用いることが可能であり、それによって温度補償における周波数補正誤差を抑制できる。即ち、エージング変動成分と温度変動成分を含む周波数制御データの変動成分からエージング変動成分を抽出する際に、正確に温度変動成分を除去して正確にエージング変動成分を抽出できる。

#### 【0019】

また本発明の一態様では、前記オープン型振動子は、ダブルオープン型振動子であってもよい。

#### 【0020】

ダブルオープン型振動子を用いることで振動子の温度変動を小さくし、発振周波数の変動を抑制できる。しかしながら、ダブルオープン内では温度変動が小さいので、回路装置に内蔵された温度センサーを用いると温度補償における周波数補正誤差が大きくなる。この点、本発明の一態様によれば、温度センサー入力端子を設けたことで、ダブルオープン外に外部温度センサーを設けることが可能となり、温度補償における周波数補正誤差を小さくできる。

#### 【0021】

また本発明の一態様では、回路装置は、前記オープン型振動子に対応して設けられたヒーターを制御するオープン制御回路を含んでもよい。

#### 【0022】

オープン制御回路によりヒーターの発熱を制御することで、振動子の温度が管理されたオープン型振動子を実現できる。このような温度が管理されたオープン内では温度変動が小さいが、本発明の一態様によれば恒温槽の外に外部温度センサーを設けることが可能となるので、高精度な温度補償が可能である。

#### 【0023】

また本発明の他の態様は、上記のいずれかに記載の回路装置と、前記外部温度センサーと、前記オープン型振動子と、前記オープン型振動子に対応して設けられたヒーターと、を含む発振器に関係する。

#### 【0024】

また本発明の他の態様では、前記オープン型振動子と前記回路装置との間の距離をL1とし、前記オープン型振動子と、前記外部温度センサーとの距離をL2とした場合に、L2 > L1であってもよい。

#### 【0025】

オープン型振動子から近いほど温度が適切に調整されており、オープン型振動子から遠いほど環境温度の変動により温度が変動しやすくなる。この点、本発明の他の態様によれば、回路装置よりも外部温度センサーの方がオープン型振動子よりも遠い。また、このような外部温度センサーからの温度検出電圧を入力するための温度センサー入力端子が回路装置に設けられている。これにより、外部温度センサーを用いて変動範囲が広い温度変化を検出することが可能となり、その温度検出電圧を用いることで正確な温度補償処理が可能となる。

#### 【0026】

10

20

30

40

50

また本発明の更に他の態様は、上記のいずれかに記載の回路装置を含む電子機器に関する。

【0027】

また本発明の更に他の態様は、上記のいずれかに記載の回路装置を含む移動体に関する。

【図面の簡単な説明】

【0028】

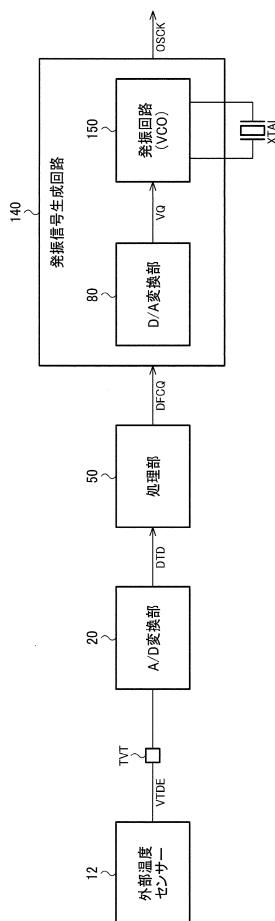

【図1】本実施形態の回路装置の構成例。

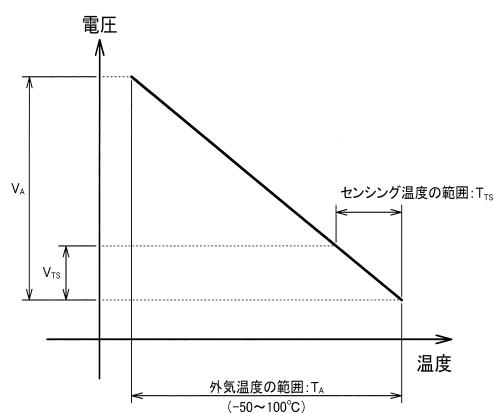

【図2】温度センサーが output する温度検出電圧の特性例。

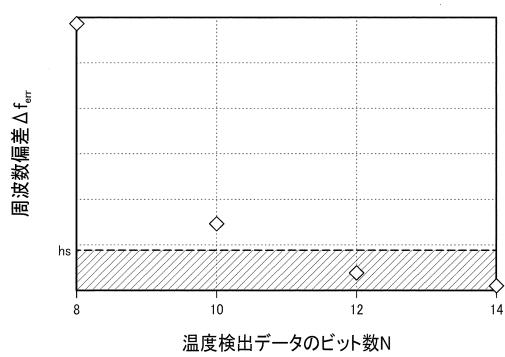

【図3】温度検出データのビット数に対する周波数偏差の特性例。

10

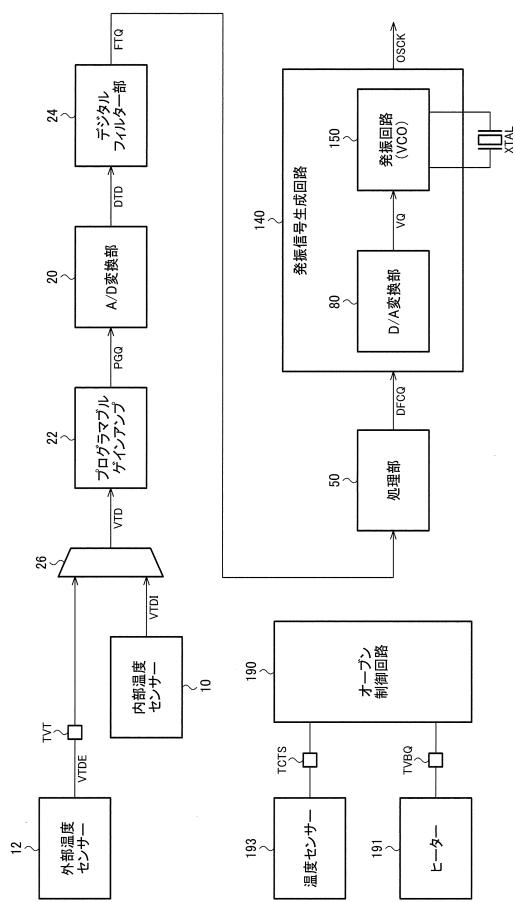

【図4】本実施形態の回路装置の詳細な構成例。

【図5】プログラマブルゲインアンプのゲイン設定例。

【図6】プログラマブルゲインアンプの詳細な構成例。

【図7】オープン制御回路の第1の詳細な構成例。

【図8】オープン制御回路の第2の詳細な構成例。

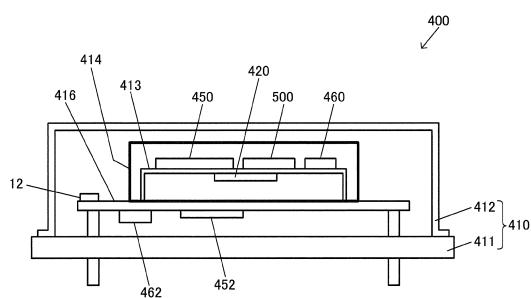

【図9】発振器の詳細な構造例。

【図10】図10A、図10Bは、発振器の変形構造例。

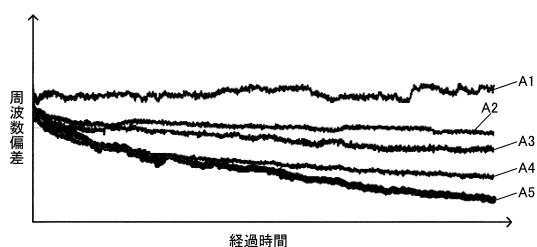

【図11】エージング特性の素子ばらつきについての説明図。

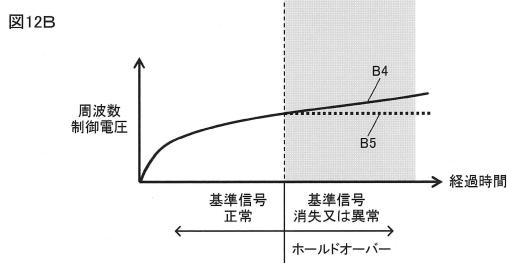

【図12】図12A、図12Bはホールドオーバーについての説明図。

【図13】本実施形態の回路装置の詳細な構成例。

20

【図14】図14A、図14Bはカルマンフィルター処理を用いたエージング補正の説明図。

【図15】処理部の詳細な構成例。

【図16】図16A、図16Bは処理部の動作説明図。

【図17】エージング補正部の構成例。

【図18】図18A、図18Bは温度センサー、発振回路の構成例。

【図19】図19A、図19Bは本実施形態の変形例の説明図。

【図20】図20A、図20B、図20Cは発振器、電子機器、移動体の構成例。

【図21】電子機器の1つである基地局の構成例。

【発明を実施するための形態】

30

【0029】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

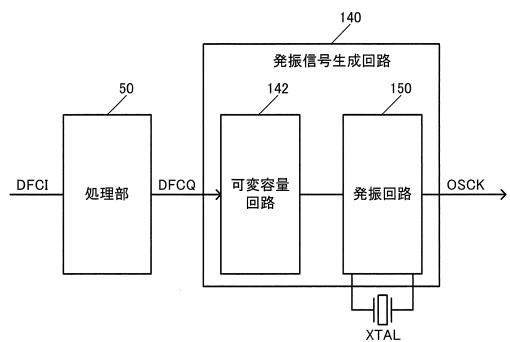

【0030】

1. 構成

図1に、本実施形態の回路装置の構成例を示す。回路装置は、温度センサー入力端子T<sub>VT</sub>、A/D変換部20（A/D変換器、A/D変換回路）、処理部50（デジタル信号処理部、処理回路）、発振信号生成回路140を含む。

【0031】

40

外部温度センサー12（第1温度センサー）は、環境の温度に応じて変化する温度依存電圧を、温度検出電圧V<sub>TDE</sub>として出力する。外部温度センサー12は、回路装置の外部に設けられる。回路装置は例えば半導体チップであり、その半導体チップの外部或いは半導体チップを収納したパッケージの外部に、外部温度センサー12が設けられる。具体的には、環境温度（例えば、回路装置と振動子XTALを収納した発振器のパッケージの外側の温度、或いは恒温槽の外側の温度）が変化した場合において、回路装置の位置における温度変化よりも温度変化が大きい位置に、外部温度センサー12が設けられる。例えば、図9～図10Bで後述するように、回路装置500は恒温槽（例えば第2の容器414）の内部に設けられる。そして、外部温度センサー12は、発振器のパッケージ410の外部、或いは発振器のパッケージ410の内部で恒温槽（例えば第2の容器414）の

50

外部に設けられる。例えば外部温度センサー 12 としては、サーミスター やダイオード(広義には P N 接合)等を用いることができる。

#### 【0032】

A / D 変換部 20 には、外部温度センサー 12 からの温度検出電圧 V T D E が温度センサー入力端子 T V T を介して入力される。A / D 変換部 20 は、その温度検出電圧 V T D E の A / D 変換を行って、温度検出データ D T D を出力する。例えば温度検出電圧 V T D E の A / D 変換結果に対応するデジタルの温度検出データ D T D (A / D 結果データ)を出力する。A / D 変換部 20 の A / D 変換方式としては、例えば逐次比較方式や逐次比較方式に類似する方式などを採用できる。なお A / D 変換方式はこのような方式には限定されず、種々の方式(計数型、並列比較型又は直並列型等)を採用できる。

10

#### 【0033】

処理部 50 は種々の信号処理(デジタル信号処理)を行う。例えば処理部 50 は、温度検出データ D T D に基づいて発振周波数(発振信号の周波数)の温度補償処理を行う。具体的には処理部 50 は、温度に応じて変化する温度検出データ D T D と、温度補償処理用の係数データ(近似関数の係数のデータ)などに基づいて、温度変化があった場合に発振周波数の変動を小さくするための温度補償処理を行う。また処理部 50 は、必要に応じて例えばエージング補正処理、カルマンフィルター処理などの信号処理を行ってもよい。そして信号処理後の周波数制御データ D F C Q(周波数制御コード)を出力する。この処理部 50 は、ゲートアレイ等の A S I C 回路により実現してもよいし、プロセッサー(D S P、C P U)とプロセッサー上で動作するプログラム(プログラムモジュール)により実現してもよい。

20

#### 【0034】

振動子 X T A L は、例えば A T カットタイプや S C カットタイプなどの厚みすべり振動タイプの水晶振動子等や屈曲振動タイプなどの圧電振動子である。振動子 X T A L は、オーブン型発振器(O C X O)の恒温槽内に設けられるタイプである。振動子 X T A L は共振器(電気機械的な共振子又は電気的な共振回路)であってもよい。なお振動子 X T A L としては、圧電振動子として、S A W (Surface Acoustic Wave)共振子、シリコン製振動子としての M E M S (Micro Electro Mechanical Systems)振動子等を採用できる。振動子 X T A L の基板材料としては、水晶、タンタル酸リチウム、ニオブ酸リチウム等の圧電単結晶や、ジルコン酸チタン酸鉛等の圧電セラミックス等の圧電材料、又はシリコン半導体材料等を用いることができる。振動子 X T A L の励振手段としては、圧電効果によるものを用いてもよいし、クーロン力による静電駆動を用いてもよい。

30

#### 【0035】

発振信号生成回路 140 は発振信号 O S C K を生成する。例えば発振信号生成回路 140 は、処理部 50 からの周波数制御データ D F C Q と振動子 X T A L を用いて、周波数制御データ D F C Q により設定される発振周波数の発振信号 O S C K を生成する。一例としては、発振信号生成回路 140 は、周波数制御データ D F C Q により設定される発振周波数で振動子 X T A L を発振させて、発振信号 O S C K を生成する。

#### 【0036】

なお発振信号生成回路 140 は、ダイレクト・デジタル・シンセサイザー方式で発振信号 O S C K を生成する回路であってもよい。例えば振動子 X T A L(固定発振周波数の発振源)の発振信号をリファレンス信号として、周波数制御データ D F C Q で設定される発振周波数の発振信号 O S C K をデジタル的に生成してもよい。

40

#### 【0037】

発振信号生成回路 140 は、D / A 変換部 80 と発振回路 150 を含むことができる。但し発振信号生成回路 140 は、このような構成には限定されず、その一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

#### 【0038】

D / A 変換部 80 は、処理部 50 からの周波数制御データ D F C Q(処理部の出力データ)の D / A 変換を行う。D / A 変換部 80 の D / A 変換方式としては例えば抵抗ストリ

50

ング型（抵抗分割型）を採用できる。但し、D/A変換方式はこれには限定されず、抵抗ラダー型（R-2Rラダー型等）、容量アレイ型、又はパルス幅変調型などの種々の方式を採用できる。またD/A変換部80は、D/A変換器以外にも、その制御回路や変調回路（ディザイア調又はPWM変調等）やフィルター回路などを含むことができる。

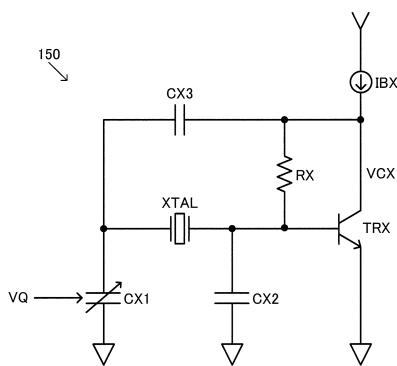

【0039】

発振回路150は、D/A変換部80の出力電圧VQと振動子XTALを用いて、発振信号OSCKを生成する。発振回路150は、第1、第2の振動子用端子（振動子用パッド）を介して振動子XTALに接続される。例えば発振回路150は、振動子XTAL（圧電振動子、共振子等）を発振させることで、発振信号OSCKを生成する。具体的には発振回路150は、D/A変換部80の出力電圧VQを周波数制御電圧（発振制御電圧）とした発振周波数で、振動子XTALを発振させる。例えば発振回路150が、電圧制御により振動子XTALの発振を制御する回路（VCO）である場合には、発振回路150は、周波数制御電圧に応じて容量値が変化する可変容量キャパシター（バリキャップ等）を含むことできる。

【0040】

なお、前述のように発振回路150はダイレクト・デジタル・シンセサイザ方式により実現してもよく、この場合には振動子XTALの発振周波数はリファレンス周波数となり、発振信号OSCKの発振周波数とは異なる周波数になる。

【0041】

以上の本実施形態によれば、回路装置は、温度検出電圧VTEDをA/D変換して温度検出データDTDを出力するA/D変換部20と、温度検出データDTDに基づいて、発振周波数の温度補償の信号処理を行う処理部50と、周波数制御データDFCQ及び恒温槽内に設けられるオープン型振動子XTALを用いて、周波数制御データDFCQに対応する発振周波数の発振信号OSCKを生成する発振信号生成回路140と、回路装置の外部に設けられる外部温度センサー12からの温度検出電圧VTEDを入力するための温度センサー入力端子TVTと、を含む。

【0042】

このように温度センサー入力端子TVTを設けることで、回路装置の外部に外部温度センサー12を設けることが可能となる。具体的には、環境温度（外気温度）の変化に対してセンシング温度の変化が大きい位置（例えば恒温槽の外）に外部温度センサー12を設けることが可能となる。これにより、センシング温度の変動範囲が大きくなるので、温度検出電圧VTEDの変動範囲が大きくなり、温度検出データDTDの分解能（1 LSBに対応する温度変化）を向上できる。温度検出データDTDの分解能が高いということは、より小さい温度変化に追従して発振周波数を温度補償できるということであり、より小さい周波数補正誤差での温度補償を実現できる。

【0043】

例えば、基地局等の基準信号源として発振器を用いる場合、PLL回路により発振周波数を基準信号（例えばGPS信号）に同期させる。基準信号が何らかの理由により消失又は異常となった場合には、PLL回路がホールドオーバーとなり発振回路150は自走発振する。このホールドオーバー状態では、温度補償における周波数補正誤差が自走発振の周波数誤差（偏差）の要因の一つとなり、その誤差が時刻情報（発振信号のパルスの数）の誤差として、時間と共に蓄積される。例えば、後述するTDD方式の通信等では高精度な時刻同期が要求されるが、温度補償における周波数補正誤差が大きいと、時刻同期が取れなくなる可能性がある。この点、本実施形態では外部温度センサー12を用いて高精度な温度補償を実現できる（周波数補正誤差を小さくできる）。

【0044】

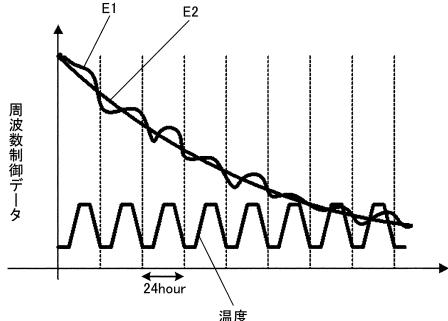

図2、図3を用いて、より具体的に説明する。図2は、温度センサーが输出する温度検出電圧の特性例である。例えば、温度検出電圧は温度に対して負の傾きで線形（一次関数）に変化する。

【0045】

10

20

30

40

50

環境温度の一例として、発振器のパッケージの外側の気温である外気温度を想定する。例えば発振器の仕様等に応じて、外気温度の変動範囲  $T_A$  は -50 度 ~ 100 度であると想定できる（なお、温度は摂氏で表すものとする）。その外気温度の変動範囲  $T_A$  に対して温度検出電圧の変動範囲を  $V_A$  とする。

【0046】

一方、温度センサーが設けられた位置での温度は、その位置に応じて変動範囲  $T_{TS}$  が異なっている。温度補償は、振動子の温度変化による発振周波数の変化を補償するものなので、従来は温度センサーは振動子の近くに設けられていた。例えば図9の発振器を例にとると、従来は温度センサーが回路装置500に内蔵されており、その回路装置500が振動子420と共に恒温槽（例えば第2の容器414）の中に収納されていた。

10

【0047】

しかしながら、恒温槽の中に温度センサー（回路装置500）が設けられた場合、その位置でのセンシング温度の変動範囲  $T_{TS}$  は、外気温度の変動範囲  $T_A$  よりも非常に小さくなる。例えば、図9のような2つのヒーター450、452で恒温槽内の温度を管理するダブルオーブン型のOCXOでは、恒温槽内の温度の変動範囲  $T_{TS}$  は非常に小さくなり、例えば変動範囲  $T_{TS}$  は85度 ~ 95度である。図2に示すように、このセンシング温度の変動範囲  $T_{TS}$  に対する温度検出電圧の変動範囲を  $V_{TS}$  とする。 $T_{TS}$ 、 $T_A$ 、 $V_{TS}$ 、 $V_A$  の幅（範囲の上限から下限を減算した値）を  $T_{TS}$ 、 $T_A$ 、 $V_{TS}$ 、 $V_A$  とすると、上記の例では  $V_{TS} / V_A = T_{TS} / T_A = 10 / 150 = 1 / 15$  となる。即ち、外気中に温度センサーを置いた場合に比べて恒温槽内に温度センサーを置いた場合には、温度検出電圧の変動範囲が  $1 / 15$  になってしまうということである。

20

【0048】

例えば、外気温度での電圧変動幅  $V_A$  に対して A/D 変換部20の出力データ DTD（温度検出データ）の変動幅が  $2^{12}$  であるとする。この場合、 $V_{TS} / V_A = 1 / 15$  なので、センシング温度での電圧変動幅  $V_{TS}$  に対して温度検出データ DTD の変動幅は約  $2^8$  となる。即ち、A/D 変換部20の実効的なビット数が4ビット小さくなつたことと同じであり、実現したい周波数精度（温度補償後の発振周波数の偏差）に対して A/D 変換部20の分解能が不足してしまう。

30

【0049】

具体的には、温度補償処理において温度誤差  $T_{err}$  [度] で生じる周波数補正誤差  $f_{err}$  [ppb] (ppb: parts per billion) は、下式(24)のように近似できる。例えばオーブン型振動子XTALの温度特性が、温度変動範囲  $T_A$  の半分の間隔で極大値と極小値を有すると共に、線形に変化するものと仮定した場合に、下式(24)によく近似できる。 $f_{err}$  は、公称発振周波数に対する偏差 ( $f / f$ ) で表している。 $f_w$  は、処理部50による温度補償処理を行わなかった場合において、外気温度が範囲  $T_A$  で変動した場合の発振周波数の偏差である。

$$f_{err} = 2 \times f_w / T_A \times T_{err} \quad (24)$$

【0050】

温度誤差  $T_{err}$  が、A/D 変換部20の温度分解能 (1 LSB に対応する温度変化、温度ステップ) に起因するものとする。A/D 変換部20の出力データ（温度検出データ）のビット数を  $N$  とすると、温度誤差  $T_{err}$  は下式(25)となる。

$$T_{err} = T_A / 2^N \quad (25)$$

【0051】

上式(24)、(25)から、A/D 変換部20の温度分解能に起因する周波数補正誤差  $f_{err}$  は下式(26)となる。

$$f_{err} = f_w / 2^{N-1} \quad (26)$$

【0052】

図3は、温度検出データのビット数  $N$  に対する周波数偏差  $f_{err}$  の特性例（上式(26)の関係）である。

50

## 【0053】

図3に示すように、例えば周波数補正誤差を  $f_{err} < h_s = f_w / 1000$  にしたいとする。この場合、上式(26)からA/D変換部20に求められるビット数Nは12ビット以上となる。

## 【0054】

図2で説明したように、外気温度をセンシングした場合のA/D変換部20の(実効的な)ビット数がN=12である場合、ダブルオープン型の恒温槽内でセンシングした場合のA/D変換部20の(実効的な)ビット数はおよそN=8となる。これを図3の例に当てはめると、ダブルオープン型の恒温槽内でセンシングした場合には所望の周波数偏差  $h_s$  を得られないことが分かる。

10

## 【0055】

N=8の場合の周波数補正誤差  $f_{err}$  は、N=12の場合の周波数補正誤差  $f_{err}$  の16倍となる。下式(1)、(2)で後述するように、発振回路150が自走発振するホールドオーバーでは、周波数補正誤差等に起因する周波数変動で、公称発振周波数に対する周波数偏差が蓄積していく(経過時間  $T_1$  が長くなるにつれてホールドオーバー時間  $t_{tot}$  は2次関数的に長くなる)。即ち、16倍の周波数補正誤差  $f_{err}$  は、ホールドオーバーにおける時刻情報の誤差を非常に大きくしてしまう。

## 【0056】

例えば、恒温槽内で温度センシングする場合であっても、温度センサーの出力をアンプ等によって増幅し、温度検出データの温度分解能(A/D変換部20の実効的なビット数N)を上げる手法が考えられる。しかしながら、小さな電圧変化を高いゲインで増幅することになるため、信号のS/Nが低下するという問題がある。温度検出電圧のS/Nが低いと、温度補償後の周波数制御データDFCQのノイズも大きくなるため、発振信号OSCCKの位相ノイズが大きくなってしまう。

20

## 【0057】

この点、本実施形態では温度センサー入力端子TWTを設けたことで、外部温度センサー12を温度変化が大きい位置に設けることが可能である。これにより、温度補償における周波数補正誤差  $f_{err}$  を小さくできる。例えばホールドオーバーにおけるホールドオーバー時間(時刻情報の誤差)が小さくなり、TDD方式の通信における高精度な時刻同期等を実現できる。

30

## 【0058】

## 2.回路装置の詳細構成

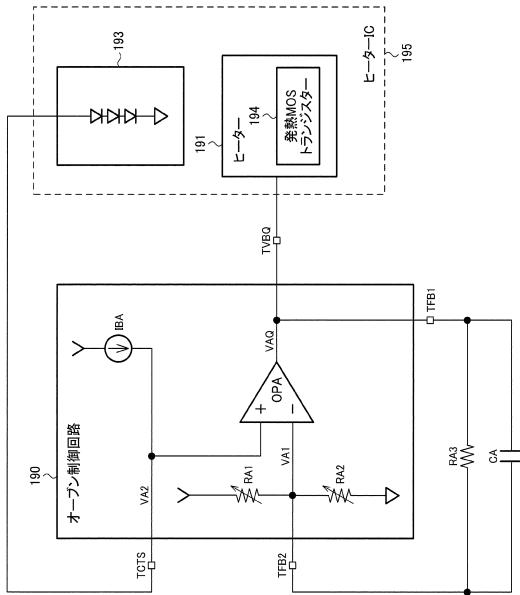

図4に、本実施形態の回路装置の詳細な構成例を示す。図4の回路装置は、図1に対して内部温度センサー10(第2温度センサー)、セレクター26、プログラマブルゲインアンプ22(PGA、アンプ回路)、デジタルフィルター部24(デジタルフィルター)、オープン制御回路190(ヒーター制御回路)を含む。

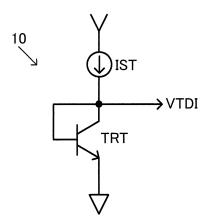

## 【0059】

内部温度センサー10は、温度検出電圧VTDIを出力する。具体的には、環境(回路装置)の温度に応じて変化する温度依存電圧を、温度検出電圧VTDIとして出力する。内部温度センサー10の具体的な構成例については後述する。

40

## 【0060】

セレクター26は、外部温度センサー12(温度センサー入力端子TWT)からの温度検出電圧VTED又は内部温度センサー10からの温度検出電圧VTDIのいずれかを選択し、選択した温度検出電圧を温度検出電圧VTDとして出力する。例えば、いずれの温度センサーを選択するかの設定情報が外部装置からレジスター部(例えば図13のレジスター部32)に設定され、その設定情報に基づいてセレクター26が温度検出電圧VTED、VTDIのいずれかを選択する。或いは、設定情報を記憶部(例えば図13の記憶部34)に予め記憶させておいてもよい。或いは、回路装置は不図示の設定端子を含み、その設定端子には外部装置等から設定電圧が入力され、その設定電圧に基づいてよりセレクター26が温度検出電圧VTED、VTDIのいずれかを選択する。

50

## 【0061】

プログラマブルゲインアンプ22は、セレクター26からの温度検出電圧VTDを可変のゲインで増幅し、増幅後の電圧PGQを出力する。A/D変換部20は、電圧PGQのA/D変換を行って、温度検出データDTDを出力する。プログラマブルゲインアンプ22の具体的な構成例については後述する。

## 【0062】

デジタルフィルター部24は、A/D変換部20からの温度検出データDTDに対してデジタルフィルター処理を行い、処理後のデータFTQを出力する。処理部50は、データFTQに基づいて発振周波数の温度補償処理を行い、処理後の周波数制御データDFCQを出力する。デジタルフィルター部24は、例えばローパスフィルター特性のデジタルフィルターである。例えば、IIR (Infinite Impulse Response)型の1次ローパスフィルターであり、その場合の伝達関数Hは、下式(27)である。

$$H = (a_0 + a_1 \times z^{-1}) / (1 + b_1 \times z^{-1}) \quad (27)$$

## 【0063】

$a_0$ 、 $a_1$ 、 $b_1$ は係数である。デジタルフィルター部24のサンプリング周波数をfsとし、1次ローパスフィルター特性のカットオフ周波数をfcとし、 $= 2 \pi f_c / f_s$ と定義する。双1次変換を用いた場合、係数は $a_0 = a_1 = 1 / (2 + \pi)$ 、 $b_1 = - (2 - \pi) / (2 + \pi)$ である。これらの係数は固定であってもよいし、レジスター部や記憶部(図13のレジスター部32、記憶部34)に可変に設定可能であってもよい。

## 【0064】

デジタルフィルター部24は、ゲートアレイ等のASIC回路により実現してもよいし、プロセッサー(DSP、CPU)とプロセッサー上で動作するプログラム(プログラムモジュール)により実現してもよい。例えば、処理部50と一体のゲートアレイやプロセッサーで実現されてもよい。

## 【0065】

オープン制御回路190は、恒温槽を有するオープン型の振動子XTAL(ダブルオープン、シングルオープン等)のオープン制御を行う。例えばオープン制御回路190は、オープン温度の調整用のヒーター191(発熱素子)の発熱を制御する。具体的には、ヒーター191に対応して設けられるオープン制御用の温度センサー193を用いて、ヒーター191の発熱を制御する。そしてオープン温度が設定温度になるように温度調整を行う。ヒーター191、温度センサー193は回路装置の外部に設けられる。オープン制御回路190には、接続端子TCTSを介して温度センサー193からの温度検出電圧が入力され、オープン制御回路190は、出力端子TVBQを介してヒーター制御電圧をヒーター191に出力する。オープン制御回路190、ヒーター191、温度センサー193の具体的な構成例については後述する。

## 【0066】

1つのヒーターでオープン制御される(恒温槽が1重の)シングルオープンでは、1組のヒーター191、温度センサー193、端子TCTS、TVBQが設けられる。2つのヒーターでオープン制御される(恒温槽が2重の)ダブルオープンでは、2組のヒーター191、温度センサー193、端子TCTS、TVBQが設けられる。ダブルオープンの場合、2組のヒーター191、温度センサー193は同一のタイプのヒーター、温度センサーであってもよいし、異なるタイプのヒーター、温度センサーであってもよい。

## 【0067】

以上の実施形態によれば、温度検出電圧VTD-Eは、温度センサー入力端子TVTからプログラマブルゲインアンプ22を介してA/D変換部20に入力される。

## 【0068】

具体的には、セレクター26により外部温度センサー12が選択されている場合には、温度センサー入力端子TVTからの温度検出電圧VTD-Eがプログラマブルゲインアンプ22を介してA/D変換部20に入力される。またセレクター26により内部温度センサー10が選択されている場合には、内部温度センサー10からの温度検出電圧VTD-Iが

10

20

30

40

50

プログラマブルゲインアンプ 2 2 を介して A / D 変換部 2 0 に入力される。

【 0 0 6 9 】

外部温度センサー 1 2 としては、種々の特性（例えば感度や出力電圧範囲等）が異なる温度センサーが接続される可能性がある。また、内部温度センサー 1 0 が用いられる可能性もある。このように、温度センサー入力端子 T V T を設けたことによって、多様な特性の温度センサーが接続される可能性がある。この点、本実施形態では A / D 変換部 2 0 の前段にプログラマブルゲインアンプ 2 2 を設けたことで、多様な特性の温度センサーに対応してゲイン調整できる。これにより、温度検出データ D T D の分解能を確保でき、所望の発振周波数精度（温度補償における周波数補正誤差）を得ることができる。

【 0 0 7 0 】

また、外部温度センサー 1 2 を配置する位置によっても温度センサーの出力電圧範囲が変わる。これに対してもプログラマブルゲインアンプ 2 2 でゲイン調整することで、所望の発振周波数精度を得ることができる。

【 0 0 7 1 】

図 5 に、プログラマブルゲインアンプ 2 2 ( P G A ) のゲイン設定例を示す。センシング温度幅  $T_{T_S} = 150$  度、70 度、30 度、10 度は、それぞれ外気温度 ( O C X O 製品のパッケージ外)、大型 O C X O 製品のパッケージ内、小型 O C X O 製品のパッケージ内、ダブルオーブン内を想定した場合である。ここでパッケージ内とは、パッケージの内側（図 9 のパッケージ 4 1 0 ）で恒温槽（例えば第 2 の容器 4 1 4 ）の外側である。

【 0 0 7 2 】

図 5 には、外部温度センサー 1 2 で外気温度を検出する場合のゲインを 1 として、各センシング温度幅  $T_{T_S}$  でのゲインを記載している。このゲインは、図 2 、図 3 で説明した温度補償における所望の周波数補正誤差を得るために必要なゲインである。即ち、センシング温度幅  $T_{T_S}$  に対する温度検出データ D T D の変動幅が、所望の周波数補正誤差を得るために必要な変動幅（例えば  $2^{1/2}$  ）となるゲインである。なお、図 5 では、外部温度センサー 1 2 の感度 ( V / ) が内部温度センサー 1 0 の感度の 5.5 倍である場合を想定している。

【 0 0 7 3 】

このように、外部温度センサー 1 2 を設けた位置に応じてプログラマブルゲインアンプ 2 2 のゲインを調整することによって、温度補償における所望の周波数補正誤差を得ることができる。

【 0 0 7 4 】

また、内部温度センサー 1 0 はダブルオーブン内（  $T_{T_S} = 10$  度）に設けられるが、外気温度を測定する場合（  $T_{T_S} = 150$  度）に比べて約 15 倍のゲインが必要である。ゲインが高いほどプログラマブルゲインアンプ 2 2 の出力電圧 P G Q の S / N が低下するため、外部温度センサー 1 2 により外気温度やパッケージ内（ダブルオーブン外）の温度を測定することが望ましいことが分かる。本実施形態では、温度センサー入力端子 T V T を設けたことで、低いゲインでの温度検出が可能となっている。

【 0 0 7 5 】

また本実施形態では、A / D 変換部 2 0 からの温度検出データ D T D は、デジタルフィルター部 2 4 を介して処理部 5 0 に入力される。

【 0 0 7 6 】

デジタルフィルター部 2 4 により温度検出データ D T D をフィルター処理することで、温度検出データ D T D のノイズを低減できる。具体的には、外部温度センサー 1 2 や内部温度センサー 1 0 からの温度検出電圧にはノイズが含まれている。また、プログラマブルゲインアンプ 2 2 を設けたので、そのゲインによって温度検出電圧のノイズが増幅される。このノイズを含んだ温度検出電圧で温度補償処理を行うと、周波数制御データ D F C Q にもノイズが含まれることになる。この周波数制御データ D F C Q のノイズは発振信号 O S C K の特性（例えば位相ノイズ）を低下させる。この点、本実施形態ではデジタルフィルター部 2 4 で温度検出電圧に起因するノイズを低減できるので、発振信号 O S C K の特

10

20

30

40

50

性を向上できる。

【0077】

また本実施形態では、回路装置は内部温度センサー10を含む。そして、A/D変換部20は、第1のモードでは、内部温度センサー10からの内部温度検出電圧VTDIを、温度検出電圧VTDとしてA/D変換を行う。第2のモードでは、外部温度センサー12から温度センサー入力端子TVTを介して入力される外部温度検出電圧VTEDを温度検出電圧VTDとしてA/D変換を行う。

【0078】

このようにすれば、例えば発振器の用途等に応じて適切な温度センサーを選択できる。例えば、外部温度センサーを設けずにコスト削減したい場合には内部温度センサーを選択できる。一方、高精度な発振周波数を得たい場合には外部温度センサーを選択できる。本実施形態では、プログラマブルゲインアンプ22を設けたことで、このような種々の温度センサーに対応できる。

【0079】

また本実施形態では、オープン型振動子XTALは、ダブルオープン型振動子であってもよい。

【0080】

ダブルオープン型振動子は、振動子が収納される恒温槽に対応して2つのヒーターが設けられ、その2つのヒーターにより恒温槽内の温度が設定温度に制御される振動子である。このようなダブルオープン型振動子を用いることで振動子の温度変動を小さくし、発振周波数の変動を抑制できる。しかしながら、ダブルオープン内では温度変動が小さいので、そのダブルオープン内に設けられる回路装置の内部温度センサーを用いると温度補償の精度が低下する。この点、本実施形態では温度センサー入力端子TVTを設けたことで、ダブルオープン外に外部温度センサーを設けることが可能となり、温度補償の精度を向上できる。

【0081】

また本実施形態では、回路装置は、オープン型振動子XTALに対応して設けられたヒーター(発熱素子)を制御するオープン制御回路190を含む。

【0082】

オープン制御回路190によりヒーターの発熱を制御することで、振動子の温度が管理されたオープン型振動子XTALを実現できる。このような温度が管理されたオープン内では温度変動が小さいが、本実施形態では外部温度センサーを設けることが可能なので、高精度な温度補償が可能である。

【0083】

また本実施形態では、図15、図16Bで後述するように周波数制御データDFCI(周波数制御データ生成部から処理部50に入力される周波数制御データ)はエージング変動成分と温度変動成分を含む。処理部50は、温度検出電圧VTDにより求められる温度検出データDTDに基づいて、周波数制御データDFCIの変動成分からエージング変動成分を抽出する。そして処理部50は、抽出したエージング変動成分に基づいて周波数制御データDFCQのエージング補正処理を行う。

【0084】

本実施形態では、温度センサー入力端子TVTを設けたことで外部温度センサー12を用いることが可能であり、それによって温度補償における周波数補正誤差を抑制できる。即ち、エージング変動成分と温度変動成分を含む周波数制御データDFCIの変動成分からエージング変動成分を抽出する際に、正確にエージング変動成分を抽出できる。具体的には、温度変動成分は、処理部50の温度補償処理によって得られた温度補償データ(図15のTCODE)である。本実施形態では、外部温度センサー12を用いることで誤差の小さい温度補償データが得られるので、正確にエージング変動成分を抽出できる。

【0085】

3. プログラマブルゲインアンプ

10

20

30

40

50

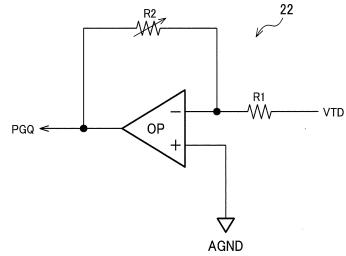

図6に、プログラマブルゲインアンプ22の詳細な構成例を示す。図6のプログラマブルゲインアンプ22は、オペアンプOP(演算増幅器)、抵抗R1、R2を含む。電圧AGNDは基準電圧(アナロググランド)である。

#### 【0086】

このプログラマブルゲインアンプ22は、いわゆる反転増幅回路(負のゲインの増幅回路)であり、抵抗R1が入力抵抗であり、抵抗R2が帰還抵抗である。帰還抵抗R2は可変抵抗となっており、この抵抗値を調整することでゲインが可変に設定される。なお、入力抵抗R1が可変抵抗であってもよい。

#### 【0087】

例えれば、帰還抵抗R2は、複数の抵抗素子が直列に接続されたラダー抵抗と、ラダー抵抗の各抵抗素子の一端に接続されるスイッチ素子を含むスイッチ回路と、で実現できる。スイッチ回路のスイッチ素子の切り替えによって、オペアンプOPの負極入力ノード(第1入力ノード)と出力ノードの間に接続される抵抗の抵抗値が変わり、ゲインが変更される。この可変の抵抗値は、例えればレジスター部や記憶部(例えれば図13のレジスター部32、記憶部34)に設定された設定値に基づいて制御される。

#### 【0088】

##### 4. オープン制御回路

図7に、オープン制御回路190の第1の詳細な構成例を示す。オープン制御回路190は、オペアンプOPA、電流源IBA(電流出力回路)、抵抗RA1、RA2を含む。

#### 【0089】

温度センサー193は、オープン制御用の温度センサーであり、発振器内に設けられる温度センサー(後述する図9の460又は462)である。図7では温度センサー193はダイオード(広義にはPN接合)により実現されている。

#### 【0090】

温度センサー193は、接続端子TCTSを介してオープン制御回路190に接続される。電流源IBAは、接続端子TCTSを介して温度センサー193にバイアス電流を供給し、ダイオードの順方向電圧VA2が接続端子TCTSを介してオープン制御回路190に入力される。電流源IBAは、例えばカレントミラー回路である。

#### 【0091】

オペアンプOPA、抵抗RA1、RA2、RA3、キャパシターCAにより積分回路(PI制御回路(Proportional-Integral Controller))が構成されている。抵抗RA3、キャパシターCAは、積分回路の帰還抵抗、帰還キャパシターであり、接続端子TFB1、TFB2の間に並列接続される。接続端子TFB2、TCTSの電圧VA1、VA2は、オペアンプOPAのイマジナリーショートにより同電圧となるように制御される。温度センサー193であるダイオードの順方向電圧VA2が変化すると、接続端子TCTSの電圧VA1が変化し、その電圧VA1と接続端子TFB2の電圧VA2が同一になるようにオペアンプOPAが動作して、ヒーター制御電圧VAQが生成される。抵抗RA1、RA2は可変抵抗であり、その可変の抵抗値によってオープン温度が設定される。

#### 【0092】

オープン制御回路190により生成されたヒーター制御電圧VAQは、出力端子TVBQを介して、発振器内に設けられるヒーター191(図9の450、452)に出力される。ヒーター191は、発熱素子である発熱MOSトランジスター194を含む。ヒーター制御電圧VAQにより発熱MOSトランジスター194のゲート電圧等が制御されて、ヒーター191の発熱制御が実現される。

#### 【0093】

なお、オープン制御用の温度センサー193とヒーター191は、1つの半導体チップであるヒーターIC195として構成されてもよい。

#### 【0094】

図8にオープン制御回路190の第2の詳細な構成例を示す。オープン制御回路190は、オペアンプOPB、抵抗RB1～RB6を含む。RB1～RB5はその抵抗値が可変

10

20

30

40

50

に制御される抵抗である。

【0095】

温度センサー193は、オープン制御用の温度センサーであり、発振器内に設けられる温度センサー（後述する図9の460又は462）である。図8では温度センサー193はサーミスターにより実現されている。

【0096】

温度センサー193は、接続端子TCTSを介してオープン制御回路190に接続される。

【0097】

抵抗RB1、RB2による電源電圧の抵抗分割により、オープン温度設定用の電圧VB1が生成される。そして発振器のオープン温度に応じて、温度センサー193であるサーミスターの抵抗値が変化して、電圧VB2が変化する。この電圧VB2とオープン温度設定用の電圧VB1がイマジナリーショートにより同じ電圧になるようにオペアンプOPBが動作して、ヒーター制御電圧VBQが生成される。

10

【0098】

オープン制御回路190により生成されたヒーター制御電圧VBQは、出力端子TVBQを介して、発振器内に設けられるヒーター191（図9の450、452）に出力される。ヒーター191は、発熱素子である発熱パワーバイポーラートランジスター192を含む。ヒーター制御電圧VBQにより発熱パワーバイポーラートランジスター192のベース電圧等が制御されて、ヒーター191の発熱制御が実現される。

20

【0099】

5. 発振器

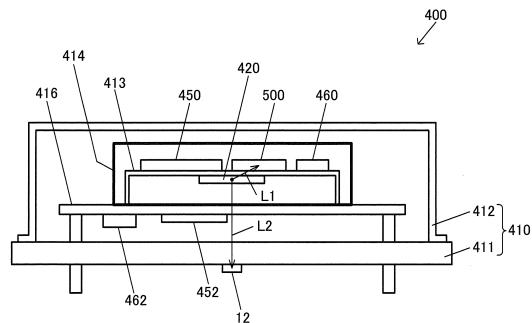

図9は、発振器400の詳細な構造例である。図9の発振器400はダブルオープン構造（広義にはオープン構造）の発振器となっている。

【0100】

パッケージ410は、基板411とケース412により構成される。基板411には不図示の種々の電子部品が搭載される。ケース412の内部には、第2の容器414が設けられ、第2の容器414の内部には第1の容器413が設けられる。そして第1の容器413の上面の内側面（下側面）に振動子420が実装される。また第1の容器413の上面の外側面（上側面）に、本実施形態の回路装置500、ヒーター450、温度センサー460が実装される。ヒーター450（発熱素子）により、例えば第2の容器414の内部の温度を調整できる。そして温度センサー460により、例えば第2の容器414の内部の温度を検出できる。

30

【0101】

第2の容器414は基板416上に設けられる。基板416は各種の電子部品を搭載可能な回路基板である。基板416のうち、第2の容器414が設けられる面の裏側面に、ヒーター452、温度センサー462が実装されている。例えばヒーター452（発熱素子）により、ケース412と第2の容器414の間の空間の温度を調整できる。そして温度センサー462により、ケース412と第2の容器414の間の空間の温度を検出できる。

40

【0102】

ヒーター450、452の発熱素子としては、例えば発熱パワーバイポーラートランジスター、発熱ヒーターMOSトランジスター、発熱抵抗体、ペルチェ素子等を用いることができる。これらのヒーター450、452の発熱の制御は、例えば回路装置500のオープン制御回路により実現できる。温度センサー460、462としては例えばサーミスター、ダイオードなどを用いることができる。

【0103】

外部温度センサー12は、パッケージ410の外に設けられる。具体的には、基板411の下面に設けられる。基板411の下面是、パッケージ410の底面であり、発振器を回路基板に実装した場合に回路基板に対向する面である。

50

## 【0104】

図9ではダブルオープン構造の恒温槽で、振動子420等の温度調整を実現できるため、振動子420の発振周波数の安定化等を図れる。また、外部温度センサー12をパッケージ410の外に設けたことで、外気温度に近いセンシング温度を検出することが可能となる。

## 【0105】

本実施形態では、オープン型振動子（振動子420）と回路装置500との間の距離をL1とし、オープン型振動子と外部温度センサー12との距離をL2とした場合に、L2 > L1である。

## 【0106】

ここで距離は、例えば2つの構成要素の中心間の距離である。例えば平面視で矩形の構成要素の場合、その矩形の対角線の交点を中心とすればよい。或いは、距離は、2つの構成要素の最も近い部分の間の距離であってもよい。或いは、オープン型振動子と回路装置500との間の距離L1においては、その距離L1は、オープン型振動子と内部温度センサー10（回路装置500において内部温度センサー10が配置されている位置）との間の距離であってもよい。

## 【0107】

オープン型振動子では、振動子420を収納した容器413、414の内部の温度がヒーター450、452により調整されている。即ち、オープン型振動子から近いほど温度が適切に調整されており、オープン型振動子から遠いほど環境温度（例えば外気温度）の変動により温度が変動しやすくなる。この点、本実施形態では、内部温度センサー10が内蔵された回路装置500よりも外部温度センサー12が遠い。また、このような外部温度センサー12からの温度検出電圧を入力するための温度センサー入力端子TVTが回路装置500に設けられている。これにより、外部温度センサー12を用いて変動範囲が広い温度変化を検出することが可能となり、その温度検出電圧を用いることで正確な温度補償処理が可能となる。

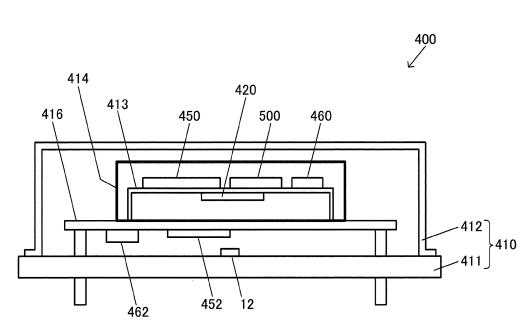

## 【0108】

図10A、図10Bは、発振器400の変形構造例である。図10A、図10Bでは、外部温度センサー12がパッケージ410の内部に設けられ、且つ第2の容器414の外部に設けられている。具体的には、図10Aでは、外部温度センサー12は基板411の上面（基板416に対向する面）に設けられる。図10Bでは、基板416の上面（第2の容器414が設けられる側の面）に設けられる。

## 【0109】

パッケージ410のケース412は例えば金属等で構成されており、セラミック等の材料と比較すると断熱効果が小さい。そのため、パッケージ410の内部であっても、第2の容器414の外側に外部温度センサー12を設けることで、センシング温度の変動範囲を広げることができる。この場合、センシング温度の変動範囲は、外気温度の変動範囲と、第2の容器414の内部における温度の変動範囲との間になる。なお、図10A、図10Bにおいても、上述したL2 > L1の条件が満たされるように外部温度センサー12が配置される。

## 【0110】

## 6. エージングによる発振周波数変動

OCXO、TCXO等の発振器では、エージングと呼ばれる経年変化により、発振周波数が変動する。そして、発振器の個体間における発振周波数のエージング変動の挙動には、発振器を構成する部品の性能、部品や発振器の実装状態、又は発振器の使用環境などの個体ばらつき（以下、素子ばらつきと称す）に起因した差がある。

## 【0111】

図11のA1～A5は、出荷ロットが同じ又は異なる複数の発振器についてのエージング特性の測定結果の一例である。図11のA1～A5に示すようにエージング変動の態様には素子ばらつきに伴う差が存在する。

## 【0112】

エージングによる発振周波数の変動の原因は、気密封止容器内で起こる振動子への粉塵の脱着や、何らかのアウトガスによる環境変化、或いは発振器に使用される接着剤の経年変化と言われている。

## 【0113】

このようなエージングによる発振周波数の変動を抑えるための対策としては、出荷前に発振器を一定期間動作させるという初期エージングを実施して、発振周波数を初期変動させてから出荷する手法がある。しかしながら、高い周波数安定度が要求される用途では、このような初期エージングの対策だけでは不十分であり、エージングによる発振周波数の変動を補償するエージング補正が要望されている。

10

## 【0114】

またその他には、発振器を、基地局の基準信号源として用いる場合には、いわゆるホールドオーバーの問題がある。例えば基地局では、GPSやネットワークからの基準信号に対して、PLL回路を用いて発振器の発振信号（出力信号）を同期させることで、周波数変動を抑制している。しかしながら、GPSやネットワーク（インターネット）からの基準信号が消失又は異常となるホールドオーバーが発生すると、同期のための基準信号を得ることができなくなる。

## 【0115】

このようなホールドオーバーが発生すると、発振器の自走発振による発振信号が、基地局の基準信号源になる。従って、ホールドオーバーの発生タイミングから、ホールドオーバーからの復帰タイミング（解除タイミング）までのホールドオーバー期間において、発振器の自走発振による発振周波数の変動を抑えるというホールドオーバー性能が要求される。

20

## 【0116】

しかしながら、上述のように発振器にはエージングによる発振周波数の無視することができないレベルの変動があるため、これが原因で、高いホールドオーバー性能を実現するのが難しいという課題がある。例えば24時間等のホールドオーバー期間において、許容される周波数偏差（ $f / f$ ）が規定されている場合に、エージングによる発振周波数の大きな変動があると、この許容周波数偏差の規定を満たせなくなるおそれがある。

## 【0117】

30

例えば基地局と通信端末との通信方式としては、FDD（Frequency Division Duplex）や、TDD（Time Division Duplex）などの種々の方式が提案されている。そしてTDD方式では、上がりと下りで同じ周波数を用いて時分割でデータが送受信され、各機器に割り当てられたタイムスロットの間にはガードタイムが設定されている。このため、適正な通信を実現するためには、各機器において時刻同期を行う必要があり、正確な絶対時刻の計時が要求される。

## 【0118】

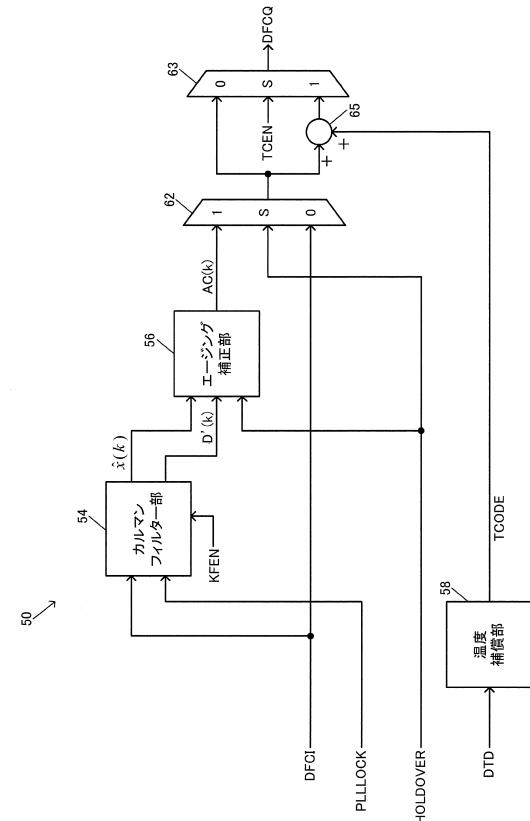

図12AのB1は、ホールドオーバーが発生した場合における理想的な発振周波数のエージングの特性を示している。一方、B2（点線）は、エージングにより発振周波数が変動する特性を示している。B3が、エージングによる発振周波数の変動幅である。また図12BのB4は、ホールドオーバーが発生した場合におけるB1の特性に近づけるための周波数制御電圧の推移を示している。一方、B5（点線）は、基準信号消失又は異常が発生した時点から周波数電圧制御が一定である状態を示している。

40

## 【0119】

図12AのB2に示す特性を、B1に示すような理想的な特性に近づける補正をするために、エージング補正が行われる。例えばエージング補正により、図12BのB4に示すように周波数制御電圧を変化させれば、図12AのB2に示す特性をB1に示す理想的な特性に近づける補正ができる、例えば補正精度を上げて行けばB2に示す特性をB1に示す理想的な特性へと補正できる。一方、図12BのB5に示すようにエージング補正を行わなかった場合には、図12AのB2に示すようにホールドオーバー期間において発振周波

50

数が変動してしまい、例えばホールドオーバー性能に対する要求仕様が図 12 A に示す B 1 であれば、その要求を満たすことができなくなる。

【0120】

例えばホールドオーバー期間における発振周波数の変動に基づく時間のずれ量（総量）を表すホールドオーバー時間  $t_{\text{hold}}$  は、下式（1）のように表すことができる。

【数1】

$$\begin{aligned}\theta_{\text{tot}} &= T_1 \times f_0 \times \frac{\Delta f}{f_0} \times \frac{1}{f_0} \times \frac{1}{2} \\ &= T_1 \times \frac{\Delta f}{f_0} \times \frac{1}{2} \quad \dots (1)\end{aligned}$$

$$\frac{\Delta f}{f_0} = \frac{2 \times \theta_{\text{tot}}}{T_1} \quad \dots (2)$$

10

【0121】

ここで  $T_1$  はホールドオーバーによるエージングの経過時間を表す。  $f_0$  は公称発振周波数であり、  $f / f_0$  は周波数偏差である。上式（1）において、  $T_1 \times f_0$  は総クロック数を表し、  $(f / f_0) \times (1 / f_0)$  は 1 クロックでのタイミングのずれ量を表す。そしてホールドオーバー時間  $t_{\text{hold}}$  と経過時間  $T_1$  を用いて、周波数偏差  $f / f_0$  は上式（2）のように表すことができる。

20

【0122】

ここで、周波数偏差  $f / f_0$  は、経過時間に対して 1 次関数的に一定の傾きで変化するものと想定している。この場合に、経過時間  $T_1$  が長くなるにつれてホールドオーバー時間  $t_{\text{hold}}$  は 2 次関数的に長くなる。

【0123】

例えば TDD 方式の場合には、ガードタイムが設定されたタイムスロットが重なってしまうのを防止するために、ホールドオーバー時間は例えば  $t_{\text{hold}} < 1.5 \mu\text{s}$  であることが要求される。従って、上式（2）から明らかなように、発振器に許容される周波数偏差  $f / f_0$  としては、非常に小さな値が要求されることになる。特に、この許容周波数偏差は、経過時間  $T_1$  が長くなるほど、小さな値が要求される。例えばホールドオーバーの発生タイミングから、メインテナンス作業によるホールドオーバーからの復帰タイミングまでの時間として想定される時間が、例えば  $T_1 = 24$  時間である場合には、許容周波数偏差として非常に小さな値が要求されることになってしまう。そして、周波数偏差  $f / f_0$  には、例えば温度依存の周波数偏差と、エージングによる周波数偏差が含まれるため、上記要求を満たすためには、非常に高精度なエージング補正が必要になる。

30

【0124】

7. 回路装置の詳細な構成例

図 13 に本実施形態の回路装置の詳細な構成例を示す。図 13 では図 4 の構成に対して、デジタル I/F 部 30（インターフェース部、インターフェース回路）、レジスター部 32（レジスター）、記憶部 34（メモリー）、周波数制御データ生成部 40（周波数制御データ生成回路）が更に設けられている。なお図 13 では、プログラマブルゲインアンプ 22、デジタルフィルター部 24、オープン制御回路 190 の図示を省略している。回路装置の構成は図 13 の構成には限定されず、その一部の構成要素（例えば周波数制御データ生成部）を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

40

【0125】

デジタル I/F 部 30 は、回路装置と外部装置（マイクロコンピューター、コントローラー等）との間でデジタルデータを入出力するためのインターフェースである。デジタル I/F 部 30 は、例えばシリアルクロック線とシリアルデータ線を用いた同期式のシリアル

50

ル通信方式により実現できる。具体的には、I<sub>2</sub>C (Inter-Integrated Circuit) 方式や、3線又は4線のS<sub>P</sub>I (Serial Peripheral Interface) 方式などにより実現できる。I<sub>2</sub>C 方式は、シリアルクロック線SCLと、双方向のシリアルデータ線SDAの2本の信号線で通信を行う同期式のシリアル通信方式である。I<sub>2</sub>Cのバスには複数のスレーブを接続でき、マスターは、個別に決められたスレーブのアドレスを指定して、スレーブを選択した後に、当該スレーブと通信を行う。S<sub>P</sub>I 方式は、シリアルクロック線SCKと、単方向の2本のシリアルデータ線SDI、SDOで通信する同期式のシリアル通信方式である。S<sub>P</sub>Iのバスには複数のスレーブを接続できるが、それらを特定するためには、マスターは、スレーブセレクト線を用いてスレーブを選択する必要がある。デジタルI/F部30は、これらの通信方式を実現する入出力バッファー回路や制御回路などにより構成される。

#### 【0126】

レジスター部32は、ステータスレジスター、コマンドレジスター、データレジスターなどの複数のレジスターで構成される回路である。回路装置の外部装置は、デジタルI/F部30を介してレジスター部32の各レジスターにアクセスする。そして外部装置は、レジスター部32のレジスターを用いて、回路装置のステータスを確認したり、回路装置に対してコマンドを発行したり、回路装置に対してデータを転送したり、回路装置からデータを読み出すことなどが可能になる。

#### 【0127】

記憶部34は、回路装置の各種の処理や動作に必要な各種の情報を記憶するものである。この記憶部34は、例えば不揮発性メモリーにより実現できる。不揮発性メモリーとしては、例えばEEPROMなどを用いることができる。EEPROMとしては例えばMONOS (Metal-Oxide-Nitride-Oxide-Silicon) 型のメモリーなどを用いることができる。例えばMONOS型のメモリーを用いたフラッシュメモリーを用いることができる。あるいはEEPROMとして、フローティングゲート型などの他のタイプのメモリーを用いてもよい。なお記憶部34は、電源が非供給でも情報を保持して記憶できるものであればよく、例えばヒューズ回路等により実現することも可能である。

#### 【0128】

処理部50は、ホールドオーバー処理部52 (ホールドオーバー処理の回路又はプログラムモジュール)、カルマンフィルター部54 (カルマンフィルター処理の回路又はプログラムモジュール)、エージング補正部56 (エージング補正処理の回路又はプログラムモジュール)、温度補償部58 (温度補償処理の回路又はプログラムモジュール)を有する。ホールドオーバー処理部52は、ホールドオーバーに関する種々の処理を行う。温度補償部58は、A/D変換部20からの温度検出データDTDに基づいて発振周波数の温度補償処理を行う。具体的には温度補償部58は、温度に応じて変化する温度検出データDTD (温度依存データ)と、温度補償処理用の係数データ (近似関数の係数のデータ)などに基づいて、温度変化があった場合に発振周波数の変動を小さくするための温度補償処理を行う。

#### 【0129】

基準信号RFCKは、回路装置の外部接続端子である端子TRFCK (パッド)を介して回路装置に入力される。外部PLL回路がロック状態となっているか否かを通知する信号PLOCKは、回路装置の外部接続端子である端子TPLOCK (パッド)を介して回路装置に入力される。

#### 【0130】

記憶部34は、カルマンフィルター処理のシステムノイズの設定用のシステムノイズ定数 (V)と、カルマンフィルター処理の観測ノイズの設定用の観測ノイズ定数 (W)を記憶する。例えば製品 (発振器等) の製造、出荷時において、発振周波数等の各種の情報をモニターするための測定 (検査) が行われる。そしてこの測定結果に基づいて、システムノイズ定数や観測ノイズ定数が決定されて、例えば不揮発性メモリー等により実現される記憶部34に書き込まれる。このようにすれば、素子ばらつきによる悪影響を低減したシ

10

20

30

40

50

ステムノイズ定数や観測ノイズ定数の設定が可能になる。

【0131】

周波数制御データ生成部40は周波数制御データDFCIを生成する。例えば発振信号OSCKに基づく入力信号と基準信号RFCKとを比較して周波数制御データDFCIを生成する。生成された周波数制御データDFCIは処理部50に入力される。ここで発振信号OSCKに基づく入力信号は、発振信号OSCKそのものであってもよいし、発振信号OSCKから生成された信号（例えば分周した信号）であってもよい。以下では、入力信号が発振信号OSCKそのものである場合を主に例にとり説明する。

【0132】

周波数制御データ生成部40は、比較演算部41、デジタルフィルター部44を含む。

比較演算部41は、入力信号である発振信号OSCKと基準信号RFCKとの比較演算を行なう回路であり、カウンター42、TDC43（時間デジタル変換器）を含む。

10

【0133】

カウンター42は、基準信号RFCKの基準周波数（例えば1Hz）を、発振信号OSCKの発振周波数で除算した結果の整数部に相当するデジタルデータを生成する。TDC43は、当該除算結果の小数部に相当するデジタルデータを生成する。TDC43は、例えば、複数の遅延素子と、複数の遅延素子が出力する複数の遅延クロック信号を、基準信号RFCKのエッジ（High）タイミングでラッチする複数のラッチ回路と、複数のラッチ回路の出力信号のコーディングを行うことで、除算結果の小数部に相当するデジタルデータを生成する回路を含む。そして比較演算部41は、カウンター42からの整数部に相当するデジタルデータと、TDC43からの小数部に相当するデジタルデータを加算し、設定周波数との位相誤差を検出する。そしてデジタルフィルター部44が位相誤差の平滑化処理を行うことで、周波数制御データDFCIが生成される。例えば発振信号OSCKの周波数をFOS、基準信号RFCKの周波数をFRF、設定周波数に対応する分周数（分周比）をFCWとした場合に、 $F_{OS} = F_{CW} \times F_{RF}$ の関係が成り立つように、周波数制御データDFCIが生成される。

20

【0134】

なお周波数制御データ生成部40の構成は図13に示す構成に限定されず、種々の変形実施が可能である。例えば比較演算部41をアナログ回路の位相比較器で構成したり、デジタルフィルター部44をアナログ回路のフィルター部（ループフィルター）で構成してもよい。

30

【0135】

また図13では、回路装置が周波数制御データ生成部40を内蔵する構成となっているが、周波数制御データ生成部は、回路装置の外部に設けられる回路であってもよい。この場合には、外部に設けられた周波数制御データ生成部から、デジタルI/F部30を介して周波数制御データDFCIを処理部50に入力すればよい。

【0136】

このように本実施形態では、処理部50（プロセッサー）には、発振信号OSCKに基づく入力信号と基準信号RFCKとを比較して周波数制御データDFCIを生成する周波数制御データ生成部40からの周波数制御データDFCIが入力される。そして処理部50（プロセッサー）は、基準信号の消失又は異常によるホールドオーバーが検出される前の期間において、周波数制御データ生成部40からの周波数制御データDFCIの観測値に対する真値を、カルマンフィルター処理により推定する処理を行う。この真値は、カルマンフィルター処理により推定された真値であり、本当の真の値であるとは限らない。カルマンフィルター処理はカルマンフィルター部54により実行される。またホールドオーバーの検出による制御処理は、ホールドオーバー処理部52により実行される。

40

【0137】

そして処理部50（プロセッサー）は、ホールドオーバーが検出された場合に、ホールドオーバーの検出タイミングに対応するタイミングでの真値を保持する。この真値を保持するタイミングは、ホールドオーバーの検出タイミングそのものであってもよいし、当該

50

タイミングの前のタイミング等であってもよい。そして処理部50は、保持された真値に基づく演算処理を行うことで、エージング補正された周波数制御データDFCQを生成する。生成された周波数制御データDFCQは、発振信号生成回路140に出力される。このエージング補正された周波数制御データDFCQの生成処理は、エージング補正部56により実行される。

#### 【0138】

例えば通常動作期間において、処理部50は、周波数制御データ生成部40から入力された周波数制御データDFCIに対して、例えば温度補償処理等の信号処理を行い、信号処理後の周波数制御データDFCQを発振信号生成回路140に出力する。発振信号生成回路140は、処理部50からの周波数制御データDFCQと振動子XTALを用いて、発振信号OSCKを生成して、周波数制御データ生成部40に出力する。これにより、周波数制御データ生成部40、発振信号生成回路140等によるPLL回路のループが形成され、基準信号RFCKに位相同期した正確な発振信号OSCKを生成できるようになる。

10

#### 【0139】

そして本実施形態では、ホールドオーバーが検出される前の通常動作期間においても、処理部50のカルマンフィルター部54が動作し、周波数制御データDFCIに対するカルマンフィルター処理を実行している。即ち、周波数制御データDFCIの観測値に対する真値を、カルマンフィルター処理により推定する処理を行っている。

#### 【0140】

20

ホールドオーバーが検出されると、ホールドオーバーの検出タイミングに対応するタイミングでの真値が、処理部50において保持される。具体的にはエージング補正部56が、この真値を保持する。そしてエージング補正部56が、保持された真値に基づく演算処理を行うことで、エージング補正された周波数制御データDFCQを生成する。

#### 【0141】

このようにすれば、ホールドオーバーの検出タイミングに対応するタイミングでの真値に基づいて、エージング補正が行われるため、エージング補正の精度を大幅に向上できる。即ち、観測ノイズやシステムノイズの影響を考慮したエージング補正を実現できるようになる。

#### 【0142】

30

なお発振信号生成回路140は、ホールドオーバーから復帰した場合には、周波数制御データ生成部40から処理部50を介して入力された周波数制御データDFCQに基づいて、発振信号OSCKを生成する。例えば基準信号RFCKの消失状態や異常状態が解消されると、ホールドオーバーの状態が解除されて、ホールドオーバーから復帰する。この場合には、回路装置の動作は通常動作に復帰する。そして発振信号生成回路140は、処理部50がエージング補正を行うことで生成した周波数制御データDFCQに代えて、周波数制御データ生成部40から処理部50を介して入力された周波数制御データDFCQ（温度補償処理等の信号処理後の周波数制御データ）に基づいて、発振信号OSCKを生成する。

#### 【0143】

40

また処理部50は、保持された真値に対して補正值を加算する演算処理（エージングによる周波数変化を補償する演算処理）を行うことで、エージング補正された周波数制御データDFCQを生成する。例えばホールドオーバーの検出タイミングに対応するタイミングでの真値に対して、エージングレート（エージングの勾配、エージング係数）に対応する補正值（エージングレートによる周波数変化をキャンセルする補正值）を、所定タイミング毎に順次に加算することで、エージング補正された周波数制御データDFCQを生成する。

#### 【0144】

例えばタイムステップkでの補正值をD(k)とし、タイムステップkでのエージング補正された周波数制御データをAC(k)とする。この場合に処理部50は、タイムステ

50

ツップ  $k + 1$  でのエージング補正された周波数制御データ  $AC(k + 1)$  を、 $AC(k + 1) = AC(k) + D(k)$  により求める。処理部 50 は、このような各タイムステップごとの補正值  $D(k)$  の加算処理を、ホールドオーバーからの復帰タイミング（解除タイミング）まで行う。

【0145】

また処理部 50 は、真値に対してフィルター処理後の補正值を加算する演算処理を行う。例えば、補正值  $D(k)$  に対して、ローパスフィルター処理等のフィルター処理を行い、フィルター処理後の補正值  $D'(k)$  を真値に対して順次に加算する演算処理を行う。具体的には  $AC(k + 1) = AC(k) + D'(k)$  の演算処理を行う。

【0146】

また処理部 50 は、補正值を、カルマンフィルター処理における観測残差に基づき求める。例えば処理部 50 は、ホールドオーバーが検出される前の期間において、観測残差に基づいて、エージング補正の補正值を推定する処理を行う。例えば観測残差を  $e_k$  とした場合に、 $D(k) = D(k - 1) + E \cdot e_k$  の処理を行うことで、補正值  $D(k)$  を推定する。ここで  $E$  は例えば定数であるが、定数  $E$  の代わりにカルマンゲインを用いてもよい。そして、ホールドオーバーの検出タイミングに対応するタイミングでの補正值を保持し、保持された補正值を真値に加算する演算処理を行うことで、エージング補正された周波数制御データ  $DFCQ$  を生成する。

【0147】

また処理部 50 は、ホールドオーバーの検出信号が入力される入力端子の電圧、又は、デジタル I / F 部 30 を介して入力されるホールドオーバーの検出情報に基づいて、ホールドオーバーの状態になった否かを判断する。これらの判断処理は、ホールドオーバー処理部 52 が行う。例えばホールドオーバー処理部 52 はステートマシーンの回路を有しており、このステートマシーンの状態遷移は、各種の信号や情報に基づいて実行される。そして、ホールドオーバーの検出信号が入力される入力端子の電圧や、デジタル I / F 部 30 を介して入力されるホールドオーバーの検出情報などに基づいて、ホールドオーバーの状態になったと判断されると、ステートマシーンの状態がホールドオーバーの状態に遷移する。そしてホールドオーバー時の各種処理（エージング補正等）が実行される。

【0148】

ホールドオーバーの検出信号としては、例えば基準信号  $RFC_K$  や信号  $PLOCK$  を想定できる。この場合に処理部 50 は、基準信号  $RFC_K$  が入力される端子  $TRFC_K$  の電圧や、信号  $PLOCK$  が入力される端子  $TPLOCK$  の電圧に基づいて、ホールドオーバーの状態になった否かを判断する。

【0149】

例えば、回路装置の内部に設けられた周波数制御データ生成部 40 により  $PLL$  回路が形成される場合には、基準信号  $RFC_K$  が入力される端子  $TRFC_K$  の電圧に基づいて、ホールドオーバーの状態になった否かを判断できる。例えば処理部 50 は、端子  $TRFC_K$  の電圧に基づいて、基準信号  $RFC_K$  が消失又は異常な状態になったことが検出された場合に、ホールドオーバーの状態になった否かを判断する。

【0150】

一方、回路装置の外部に設けられた周波数制御データ生成部により  $PLL$  回路が形成される場合には、信号  $PLOCK$  が入力される端子  $TPLOCK$  の電圧に基づいて、ホールドオーバーの状態になった否かを判断できる。例えば外部装置（外部  $PLL$  回路を制御する装置）は、外部  $PLL$  回路がロック状態となっているか否かを通知する信号  $PLOCK$  を回路装置に出力する。そして例えば信号  $PLOCK$  により、外部  $PLL$  回路がロック状態になつていないと判断した場合には、処理部 50 はホールドオーバーの状態であると判断する。なお、信号  $PLOCK$  に加えて、基準信号  $RFC_K$  も用いて、ホールドオーバーの状態になったか否かを判断してもよい。また外部  $PLL$  回路は、例えば回路装置の外部に設けられた周波数制御データ生成部と、回路装置の発振信号生成回路 140 等により構成される  $PLL$  回路である。

10

20

30

40

50

## 【0151】

また、回路装置の外部に設けられた周波数制御データ生成部によりPLL回路が形成される場合に、デジタルI/F部30を介して入力されるホールドオーバーの検出情報に基づいて、ホールドオーバーの状態になったか否かを判断してもよい。例えば外部PLL回路を制御する外部装置（例えばマイクロコンピューター）は、基準信号の消失又は異常にによりホールドオーバーの状態になったと判断した場合に、ホールドオーバーの検出情報を、デジタルI/F部30を介してレジスター部32のレジスター（通知レジスター）に設定する。処理部50は、このレジスターに設定されたホールドオーバーの検出情報を読み出すことで、ホールドオーバーの状態になったか否かを判断する。このようにすればホールドオーバーの検出用の端子を新たに設ける必要がなくなり、回路装置の端子数の削減等を図れるようになる。10

## 【0152】

## 8. カルマンフィルター処理を用いたエージング補正

本実施形態では、カルマンフィルター処理を用いたエージング補正手法を採用している。具体的には本実施形態では、ホールドオーバーが検出される前の期間において周波数制御データ（発振周波数）の観測値に対する真値を、カルマンフィルター処理により推定する。そしてホールドオーバーが検出された場合には、ホールドオーバーの検出タイミングに対応するタイミング（時点）での真値を保持し、保持した真値に基づく演算処理を行うことで、エージング補正を実現する。20

## 【0153】

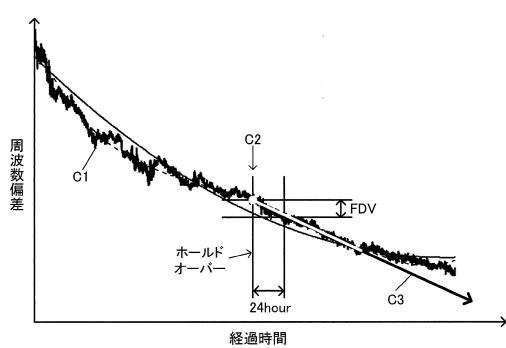

図14Aは、エージングによる発振周波数の変動の測定結果の例を示す図である。横軸は経過時間（エージング時間）であり、縦軸は発振周波数の周波数偏差（ $f / f_0$ ）である。図14AのC1に示すように観測値である測定値には、システムノイズや観測ノイズに起因する大きなばらつきが存在する。このばらつきには、環境温度に起因するばらつきも含まれる。20

## 【0154】

このように測定値に大きなばらつきがある状況において、真値を正しく求めるために、本実施形態では、カルマンフィルター処理（例えば線形カルマンフィルター処理）による状態推定を行う。30

## 【0155】

図14Bは、時系列の状態空間モデルを示すものであり、このモデルの離散時間状態方程式は、下式（3）、（4）の状態方程式、観測方程式により与えられる。30

## 【数2】

$$x(k+1) = A \cdot x(k) + v(k) \quad \dots (3)$$

$$y(k) = x(k) + w(k) \quad \dots (4)$$

## 【0156】

$x(k)$ は時刻kにおける状態であり、 $y(k)$ は観測値である。 $v(k)$ はシステムノイズであり、 $w(k)$ は観測ノイズであり、Aはシステム行列である。 $x(k)$ が発振周波数（周波数制御データ）である場合に、Aは例えばエージングレート（エージング係数）に相当する。エージングレートは経過期間に対する発振周波数の変化率を表すものである。40

## 【0157】

例えば図14AのC2に示すタイミングでホールドオーバーが発生したとする。この場合に、基準信号RFCが途絶えたC2の時点での真の状態 $x(k)$ と、図14AのC3に示す傾きに相当するエージングレート（A）に基づいて、エージング補正を実行する。具体的には、C2の時点での発振周波数（周波数制御データ）の真値 $x(k)$ を、C3に示すエージングレートによる周波数変化を小さくするための補償（補正）として、例えば当該周波数変化をキャンセル（相殺）する補正值で、順次に変化させるエージング補正50

を行う。即ち図12AのB2に示すようなエージングレートでの周波数変化をキャンセルして、B1に示すような理想的な特性になるような補正值で、真値 $x(k)$ を変化させる。このようにすれば、例えばホールドオーバーの期間が24時間であった場合に、24時間経過後における発振周波数の変動である図14AのFDVを、エージング補正により補償できるようになる。

#### 【0158】

ここで図14AのC1に示す発振周波数（周波数偏差）の変動には、温度変動に起因するものと、エージングに起因するものが含まれる。そこで本実施形態では、例えば恒温槽を有するオープン構造の発振器（OCXO）を採用することで、温度変動に起因する発振周波数の変動を最小限に抑える。また図4の外部温度センサー12、内部温度センサー10等を用いて、温度変動に起因する発振周波数の変動を低減する温度補償処理を実行する。

10

#### 【0159】

そしてPLL回路（内部PLL回路、外部PLL回路）が基準信号RFCKに同期している期間（通常動作期間）において、周波数制御データ（周波数制御コード）をモニタし、誤差（システムノイズ、観測ノイズ）を除去した真値を求めて、レジスターに保持しておく。そして、基準信号RFCKの消失又は異常によりPLL回路のロックが外れた場合に、ロックが外れた時点において保持されている真値（周波数制御データの観測値に対する真値）に基づいて、エージング補正を実行する。例えば、保持された周波数制御データの真値に対して、図14AのC3の傾きであるエージングレートによる周波数変化を小さくするための補償として、例えば当該周波数変化をキャンセルする補正值を、順次に加算する処理を行うことで、ホールドオーバー期間の自走発振時における周波数制御データDFCQを生成して、振動子XTALを発振させる。このようにすれば、ホールドオーバーの突入時点での真値を、最小誤差で求めて、エージング補正を実行できるため、エージング変動による悪影響を最小限に抑えたホールドオーバー性能を実現できるようになる。

20

#### 【0160】

##### 9. 処理部の構成

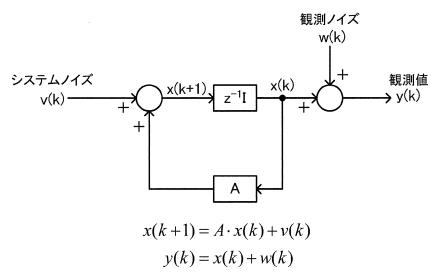

図15に処理部50の詳細な構成例を示す。図15に示すように処理部50は、カルマンフィルター部54、エージング補正部56、温度補償部58、セレクター62、63、加算器65を含む。

30

#### 【0161】

カルマンフィルター部54は、周波数制御データDFCI（環境変動成分が除去された周波数制御データ）が入力され、カルマンフィルター処理を実行する。そして、カルマンフィルター処理により推定された真値に相当する事後推定値 $x^{\wedge}(k)$ を出力する。なお本明細書では、推定値であることを表すハットの記号「 $\wedge$ 」を、適宜、2文字に並べて記載する。

#### 【0162】

カルマンフィルター処理とは、観測値及びシステムの状態を表す変数にノイズ（誤差）が含まれると仮定し、過去から現在までに取得した観測値を用いてシステムの最適な状態を推定する処理である。具体的には、観測更新（観測過程）と時間更新（予測過程）を繰り返し行って状態を推定する。観測更新は、観測値と時間更新の結果を用いてカルマンゲイン、推定値、誤差共分散を更新する過程である。時間更新は、観測更新の結果を用いて、次の時刻での推定値、誤差共分散を予測する過程である。なお本実施形態では線形カルマンフィルター処理を用いた手法を主に説明するが、拡張カルマンフィルター処理を採用することも可能である。本実施形態のカルマンフィルター処理の詳細については後述する。

40

#### 【0163】

エージング補正部56は、カルマンフィルター部54から事後推定値 $x^{\wedge}(k)$ と補正值 $D'(k)$ が入力される。そして、周波数制御データの真値に相当する事後推定値 $x^{\wedge}(k)$ に対して、補正值 $D'(k)$ を加算する演算処理を行うことで、エージング補正さ

50

れた周波数制御データである  $A_C(k)$  を生成する。ここで  $D'(k)$  は、フィルター処理後（ローパスフィルター処理後）の補正值  $D(k)$  である。即ち、タイムステップ  $k$ （時刻  $k$ ）での補正值（フィルター処理後の補正值）を  $D'(k)$  とし、タイムステップ  $k$  でのエージング補正された周波数制御データを  $A_C(k)$  とした場合に、エージング補正部 56 は、タイムステップ  $k+1$ （時刻  $k+1$ ）でのエージング補正された周波数制御データ  $A_C(k+1)$  を、 $A_C(k+1) = A_C(k) + D'(k)$  により求める。

#### 【0164】

温度補償部 58 は、温度検出データ  $D_T D$  が入力されて、温度補償処理を行い、温度変動に対して発振周波数を一定に保つための温度補償データ  $T C O D E$ （温度補償コード）を生成する。

10

#### 【0165】

発振周波数の温度特性は製品のサンプルごとに大きくばらつく。このため、製品（発振器）の製造、出荷時の検査工程において、発振周波数の温度特性や、周囲温度に対応する温度検出データの変化特性を測定する。そして測定結果に基づいて、下式（5）の多項式（近似関数）の係数  $A_0 \sim A_5$  を求め、求めた係数  $A_0 \sim A_5$  の情報を、図 13 の記憶部 34（不揮発性メモリー）に書き込んで記憶させる。

#### 【数3】

$$T C O D E = A_5 \cdot X^5 + A_4 \cdot X^4 + A_3 \cdot X^3 + A_2 \cdot X^2 + A_1 \cdot X + A_0 \quad \dots \quad (5)$$

20

#### 【0166】

上式（5）において、 $X$  は、A/D 変換部 20 により得られた温度検出データ  $D_T D$ （A/D 変換値）に相当する。周囲温度の変化に対する温度検出データ  $D_T D$  の変化も測定されているため、上式（5）の多項式で表される近似関数により、周囲温度と発振周波数とを対応づけることができる。温度補償部 58 は、記憶部 34 から係数  $A_0 \sim A_5$  の情報を読み出し、この係数  $A_0 \sim A_5$  と、温度検出データ  $D_T D$ （=  $X$ ）に基づいて、上式（5）の演算処理を行って、温度補償データ  $T C O D E$ （温度補償コード）を生成する。これにより、周囲温度の変化に対して発振周波数を一定に保つための温度補償処理を実現できる。

#### 【0167】

セレクター 62、63 は、セレクト端子  $S$  の入力信号の論理レベルが「1」（アクティブ）である場合に、「1」側の端子の入力信号を選択して、出力信号として出力する。またセレクト端子  $S$  の入力信号の論理レベルが「0」（非アクティブ）である場合に、「0」側の端子の入力信号を選択して、出力信号として出力する。

30

#### 【0168】

信号  $K F E N$  はカルマンフィルター処理のイネーブル信号である。カルマンフィルター部 54 は、信号  $K F E N$  が論理レベル「1」（以下、単に「1」と記載）である場合にカルマンフィルター処理を実行する。信号  $P L L L O C K$  は PLL 回路がロック状態である場合に「1」になる信号である。信号  $H O L D O V E R$  はホールドオーバーが検出されたホールドオーバー期間において「1」になる信号である。

40

#### 【0169】

信号  $T C E N$  は、温度補償処理のイネーブル信号である。以下では信号  $T C E N$  が「1」であり、セレクター 63 が「1」側の入力信号を選択する場合を主に例にとり説明を行う。また信号  $K F E N$  も「1」であるとする。

#### 【0170】

通常動作期間では、信号  $H O L D O V E R$  が論理レベル「0」（以下、単に「0」と記載）になるため、セレクター 62 が「0」端子側の周波数制御データ  $D F C I$  を選択する。そして、この周波数制御データ  $D F C I$  に対して、加算器 65 により温度補償データ  $T C O D E$  が加算され、温度補償処理後の周波数制御データ  $D F C Q$  が、後段の発振信号生成回路 140 に出力される。

50

## 【0171】

一方、ホールドオーバー期間では、信号HOLDOVERが「1」なり、セレクター62が「1」端子側のAC(k)を選択する。AC(k)はエージング補正された周波数制御データである。

## 【0172】

図16Aはカルマンフィルター部54の動作を説明する真理値表である。信号PLLLOC、KFEENが共に「1」である場合には、カルマンフィルター部54は真値推定処理（カルマンフィルター処理）を実行する。即ち、通常動作期間においてPLL回路（内部又は外部のPLL回路）がロック状態である場合に、観測値である周波数制御データDFCIの真値推定処理を行い続ける。

10

## 【0173】

そしてホールドオーバーの状態になってPLL回路のロックが外れ、信号PLLLOCが「0」になった場合には、カルマンフィルター部54は前回の出力状態を保持する。例えば図15において、周波数制御データDFCIの真値として推定される事後推定値 $x^k$ や、エージング補正の補正值 $D'(k)$ として、ホールドオーバーの検出タイミング（PLL回路のロックが外れたタイミング）での値を、保持して出力し続ける。

## 【0174】

エージング補正部56は、ホールドオーバー期間において、カルマンフィルター部54からの事後推定値 $x^k$ 、補正值 $D'(k)$ を用いてエージング補正を行う。具体的にはホールドオーバーの検出タイミングにおける事後推定値 $x^k$ 、補正值 $D'(k)$ を保持して、エージング補正を行う。

20

## 【0175】

また図15では、カルマンフィルター部54には、温度変動成分（広義には環境変動成分）とエージング変動成分のうち、温度変動成分が除去された周波数制御データDFCIが入力される。カルマンフィルター部54は、温度変動成分（環境変動成分）が除かれた周波数制御データDFCIに対してカルマンフィルター処理を行って、周波数制御データDFCIについての真値を推定する。即ち、事後推定値 $x^k$ を求める。そしてエージング補正部56は、推定された真値である事後推定値 $x^k$ に基づいて、エージング補正を行う。より具体的には、カルマンフィルター部54からの事後推定値 $x^k$ と補正值 $D'(k)$ に基づいて、エージング補正された周波数制御データAC(k)を求める。そしてエージング補正された周波数制御データであるAC(k)は、セレクター62を介して、加算器65に入力され、加算器65がAC(k)に対して、温度補償データTCODE（環境変動成分の補償用データ）を加算する処理を行う。

30

## 【0176】

例えば図16Bの模式図に示すように、温度が変動すると、E1に示すように周波数制御データもそれに応じて変動してしまう。従って、E1のように温度変動に伴い変動する周波数制御データを用いて、カルマンフィルター処理を行ってしまうと、ホールドオーバー検出タイミングでの真値にも揺らぎが生じてしまう。

## 【0177】

そこで本実施形態では、温度変動成分が除去された周波数制御データを取得して、カルマンフィルター部54に入力する。即ち、温度変動成分（環境変動成分）とエージング変動成分のうち、温度変動成分が除かれた周波数制御データを、カルマンフィルター部54に入力する。つまり、図16BのE2に示すような周波数制御データを入力する。E2の周波数制御データは、温度変動成分が除かれており、エージング変動成分が残存した周波数制御データになっている。

40

## 【0178】

カルマンフィルター部54は、このように温度変動成分が除去されて、エージング変動成分が残存した周波数制御データDFCIに対して、カルマンフィルター処理を行うことで、真値として推定される事後推定値 $x^k$ や、エージング補正の補正值 $D'(k)$ を求める。そして、ホールドオーバーの検出タイミングで推定された真値である事後推定

50

値  $x^k$  や、補正值  $D'(k)$  がエージング補正部 56 に保持されて、エージング補正が実行される。

【0179】

例えば加算器 65 により温度補償データ TCODE を加算する処理を行うことで、周波数制御データ DFCQ は温度補償された周波数制御データになる。従って、周波数制御データ DFCQ が入力された発振信号生成回路 140 は、温度補償された発振周波数の発振信号 OSCK を出力することになる。従って、この発振信号生成回路 140 と共に PLL 回路を構成する図 13 の周波数制御データ生成部 40 は、図 16B の E2 に示すように温度変動成分が除去された周波数制御データ DFCI を、処理部 50 に供給することになる。そして、この温度変動成分が除去された周波数制御データ DFCI には、図 16B の E2 に示すように、経過時間と共に変化するエージング変動成分が残存している。従って、処理部 50 のカルマンフィルター部 54 が、このエージング変動成分が残存する周波数制御データ DFCI に対するカルマンフィルター処理を行い、エージング補正部 56 が、カルマンフィルター処理の結果に基づいてエージング補正を行えば、高精度のエージング補正を実現できるようになる。

【0180】

図 1 等で説明したように、本実施形態では温度センサー入力端子 TTT を設けたことで、外部温度センサー 12 で検出した温度検出電圧に基づいて温度変動成分を求める（温度補償処理を行う）ことが可能となっている。これにより、回路装置に内蔵の温度センサーを用いる場合よりも高精度な（周波数補正誤差が小さい）温度変動成分を求めることがで 20 き、その温度変動成分を周波数制御データ DFCI から除去することで、エージング変動成分を高精度に抽出できる。

【0181】

なお図 15 の変形例として、加算器 65 での温度補償データ TCODE の加算処理を行わずに、周波数制御データ DFCI の温度変動成分（環境変動成分）を除去するための演算処理を行って、演算処理後の周波数制御データ DFCI をカルマンフィルター部 54 に入力するようにしてもよい。例えば図 15 の加算器 65 及びセレクター 63 の構成を省略して、カルマンフィルター部 54 の前段に、周波数制御データ DFCI から温度補償データ TCODE を減算する減算器を設け、この減算器の出力をカルマンフィルター部 54 に入力する。またエージング補正部 56 とセレクター 62 の間に、エージング補正部 56 の出力と温度補償データ TCODE を加算する加算器を設け、加算器の出力をセレクター 62 の「1」側の端子に入力する。このような構成によつても、温度変動成分が除去されて、エージング変動成分だけが残存した周波数制御データ DFCI を、カルマンフィルター部 54 に入力できるようになる。

【0182】

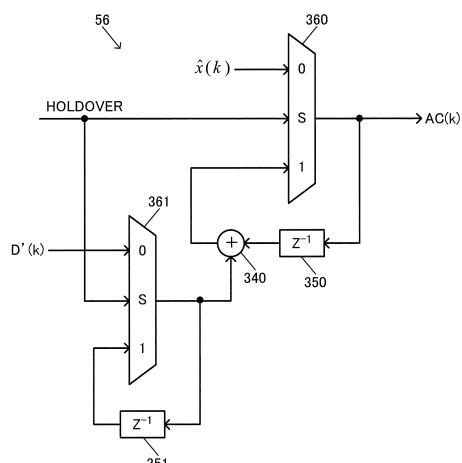

図 17 に、エージング補正部 56 の詳細な構成例を示す。通常動作期間では、信号 HOLDOVER が「0」になるため、セレクター 360、361 は「0」端子側を選択する。これにより、通常動作期間においてカルマンフィルター部 54 により演算された事後推定値  $x^k$ 、補正值  $D'(k)$ （フィルター処理後の補正值）が、各々、レジスター 350、351 に保持される。

【0183】

ホールドオーバーが検出されて、信号 HOLDOVER が「1」になると、セレクター 360、361 は「1」端子側を選択する。これによりセレクター 361 は、ホールドオーバーの検出タイミングでレジスター 351 に保持された補正值  $D'(k)$  を、ホールドオーバー期間中は出力し続けることになる。

【0184】

そして、加算器 340 は、ホールドオーバーの検出タイミングでレジスター 350 に保持された事後推定値  $x^k$  に対して、レジスター 351 に保持されてセレクター 361 から出力された補正值  $D'(k)$ （補正值）を、各タイムステップごとに順次に加算する処理を行う。これにより下式（6）に示すようなエージング補正が実現される。

## 【数4】

$$AC(k+1) = AC(k) + D'(k) \quad \dots \quad (6)$$

## 【0185】

即ち図14AのC2のタイミングで保持された真値である事後推定値 $\hat{x}(k)$ に対して、C3の傾きに相当するエージングレートによる周波数変化をキャンセル（補償）する補正値 $D'(k)$ を、順次に加算する処理が行われて、エージング補正が実現される。

## 【0186】

## 10. カルマンフィルター処理

次に本実施形態のカルマンフィルター処理の詳細について説明する。カルマンフィルターのモデルの状態方程式、観測方程式は下式(7)、(8)のように表される。

## 【数5】

$$x(k+1) = A \cdot x(k) + v(k) \quad \dots \quad (7)$$

$$y(k) = C^T \cdot x(k) + w(k) \quad \dots \quad (8)$$

## 【0187】

$k$ は離散的な時間であるタイムステップを表す。 $x(k)$ はタイムステップ $k$ （時刻 $k$ ）におけるシステムの状態であり、例えば $n$ 次元のベクトルである。Aはシステム行列と呼ばれるものである。具体的には、Aは $n \times n$ の行列であり、システムノイズがない場合のタイムステップ $k$ におけるシステムの状態とタイムステップ $k+1$ におけるシステムの状態を関連づけるものである。 $v(k)$ はシステムノイズである。 $y(k)$ は観測値であり、 $w(k)$ は観測ノイズである。Cは観測係数ベクトル（ $n$ 次元）であり、 $T$ は転置行列を表す。

## 【0188】

上式(7)、(8)のモデルのカルマンフィルター処理では、下式(9)～(13)の処理を行って、真値を推定する。

## 【数6】

$$\hat{x}^-(k) = A\hat{x}(k-1) \quad \dots \quad (9)$$

$$P^-(k) = A \cdot P(k-1) \cdot A^T + v(k) \quad \dots \quad (10)$$

$$G(k) = \frac{P^-(k) \cdot C}{C^T \cdot P^-(k) \cdot C + w(k)} \quad \dots \quad (11)$$

$$\hat{x}(k) = \hat{x}^-(k) + G(k) \cdot (y(k) - C^T \cdot \hat{x}^-(k)) \quad \dots \quad (12)$$

$$P(k) = (1 - G(k) \cdot C^T) \cdot P^-(k) \quad \dots \quad (13)$$

$\hat{x}(k)$ : 事後推定値

$\hat{x}^-(k)$ : 事前推定値

$P(k)$ : 事後共分散

$P^-(k)$ : 事前共分散

$G(k)$ : カルマンゲイン

## 【0189】

上式(9)、(10)は時間更新（予測過程）の式であり、上式(11)～(13)は観測更新（観測過程）の式である。離散的な時間であるタイムステップ $k$ が1つ進む毎に、カルマンフィルター処理の時間更新（式(9)、(10)）及び観測更新（式(11)～(13)）が1回行われる。

10

20

30

40

50

## 【0190】

$\hat{x}^-(k)$ 、 $\hat{x}^-(k-1)$ は、タイムステップ  $k$ 、 $k-1$ でのカルマンフィルター処理の事後推定値である。 $\hat{x}^-(k)$ は、観測値を得る前に予測した事前推定値である。 $P(k)$ は、カルマンフィルター処理の事後共分散であり、 $P^-(k)$ は、観測値を得る前に予測した事前共分散である。 $G(k)$ はカルマンゲインである。

## 【0191】

カルマンフィルター処理では、観測更新において、上式(11)によりカルマンゲイン  $G(k)$ が求められる。また観測値  $y(k)$ に基づいて上式(12)により、事後推定値  $\hat{x}^-(k)$ が更新される。また上式(13)により、誤差の事後共分散  $P(k)$ が更新される。

10

## 【0192】

またカルマンフィルター処理では、時間更新において、上式(9)に示すように、タイムステップ  $k-1$ での事後推定値  $\hat{x}^-(k-1)$ と、システム行列  $A$ に基づいて、次のタイムステップ  $k$ での事前推定値  $\hat{x}^-(k)$ を予測する。また上式(10)に示すように、タイムステップ  $k-1$ での事後共分散  $P(k-1)$ と、システム行列  $A$ と、システムノイズ  $v(k)$ に基づいて、次のタイムステップ  $k$ での事前共分散  $P^-(k)$ を予測する。

## 【0193】

さて、上式(9)～(13)のカルマンフィルター処理を実行しようとすると、処理部50の処理負荷が過大になり、回路装置の大規模化を招く場合がある。例えば上式(9)の  $\hat{x}^-(k) = A \hat{x}^-(k-1)$  の  $A$ を求めるためには、拡張カルマンフィルター処理が必要になる。そして拡張カルマンフィルター処理は、処理負荷が非常に重く、処理部50を、拡張カルマンフィルター処理が可能なハードウェアにより実現しようとすると、処理部50の回路面積が非常に大きくなり易い。このため、発振器に内蔵される回路装置に小型化が強く求められている状況においては不適なものになってしまふ。一方、システム行列  $A$ として固定値のスカラー値を用いると、適切なエージング補正を実現する際の難易度が上がる。

20

## 【0194】

そこでこのような状況を避ける必要性がある場合の解決手段として、本実施形態では、カルマンフィルター処理を、上式(9)～(13)に代えて、下式(14)～(19)に従った処理により実現する。即ち、処理部50(カルマンフィルター部54)は、下式(14)～(19)に基づくカルマンフィルター処理を実行する。

30

## 【数7】

$$\hat{x}^-(k) = \hat{x}(k-1) + D(k-1) \quad \dots (14)$$

$$P^-(k) = P(k-1) + v(k) \quad \dots (15)$$

$$G(k) = \frac{P^-(k)}{P^-(k) + w(k)} \quad \dots (16)$$

$$\hat{x}(k) = \hat{x}^-(k) + G(k) \cdot (y(k) - \hat{x}^-(k)) \quad \dots (17)$$

$$P(k) = (1 - G(k)) \cdot P^-(k) \quad \dots (18)$$

$$D(k) = D(k-1) + E \cdot (y(k) - \hat{x}^-(k)) \quad \dots (19)$$

40

## 【0195】

なお本実施形態において、真値の推定処理の対象となる  $x(k)$  は周波数制御データであり、観測値  $y(k)$  も周波数制御データであるため、 $C = 1$  になる。また、 $A$  のスカラー値は 1 に限りなく近いため、上式(10)の代わりに上式(15)を用いることができる。

## 【0196】

前述したように、カルマンフィルター処理として、拡張カルマンフィルター処理を採用

50

する場合と比較して、本実施形態のカルマンフィルター処理では、上式(14)に示すように、タイムステップkでの事前推定値 $\hat{x}^-(k)$ を、タイムステップk-1での事後推定値 $\hat{x}^-(k-1)$ と補正值D(k-1)の加算処理により求めている。このため、拡張カルマンフィルター処理を用いる必要がなくなり、処理部50の処理負荷の軽減や回路規模の増加の抑制等を図れるという点で優れる。

#### 【0197】

本実施形態では下記のような式の変形により、上式(14)を導出している。

#### 【数8】

$$\begin{aligned}\hat{x}^-(k) &= A\hat{x}(k-1) && \cdots (20) \\ &= \hat{x}(k-1) + (A-1) \cdot \hat{x}(k-1) && \cdots (21) \\ &\approx \hat{x}(k-1) + (A-1) \cdot F_0 && \cdots (22) \\ &= \hat{x}(k-1) + D(k-1) && \cdots (23)\end{aligned}$$

10

#### 【0198】

例えば上式(20)は上式(21)のように変形できる。ここで上式(21)の(A-1)は非常に小さい数になるため、上式(22)、(23)に示すように、(A-1)・ $\hat{x}^-(k-1)$ を、(A-1)・ $F_0$ に置き換える近似が可能になる。そして、この(A-1)・ $F_0$ を、補正值D(k-1)と置く。

20

#### 【0199】

そして上式(19)に示すように、タイムステップk-1からタイムステップkへの時間更新の際に、補正值D(k) = D(k-1) + E・(y(k) -  $\hat{x}^-(k)$ ) = D(k-1) + E・ $e_k$ の更新処理を行う。ここで、 $e_k = y(k) - \hat{x}^-(k)$ は、カルマンフィルター処理における観測残差と呼ばれるものである。またEは定数である。なお、定数Eの代わりに、カルマンゲインG(k)を用いる変形実施も可能である。即ち、D(k) = D(k-1) + G(k)・ $e_k$ としてもよい。

#### 【0200】

このように式(19)では、観測残差を $e_k$ とし、定数をEとした場合に、D(k) = D(k-1) + E・ $e_k$ により補正值D(k)を求めている。このようにすることで、カルマンフィルター処理における観測残差 $e_k$ を反映させた、補正值D(k)の更新処理が可能になる。

30

#### 【0201】

以上のように本実施形態では、処理部50は、上式(14)に示すように、カルマンフィルター処理の事前推定値の更新処理(時間更新)において、今回のタイミングでの事前推定値 $\hat{x}^-(k)$ を、前回のタイミングでの事後推定値 $\hat{x}^-(k-1)$ と補正值D(k-1)との加算処理により求める処理を行う。そしてカルマンフィルター処理の結果に基づいて、周波数制御データのエージング補正を行う。即ち、前回のタイミングであるタイムステップk-1での事後推定値 $\hat{x}^-(k-1)$ と補正值D(k-1)との加算処理を行って、今回のタイミングであるタイムステップkでの事前推定値 $\hat{x}^-(k)$ を、 $\hat{x}^-(k) = \hat{x}^-(k-1) + D(k-1)$ により求める。

40

#### 【0202】

そして処理部50(エージング補正部56)は、このカルマンフィルター処理の結果(真値、補正值)に基づいて、エージング補正を行う。即ち、タイムステップkでの補正值をD(k)(或いはD'(k))とし、タイムステップkでのエージング補正された周波数制御データをAC(k)とした場合に、タイムステップk+1でのエージング補正された周波数制御データAC(k+1)を、 $AC(k+1) = AC(k) + D(k)$ (或いは $AC(k) + D'(k)$ )により求める。

#### 【0203】

また処理部50は、上式(19)に示すように、今回のタイミングでの補正值D(k)

50

を、前回のタイミングでの補正值  $D(k-1)$  とカルマンフィルター処理での観測残差  $e_k$  に基づいて求める。例えば前回のタイミングでの補正值  $D(k-1)$  に対して、観測残差に基づく値である  $E \cdot e_k$  (或いは  $G(k) \cdot e_k$ ) を加算する処理を行うことで、今回のタイミングでの補正值  $D(k)$  を求める。具体的には、今回のタイミングであるタイムステップ  $k$  での補正值  $D(k)$  を、前回のタイミングであるタイムステップ  $k-1$  での補正值  $D(k-1)$  とカルマンフィルター処理における観測残差  $e_k$  に基づいて求める。例えば、観測残差を  $e_k$  とし、定数を  $E$  とした場合に、 $D(k) = D(k-1) + E \cdot e_k$  により、補正值  $D(k)$  を求める。

#### 【0204】

例えば本実施形態では、図16Bで説明したように、温度変動成分情報等の環境変動成分情報を取得し、取得された環境変動成分情報を用いて、環境変動成分とエージング変動成分のうち環境変動成分が除かれた周波数制御データを取得する。ここで環境変動成分情報は、電源電圧変動成分、気圧変動成分又は重力変動成分等であってもよい。そして環境変動成分が除かれた周波数制御データに基づいて、エージング補正を行う。具体的には環境変動成分が温度であったとする。この場合、環境変動成分情報を取得するための環境変動情報取得部としての図4の外部温度センサー12又は内部温度センサー10からの、温度検出電圧VTDにより求められる温度検出データDTDに基づいて、環境変動成分情報である温度変動成分情報を取得する。そして取得された温度変動成分情報を用いて、温度変動成分が除かれた周波数制御データが取得される。例えば図13の温度補償部58が温度補償データTCODEを取得し、加算器65により温度補償データTCODEの加算処理を行うことで、温度変動成分が除去された周波数制御データDFCIが周波数制御データ生成部40から入力され、処理部50により取得されるようになる。即ち、図16BのE2に示すように、温度変動成分が除去される一方で、エージング変動成分が残存した周波数制御データDFCIが取得されて、カルマンフィルター部54に入力されるようになる。

#### 【0205】

なお、環境変動成分が除かれた周波数制御データとは、環境変動成分が完全に除かれた好適な状態の周波数制御データの他に、周波数制御データ内に無視できるレベルの環境変動成分が含まれている状態の周波数制御データも含む。

#### 【0206】

例えば温度変動成分情報、或いは電源電圧変動成分情報等の環境変動成分情報については、環境変動成分情報を検出する環境変動情報取得部である温度センサー、電圧検出回路等により取得することができる。一方、エージング変動成分は、時間経過と共に変化する発振周波数の変動成分であり、当該エージング変動成分の情報をセンサー等により直接に検出することは難しい。

#### 【0207】

そこで本実施形態では、センサー等により検出可能な温度変動成分情報等の環境変動成分情報を取得し、この環境変動成分情報を用いて、環境変動成分とエージング変動成分のうち環境変動成分が除かれた周波数制御データを取得する。即ち、周波数制御データの変動成分から、環境変動成分を除去する処理(例えば加算器65による加算処理)を行うことで、図16BのE2に示すようにエージング変動成分だけが残存した周波数制御データを取得できる。そして、エージング変動成分が残存した周波数制御データに基づいて、カルマンフィルター処理等を行えば、周波数制御データについての真値を推定できる。そして、このようにして推定された真値に基づいて、エージング補正を行えば、従来例では実現できなかった高精度のエージング補正を実現できるようになる。

#### 【0208】

このように本実施形態では、カルマンフィルター部54には、温度変動成分(環境変動成分)が除去される一方で、エージング変動成分が残存する周波数制御データDFCIが入力されている。そして図11、図14Aに示すように、期間を限定すれば、その期間内では、発振周波数は一定のエージングレートで変化するものと想定できる。例えば図14

10

20

30

40

50

AのC3に示すような一定の傾きで変化するものと想定できる。

【0209】

本実施形態では、このようなエージング変動成分による一定のエージングレートでの周波数変化を、補償（キャンセル）するための補正值を、 $D(k) = D(k-1) + E \cdot e^k$  の式により求めている。即ち、図14AのC3の傾きに相当するエージングレートによる周波数変化を、補償するための補正值 $D(k)$ を求めている。ここで、エージングレートは一定ではなく、図11、図14Aに示すように、経過時間に応じて変化する。

【0210】

この点、本実施形態では、 $D(k) = D(k-1) + E \cdot e^k$  というように、カルマンフィルター処理の観測残差 $e_k = y(k) - x^{(k)}$ に基づいて、エージングレートに対応する補正值 $D(k)$ の更新処理を行っている。従って、経過時間に応じたエージングレートの変化についても反映させた補正值 $D(k)$ の更新処理を実現できるようになる。従って、より高精度なエージング補正の実現が可能になる。

【0211】

11. 温度センサー、発振回路

図18Aに内部温度センサー10の構成例を示す。図18Aの内部温度センサー10は、電流源ISTと、電流源ISTからの電流がコレクターに供給されるバイポーラートランジスターTRTを有する。バイポーラートランジスターTRTは、そのコレクターとのベースが接続されるダイオード接続となっており、バイポーラートランジスターTRTのコレクターのノードに、温度特性を有する温度検出電圧VTDIが outputされる。温度検出電圧VTDIの温度特性は、バイポーラートランジスターTRTのベース・エミッター間電圧の温度依存性によって生じる。この内部温度センサー10の温度検出電圧VTDIは、例えは負の温度特性（負の勾配を有する1次の温度特性）を有する。

【0212】

図18Bに発振回路150の構成例を示す。この発振回路150は、電流源IBX、バイポーラートランジスターTRX、抵抗RX、可変容量キャパシターCX1、キャパシタ-CX2、CX3を有する。

【0213】

電流源IBXは、バイポーラートランジスターTRXのコレクターにバイアス電流を供給する。抵抗RXは、バイポーラートランジスターTRXのコレクターとベースの間に設けられる。

【0214】

容量が可変である可変容量キャパシターCX1の一端は、振動子XTALの一端に接続される。具体的には、可変容量キャパシターCX1の一端は、回路装置の第1の振動子用端子（振動子用パッド）を介して振動子XTALの一端に接続される。キャパシターCX2の一端は、振動子XTALの他端に接続される。具体的には、キャパシターCX2の一端は、回路装置の第2の振動子用端子（振動子用パッド）を介して振動子XTALの他端に接続される。キャパシターCX3は、その一端が振動子XTALの一端に接続され、その他端がバイポーラートランジスターTRXのコレクターに接続される。

【0215】

バイポーラートランジスターTRXには、振動子XTALの発振により生じたベース・エミッター間電流が流れる。そしてベース・エミッター間電流が増加すると、バイポーラートランジスターTRXのコレクター・エミッター間電流が増加し、電流源IBXから抵抗RXに分岐するバイアス電流が減少するので、コレクター電圧VCXが低下する。一方、バイポーラートランジスターTRXのベース・エミッター間電流が減少すると、コレクター・エミッター間電流が減少し、電流源IBXから抵抗RXに分岐するバイアス電流が増加するので、コレクター電圧VCXが上昇する。このコレクター電圧VCXはキャパシターCX3を介して振動子XTALにフィードバックされる。

【0216】

振動子XTALの発振周波数は温度特性を有しており、この温度特性は、D/A変換部

10

20

30

40

50

80の出力電圧VQ（周波数制御電圧）により補償される。即ち、出力電圧VQは可変容量キャパシターCX1に入力され、出力電圧VQにより可変容量キャパシターCX1の容量値が制御される。可変容量キャパシターCX1の容量値が変化すると、発振ループの共振周波数が変化するので、振動子XTALの温度特性による発振周波数の変動が補償される。可変容量キャパシターCX1は、例えば可変容量ダイオード（バラクター）などにより実現される。

#### 【0217】

なお、本実施形態の発振回路150は、図18Bの構成に限定されず、種々の変形実施が可能である。例えば図18BではCX1を可変容量キャパシターとする場合を例に説明したが、CX2又はCX3を、出力電圧VQで制御される可変容量キャパシターとしてもよい。また、CX1～CX3のうち複数を、出力電圧VQで制御される可変容量キャパシターとしてもよい。

#### 【0218】

また、発振回路150は、振動子XTALを発振させるためのすべての回路要素を含んでいなくてもよい。例えば、回路装置500の外部に設けたディスクリート部品によって一部の回路要素を構成し、外部接続端子を介して発振回路150と接続するような構成であってもよい。

#### 【0219】

##### 12. 变形例

次に本実施形態の種々の変形例について説明する。図19Aに本実施形態の変形例の回路装置の構成例を示す。

#### 【0220】

図19Aでは、図1、図4、図13とは異なり、発振信号生成回路140にD/A変換部80が設けられていない。そして発振信号生成回路140により生成される発振信号OSC Kの発振周波数が、処理部50からの周波数制御データDFCQに基づいて、直接に制御される。即ちD/A変換部を介さずに発振信号OSC Kの発振周波数が制御される。

#### 【0221】

例えば図19Aでは、発振信号生成回路140が、可変容量回路142と発振回路150を有する。この発振信号生成回路140には図1、図4、図13のD/A変換部80は設けられていない。そして図18Bの可変容量キャパシターCX1の代わりに、この可変容量回路142が設けられ、可変容量回路142の一端が振動子XTALの一端に接続される。

#### 【0222】

この可変容量回路142は、処理部50からの周波数制御データDFCQに基づいて、その容量値が制御される。例えば可変容量回路142は、複数のキャパシター（キャパシターアレイ）と、周波数制御データDFCQに基づき各スイッチ素子のオン、オフが制御される複数のスイッチ素子（スイッチアレイ）を有する。これらの複数のスイッチ素子の各スイッチ素子は、複数のキャパシターの各キャパシターに電気的に接続される。そして、これらの複数のスイッチ素子がオン又はオフされることで、複数のキャパシターのうち、振動子XTALの一端に、その一端が接続されるキャパシターの個数が変化する。これにより、可変容量回路142の容量値が制御されて、振動子XTALの一端の容量値が変化する。従って、周波数制御データDFCQにより、可変容量回路142の容量値が直接に制御されて、発振信号OSC Kの発振周波数を制御できるようになる。

#### 【0223】

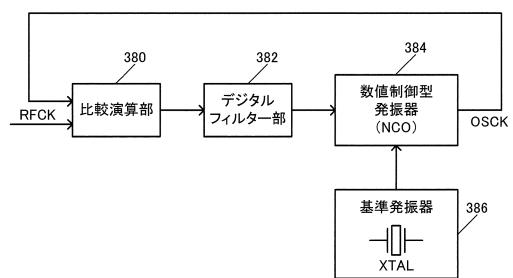

また本実施形態の回路装置を用いてPLL回路を構成する場合に、ダイレクト・デジタル・シンセサイザー方式のPLL回路とすることも可能である。図19Bにダイレクト・デジタル・シンセサイザー方式の場合の回路構成例を示す。

#### 【0224】

比較演算部380は、基準信号RFC Kと発振信号OSC K（発振信号に基づく入力信号）の比較演算を行う。デジタルフィルター部382は、位相誤差の平滑化処理を行う。

10

20

30

40

50

比較演算部 380 の構成、動作は図 13 の比較演算部 41 と同様であり、カウンターや T D C ( 時間デジタル変換器 ) を含むことができる。デジタルフィルター部 382 は図 13 のデジタルフィルター部 44 に相当するものである。数値制御型発振器 384 は、振動子 X T A L を有する基準発振器 386 からの基準発振信号を用いて、任意の周波数や波形をデジタル的に合成する回路である。即ち V C O のように D / A 変換器からの制御電圧に基づいて発振周波数を制御するのではなく、デジタルの周波数制御データと基準発振器 386 ( 振動子 X T A L ) を用いて、デジタル演算処理により任意の発振周波数の発振信号 O S C K を生成する。

【 0225 】

13. 発振器、電子機器、移動体

10

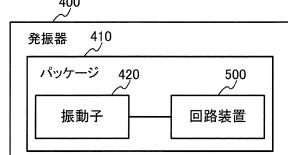

図 20A に、本実施形態の回路装置 500 を含む発振器 400 の構成例を示す。図 20A に示すように、発振器 400 は、振動子 420 と回路装置 500 を含む。振動子 420 と回路装置 500 は、発振器 400 のパッケージ 410 内に実装される。そして振動子 420 の端子と、回路装置 500 ( I C ) の端子 ( パッド ) は、パッケージ 410 の内部配線により電気的に接続される。

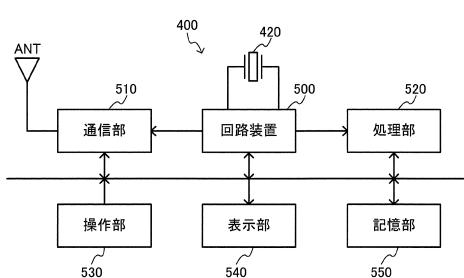

【 0226 】

図 20B に、本実施形態の回路装置 500 を含む電子機器の構成例を示す。この電子機器は、本実施形態の回路装置 500 、水晶振動子等の振動子 420 、アンテナ A N T 、通信部 510 、処理部 520 を含む。また操作部 530 、表示部 540 、記憶部 550 を含むことができる。振動子 420 と回路装置 500 により発振器 400 が構成される。なお電子機器は図 20B の構成に限定されず、これらの一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

20

【 0227 】

図 20B の電子機器としては、例えば基地局又はルーター等のネットワーク関連機器や、高精度の計測機器や、 G P S 内蔵時計、生体情報測定機器 ( 脈波計、歩数計等 ) 又は頭部装着型表示装置等のウェアラブル機器や、スマートフォン、携帯電話機、携帯型ゲーム装置、ノート P C 又はタブレット P C 等の携帯情報端末 ( 移動端末 ) や、コンテンツを配信するコンテンツ提供端末や、デジタルカメラ又はビデオカメラ等の映像機器などの種々の機器を想定できる。

30

【 0228 】

通信部 510 ( 無線回路 ) は、アンテナ A N T を介して外部からデータを受信したり、外部にデータを送信する処理を行う。処理部 520 は、電子機器の制御処理や、通信部 510 を介して送受信されるデータの種々のデジタル処理などを行う。この処理部 520 の機能は、例えばマイクロコンピューターなどのプロセッサーにより実現できる。

【 0229 】

操作部 530 は、ユーザーが入力操作を行うためのものであり、操作ボタンやタッチパネルディスプレイをなどにより実現できる。表示部 540 は、各種の情報を表示するものであり、液晶や有機 E L などのディスプレイにより実現できる。なお操作部 530 としてタッチパネルディスプレイを用いる場合には、このタッチパネルディスプレイが操作部 530 及び表示部 540 の機能を兼ねることになる。記憶部 550 は、データを記憶するものであり、その機能は R A M や R O M などの半導体メモリーや H D D ( ハードディスクドライブ ) などにより実現できる。

40

【 0230 】

図 20C に、本実施形態の回路装置を含む移動体の例を示す。本実施形態の回路装置 ( 発振器 ) は、例えば、車、飛行機、バイク、自転車、或いは船舶等の種々の移動体に組み込むことができる。移動体は、例えばエンジンやモーター等の駆動機構、ハンドルや舵等の操舵機構、各種の電子機器 ( 車載機器 ) を備えて、地上や空や海上を移動する機器・装置である。図 20C は移動体の具体例としての自動車 206 を概略的に示している。自動車 206 には、本実施形態の回路装置と振動子を有する発振器 ( 不図示 ) が組み込まれる。制御装置 208 は、この発振器により生成されたクロック信号により動作する。制御装

50

置 2 0 8 は、例えば車体 2 0 7 の姿勢に応じてサスペンションの硬軟を制御したり、個々の車輪 2 0 9 のブレーキを制御する。例えば制御装置 2 0 8 により、自動車 2 0 6 の自動運転を実現してもよい。なお本実施形態の回路装置や発振器が組み込まれる機器は、このような制御装置 2 0 8 には限定されず、自動車 2 0 6 等の移動体に設けられる種々の機器（車載機器）に組み込むことが可能である。

【 0 2 3 1 】

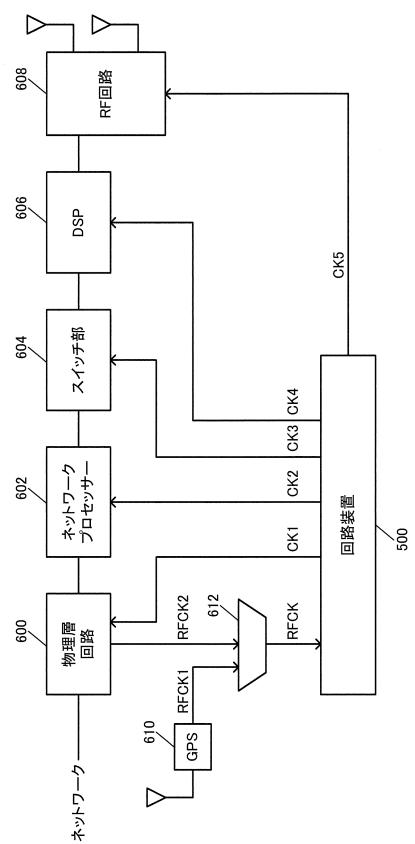

図 2 1 は電子機器の 1 つである基地局（基地局装置）の構成例である。物理層回路 6 0 0 はネットワークを介した通信処理における物理層の処理を行う。ネットワークプロセッサー 6 0 2 は、物理層よりも上位層の処理（リンク層等）を行う。スイッチ部 6 0 4 は通信処理の各種の切替処理を行う。D S P 6 0 8 は、通信処理に必要な各種のデジタル信号処理を行う。R F 回路 6 0 8 は、ローノイズアンプ（L N A）により構成される受信回路、や、パワーアンプにより構成される送信回路や、D / A 変換器、A / D 変換器などを含む。

10

【 0 2 3 2 】

セレクター 6 1 2 は、G P S 6 1 0 からの基準信号 R F C K 1 、物理層回路 6 0 0 からの基準信号 R F C K 2 （ネットワークからクロック信号）のいずれかを、基準信号 R F C K として、本実施形態の回路装置 5 0 0 に出力する。回路装置 5 0 0 は、基準信号 R F C K に対して発振信号（発振信号に基づく入力信号）を同期させる処理を行う。そして周波数が異なる各種のクロック信号 C K 1 、C K 2 、C K 3 、C K 4 、C K 5 を生成して、物理層回路 6 0 0 、ネットワークプロセッサー 6 0 2 、スイッチ部 6 0 4 、D S P 6 0 6 、R F 回路 6 0 8 に供給する。

20

【 0 2 3 3 】

本実施形態の回路装置 5 0 0 によれば、図 2 1 に示すような基地局において、基準信号 R F C K に発振信号を同期させ、当該発振信号に基づいて生成された周波数安定度の高いクロック信号 C K 1 ～ C K 5 を、基地局の各回路に供給できるようになる。

【 0 2 3 4 】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本発明の範囲に含まれる。また外部温度センサー、プログラマブルゲインアンプ、デジタルフィルター部、処理部、オープン制御回路、回路装置、発振器、電子機器、移動体の構成・動作等も、本実施形態で説明したものに限定されず、種々の変形実施が可能である。

30

【 符号の説明 】

【 0 2 3 5 】

1 0 … 内部温度センサー、1 2 … 外部温度センサー、2 0 … A / D 変換部、

2 2 … プログラマブルゲインアンプ、2 4 … デジタルフィルター部、

2 6 … セレクター、3 0 … デジタル I / F 部、3 2 … レジスター部、3 4 … 記憶部、

40

4 0 … 周波数制御データ生成部、4 1 … 比較演算部、4 2 … カウンター、

4 4 … デジタルフィルター部、5 0 … 処理部、5 2 … ホールドオーバー処理部、

5 4 … カルマンフィルター部、5 6 … エージング補正部、5 8 … 温度補償部、

6 2 , 6 3 … セレクター、6 5 … 加算器、8 0 … D / A 変換部、

1 4 0 … 発振信号生成回路、1 4 2 … 可変容量回路、1 5 0 … 発振回路、

1 9 0 … オープン制御回路、1 9 1 … ヒーター、

1 9 2 … 発熱パワーバイポーラトランジスター、1 9 3 … 温度センサー、

1 9 4 … 発熱M O Sトランジスター、2 0 6 … 自動車、2 0 7 … 車体、

2 0 8 … 制御装置、2 0 9 … 車輪、3 4 0 … 加算器、3 5 0 , 3 5 1 … レジスター、

3 6 0 , 3 6 1 … セレクター、3 8 0 … 比較演算部、3 8 2 … デジタルフィルター部、

50

3 8 4 ... 数値制御型発振器、 3 8 6 ... 基準発振器、 4 0 0 ... 発振器、

4 1 0 ... パッケージ、 4 1 1 ... 基板、 4 1 2 ... ケース、 4 1 3 ... 第 1 の容器、

4 1 4 ... 第 2 の容器、 4 1 6 ... 基板、 4 2 0 ... 振動子、 4 5 0 , 4 5 2 ... ヒーター、

4 6 0 , 4 6 2 ... 温度センサー、 5 0 0 ... 回路装置、 5 1 0 ... 通信部、

5 2 0 ... 処理部、 5 3 0 ... 操作部、 5 4 0 ... 表示部、 5 5 0 ... 記憶部、

6 0 0 ... 物理層回路、 6 0 2 ... ネットワークプロセッサー、 6 0 4 ... スイッチ部、

6 0 8 ... R F 回路、 6 1 0 ... G P S 、 6 1 2 ... セレクター、

O S C K ... 発振信号、 R F C K ... 基準信号、 T V T ... 温度センサー入力端子、

V T D ... 温度検出電圧、 V T D E ... 外部温度検出電圧、

V T D I ... 内部温度検出電圧、 X T A L ... オープン型振動子（振動子）

10

【 义 1 】

【 図 2 】

〔 3 〕

【図4】

【図7】

【図5】

| センシング温度幅 $\Delta T_{TS} [^{\circ}\text{C}]$<br>( $T_{TS} [^{\circ}\text{C}]$ ) | 必要なPGAゲイン<br>(外部温度センサー) | 必要なPGAゲイン<br>(内部温度センサー) |

|--------------------------------------------------------------------------------|-------------------------|-------------------------|

| 150 (-50~100)                                                                  | 1                       | 5.9                     |

| 70 (30~100)                                                                    | 2.3                     | 12.6                    |

| 30 (70~100)                                                                    | 5.4                     | 29.3                    |

| 10 (85~95)                                                                     | 16                      | 87.9                    |

【図6】

【図8】

【図9】

【図10】

図10B

【図11】

【図12】

【図13】

【図14】

図14A

図14B

【図15】

【図16】

図16A

| PLLLOCK | KFEN | $\hat{x}(k)$            |

|---------|------|-------------------------|

| 0       | 0    | DFCI(スルー出力)             |

| 0       | 1    | 前回出力状態保持                |

| 1       | 0    | DFCI(スルー出力)             |

| 1       | 1    | 真値推定処理<br>(カルマンフィルター処理) |

図16B

【図17】

【図18】

図18A

図18B

【図19】

図19A

図19B

【図20】

図20A

図20B

図20C

【図21】

---

フロントページの続き

(56)参考文献 特開2015-046704(JP, A)

特開2010-263503(JP, A)

特開2013-142648(JP, A)

特開2011-217302(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03B 5/32

H03L 1/02