(19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2007-173669 (P2007-173669A)

(43) 公開日 平成19年7月5日(2007.7.5)

(51) Int.C1.

FL

テーマコード (参考)

HO1L 25/00

(2006, 01)

HO1L 25/00

В

審査請求 未請求 請求項の数 14 〇L (全 19 頁)

(21) 出願番号 (22) 出願日 特願2005-371530 (P2005-371530) 平成17年12月26日 (2005.12.26)

|(71)出願人 000006231

株式会社村田製作所

京都府長岡京市東神足1丁目1〇番1号

(74)代理人 100101926

弁理士 塚原 孝和

(72) 発明者 山長 功

京都府長岡京市東神足1丁目1〇番1号

株式会社村田製作所内

(72) 発明者 東 貴博

京都府長岡京市東神足1丁目1〇番1号

株式会社村田製作所内

(54) 【発明の名称】多層回路基板及び I Cパッケージ

# (57)【要約】

【課題】デカップリング及びバイパスの機能を有するコンデンサをICの電源端子の間近に実装することで、ICの誤動作を防止した多層回路基板及びICパッケージを提供する。

【解決手段】I Cパッケージ1と信号層2とグランド層3と電源層4とを備える。I Cパッケージ1はB G A タイプの端子群と凹部11とを有している。信号層2は2端子コンデンサ7用の実装スペースS1を有し、この実装スペースS1内に、I Cパッケージ1の電源端子12に対応したランド21とこのランド21に対向するランド22とが形成されている。2端子コンデンサ7はランド21,2は2端子コンデンサ7が接続されたランド21,ビアホール41~43を通じて電源層4に接続され、2端子コンデンサ7のアース端子72はランド22及びビアホール31を通じてグランド層3に接続される。

#### 【選択図】図1

#### 【特許請求の範囲】

# 【請求項1】

裏面にBGAタイプの端子群を有したICパッケージが表面に実装され且つ電源層とグランド層とが設けられた多層回路基板であって、

上記ICパッケージの裏面と対向するIC実装領域内に、コンデンサの実装スペースを 設けて、コンデンサを当該実装スペースに配し、

当該コンデンサの電源用の電極を、上記ICパッケージの電源端子に接続すると共に上記電源層に接続し、グランド用の電極を、上記グランド層に接続した、

ことを特徴とする多層回路基板。

#### 【請求項2】

請求項1に記載の多層回路基板において、

上記コンデンサは、チップ型の2端子コンデンサであり、

上記電源用の電極は、当該2端子コンデンサの入出力端子であり、

上記グランド用の電極は、当該2端子コンデンサのアース端子である、

ことを特徴とする多層回路基板。

#### 【請求項3】

請求項1に記載の多層回路基板において、

上記コンデンサは、チップ型の3端子コンデンサであり、

上記電源用の電極は、当該3端子コンデンサの入力端子と出力端子とでなり、当該入力端子が上記電源層に接続すると共に、当該出力端子が上記電源端子に接続し、

上記グランド用の電極は、当該3端子コンデンサのアース端子である、

ことを特徴とする多層回路基板。

#### 【請求項4】

請求項1ないし請求項3のいずれかに記載の多層回路基板において、

上記コンデンサの実装スペースを、上記ICパッケージの電源端子の近傍に設けた、

ことを特徴とする多層回路基板。

# 【請求項5】

請求項1ないし請求項4のいずれかに記載の多層回路基板において、

上記ICパッケージの裏面であって且つ上記コンデンサの実装スペースに対応する個所に、当該ICパッケージとコンデンサとの接触を回避するための凹部を形成した、

ことを特徴とする多層回路基板。

# 【請求項6】

請 求 項 1 な い し 請 求 項 5 の い ず れ か に 記 載 の 多 層 回 路 基 板 に お い て 、

上記コンデンサの実装スペースを、上記ICパッケージの裏面と対向する上記IC実装領域のほぼ中央部に設けた、

ことを特徴とする多層回路基板。

#### 【請求項7】

請求項1ないし請求項5のいずれかに記載の多層回路基板において、

上記コンデンサの実装スペースを、上記ICパッケージの裏面と対向する上記IC実装 領域の周縁部に1以上設けた、

ことを特徴とする多層回路基板。

#### 【請求項8】

電源端子とグランド端子とを含むBGAタイプの端子群を裏面に有し且つ多層回路基板の表面に実装されるICパッケージであって、

上記ICパッケージの端子群内に、コンデンサの実装スペースを設けて、コンデンサを 当該実装スペースに取り付け、

当該コンデンサの電源用の電極を、上記電源端子に接続すると共に、グランド用の電極を、上記グランド端子に接続した、

ことを特徴とするICパッケージ。

## 【請求項9】

50

40

10

20

請求項8に記載のICパッケージにおいて、

上記コンデンサは、チップ型の2端子コンデンサであり、

上記電源用の電極は、当該2端子コンデンサの入出力端子であり、

上記グランド用の電極は、当該2端子コンデンサのアース端子である、

ことを特徴とするICパッケージ。

#### 【請求項10】

請求項8に記載のICパッケージにおいて、

上記コンデンサは、チップ型の3端子コンデンサであり、

上記電源用の電極は、当該3端子コンデンサの入力端子と出力端子とでなり、当該入力端子を、上記多層回路基板の電源層に接続すると共に、当該出力端子が、上記電源端子に接続し、

上記グランド用の電極は、当該3端子コンデンサのアース端子である、

ことを特徴とするICパッケージ。

# 【請求項11】

請求項8ないし請求項10のいずれかに記載のICパッケージにおいて、

上記コンデンサの実装スペースを、上記電源端子とグランド端子の近傍に設けた、

ことを特徴とするICパッケージ。

#### 【請求項12】

請求項8ないし請求項10のいずれかに記載のICパッケージにおいて、

互いに電気的に接続された複数の電源端子と互いに電気的に接続された複数のグランド 端子とを、上記コンデンサの実装スペースの周囲に配置した、

ことを特徴とするICパッケージ。

#### 【請求項13】

請求項8ないし請求項12のいずれかに記載のICパッケージにおいて、

上記コンデンサの実装スペースに対応する個所に、上記コンデンサを収納する凹部を形成した、

ことを特徴とするICパッケージ。

#### 【請求項14】

請求項8ないし請求項13のいずれかに記載のICパッケージにおいて、

上記コンデンサの実装スペースを、上記端子群内のほぼ中央部に設けた、

ことを特徴とするICパッケージ。

# 【発明の詳細な説明】

#### 【技術分野】

# [0001]

この発明は、BGA(Ball Grid Array)タイプのICパッケージを搭載した多層回路基板及びICパッケージに関するものである。

#### 【背景技術】

#### [0002]

携帯情報端末等の電子機器では、高機能化に伴いICの集積化と信号周波数の高速化が進んでいるが、このICの高集積化と高周波化が高周波の電源電流の増加を招き、誤動作、受信障害,放射ノイズの増大という様々な問題を引き起こしている。特に、電源ラインは、ノイズを生み出している根源であり、ノイズ電流がICのスイッチングによって電源端子に生じ、このノイズ電流が電源ラインを伝導して基板全体に広がるおそれがある。

このため、一般には、コンデンサを基板の電源ラインに配設し、デカップリングコンデンサとして機能させることで、発生したノイズが他の回路に流出することを防ぐと共に、バイパスコンデンサとして機能させることで、電源ピンに電荷を供給し、電源電圧を安定させ、誤作動を防止する。

ところが、端子群がBGAタイプのICでは、多数のコンデンサを基板の表面に実装して、上記機能を確実に発揮させることは、構造上困難である。このため、従来の技術では、コンデンサを基板の裏面であって且つICのほぼ真下に配設することにより、コンデン

10

20

30

40

サの上記機能を可能な限り発揮させるようにしている(例えば、特許文献 1 参照)。

[0003]

【特許文献1】特開2004-006488号公報

【発明の開示】

【発明が解決しようとする課題】

[0004]

上記のようなコンデンサでは、一方端子をICの電源端子と電源層との間に接続すると共に、他方端子をグランド層に接続するが、コンデンサを適切な個所に接続しないと、ICに供給される電流によって逆起電力が発生して、電源電圧が低下し、ICが誤動作を起こすおそれがある。この逆起電力は、ICの電源端子からコンデンサ迄のパターンのインダクタンスとの和に比例する。したがって、ICの誤動作を防止するためには、これらのインダクタンス値を極力小さくするようにコンデンサを配設する必要がある。しかしながら、上述した従来の技術では、コンデンサを基板の裏面に配設した構造をとった場合、インダクタンスの高いビアホールによって基板の表面と裏面をつなぐことになる。このため、電源端子からコンデンサ迄のインダクタンスやコンデンサからグランド層

[0005]

この発明は、上述した課題を解決するためになされたもので、デカップリング及びバイパスの機能を有するコンデンサをICの電源端子の間近に実装することで、ICの誤動作を防止した多層回路基板及びICパッケージを提供することを目的とする。

迄のインダクタンスが大きくなり、その結果、ICが誤動作を起こすおそれが高かった。

【課題を解決するための手段】

[0006]

上記課題を解決するために、請求項1の発明は、裏面にBGAタイプの端子群を有したICパッケージが表面に実装され且つ電源層とグランド層とが設けられた多層回路基板であって、ICパッケージの裏面と対向するIC実装領域内に、コンデンサの実装スペースを設けて、コンデンサを実装スペースに配し、コンデンサの電源用の電極を、ICパッケージの電源端子に接続すると共に電源層に接続し、グランド用の電極を、グランド層に接続した構成とする。

かかる構成により、外部電源が電源層に入力されると、電源層に接続されたコンデンサに充電される。そして、コンデンサに充電された電荷が、ICパッケージのスイッチング等のタイミングで電源端子を通じてICパッケージに電流として供給される。したがって、電源電圧を安定させるバイパスコンデンサとして機能する。

また、ICパッケージのスイッチング等によって電源端子に生じたノイズ電流は、コンデンサの電源用の電極及びグランド用の電極を通じてグランド層に排出される。したがって、コンデンサは、発生したノイズを除去するデカップリングコンデンサとして機能する

ところで、ICパッケージに電流が供給されると、ICパッケージの電源端子からコンデンサ迄のインダクタンスと、コンデンサの残留インダクタンスと、コンデンサからグランド層迄のインダクタンスとの和に比例した逆起電力が発生する。

しかし、この発明では、コンデンサを、ICパッケージの裏面と対向するIC実装領域に設けられた実装スペースに配しているので、ICパッケージの電源端子からコンデンサ 迄の距離と、コンデンサからグランド層迄の距離が短くなり、これらの間のインダクタンス値が小さくなる。このため、ICパッケージに供給される電流によって生じる逆起電力は、上記した従来の技術で生じる逆起電力に比べて、極めて小さくなる。

[0007]

請求項2の発明は、請求項1に記載の多層回路基板において、コンデンサは、チップ型の2端子コンデンサであり、電源用の電極は、2端子コンデンサの入出力端子であり、グランド用の電極は、2端子コンデンサのアース端子である構成とした。

かかる構成により、外部電源が電源層に入力されると、電源層に接続された入出力端子

20

30

40

を通じて 2 端子コンデンサに充電される。そして、 2 端子コンデンサに充電された電荷が 入出力端子に接続された電源端子を通じてICパッケージに電流として供給される。

また、ICパッケージの電源端子に生じたノイズ電流は、2端子コンデンサの入出力端子及びアース端子を通じてグランド層に排出される。

#### [ 0 0 0 8 ]

請求項3の発明は、請求項1に記載の多層回路基板において、コンデンサは、チップ型の3端子コンデンサであり、電源用の電極は、3端子コンデンサの入力端子と出力端子とでなり、入力端子が電源層に接続すると共に、出力端子が電源端子に接続し、グランド用の電極は、3端子コンデンサのアース端子である構成とした。

かかる構成により、外部電源が電源層に入力されると、電源層に接続された入力端子を通じて3端子コンデンサに充電される。そして、3端子コンデンサに充電された電荷が出力端子に接続された電源端子を通じてICパッケージに電流として供給される。

また、電源端子に生じたノイズ電流は、3端子コンデンサを介さなければ電源層に流出できなくなるため、より高いデカップリング効果を得ることができる。

さらに、この3端子コンデンサの残留インダクタンスは、極めて小さいので、ICパッケージの電源端子からグランド層迄のインダクタンス値をさらに小さくすることができる

#### [0009]

請求項4の発明は、請求項1ないし請求項3のいずれかに記載の多層回路基板において、コンデンサの実装スペースを、ICパッケージの電源端子の近傍に設けた構成とする。かかる構成により、ICパッケージの電源端子からコンデンサ迄の間のインダクタンス値を小さくすることができる。

#### [0010]

請求項5の発明は、請求項1ないし請求項4のいずれかに記載の多層回路基板において、ICパッケージの裏面であって且つコンデンサの実装スペースに対応する個所に、ICパッケージとコンデンサとの接触を回避するための凹部を形成した構成とする。

かかる構成により、ICパッケージの実装時に、ICパッケージが凹部内に納まって、ICパッケージとコンデンサとの接触を回避することができ、この結果、多層回路基板全体の低背化を図ることができる。

#### [0011]

請求項6の発明は、請求項1ないし請求項5のいずれかに記載の多層回路基板において、コンデンサの実装スペースを、ICパッケージの裏面と対向するIC実装領域のほぼ中央部に設けた構成とする。

かかる構成により、裏面のほぼ中央部に多くの電源端子を有するICパッケージを用いることで、コンデンサを多くの電源端子に近づけることができる。

#### [0012]

請求項7の発明は、請求項1ないし請求項5のいずれかに記載の多層回路基板において、コンデンサの実装スペースを、ICパッケージの裏面と対向するIC実装領域の周縁部に1以上設けた構成とする。

かかる構成により、裏面の周縁部に多くの電源端子を有するICパッケージを用いることで、コンデンサを多くの電源端子に近づけることができる。

#### [0013]

請求項8の発明は、電源端子とグランド端子とを含むBGAタイプの端子群を裏面に有し且つ多層回路基板の表面に実装されるICパッケージであって、ICパッケージの端子群内に、コンデンサの実装スペースを設けて、コンデンサを実装スペースに取り付け、コンデンサの電源用の電極を、電源端子に接続すると共に、グランド用の電極を、グランド端子に接続した構成とする。

かかる構成により、電源端子を多層回路基板の電源層に接続し、グランド端子を多層回路基板のグランド層に接続して、ICパッケージを多層回路基板の表面に実装することができる。かかる状態で、外部電源を電源層に入力すると、電源端子を通じて電源層に接続

10

20

30

40

されたコンデンサが充電される。そして、コンデンサに充電された電荷が、電源端子を通 じてICパッケージ内に電流として供給される。したがって、コンデンサが、バイパスコ ンデンサとして機能する。

ま た 、 電 源 端 子 に 生 じ た ノ イ ズ 電 流 は 、 コ ン デ ン サ の 電 源 用 の 電 極 及 び グ ラ ン ド 用 の 電 極を通じてグランド端子に至り、グランド端子を通じてグランド層に排出される。したが って、コンデンサが、発生したノイズを除去するデカップリングコンデンサとして機能す

さらに、コンデンサを、ICパッケージの端子群内に設けられた実装スペースに取り付 け、コンデンサの電源用の電極及びグランド用の電極を、電源端子及びグランド端子に直 接接続しているので、 電源端子からコンデンサ迄のインダクタンスとコンデンサからグラ ンド端子迄のインダクタンスとを極めて小さくすることができる。

[ 0 0 1 4 ]

請求項9の発明は、請求項8に記載のICパッケージにおいて、コンデンサは、チップ 型の2端子コンデンサであり、電源用の電極は、2端子コンデンサの入出力端子であり、 グランド用の電極は、2端子コンデンサのアース端子である構成とした。

か か る 構 成 に よ り 、 I C パ ッ ケ ー ジ を 多 層 回 路 基 板 に 実 装 し て 、 外 部 電 源 を 電 源 層 に 入 力すると、外部電源が、電源層に接続された電源端子に入力し、電源端子に接続された入 出力端子を通じて2端子コンデンサに充電される。そして、2端子コンデンサに充電され た電荷が入出力端子に接続された電源端子を通じてICパッケージ内に電流として供給さ れる。

ま た 、 電 源 端 子 に 生 じ た ノ イ ズ 電 流 は 、 2 端 子 コ ン デ ン サ の 入 出 力 端 子 及 び ア ー ス 端 子 を通じてグランド端子に至り、グランド端子を通じて多層回路基板のグランド層に排出さ れる。

[0015]

請 求 項 1 0 の 発 明 は 、 請 求 項 8 に 記 載 の IC パ ッ ケ ー ジ に お い て 、 コ ン デ ン サ は 、 チ ッ プ型の3端子コンデンサであり、電源用の電極は、3端子コンデンサの入力端子と出力端 子とでなり、入力端子を、多層回路基板の電源層に接続すると共に、出力端子が、電源端 子に接続し、グランド用の電極は、3端子コンデンサのアース端子である構成とした。

かかる構成により、ICパッケージの電源端子と多層回路基板の電源層を3端子コンデ ンサを介して接続し、グランド端子を多層回路基板のグランド層に接続して、ICパッケ ー ジ を 多 層 回 路 基 板 の 表 面 に 実 装 す る こ と が で き る 。 か か る 状 態 で 、 外 部 電 源 を 電 源 層 に 入力すると、外部電源が、電源層に接続された3端子コンデンサに充電される。そして、 3 端 子 コン デ ン サ に 充 電 さ れ た 電 荷 が 出 力 端 子 に 接 続 さ れ た 電 源 端 子 を 通 じ て I C パ ッ ケ ージ内に電流として供給される。

ま た 、 電 源 端 子 に 生 じ た ノ イ ズ 電 流 は 、 3 端 子 コ ン デ ン サ の ア ー ス 端 子 を 通 じ て グ ラ ン ド端子に至り、グランド端子を通じてICパッケージのグランド電極に排出される。

さらに、この3端子コンデンサの残留インダクタンスは、極めて小さいので、電源端子 から多層回路基板のグランド層迄のインダクタンス値をさらに小さくすることができる。

[ 0 0 1 6 ]

請 求 項 1 1 の 発 明 は 、 請 求 項 8 な い し 請 求 項 1 0 の い ず れ か に 記 載 の I C パ ッ ケ ー ジ に おいて、コンデンサの実装スペースを、電源端子とグランド端子の近傍に設けた構成とす

か か る 構 成 に よ り 、 電 源 端 子 か ら コ ン デ ン サ 迄 の 間 の イ ン ダ ク タ ン ス 値 を さ ら に 小 さ く することができる。

[ 0 0 1 7 ]

請 求 項 1 2 の 発 明 は 、 請 求 項 8 な い し 請 求 項 1 0 の い ず れ か に 記 載 の I C パ ッ ケ ー ジ に お い て 、 互 い に 電 気 的 に 接 続 さ れ た 複 数 の 電 源 端 子 と 互 い に 電 気 的 に 接 続 さ れ た 複 数 の グ ランド端子とを、コンデンサの実装スペースの周囲に配置した構成とする。

かかる構成により、ICパッケージの複数の電源端子からコンデンサ迄の間のインダク タンス値を小さくすることができる。

20

10

30

40

10

20

30

40

50

#### [0018]

請求項13の発明は、請求項8ないし請求項12のいずれかに記載のICパッケージにおいて、コンデンサの実装スペースに対応する個所に、コンデンサを収納する凹部を形成した構成とする。

かかる構成により、多層回路基板への実装時におけるICパッケージの低背化が可能となる。

# [0019]

請求項14の発明は、請求項8ないし請求項13のいずれかに記載のICパッケージにおいて、コンデンサの実装スペースを、端子群内のほぼ中央部に設けた構成とする。

かかる構成により、コンデンサを、裏面のほぼ中央部に存する電源端子に近づけることができる。

#### 【発明の効果】

#### [ 0 0 2 0 ]

以上詳しく説明したように、請求項1ないし請求項7の発明によれば、、コンデンサの実装スペースを設けて、コンデンサをこの実装スペースに配するので、コンデンサの実装を容易に行うことができる。また、コンデンサを、ICパッケージの裏面と対向するIC実装領域内に設けた実装スペースに配して、ICパッケージの電源端子とコンデンサとグランド層間の距離を短くし、これらの間のインダクタンス値を小さくしたので、安定した電源電圧をICパッケージに供給することができ、この結果、ICパッケージの誤動作が生ぜず、動作特性に優れた多層回路基板を提供することができるという優れた効果がある

## [0021]

特に、請求項3の発明によれば、コンデンサとして、残留インダクタンスが極めて小さな3端子コンデンサを用いて、ICパッケージの電源端子からグランド層迄のインダクタンス値をさらに小さくしたので、ICパッケージの動作特性をさらに向上させた多層回路基板を提供することができる。

# [0022]

また、請求項4ないし請求項7の発明によれば、コンデンサをICパッケージの電源端子の近くに位置させて、電源端子からコンデンサ迄の間のインダクタンス値を小さくしたので、ICパッケージの誤動作をほぼ完全に防止することができ、ICパッケージの動作特性のさらに優れた多層回路基板を提供することができる。特に、請求項7の発明によれば、コンデンサの実装スペースを、ICパッケージの裏面と対向するIC実装領域の周縁部に1以上設けたので、コンデンサが多層回路基板表面の実装スペースに確実に実装されているか否かを、外部から容易に確認することができる。

# [0023]

また、請求項8ないし請求項14の発明によれば、コンデンサを、ICパッケージ裏面に設けた実装スペースに取り付けるので、コンデンサのICパッケージへの実装が容易になる。さらに、コンデンサを、ICパッケージの裏面の端子群内の実装スペースに取り付けることにより、電源端子からコンデンサ迄のインダクタンスとコンデンサからグランド層迄のインダクタンスを極めて小さくしたので、安定した電源電圧をICパッケージに供給することができ、この結果、誤動作のない動作特性に優れたICパッケージを提供することができるという効果がある。

## [0024]

特に、請求項10の発明によれば、コンデンサとして、残留インダクタンスが極めて小さな3端子コンデンサを用いたので、動作特性をさらに向上させたICパッケージを提供することができる。

#### [0025]

また、請求項11ないし請求項14の発明によれば、コンデンサを電源端子の近くに位置させて、電源端子からコンデンサ迄の間のインダクタンス値を小さくしたので、ICパッケージの誤動作をほぼ完全に防止することができ、動作特性の極めて優れたICパッケ

20

30

40

50

- ジを提供することができる。

【発明を実施するための最良の形態】

[0026]

以下、この発明の最良の形態について図面を参照して説明する。

- 【実施例1】

- [0027]

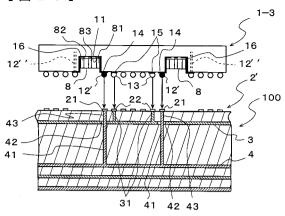

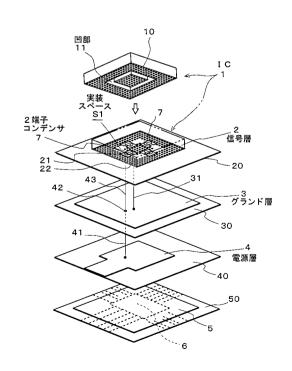

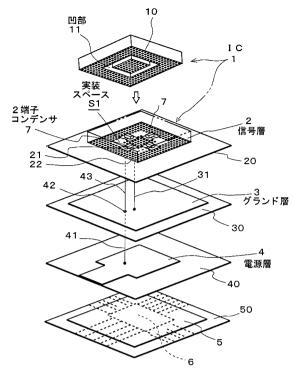

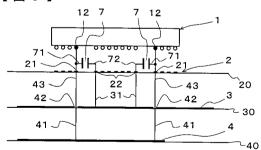

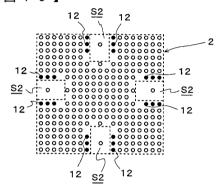

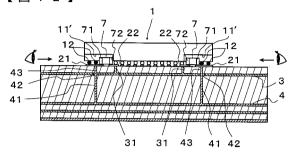

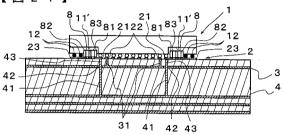

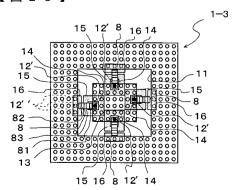

図 1 は、この発明の第 1 実施例に係る多層回路基板の分解斜視図であり、図 2 は、コンデンサの実装スペースを示す平面図である。

[0028]

この実施例の多層回路基板は、図4に示すように、ICパッケージ1を実装する最上位の信号層2と、グランド層3と、電源層4と、グランド層5と、最下位の信号層6とを備えている。

[0029]

ICパッケージ1は、コンピュータ等に用いられるCPUやチップコントローラ等の半導体集積回路であり、BGAタイプの端子群を裏面10に有している。そして、実装スペースS1と同形の凹部11を、この裏面10であって且つ後述する2端子コンデンサ7の実装スペースS1に対応する個所に有し、ICパッケージ1と2端子コンデンサ7との接触を回避している。

[0030]

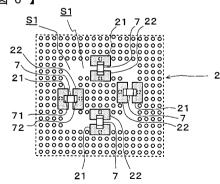

信号層 2 は、ICパッケージ 1 の端子を接続するためのランド群で成るIC実装領域であり、ICパッケージ 1 の裏面 1 0 に対向するように、絶縁層 2 0 の表面に形成されている。この信号層 2 は、平面視において、ICパッケージ 1 の端子群とほぼ同形を成し、その内側には、 2 端子コンデンサ 7 用の実装スペースS1を有している。

[ 0 0 3 1 ]

実装スペースS1は、口字状に画成された絶縁層20の表面で成り、図2に示すように、この実装スペースS1は、信号層2のほぼ中央部であって、ICパッケージ1の電源端子の近傍に位置するように設けられている。具体的には、この実施例では、ICパッケージ1の信号層2への実装時に、ICパッケージ1の電源端子12が、図2の黒丸で示す位置に位置するので、これら電源端子12が、実装スペースS1の周囲に位置するように、実装スペースS1の形状を設定した。そして、幅広の銅箔パターンで成るランド21を、黒丸で示す電源端子12対応位置に設け、ランド21が複数のこれらの電源端子12と同時に接触できるようにした。また、幅広の銅箔パターンで成るランド22を、実装スペースS1を挟んでランド21と対向する位置に設けた。

[0032]

そして、図1に示すように、複数の2端子コンデンサ7を、上記実装スペースS1に実装した。

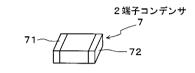

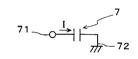

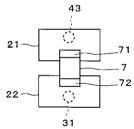

図3は、この実施例に適用する2端子コンデンサの外観図であり、図4は、2端子コンデンサの等価回路図であり、図5は、2端子コンデンサのランド実装状態を示す平面図であり、図6は、2端子コンデンサを実装スペースに実装した状態を示す平面図である。

図3に示すように、2端子コンデンサ7は、電源用の入出力端子71を一方端部に有し且つグランド用のアース端子72を他方端部に有するチップ型の2端子コンデンサである

すなわち、この2端子コンデンサ7は、誘電体シートにパターンを印刷して、パターンが交互に向き合うように、複数の誘電体シートを積層して構成したもので、図4に示すように、ノイズ等の高周波電流Iを入出力端子71からアース端子72に通す。

[0033]

このような構造の各2端子コンデンサ7は、図5に示すように、その入出力端子71を ランド21に接続すると共に、アース端子72をランド22に接続している。そして、図6に示すように、かかる接続状態で、複数の2端子コンデンサ7が実装スペースS1内に 等間隔で実装されている。

#### [0034]

図1において、グランド層3は、絶縁層30の表面の大部分に形成されており、絶縁層20を介して信号層2と対向している。かかるグランド層3は、絶縁層20に形成されたビアホール31を介して2端子コンデンサ7のランド22に接続されている。

#### [0035]

また、電源層4は、外部電源をICパッケージ1に供給するための導体層であり、絶縁層40の表面に形成され、絶縁層30を介してグランド層3の下側に位置する。かかる電源層4は、絶縁層30に形成されたビアホール41とグランド層3に開けられた孔42と絶縁層20の形成されたビアホール43とを介して2端子コンデンサ7のランド21に接続されている。

[0036]

グランド層 5 及び信号層 6 は、絶縁層 5 0 の表面及び裏面に形成され、最下層に位置する。

# [0037]

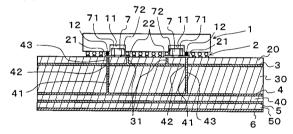

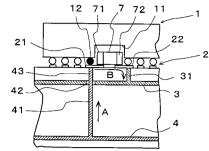

図7は、多層回路基板の概略断面図である。

この実施例の多層回路基板が上記の如き積層構造を取ることにより、図7に示すように、ICパッケージ1を信号層2に実装した状態においては、ICパッケージ1の電源端子12がランド21に接続するので、2端子コンデンサ7の入出力端子71が、ICパッケージ1の電源端子12に接続すると共に電源層4にも接続した状態になる。

また、一方、 2 端子コンデンサ 7 のアース端子 7 2 は、ランド 2 2 を通じてグランド層 3 に接続した状態になる。

#### [0038]

次に、この実施例の多層回路基板が示す作用及び効果について説明する。

図8は、各部材の電気的接続状態を示す概略図であり、図9は、2端子コンデンサの機能を説明するための概略部分拡大断面図である。

図8に示すように、ICパッケージ1を実装した状態では、ICパッケージ1の電源端子12が、2端子コンデンサ7の入出力端子71が固着されたランド21,ビアホール43,孔42,ビアホール41を通じて、電源層4に接続されている。一方、2端子コンデンサ7のアース端子72が固着されたランド22は、ビアホール31を通じてグランド層3に接続されている。

[0039]

したがって、図9において、電源を外部から電源層4に入力すると、電源電圧に対応した電荷が、矢印Aで示すように、ビアホール41~43及びランド21を通じて2端子コンデンサ7に充電される。すると、この2端子コンデンサ7に充電された電荷が、ICパッケージ1の図示しないスイッチング等のタイミングで電源端子12を通じてICパッケージ1に供給される。したがって、2端子コンデンサ7は、電源端子12に最も近い位置で電荷をICパッケージ1に供給する。このため、ICパッケージの電源端子から離れた個所にコンデンサを配した従来の技術に比べて、安定した電源電圧の供給を行うことができると共に、ノイズ発生をより効果的に防止することができ、高性能のバイパスコンデンサとして機能する。

[ 0 0 4 0 ]

また、ICパッケージ1のスイッチング等によって、ノイズが電源端子12に生じた場合には、矢印Bで示すように、電源端子12に生じたノイズ電流は、ランド21を通じて2端子コンデンサ7のランド22側に流出し、ビアホール31を通じて、グランド層3に排出される。したがって、2端子コンデンサ7は、電源端子12で発生したノイズを除去するデカップリングコンデンサとして機能する。

#### [0041]

ところで、図 8 に示すように、ICパッケージ 1 の電源端子 1 2 から 2 端子コンデンサ 7 迄のインダクタンスは、ランド 2 1 によるインダクタンスのみである。ランド 2 1 は、 幅広の銅箔パターンであり、そのインダクタンス値はほとんど無視できる。また、 2 端子 10

20

30

40

コンデンサ 7 からグランド層 3 迄のインダクタンスは、ランド 2 2 とビアホール 3 1 によるインダクタンスである。ランド 2 2 も、幅広の銅箔パターンであり、そのインダクタンス値はほとんど無視できる。また、グランド層 3 が、信号層 2 のほぼ真下に設けられているので、ビアホール 3 1 の長さは極めて短く、そのインダクタンスは非常に小さい。

このように、この実施例によれば、ICパッケージ1の電源端子12から2端子コンデンサ7迄のインダクタンスや2端子コンデンサ7からグランド層3迄のインダクタンスが非常に小さい。このため、ICパッケージ1に供給される電流によって生じる逆起電力は、上記した従来の技術で生じる逆起電力に比べて、無視できる程度に小さく、ICパッケージ1に対して安定した電源供給がなされる。

#### 【実施例2】

[0042]

次に、この発明の第2実施例について説明する。

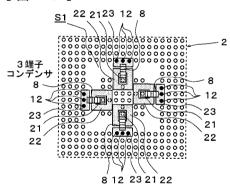

図10は、この発明の第2実施例に係る多層回路基板の要部であるコンデンサの実装スペースを示す平面図であり、図11は、2端子コンデンサを実装スペースに実装した状態を示す平面図であり、図12は、第2実施例の多層回路基板の概略断面図である。

この実施例は、実装スペースの形成位置が、上記第1実施例と異なる。

#### [ 0 0 4 3 ]

この実施例の実装スペースS2は、矩形状に画成された絶縁層20の表面で成り、図10に示すように、信号層2の周縁部であって、ICパッケージ1の電源端子の近傍に位置するように設けられている。具体的には、この実施例では、ICパッケージ1の信号層2への実装時には、図10の黒丸で示すように、ICパッケージ1の電源端子12が、信号層2の各周縁部に平行に位置する。このため、実装スペースS2の大きさをを、これらの電源端子12が各実装スペースS2の両側に位置するように設定した。そして、図11で示すように、電源端子12に対応する位置に、幅広のランド21を設け、実装スペースS2の奥側に幅広のランド22を設けた。

そして、2端子コンデンサ7の入出力端子71をランド21に接続すると共に、アース端子72をランド22に接続した。

[0044]

一方、ICパッケージ1の裏面10には、図12に示すように、凹部11 を、上記2端子コンデンサ7が実装された実装スペースS2に対応させて設けている。

[0045]

これにより、ICパッケージ1を信号層2に実装すると、各2端子コンデンサ7がICパッケージ1の凹部11 に収納され、ICパッケージ1の電源端子12が、ランド21に接続する。この結果、2端子コンデンサ7の入出力端子71が、電源端子12に接続すると共に電源層4にも接続した状態になる。また、2端子コンデンサ7のアース端子72は、ランド22を通じてグランド層3に接続した状態になる。

[0046]

かかる構成により、2端子コンデンサ7が実装スペースS2に確実に実装されているか否かを、外部から容易に確認することができる。すなわち、上記第1実施例では、2端子コンデンサ7がICパッケージ1の凹部11内に完全に隠れてしまうので、ICパッケージ1を信号層2に実装した後も、2端子コンデンサ7が外れることなく実装スペースS1に実装されているかを確認することができない。しかし、この実施例では、凹部11 内を図12の矢印方向から覗き込むことができ、2端子コンデンサ7の実装状態を一目で確認することができる。

その他の構成、作用及び効果は、上記第1実施例と同様であるので、その記載は省略する。

## 【実施例3】

[0047]

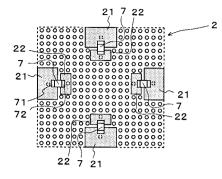

次に、この発明の第3実施例について説明する。

図13は、この発明の第3実施例の要部である3端子コンデンサの実装状態を示す平面

10

20

30

40

10

20

30

40

50

図であり、図14は、第3実施例の多層回路基板の概略断面図である。

この実施例は、図13及び図14に示すように、上記第1実施例で用いた2端子コンデンサ7の代わりに、3端子コンデンサ8を用いた。

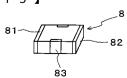

# [0048]

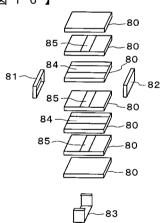

図15は、3端子コンデンサの外観図であり、図16は、3端子コンデンサの分解斜視図であり、図17は、3端子コンデンサの等価回路図であり、図18は、3端子コンデンサのランド実装状態を示す平面図である。

図15に示すように、3端子コンデンサ8は、電源用電極としての入力端子81及び出力端子82を両端部に有すると共にグランド用電極としてのアース端子83を中央部に有したチップ型の積層貫通コンデンサである。

この3端子コンデンサ8では、図16に示すように、入力端子81,出力端子82を接続する貫通電極となるパターン84を、誘電体シート80に印刷し、これらの誘電体シート80を積層した。そして、アース端子83を接続するアース電極となるパターン85を誘電体シート80に印刷し、この誘電体シート80をパターン84が印刷された誘電体シート80と交互に積層した。これにより、図17に示すように、電源等の電流ェが入力端子81からパターン84を通じて出力端子82に至るようになっている。また、アース端子83に接続されたパターン85の接地機能により、アース端子83側の残留インダクタンスを低減している。すなわち、3端子コンデンサ8は、残留インダクタンスを2端子コンデンサ7に比べて極めて小さくした構造になっている。

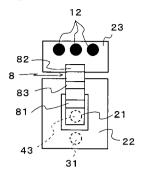

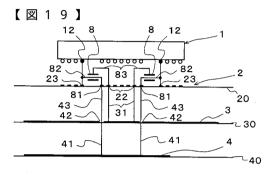

#### [0049]

このような3端子コンデンサ8を実装する信号層2では、図13,図14に示すように、ランド21を、ICパッケージ1の電源端子12と対応する箇所(黒丸で示す箇所)である実装スペースS1の外側には形成せず、実装スペースS1の内側に形成した。そして、ランド22を、このランド21を囲むように形成した。さらに、銅箔パターンのランド23をICパッケージ1の電源端子12に対応する箇所に形成した。

そして、図18に示すように、3端子コンデンサ8の入力端子81,出力端子82及びアース端子83を、かかるランド21,ランド23及びランド22に固着した。このとき、図14に示すように、ランド21がビアホール41~43を通じて電源層4に接続し、ランド22がビアホール31を通じてグランド層3に接続しているので、3端子コンデンサ8の入力端子81がランド21及びビアホール41~43を通じて電源層4接続し、アース端子83がランド22及びビアホール31を通じてグランド層3に接続することとなる。したがって、各3端子コンデンサ8を凹部11内に収納した状態で、ICパッケージ1を信号層2に実装すると、ICパッケージ1の電源端子12が電源層4に接続された状態になる。

# [0050]

図19は、各部材の電気的接続状態を示す概略図である。

この図19及び図18に示すように、電源層4は、ビアホール41~43及びランド21を通じて3端子コンデンサ8の入力端子81に接続され、この3端子コンデンサ8の出力端子82は、ランド23を通じてICパッケージ1の電源端子12に接続されている。そして、3端子コンデンサ8のアース端子83は、ランド22及びビアホール31を通じてグランド層3に接続されている。

#### [0051]

かかる構成により、外部電源が電源層4に入力されると、電源電圧に対応した電荷が、電源層4に接続された入力端子81を通じて3端子コンデンサ8に充電される。そして、3端子コンデンサ8に充電された電荷が、出力端子82に接続された電源端子12を通じてICパッケージ1に電源電流として供給される。

また、ICパッケージ 1 の電源端子 1 2 に生じたノイズ電流は、 3 端子コンデンサ 8 のアース端子 8 3 及びランド 2 2 を通じてグランド層 3 に排出される。

#### [ 0 0 5 2 ]

この実施例では、3端子コンデンサ8を適用したが、ICパッケージ1の電源端子12

から3端子コンデンサ8迄のインダクタンス値や、3端子コンデンサ8からグランド層3迄のインダクタンス値は、それぞれ、上記第1実施例における電源端子12から2端子コンデンサ7迄のインダクタンス値や、2端子コンデンサ7からグランド層3迄のインダクタンス値とほぼ同じである。しかしながら、上記したように、この3端子コンデンサ8の残留インダクタンスに比べて極めて小さい。このため、ICパッケージ1に供給される電流によって生じる逆起電力は、上記第1実施例で生じる逆起電力に比べて極めて小さくなり、ICパッケージ1に対して、より一層安定した電源供給がなされ、動作特性の更なる向上を図ることができる。

その他の構成、作用及び効果は、上記第1実施例と同様であるので、その記載は省略する。

【実施例4】

#### [0053]

次に、この発明の第4実施例について説明する。

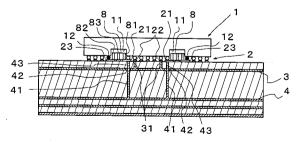

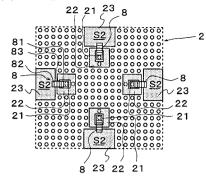

図 2 0 は、この発明の第 4 実施例の要部である 3 端子コンデンサの実装状態を示す平面図であり、図 2 1 は、第 4 実施例の多層回路基板の概略断面図である。

この実施例は、図20及び図21に示すように、上記第2実施例で用いた2端子コンデンサ7の代わりに、3端子コンデンサ8を用いた。

#### [0054]

すなわち、図 2 0 に示すように、幅広のランド 2 3 を、各実装スペース S 2 の電源端子 1 2 対応位置に設け、ランド 2 1 を、実装スペース S 2 の奥側に設けた。さらに、ランド 2 2 を、ランド 2 1 を囲むように形成した。

そして、3端子コンデンサ8の入力端子81,出力端子82及びアース端子83を、かかるランド21,ランド23及びランド22に固着した。

これにより、図21に示すように、ランド21がビアホール41~43を通じて電源層4に接続し、ランド22がビアホール31を通じてグランド層3に接続しているので、3端子コンデンサ8の入力端子81がランド21及びビアホール41~43を通じて電源層4に接続し、アース端子83がランド22及びビアホール31を通じてグランド層3に接続することとなる。したがって、各3端子コンデンサ8を凹部11 内に収納した状態で、ICパッケージ1を信号層2に実装すると、ICパッケージ1の電源端子12が電源層4に接続された状態になる。

# [ 0 0 5 5 ]

かかる構成により、残留インダクタンスの極めて小さな3端子コンデンサ8を用いて、ICパッケージ1の動作特性をより向上させることができるだけでなく、凹部11 内を覗き込むことで、3端子コンデンサ8の実装状態を一目で確認することができる。

その他の構成、作用及び効果は、上記第2及び第3実施例と同様であるので、その記載 は省略する。

#### 【実施例5】

#### [0056]

次に、この発明の第5実施例について説明する。

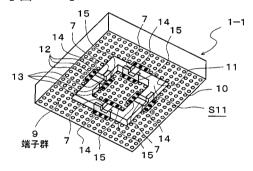

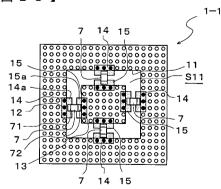

図 2 2 は、この発明の第 5 実施例に係るICパッケージを示す斜視図であり、図 2 3 は、コンデンサの実装状態を示す平面図である。

#### [0057]

図22に示すように、この実施例のICパッケージ1-1は、コンピュータ等に用いられるCPUやチップコントローラ等の半導体集積回路であり、電源端子12とグランド端子13とを含むBGAタイプの端子群9を裏面10に有している。なお、理解を容易にするため、図22及び図23では、2端子コンデンサ7に接続されている電源端子12及びグランド端子13を黒塗りで示した。

#### [0058]

また、このような裏面10には、ロ字状の凹部11が凹設され、2端子コンデンサ7を 実装するための実装スペースS11がこの凹部11内に形成されている。 10

30

20

50

実装スペース S 1 1 を有する凹部 1 1 は、端子群 9 のほぼ中央部であって、電源端子 1 2 とグランド端子 1 3 の近傍に位置する。具体的には、黒丸で示すように、複数の電源端子 1 2 の組を、凹部 1 1 の外周に沿ってそれぞれ配置し、複数のグランド端子 1 3 の組を、電源端子 1 2 の各組に対向するように、凹部 1 1 の内周に沿ってそれぞれ配置した。

そして、各組の複数の電源端子12を幅広の銅箔パターン14で電気的に接続すると共に、各組の複数のグランド端子13を幅広の銅箔パターン15で電気的に接続した。

[0059]

銅箔パターン 1 4 , 1 5 は、図 2 3 にも示すように、凹部 1 1 の内部迄延出して、互いに対向し、かかる対向部が 2 端子コンデンサ 7 用のランド部 1 4 a , 1 5 a を形成している。

2端子コンデンサ7は、かかるランド部14a,15aに接続されている。

具体的には、その入出力端子71をランド部14aに接続し、アース端子72をランド部15aに接続した状態で、複数の2端子コンデンサ7が凹部11内の実装スペースS11に等間隔で実装されている。

これにより、 2 端子コンデンサ 7 の入出力端子 7 1 が銅箔パターン 1 4 を通じて電源端子 1 2 に接続し、アース端子 7 2 が銅箔パターン 1 5 を通じてグランド端子 1 3 に接続した状態になっている。

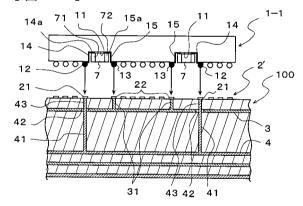

[0060]

次に、この実施例のICパッケージが示す作用及び効果について説明する。

図 2 4 は、この実施例のICパッケージの実装例を示す概略断面図である。

このICパッケージ1 - 1 は、図24に示す多層回路基板100に実装することができる。

多層回路基板100は、上記第1実施例の多層回路基板とほぼ同じ多層構造を成す。 すなわち、多層回路基板100は、ICパッケージ1-1の端子群9の配列に対応した ランド群で成る信号層2 を表面に有している。そして、ランド21がビアホール41, 孔42及びビアホール43を通じて電源層4に接続しており、ランド22がビアホール3 1を通じてグランド層3に接続している。

[0061]

I C パッケージ1 - 1 をかかる多層回路基板100に実装すると、I C パッケージ1 - 1 の電源端子12と多層回路基板100のランド21とが接続し、また、グランド端子13 とランド22とが接続する。

かかる状態で、電源を外部から電源層4に入力すると、電源が、ビアホール41~43を通じてランド21に印加され、ランド21に接続された電源端子12から銅箔パターン14のランド部14aを通じて2端子コンデンサ7の入出力端子71に至り、2端子コンデンサ7に充電された電荷は、入出力端子71から銅箔パターン14の電源端子12を通じてICパッケージ1内に電流として供給される。すなわち、この実施例の2端子コンデンサ7も、上記第1実施例の2端子コンデンサと同様に、電源電圧を安定させるバイパスコンデンサとして機能する。

また、ICパッケージ1-1の電源端子12に生じたノイズ電流は、銅箔パターン14のランド部14aを通じて入出力端子71から2端子コンデンサ7に入力し、アース端子72から銅箔パターン15のランド部15aを通じてグランド端子13に至る。そして、かかるノイズ電流は、グランド端子13が接続された多層回路基板100のランド22を通じてグランド層3に排出される。すなわち、この2端子コンデンサ7も、発生したノイズを除去するデカップリングコンデンサとして機能する。

[0062]

ところで、この実施例のICパッケージ1・1においても、電源端子12から2端子コンデンサ7迄のインダクタンスは、銅箔パターン14のインダクタンスであり、ほとんど無視できる大きさである。また、2端子コンデンサ7からグランド層3迄のインダクタンスは、銅箔パターン15とランド22とビアホール31のインダクタンスであり、極めて小さい。

10

20

30

40

#### 【実施例6】

# [0063]

次に、この発明の第6実施例について説明する。

図 2 5 は、この発明の第 6 実施例の要部であるコンデンサの実装状態を示す平面図であり、図 2 6 は、この実施例のICパッケージの実装例を示す概略断面図である。なお、これらの図において、理解を容易にするため、電源層 4 に接続させる端子を黒塗りで示した

この実施例は、上記第5実施例で用いた2端子コンデンサ7の代わりに、3端子コンデンサ8を用いた。

#### [0064]

すなわち、この実施例のICパッケージ1-3においては、図25に示すように、銅箔パターン14を、凹部11の内側に形成し、この銅箔パターン14にのみ電気的に接続した端子12 を銅箔パターン14の表面に形成した。そして、銅箔パターン15を、この銅箔パターン14を囲むように形成し、複数のグランド端子13を、この銅箔パターン15で電気的に接続した。さらに、銅箔パターン16を、銅箔パターン15と対向するように、凹部11の外側に形成し、ICパッケージ1-3内部の電源パターン12 と電気的に接続させた。

そして、3端子コンデンサ8の入力端子81,出力端子82及びアース端子83を、これら銅箔パターン14,銅箔パターン16及び銅箔パターン15に固着した。

これにより、 3 端子コンデンサ 8 の入力端子 8 1 が端子 1 2 に接続した状態になり、 出力端子 8 2 が I C パッケージ 1 - 3 内部の電源パターン 1 2 に接続した状態になる

# [0065]

かかる構成により、図26に示すように、ICパッケージ1-3を多層回路基板100に実装すると、端子12 がランド21に接触し、端子12 がビアホール41~43を通じて電源層4に接続した状態になる。また、グランド端子13がランド22に接触し、グランド端子13がビアホール31を通じてグランド層3に接続した状態になる。

かかる状態で、外部電源が、電源層 4 に入力されると、電源層 4 に接続された端子 1 2 から入力端子 8 1 を通じて 3 端子コンデンサ 8 に充電される。そして、 3 端子コンデンサ 8 に充電された電荷が、出力端子 8 2 から銅箔パターン 1 6 を通じて、ICパッケージ1 - 3 内部の電源パターン 1 2 に電流として供給される。

また、電源パターン 1 2 に生じたノイズ電流は、 3 端子コンデンサ 8 のアース端子 8 3 を通じてグランド端子 1 3 に至り、グランド端子 1 3 から多層回路基板 1 0 0 のランド 2 2 及びビアホール 3 1 を通じてグランド層 3 に排出される。

その他の構成、作用及び効果は、上記第3及び第5実施例と同様であるので、その記載は省略する。

#### [0066]

なお、この発明は、上記実施例に限定されるものではなく、発明の要旨の範囲内において種々の変形や変更が可能である。

例えば、上記第実施例では、ロ字状の実装スペースS1,S11や矩形状の実装スペースS2,S12を多層回路基板の信号層2やICパッケージの裏面10に設けた例を示したが、実装スペースの形状,大きさ及び個数は、上記実施例に限定されるものではないことは勿論である。

また、上記実施例では、ICパッケージの裏面10に凹部11,11 を設けた例について説明したが、これらの凹部11,11 を有しないICパッケージを有した多層回路基板やICパッケージ自体をこの発明の範囲から除外する意ではない。

#### 【図面の簡単な説明】

#### [0067]

【図1】この発明の第1実施例に係る多層回路基板の分解斜視図である。

【図2】コンデンサの実装スペースを示す平面図である。

10

20

30

40

- 【図3】第1実施例に適用する2端子コンデンサの外観図である。

- 【図4】2端子コンデンサの等価回路図である。

- 【図5】2端子コンデンサのランド実装状態を示す平面図である。

- 【 図 6 】 2 端 子 コン デ ン サ を 実 装 ス ペ ー ス に 実 装 し た 状 態 を 示 す 平 面 図 で あ る 。

- 【図7】多層回路基板の概略断面図である。

- 【図8】各部材の電気的接続状態を示す概略図である。

- 【 図 9 】 2 端 子 コ ン デ ン サ の 機 能 を 説 明 す る た め の 概 略 部 分 拡 大 断 面 図 で あ る 。

- 【図 1 0 】この発明の第 2 実施例に係る多層回路基板の要部であるコンデンサの実装スペースを示す平面図である。

- 【 図 1 1 】 2 端 子 コン デン サ を 実 装 ス ペ ー ス に 実 装 し た 状 態 を 示 す 平 面 図 で あ る 。

- 【図12】第2実施例の多層回路基板の概略断面図である。

- 【図13】この発明の第3実施例の要部である3端子コンデンサの実装状態を示す平面図である。

- 【図14】第3実施例の多層回路基板の概略断面図である。

- 【図15】3端子コンデンサの外観図である。

- 【 図 1 6 】 3 端 子 コン デン サ の 分 解 斜 視 図 で あ る。

- 【図17】3端子コンデンサの等価回路図である。

- 【 図 1 8 】 3 端 子 コン デ ン サ の ラン ド 実 装 状 態 を 示 す 平 面 図 で あ る 。

- 【図19】各部材の電気的接続状態を示す概略図である。

- 【 図 2 0 】この発明の第 4 実施例の要部である 3 端子コンデンサの実装状態を示す平面図である。

- 【図21】第4実施例の多層回路基板の概略断面図である。

- 【 図 2 2 】 この発明の第 5 実施例に係るICパッケージを示す斜視図である。

- 【図23】コンデンサの実装状態を示す平面図である。

- 【図24】第5実施例のICパッケージの実装例を示す概略断面図である。

- 【図25】この発明の第6実施例の要部であるコンデンサの実装状態を示す平面図である

- 【図26】第6実施例のICパッケージの実装例を示す概略断面図である。

# 【符号の説明】

# [0068]

1 , 1 - 1 ~ 1 - 4 … I C パッケージ、 2 , 2 , 6 …信号層、 3 , 5 …グランド層、 4 …電源層、 7 … 2 端子コンデンサ、 8 … 3 端子コンデンサ、 9 …端子群、 10 …裏面、 11 , 11 …凹部、 12 …電源端子、 12 …端子、 12 …電源パターン、 13 …グランド端子、 14 ~ 16 …銅箔パターン、 14 a , 15 a … ランド部、 21 ~ 23 …ランド、 31 , 41 , 43 …ビアホール、 42 …孔、 71 …入出力端子、 72 …アース端子、 81 …入力端子、 82 …出力端子、 83 …アース端子、 100 …多層回路基板、 S1 , S2 , S11 , S12 …実装スペース。

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図10】

【図11】

【図12】

【図13】

【図16】

【図14】

【図17】

【図15】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

# 【図26】