## ITALIAN PATENT OFFICE

Document No.

102012902028448A1

**Publication Date**

20130902

**Applicant**

STMICROELECTRONICS S.R.L.

Title

STADIO DI PILOTAGGIO AD ELEVATA EFFICIENZA PER DISPOSITIVI DI MEMORIA NON VOLATILE A CAMBIAMENTO DI FASE

## DESCRIZIONE

del brevetto per invenzione industriale dal titolo:

"STADIO DI PILOTAGGIO AD ELEVATA EFFICIENZA PER DISPOSITIVI

DI MEMORIA NON VOLATILE A CAMBIAMENTO DI FASE"

di STMICROELECTRONICS S.R.L.

di nazionalità italiana

con sede: VIA C. OLIVETTI, 2

AGRATE BRIANZA (MB)

Inventori: CONTE Antonino, GIAQUINTA Maria, CHIARAMONTE

Loredana

\* \* \*

La presente invenzione è relativa ad uno stadio di pilotaggio ad elevata efficienza per dispositivi di memoria non volatile a cambiamento di fase, in particolare per la fornitura di correnti di pilotaggio durante operazioni di programmazione delle celle di memoria.

In modo noto, le memorie non volatili a cambiamento di fase (cosiddette ePCM, dall'inglese "embedded Phase Change Memory") rappresentano una nuova generazione di memorie integrate, in cui, per immagazzinare informazioni, vengono sfruttate le caratteristiche di materiali che hanno la proprietà di commutare fra fasi aventi caratteristiche elettriche diverse. Ad esempio, tali materiali possono commutare fra una fase amorfa, disordinata, ed una fase cristallina o policristallina, ordinata, e le due fasi sono

associate a resistività di valore notevolmente differente, e conseguentemente ad un differente valore di un dato memorizzato. Ad esempio, gli elementi del VI gruppo della tavola periodica, quali Tellurio (Te), Selenio (Se), o Antimonio (Sb), chiamati calcogenuri o materiali calcogenici, sono utilizzabili vantaggiosamente per la realizzazione di celle di memoria a cambiamento di fase; in particolare, una lega composta da Germanio (Ge), Antimonio (Sb) e Tellurio (Te), nota come GST (avente composizione chimica Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>) trova attualmente largo utilizzo in tali celle di memoria.

cambiamenti di fase vengono ottenuti aumentando localmente la temperatura delle celle di materiale calcogenico, attraverso elettrodi resistivi (generalmente noti come riscaldatori) disposti a contatto con rispettive regioni di materiale calcogenico. Dispositivi di selezione esempio transistori MOSFET), sono collegati riscaldatori, ed abilitano il passaggio di una corrente elettrica di programmazione attraverso un rispettivo riscaldatore; tale corrente elettrica, per effetto Joule, genera le temperature necessarie per il cambiamento di fase. In particolare, quando il materiale calcogenico si trova nello stato amorfo, ad alta resistività (cosiddetto "stato di RESET"), è necessario applicare un impulso (o un impulsi) di corrente/tensione di durata numero di ampiezza tali da consentire al materiale calcogenico di

raffreddarsi lentamente. Sottoposto a questo trattamento, il materiale calcogenico cambia il suo stato e commuta dallo stato di alta resistività ad uno stato di bassa resistività (cosiddetto "stato di SET"). Viceversa, quando il materiale calcogenico si trova nello stato di SET, è necessario applicare un impulso di corrente/tensione di durata appropriata ed elevata ampiezza in modo da far sì che il materiale calcogenico ritorni nello stato amorfo ad elevata resistività.

In lettura, lo stato del materiale calcogenico viene rilevato applicando una tensione sufficientemente bassa da non causarne un sensibile riscaldamento, e quindi leggendo il valore della corrente che fluisce nella cella di memoria. Dato che la corrente è proporzionale alla conduttività del materiale calcogenico, è possibile determinare in quale stato si trovi il materiale, e quindi risalire al dato memorizzato nella cella di memoria.

In generale, le memorie PCM offrono importanti vantaggi, tra cui elevate scalabilità e velocità di lettura abbinate ad un ridotto consumo di corrente ed un elevato rendimento.

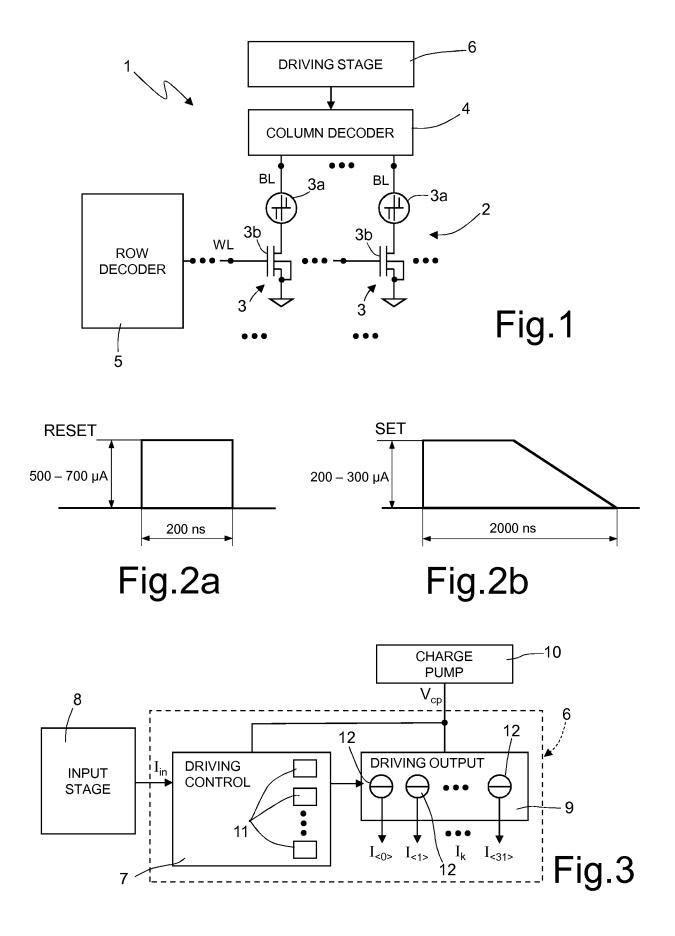

In modo noto, e come mostrato schematicamente in figura 1 (limitatamente alle sole parti richieste per la comprensione della presente invenzione), un dispositivo di memoria non volatile PCM, indicato con 1, comprende in

generale una matrice di memoria 2 composta da una pluralità di celle di memoria 3, organizzate in righe (linee di parola, o "WL - Word Line") e colonne (linee di bit, o "BL - Bit Line").

Ciascuna cella di memoria 3 è realizzata da un elemento di memorizzazione 3a a cambiamento di fase e da un elemento selettore 3b, collegati in serie tra una rispettiva bit line BL ed un terminale a potenziale di riferimento (ad esempio a massa, GND). In particolare, una word line WL è definita dall'insieme di tutti i terminali di controllo dei transistori selettori allineati lungo una stessa riga.

L'elemento di memorizzazione 3a include un materiale a cambiamento di fase (ad esempio un calcogenuro, quale il GST), ed è quindi in grado di immagazzinare dati sotto forma di livelli di resistenza associati alle differenti assunte dal materiale a cambiamento di L'elemento selettore 3b, come nella forma di realizzazione illustrata, può essere un transistore NMOS avente terminale di porta (gate) collegato alla word line WL, terminale di pozzo (drain) collegato all'elemento di memorizzazione 3a, e terminale di sorgente (source) collegato al potenziale di riferimento (in particolare massa, GND). L'elemento selettore 3b è controllato in modo da consentire, quando selezionato, il passaggio di una corrente di pilotaggio di

lettura/programmazione attraverso l'elemento a cambiamento di fase 3a, durante rispettive operazioni di lettura/programmazione.

Un decodificatore di colonna 4 ed un decodificatore di riga 5 permettono di selezionare, sulla base di segnali di indirizzo ricevuti in ingresso e schemi di decodifica più o meno complessi, le celle di memoria 3, ed in particolare le relative word line WL e bit line BL, di volta in volta indirizzate, consentendone la polarizzazione a valori di tensione e corrente opportuni da parte di relativi stadi di pilotaggio; in particolare, in figura 1 viene mostrato ed indicato con 6 lo stadio di pilotaggio atto a fornire le correnti di pilotaggio per le bit line BL della matrice di memoria 2 durante le operazioni di programmazione degli stati di SET o RESET nelle celle di memoria 3.

particolare, è noto che tali operazioni di programmazione, sia nel caso in cui si richieda la programmazione dello stato di SET, sia nel caso in cui venga richiesta la programmazione dello stato di RESET del materiale calcogenuro delle celle di memoria 3, necessitano la fornitura agli elementi di memorizzazione 3a di impulsi corrente di valore elevato, per l'attivazione dei di meccanismi di cambiamento di stato. Inoltre, un accurato controllo dei parametri degli impulsi di corrente programmazione è critico per assicurare efficienti

ripetibili transizioni tra gli stati di SET e RESET, e tale controllo deve essere assicurato in un ampio intervallo di valori di corrente, in modo da far fronte alle varie condizioni operative del dispositivo di memoria. Ad esempio, una bassa distorsione della forma d'onda degli impulsi di corrente può essere richiesta in un ampio intervallo di correnti che va da 100  $\mu A$  a 1000  $\mu A$  (con una tensione massima generata sulle bit line BL in uscita dal decodificatore di colonna 4 che può raggiungere un valore pari a circa 3 V).

Nuovamente a titolo esemplificativo, le figure 2a e 2b mostrano possibili andamenti degli impulsi di RESET e, rispettivamente, degli impulsi di SET.

evidente che il soddisfacimento dei suddetti stringenti requisiti nel controllo dei parametri delle forme d'onda degli impulsi di corrente di programmazione è un importante aspetto che deve essere indirizzato nel dispositivi di е progetto dei memoria che ne può rappresentare una delle maggiori criticità.

In figura 3 è mostrato schematicamente uno stadio di pilotaggio 6, di tipo noto, per la fornitura, durante le operazioni di programmazione, di correnti di pilotaggio di uscita, qui indicate con  $I_{k}$  (dove k è un indice di valore intero, ad esempio compreso tra 0 e 31, nel caso in cui lo stadio di polarizzazione 6 sia collegata ad un numero di

bit line BL pari a 32), destinate al pilotaggio delle celle di memoria 3; tali correnti di pilotaggio di uscita  $I_k$  vengono fornite al decodificatore di colonna 4 per essere alimentate, secondo gli schemi di decodifica di volta in volta implementati, alle bit line BL della matrice di memoria 2.

In dettaglio, lo stadio di pilotaggio 6 comprende un'unità di controllo pilotaggio 7, avente un ingresso a bassa impedenza ricevente una corrente di ingresso Iin di valore ridotto (ovvero sensibilmente minore del valore richiesto per le correnti di pilotaggio di uscita Ik, esempio pari a 200 µA se il valore richiesto per corrente di pilotaggio di uscita  $I_k$  è di 800  $\mu A$ ) generata da uno stadio generatore di corrente di ingresso 8 in funzione della specifica operazione di memoria richiesta (ad esempio avente valore differente per le operazioni di programmazione di SET e di RESET). Tale stadio generatore di corrente di ingresso 8 può essere realizzato in una larga variabilità di modi, più che altro dipendente dal tipo di applicazione; ad esempio, può essere utilizzato un convertitore di tipo digitale analogico (DAC), per il quale, a una determinata configurazione di un certo numero di bit in ingresso, corrisponde una determinata corrente in uscita.

Lo stadio di pilotaggio 6 comprende inoltre un'unità

di uscita di pilotaggio 9, collegata all'unità di controllo pilotaggio 7 ed atta a generare e distribuire verso le bit line BL le correnti di pilotaggio di uscita  $I_k$ .

L'unità di controllo pilotaggio 7 e l'unità di uscita di pilotaggio 9 sono inoltre alimentate da uno stadio a pompa di carica 10, che fornisce opportune grandezze elettriche di alimentazione, in particolare una tensione survoltata  $V_{\rm cp}$  nel range dell'alta tensione (HV - High Voltage, ad esempio nell'intervallo compreso tra 4 V e 5 V), di valore maggiore rispetto alle basse tensioni logiche utilizzate nel dispositivo di memoria 1 (aventi ad esempio valore compreso nell'intervallo tra 1,08 V e 1,32 V).

L'unità di controllo pilotaggio 7 comprende una pluralità di sotto-unità di controllo 11, e l'unità di uscita di pilotaggio 9 comprende una rispettiva pluralità di sotto-unità di pilotaggio 12, ciascuna delle quali, opportunamente alimentata dallo stadio a pompa di carica 10, è atta a fornire una rispettiva corrente di pilotaggio di uscita  $I_k$ , avente un valore amplificato di un fattore  $\beta$  rispetto alla corrente di ingresso  $I_{in}$ , secondo la relazione:  $I_k = I_{in} \cdot \beta$ . Le tensioni fornite in uscita dalle sotto-unità di pilotaggio 12 sono ad esempio nell'intorno di 3 V.

In particolare, ciascuna sotto-unità di controllo 11 pilota in maniera opportuna un rispettivo gruppo di sotto-

unità di pilotaggio 12, fornendo opportuni segnali di comando per abilitare la fornitura in uscita delle rispettive correnti di pilotaggio di uscita  $I_k$ . Ad esempio, ciascuna sotto-unità di controllo 11 può pilotare quattro rispettive sotto-unità di pilotaggio 12 (così che possono ad esempio essere presenti nello stadio di polarizzazione otto sotto-unità di controllo 11 per fornire trentadue correnti di pilotaggio di uscita  $I_k$  tramite un numero corrispondente di sotto-unità di pilotaggio 12).

Come illustrato in figura 4 (che si riferisce, per semplicità illustrativa, ad una singola sotto-unità di controllo 11 ed al relativo gruppo di sotto-unità pilotaggio 12, nell'esempio in numero pari a quattro), ciascuna sotto-unità di controllo 11 forma, con il relativo gruppo di sotto-unità di pilotaggio 12, uno specchio di corrente in configurazione cascode, atto a specchiare sulle varie uscite la corrente di ingresso Iin con fattore di amplificazione β. La sotto-unità di controllo 11 costituisce il ramo di ingresso dello specchio di corrente, mentre le sotto-unità di pilotaggio 12 costituiscono rispettivi rami di uscita dello stesso specchio, tra loro collegati in parallelo.

In maggiore dettaglio, la sotto-unità di controllo 11 comprende un transistore cascode di controllo MCc ed un transistore di specchio di ingresso MPc, entrambi di tipo

PMOS e collegati in serie tra un primo ingresso In<sub>1</sub> dello stadio di pilotaggio 6, ricevente la corrente di ingresso I<sub>in</sub> ed un secondo ingresso In<sub>2</sub> dello stesso stadio di pilotaggio 6, collegato all'uscita dello stadio a pompa di carica 10 e ricevente la tensione survoltata V<sub>cp</sub>. terminale di controllo del transistore cascode di controllo MCc è collegato ad un terzo ingresso In3, ricevente una tensione di polarizzazione cascode V<sub>cascp</sub>, di opportuno, mentre il terminale di controllo del transistore di specchio di ingresso MPc è collegato al primo ingresso al rispettivo terminale di conduzione transistore cascode di controllo MCc, in modo da realizzare la configurazione a diodo per l'operazione di specchiaggio di corrente.

Ciascuna sotto-unità di pilotaggio 12 (per comodità si descrive una n-esima sotto-unità di pilotaggio 12, ma considerazioni del tutto analoghe si applicano alle altre sotto-unità del relativo gruppo, indicate con n+1, n+2 e n+3, dove n è un indice intero rappresentativo del gruppo stesso) comprende un rispettivo transistore cascode di pilotaggio MCn ed un transistore di specchio di uscita MPn, entrambi di tipo PMOS e collegati in serie tra il secondo ingresso  $In_2$  ed una rispettiva uscita dello stadio di pilotaggio 6 fornente la rispettiva corrente di pilotaggio di uscita, qui indicata con  $I_{<n>}$ ; i terminali di controllo

del transistore cascode di pilotaggio MCn e del transistore di specchio di uscita MPn sono collegati rispettivamente ai terminali di controllo del transistore cascode di controllo MCc e del transistore di specchio di ingresso MPc.

La configurazione circuitale descritta consente di specchiare la corrente di ingresso  $I_{\rm in}$  con il desiderato fattore di amplificazione  $\beta$ , dato dai differenti rapporti di dimensionamento (larghezza/lunghezza, W/L) dei transistori nei rami di ingresso e uscita; in particolare, la configurazione cascode consente vantaggiosamente di ottenere una caduta di tensione drain-source Vds sui transistori di specchio di uscita MPn sostanzialmente costante, in modo da assicurare una buona ripetibilità delle prestazioni elettriche.

Tuttavia, la configurazione descritta presenta anche alcune limitazioni che non consentono di sfruttarne appieno i vantaggi.

In particolare, per motivi di velocità e di consumo, ciascuna sotto-unità di controllo 11 può pilotare un numero limitato (pari a tre o, come nel caso illustrato, quattro) di sotto-unità di pilotaggio 12 collegate in parallelo, così che è richiesta una notevole occupazione di area in realizzazione integrata per la sola unità di controllo pilotaggio 7. Inoltre, è richiesto che tutti i transistori nel circuito siano del tipo high-voltage per sopportare gli

alti valori di tensione presenti, il che, abbinato alle elevate richieste di corrente in uscita. comporta l'utilizzo di transistori di grandi dimensioni (con elevati relativi ossidi), con costi elevati spessori dei nuovamente una considerevole occupazione di spazio. Dato che l'intero stadio di pilotaggio 6 è alimentato dallo stadio a pompa di carica 10, quest'ultimo deve essere dimensionato in modo da soddisfarne gli elevati requisiti di corrente, ed in particolare l'inefficienza dello stesso stadio di pilotaggio 6 si riflette in un elevato consumo di corrente richiesta dallo stadio a pompa di carica 10.

Scopo della presente invenzione è pertanto quello di risolvere, almeno in parte, i problemi precedentemente evidenziati, in particolare relativamente agli elevati consumi di corrente ed occupazione d'area delle soluzioni note.

Secondo la presente invenzione viene fornito uno stadio di pilotaggio per un dispositivo di memoria non volatile a cambiamento di fase, come definito nelle rivendicazioni allegate.

Per una migliore comprensione della presente invenzione, ne vengono ora descritte forme di realizzazione preferite, a puro titolo di esempio non limitativo, con riferimento ai disegni allegati, nei quali:

- la figura 1 mostra uno schema a blocchi generale di

un dispositivo di memoria non volatile PCM, di tipo noto;

- le figure 2a e 2b mostrano impulsi di corrente di programmazione in differenti condizioni operative del dispositivo di memoria di figura 1;

- la figura 3 mostra uno schema a blocchi di massima di uno stadio di pilotaggio, di tipo noto, del dispositivo di figura 1;

- la figura 4 mostra in maggiore dettaglio l'implementazione circuitale di una porzione dello stadio di pilotaggio di figura 3;

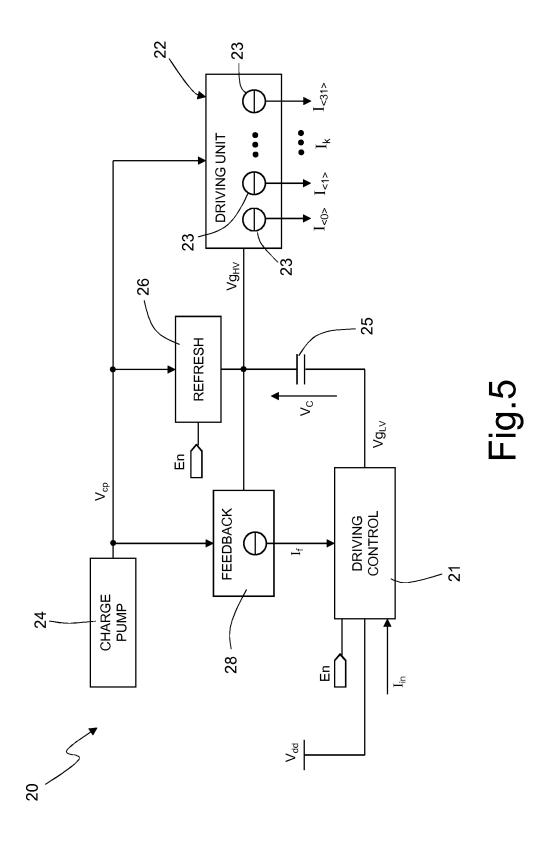

- la figura 5 mostra uno schema a blocchi di massima di uno stadio di pilotaggio per un dispositivo di memoria non volatile a cambiamento di fase, secondo una forma di realizzazione della presente invenzione;

- la figura 6 mostra in maggiore dettaglio una possibile realizzazione circuitale di parti dello stadio di pilotaggio di figura 5;

- la figura 7 mostra uno schema circuitale di un'unità di controllo pilotaggio dello stadio di pilotaggio delle figure 5 e 6; e

- la figura 8 mostra diagrammi temporali di segnali elettrici nello stadio di pilotaggio di figura 5.

Come mostrato in figura 5, secondo una forma di realizzazione dell'invenzione, uno stadio di pilotaggio per un dispositivo di memoria non volatile a cambiamento di

fase (ad esempio del tipo descritto con riferimento alla figura 1, per questo qui non descritto nuovamente), 20, comprende: un'unità di indicato con controllo pilotaggio, qui indicata con 21, che riceve, su un primo ingresso a bassa impedenza, la corrente di ingresso Iin, con valore opportuno che è funzione della specifica operazione di memoria richiesta; ed un'unità di uscita di pilotaggio, qui indicata con 22, comprendente (in maniera sostanzialmente analoga а quanto precedentemente illustrato) una pluralità di sotto-unità di pilotaggio, qui indicate con 23 (e schematizzate come generatori corrente controllati), ciascuna delle quali, opportunamente alimentata da uno stadio a pompa di carica, qui indicato con 24, fornisce su una rispettiva uscita una rispettiva corrente di pilotaggio di uscita Ik, avente un valore amplificato di un fattore β rispetto alla corrente di ingresso  $I_{in}$ , secondo la relazione:  $I_k = I_{in} \cdot \beta$ .

Come sarà descritto in dettaglio in seguito, oltre a ricevere una tensione survoltata  $V_{\rm cp}$  dallo stadio a pompa di carica 24, l'unità di uscita di pilotaggio 22 riceve in ingresso un segnale di controllo ad alta tensione  $Vg_{\rm HV}$ , in particolare destinato a pilotare i terminali di controllo di rispettivi transistori di uscita collegati tra loro in parallelo e ciascuno ad una rispettiva uscita della stessa unità di uscita di pilotaggio 22.

Secondo un aspetto della presente forma di realizzazione, l'unità di controllo pilotaggio 21, anziché essere alimentata, come in soluzioni note (ad esempio come descritto con riferimento alla figura 3), dallo stadio a pompa di carica 24, presenta un ingresso di alimentazione collegato ad una sorgente di alimentazione a bassa tensione del dispositivo di memoria, fornente una tensione di alimentazione logica  $V_{DD}$ , ad esempio di valore compreso tra 1,08 V e 1,32 V.

Inoltre, anziché pilotare direttamente l'unità di uscita di pilotaggio 22 (nuovamente come in soluzioni note), l'unità di controllo pilotaggio 21 fornisce in uscita un segnale di controllo a bassa tensione  $Vg_{LV}$ , che viene alimentato ad un primo morsetto di un condensatore traslatore di livello 25, di tipo per alta tensione. Un secondo morsetto di tale condensatore traslatore di livello 25 fornisce il segnale di controllo ad alta tensione  $Vg_{HV}$  per l'unità di uscita di pilotaggio 22, con valore pari alla somma della tensione del segnale di controllo a bassa tensione  $Vg_{LV}$  e della tensione immagazzinata sullo stesso condensatore traslatore di livello 25.

In altre parole, l'unità di controllo pilotaggio 21 fornisce in uscita un segnale di controllo nel range delle basse tensioni, che, solo dopo opportuna traslazione di livello operata da parte del condensatore traslatore di

livello 25 (mediante addizione di una componente continua), pilota in maniera opportuna le sotto-unità di pilotaggio 23 collegate in parallelo tra loro in uscita. In particolare, sul condensatore traslatore di livello 25 si accumula in uso una tensione di traslazione  $V_c$ , di valore opportuno tale che, una volta sommata al segnale di controllo a bassa tensione  $Vg_{LV}$ , consenta di generare, attraverso le sotto-unità di pilotaggio 23 pilotate dal risultante segnale di controllo ad alta tensione  $Vg_{HV}$ , i valori desiderati per le correnti di pilotaggio di uscita  $I_k$ .

Lo stadio di pilotaggio 20 comprende inoltre un'unità di aggiornamento (refresh) 26, avente un'uscita collegata al secondo morsetto del condensatore traslatore di livello 25 ed un ingresso ricevente la tensione survoltata  $V_{cp}$ dallo stadio a pompa di carica 24. L'unità di refresh 26 riceve inoltre in ingresso un segnale di abilitazione En, ad esempio di tipo impulsivo, ed è configurata in modo da attivare, in funzione del valore di tale segnale abilitazione En, l'aggiornamento del valore della tensione di traslazione Vc sul condensatore traslatore di livello 25, in modo tale da compensare cali della tensione ai suoi capi in seguito alle operazioni di programmazione e da ripristinarne un valore desiderato. Come descritto in dettaglio in seguito, lo stesso segnale di abilitazione En viene inoltre fornito in ingresso all'unità di controllo

pilotaggio 21.

Lo stadio di pilotaggio 20 comprende inoltre un'unità di retroazione (feedback) 28, avente un primo ingresso collegato al secondo morsetto del condensatore traslatore di livello 25 ed un secondo ingresso ricevente la tensione survoltata  $V_{cp}$  dallo stadio a pompa di carica 24. L'unità di retroazione 28 fornisce in uscita un segnale di retroazione  $I_F$ , ad esempio un segnale di corrente, all'unità di controllo pilotaggio 21, in base al quale la stessa unità di controllo pilotaggio 21 è in grado di controllare che la corrente di pilotaggio di uscita  $I_k$  raggiunga il valore desiderato (implementando quindi un anello chiuso di controllo in retroazione).

In particolare, secondo un aspetto della presente invenzione, il valore della corrente di retroazione  $I_F$  rappresenta soltanto una piccola frazione della corrente di pilotaggio di uscita  $I_k$ , ad esempio essendo soddisfatta la relazione:  $I_F = I_K/10$ .

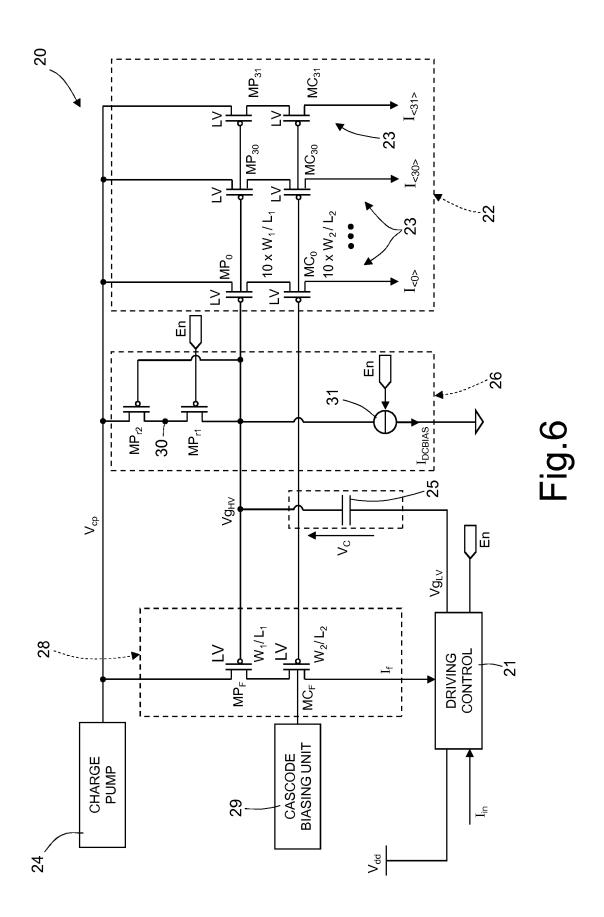

Viene ora descritta più in dettaglio una possibile realizzazione circuitale dello stadio di pilotaggio 20, ad eccezione di quanto riguarda l'unità di controllo pilotaggio 21, che verrà descritta a parte in seguito, sottolineando in generale il fatto che vengono utilizzati per la realizzazione delle unità e sotto-unità precedentemente elencate solamente transistori a bassa

tensione (a differenza di quanto richiesto dalle soluzioni circuitali note, ad esempio del tipo descritto in precedenza con riferimento alla figura 3).

Come illustrato in figura 6, l'unità di uscita di pilotaggio 22 comprende una pluralità di sotto-unità di pilotaggio 23, in numero pari a trentadue nell'esempio illustrato (ed in ogni caso corrispondenti al numero totale di uscite dello stadio di pilotaggio 20 verso il decodificatore di colonna, qui non illustrato), collegate in serie tra l'uscita dello stadio a pompa di carica 24 ed una rispettiva uscita dello stesso stadio di pilotaggio 20. Ciascuna sotto-unità di pilotaggio 23 comprende rispettivo transistore cascode di pilotaggio MCk (con k che va in questo caso da 0 a 31) ed un transistore di uscita MPk, entrambi di tipo PMOS per bassa tensione, collegati in serie e ad una rispettiva uscita dello stadio di pilotaggio 20 fornente la rispettiva corrente di pilotaggio di uscita  $I_k$  .

Il terminale di controllo di ciascun transistore cascode di pilotaggio MCk è collegato all'uscita di un'unità di polarizzazione cascode 29 (di tipo per sé noto, qui non descritto in dettaglio, ad esempio includente un diodo PMOS polarizzato da una corrente costate di valore opportuno) fornente una opportuna tensione di polarizzazione cascode  $V_{\rm cascp}$ , con valore tale da ottenere

una tensione tra drain e source  $V_{DS}$  sui transistori di uscita MPk che consenta il funzionamento in regione di saturazione. Il terminale di controllo di ciascun transistore di uscita MPk è invece collegato al secondo morsetto del condensatore traslatore di livello 25, ricevendo in tal modo il segnale di controllo ad alta tensione  $Vg_{HV}$ .

L'unità di refresh 26 comprende: un primo transistore di refresh MPr<sub>1</sub>, di tipo PMOS per bassa tensione, collegato tra il secondo morsetto del condensatore traslatore di livello 25 ed un nodo interno 30, ed avente terminale di controllo ricevente il segnale di abilitazione En; ed un secondo transistore di refresh MPr<sub>2</sub>, anch'esso di tipo PMOS per bassa tensione, collegato tra il nodo interno 30 e l'uscita dello stadio a pompa di carica 24, ed avente terminale di controllo collegato al suddetto secondo morsetto del condensatore traslatore di livello 25.

L'unità di refresh 26 comprende inoltre un generatore di corrente di polarizzazione 31 controllato e selettivamente abilitato dal segnale di abilitazione En, e collegato tra un nodo a potenziale di riferimento (ad esempio a massa) ed il secondo morsetto del condensatore traslatore di livello 25; quando abilitato, il generatore di corrente di polarizzazione 31 fornisce una corrente di polarizzazione continua  $I_{\text{DCBIAS}}$  di valore opportuno (funzione

anche della dinamica che si desidera ottenere per la corrente in uscita, ad esempio tra 100  $\mu A$  e 1000  $\mu A$ ).

In uso, un opportuno valore logico del segnale di abilitazione En (indicativo della presenza di una modalità operativa di refresh), nell'esempio un valore logico basso, fa sì che il primo ed il secondo transistore di refresh  $MPr_1$ , configurazione di  $\mathtt{MPr}_2$ assumano una diodo, sostanzialmente creando selettivamente un percorso conduttivo tra l'uscita dello stadio a pompa di carica 24 ed il secondo morsetto del condensatore traslatore 25**;** lo stesso valore logico del segnale abilitazione En comporta inoltre l'attivazione generatore di corrente di polarizzazione 31.

Nella modalità operativa di refresh, il valore della tensione di traslazione  $V_c$  ai capi del condensatore traslatore di livello 25 viene opportunamente aggiornata ad un valore desiderato, sostanzialmente definito dal valore della tensione survoltata  $V_{cp}$ , diminuito della caduta di tensione ai capi del diodo realizzato dal primo e dal secondo transistore di refresh  $MPr_1$ ,  $MPr_2$  (il cui valore è funzione anche della corrente di polarizzazione continua  $I_{DCDias}$ ) e della tensione presente sul primo morsetto dello stesso condensatore traslatore di livello 25, determinata, come descritto più in dettaglio in seguito, dall'unità di controllo polarizzazione 21 (operante a sua volta in

funzione del valore del segnale di abilitazione En). Durante la modalità operativa di refresh, la corrente di polarizzazione continua  $I_{\text{DCBIAS}}$  può inoltre presentare un valore tale per cui i transistori di uscita MPk eroghino la minima corrente della dinamica prevista, ad esempio pari a 100  $\mu$ A, in modo che il consumo durante la stessa modalità di refresh risulti ridotto.

Al contrario, quando il segnale di abilitazione En presenta un differente valore logico (determinando così una differente modalità di funzionamento normale, modalità di refresh, nella quale vengono fornite in uscita le correnti di pilotaggio desiderate per il funzionamento delle celle di memoria), il valore di tensione sul secondo morsetto del condensatore traslatore di livello 25, corrispondente al valore del segnale di controllo ad alta tensione  $Vg_{HV}$ , è fissato dal valore del segnale di controllo a bassa tensione  $Vq_{LV}$  e dalla tensione traslazione  $V_c$  ai capi dello stesso condensatore traslatore di livello 25; il generatore di corrente di polarizzazione 31 è disattivato dal segnale di abilitazione En, mentre il primo transistore di refresh MPr<sub>1</sub> è spento dallo stesso segnale di abilitazione En, scollegando il secondo morsetto del condensatore traslatore di livello 25 dall'uscita dello stadio a pompa di carica 24.

L'unità di feedback 28 definisce un ramo circuitale

sostanzialmente speculare e specchiato rispetto a ciascuna delle sotto-unità di pilotaggio 23, comprendendo infatti un transistore cascode di feedback MCf ed un transistore di feedback MPf, entrambi di tipo PMOS per bassa tensione e collegati in serie tra l'uscita dello stadio a pompa di carica 24 e l'ingresso di retroazione dell'unità di controllo pilotaggio 21. Il terminale di controllo del transistore cascode di feedback MCf riceve inoltre la tensione di polarizzazione cascode V<sub>cascp</sub> dall'unità polarizzazione cascode 29 (analogamente a ciascuno dei transistori cascode di polarizzazione MCk), ed il terminale di controllo del transistore di feedback MPf riceve il di controllo ad alta tensione Vg<sub>HV</sub>, segnale essendo collegato al secondo morsetto del condensatore traslatore di livello 25 (analogamente a ciascuno dei transistori di uscita MPk).

particolare, il transistore di feedback presenta un primo rapporto di dimensionamento (rapporto W1/L1 è larghezza/lunghezza) che una frazione del corrispondente rapporto di dimensionamento di ciascuno dei transistori di uscita MPk (aventi ad esempio un rapporto dieci volte maggiore,  $10 \cdot W1/L1);$ analogamente, il transistore cascode di feedback MCf presenta un secondo rapporto di dimensionamento W2/L2 che è pari alla stessa frazione del corrispondente rapporto di dimensionamento di ciascuno dei transistori cascodi di uscita MCk (ad esempio aventi un rapporto dieci volte maggiore, 10·W2/L2).

In uso, data la suddetta configurazione circuitale ed il suddetto dimensionamento dei componenti dell'unità di di feedback 28, la corrente feedback If fornita retroazione dell'unità di controllo all'ingresso di pilotaggio 21 risulta automaticamente diminuita rispetto alla corrente di polarizzazione di uscita  $I_k$  dello stesso che lega i rapporti di dimensionamento dei transistori suddetti, nell'esempio un fattore pari a dieci, così che si dimostra valida la relazione:  $I_k = 10 \cdot I_f$ .

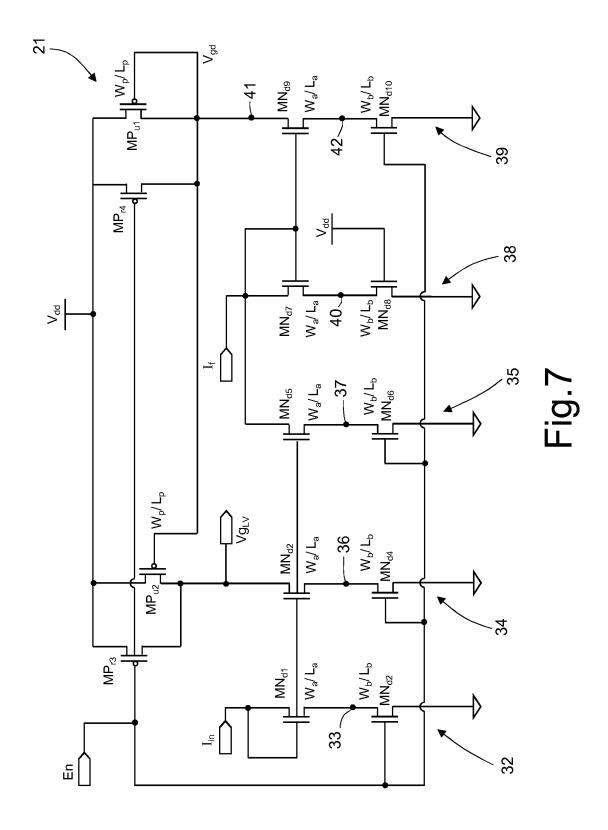

Viene ora descritta la configurazione circuitale dell'unità di controllo pilotaggio 21, con riferimento alla figura 7.

In generale, l'unità di controllo pilotaggio 21 realizza, utilizzando anch'essa solamente transistori per bassa tensione, un amplificatore differenziale di corrente di transresistenza, ricevendo in ingresso la corrente di ingresso I<sub>in</sub> e la corrente di feedback I<sub>f</sub>, ed operando in modo tale da fornire in uscita (in particolare, un'uscita ad elevata impedenza) un valore del segnale di controllo a bassa tensione Vg<sub>IV</sub> tale per cui, in condizione di equilibrio, sussista una relazione desiderata tra i valori delle stesse correnti di ingresso I<sub>in</sub> e di feedback I<sub>f</sub> (ad esempio, al fine di ridurre quanto più possibile una

differenza o sbilanciamento tra tali valori).

In particolare, nella forma di realizzazione illustrata, la configurazione circuitale è tale per cui sussiste la relazione:  $I_f = 2 \cdot I_{\rm in}$ ; di conseguenza, le correnti di ingresso  $I_{\rm in}$  e di uscita  $I_k$  risultano legate dalla relazione:

$$I_k = 2 \cdot \beta \cdot I_{in}$$

dove, come precedentemente evidenziato, il fattore  $\beta$  è ad esempio pari a 10.

In maggiore dettaglio, l'unità di controllo pilotaggio 21 comprende un ramo di ingresso 32, costituito da: un primo transistore NMOS  $MNd_1$ , collegato a diodo tra l'ingresso dell'unità di controllo pilotaggio 21 ricevente la corrente di ingresso  $I_{in}$  ed un nodo 33; ed un secondo transistore NMOS  $MNd_2$ , collegato in serie al primo transistore NMOS  $MNd_1$ , tra il nodo 33 ed il nodo a potenziale di riferimento del circuito, ed avente terminale di controllo ricevente il segnale di abilitazione En.

L'unità di controllo pilotaggio 21 comprende inoltre un primo ed un secondo ramo specchiato 34, 35.

Il primo ramo specchiato 34 è costituito da: un terzo transistore NMOS  $MNd_3$ , collegato tra l'uscita dell'unità di controllo pilotaggio 21 fornente il segnale di controllo a bassa tensione  $Vg_{LV}$  ed un nodo 36, ed avente terminale di controllo collegato al terminale di controllo del primo

transistore NMOS  $MNd_1$ ; ed un quarto transistore  $NMOS \ MNd_4$ , collegato in serie al terzo transistore  $NMOS \ MNd_3$ , tra il nodo 36 ed il nodo a potenziale di riferimento del circuito, ed avente terminale di controllo ricevente il segnale di abilitazione En.

Il secondo ramo specchiato 35 è costituito da: un quinto transistore NMOS MNd<sub>5</sub>, collegato tra l'ingresso di feedback dell'unità di controllo pilotaggio 21 ricevente la corrente di feedback I<sub>f</sub> ed un nodo 37, ed avente terminale di controllo collegato al terminale di controllo del primo transistore NMOS MNd<sub>1</sub>; ed un sesto transistore NMOS MNd<sub>6</sub>, collegato in serie al quinto transistore NMOS MNd<sub>5</sub>, tra il nodo 37 ed il nodo a potenziale di riferimento del circuito, ed avente terminale di controllo ricevente il segnale di abilitazione En.

L'unità di controllo pilotaggio 21 comprende inoltre un ramo di ingresso di retroazione 38 ed un ramo specchiato di retroazione 39.

Il ramo di ingresso di retroazione 38 è costituito da: un settimo transistore NMOS MNd $_7$ , collegato a diodo tra l'ingresso di retroazione dell'unità di controllo pilotaggio 21 ricevente la corrente di feedback  $I_f$  ed un nodo 40; ed un ottavo transistore NMOS MNd $_8$ , collegato in serie al settimo transistore NMOS MNd $_7$ , tra il nodo 40 ed il nodo a potenziale di riferimento del circuito, ed avente

terminale di controllo collegato alla sorgente di alimentazione fornente la tensione di alimentazione logica Vdd.

Il ramo specchiato di retroazione 38 comprende a sua volta: un nono transistore NMOS MNd<sub>9</sub>, collegato tra un nodo 41 ed un nodo 42, ed avente terminale di controllo collegato al terminale di controllo del settimo transistore NMOS MNd<sub>7</sub>; ed un decimo transistore NMOS MPN<sub>10</sub>, collegato in serie al nono transistore NMOS MNd<sub>9</sub>, tra il nodo 42 ed il nodo a potenziale di riferimento del circuito, ed avente terminale di controllo ricevente il segnale di abilitazione En.

In particolare, il primo, terzo, quinto, settimo e nono transistore NMOS  $MNd_1$ ,  $MNd_3$ ,  $MNd_5$ ,  $MNd_7$ ,  $MNd_9$  presentano uno stesso rapporto di dimensionamento  $W_a/L_a$ , così come il secondo, quarto, sesto, ottavo e decimo transistore NMOS  $MNd_2$ ,  $MNd_4$ ,  $MNd_6$ ,  $MNd_8$ ,  $MNd_{10}$  presentano un rispettivo stesso rapporto di dimensionamento  $W_b/L_b$ .

L'unità di controllo pilotaggio 21 comprende inoltre un primo ed un secondo transistore di uscita  $MPu_1$  e  $MPu_2$ , di tipo PMOS, ed un terzo ed un quarto transistore di refresh  $MPr_3$ ,  $MPr_4$ , anch'essi di tipo PMOS.

Il primo transistore di uscita  $MPu_1$  è collegato a diodo tra la sorgente di alimentazione fornente la tensione di alimentazione logica Vdd ed il nodo 41; il secondo

transistore di uscita  $MPu_2$  è collegato tra la sorgente di alimentazione fornente la tensione di alimentazione logica Vdd e l'uscita su cui è presente il segnale di controllo a bassa tensione  $Vg_{LV}$ , ed ha terminale di controllo collegato al terminale di controllo del primo transistore di uscita  $MPu_1$ . Il primo ed il secondo transistore di uscita  $MPu_1$ ,  $MPu_2$  presentano inoltre uno stesso rapporto di dimensionamento  $W_D/L_D$ .

Il terzo transistore di refresh MPr $_3$  è collegato tra la sorgente di alimentazione fornente la tensione di alimentazione logica Vdd e l'uscita su cui è presente il segnale di controllo a bassa tensione  $Vg_{LV}$  e presenta terminale di controllo ricevente il segnale di abilitazione En; il quarto transistore di refresh MPr $_4$  è collegato tra la sorgente di alimentazione fornente la tensione di alimentazione logica Vdd ed il nodo 41, e presenta anch'esso terminale di controllo ricevente il segnale di abilitazione En.

In uso, ed in maniera che apparirà di per sé evidente dall'esame del circuito, durante la modalità di normale funzionamento (segnale di abilitazione En con valore logico alto), una corrente di valore sostanzialmente uguale alla corrente di ingresso I<sub>in</sub> circola nei vari rami circuitali, essendo questi ultimi composti da transistori con le stesse caratteristiche e polarizzati nelle stesse condizioni

operative. Pertanto, la corrente di feedback  $I_f$  risulta uquale a due volte il valore della corrente di ingresso I<sub>in</sub>, dato che all'ingresso di retroazione afferiscono sia il secondo rampo specchiato 35 che il primo ramo di equilibrio, feedback 38. Inoltre, in condizione di nuovamente data la sostanziale simmetria circuitale, il valore del segnale di controllo a bassa tensione  $Vg_{ ext{LV}}$ risulta sostanzialmente uquale al valore di tensione sul terminale di controllo del primo transistore di uscita  $MPu_1$ , collegato a diodo (qui indicata con  $Vg_d$ ). Si noti che, per effetto della retroazione, il valore del segnale di controllo a bassa tensione  $Vg_{LV}$  si sposta in maniera opportuna tra 0 V ed il valore della tensione di alimentazione logica Vdd, al fine di riportare il circuito in condizione di equilibrio.

In ogni caso, il valore del segnale di controllo a bassa tensione  $Vg_{LV}$ , dopo l'opportuna traslazione di livello da parte del condensatore traslatore di livello 25, pilota i terminali di controllo dei transistori di polarizzazione di uscita, al fine di ottenere, in situazione di equilibrio, il valore desiderato per la corrente di pilotaggio di uscita  $I_k$  (ad esempio, nel caso illustrato,  $I_k = 2 \cdot \beta \cdot I_{in}$ ).

Durante la modalità di refresh, al contrario, il valore logico basso del segnale di abilitazione En spegne

il secondo, quarto, sesto, ottavo e decimo transistore NMOS  $MNd_2$ ,  $MNd_4$ ,  $MNd_6$ ,  $MNd_8$ ,  $MNd_{10}$  ed accende il terzo ed il quarto transistore di refresh MPr3, MPr4, così che il bassa tensione  $V_{\text{GLV}}$  si segnale di controllo a sostanzialmente al valore della tensione di alimentazione Vdd. logica In questa modalità operativa, precedentemente evidenziato, avviene l'aggiornamento della tensione di traslazione  $V_{\rm c}$  sul condensatore traslatore di un valore prefissato e livello 25, in presenza di controllato del segnale di controllo a bassa tensione  $V_{\text{qLV}}$ (corrispondente sostanzialmente al valore Vdd).

In maniera non illustrata nelle figure precedenti, il segnale di abilitazione En viene generato e fornito all'unità di controllo pilotaggio 21 da un'unità gestione del dispositivo di memoria, che sovraintende al suo funzionamento generale, determinando tra l'altro temporizzazione delle operazioni di lettura programmazione. Ad esempio, vantaggiosamente, la modalità di della tensione di refresh traslazione  $m V_c$ condensatore traslatore di livello 25 può essere attivata in seguito ad ogni impulso di programmazione (di SET o RESET) che viene applicato alle celle di memoria per il tramite dello stadio di pilotaggio 20.

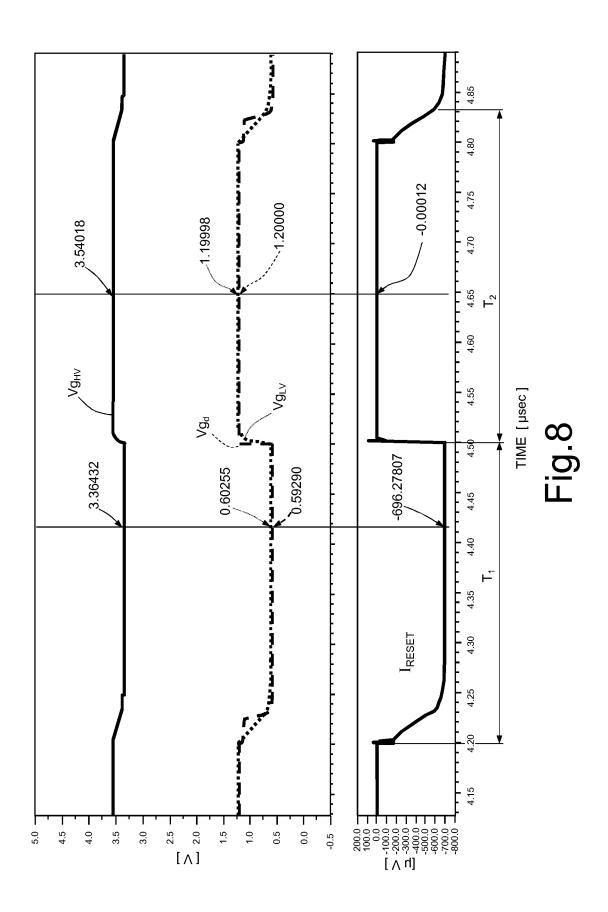

A questo riguardo, la figura 8 mostra l'esempio di applicazione, nell'intervallo temporale  $T_1$ , di un impulso

di programmazione, in particolare un impulso di corrente di RESET (indicata con  $I_{Reset}$ ), avente una ampiezza pari a seguito, in un consecutivo intervallo circa 700 μA, temporale T2, dall'operazione di aggiornamento del valore di traslazione V<sub>c</sub> della tensione sul condensatore traslatore di livello 25; nell'esempio, in all'operazione di refresh, il valore del segnale controllo ad alta tensione  $Vg_{HV}$  passa ad esempio da un valore circa pari a 3,36 V ad un valore circa pari a 3,54 V, per l'effetto dell'aggiornamento del valore della tensione di traslazione  $V_c$ . Si noti inoltre la sostanziale uquaglianza dei valori del segnale di controllo a bassa tensione  $Vg_{LV}$  e della tensione  $Vg_d$  del terminale di controllo del primo transistore di uscita MPu<sub>1</sub>, collegato a diodo.

I vantaggi dello stadio di polarizzazione secondo la presente invenzione emergono in maniera evidente dalla descrizione precedente.

In ogni caso, si sottolinea che la soluzione descritta consente di ottenere un evidente risparmio nell'occupazione di area richiesta per la realizzazione dell'unità di controllo pilotaggio 21, che risulta infatti avere una struttura unitaria e particolarmente compatta per tutte le sotto-unità di pilotaggio 23 in uscita. In particolare, l'utilizzo di soli componenti per bassa tensione (ad

eccezione del solo condensatore traslatore di livello 25) consente di ottenere un notevole risparmio di area nella realizzazione integrata.

La soluzione descritta presenta un'elevata efficienza nel consumo di corrente, in quanto il pilotaggio dei terminali di controllo dei transistori di uscita delle sotto-unità di pilotaggio 23 avviene tramite il condensatore traslatore di livello 25, così che non viene richiesta alcuna corrente dallo stadio a pompa di carica 24.

Inoltre, la corrente di feedback  $I_f$ , che risulta essere richiesta dallo stadio a pompa di carica 24, ha un valore ridotto, corrispondendo solo ad una piccola frazione (ad esempio un decimo, ma potrebbe essere ridotta ulteriormente senza alterare il funzionamento del circuito) della corrente di pilotaggio di uscita  $I_k$ , il che consente un notevole risparmio in termini dei consumi.

In aggiunta, l'unità di controllo pilotaggio 21 è vantaggiosamente alimentata dalla tensione di alimentazione logica Vdd, di valore particolarmente contenuto, anziché essere alimentata dallo stadio a pompa di carica 24.

La presente richiedente ha verificato la possibilità di ottenere un risparmio nell'occupazione di area anche fino a cinque volte rispetto a soluzioni tradizionali, con un'efficienza (valutata come rapporto tra la corrente

fornita dallo stadio di alimentazione e la corrente fornita in uscita) minore di 1,2.

In maniera evidente, i suddetti risparmi nel consumo di area e di corrente consentono di ottenere un associato risparmio nei costi di realizzazione e di utilizzo in condizione operativa del dispositivo di memoria.

Risulta infine chiaro che a quanto qui descritto ed illustrato possono essere apportate modifiche e varianti, senza per questo uscire dall'ambito di protezione della presente invenzione, come definito nelle rivendicazioni allegate.

In particolare, è evidente che il dispositivo di memoria non volatile a cambiamento di fase incorporante lo stadio di polarizzazione descritto può avere svariati utilizzi, tra cui ad esempio in microcontrollori, in applicazioni ad elevata richiesta di sicurezza che fanno uso di Smart Card con interfaccia contact (quali sistemi PAYTV, moduli SIM, TPM) che devono soddisfare le specifiche di consumo ETSI, e in applicazioni Smart Card contactless (RFID, NFC, carte di credito bancarie, ecc.), dove il modulo di memoria ha un budget di corrente limitato dal sistema di "energy harvesting" (recupero di energia dalla portante) per tutte le operazioni (sia di scrittura che di lettura).

## RIVENDICAZIONI

1. Stadio di pilotaggio (20) per un dispositivo di memoria non volatile а cambiamento di fase (1),di comprendente: un'unità di pilotaggio uscita (22),configurata in modo da fornire una corrente di pilotaggio di uscita (Ik) durante un'operazione di programmazione di almeno una cella di memoria (3) di detto dispositivo di memoria non volatile a cambiamento di fase (1); ed un'unità controllo pilotaggio (21), configurata in modo ricevere una corrente di ingresso (I<sub>in</sub>) e da generare su una uscita di controllo un primo segnale di controllo (Vq<sub>I,V</sub>) destinato a controllare la fornitura della corrente di pilotaggio di uscita (Ik) da parte di detta unità di pilotaggio di uscita (22), in modo tale che un valore di detta corrente di pilotaggio di uscita (Ik) presenti una relazione desiderata con detta corrente di ingresso (Iin),

caratterizzato dal fatto di comprendere un elemento traslatore di livello (25), interposto tra l'uscita di controllo di detta unità di controllo pilotaggio (21) ed un ingresso di controllo di detta unità di pilotaggio di uscita (22), ed atto a traslare di livello una tensione di detto primo segnale di controllo ( $Vg_{LV}$ ) per fornire a detto ingresso di controllo di detta unità di pilotaggio di uscita (22) un secondo segnale di controllo ( $Vg_{HV}$ ), avente valore di tensione incrementato rispetto a, e funzione di,

detto primo segnale di controllo (VgLV).

- 2. Stadio di pilotaggio secondo la rivendicazione 1, in cui detta unità di pilotaggio di uscita (22) comprende una pluralità di transistori di uscita (MPk), aventi un rispettivo terminale di controllo ricevente detto secondo segnale di controllo ( $Vg_{HV}$ ), ed un rispettivo terminale di conduzione fornente detta corrente di pilotaggio di uscita ( $I_k$ ) su una rispettiva uscita di pilotaggio di detta unità di pilotaggio di uscita (22).

- 3. Stadio di pilotaggio secondo la rivendicazione 1 o 2, in cui detta unità di controllo pilotaggio (21) presenta un ingresso di alimentazione logica atto a ricevere una tensione di alimentazione logica (Vdd), e detto primo segnale di controllo (Vg\_Lv) presenta un valore massimo non superiore a detta tensione di alimentazione logica (Vdd); ed in cui detto elemento traslatore di livello (25) comprende un elemento condensatore configurato in modo da immagazzinare ai suoi capi una tensione di traslazione (Vc) di valore tale per cui detto secondo segnale di controllo (Vg\_Hv) presenta un valore maggiore rispetto a detta tensione di alimentazione logica (Vdd).

- 4. Stadio di pilotaggio secondo la rivendicazione 3, in cui detta unità di pilotaggio di uscita (22) presenta un ingresso di alimentazione survoltata atto a ricevere una tensione survoltata ( $V_{\rm cp}$ ) da uno stadio a pompa di carica

- (24), avente valore maggiore rispetto al valore di detta tensione di alimentazione logica (Vdd).

- 5. Stadio di pilotaggio secondo la rivendicazione 3 o 4, in cui detta unità di controllo pilotaggio (21) e detta unità di pilotaggio di uscita (22) comprendono esclusivamente transistori operanti in un intervallo di tensione non superiore al valore di detta tensione di alimentazione logica (Vdd).

- 6. Stadio di pilotaggio secondo una qualsiasi delle rivendicazioni precedenti, comprendente inoltre un'unità di retroazione (28), collegata all'ingresso di controllo di detta unità di pilotaggio di uscita (22), e configurata in modo da fornire ad un ingresso di retroazione di detta unità di controllo pilotaggio (21) una corrente di retroazione ( $I_f$ ), un cui valore corrisponde ad una frazione desiderata del valore di detta corrente di pilotaggio di uscita ( $I_k$ ).

- 7. Stadio di pilotaggio secondo la rivendicazione 6, in cui detta unità di controllo pilotaggio (21) è configurata in modo da generare detto primo segnale di controllo ( $Vg_{LV}$ ) in funzione del valore di detta corrente di retroazione ( $I_f$ ) e di detta corrente di ingresso ( $I_{in}$ ).

- 8. Stadio di pilotaggio secondo la rivendicazione 7, in cui detta unità di controllo pilotaggio (21) realizza un amplificatore differenziale di corrente di transresistenza,

configurato in modo da ricevere su un primo ed un secondo ingresso differenziale detta corrente di ingresso ( $I_{\rm in}$ ) e detta corrente di retroazione ( $I_{\rm f}$ ), ed in modo da generare in uscita detto primo segnale di controllo ( $Vg_{\rm LV}$ ) avente un valore tale da ottenere, in condizione di equilibrio, un rapporto prefissato tra detta corrente di retroazione ( $I_{\rm f}$ ) e detta corrente di ingresso ( $I_{\rm in}$ ).

- 9. Stadio di pilotaggio secondo una qualsiasi delle rivendicazioni 6-8, in cui detta unità di pilotaggio di uscita (22) comprende una pluralità di rami di uscita (23), atti a fornire detta corrente di pilotaggio di uscita ( $I_k$ ) su una rispettiva uscita di detta unità di pilotaggio di uscita (22); ed in cui detta unità di retroazione (28) comprende un ramo circuitale specchiato rispetto a detti rami di uscita (23), con fattore di specchiaggio tale che il valore di detta corrente di retroazione ( $I_f$ ) corrisponde alla frazione desiderata del valore di detta corrente di pilotaggio di uscita ( $I_k$ ).

- 10. Stadio di pilotaggio secondo una qualsiasi delle rivendicazioni precedenti, comprendente inoltre un'unità di aggiornamento (26), collegata a detto elemento traslatore di livello (25) e configurata in modo da ricevere un segnale di abilitazione (En) e da attivare, in funzione del valore del segnale di abilitazione (En), un'operazione di aggiornamento ad un valore desiderato della tensione di

traslazione ( $V_c$ ) presente ai capi di detto elemento traslatore di livello (25).

- 11. Stadio di pilotaggio secondo la rivendicazione 10, in cui un primo valore di detto segnale di abilitazione (En) determina una prima condizione operativa in cui viene effettuata detta operazione di aggiornamento del valore di tensione di traslazione ( $V_c$ ) presente ai capi dell'elemento traslatore di livello (25); ed un secondo valore di detto segnale di abilitazione (En) determina una seconda condizione operativa in cui viene fornita detta corrente di pilotaggio di uscita ( $I_k$ ) avente detta relazione desiderata con la corrente di ingresso ( $I_{in}$ ).

- 12. Stadio di pilotaggio secondo la rivendicazione 10 o 11, in cui detto segnale di abilitazione (En) è un segnale di tipo impulsivo, e detta unità di aggiornamento (26) è configurata in modo da attivare detta operazione di aggiornamento in seguito a detta operazione di programmazione effettuata su detta cella di memoria (3).

- 13. Stadio di pilotaggio secondo una qualsiasi delle rivendicazioni 10-12, in cui detta unità di aggiornamento (26) comprende un elemento di conduzione selettiva di corrente (MPa1, MPa2) controllato da detto segnale di abilitazione (En), ed azionabile per stabilire un percorso conduttivo tra detto elemento traslatore di livello (25) ed un ingresso di alimentazione survoltata atto a ricevere una

tensione survoltata ( $V_{cp}$ ) da uno stadio a pompa di carica (24) durante detta operazione di aggiornamento; ed in cui detta unità di controllo pilotaggio (21) è configurata per fornire detto primo segnale di controllo ( $Vg_{LV}$ ) a detto elemento traslatore di livello (25) con un valore di tensione prefissato e controllato durante detta operazione di aggiornamento.

14. Dispositivo di memoria non volatile a cambiamento di fase (1) comprendente una matrice (2) di celle di memoria (3), ed uno stadio di pilotaggio (20) secondo una qualsiasi delle rivendicazioni precedenti, operativamente accoppiato a dette celle di memoria (3).

15. Dispositivo di memoria secondo la rivendicazione 14, comprendente inoltre un decodificatore di colonna (4), configurato in modo da selezionare linee di bit (BL) di detta matrice (2) in funzione di segnali di indirizzo durante detta operazione di programmazione, ed interposto tra detto stadio di pilotaggio (20) e detta matrice (2), in modo da ricevere detta corrente di pilotaggio di uscita  $(I_k)$  e fornirla alle linee di bit (BL) selezionate.

p.i.: STMICROELECTRONICS S.R.L.

Lorenzo NANNUCCI

## CLAIMS

1. A driving stage (20) for a phase change non-volatile memory device (1), comprising: an output driving unit (22), configured to supply an output driving current ( $I_k$ ) during an operation of programming of at least one memory cell (3) of said phase change non-volatile memory device (1); and a driving-control unit (21), configured to receive an input current ( $I_{\rm in}$ ) and to generate on a control output a first control signal ( $Vg_{\rm LV}$ ) designed to control supply of the output driving current ( $I_k$ ) by said output driving unit (22) in such a way that a value of said output driving current ( $I_k$ ) has a desired relation with said input current ( $I_{\rm in}$ ),

5

10

25

characterized by comprising a level-shifter element (25), set between the control output of said driving-control unit (21) and a control input of said output driving unit (22), and designed to determine a level shift of a voltage of said first control signal ( $Vg_{LV}$ ) for supplying to said control input of said output driving unit (22) a second control signal ( $Vg_{HV}$ ), having a voltage value that is increased with respect to, and

is a function of, said first control signal (Vg\_IN).

- 2. The driving stage according to claim 1, wherein said output driving unit (22) comprises a plurality of output transistors (MPk), having a respective control terminal receiving said second control signal (Vg<sub>HV</sub>), and a respective conduction terminal supplying said output driving current ( $I_k$ ) on a

- 30 3. The driving stage according to claim 1 or 2, wherein said driving-control unit (21) has a logic-supply input designed to receive a logic supply voltage (Vdd), and said first control signal (Vg $_{\rm LV}$ ) has a maximum value not higher than said logic supply voltage (Vdd); and wherein said level-shifter element

respective driving output of said output driving unit (22).

(25) comprises a capacitor element configured to store a shift voltage ( $V_c$ ) having a value such that said second control signal ( $Vg_{HV}$ ) has a value higher than said logic supply voltage (Vdd).

5

10

15

20

- 4. The driving stage according to claim 3, wherein said output driving unit (22) has a boosted-supply input designed to receive a boosted voltage ( $V_{\text{cp}}$ ) from a charge-pump stage (24), having a value higher than that of said logic supply voltage (Vdd).

- 5. The driving stage according to claim 3 or 4, wherein said driving-control unit (21) and said output driving unit (22) comprise solely transistors operating in a voltage range not higher than the value of said logic supply voltage (Vdd).

- 6. The driving stage according to any one of the preceding claims, further comprising a feedback unit (28), connected to the control input of said output driving unit (22), and configured to supply to a feedback input of said driving-control unit (21) a feedback current ( $I_F$ ), a value of which corresponds to a desired fraction of the value of said output driving current ( $I_k$ ).

- 7. The driving stage according to claim 6, wherein said driving-control unit (21) is configured to generate said first control signal ( $Vg_{LV}$ ) as a function of the value of said feedback current ( $I_F$ ) and of said input current ( $I_{in}$ ).

- 30 8. The driving stage according to claim 7, wherein said driving-control unit (21) defines a transresistance differential current amplifier, configured to receive on a first differential input and a second differential input said input current ( $I_{\rm in}$ ) and said feedback current ( $I_{\rm F}$ ), and to

generate at output said first control signal ( $Vg_{LV}$ ) having a value such as to obtain, in a condition of equilibrium, a preset ratio between said feedback current ( $I_F$ ) and said input current ( $I_{in}$ ).

5

9. The driving stage according to any one of claims 6-8, wherein said output driving unit (22) comprises a plurality of output branches (23), designed to supply said output driving current ( $I_k$ ) on a respective output of said output driving unit (22), and wherein said feedback unit (28) comprises a circuit branch mirrored with respect to said output branches (23), with a mirroring factor such that the value of said feedback current ( $I_F$ ) corresponds to the desired fraction of the value of said output driving current ( $I_k$ ).

15

20

10

- 10. The driving stage according to any one of the preceding claims, further comprising a refresh unit (26), connected to said level-shifter element (25) and configured to receive an enable signal (En) and to activate, as a function of the value of the enable signal (En), an operation of refresh to a desired value of the shift voltage ( $V_c$ ) present across said level-shifter element (25).

- 11. The driving stage according to claim 10, wherein: a first value of said enable signal (En) determines a first operating condition in which said operation of refresh of the value of the shift voltage ( $V_c$ ) present across the level-shifter element (25) is carried out; and a second value of said enable signal (En) determines a second operating condition in which said output driving current ( $I_k$ ) having said desired relation

with the input current ( $I_{in}$ ) is supplied.

12. The driving stage according to claim 10 or 11, wherein

said enable signal (En) is a signal of an impulsive type, and

said refresh unit (26) is configured to activate said refresh operation after said programming operation carried out on said memory cell (3).

- 5 13. The driving stage according to any one of claims 10-12, wherein said refresh unit (26) comprises a selective current-conduction element (MPa<sub>1</sub>, MPa<sub>2</sub>), which is controlled by said enable signal (En) and is operable for defining a conductive path between said level-shifter element (25) and a boosted-supply input designed to receive a boosted voltage (V<sub>cp</sub>) from a charge-pump stage (24) during said refresh operation, and wherein said driving-control unit (21) is configured to supply said first control signal (Vg<sub>LV</sub>) to said level-shifter element (25) with a pre-set and controlled voltage value during said refresh operation.

- 14. A phase change non-volatile memory device (1) comprising an array (2) of memory cells (3), and a driving stage (20) according to any one of the preceding claims, operatively coupled to said memory cells (3).

- 15. The memory device according to claim 14, further comprising a column decoder (4), which is configured to select bitlines (BL) of said array (2) as a function of address signals during said programming operation, and is set between said driving stage (20) and said array (2) so as to receive said output driving current ( $I_k$ ) and supply it to the selected bitlines (BL).

20

25

Lorenzo NANNUCCI (Iscrizione Albo nr. 1214/B)

Lorenzo NANNUCCI (Iscrizione Albo nr. 1214/B)

Lorenzo NANNUCCI (Iscrizione Albo nr. 1214/B)