(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-505433

(P2004-505433A)

(43) 公表日 平成16年2月19日(2004.2.19)

(51) Int.Cl.<sup>7</sup>

H01L 21/00

H01L 21/02

F 1

H01L 21/00

H01L 21/02

テーマコード(参考)

Z

審査請求 未請求 予備審査請求 有 (全 160 頁)

(21) 出願番号 特願2001-537527 (P2001-537527)

(86) (22) 出願日 平成12年11月17日 (2000.11.17)

(85) 翻訳文提出日 平成14年5月20日 (2002.5.20)

(86) 國際出願番号 PCT/US2000/031665

(87) 國際公開番号 WO2001/035718

(87) 國際公開日 平成13年5月25日 (2001.5.25)

(31) 優先権主張番号 09/442,699

(32) 優先日 平成11年11月18日 (1999.11.18)

(33) 優先権主張国 米国(US)

(71) 出願人 502180233

ピー・ディ・エフ ソリューションズ インコーポレイテッド

P D F S O L U T I O N S, I N C.

アメリカ合衆国 カリフォルニア州 95110 サンノゼ ウエスト・サン・カーロス・ストリート 333 スイート 700

333 West San Carlos Street, Suite 700, San Jose, California 95110, United States of America

(74) 代理人 100062993

弁理士 田中 浩

最終頁に続く

(54) 【発明の名称】製品歩留まり予測用のシステムおよび方法

## (57) 【要約】

集積回路の歩留まりを予測するためのシステムおよび方法は、最終的な集積回路製品に組み込むべき少なくとも1つのタイプのフィーチャを表す少なくとも1つのフィーチャを組み込む、少なくとも1つのタイプの特徴付けビヒクルを含む。この特徴付けビヒクルは、歩留まりモデルを生成するために、集積回路製品を製造する際に使用すべき製造サイクルを構成するプロセス・オペレーションのうちの少なくとも1つを受ける。この歩留まりモデルは、特徴付けビヒクルによって定義されるレイアウトを実施し、好ましくは、動作速度での電気的テスト・データの収集およびプロトタイプ・セクションのテストを容易にするフィーチャを含む。抽出エンジンは、提案される製品レイアウトから所定のレイアウト属性を抽出する。歩留まりモデルに対して操作して、この抽出エンジンは、レイアウト属性と、層または製造プロセスのステップごとの破壊に応じて歩留まり予測を生成する。次いでこれらの歩留まり予測を使用して、製造プロセス中のどのエリアを最も改良する必要があるかを判定する。

**【特許請求の範囲】****【請求項 1】**

- a ) 最終的な集積回路製品に組み込むべき少なくとも 1 つのタイプのフィーチャを表す少なくとも 1 つのフィーチャを含む、少なくとも 1 つのタイプの特徴付けビヒクルと、

- b ) 特徴付けビヒクルによって定義されるレイアウトを実施する歩留まりモデルであって、集積回路製品を製造する際に使用すべき製造サイクルを構成する、少なくとも 1 つのプロセス・オペレーションを受けた歩留まりモデルと、

- c ) 製品レイアウトと、

- d ) 製品レイアウトから所定のレイアウト特性を抽出するための抽出エンジンであって、その特性が歩留まりモデルと共に使用されて、歩留まり予測が生成される抽出エンジンとを備える、

- 集積回路の歩留まりを予測するためのシステム。

**【請求項 2】**

特徴付けビヒクル・レイアウトが、製品レイアウト上に現れる各フィーチャの変動の範囲と同じ範囲を含む、請求項 1 に記載のシステム。

**【請求項 3】**

特徴付けビヒクルがショート・フロー・テスト・ビヒクルを備える、請求項 2 に記載のシステム。

**【請求項 4】**

特徴付けビヒクルが、提案される製品レイアウトを表すフィーチャを含む部分レイアウトを有するショート・フロー・テスト・ビヒクルを備える、請求項 3 に記載のシステム。

**【請求項 5】**

特徴付けビヒクルが、少なくとも 1 つの能動領域と、提案される製品レイアウトを表す少なくとも 1 つの事前選択した隣接フィーチャとを定義する、請求項 4 に記載のシステム。

**【請求項 6】**

特徴付けビヒクルが金属ショート・フロー・テスト・ビヒクルを備える、請求項 3 に記載のシステム。

**【請求項 7】**

金属ショート・フロー・テスト・ビヒクルが少なくとも 1 つの基本構造を含む、請求項 6 に記載のシステム。

**【請求項 8】**

前記少なくとも 1 つの基本構造が、

- a ) ケルビン金属臨界寸法構造と、

- b ) スネーク構造と、

- c ) コーム構造と、

- d ) スネークおよびコーム構造と、

- e ) ネスト欠陥サイズ分布構造と、

- f ) ファン・デル・ポー構造と、

- g ) 光近接補正構造と、

- h ) 走査電子顕微鏡構造とからなるグループから選択される、請求項 7 に記載のシステム。

**【請求項 9】**

金属ショート・フロー・テスト・ビヒクルが、单一金属層中に少なくとも 1 つの基本構造を含む、請求項 8 に記載のシステム。

**【請求項 10】**

金属ショート・フロー・テスト・ビヒクルが、複数の金属層中に少なくとも 1 つの基本構造を含む、請求項 8 に記載のシステム。

**【請求項 11】**

提案される製品レイアウトを表すフィーチャが少なくとも 1 つのバイアまたは接点を含む、請求項 4 に記載のシステム。

10

20

30

40

50

**【請求項 1 2】**

提案される製品レイアウトを表すフィーチャが少なくとも 1 つの能動デバイスを含む、請求項 4 に記載のシステム。

**【請求項 1 3】**

提案される製品レイアウトを表すフィーチャが少なくとも 1 つのケイ化物領域を含む、請求項 4 に記載のシステム。

**【請求項 1 4】**

提案される製品レイアウトを表すフィーチャが少なくとも 1 つのポリシリサイド領域またはポリシリコン領域を含む、請求項 4 に記載のシステム。

**【請求項 1 5】**

抽出エンジンが、特徴付けビヒクルを設計するときに使用するためのレイアウト・フィーチャ・レベルの範囲を決定するためにも使用される、請求項 1 に記載のシステム。

**【請求項 1 6】**

レベルのレイアウト・フィーチャ範囲が、線幅、線スペース、および線密度を含む、請求項 1 5 に記載のシステム。

**【請求項 1 7】**

a ) 最終的な集積回路製品に組み込むべき少なくとも 1 つのタイプのフィーチャを表す少なくとも 1 つのフィーチャを有する、少なくとも 1 つのタイプの特徴付けビヒクルを製造するための情報を提供すること、

b ) 集積回路製品を製造する際に使用すべき製造サイクルを構成する少なくとも 1 つのプロセス・オペレーションを利用して、歩留まりモデルと、製品を表すレイアウト・フィーチャとを実施する特徴付けビヒクルを製造すること、

c ) 製品レイアウトを提供すること、

d ) 製品レイアウトから所定のレイアウト特性を抽出すること、

e ) 抽出したレイアウト特性を歩留まりモデルとモデルと共に使用して、歩留まり予測を生成することを含む

集積回路に関する歩留まりを予測するための方法。

**【請求項 1 8】**

特徴付けビヒクル・レイアウトが、製品レイアウト上に現れる各フィーチャの変動の範囲と同じ範囲を含む、請求項 1 7 に記載の方法。

**【請求項 1 9】**

特徴付けビヒクルがショート・フロー・テスト・ビヒクルを備える、請求項 1 8 に記載の方法。

**【請求項 2 0】**

特徴付けビヒクルが、提案される製品レイアウトを表すフィーチャを含む部分レイアウトを有するショート・フロー・テスト・ビヒクルを備える、請求項 1 9 に記載の方法。

**【請求項 2 1】**

特徴付けビヒクルが、少なくとも 1 つの能動領域と、提案される製品レイアウトを表す少なくとも 1 つの事前選択した隣接フィーチャとを定義する、請求項 2 0 に記載の方法。

**【請求項 2 2】**

特徴付けビヒクルが金属ショート・フロー・テスト・ビヒクルを備える、請求項 1 9 に記載の方法。

**【請求項 2 3】**

金属ショート・フロー・テスト・ビヒクルが少なくとも 1 つの基本構造を含む、請求項 2 2 に記載の方法。

**【請求項 2 4】**

前記少なくとも 1 つの基本構造が、

a ) ケルビン金属臨界寸法構造と、

b ) スネーク構造と、

c ) コーム構造と、

10

20

30

40

50

- d ) スネークおよびコーム構造と、

- e ) ネスト欠陥サイズ分布構造と、

- f ) ファン・デル・ポー構造と、

- g ) 光近接補正構造と、

h ) 走査電子顕微鏡構造とからなるグループから選択される、請求項 2 3 に記載の方法。

【請求項 2 5】

金属ショート・フロー・テスト・ビヒクルが、単一金属層中に少なくとも 1 つの基本構造を含む、請求項 2 4 に記載の方法。

【請求項 2 6】

金属ショート・フロー・テスト・ビヒクルが、複数の金属層中に少なくとも 1 つの基本構造を含む、請求項 2 4 に記載の方法。 10

【請求項 2 7】

提案される製品レイアウトを表すフィーチャが少なくとも 1 つのバイアまたは接点を含む、請求項 2 0 に記載の方法。

【請求項 2 8】

提案される製品レイアウトを表すフィーチャが少なくとも 1 つの能動デバイスを含む、請求項 2 0 に記載の方法。

【請求項 2 9】

提案される製品レイアウトを表すフィーチャが少なくとも 1 つのケイ化物領域を含む、請求項 2 0 に記載の方法。 20

【請求項 3 0】

提案される製品レイアウトを表すフィーチャが少なくとも 1 つのポリシリサイド領域またはポリシリコン領域を含む、請求項 2 0 に記載の方法。

【請求項 3 1】

抽出エンジンが、特徴付けビヒクルを設計するときに使用するためのレベルの範囲を決定するためにも使用される、請求項 1 7 に記載の方法。

【請求項 3 2】

レベルの範囲が、線幅、線スペース、および線密度を含む、請求項 3 1 に記載の方法。

【請求項 3 3】

所定のレイアウト特性が、

- a ) 特徴付けビヒクル中のすべての構造をリストするステップと、

- b ) 各構造をファミリに分類し、それによって各ファミリ中のすべての構造が特定の属性にわたる実験を形成するステップと、

- c ) 各ファミリについて、どの属性を製品レイアウトに関して抽出すべきかを決定するステップとを含むプロセスを使用して、製品レイアウトから抽出される、請求項 1 7 に記載の方法。

【請求項 3 4】

ファミリが、選択した数の線幅およびスペースにわたって基本的欠陥を調査するためのネスト構造を有するファミリを含む、請求項 3 3 に記載の方法。

【請求項 3 5】

ファミリが、特定の幅の線幅およびスペースにわたって歩留まりを調査するためのスネークおよびコーム構造を有するファミリを含む、請求項 3 3 に記載の方法。 40

【請求項 3 6】

所定の範囲の線幅およびスペースが、比較的小さいスペースに並ぶ比較的広い線幅と、比較的狭い線幅に並ぶ比較的大きい線間スペースとを含む、請求項 3 5 に記載の方法。

【請求項 3 7】

ファミリが、線密度、線幅、および間にわたる臨界寸法変動を調査するためのケルビン臨界寸法構造およびファン・デル・ポー構造を有するファミリを含む、請求項 3 3 に記載の方法。

【請求項 3 8】

ファミリが、歩留まりに対する様々な光近接補正方式の効果を調査するためのボーダ構造を有するファミリを含む、請求項 3 3 に記載の方法。

【請求項 3 9】

特徴付けてビヒクル・データおよび抽出したレイアウト属性が与えられた場合に、歩留まり損失機構を決定し、配置するためのシステム。

【発明の詳細な説明】

【0 0 0 1】

(発明の背景)

本発明は、集積回路の製造に関し、より詳細には、製造歩留まりを改善するためのシステムおよび方法に関する。

10

【0 0 0 2】

集積回路の製造は、何百もの個別の作業を含むことがある非常に複雑な工程である。基本的には、この工程は、精密にあらかじめ定めた量のドーパント材料を、精密にあらかじめ定めたシリコン・ウェハのエリアに拡散し、トランジスタなどの能動デバイスを生成することを含む。これは一般に、ウェハ上に二酸化シリコンの層を形成し、次いで二酸化シリコン・マスクを通じて拡散を行うべきエリアのパターンを画定するために、フォトマスクおよびフォトレジストを利用する。次いで、二酸化シリコン層を貫いて開口がエッチングされ、大きさに合わせて精密に作られ、位置付けられた、拡散がそれを通じて行われる開口のパターンが画定される。所定の数のこのような拡散操作を実施してウェハ中に所望の数のトランジスタを生成した後、これらのトランジスタは、必要に応じて相互接続線によって相互接続される。これらの相互接続線、または相互接続としても知られるものは一般に、フォトマスク、フォトレジスト、およびエッチング工程によって所望の相互接続パターンに画定される導電性材料の付着によって形成される。典型的な完成後の集積回路は、0.1インチ×0.1インチ(2.54mm×2.54mm)のシリコン・チップに含まれる数百万のトランジスタと、サブミクロン寸法の相互接続とを有することができる。

20

【0 0 0 3】

今日の集積回路で必要とされるデバイスおよび相互接続の密度を考えると、製造工程を最大の精度で、かつ欠陥を最小にするように実施することが不可欠である。動作を信頼性あるものとするために、回路の電気的特性を、注意深く制御される限度内に保たなければならない。このことは、無数の作業および製造工程にわたって高度な制御を行うことを意味する。例えば、フォトレジスト作業およびフォトマスク作業では、塵などの異物の存在、微細なスクランチ、およびフォトマスク上のパターン中の他の欠陥により、半導体ウェハ上に欠陥パターンが生成され、欠陥集積回路が生成される可能性がある。さらに、拡散操作自体の間に、欠陥が回路中に導入される可能性がある。欠陥のある回路は、高倍率の下での外観検査と、電気的テストの両方によって識別することができる。欠陥のある集積回路を識別した後に、その製造工程で製造された欠陥のある集積回路の数を削減するための措置を講じ、それによって仕様に適合する集積回路の歩留まりを向上することが望ましい。

30

【0 0 0 4】

過去においては、集積回路の芳しくない歩留まりを引き起こす欠陥の多くは、微粒子の異物または他の不定の源泉によって引き起こされた。以前にも増して、現代の集積回路工程に見られる欠陥の多くは、プロセス開発またはイールド・ランピング(yield mapping)の初期段階では特に、微粒子または不定の異物を源泉とするのではなく、非常に系統的な源泉に由来している。これらの系統的な欠陥の源泉の例には、積極的なリソグラフィ・ツールを使用することによる転写問題、不十分に形成されたケイ化物によるポリ・ストリング、駆動される密度によるゲート長の変動、および光近接効果が含まれる。

40

【0 0 0 5】

製造工程で生成される欠陥のある集積回路の数を削減し、したがって歩留まりを向上するように試みるときに、場合によっては数百もの処理ステップのうちの任意の1つまたは複数の処理ステップが、特定の回路の欠陥を引き起こした可能性があるという現実に直面す

50

る。このような多数の変数を扱う場合、特定の回路内の欠陥の正確な原因を判定することは非常に難しいことがあり、それによって、歩留まりを低下させるプロセス・オペレーションを識別し、補正することが非常に難しくなる。完成した集積回路の詳細な検査により、どのプロセス・オペレーションが回路の欠陥を引き起こした可能性があるかについてある徴候が得られることがある。しかし、検査装置はしばしば系統的な欠陥の源泉の多くを捕捉せず、かつ／またはツールは、効果的かつ確実に同調し、最適化し、または使用することが難しいことがある。さらに、特に最近の技術における検査装置は、しばしば多くの偽りの警報または妨害欠陥を受け、周知であるように、それらにより本当の欠陥または欠陥の源泉を確実に観測するためのどんな試行も妨害される。

#### 【 0 0 0 6 】

10

特定の問題を製造サイクルの完了後の最終テストで識別した後に、特定のプロセス・オペレーションでの問題が、数週間または数ヶ月早いこともある、オペレーションが実施された時間に存在したということが確認される可能性があることが一般に分かっている。したがって、問題がずっと後になって補正される可能性がある。この時点では、異なるプロセス・オペレーションにより、問題が引き起こされる可能性がある。したがって、その後では、欠陥のある集積回路の事実分析、およびこれらの欠陥のある製品を引き起こすプロセス・オペレーションの識別は、集積回路の全体的歩留まりを改善するための手段としては非常に限られたものとなる。

#### 【 0 0 0 7 】

20

事実分析の後に不具合をもたらさずに歩留まりを予測するためのいくつかの試行が行われているが、それらの成功の程度は様々である。したがって、集積回路製品の歩留まり予測のための改良型のシステムおよび方法が求められている。

#### 【 0 0 0 8 】

30

##### ( 発明の概要 )

集積回路の歩留まりを予測するためのシステムおよび方法は、最終的な集積回路製品に組み込むべき少なくとも 1 つのタイプのフィーチャ ( 特徴 : feature ) を表す少なくとも 1 つのフィーチャを組み込む、少なくとも 1 つのタイプの特徴付けビヒクル ( v e h i c l e ) を含む。この特徴付けビヒクルは、歩留まりモデルを生成するために、集積回路製品を製造する際に使用すべき製造サイクルを構成するプロセス・オペレーションのうちの少なくとも 1 つを受ける。この歩留まりモデルは、特徴付けビヒクルによって定義されるレイアウトを実施し、好ましくは、動作速度での電気的テスト・データの収集およびプロトタイプ・セクションのテストを容易にするフィーチャを含む。抽出エンジン ( 抽出装置 : e x t r a c t i o n e n g i n e ) は、提案される製品レイアウトから所定のレイアウト属性を抽出する。歩留まりモデルに対して操作して、この抽出エンジンは、レイアウト属性と、層または製造工程のステップごとの破壊に応じて歩留まり予測を生成する。次いでこれらの歩留まり予測を使用して、製造工程中のどのエリアを最も改良する必要があるかを判定する。

#### 【 0 0 0 9 】

40

##### ( 詳細な説明 )

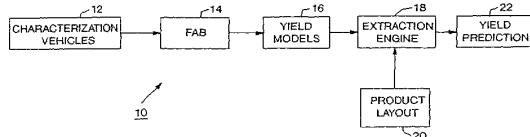

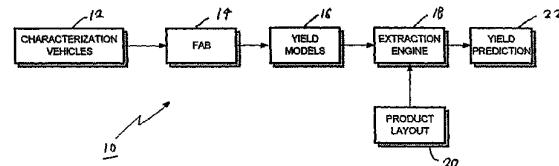

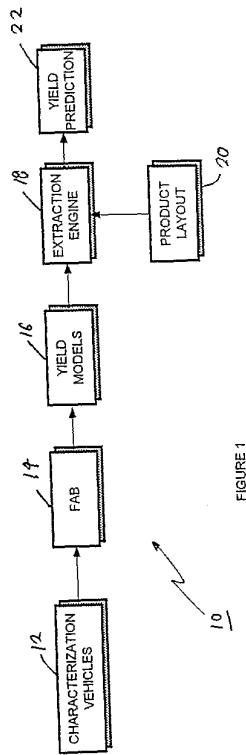

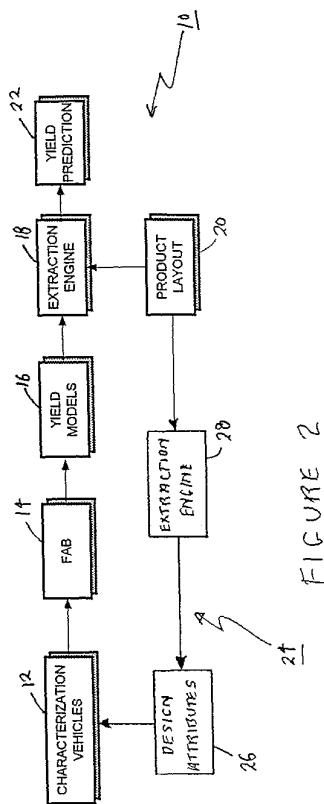

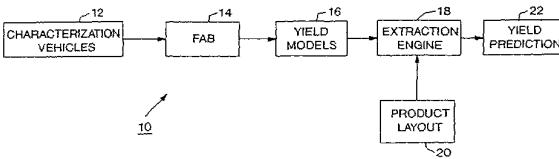

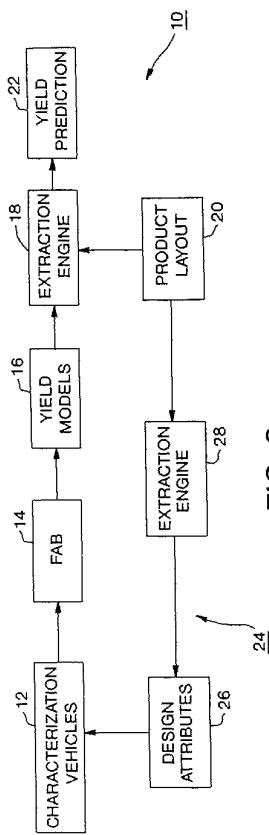

次に図 1 を参照すると、本発明に従って集積回路歩留まりを予測するために、システム 1 0 と総称するシステムによって実行されるステップを示すブロック図が示されている。システム 1 0 は、少なくとも 1 つのタイプの特徴付けビヒクル 1 2 を利用する。特徴付けビヒクル 1 2 は、最終的製品に組み込むべき少なくとも 1 つのタイプのフィーチャを表す、少なくとも 1 つの特定のフィーチャを組み込む集積回路構造を構築するのに必要な情報を含むソフトウェアの形態であることが好ましい。例えば、特徴付けビヒクル 1 2 は、考慮中のプロセス・フロー ( p r o c e s s f l o w ) の金属相互接続モジュールのヘルスおよび製造性を検出するための単一リソグラフィック層のショート・フロー ( s h o r t f l o w ) ・ テスト・ビヒクルを定義することができる。この構造は、製造中に製品に影響を与える可能性の高い様々な欠陥の取込みまたはフィンガープリント ( f i n g e r p r i n t ) の信頼性を高めることができるように十分大きくする必要があり、かつ

50

製造工程で動作する実際の製品または製品のタイプと同じくらいである必要がある。ショート・フローおよびショート・フローで実施される構造のより具体的な例および説明を以下で説明する。

#### 【0010】

ショート・フローは、集積回路製造サイクル中のプロセス・ステップの合計数の特定のサブセットを包含するものとして定義される。例えば、合計製造サイクルは450またはそれ以上のプロセス・ステップを含むことができるが、単一相互接続層の製造性を調査するために設計されるような特徴付けビヒクルは、少ない数、例えば10～25プロセス・ステップだけが含まれることになる。能動デバイスおよび複数の相互接続層は、歩留まりモデルを得るため、またはプロセス・フロー中の単一相互接続層に関連するこれらのステップに影響を与える欠陥の正確な診断を可能にするためには必要ではないからである。10

#### 【0011】

特徴付けビヒクル12は、提案される製品レイアウトの1つまたは複数の属性に一致するフィーチャを定義する。例えば、特徴付けビヒクル12は、この特定の設計タイプに影響を与え、歩留まり損失を引き起こす可能性が高い欠陥を判定するために、提案される製品レイアウトを表すフィーチャ（例えば、線サイズ、間隔、および周期性、ライン・ベンドおよびランなど）を含む部分レイアウトを有するショート・フロー・テスト・ビヒクルを定義することができる。

#### 【0012】

特徴付けビヒクル12は、デバイス性能およびプロセス・パラメータに関するレイアウト近隣のインパクトを調査するために、提案される設計の1つまたは複数の能動領域および隣接フィーチャを定義し、レイアウト属性に応じてデバイス・パラメータをモデル化し、製品性能と最良に相關するデバイスを決定することもできる。さらに、プロセス全体のすべてのモジュラ構成要素のすべての可能なサブセットまたは主要なサブセットの範囲が働くように、十分な数のショート・フロー・ビヒクルを構築し、解析することによって、製造される特定の製品に影響を与えることになる歩留まり問題のすべてではないとしても、その多くの完全な評価を明らかにし、モデル化し、および／または診断することができる。20

#### 【0013】

製造中の製品に見られる可能性の高い歩留まり問題を評価し、診断するための情報を提供することに加えて、特徴付けビヒクルは、正確な歩留まり予測のために使用できる歩留まりモデル16を生成するように設計される。これらの歩留まりモデルは、限定はしないが、製品計画と、プロセス全体にわたる歩留まり改善作業の優先順位付けと、製品自体の元の設計を変更してより良く製造できるようにすることを含む目的のために使用することができる。30

#### 【0014】

本発明で企図される特徴付けビヒクル12におけるテスト構造の大部分は、電気的テスト用に設計される。この目的で、各特徴付けビヒクルによって評価される、モジュール内の故障および欠陥を検出する信頼性は非常に高い。検査装置は、この高度な信頼性を達成し、または保証することができない。さらに、電気的テストが高速かつ安価であるので、データ収集の速度および量は、それぞれ非常に高速であり、大きい。このようにして、統計的に有意な診断および／または歩留まりモデルを実現することができる。40

#### 【0015】

好ましくは、特徴付けビヒクル12は、テープまたはディスク上のGDS2レイアウトの形態であり、次いでそれを使用してレチクル・セット（reticle set）が生成される。レチクル・セットが製造サイクル14の選択した部分の間で使用され、歩留まりモデル16が生成される。したがって、歩留まりモデル16は、特徴付けビヒクル12によって定義されるレチクル・セットを使用する、選択した製造プロセス・ステップを受けたウェハの少なくとも一部から測定されるデータから構築されることが好ましい。

#### 【0016】

10

30

40

50

歩留まりモデル 16 は、特徴付けビヒクルによって定義されるレイアウトを実施するだけでなく、製造プロセス・オペレーション自体によって導入されたアーチファクトも含む。歩留まりモデル 16 は、プロトタイプ・アーキテクチャおよびレイアウト・パターン、ならびに動作速度での電気的テスト・データおよびテスト・プロトタイプ・セクション収集を容易にするフィーチャも含むことができる。これにより、歩留まり予測の正確さおよび信頼性が改善される。

## 【 0 0 1 7 】

抽出エンジン（抽出装置）18 は、提案される製品レイアウト 20 からレイアウト属性を抽出し、この情報を歩留まりモデル 16 に接続して製品歩留まり予測 22 を得るためのツールである。このようなレイアウト属性は、例えばバイア冗長度（v i a r e d u n d a n c y）、臨界エリア、正味長さ分布、および線幅／スペース分布を含むことができる。次いで、提案される製品レイアウト 20 からのレイアウト属性と、特徴付けビヒクル 12 からの情報に基づいて製造された歩留まりモデル 16 からのデータが与えられた場合、製品歩留まり 22 が予測される。本発明のシステムおよび方法を使用して、得ることのできる予測可能な製品歩留まりは、定義された各属性、機能ブロックまたは層と関連する歩留まりとすることができます、あるいは製品レイアウト全体に関して結果として得られる歩留まり予測とすることができます。

## 【 0 0 1 8 】

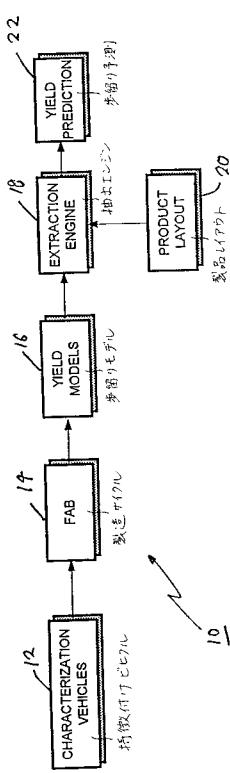

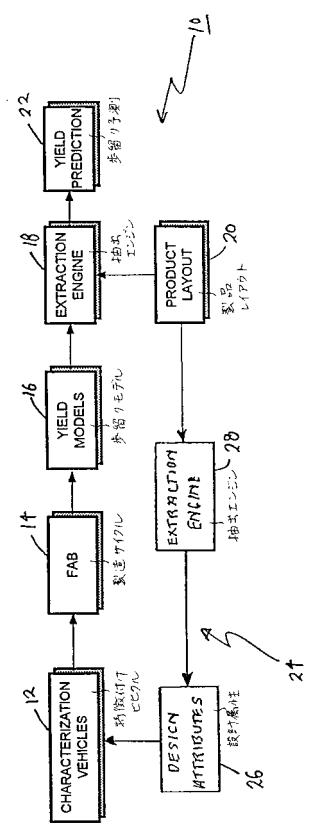

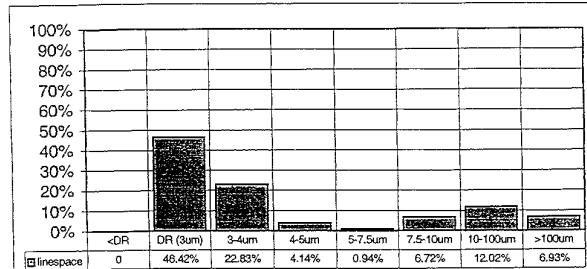

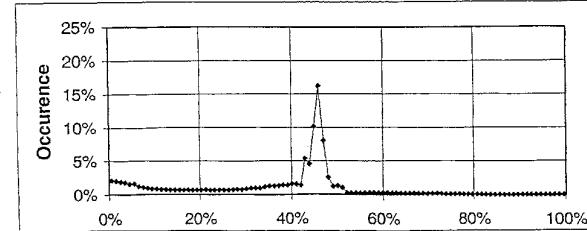

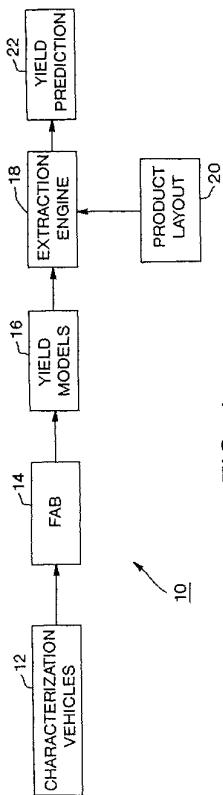

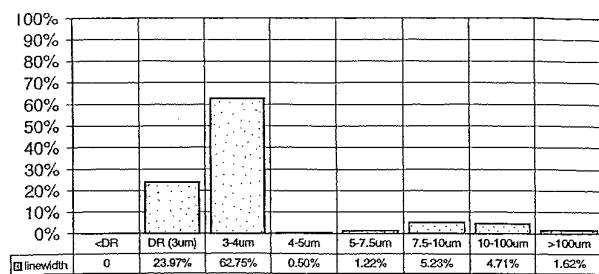

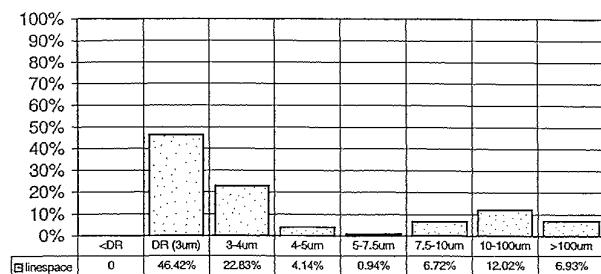

次に図 2 を参照すると、抽出エンジン 28 によって製品レイアウト 20 から設計属性 26 を抽出するための、フィードバック・ループ 24 と総称するフィードバック・ループを追加で備える、本発明による集積回路歩留まり 10 を予測するためのシステムのブロック図が示されている。本発明のこの特徴によれば、特徴付けビヒクル 12 は、製品レイアウト 20 の属性を使用して開発される。この場合、製品レイアウトの属性が抽出され、属性の範囲が特徴付けビヒクル 12 中に確実に含まれるようにされる。例えば製品レイアウトが解析されて、線スペース分布、幅分布、密度分布、アイランド・パターンの数が決定され、実質上、製造工程の設計規則のセット全体のサブセットが開発される。このサブセットは、考慮中の特定の製品レイアウトに応用可能である。パターンに関しては、製品レイアウト分析により、最も共通するパターンが決定され、2 番目に共通するパターンが決定され、以下同様である。これらは、抽出エンジン 28 によって抽出され、特徴付けビヒクル 12 中に含めるために、これらのパターンのすべてを包含する設計属性 26 が生み出される。密度に関しては、製品レイアウトの分析により、最初の金属の密度が 10 % ~ 50 % であることが明らかとなった場合、特徴付けビヒクルは、最初の金属についての幅全体の 10 % ~ 50 % を含むことになる。

## 【 0 0 1 9 】

1 つのタイプの特徴付けビヒクルは、金属ショート・フロー・特徴付けビヒクルである。金属ショート・フロー・特徴付けビヒクルの目的は、単一相互接続層の転写性および製造性を定量化することである。高い製品歩留まりのために重要である金属歩留まりは、しばしば得ることが非常に難しく、かつ、いくつかの独立な処理ステップだけからなるので、通常、金属ショート・フロー はプロセスの非常に初期に実行される。金属ショート・フロー・マスクを使用するショート・フロー 実験を実施することにより、迅速かつ連続的に実験および分析を実施することが可能となり、完全なフロー・ランが完了するまで待機する必要なく検出される、どんな系統的歩留まり問題または不定の欠陥歩留まり問題もなくなり、または最小となる。

## 【 0 0 2 0 】

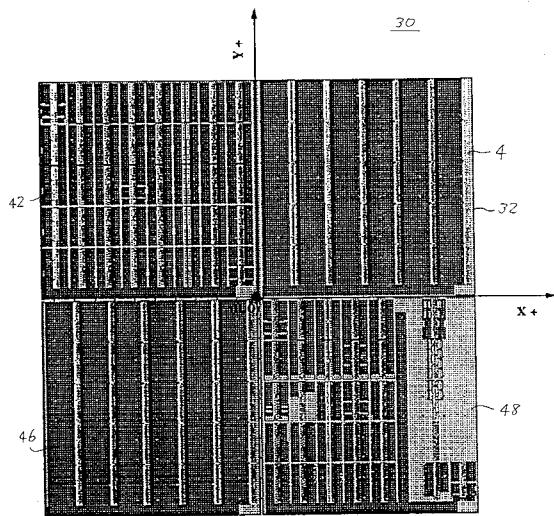

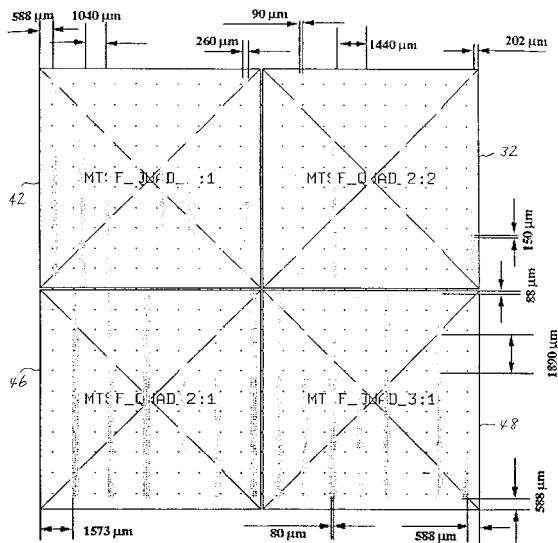

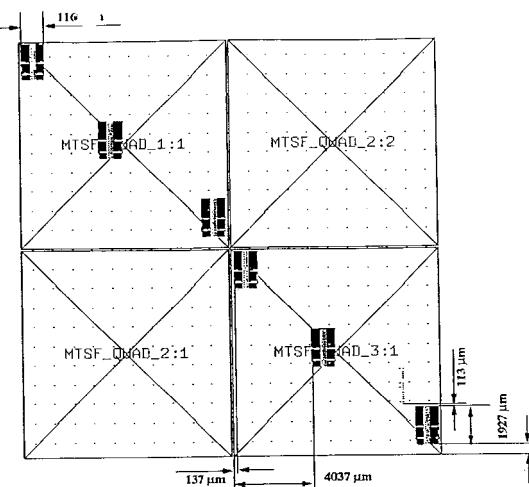

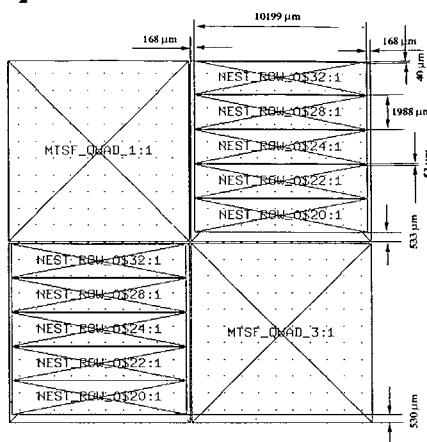

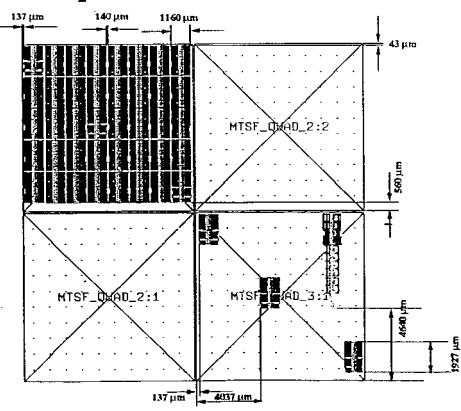

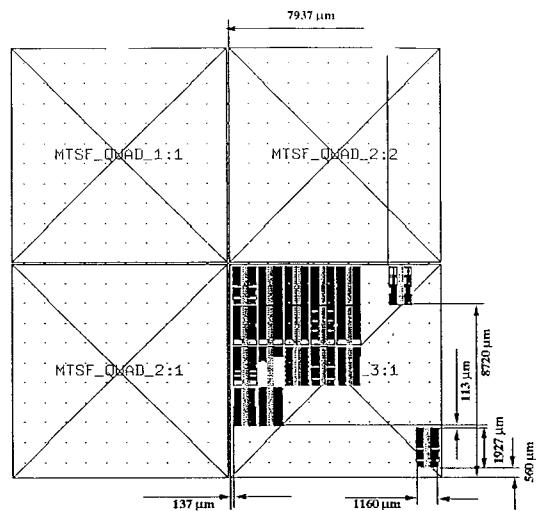

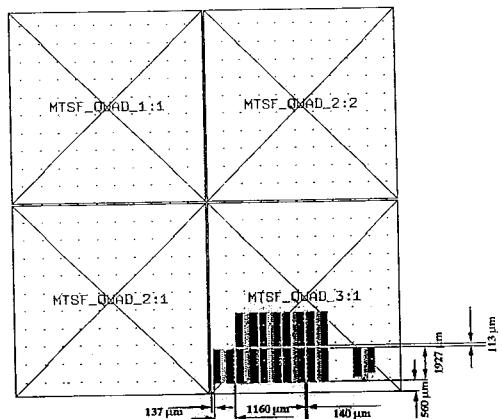

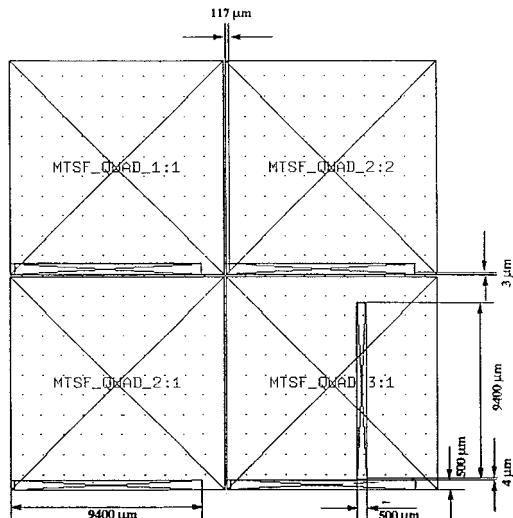

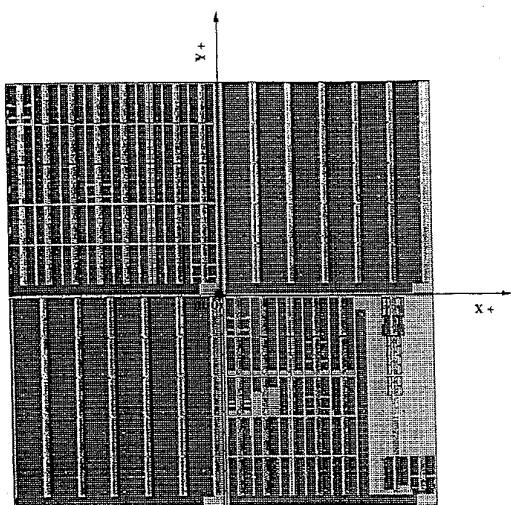

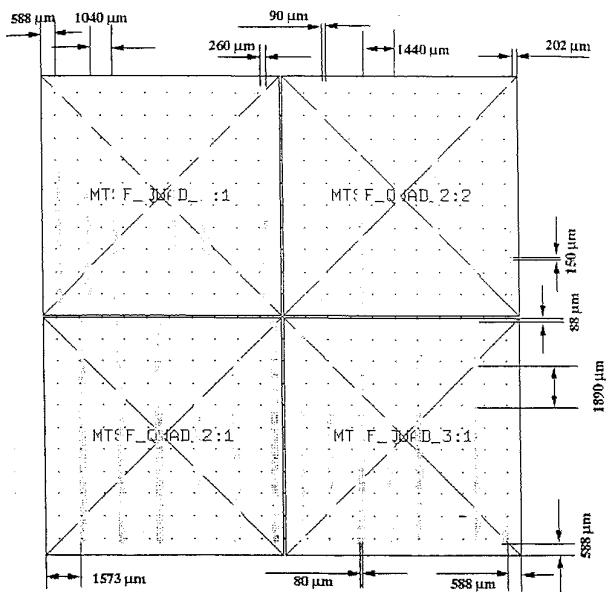

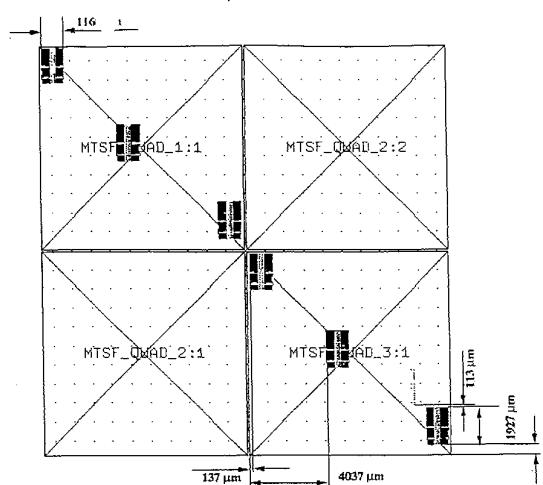

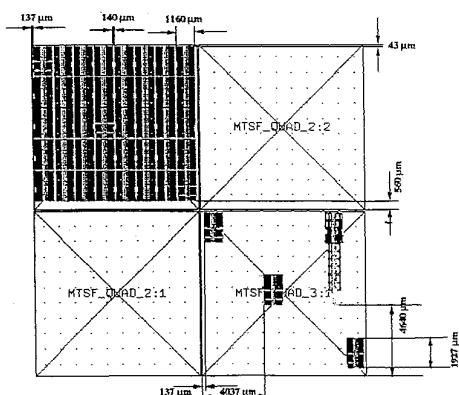

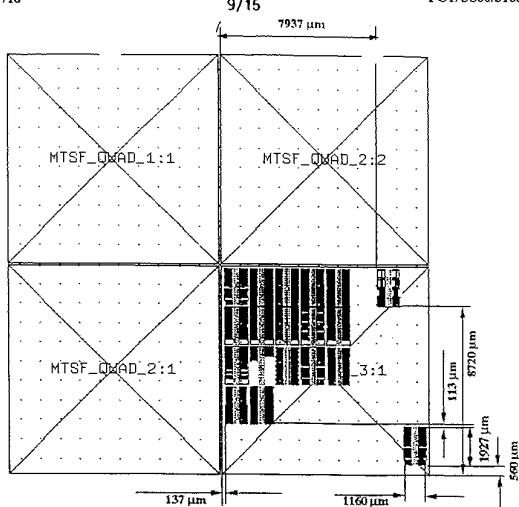

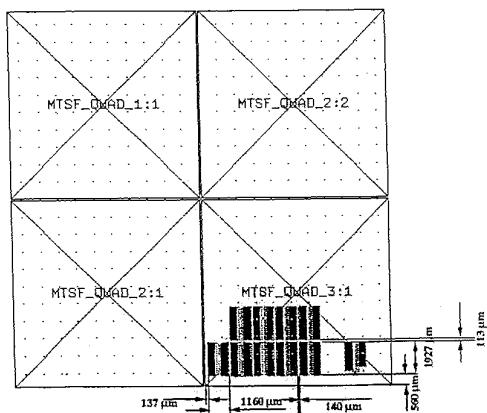

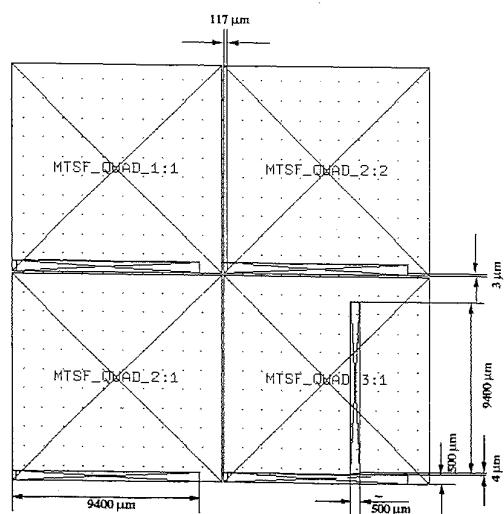

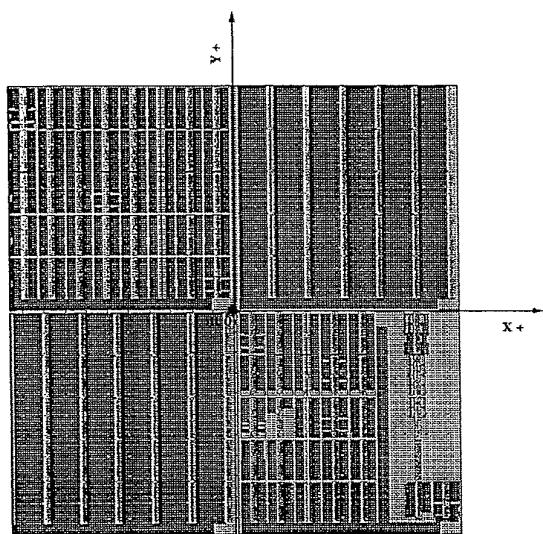

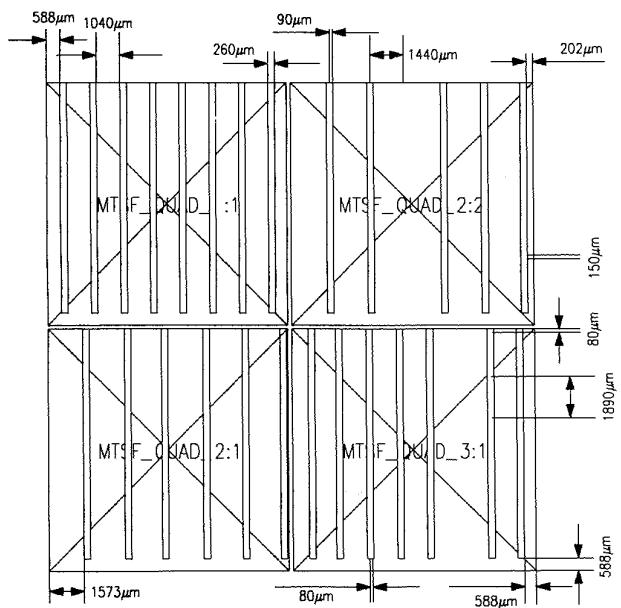

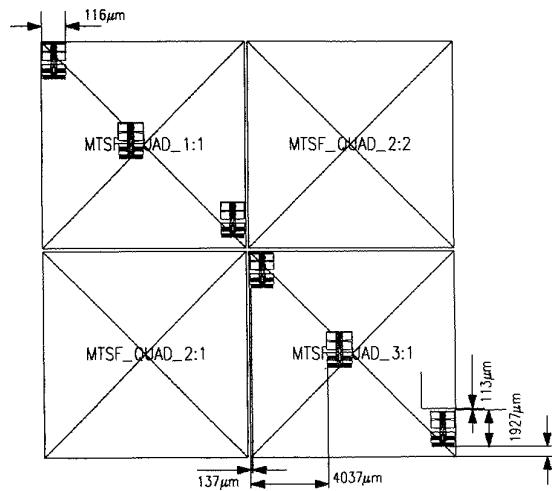

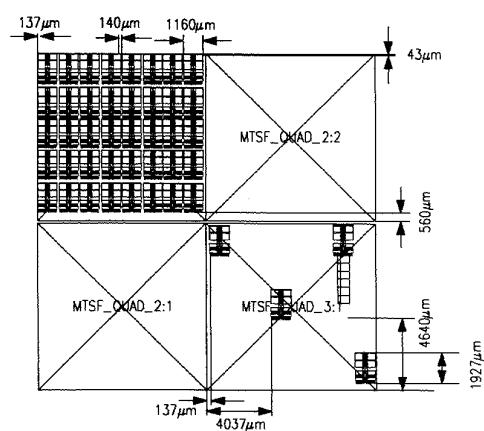

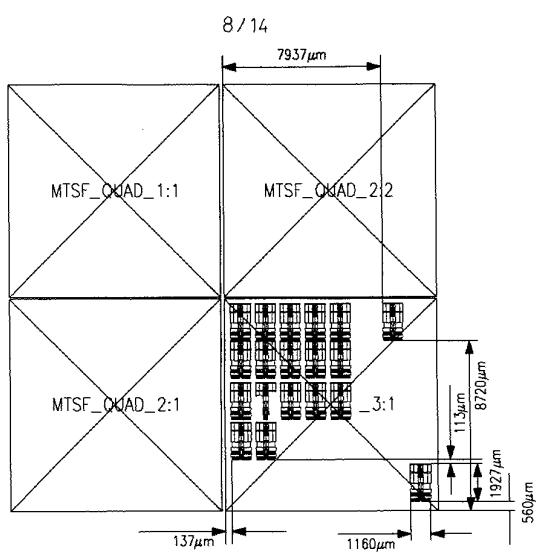

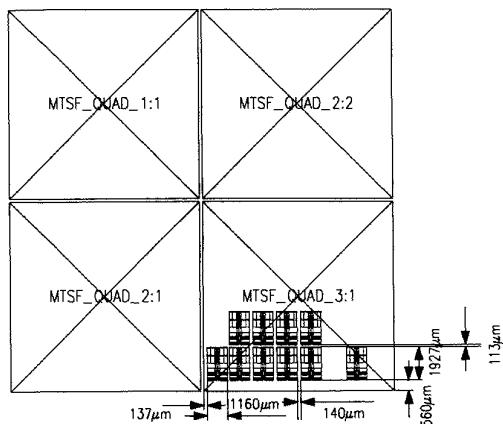

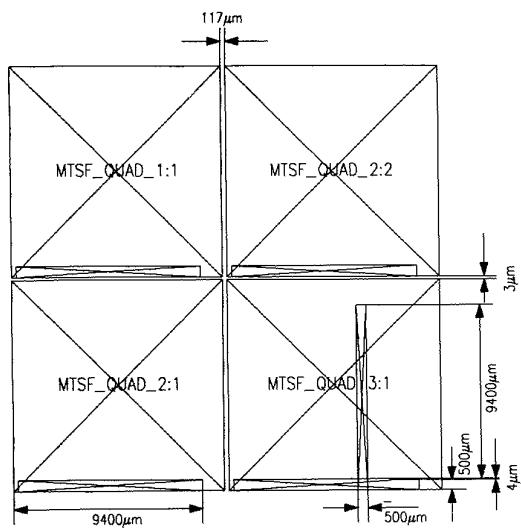

図 3 を参照すると、一般的に 30 で示された単一のリソグラフィック層からなる通常の金属ショート・フロー・マスクの例の画像が示されている。マスク 30 はチップ上の単一の金属層を画定するために使用され、図 3 に示す例示のチップ 32 はこの例では約 22 mm × 22 mm のサイズであるステッパーが収容できる大きさである。このチップは図 4 に示す 4 つの象限 42、44、46 および 48 に分割され、前記各象限は以下の 6 つの基本構造の 1 つまたはそれ以上を含む。すなわち、(i) ケルビン金属臨界寸法構造（K e l v i n

10

20

30

40

50

metal critical dimension structure)、(ii) スネークおよびコーム構造(snake and comb structure)、(iii) ネスト欠陥サイズ分布構造(nest defect size distribution structure)、(iv) ファン・デル・ポー構造(Van der Pauw structure)、(v) OPC評価構造(OPC evaluation structure)、(vi) 古典的走査型電子顕微鏡(SEM)構造(classical scanning electron microscopy(SEM) structure)である。

## 【0021】

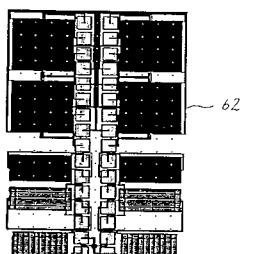

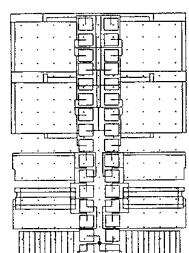

チップ・エリアの約50%が欠陥サイズ分布の抽出のためのネスト構造に使用され、チップ・エリアの40%が系統的な歩留まり損失機構の検出とパラメータ変動の測定に使用されている。図3はまたチップ上のパッド・フレーム34のロケーションを示す。本明細書に記載する実施形態では、図5に示すように、チップ・カードプロセス上に131のパッド・フレームがあり、各パッド・フレーム34は32のパッドを含む。各パッド・フレーム34内のパッドは後述する試験プログラムの必要に応じて外部試験装置が接触する電機接続点を提供する。

## 【0022】

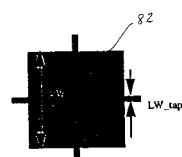

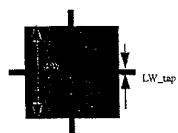

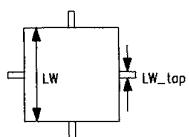

このチップで使用するファン・デル・ポー構造82(図8参照)は構造の対称性を利用してシート抵抗を直接測定する4端子の正方形構造である。シート抵抗の高精度の判定は線幅変動の測定の要件である。ファン・デル・ポー構造82は2つの異なるフレーム・タイプ、すなわち、混載フレーム62(図6A参照)とVDP1 64(図6B参照)とに配置されている。図7は本明細書に記載する例示の金属ショート・フロー・チップ内のファン・デル・ポー構造を含むパッド・フレーム72のロケーションを示す。この例示のチップ内では、ファン・デル・ポー構造はチップ面積の1%未満しか占有しない。ファン・デル・ポー構造内では、線幅(LW)とLWタップ(図8参照)とは変動するパラメータである。テーブル1は本明細書に記載する例示の金属ショート・フロー・チップ内のファン・デル・ポー構造の変動を示す。

## 【0023】

## 【表1】

テーブル1 (TABLE I)

| LW(μm) | LW <sup>タップ</sup> (μm) |

|--------|------------------------|

| 1(DR)  | 1(DR)                  |

| 1.1    | 1.1                    |

| 5      | 1                      |

| 10     | 2                      |

| 25     | 5                      |

| 35     | 7                      |

| 35     | 3.5                    |

| 50     | 5                      |

## 【0024】

ネスト検出サイズ分布構造はオープンおよびショート検出と欠陥サイズ分布用に設計された入れ子式の連続的な線のアレイである。線幅と線間距離は欠陥サイズ分布の検出を容易

10

20

30

40

50

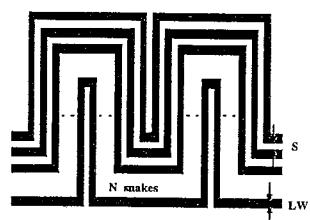

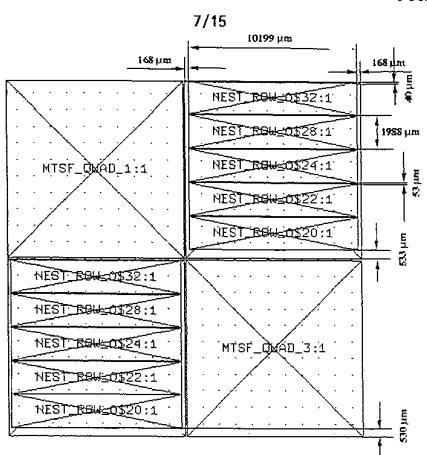

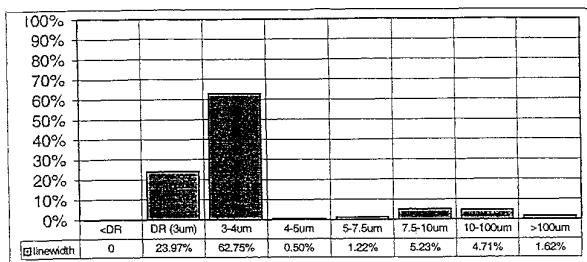

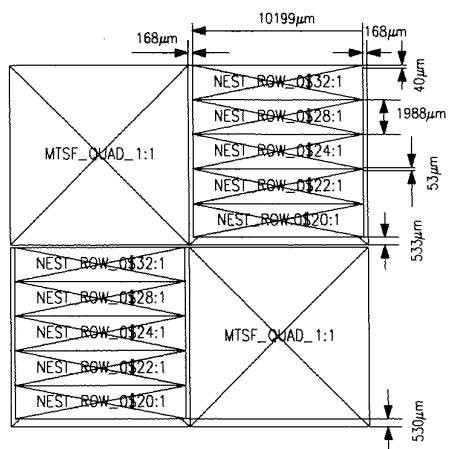

にするために変動するパラメータである。本明細書に記載する実施形態では、これらの構造は図9に示すロケーション9.2および9.4でチップ面積の50%を占め、総計10個のセル9.6内に14の変種を有する。これらの構造が占有できるエリアの量はウェーハあたり0.25個以内の欠陥を高精度に検出できる大きさがなくてはならない。変種の数は通常、設計規則(DR)、DRよりやや下、DRよりやや上、DRよりほぼ上を含む。したがって、例えば、DRが線間距離で10μmの場合、プロットはテーブル2に示すように0.9、1.1、1.3および2.5についてである。

【0025】

【表2】

テーブル2(TABLE II)

| 線幅 = 線間距離 | Line Width = Space (μm) | Length 長さ (cm) |

|-----------|-------------------------|----------------|

|           | 0.9                     | 39.6           |

|           | 1.0 (DR)                | 36             |

|           | 1.1                     | 33             |

|           | 1.3                     | 28.2           |

|           | 2.5                     | 24.6           |

10

20

30

40

【0026】

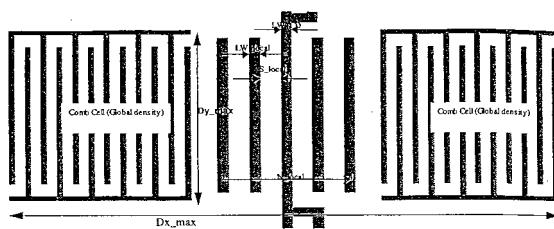

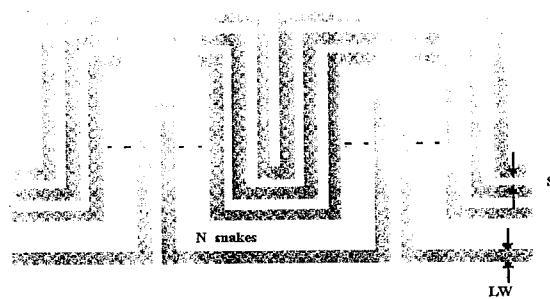

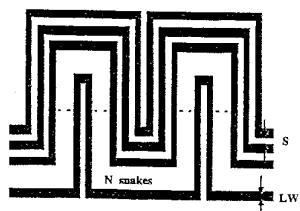

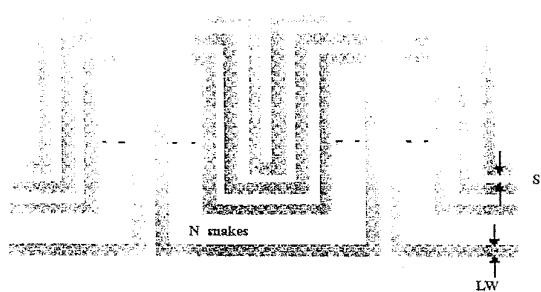

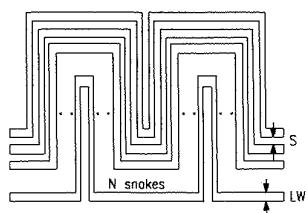

各セルは6つのサブセルに分割され、線抵抗を合理的なレベル(250k未満)に低減し、セルあたりの多数の欠陥の発生を最小限にする。この実施形態では、セル当たり16個のスネークがある。一般的に1002で示す例示のネスト欠陥サイズ分布構造自体も図10に示されている。ネスト欠陥サイズ分布構造は線幅(LW)が線間距離(S)に等しく、その後のデータ解析が容易になるように設計されている。

【0027】

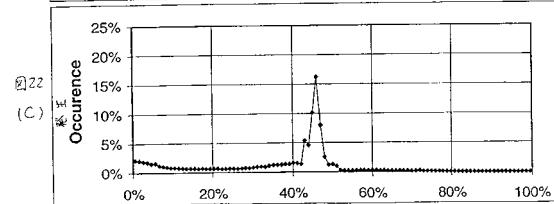

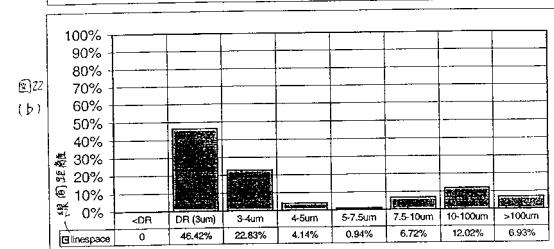

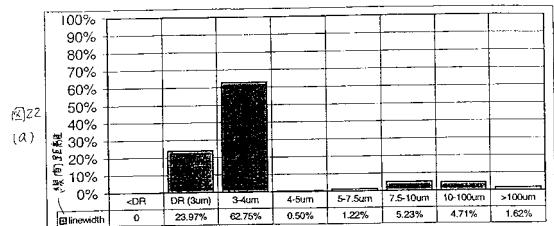

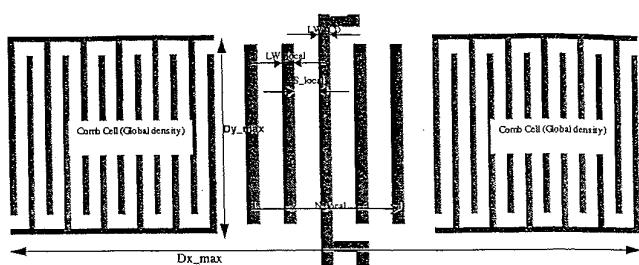

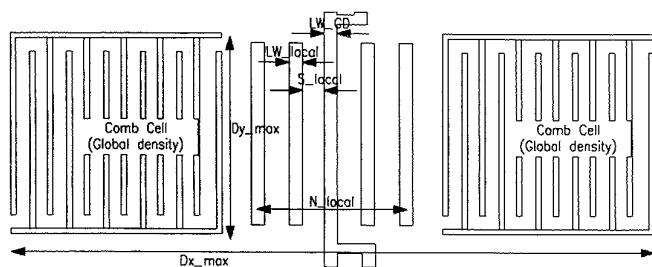

ケルビン金属臨界寸法(CD)構造は各端部で成端される連続的な直線からなる。これらの構造はファン・デル・ポー構造から決定されるシート抵抗に関連してケルビン線幅の決定が可能な高精度の線抵抗測定を可能にする。これらの構造は第1に電気的臨界寸法の変動を決定するために設計されている。一般的に110で示す例示のケルビン臨界寸法構造を図11に示す。電気的臨界寸法変動可能性の光近接効果のインパクトを研究するため、ローカル近隣構造が変動する。ローカル近隣で変動するパラメータは線の番号112、線幅114、線間距離116である。ケルビン構造周辺の大域環境118も変動してまず電気的臨界寸法へのエッティング関連効果が研究される(図11参照)。大域近隣(globa1neighborhood)で変動するパラメータは集積度とエリアである。大域近隣構造は他の電気的測定のニーズにも応えることができる。例えば、これらの構造の歩留まりを測定して環境に応じた金属臨界寸法だけでなく環境の関数としての歩留まりが得られる。図12は本明細書に記載する金属ショート・フロー・チップ内のケルビン構造のロケーションを示す。これらのロケーションは使用可能なエリアを占有するように選択されている。テーブル3~9は本明細書に記載する金属ショート・フロー・チップ内のケルビン構造の変動を説明する。これらの値は図22(a)~22(b)で識別したスペースを占有するように選択されている。例えば、パターン集積度は45%付近に集中し、線幅と線間距離は1.0~3.3μmの範囲内にある。これは例示の製品レイアウトの大半で集中する数字であるからである。

【0028】

【表3】

50

| テ-ブ"レ3 (TABLE III) |          |        |                              |

|--------------------|----------|--------|------------------------------|

| 線幅 (μm)            | 距離 (μm)  | ローカル線数 | 固定パラメータ                      |

| 0.75               | 0.75     | 6      | Local line width = 1μm       |

| 0.9                | 0.9      | ローカル線幅 | Density = 45%                |

| 1μm (DR)           | 1.0 (DR) | 集積度    | Line width of comb = 1.3μm   |

| 1.1                | 1.1      | コームの線幅 | Dx <sub>max</sub> = 400 (μm) |

| 1.3                | 1.3      |        | Dy <sub>max</sub> = 400 (μm) |

| 2.5                | 2.5      |        |                              |

| 3.3                | 3.0      |        |                              |

| 10                 | 3.3      |        |                              |

|                    | 10       |        |                              |

|                    | 50       |        |                              |

10

20

【0029】

【表4】

| テ-ブ"レ4 (TABLE IV) |        |        |                              |

|-------------------|--------|--------|------------------------------|

| 線幅 (μm)           | 距離比    | ローカル線数 | 固定パラメータ                      |

| 0.75              | 2 to 1 | 6      | Local line width = 1μm       |

| 0.9               | 3 to 1 | 2      | Density = 45%                |

| 1 (DR)            |        | ローカル線幅 | Line width of comb = 1.3μm   |

| 1.1               |        | 集積度    | Dx <sub>max</sub> = 400 (μm) |

| 1.3               |        | コームの線幅 | Dy <sub>max</sub> = 400 (μm) |

| 2.5               |        |        |                              |

| 3.3               |        |        |                              |

| 10                |        |        |                              |

30

【0030】

【表5】

| TABLE V                         |                          |                                       |                              |                                          |

|---------------------------------|--------------------------|---------------------------------------|------------------------------|------------------------------------------|

| Line Width<br>( $\mu\text{m}$ ) | Number of<br>Local lines | Local Line<br>Width ( $\mu\text{m}$ ) | Spacing<br>( $\mu\text{m}$ ) | Fixed Parameters                         |

| 0.75                            | 1                        | 1 (DR)                                | 1 (DR)                       | Density = 0.45                           |

| 0.9                             | 2                        | 1.3                                   | 1.3                          | Line width of comb = 1.3 $\mu\text{m}$   |

| 1 (DR)                          | 4                        |                                       | 集積度                          | Dx <sup>最大</sup> = 400 ( $\mu\text{m}$ ) |

| 1.1                             |                          |                                       | コームの線幅                       | Dy <sup>最大</sup> = 400 ( $\mu\text{m}$ ) |

| 1.3                             |                          |                                       |                              |                                          |

| 2.5                             |                          |                                       |                              |                                          |

| 3.3                             |                          |                                       |                              |                                          |

| 10                              |                          |                                       |                              |                                          |

10

20

30

【0031】

【表6】

| TABLE VI                        |                              |                          |                |                              |                                          |

|---------------------------------|------------------------------|--------------------------|----------------|------------------------------|------------------------------------------|

| Line Width<br>( $\mu\text{m}$ ) | Spacing<br>( $\mu\text{m}$ ) | Number of<br>local lines | Density<br>集積度 | LW comb<br>( $\mu\text{m}$ ) | Fixed Parameters                         |

| 1.0 (DR)                        | 1.0 (DR)                     | 6                        | 0              | 1.3                          | Dx <sup>最大</sup> = 400 ( $\mu\text{m}$ ) |

| 1.3                             | 1.3                          | 2                        | 0.2            | 10                           | Dy <sup>最大</sup> = 400 ( $\mu\text{m}$ ) |

|                                 |                              |                          | 0.40           |                              |                                          |

|                                 |                              |                          | 0.45           |                              |                                          |

|                                 |                              |                          | 0.50           |                              |                                          |

【0032】

【表7】

| TABLE VII                    |                           |                                    |                                          |

|------------------------------|---------------------------|------------------------------------|------------------------------------------|

| Line Width ( $\mu\text{m}$ ) | Spacing ( $\mu\text{m}$ ) | Line width local ( $\mu\text{m}$ ) | Fixed Parameters                         |

| 0.9                          | 1.0 (DR)                  | 10                                 | Number of local lines 2                  |

| 1.0 (DR)                     | 1.1                       | 30                                 | Density 0.45                             |

| 1.1                          | 1.3                       | 100                                | Line width comb 1.3                      |

| 1.3                          | 2.5                       | ローカル線幅                             | Dx <sup>最大</sup> = 400 ( $\mu\text{m}$ ) |

| 2.5                          | 3.3                       | 集積度                                | Dy <sup>最大</sup> = 400 ( $\mu\text{m}$ ) |

| 3.3                          | 10                        | コームの線幅                             |                                          |

| 10                           |                           |                                    |                                          |

40

【0033】

【表8】

(線幅) (距離)

TABLE VIII

| Line Width<br>( $\mu\text{m}$ ) | Spacing<br>( $\mu\text{m}$ ) | Fixed Parameters<br>固定パラメータ                      |

|---------------------------------|------------------------------|--------------------------------------------------|

| 1.0 (DR)                        | 1.0 (DR)                     | Number of local lines 6 口一ガル 線数 6                |

| 1.1                             | 1.1                          | Density - 0.45 集積度 - 0.45                        |

| 1.3                             | 1.3                          | Line width comb 1.3 コーナの線幅                       |

| 2.5                             | 2.5                          | $Dx_{\text{max}}^{\text{最大}} = 400(\mu\text{m})$ |

| 10                              | 3.0                          | $Dy_{\text{max}}^{\text{最大}} = 400(\mu\text{m})$ |

|                                 | 5.3                          | Line width local 1.3 口一ガル 線幅 1.3                 |

【 0 0 3 4 】

【表 9】

| テーブル9 (TABLE IX) |              |               |        | 固定パラメータ                                                                                                                                                                                                               | コメント                                                 |

|------------------|--------------|---------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 線幅               | 距離           | ローカル集積度       | 最大     |                                                                                                                                                                                                                       |                                                      |

| Line Width (μm)  | Spacing (μm) | Local density | Dx_max | Number of local lines 0<br>ローカル線数<br>Density 0<br>集積度<br>Line width comb 0<br>コームの線幅<br>Line width local 0<br>ローカル線幅<br>Dx_max = 400(μm)                                                                              | Isolated Kelvins<br>隔離ケルビン<br>10                     |

| 0.75             |              |               |        |                                                                                                                                                                                                                       |                                                      |

| 0.9              |              |               |        |                                                                                                                                                                                                                       |                                                      |

| 1.0 (DR)         |              |               |        |                                                                                                                                                                                                                       |                                                      |

| 1.1              |              |               |        |                                                                                                                                                                                                                       |                                                      |

| 1.3              |              |               |        |                                                                                                                                                                                                                       |                                                      |

| 2.5              |              |               | 最大     |                                                                                                                                                                                                                       |                                                      |

| 3.3              |              |               |        |                                                                                                                                                                                                                       |                                                      |

| 10               |              |               |        |                                                                                                                                                                                                                       |                                                      |

|                  | 10           | 2.5           |        |                                                                                                                                                                                                                       |                                                      |

|                  | 20           | 3.5           |        | Line width = 1.0.(μm)<br>線幅<br>Local line width = 1.0<br>(μm) ローカル線幅<br>Number of local lines 2<br>ローカル線数<br>Density 0.45<br>集積度<br>Comb line width 1.3<br>コーム線幅<br>Dx_max = 400(μm)<br>最大<br>Dy_max = 400 (μm)<br>最大 | Local<br>neighborhood<br>size<br>ローカル近隣<br>サイズ       |

|                  | 30           | 4.5           |        |                                                                                                                                                                                                                       |                                                      |

|                  | 40           | 5.5           |        |                                                                                                                                                                                                                       |                                                      |

|                  | 50           | 6.5           |        |                                                                                                                                                                                                                       |                                                      |

|                  | 60           | 7.5           |        |                                                                                                                                                                                                                       |                                                      |

|                  | 70           | 8.5           |        |                                                                                                                                                                                                                       |                                                      |

|                  | 80           | 9.5           |        |                                                                                                                                                                                                                       |                                                      |

|                  |              |               | 25     |                                                                                                                                                                                                                       |                                                      |

|                  |              |               | 50     | Line width 1.0<br>線幅<br>Line width local 1.0<br>ローカル線幅<br>Space 1.0<br>距離<br>Number of local lines 6<br>ローカル線数<br>Density 0.45<br>集積度<br>Line width comb 1.3<br>コームの線幅<br>Dy_max 400 (μm)                             | Global<br>neighborhood<br>size<br>大域近隣サイズ<br>固定パラメータ |

|                  |              |               | 100    |                                                                                                                                                                                                                       |                                                      |

|                  |              |               | 150    |                                                                                                                                                                                                                       |                                                      |

|                  |              |               | 200    |                                                                                                                                                                                                                       |                                                      |

|                  |              |               | 250    |                                                                                                                                                                                                                       |                                                      |

|                  |              |               | 300    |                                                                                                                                                                                                                       |                                                      |

| 線幅               | 距離           | N_ローカル        |        | Fixed Parameters                                                                                                                                                                                                      | Comments                                             |

| Line Width       | Spacing      | N_local       | Dx_max | D_local 5<br>D_ローカル<br>Line width comb 1.3<br>コーム線幅<br>0.45                                                                                                                                                           | Standards<br>標準                                      |

| 1.0 (DR)         | 1.0 (DR)     | 6             | 最大     |                                                                                                                                                                                                                       |                                                      |

| 1.3              | 1.3          | 6             |        |                                                                                                                                                                                                                       |                                                      |

| 1.0              | 40           | 2             |        |                                                                                                                                                                                                                       |                                                      |

| 1.3              | 40           | 2             |        |                                                                                                                                                                                                                       |                                                      |

## 【0035】

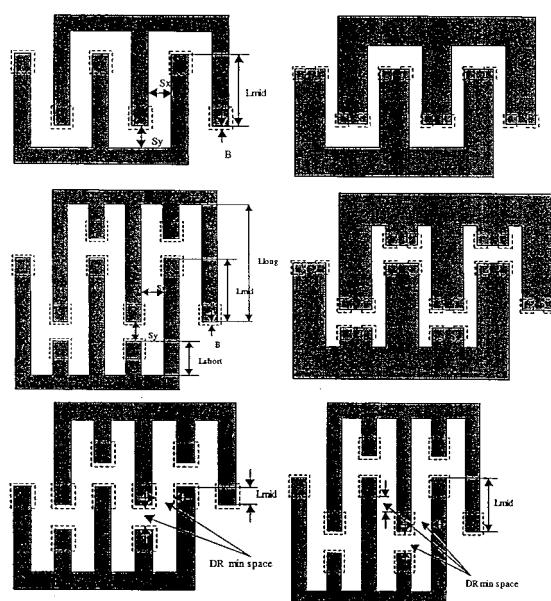

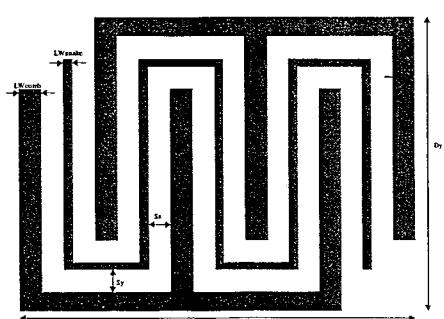

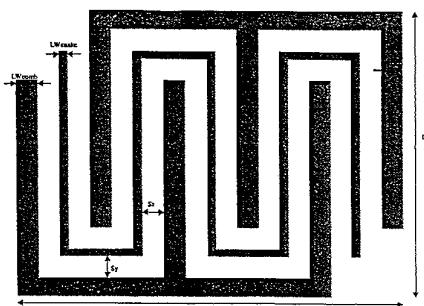

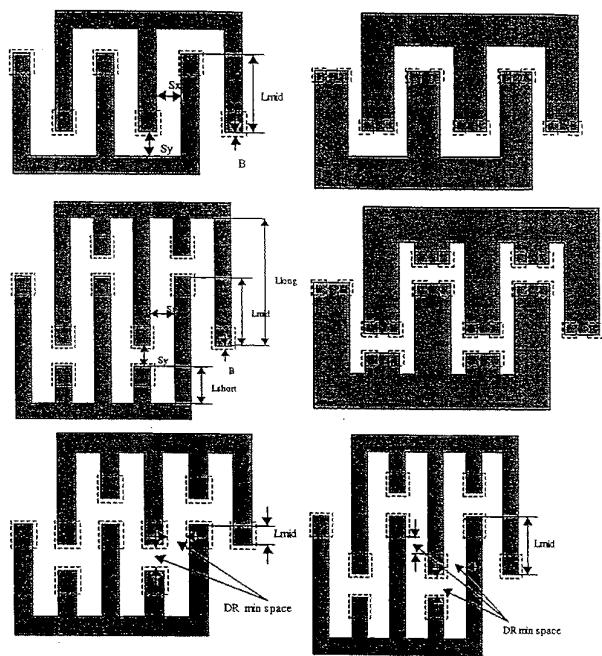

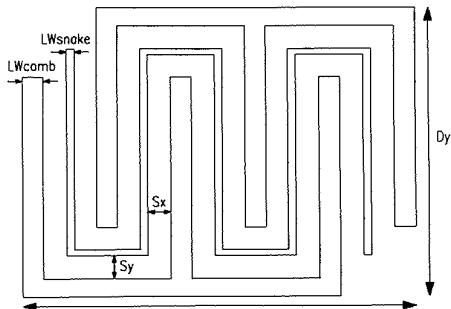

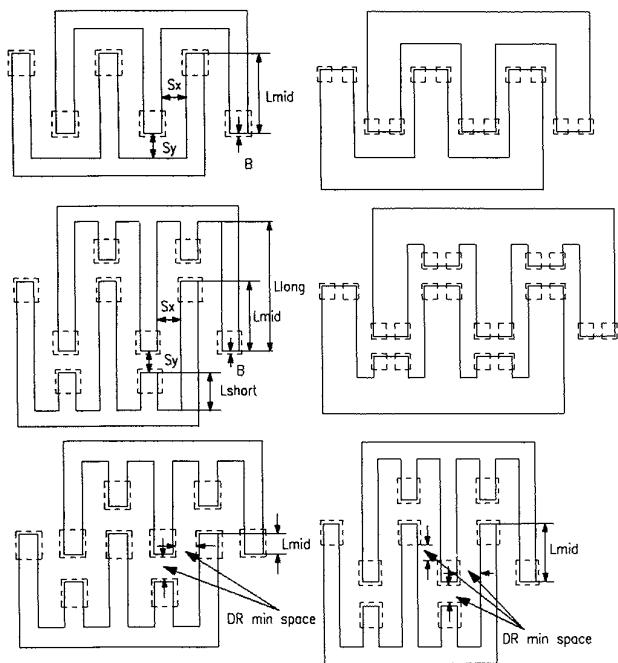

スネーク、コームおよびスネーク & コーム構造は主として各種パターンについてショートおよびオープンを検出するために設計されている。スネークは主としてオープンの検出に使用され、抵抗値の変動のモニタにも使用できる。コームはショートの検出に使用される。ショートおよびオープンは基本的な歩留まり損失機構であり、両方とも最小限にして高い製品歩留まりを得る必要がある。図13は本明細書に記載する金属ショート・フロー・チップ内のスネークおよびコーム1302のロケーションを示す。象限1 1304も例えば図14に示すケルビン構造内に入れ子になっているスネーク1402およびコーム1404を含む。図14に示す線幅(LW)および線間距離(S)はショートおよびオープンに与えるインパクトを研究するためのこれらの構造上で変動するパラメータである。テーブル10～13は本明細書に記載する金属ショート・フロー・チップ内で使用されるスネークおよびコーム構造の変動を説明する。さらに、各パラメータは線幅、線間距離および集積度が占めるスペースが図22(a)～22(c)に示す例示の製品レイアウトのそれと同様になるように選択されている。

## 【0036】

10

20

30

40

50

【表10】

テ-7"ル10(TABLE X)

| LW_コ-4)      | 距離         | LW_スネ-1)      | 固定パラメータ               |

|--------------|------------|---------------|-----------------------|

| LW_comb (μm) | Space (μm) | LW_snake (μm) | Fixed Parameters      |

| 20           | 0.9        | 1.0 (DR)      | Dx_max = 200 μm<br>最大 |

| 50           | 1.0 (DR)   |               | Dy_max = 400 μm<br>最大 |

| 100          | 1.1        |               |                       |

| 200          | 1.3        |               |                       |

| 300          | 2.5        |               |                       |

|              | 3.0        |               |                       |

|              | 3.3        |               |                       |

|              | 10         |               |                       |

| 20           | 1.3        | 1.3           |                       |

| 50           | 3.1        |               |                       |

| 100          | 3.3        |               |                       |

| 200          | 3.5        |               |                       |

| 300          | 10         |               |                       |

10

20

【0037】

【表11】

テ-7"ル11(TABLE XI)

| LW_コ-4)      | 距離         | 固定パラメータ               |

|--------------|------------|-----------------------|

| LW_comb (μm) | Space (μm) | Fixed Parameters      |

| 0.75         | 0.75       | Dx_max = 200 μm<br>最大 |

| 0.9          | 0.9        | Dy_max = 400 μm<br>最大 |

| 1.0 (DR)     | 1.0 (DR)   |                       |

| 1.1          | 1.1        |                       |

| 1.3          | 1.2        |                       |

| 2.0          | 1.3        |                       |

| 3.3          | 2.5        |                       |

| 10           | 3.0        |                       |

|              | 3.3        |                       |

|              | 10         |                       |

30

40

【0038】

【表12】

## テーブル12(TABLE XII)

| 線幅              | Fixed Parameters 固定パラメータ |

|-----------------|--------------------------|

| Line Width (μm) |                          |

| 0.75            | Dx_max = 200 μm          |

| 0.9             | Dy_max = 400 μm          |

| 1.0 (DR)        | 10 μm                    |

| 1.1             |                          |

| 1.3             |                          |

| 2.5             |                          |

| 3.3             |                          |

| 1.0             |                          |

10

20

30

40

50

【0039】

【表13】

## テーブル13(TABLE XIII)

| LW (μm) | 距離       | Fixed Parameters 固定パラメータ |

|---------|----------|--------------------------|

|         | 0.7      |                          |

| 20      |          | Dx_max = 400 μm          |

| 50      | 1.0 (DR) | Dy_max = 200 μm          |

| 100     | 1.1      | 最大                       |

| 200     | 1.3      |                          |

| 500     | 2.5      |                          |

|         | 2.7      |                          |

|         | 3.0      |                          |

|         | 3.3      |                          |

|         | 5        |                          |

|         | 10       |                          |

【0040】

ボーダおよびフリンジ構造はショートに与える光近接補正(OPC)構造のインパクトを研究するために設計されている。これらの光近接補正は普通バイア歩留まりを向上させるために追加される。ただし、これらのボーダがある、またはない金属ショート歩留まりを検査してショート歩留まりへの悪影響はないという確証が得られる。ボーダ1502は、図15に示すように、両方共一般的に1504で示すコーム構造内のコーム線端部に配置される。図16は本明細書に記載する金属ショート・フロー・チップ内の一般的に1602で示すボーダ構造のロケーションを示す。

【0041】

走査型電子顕微鏡(SEM)構造はトップ・ダウンまたは断面SEMによる線幅の非電気的測定に使用される。本明細書に記載する金属ショート・フロー・チップ内のSEMバー

の場合、線幅は従来のSEM技法による線間距離と同じである。図17は本明細書に記載する金属ショート・フロー・チップ内のSEM構造1702のロケーションを示す。これらの構造は図示の実施形態の各象限1704、1706、1708および1710の底部に配置されるが、これはこの位置でスペースが利用できるからである。

【0042】

図3～17と付随する説明で、金属歩留まりの向上のための例示の特徴付けビヒクルについて説明した。バイア、デバイス、ケイ化物、ポリ他のその他の特徴付けビヒクルが指定され使用されることが多い。ただし、それらを設計する手順と技法は同じである。図を見やすくするために、例示の金属特徴付けビヒクルを抽出エンジンおよび歩留まりモデル上で実現される。

10

【0043】

抽出エンジン18は2つの主要な目的を有する。すなわち、(1)特徴付けビヒクルを設計する際に使用するレベル(例えば、線幅、線間距離、集積度)の範囲を決定するのに用いる。(2)その後歩留まりモデル内で使用されて歩留まりを予測するための製品レイアウトの属性を抽出するために用いる。(1)は、特徴付けビヒクルの例でスネーク、コームおよびケルビン構造の線幅、線間距離および集積度の選択方法に関してすでに述べた。したがって、以下に主として(2)に関して説明する。

【0044】

製品レイアウトから抽出できる属性の数はほぼ無限であるため、製品ごとにすべての属性を列挙または抽出することは不可能である。したがって、どの属性を抽出するかを案内するための手順が必要である。普通、特徴付けビヒクルはどの属性を抽出するか決定する。このプロセスは以下のステップを含む。

20

1. 特徴付けビヒクル内のすべての構造を列挙する。

2. 各構造をグループまたはファミリに分類してファミリ内のすべての構造が特定の属性についての実験を形成するようにする。例えば、上記の金属特徴付けビヒクルでは、ファミリ分類表は以下のようになる。

表

| ファミリ          | 探索する属性                                                             |

|---------------|--------------------------------------------------------------------|

| ネスト構造         | 2、3の線幅および線間距離での基本欠陥度                                               |

| スネークおよびコーム    | 小さい線間距離に隣接する極めて大きい線幅<br>と小さい線幅に隣接する極めて大きい線間距離とを含む広範囲の線幅と線間距離での歩留まり |

| ケルビン-CD       | 集積度、線幅、および線間距離でのCDの変動                                              |

| +ファン・デル・ポーリ構造 |                                                                    |

| ボーダ構造         | 歩留まりに対する異なるOPCスキームの影響                                              |

30

【0045】

3. ファミリごとに、製品レイアウトからどの属性を抽出するか決定する。選択する属性はどの属性を探索するかという点から決定される。例えば、特定のファミリが異なる範囲の線間距離の歩留まりを探索する場合、線間距離または線間距離ごとのショート可能エリアのヒストグラムを抽出しなければならない。上記の例では、必要な属性リストは以下のようになる。

40

| 表                           |                         |                                                      |

|-----------------------------|-------------------------|------------------------------------------------------|

| ファミリ                        | 探索する属性                  | 製品レイアウトから抽出する属性                                      |

| (A) ネスト構造                   | 2、3の線幅および線間距離での基本欠陥度    | 臨界エリア曲線                                              |

| (B) スネークおよびコーム              | ...を含む広範囲の線幅と線間距離での歩留まり | 特徴付けビヒクル内で探索した線幅および線間距離ごとのショート可能エリアおよび/またはインスタンス数    |

| (C) ケルビング<br>CD+ファン・デル・ポー構造 | 集積度、線幅および線間距離でのCDの変動    | パターン集積度、線幅および線間距離のヒストグラム(図22の例と同様)                   |

| (D) ボーダ構造                   | 歩留まりに対する異なるOPCスキームの影響   | 製品レイアウトについて使用するため選択されたOPCレイアウトごとのショート可能エリアまたはインスタンス数 |

10

20

30

## 【0046】

4. 前述したように、適当な歩留まりモデル内で抽出した属性を使用する。

## 【0047】

他の特徴付けビヒクルの場合、ファミリと必要な属性は明らかに異なる。ただし、手順および実施態様は上記の例と同様である。

## 【0048】

前述したように、歩留まりモデル16は好ましくは特徴付けビヒクル12によって画定された網線セットを用いる選択された製作プロセスを経たウェーハの少なくとも一部から測定されたデータから構成される。好ましい実施形態では、歩留まりは不定および系統的な構成要素からなる製品としてモデル化される。

## 【数1】

$$Y = \left( \prod_{i=1}^n Ys_i \right) \left( \prod_{j=1}^m Yr_j \right)$$

## 【0049】

$Y_{s_i}$  および  $Y_{r_j}$  を決定する方法および技法について以下に説明する。

## 【0050】

系統的歩留まりモデル化

極めて多くのタイプの系統的歩留まり損失機構があり、それらはメーカーごとに異なるので、可能な系統的歩留まりモデルをすべて列挙することは実際的でない。以下に2つの極めて一般的な技法を説明し、特に本明細書に記載する特徴付けビヒクルと方法に限ってその技法の用例を示す。

## 【0051】

エリア・ベースのモデル

エリア・ベース・モデルは次のように書かれる。

## 【数2】

40

$$Y_{S_i} = \left[ \frac{Y_o(q)}{Y_r(q)} \right]^{A(q)/A_o(q)}$$

## 【0052】

上式で、 $q$  は線幅、線間距離、長さ、線幅 / 線間距離の比、集積度などの特徴付けビヒクル内で探索する設計係数である。 $Y_o(q)$  は特徴付けビヒクルからの設計係数  $q$  を備えた構造の歩留まりである。 $A_o(q)$  はこの構造のショート可能エリア、 $A(q)$  は製品レイアウト上のタイプ  $q$  のすべてのインスタンスのショート可能エリアである。 $Y_r(q)$  は不定欠陥が歩留まり損失機構のみであろうと仮定した場合のこの構造の予測歩留まりである。この量を計算する手順を不定歩留まりモデル化に関連して以下に説明する。

## 【0053】

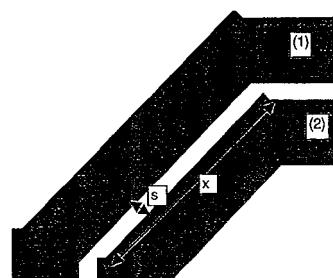

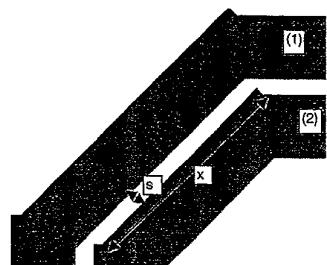

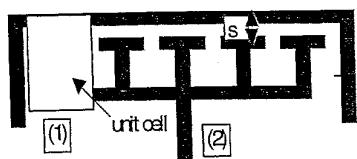

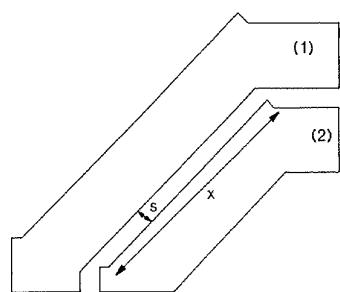

ショート可能エリアの画定は図 18 の例で最もよく示されている。このタイプの試験構造はメーカーが  $s$  の線間距離を備えた曲げを有する広い線を製造できるか否かを決定するために使用できる。例示の試験構造では、ショートは端子 (1) と (2) の間に電圧を印加して端子 (1) から (2) に流れる電流を測定することで測定される。この電流が指定のしきい値 (普通 1 ~ 100 nA) より大きい場合、ショートが検出される。ショート可能エリアは、ブリッジングが発生するとショートが測定されるエリアとして画定される。図 18 の例では、ショート可能エリアは  $h \times s$  である。 $A(q)$  項は製品レイアウト内の図 18 に示すすべての出現する厳密なまたはほぼ厳密なパターン (すなわち、線間距離が  $s$  で 45 度に曲がった広い線) のショート可能エリアである。 $Y_r(q)$  項は下記の臨界エリア方法を用いるこの構造の不定歩留まり限界を予測することで抽出される。

## 【0054】

このモデルの有効性は特徴付けビヒクル上に配置された構造の数と構造のサイズと同じ程度でしかないということを認識することが重要である。例えば、図 18 に示す角度が付いた曲がり試験構造が特徴付けビヒクル上に配置されないかまたは意味がある歩留まり数を得るほどの回数配置されなかった場合、この製品レイアウト上で幅広い線の曲がりの歩留まり損失をモデル化する望みはないであろう。どれ位大きい試験構造をいくつ特徴付けビヒクル上に配置するかを厳密に定義するのは困難であるが、実際の経験から特徴付けビヒクル上の各試験構造の全ショート可能エリアは理想的には  $A(q) / A_o(q) < 10$  を満たすべきである。

## 【0055】

ショートは一般に複数のオープン歩留まり損失機構に広がっている傾向があるので上記の説明はショートについてであった。ただし、ショート可能エリアをオープン原因エリアと交換する限り、オープン歩留まり損失機構もこの歩留まりモデルで同様にモデル化できる。

## 【0056】

インスタンス・ベースの歩留まりモデル

インスタンス・ベースの歩留まりモデルの一般的な形式は、

## 【数3】

$$Y_{S_i} = \left[ \frac{Y_o(q)}{Y_r(q)} \right]^{N_i(q)/N_o(q)}$$

のようになる。

## 【0057】

上式で、 $Y_o(q)$  および  $Y_r(q)$  はエリア・ベースの歩留まりモデルと厳密に同じである。 $N_i(q)$  は単位格子・パターンまたは特徴付けビヒクル上の試験パターンに酷似した単位格子・パターンが製品レイアウト上に出現する回数である。 $N_o(q)$  は単位格子・パターンが特徴付けビヒクル上に出現する回数である。

10

20

30

40

50

## 【0058】

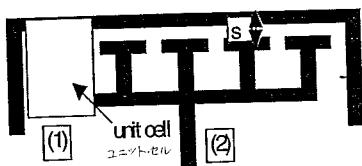

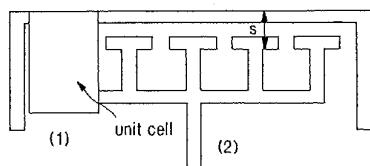

例えば、図19は線間距離s付近の線の端部のT型末端の歩留まりを検証する簡単な試験パターンを示す。この試験パターンは端子(1)と(2)の間に電圧を印加してショート電流を測定することで測定される。このパターンが特徴付けビヒクルのどこかで25回繰り返されると、No(q)は $25 \times 5 = 125$ となる。試験構造あたり5つの単位格子があるからである。

## 【0059】

この単位格子が線間距離sで出現する回数が製品レイアウトから抽出されると、このタイプの構造の系統的な歩留まりを予測できる。例えば、各々の構造に500の単位格子を備えた5つの構造がある場合、No(q) = 2500である。同じ製品のNi(q)が10、000の場合、98.20%の特徴付けビヒクル上の試験構造の歩留まりが測定された。下記の技法を用いて、Yr(q)を99.67%と推定することができる。これらの数字を以下の式に代入して、

## 【数4】

$$Y_{s_i} = \left[ \frac{0.9820}{0.9967} \right]^{10000/2500} = 92.84\%$$

が得られる。

## 【0060】

不定歩留まりモデル化

不定構成要素は、

## 【数5】

$$Y_r = e^{- \int_{x_0}^{\infty} CA(x) \times DSD(x) dx}$$

のように記述できる。

## 【0061】

十分に記載されているかのようにこの詳細な説明に参照として組み込まれた「Modeling of Lithography Related Yield Losses for CAD of VLSI Circuits」、W. Maly、IEEE Trans. on CAD、1985年7月、pp 161~177にも記載されているように、上式で、CA(x)は欠陥サイズxの臨界エリア、DSD(x)は欠陥サイズ分布である。X0は確信を持って観察または測定できる最小欠陥サイズである。これは普通最小線間距離設計規則に設定される。臨界エリアはサイズxの欠陥が存在する場合、ショートが発生するエリアである。極めて小さいXの場合、臨界エリアは0付近であるが、極めて大きい欠陥サイズはチップの全エリアに近づく臨界エリアを有する。臨界エリアと抽出技法の別の説明は、すべて十分に記載されているかのようにこの詳細な説明に参照として組み込まれている、P. K. NagおよびW. Malyの「Yield Estimation of VLSI Circuits」、Techcon 90、1990年10月16~18日、San Jose、P. K. NagおよびW. Malyの「Hierarchical Extraction of Critical Area for Shorts in Very Large ICs」Proceedings of the IEEE International Workshop on Detect and Fault Tolerance in VLSI Systems所収、IEEE Computer Society Press 1995年、pp. 10~18、I. Bubel, W. Maly, T. Waas, P. K. Nag, H. M. Hartmann, D. Schmitt-LandsiedelおよびS. Griepの「AFFCCA」

10

20

30

40

50

A tool for Critical Area Analysis with Circular Defects and Lithography Deformed Layout」Proceedings of the IEEE International Workshop on Detect and Fault Tolerance in VLSI Systems所収, IEEE Computer Society Press 1995年、pp. 19~27、C. Ouyang およびW. Malyの「Efficient Extraction of Critical Area in Large VLSI ICs」Proc. IEEE International Symposium on Semiconductor manufacturing、1996年、pp. 301~304、C. Ouyang, W. Pleskacz、およびW. Malyの「Extraction of Critical Area for opens in Large VLSI Circuits」Proc. IEEE International Workshop on Detect and Fault Tolerance of VLSI Systems、1996年、pp. 21~29に記載されている。

10

#### 【0062】

欠陥サイズ分布はサイズが  $x$  の欠陥の欠陥密度を表す。欠陥サイズ分布のための提案されているモデルは多数ある（例えば、共に十分に記載されているかのようにこの詳細な説明に参照として組み込まれているW. Malyの「Yield Models - Comparative Study」、Defect and Fault Tolerance in VLSI Systems, Ed. by C. Stapper他、Plenum Press, New York, 1990年およびC. H. Stapperの「Modeling of Integrated Circuit Defect Sensitivities」、IBM J. Res. Develop., Vol. 27, No. 6、1983年11月）。ただし、図を見やすくするために、最も一般的な分布式

20

#### 【数6】

$$DSD(x) = \frac{D_o \times k}{x^p}$$

30

が使用される。上式で、 $D_o$  は観察された  $x_o$  より大きい欠陥総数 /  $\text{cm}^2$  を表す。 $P$  は欠陥のサイズが減衰する速度を表す単位がない値である。通常、 $p$  は 2 ~ 4 の間の数である。K は正規化係数である。したがって、

#### 【数7】

$$\int_{x_o}^{\infty} \frac{k}{x^p} dx = 1$$

となる。

#### 【0063】

以下の 2 つの節で特徴付けヒヒクルから欠陥サイズ分布を抽出する技法を説明する。

40

#### 【0064】

##### ネスト構造技法

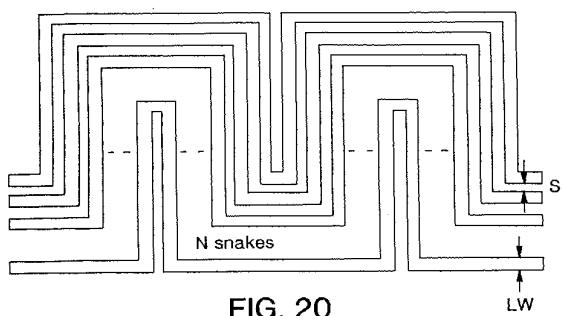

ネスト構造技法は欠陥サイズ分布を抽出するために設計されている。図 20 に示すように、ネスト構造は線幅が  $w$ 、線間距離が  $s$  の  $N$  本の線で構成されている。この構造は線 1 と 2、2 と 3、3 と 4、. . . 、および  $N - 1$ 、 $N$  の間のショート電流を測定することで測定される。所与の仕様書の制限値を超える電流はすべてショートと見なされる。さらに、オープンは線 1、2、3、の抵抗値を測定することで試験できる。一定の仕様書の制限値を超える抵抗はすべてオープン線と見なされる。いくつの線をショートさせるかを検証することで、欠陥サイズ分布を決定できる。

50

## 【0065】

2本の線のみがショートされる場合、欠陥サイズは  $s$  より大きく  $3w + 2s$  を超えないことが必要である。欠陥が  $s$  より小さければショートは発生しないが、 $3w + 2s$  より大きい欠陥は少なくとも 3 本の線のショートを引き起こすことが保証される。ショートされる線の数ごとにサイズの間隔を作成できる。

## 【0066】

## 【表 14】

| ショート線数 )<br>Number Lines Shorted | サイズ間隔 )<br>Size Interval             |

|----------------------------------|--------------------------------------|

| 2                                | $s$ to $3w + 2s$                     |

| 3                                | $2s + w$ to $3s + 4w$                |

| 4                                | $3s + 2w$ to $4s + 5w$               |

| ...                              | ...                                  |

| N                                | $(N-1)s + (N-2)w$ to $(N)s + (N+1)w$ |

10

20

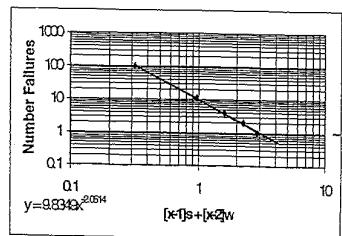

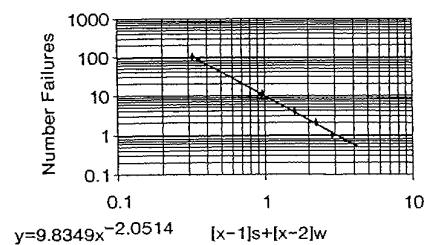

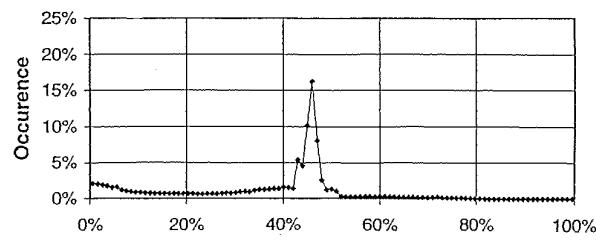

## 【0067】

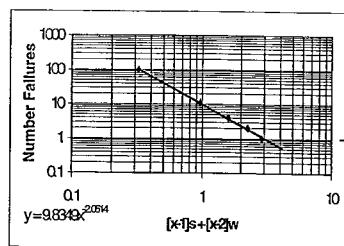

前記間隔は重なることに留意すべきである。したがって、欠陥サイズ分布は直接計算できない。この制約は  $p$  の抽出を制限するのみである。したがって、 $p$  を推定するために、すべての偶数番号の線、次にすべての奇数番号の線について  $P$  の予想値が計算される。最後に、2つの値を平均して  $p$  を推定する。 $p$  を抽出するため、 $l_n$  (ショートした  $x$  本の線での欠陥数) 対  $l_o g ([x - 1]s + [x - 2]w)$  がプロットされる。この線の勾配は  $-p$  であることが分かる。  $D_o$  項は線の各グループで欠陥数をカウントし構造のエリアで割ることで抽出される。ただし、極めて大きい  $D_o$  の場合、この推定は楽観的すぎる。試験構造と同様の構造から欠陥サイズ分布を抽出する手順に関する別の情報が例えれば、十分に記載されているかのようにこの詳細な説明に参照として組み込まれた J. K h a r e , W. M a l y および M. E. T h o m a s の「 E x t r a c t i o n o f D e f e c t S i z e D i s t r i b u t i o n i n a n I C l a y e r U s i n g T e s t S t r u c t u r e D a t a 」、 I E E E T r a n s a c t i o n s o n S e m i c o n d u c t o r s M a n u f a c t u r i n g 」、 pp. 354 ~ 368、 Vol. 7、 No. 3、 1994 年 8 月に記載されている。

30

## 【0068】

例として、100 のダイの 1 枚のウェーハからとった以下のデータを考える。

## 【0069】

## 【表 15】

| Number Lines Shorted | Number of Failures |

|----------------------|--------------------|

| 2                    | 98                 |

| 3                    | 11                 |

| 4                    | 4                  |

| 5                    | 2                  |

| 6                    | 1                  |

| 7                    | 0                  |

| 8                    | 0                  |

10

20

40

50

## 【0070】

構造サイズが  $1 \text{ cm}^2$  の場合、D o は  $98 + 11 + 4 + 2 + 1 = 133 / (100 * 1) = 1.33$  欠陥 /  $\text{cm}^2$  である。また、ログのプロット (欠陥数) 対  $\log([x-1]s + [x-2]w)$  (図21を参照) によって  $P = 2.05$  が分かる。

## 【0071】

## コード構造技法

線幅 = 線間距離 =  $s$  のコードを仮定すると、この構造の歩留まりは、

## 【数8】

$$\ln[|\ln(Y)|] = \ln\left[-\int_{x_0}^{\infty} DSD(x) \times CA(x) dx\right] \propto (1-p) \times \ln(s)$$

として記述できることが分かる。

## 【0072】

したがって、 $\ln[|\ln(n)|]$  対  $\ln(s)$  のプロットの勾配から、 $p$  を推定することができる。D o 抽出技法は上記と同じである。

## 【0073】

## 歩留まりインパクトおよび評価

十分な数の特徴付けビヒクルが実行され、各特徴付けビヒクルについて歩留まり推定が行われると、その結果がスプレッドシートに表示されて歩留まり活動の優先順位付けが可能になる。テーブル14～16はそのようなスプレッドシートに含まれる情報の例である。スプレッドシートは金属歩留まり、ポリおよびアクティブ・エリア (AA) 歩留まり (テーブル14)、コンタクトおよびバイア歩留まり (テーブル15)、およびデバイス歩留まり (テーブル16) に分割されている。左側のカラムは系統的な歩留まり損失機構を示し、右側のカラムは不定歩留まり損失機構を示す。系統的欠陥機構の正確なタイプは製品や技術によって異なるが、例を表XIV～XVIに示す。

## 【0074】

普通、目標はスプレッドシートに列挙した各モジュールに対応する。モジュール歩留まりが目標から離れれば離れるほど、問題解決のためにより多くの強調とリソースとが向けられる。例えば、テーブル14～16に示す例の各モジュールについて目標が人為的に95パーセントに設定されると、明らかに ( $M_2 M_3$ ) バイア (75.2%) とそれに続く同様のバイア ( $M_1 M_2$ ) (81.92%)、 $M_1$  ショート (82.25%)、およびポリへのコンタクト (87.22%) が目標を下回り、バイア ( $M_1 M_3$ ) が最大量の作業を必要とし、ポリが最小量の作業を必要とする。

## 【0075】

各モジュール内で、最大歩留まり損失がどこにあるかを判定できる。すなわち、歩留まりを下げているのはある特定の系統的な機構なのか、単に不定の欠陥問題なのか、または2つの組み合わせなのか。例えば、テーブル15に示すように、バイア( $M_2$   $M_3$ )歩留まり損失は $M_3$ レベルのロング・メタル・ランナ(*long metal runner*)に接続されたバイアに関する系統的な問題(77.40%)によって支配される。 $(M_1$   $M_2$ )のバイアは不定欠陥問題(92.49%)に加えて同じ問題(91.52%)を抱えている。バイア( $M_1$   $M_2$ )の歩留まり問題を解決するにはこれらの問題の両方を解決する必要がある。

## 【0076】

10

テーブル14に示すように、 $M_1$ 歩留まり損失は小さい線間距離に近い大きい線幅に影響を与える系統的な問題(96.66%)に加えて不定欠陥問題(85.23%)によっても支配される。金属1を改良するにはこれらの問題の両方を解決する必要がある。スプレッドシートの他のモジュールについても同様の結論を出すことができる。

## 【0077】

20

最悪の歩留まりモジュールの場合、このモジュールの別の特徴付けビヒクルを頻繁に実行する必要がある。普通、モジュール歩留まりのこれらの改良を試行、改善、確認するためにこれらの特徴付けビヒクルを分割する。目標内のモジュールの場合、モジュール歩留まりの下降などの動きが現在までないことを確認するためにショート・フロー・特徴付けビヒクルの定期的なモニタがまだ必要である。ただし、知られている問題を抱えたモジュールと比較してこれらの特徴付けビヒクルは実行頻度を減らすことができる。

## 【0078】

## 【表16】

系統的歩留損失メカニズム

テーブル4 (TABLE XIV)

| オーブンおよびショート(金属層) Opens and Shorts (Metal Layers) 不定歩留損失メカニズム |                                   |               |                 |                              |      |                 |

|--------------------------------------------------------------|-----------------------------------|---------------|-----------------|------------------------------|------|-----------------|

| 金属層                                                          | Systematic Yield Loss Mechanisms  |               |                 | Random Yield Loss Mechanism  |      |                 |

|                                                              | Shortable Area (cm <sup>2</sup> ) | Instant Count | Estimated Yield | Do                           | P    | Estimated Yield |

| 金属層-1                                                        | Random Yield                      |               |                 | 0.7 defects/cm <sup>2</sup>  | 2.3  | 85.23%          |

|                                                              | Wide lines near small space       | 0.034         | 96.66%          | 欠陥                           |      |                 |

|                                                              | Wide space near small lines       | 0.00014       | 99.99%          |                              |      |                 |

|                                                              | Yield for OPC structures          |               | 72,341          | 99.86%                       |      |                 |

|                                                              | Bent lines                        |               | 492             | 100.00%                      |      |                 |

|                                                              | Total for M1 M1 総計                |               |                 |                              |      | 82.25%          |

| 金属層-2                                                        | Random Yield                      |               |                 | 0.35 defects/cm <sup>2</sup> | 1.92 | 97.45%          |

|                                                              | Wide lines near small space       | 0.00079       | 99.92%          | 欠陥                           |      |                 |

|                                                              | Wide space near small lines       | 0.000042      | 100.00%         |                              |      |                 |

|                                                              | Yield for OPC structures          |               | 1040372         | 97.94%                       |      |                 |

|                                                              | Bent lines                        |               | 103             | 100.00%                      |      |                 |

|                                                              | Total for M2 M2 総計                |               |                 |                              |      | 95.36%          |

| 金属層-3                                                        | Random Yield                      |               |                 | 0.25 defects/cm <sup>2</sup> | 2.02 | 96.92%          |

|                                                              | Wide lines near small space       | 0.0000034     | 100.00%         | 欠陥                           |      |                 |

|                                                              | Wide space near small lines       | 0             | 100.00%         |                              |      |                 |

|                                                              | Yield for OPC structures          |               | 352             | 100.00%                      |      |                 |

|                                                              | Bent lines                        |               | 7942            | 99.92%                       |      |                 |

|                                                              | Total for M3 M3 総計                |               |                 |                              |      | 96.84%          |

| オーブンおよびショート(ポリおよびAA層) Open and Shorts (Poly and AA Layer) 欠陥 |                                   |               |                 |                              |      |                 |

| Poly                                                         | Random Yield (without silicide)   |               |                 | 0.17 defects/cm <sup>2</sup> | 2.03 | 99.81%          |

|                                                              | Random Yield (with silicide)      |               |                 | 4.34 defects/cm <sup>2</sup> | 4.56 | 89.54%          |

|                                                              | Wide lines near small space       | 0             | 100.00%         | 欠陥                           |      |                 |

|                                                              | Wide space near small lines       | 0.01203       | 98.80%          |                              |      |                 |

|                                                              | Yield for OPC structures          |               | 0               | 100.00%                      |      |                 |

|                                                              | Bent lines                        |               | 786541          | 92.44%                       |      |                 |

|                                                              | Over wide AA 突き AA 対象             | 0.034         | 96.66%          |                              |      |                 |

| AA                                                           | Over narrow AA 窪い AA 対象           | 0.101         | 99.00%          |                              |      |                 |

|                                                              | Total for Poly ポリ 総計              |               |                 |                              |      | 87.22%          |

|                                                              | Random Yield (without silicide)   |               |                 | 1.3                          | 3.45 | 99.12%          |

|                                                              | Random Yield (with silicide)      |               |                 | 1.7                          | 3.02 | 98.72%          |

| AA                                                           | Wide lines near small space       | 10952         | 99.96%          |                              |      |                 |

|                                                              | Wide space near small lines       | 0             | 100.00%         |                              |      |                 |

|                                                              | Total for AA AA 総計                |               |                 |                              |      | 98.70           |

① 不定歩留(ランダム歩留)

小さな距離に近い大きな線幅

小さな線幅に近い大きな距離

OPC構造の歩留

② 不定歩留(ケイ化物なし)

不定歩留(ケイ化物あり)

小さな距離に近い広い線幅

小さな線幅に近い大きな距離

OPC構造の歩留

【0 0 7 9】

【表17】

10

20

30

系統的歩留損失メカニズム

テーブル XV (TABLE XV)

| コントラクトおよびバイア                   |                                    | Contacts and Vias                |                 |                             | 不特定歩留損失メカニズム |        |

|--------------------------------|------------------------------------|----------------------------------|-----------------|-----------------------------|--------------|--------|

| ショートコントラクト                     |                                    | Systematic Yield Loss Mechanisms |                 | Random Yield Loss Mechanism |              | 推定歩留   |

| Contact to Poly                | Shortable Area (cm <sup>2</sup> )  | Instant Count                    | Estimated Yield | Fault Rate                  | Fault Number |        |

| Contact to Poly                | Random Yield (without silicide) ①  | 歩留数 (推定歩留)                       |                 | 2.20E-09                    | 3270432      | 99.28% |

|                                | Random Yield (with silicide) ②     |                                  |                 | 3.10E-09                    | 3270432      | 98.99% |

|                                | Yield for Long Runners (on M1) ③   | 11,921                           | 100.00%         |                             |              |        |

|                                | Yield for Long Runners (on Poly) ④ | 0                                | 100.00%         |                             |              |        |

|                                | Yield for Redundant Vias ⑤         | 39421                            | 100.00%         |                             |              |        |

|                                | Yield for very isolated contacts ⑥ | 7200                             | 96.46%          |                             |              |        |

| Total for Contact to Poly ⑦    |                                    |                                  |                 |                             |              | 94.80% |

| Contact to n+AA                | Random Yield (without silicide) ①  |                                  |                 | 2.20E-09                    | 5270432      | 98.85% |

|                                | Random Yield (with silicide) ②     |                                  |                 | 3.10E-09                    | 5270532      | 98.38% |

|                                | Yield for Long Runners (on M1) ③   | 75,324                           | 99.99%          |                             |              |        |

|                                | Yield for Long Runners (on n+AA) ④ | 0                                | 100.00%         |                             |              |        |

|                                | Yield for Redundant Vias ⑤         | 4032007                          | 99.60%          |                             |              |        |

|                                | Yield for very isolated contacts ⑥ | 7200                             | 99.93%          |                             |              |        |

| Total for Contact to AA (n+) ⑦ |                                    |                                  |                 |                             |              | 96.78% |

| Contact to p+AA                | Random Yield (without silicide) ①  |                                  |                 | 2.20E-09                    | 6093450      | 98.67% |

|                                | Random Yield (with silicide) ②     |                                  |                 | 3.10E-09                    | 6093450      | 98.13% |

|                                | Yield for Long Runners (on M1) ③   | 96,732                           | 99.99%          |                             |              |        |

|                                | Yield for Long Runners (on p+AA) ④ | 0                                | 100.00%         |                             |              |        |

|                                | Yield for Redundant Vias ⑤         | 39421                            | 100.00%         |                             |              |        |

|                                | Yield for very isolated contacts ⑥ | 7200                             | 99.93%          |                             |              |        |

| Total for Contact to AA (p+) ⑦ |                                    |                                  |                 |                             |              | 96.74% |

| Vias M1-M2                     | Random Yield (single vias) ⑨       |                                  |                 | 1.10E-08                    | 7093210      | 92.49% |

|                                | Yield for Long Runners (M2) ⑩      | 88640                            | 91.52%          |                             |              |        |

|                                | Yield for Long Runners (M1) ⑪      | 97645                            | 99.03%          |                             |              |        |

|                                | Yield for Redundant Vias ⑫         | 11003456                         | 96.91%          |                             |              |        |

|                                | Yield for Isolated Vias ⑬          | 119582                           | 96.81%          |                             |              |        |

|                                | Total for Via M1-M2 ⑭              |                                  |                 |                             |              | 81.92% |

| Vias M2-M3                     | Random Yield (single vias) ⑨       |                                  |                 | 3.10E-09                    | 4002063      | 98.77% |

|                                | Yield for Long Runners (M3) ⑩      | 256128                           | 77.40%          |                             |              |        |

|                                | Yield for Long Runners (M2) ⑪      | 103432                           | 96.97%          |                             |              |        |

|                                | Yield for Redundant Vias ⑫         | 7096230                          | 99.29%          |                             |              |        |

|                                | Yield for Isolated Vias ⑬          | 1024                             | 99.99%          |                             |              |        |

|                                | Total for Via M2-M3 ⑭              |                                  |                 |                             |              | 75.12% |

- ① 不定歩留 (ケイ化物なし)

不定歩留 (ケイ化物あり)

ロングランナの歩留 (M1上)

② ロングランナの歩留 (ポリ上)

③ 不長バイアの歩留

超隔離バイアの歩留

- ④ ポリへのコントラクト数

⑤ ロングランナの歩留 (n+AA上)

⑥ AAへのコントラクト数 (n+)

⑦ ロングランナの歩留 (p+AA上)

⑧ AAへのコントラクト数 (p+)

⑨ 不定歩留 (単一バイア)

⑩ ロングランナの歩留 (M2)

⑪ ロングランナの歩留 (M1)

⑫ 不長バイアの歩留

⑬ 隔離バイアの歩留

⑭ ハイアM1-M2 惣計

⑮ ロングランナの歩留 (M3)

⑯ ハイアM2-M3 の歩留

【 0 0 8 0 】

【 表 18 】

10

20

30

テーブル16 (TABLE XVI) 不良歩留換算メカニズム

| ショット可能なエラー                 |                                   | デバイス                             |                 |                             | 不良歩留換算メカニズム |        |

|----------------------------|-----------------------------------|----------------------------------|-----------------|-----------------------------|-------------|--------|

|                            |                                   | Systematic Yield Loss Mechanisms |                 | Random Yield Loss Mechanism |             | 推定歩留   |

| NMOS                       | Shortable Area (cm <sup>2</sup> ) | Instant Count                    | Estimated Yield | Fault Rate                  | Number      |        |

|                            | Random Yield (Logic Xtor)         | 基底数                              | 推定歩留            | 2.90E-09                    | 1395228     | 99.60% |

|                            | Random Yield (SRAM Xtor)          |                                  |                 | 2.80E-09                    | 2226720     | 99.38% |

|                            | S/D Shorts                        |                                  |                 | 1.00E-09                    | 3621948     | 99.64% |

|                            | Bent Transistors                  | 1113360                          | 99.89%          |                             |             |        |

|                            | Near Large AA                     | 754000                           | 99.92%          |                             |             |        |

|                            | Near Small AA                     | 1023452                          | 99.90%          |                             |             | 98.33% |

| Total for NMOS Transistors |                                   |                                  |                 |                             |             |        |

| PMOS                       | Random Yield (Logic Xtor)         |                                  |                 | 1.80E-09                    | 1491003     | 99.73% |

|                            | Random Yield (SRAM Xtor)          |                                  |                 | 3.10E-09                    | 1113360     | 99.66% |

|                            | S/D Shorts                        |                                  |                 | 9.00E-10                    | 2604363     | 99.77% |

|                            | Bent Transistors                  | 556680                           | 99.94%          |                             |             |        |

|                            | Near Large AA                     | 789092                           | 99.92%          |                             |             |        |

|                            | Near Small AA                     | 1309970                          | 99.87%          |                             |             |        |

|                            | Total for PMOS Transistors        |                                  |                 |                             |             | 98.89% |

① 不良歩留(論理Xtor)

② NMOSトランジスタ総計

不良歩留(SRAM Xtor)

③ PMOSトランジスタ総計

S/Dショット

曲ったトランジスタ

大きいAA付近

小さいAA付近

10

20

30

40

50

## 【図面の簡単な説明】

## 【図1】

本発明のシステムの好ましい実施形態によって実行されるステップを示すブロック図である。

## 【図2】

フィードバック・ループを実施するために、本発明のシステムによって実行される追加のステップを示すブロック図である。

## 【図3】

単一リソグラフィック層を備える例示的ショート・フロー・マスクのイメージである。

## 【図4】

例示的金属ショート・フロー・チップ上のパッド・フレームを示す図である。

## 【図5】

図4に示す各パッド・フレーム内のパッドを示す図である。

## 【図6】

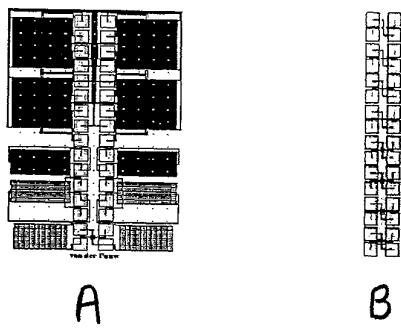

2つのタイプの、ファン・デル・ポー構造を含むパッド・フレーム構造を示す図である。

## 【図7】

ファン・デル・ポー構造を含むパッド・フレームの、例示的チップ上の位置を示す図である。

## 【図8】

例示的ファン・デル・ポー構造を示す図である。

## 【図9】

例示的金属ショート・フロー・チップ上のネスト欠陥サイズ分布構造の例示的位置を示す図である。

## 【図10】

例示的ネスト欠陥サイズ分布構造を示す図である。

## 【図11】

例示的ケルビン臨界寸法構造を示す図である。

## 【図12】

例示的金属ショート・フロー・チップ上のケルビン構造の例示的位置を示す図である。

【図 1 3】

例示的金属ショート・フロー・チップ上およびスネークおよびコームの例示的位置を示す図である。

【図 1 4】

例示的金属ショート・フロー・チップで使用される例示的スネークおよびコーム構造を示す図である。

【図 1 5】

例示的金属ショート・フロー・チップで使用されるボーダ構造の変形形態の例を示す図である。

10

【図 1 6】

例示的金属ショート・フロー・チップ上のボーダ構造の例示的位置を示す図である。

【図 1 7】

例示的金属ショート・フロー・チップ上の走査電子顕微鏡構造の例示的位置を示す図である。

【図 1 8】

ショート可能エリアを示す例示的テスト構造を示す図である。

【図 1 9】

線の端部の T 字形末端の歩留まりを検査するための例示的テスト・パターンを示す図である。

20

【図 2 0】

欠陥サイズ分布を抽出するための例示的ネスト構造を示す図である。

【図 2 1】

サイズの変化に対する、欠陥の減少率を判定するためのプロットを示す図である。

【図 2 2】

図 2 2 ( a )、 2 2 ( b )、 2 2 ( c )は、サンプル製品レイアウトのメタル 1 層に関する線幅、線スペース、およびパターン密度分布をそれぞれ示す図である。

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【図5】

【図6】

図6A

図6B

【図7】

【図8】

【図9】

【図11】

【図12】

【図10】

【図13】

【図15】

【図14】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

25 May 2001 (25.05.2001)

PCT

(10) International Publication Number

WO 01/35718 A2

(51) International Patent Classification: Not classified

(21) International Application Number: PCT/US00/31665

(22) International Filing Date:

17 November 2000 (17.11.2000)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

09/442,699 18 November 1999 (18.11.1999) US

(71) Applicant: PDF SOLUTIONS, INC. [US/US]: Suite 700,

333 West San Carlos Street, San Jose, CA 95110 (US).(72) Inventor: STINE, Brian, E.: 560 Vista Club Circle #105,

Santa Clara, CA 95054 (US).(74) Agents: KOFFS, Steven, E. et al.; Duane, Morris &

Heckscher LLP, One Liberty Place, Philadelphia, PA

19103-7396 (US).(81) Designated States (national): AE, AG, AL, AM, AT, AU,

AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CR, CU, CZ,

DE, DK, DM, DZ, EE, ES, FI, GB, GD, GE, GH, GM, HR,

HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR,

LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ,

NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM,

TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZW.(84) Designated States (regional): ARPO patent (GH, GM,

KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW), Eurasian

patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European

patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE,

IT, LU, MC, NL, PT, SE, TR), OAPI patent (BE, BJ, CF,

CG, CI, CM, GA, GN, GW, ML, MR, NE, SN, TD, TG).

Published:

— Without international search report and to be republished

upon receipt of that report.

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: SYSTEM AND METHOD FOR PRODUCT YIELD PREDICTION

WO 01/35718 A2

(57) Abstract: A system and method for predicting yield of integrated circuits includes at least one type of characterization vehicle which incorporates at least one feature which is representative of at least one type of feature to be incorporated in the final integrated circuit product. The characterization vehicle is subjected to at least one of the process operations making up the fabrication cycle to be used in fabricating the integrated circuit product in order to produce a yield model. The yield model embodies a layout as defined by the characterization vehicle and preferably includes features which facilitate the gathering of electrical test data and testing of prototype section at operating speeds. An extraction engine extracts predetermined layout attributes from a proposed product layout. Operating on the yield model, the extraction engine produces yield predictions as a function of layout attributes and broken down by layers or steps in the fabrication process. These yield predictions are then used to determine which areas in the fabrication process require the most improvement.

## SYSTEM AND METHOD FOR PRODUCT YIELD PREDICTION

Background of the Invention

The present invention pertains to fabrication of integrated circuits and more particularly to systems and methods for improving fabrication yields.

5        The fabrication of integrated circuits is an extremely complex process that may involve hundreds of individual operations. Basically, the process includes the diffusion of precisely predetermined amounts of dopant material into precisely predetermined areas of a silicon wafer to produce active devices such as transistors. This is typically done by forming a layer of silicon dioxide on the wafer, then utilizing a photomask and photoresist to define a pattern of areas into

10      which diffusion is to occur through a silicon dioxide mask. Openings are then etched through the silicon dioxide layer to define the pattern of precisely sized and located openings through which diffusion will take place. After a predetermined number of such diffusion operations have been carried out to produce the desired number of transistors in the wafer, they are interconnected as required by interconnection lines. These interconnection lines, or

15      interconnects as they are also known, are typically formed by deposition of an electrically conductive material which is defined into the desired interconnect pattern by a photomask, photoresist and etching process. A typical completed integrated circuit may have millions of transistors contained within a 0.1 inch by 0.1 inch silicon chip and interconnects of submicron dimensions.

WO 01/35718

PCT/US00/31665

In view of the device and interconnect densities required in present day integrated circuits, it is imperative that the manufacturing processes be carried out with utmost precision and in a way that minimizes defects. For reliable operation, the electrical characteristics of the circuits must be kept within carefully controlled limits, which implies a high degree of control over the myriad of operations and fabrication processes. For example, in the photoresist and photomask operations, the presence of contaminants such as dust, minute scratches and other imperfections in the patterns on the photomasks can produce defective patterns on the semiconductor wafers, resulting in defective integrated circuits. Further, defects can be introduced in the circuits during the diffusion operations themselves. Defective circuits may be identified both by visual inspection under high magnification and by electrical tests. Once defective integrated circuits have been identified, it is desired to take steps to decrease the number of defective integrated circuits produced in the manufacturing process, thus increasing the yield of the integrated circuits meeting specifications.