#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

##

(43) International Publication Date 25 October 2007 (25.10.2007)

CT (10) International Publication Number WO 2007/120354 A2

- (51) International Patent Classification: *H01L 21/8242* (2006.01) *H01L 21/20* (2006.01)

- (21) International Application Number:

PCT/US2006/062388

(22) International Filing Date:

20 December 2006 (20.12.2006)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

11/326,524

4 January 2006 (04.01.2006) US

- (71) Applicant (for all designated States except US): FREESCALE SEMICONDUCTOR INC. [US/US]; 6501 William Cannon Drive West, Austin, Texas 78735 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): ROBERTS, Douglas R. [US/US]; 7608 Tisdale Drive, Austin, Texas 78757 (US). LUCKOWSKI, Eric D. [US/US]; 3016 Flower Hill Drive, Round Rock, Texas 78664 (US). RAUF, Shahid [US/US]; 712 Yale Drive, Pflugerville, Texas 78660 (US). VENTZEK, Peter L.G. [US/US]; 10843 Redmond Road, Austin, Texas 78739 (US).

- (74) Agents: KING, Robert L. et al.; 7700 W. Parmer Lane, MD:PL02, Austin. Texas 78729 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: THIN-FILM CAPACITOR WITH A FIELD MODIFICATION LAYER AND METHODS FOR FORMING THE SAME

(57) Abstract: A method for forming a capacitor includes providing a metal-containing bottom electrode (12), forming a capacitor insulator (14) over the metal-containing bottom electrode (12), forming a metal-containing top electrode (18) over the capacitor insulator (14), forming a dielectric-containing modification layer (22) field over the capacitor insulator (14)and at least partially surrounding the metal-containing top electrode (18). Forming dielectric-containing the field modification layer (22) may include oxidizing a sidewall (22) of the metal-containing field modification layer (18). A barrier layer (16) may be formed over the capacitor insulator (14) prior to forming the metal-containing top electrode (18).

# THIN-FILM CAPACITOR WITH A FIELD MODIFICATION LAYER AND METHODS FOR FORMING THE SAME

#### **BACKGROUND OF THE INVENTION**

#### Field of the Invention

[0001] This invention relates in general to thin-film capacitors and more specifically to a thin-film capacitor with a field modification layer and methods for forming the same.

#### **Description of the Related Art**

[0002] Thin-film capacitors increasingly have thinner insulator and electrode layers. Thinning of the insulator layer, however, poses several problems in such capacitors. In particular, enhanced electric field at the corners of the electrode layers can generate higher leakage current at the periphery of the thin-film capacitors. In certain instances, leakage current can be large enough to cause insulator breakdown at the electrode layer edges. Insulator breakdown is more likely to happen in thin-film capacitors with thinner insulator layers. Susceptibility to insulator breakdowns lowers the reliability of thin-film capacitors.

[0003] Thus, there is a need for improved thin-film capacitors and methods for forming the same.

### **BRIEF DESCRIPTION OF THE DRAWINGS**

[0004] The present invention may be better understood, and its numerous objects, features, and advantages made apparent to those skilled in the art by referencing the accompanying drawings.

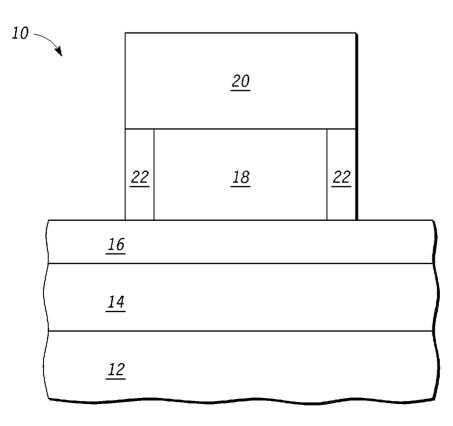

[0005] Figure 1 shows a partial side view of one embodiment of a thin-film capacitor during a processing stage, consistent with one embodiment of the invention;

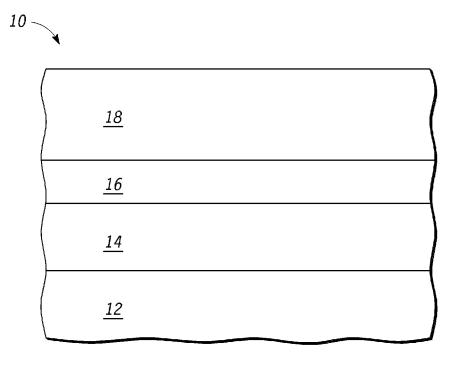

[0006] Figure 2 shows a partial side view of one embodiment of a thin-film capacitor during a processing stage, consistent with one embodiment of the invention;

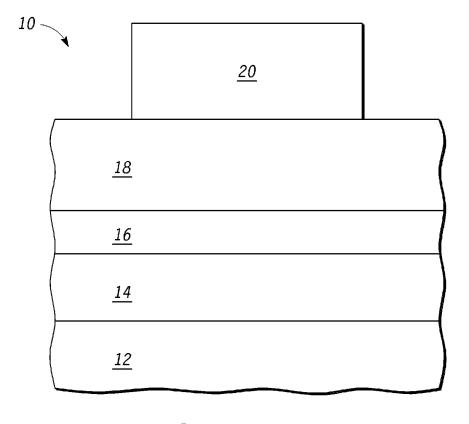

[0007] Figure 3 shows a partial side view of one embodiment of a thin-film capacitor during a processing stage, consistent with one embodiment of the invention;

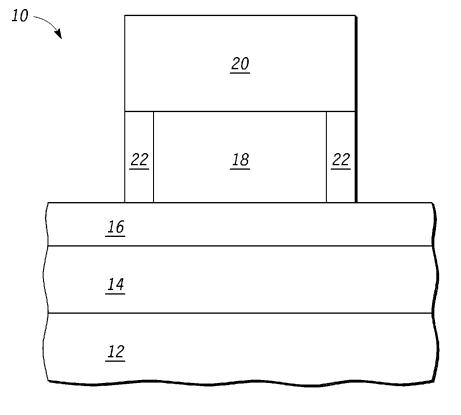

- [0008] Figure 4 shows a partial side view of one embodiment of a thin-film capacitor during a processing stage, consistent with one embodiment of the invention;

- [0009] Figure 5 shows a side view of one embodiment of a thin-film capacitor during a processing stage, consistent with one embodiment of the invention;

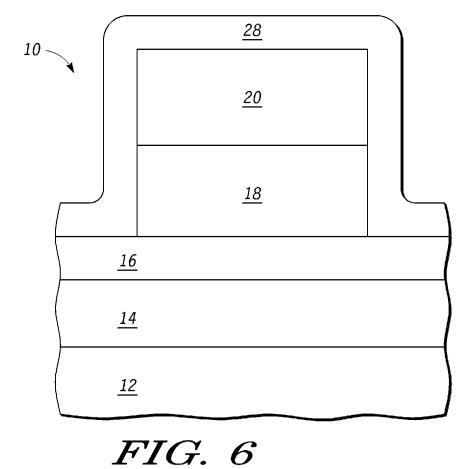

- [0010] Figure 6 shows a partial side view of one embodiment of a thin-film capacitor during a processing stage, consistent with one embodiment of the invention; and

- [0011] Figure 7 shows a partial cross-sectional side view of one embodiment of a wafer during another stage in its manufacture, consistent with one embodiment of the invention.

- [0012] Skilled artisans appreciate that elements in the figures are illustrated for simplicity and clarity and have not necessarily been drawn to scale. For example, the dimensions of some of the elements in the figures may be exaggerated relative to other elements to help improve the understanding of the embodiments of the present invention.

#### **DETAILED DESCRIPTION**

- [0013] The following sets forth a detailed description of a mode for carrying out the invention. The description is intended to be illustrative of the invention and should not be taken to be limiting.

- [0014] In one aspect, a method for forming a capacitor, such as a thin-film capacitor, is provided. The method may include providing a metal-containing bottom electrode and forming a capacitor insulator over the metal-containing bottom electrode. The method may further include forming a metal-containing top electrode layer over the capacitor insulator. The method may further include forming a dielectric-containing field modification layer over the capacitor insulator and at least partially surrounding the metal-containing top-electrode.

- [0015] In another aspect, a method for forming a capacitor, such as a thin-film capacitor is provided. The method may include providing a bottom electrode and forming a capacitor insulator over the bottom electrode. The method may further include forming a metal-

containing top electrode over the capacitor insulator. The method may further include oxidizing a sidewall region of the metal-containing top electrode to form an oxide-containing field modification layer at least partially surrounding the metal-containing top electrode.

[0016] In yet another aspect, a capacitor comprising a metal-containing bottom electrode and a capacitor insulator over the metal-containing bottom electrode is provided. The capacitor may further include a metal-containing top electrode over the capacitor insulator. The capacitor may further include a dielectric-containing field modification layer over the capacitor insulator and at least partially surrounding the metal-containing top electrode.

[0017]Figure 1 shows a partial side view of one embodiment of a thin-film capacitor 10, such as a metal-insulator-metal (MIM) or a metal-insulator-silicon (MIS) capacitor during a processing stage. Thin-film capacitor 10 may be formed of layers, including a bottom electrode layer 12, a capacitor insulator layer 14, a barrier layer 16, and a top electrode layer 18. These layers may be formed by plasma vapor deposition, chemical vapor deposition, or atomic layer deposition techniques. Alternatively, these layers may be epitaxially grown, using atomic layer epitaxy, for example. Although Figure 1 shows barrier layer 16 as part of thin-film capacitor 10, barrier layer 16 may not be formed as part of thin-film capacitor 10. Additional layers may be formed as part of thin-film capacitor 10, if necessary. Bottom electrode layer 12 and top electrode layer 18 may be metal or silicon containing layers. By way of example, the metal containing layer may include tantalum, tantalum nitride, titanium, titanium nitride, or aluminum. In addition, each of bottom electrode layer 12 and top electrode layer 18 may be a laminated structure. Capacitor insulator layer 14 may be formed using materials, such as silicon dioxide, silicon nitride, tantalum pentoxide, or hafnium oxide. Capacitor insulator layer 14 may comprise a laminate structure, as well. Barrier layer 16 may be formed using materials, such as hafnium oxide or aluminum oxide. By way of example, barrier layer 16 may be 10-100 Angstroms thick. Although barrier layer 16 is shown separately from capacitor insulator layer 14, barrier layer 16 may be formed as part of capacitor insulator layer 14. Barrier layer 16 may act as an etch stop layer during the etching of top electrode layer 18. In addition, although Figure 1 shows a planar structure, thin-film capacitor 10 may be non-planar.

[0018] As shown in Figure 2, as part of the next processing step, a patterned masking layer 20 may be formed on top of top electrode layer 18. Next, as shown in Figure 3, the

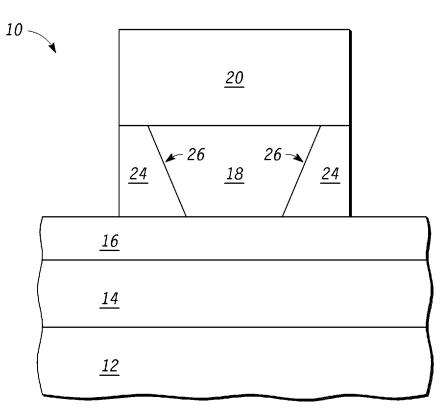

exposed portion of top electrode layer 18 may be etched away. As part of the next processing step, as shown in Figure 4, a field modification layer 22 may be formed on each side of top electrode layer 18 by oxidizing a sidewall on each side of top electrode layer 18. By way of example, field modification layer 22 may reduce the strength of an electric field along the corners of capacitor insulator layer 14. Oxidation may be performed by exposure to oxygen and/or ozone containing plasma at a temperature of 200-400 degree Celsius. Oxidation of top electrode layer 18 may be performed by free radicals of Oxygen. By way of example, a remote plasma oxidation process may be used as part of this step. Oxidation may be performed during or after the etching of top electrode layer 18. Thus, as shown in Figure 4, field modification layer 22 may be formed on top of barrier layer 16 and may at least partially surround top electrode layer 18. Alternatively, field modification layer 22 may be formed on top of capacitor insulator layer 14. By way of example, field modification layer 22 may be at least thicker than 100 Angstroms. Although Figure 4 shows field modification layer 22 having the same height as top electrode layer 18, field modification layer 22 may have a lower height than top electrode layer 18. Furthermore, although Figure 4 shows a field modification layer 22 that is uniform in width, it may have a non-uniform width. Specifically, referring now to Figure 5, an edge 26 between field modification layer 24 and top electrode layer 18 may be at an angle with respect to a top surface of barrier layer 16 and/or capacitor insulator layer 14. By way of example, oxidation of a sidewall region of top electrode layer 18 may result in a boundary between field modification layer 24 and top electrode layer 18, such that the boundary forms an angle with respect to a bottom surface of top electrode layer 18 and the angle facing top electrode layer 18 is greater than 90 degrees.

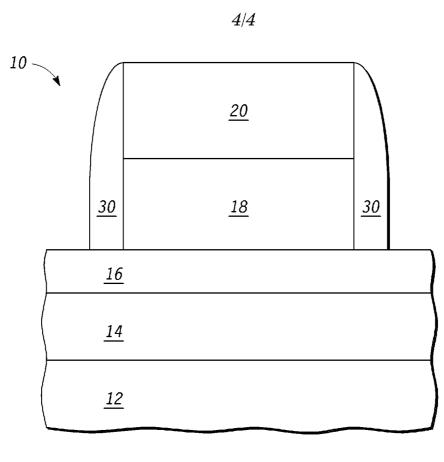

[0019] Figure 6 shows a partial side view of one embodiment of a thin-film capacitor during a processing stage, consistent with one embodiment of the invention. As part of this step, after the step shown in Figure 3, a dielectric-containing layer 28 may be deposited on top of barrier layer 16 and patterned masking layer 20. Dielectric-containing layer 28 may be deposited using chemical vapor deposition or atomic layer deposition. Next, as shown in Figure 7, dielectric-containing layer 28 may be anisotropically etched to form field modification layer 30.

[0020] In the foregoing specification, the invention has been described with reference to specific embodiments. However, one of ordinary skill in the art appreciates that various

modifications and changes can be made without departing from the scope of the present invention as set forth in the claims below. Accordingly, the specification and figures are to be regarded in an illustrative rather than a restrictive sense, and all such modifications are intended to be included within the scope of present invention.

[0021] Benefits, other advantages, and solutions to problems have been described above with regard to specific embodiments. However, the benefits, advantages, solutions to problems, and any element(s) that may cause any benefit, advantage, or solution to occur or become more pronounced are not to be construed as a critical, required, or essential feature or element of any or all the claims. As used herein, the terms "comprises," "comprising," or any other variation thereof, are intended to cover a non-exclusive inclusion, such that a process, method, article, or apparatus that comprises a list of elements does not include only those elements but may include other elements not expressly listed or inherent to such process, method, article, or apparatus.

#### **CLAIMS:**

What is claimed is:

1. A method for forming a capacitor comprising:

providing a metal-containing bottom electrode; forming a capacitor insulator over the metal-containing bottom electrode;

forming a metal-containing top electrode over the capacitor insulator; and forming a dielectric-containing field modification layer over the capacitor insulator

and at least partially surrounding the metal-containing top electrode.

- 2. The method of claim 1, wherein the dielectric-containing field modification layer comprises an oxide.

- 3. The method of claim 1, wherein the dielectric-containing field modification layer comprises an oxide selected from a group consisting of tantalum pentoxide, tantalum oxynitride, titanium oxide, titanium oxynitride, aluminum oxide, and aluminum oxynitride.

- 4. The method of claim 1, wherein forming the dielectric-containing field modification layer comprises oxidizing a sidewall of the metal-containing top electrode.

- 5. The method of claim 4, wherein oxidizing the sidewall of the metal-containing top electrode results in a boundary between the dielectric-containing field modification layer and the metal-containing top electrode, wherein the boundary forms an angle with respect to a bottom surface of the metal-containing top electrode, the angle facing the metal-containing top electrode and being greater than 90 degrees.

- 6. The method of claim 1, wherein forming the dielectric-containing field modification layer comprises forming a blanket insulating layer over the metal-containing top electrode and the capacitor insulator.

7. The method of claim 6, wherein forming the dielectric-containing field modification layer further comprises anisotropically etching the blanket insulating layer.

- 8. The method of claim 1, further comprising:

forming an insulating barrier layer over the capacitor insulator prior to forming the

metal-containing top electrode over the capacitor insulator.

- 9. The method of claim 8, wherein the insulating barrier layer comprises at least one selected from a group consisting of hafnium oxide and aluminum oxide.

- 10. A method for forming a capacitor comprising:

providing a bottom electrode;

forming a capacitor insulator over the bottom electrode;

forming a metal-containing top electrode over the capacitor insulator;

- oxidizing a sidewall region of the metal-containing top electrode to form an oxidecontaining field modification layer at least partially surrounding the metalcontaining top electrode.

- 11. The method of claim 10, wherein the oxide-containing field modification layer comprises an oxide selected from a group consisting of tantalum pentoxide, tantalum oxynitride, titanium oxide, titanium oxynitride, aluminum oxide, and aluminum oxynitride.

- 12. The method of claim 11, wherein the oxidizing is performed using plasma oxidation.

- 13. The method of claim 12, wherein the plasma oxidation is performed at a temperature in a range of approximately 200 to 400 degrees Celsius.

- 14. The method of claim 10, wherein the oxidizing is performed using an oxygen or ozone source which produces free radicals.

- 15. The method of claim 10, wherein oxidizing the sidewall region of the metal-containing top electrode results in a boundary between the oxide-containing field modification

layer and the metal-containing top electrode, wherein the boundary forms an angle with respect to a bottom surface of the metal-containing top electrode, the angle facing the metal-containing top electrode and being greater than 90 degrees.

- 16. The method of claim 10, wherein the bottom electrode comprises a metal.

- 17. The method of claim 10, further comprising:

forming an insulating barrier layer over the capacitor insulator prior to forming the metal-containing top electrode over the capacitor insulator.

- 18. The method of claim 10, further comprising patterning the metal-containing top electrode prior to the oxidizing.

- 19. A capacitor comprising:

- a metal-containing bottom electrode;

- a capacitor insulator over the metal-containing bottom electrode;

- a metal-containing top electrode over the capacitor insulator; and

- a dielectric-containing field modification layer over the capacitor insulator and at least partially surrounding the metal-containing top electrode.

- 20. The capacitor of claim 19, wherein the dielectric-containing field modification layer comprises an oxide selected from a group consisting of tantalum pentoxide, tantalum oxynitride, titanium oxide, titanium oxynitride, aluminum oxide, and aluminum oxynitride.

1/4

FIG. 1

FIG. 2

FIG. 3

FIG. 4

3/4

FIG. 5

FIG. 7