(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6220045号

(P6220045)

(45) 発行日 平成29年10月25日(2017.10.25)

(24) 登録日 平成29年10月6日(2017.10.6)

(51) Int.Cl.

F 1

H04L 1/00

(2006.01)

H04L 1/00

A

H03M 13/09

(2006.01)

H03M 13/09

G06F 13/00

(2006.01)

G06F 13/00

301 F

請求項の数 15 (全 21 頁)

(21) 出願番号

特願2016-503136 (P2016-503136)

(86) (22) 出願日

平成26年3月14日 (2014.3.14)

(65) 公表番号

特表2016-518750 (P2016-518750A)

(43) 公表日

平成28年6月23日 (2016.6.23)

(86) 国際出願番号

PCT/US2014/029554

(87) 国際公開番号

W02014/144941

(87) 国際公開日

平成26年9月18日 (2014.9.18)

審査請求日

平成29年3月9日 (2017.3.9)

(31) 優先権主張番号

13/841,574

(32) 優先日

平成25年3月15日 (2013.3.15)

(33) 優先権主張国

米国(US)

早期審査対象出願

(73) 特許権者 591025439

ザイリンクス インコーポレイテッド

X1L1NX INCORPORATED

アメリカ合衆国 カリフォルニア州 95

124-3400 サンホセ ロジック

ドライブ 2100

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 ジアン、ウェイロン

アメリカ合衆国、95124 カリフォル

ニア州、サン・ノゼ、ロジック・ドライブ

、2100

最終頁に続く

(54) 【発明の名称】モジュール式および拡張可能な巡回冗長検査計算回路

## (57) 【特許請求の範囲】

## 【請求項 1】

データパケットにCRCを追加するための装置であって、

データワードを複数の経路に分割するためのスプリッタと、

複数の巡回冗長検査ユニットとを備え、前記巡回冗長検査ユニットの各々は前記経路の

それぞれ1つを処理するためのものであり、前記巡回冗長検査ユニットの各々は、

前記巡回冗長検査ユニットに供給されるデータ内で終了するパケットの巡回冗長検査

値を出力するための第1の出力ポートと、

前記巡回冗長検査ユニットに供給される前記データ内で開始するまたは進行中のパケ

ットの巡回冗長検査値を出力するための第2の出力ポートとを備える、装置。

## 【請求項 2】

前記複数の巡回冗長検査ユニットのうち第1の巡回冗長検査ユニットに供給される第1

の分割データ内で開始するまたは進行中のパケットの第1の巡回冗長検査値を前記複数の

巡回冗長検査ユニットのうち第2の巡回冗長検査ユニットに供給される第2の分割データ

内で終了するパケットの第2の巡回冗長検査値と組合せるための少なくとも1つの結合器

をさらに備える、請求項1に記載の装置。

## 【請求項 3】

前記複数の巡回冗長検査ユニットのうち前記第1の巡回冗長検査ユニットに供給される

前記第1の分割データ内で開始するまたは進行中の前記パケットと、前記複数の巡回冗長

検査ユニットのうち前記第2の巡回冗長検査ユニットに供給される前記第2の分割データ

10

20

内で終了する前記パケットとは同じパケットである、請求項 2 に記載の装置。

**【請求項 4】**

前記複数の巡回冗長検査ユニットのうち少なくとも 2 つによって処理される少なくとも 1 つのパケットが前記複数の巡回冗長検査ユニットのうち前記少なくとも 2 つの間で連続的か否かを検査するための少なくとも 1 つの検査回路をさらに備える、請求項 2 または 3 に記載の装置。

**【請求項 5】**

前記検査回路は、パケット開始信号が前記 2 つの巡回冗長検査ユニットのうちの第 1 の巡回冗長検査ユニットに関連付けられる第 1 の経路中に見出されるかまたは前記パケットが第 1 の経路中で進行中である場合、かつパケット終了信号が前記 2 つの巡回冗長検査ユニットのうちの前記第 2 の巡回冗長検査ユニットに関連付けられる第 2 の経路中に見出される場合、前記 2 つの巡回冗長検査ユニットの間で前記パケットが連続していると判断する、請求項 4 に記載の装置。10

**【請求項 6】**

前記巡回冗長検査ユニットの各々はさらに、

前記経路の 1 つを複数のレーンに分割するためのスプリッタと、

前記複数のレーンのうちそれぞれ 1 つのビットの部分的巡回冗長検査値を算出するための複数の巡回冗長検査モジュールとを備える、請求項 1 から 5 のいずれかに記載の装置。

**【請求項 7】**

前記巡回冗長検査ユニットの各々はさらに、前記巡回冗長検査ユニットに供給される前記データ内で終了する前記パケットの前記巡回冗長検査値としての出力のための巡回冗長検査値を選択するための選択モジュールを備える、請求項 1 から 6 のいずれかに記載の装置。20

**【請求項 8】**

前記巡回冗長検査ユニットの各々はさらに、前記巡回冗長検査ユニットに供給される前記データ内で開始するまたは進行中の前記パケットの前記巡回冗長検査値としての出力のための巡回冗長検査値を選択するための選択モジュールを備え、前記選択モジュールは、前記レーンのいずれにもパケット開始信号が存在しなければ、前記レーンのうち 1 つの中のパケット開始信号に基づいてまたはデフォルト条件に基づいて、前記巡回冗長検査ユニットに供給される前記データ内で開始するまたは進行中の前記パケットの前記巡回冗長検査値としての出力のための前記巡回冗長検査値を選択するためのものである、請求項 1 から 6 のいずれかに記載の装置。30

**【請求項 9】**

前記巡回冗長検査ユニットの各々はさらに、少なくとも第 1 の巡回冗長検査モジュールからの部分的巡回冗長検査値と少なくとも第 2 の巡回冗長検査モジュールからの部分的巡回冗長検査値とを組合せて、前記第 2 の巡回冗長検査モジュールに関連付けられる前記レーンのうちそれぞれ 1 つの巡回冗長検査値を出力するための少なくとも 1 つの結合器を備える、請求項 3 から 6 のいずれかに記載の装置。

**【請求項 10】**

前記巡回冗長検査ユニットの各々はさらに、少なくとも 1 つのフォワーディングモジュールのレーンと宛先レーンとの間の多数のビットに基づいて少なくとも 1 つの部分的巡回冗長検査値をビットフォワーディングするための少なくとも 1 つのフォワーディングモジュールを備える、請求項 1 から 9 のいずれかに記載の装置。40

**【請求項 11】**

以前のデータワードからの積算巡回冗長検査値を受信するための入力ポート、または次のデータワードの積算巡回冗長検査値を出力するための出力ポートをさらに備える、請求項 1 から 10 のいずれかに記載の装置。

**【請求項 12】**

積算巡回冗長検査値を、前記巡回冗長検査ユニットの少なくとも 1 つに供給されるデータ内で終了するパケットの少なくとも 1 つの巡回冗長検査値と組合せるための少なくとも50

1つの結合器をさらに備え、

前記複数の巡回冗長検査ユニットによって処理されるパケットのサイズは前記経路の各々の少なくとも経路サイズである、請求項3から6のいずれかに記載の装置。

【請求項13】

少なくとも1つのフォワーディングユニットのそれぞれの経路と宛先経路との間の多数のビットに基づいて少なくとも1つの巡回冗長検査値をビットフォワーディングするための少なくとも1つのフォワーディングユニットをさらに備える、請求項1から12のいずれかに記載の装置。

【請求項14】

パケットの終わりとレーンの終わりとの間または前記パケットの前記終わりと経路の終わりとの間の多数の空ビットに基づいて少なくとも1つの巡回冗長検査値の行列変換を行なうための少なくとも1つのアンロールユニットをさらに備える、請求項1から13のいずれかに記載の装置。 10

【請求項15】

データパケットにCRCを追加するための方法であって、

データワードを複数の経路に分割することと、

前記経路の各々を並列に処理することとを備え、各経路毎に、前記処理することは、

前記経路に供給されるデータ内で終了するパケットの巡回冗長検査値を算出することと、

前記経路に供給される前記データ内で開始するまたは進行中のパケットの巡回冗長検査値を算出することとを備える、方法。 20

【発明の詳細な説明】

【技術分野】

【0001】

発明の分野

この発明は一般的に、たとえばフィールドプログラマブルゲートアレイなどの集積回路などの装置、および高いデータレートでパケットの巡回冗長検査計算を行なうための方法に関する。

【背景技術】

【0002】

発明の背景

巡回冗長コード(CRC)は、データの完全性を確実にするために電気通信およびネットワーク化において広く用いられる。たとえば、あらゆるイーサネット(登録商標)パケットは、追加CRC32コード(32ビットCRCコード)とともに伝送される。巡回冗長検査を行なうための回路は、シフトレジスタを用いてシリアルに実現されている。しかしながら、この方策は、現在のデータレートに追従するには不十分である。さらに、100Gb/sまでのデータレートのためのいくつかのCRC回路設計が存在するが、これらは一般的に、入力幅が52ビット以下の比較的狭いデータバスを用いることに係る。

【発明の概要】

【課題を解決するための手段】

【0003】

発明の要約

1つの実施形態では、巡回冗長検査を行なうための装置が開示される。たとえば、装置は、データワードを複数の経路に分割するためのスプリッタを備える。装置は、複数の巡回冗長検査ユニットも備える。ユニットの各々は経路のそれぞれ1つを処理するためのものである。さらに、ユニットの各々は、ユニット内で終了するパケットの巡回冗長検査値を出力するための第1の出力ポートと、ユニット内で開始するまたは進行中のパケットの巡回冗長検査値を出力するための第2の出力ポートとを備える。

【0004】

さまざまな実施形態では、複数の巡回冗長検査ユニットによって処理されるパケットの

10

20

30

40

50

サイズは、経路のうちの各々の少なくとも経路サイズであり、装置はさらに、複数の巡回冗長検査ユニットの第1のもの内で開始するまたは進行中のパケットの第1の巡回冗長検査値を複数の巡回冗長検査ユニットの第2のもの内で終了するパケットの第2の巡回冗長検査値と組合せるための少なくとも1つの結合器を備え、少なくとも1つの結合器は、第1の巡回冗長検査値および第2の巡回冗長検査値に対する排他的or演算を行なうためのものであり、複数の巡回冗長検査ユニットのうち第1のもの内で開始するまたは進行中のパケットと複数の巡回冗長検査ユニットのうち第2のもの内で終了するパケットとは同じパケットであり、装置はさらに、複数の巡回冗長検査ユニットのうち少なくとも2つの間に、複数の巡回冗長検査ユニットのうち少なくとも2つによって処理される少なくとも1つのパケットが連続的であるか否かを検査するための少なくとも1つの検査回路を備え、検査回路は、パケット開始信号が2つのユニットのうち第1のユニットに関連付けられる第1の経路の中に見出されれば、またはパケットが第1の経路中で進行中であれば、かつパケット終了信号が2つのユニットのうち第2のユニットに関連付けられる第2の経路中に見出される場合は、パケットが2つのユニット間で連続していると判断し、巡回冗長検査ユニットの各々はさらに、経路のうち1つを複数のレーンに分割するためのスプリッタと、レーンのうちそれぞれ1つのビットの部分的巡回冗長検査値を算出するための複数の巡回冗長検査モジュールとを備え、M個の巡回冗長検査ユニットの各々はさらに、巡回冗長検査ユニット内で終了するパケットの巡回冗長検査値としての出力の巡回冗長検査値を選択するための選択モジュールを備え、選択ユニットは、レーンのうち1つの中のパケット終了信号に基づいて、またはレーンのいずれにもパケット終了信号が存在しなければデフォルト条件に基づいて、巡回冗長検査ユニット内で終了するパケットの巡回冗長検査値としての出力のための中間巡回冗長検査値を選択するためのものであり、巡回冗長検査ユニットの各々はさらに、巡回冗長検査ユニット内で開始するまたは進行中のパケットの巡回冗長検査値としての出力の巡回冗長検査値を選択するための選択モジュールを備え、選択モジュールは、レーンのうち1つの中のパケット開始信号に基づいて、またはレーンのいずれにもパケット開始信号が存在しなければデフォルト条件に基づいて、巡回冗長検査ユニット内で開始するまたは進行中のパケットの巡回冗長検査値としての出力の巡回冗長検査値を選択するためのものであり、巡回冗長検査ユニットの各々は、少なくとも第1の巡回冗長検査モジュールからの部分的巡回冗長検査値を少なくとも第2の巡回冗長検査モジュールからの部分的巡回冗長検査値と組合せて、第2の巡回冗長検査モジュールに関連付けられるレーンのそれぞれ1つの巡回冗長検査値を出力するための少なくとも1つの結合器をさらに備え、巡回冗長検査ユニットの各々はさらに、少なくとも1つのフォワーディングモジュールのレーンと宛先レーンとの間の多数のビットに基づいて少なくとも1つの部分的巡回冗長検査値をビットフォワーディングするための少なくとも1つのフォワーディングモジュールを備え、装置はさらに、以前のデータワードからの積算巡回冗長検査値を受信するための入力ポートおよび/または次のデータワードの積算巡回冗長検査値を出力するための出力ポートを備え、装置はさらに、積算巡回冗長検査値を、巡回冗長検査ユニットのうち少なくとも1つ内で終了するパケットの少なくとも1つの巡回冗長検査値と組合せるための少なくとも1つの結合器を備え、装置はさらに、少なくとも1つのフォワーディングユニットの経路と宛先経路との間の多数のビットに基づいて少なくとも1つの巡回冗長検査値をビットフォワーディングするための少なくとも1つのフォワーディングユニットを備え、装置はさらに、パケットの終わりとレーンの終わりとの間またはパケットの終わりと経路の終わりとの間の多数の空ビットに基づいて少なくとも1つの巡回冗長検査値をアンロールするための少なくとも1つのアンロールユニットを備える。

【0005】

別の実施形態では、巡回冗長検査を行なうための別の装置が開示される。たとえば、装置は、データワードを処理するための複数の巡回冗長検査ユニットを備える。1つの実施形態では、巡回冗長検査ユニットの各々は、データワードの一部を処理するためおよびそれぞれの巡回冗長検査値を出力するためのものである。装置は、それぞれ複数のパケットの最終的な巡回冗長検査値としての出力の複数のそれぞれの巡回冗長検査値を選択するた

10

20

30

40

50

めの選択ユニットも含む。データワードは最小パケットサイズよりも大きい。

#### 【0006】

さらなる実施形態では、巡回冗長検査を行なうための方法が開示される。たとえば、方法は、データワードを複数の経路に分割することと、経路の各々を処理することとを備える。1つの実施形態では、経路の各々毎に、処理することは、経路内で終了するパケットの巡回冗長検査値を算出することと、経路内で開始するまたは進行中のパケットの巡回冗長検査値を算出することとを備える。

#### 【0007】

添付の図面は開示の1つ以上の局面に従う例示的な実施形態を示す。しかしながら、添付の図面は、開示を示される実施形態に限定するように扱われるべきではなく、図面は、説明および理解のためのみのものである。10

#### 【図面の簡単な説明】

#### 【0008】

【図1】CRC回路／装置実現例のブロック図である。

【図2】CRCユニットのブロック図である。

【図3】CRCユニットの代替的な実施形態のブロック図である。

【図4】経路上でおよび／またはCRCユニットを通して処理されるビットの例示的なシナリオのタイミング図である。

【図5】パケットが2つのCRCユニットの間で連続しているか否かを検査するための検査回路のブロック図である。20

【図6】経路上でおよび／またはCRCユニットを通して処理されるビットのさらなる例示的なシナリオのタイミング図である。

【図7】巡回冗長検査を行なうための方法のブロック図である。

【図8】本明細書中に記載の機能を実行するのに用いるのに好適な汎用コンピュータまたは計算装置の高レベルブロック図である。

#### 【発明を実施するための形態】

#### 【0009】

##### 図面の詳細な説明

本開示は一般的に、巡回冗長検査を行なうための装置および方法に関する。たとえば、本開示は、たとえば、プログラマブル論理装置（PLD）、専用IC、フィールドプログラマブルゲートアレイ（FPGA）などの集積回路（IC）内で実現されて、高いビットレートでかつ広いデータバス上で受信されるパケットに対して巡回冗長検査動作を行なうことができる。本開示の実施形態は、1024ビット以上を含む入力幅を有する広いデータバスを用いて、たとえば400Gb/s以上など、100Gb/sを上回るデータ伝送速度をサポートし得る。回路のアーキテクチャは、モジュール式および拡張可能であり、リソース・性能のトレードオフを提供することができる。30

#### 【0010】

巡回冗長コード（CRC）は、データの完全性を確実にするのに電気通信およびネットワーク化および多数の他の適用例で広く用いられる。たとえば、イーサネット（登録商標）パケットは、フレーム検査シーケンス（FCS）とも称される、追加CRC32コード（32ビットCRCコード）とともに伝送される。巡回冗長検査を行なうための回路は、シフトレジスタを用いてシリアルに実現されている。しかしながら、この方策は現在のデータレートに追従するには不十分である。さらに、100Gb/sまでのデータレートのためのいくつかのCRC回路設計が存在するが、これらは一般的に、512ビット以下の入力幅／ワードサイズを有する比較的狭いデータバスを用いることに係る。これは、将来的なスループットの拡張を限定してしまう。というのも、クロック周波数の大きな上昇を得ることがより難しくなるからである。400Gb/sなどのより高いスループットを達成するため、CRC回路はより広いデータバスを用いてもよい。たとえばこれによって、クロックサイクル当たり1024ビットよりも多くのパケットを処理することができるようになる。しかしながら、ネットワークパケット／イーサネット（登録商標）フレームの最小サイズ40

は 512 ビットであるので、複数のパケットが同時にこの広いデータバス上に現われることがある。パケットはデータバス内の任意の位置で開始および終了する可能性がある。このように、ワード当たりのパケット数が増大するにつれて、したがって、異なるパケット位置に対処することがより複雑になってしまう。

## 【0011】

応じて、本開示の実施形態は、たとえば 512 ビット入力データ幅に最適化される、たとえば 512 ビット C R C ユニット上に構築される拡張可能 C R C アーキテクチャを記載する。本実施形態は、スループットが増大するのに応じたリソースの使用の線形拡張を提供する一方で、伝統的な方策は超線形拡張に係る。本開示の実施形態は 512 ビットの倍数および分数に関連して説明されるが、本開示はそのように限定されるものではないことに留意すべきである。すなわち、例示的なアーキテクチャは、512 ビット経路サイズ / C R C ユニットサイズを特徴とし、これは、現在の最小のイーサネット（登録商標）フレームサイズに対応し、したがって、示される目的によく適合している。しかしながら、当業者は、本開示に従って他のデータバス幅、フレームサイズ、経路サイズ、および線のサイズを用いてもよいことを認めるであろう。このように、本開示の他の実施形態は、異なる通信技術に対応してもよく、異なるネットワーク層について最適化されてもよく、かつたとえば、フレーム、パケット、セグメント、データグラム、プロトコルデータユニット（P D U）、運搬データユニット（T D U）、セッションデータユニット（S D U）などの異なるパケット / ユニットサイズに合わせられてもよい。

## 【0012】

巡回冗長検査は、データ伝送適用例で広く用いられるパリティビットベースの誤り検出方式であり、多項式算数に基づいている。伝送すべきデータのビットは多項式係数である。一例として、ビットストリーム 1101011011 は 10 項多項式を表わす 10 ビットを有する。

## 【0013】

## 【数 1】

$$\begin{aligned} M(x) = & 1 \cdot x^9 + 1 \cdot x^8 + 0 \cdot x^7 + 1 \cdot x^6 + 0 \cdot x^5 + 1 \cdot x^4 + 1 \cdot x^3 + 0 \cdot x^2 + 1 \cdot x^1 + 1 \cdot x^0 = \\ & x^9 + x^8 + x^6 + x^4 + x^3 + x^1 + 1 \end{aligned}$$

## 【0014】

メッセージの C R C を計算するため、生成多項式  $G(x)$  と呼ばれる別の多項式が選ばれる。 $G(x)$  は、ゼロよりも大きな次を有し、かつ  $x^0$  項において非ゼロ係数を有するべきである。この結果、生成多項式について、いくつかの可能な選択肢、したがって標準化の必要性が生じる。C R C 16 は、生成多項式を用いる 1 つのそのような標準である。

## 【0015】

## 【数 2】

$$G(x) = x^{16} + x^{15} + x^2 + 1$$

## 【0016】

C R C 16 は、すべての単一および二重の誤り、奇数ビットについてのすべての誤り、長さ 16 以下のすべてのバースト誤り、ならびにより長いバーストの大部分の誤りを検出する。別の標準的な C R C は、生成多項式を用いる C R C 32 である。

## 【0017】

## 【数 3】

$$G(x) = x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$$

## 【0018】

10

20

30

40

50

一般的に、 $n$ ビットのCRCは、データストリームを多項式 $M(x)$ として表わし、 $M(x)$ を $x^n$ で乗算し( $n$ は多項式 $G(x)$ の次である)、かつ結果を生成多項式 $G(x)$ で除算することによって算出される。結果的に得られる余りがデータストリームに追加されて伝送される。次に、完全な伝送された多項式が受信器端において同じ生成多項式で除算される。この除算の結果が余りを有しなければ、伝送誤りは存在しない。数学的には、これを以下のように表わすことができる。

#### 【0019】

$$CRC = [(M(x) \cdot x^n) / G(x)] \text{ の余り}$$

I E E E 8 0 2 . 3 は、最初の32ビットを補って、多項式 $M(x)$ を、宛先アドレス、発信元アドレス、長さ／種類、およびフレームのデータとして定義する。以上のCRCの算出からの余りが補われ、結果は、I E E E 8 0 2 . 3 32ビットフレーム検査シーケンス(FCS)フィールドである。FCSは、イーサネット(登録商標)フレームの端に追加され、まず最上位ビット( $x^{31}, x^{30}, \dots, x^1, x^0$ )が伝送される。10

#### 【0020】

1つの実施形態では、本開示は、生成多項式に従って入来データのさまざまな部分に対して行列演算を用いて、部分的な、中間の、および最終的なCRCを生成する。巡回冗長コード(CRC)のいくつかの有用なプロパティを本実施形態で用いる。たとえば以下のとおりである。

#### 【0021】

$$\text{プロパティ } 1 : CRC(A \text{ xor } B) = CRC(A) \text{ xor } CRC(B)$$

$$\text{プロパティ } 2 : CRC(\{X, 0^P\}) = H^P \cdot CRC(X)$$

$0^P$ は $P$ ビットのゼロであり、 $\{X, 0^P\}$ は $P$ 個のゼロが追加された $X$ であり、 $H^P$ は生成多項式から導出される行列である。

$$\text{プロパティ } 3 : CRC(\{0^P, Y\}) = CRC(Y)$$

#### 【0022】

一例として、入来データワードDは1024ビットを備えてよい。Dについて巡回冗長コード(CRC)を算出するために、データを $D = [\text{ビット } 1023 \dots \text{ビット } 0] = E [D_1 | 0^{512}] \text{ xor } F [0^{512} | D_2]$ として記述することができ、式中、 $D_1 = [\text{ビット } 1023 \dots \text{ビット } 512]$ 、かつ $D_2 = [\text{ビット } 511 \dots \text{ビット } 0]$ である。このように、プロパティ1に従うと、 $CRC(D) = CRC(E) \text{ xor } CRC(F)$ である。プロパティ3に従って単に $D_2$ についてCRCを算出することによって、 $CRC(F)$ を算出することができる。換言すると、Fのすべての1024ビットに対してよりもむしろ、 $D_2$ の512ビットのみについてCRC(F)算出を行なうことができる。プロパティ2に従うと、 $CRC(E)$ を以下のように算出することができる。まず、 $D_1$ についてCRCを算出する。第2に、生成関数 $H^P$ から導出される行列で $CRC(D_1)$ を乗算し、結果、 $CRC(E)$ が得られる。 $CRC(E)$ および $CRC(F)$ が一旦わかると、 $CRC(D)$ は、 $CRC(D) = CRC(E) \text{ xor } CRC(F)$ として計算される。

30

#### 【0023】

これらのさまざまなプロパティおよび変換の有用性をさまざまな構成要素および特徴と関連して以下に論じる。特に、本開示の実施形態は、並列CRCユニットおよび並列経路を用いるCRC回路を特徴とする。各々の経路はCRCユニットを含み、これを用いて、各々は、入来データワードの一部を処理して2つのCRC出力を生成し、次にこれを他のユニットのうち1つ以上からのCRC出力と組合せて、データワード内で終了する1つ以上のパケットの最終CRC値を生じてもよい。

40

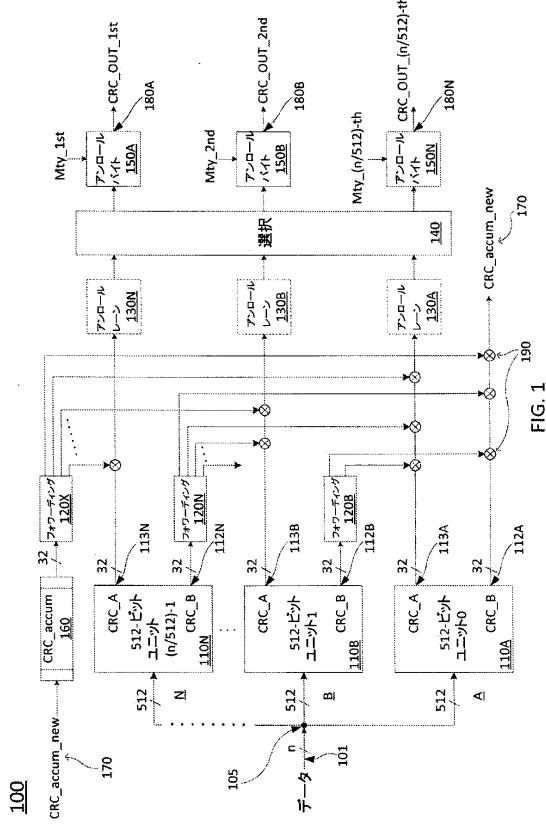

#### 【0024】

図1は、本開示の実施形態に従う装置またはCRC回路100のブロック図を示す。図1に示されるように、CRC回路100はN個の経路に分割され、各々の経路は、512ビット幅の計算ブロック(概して、 $n$ ビット幅の計算ブロック)を含み、たとえば各々は、それぞれ512ビットCRCユニット110A, 110B...110Nを有する。さまざ

50

まな実施形態では、各々の 512 ビット C R C ユニットは 4 本のレーンを備え、各々のレーンは 128 ビット C R C 計算モジュールを有し、これは図 2 および図 3 により詳細にそれぞれ示される。4 本の 128 ビットレーンは例示の目的のためにのみ示されることに留意すべきである。このように、本開示は、任意の数のレーンまたは任意の特定のレーンのサイズに限定されるものではない。さらに、1 つの実施形態では、たとえば、幅広い（549 ビットまでの）排他的 OR ゲートに基づいて、よりモノリシックなブロックである異なる種類の C R C ユニットアーキテクチャを用いてもよい。このように、C R C ユニット 110A - 110N のうち任意の 1 つ以上のためのそのような代替的なアーキテクチャを、その基本的な機能を変更せずに、C R C 回路 100 中に組入れてもよい。

## 【0025】

10

1 つの実施形態では、C R C 回路 100 は、N 個の 512 ビット経路 A, B および N を備える（図 1 には 3 本の経路のみが示される）。したがって、入力ポート 101 への入来データは、1536 ビット幅のデータバスを備え得る。スプリッタ 105 は、データバス上の信号を、それぞれの 512 ビット経路 A, B, および N に分割する。1 つの実施形態では、シリアルデータは、C R C 回路 100 に入る前に並列データワードに変換される。このように、1 つの実施形態では、「より早い」ビットを、回路のいちばん上から「後の」ビットが処理される回路のいちばん下に向けてバス上に置いてもよい。

## 【0026】

20

本開示の実施形態に従うと、データワードの幅は N ビットである。最小サイズのイーサネット（登録商標）パケットは 64 バイト（すなわち 512 ビット）であるので、同じワード内で終了する（ $N / 512$ ）個までのパケットが存在する。このように、各々のワード毎に（ $N / 512$ ）個までの C R C 出力が存在する。応じて、図 1 では、たとえば出力ポート 180A、180B、および 180N 上に潜在的に 3 つの C R C 出力が存在する。というのも、同じ 1536 ビットデータワード内で 3 つまでの 512 ビットイーサネット（登録商標）フレームが終了し得るからである。たとえば、n 番目の C R C 出力 180N は、同じ N ビット入力データワード（ $n = N / 512$ ）上の n 番目の完了パケットについてのものである。

## 【0027】

20

各々の 512 ビット C R C ユニット 110A - 110N は、2 つの巡回冗長コードを生成する。一方は、ユニット / 経路内で終了するパケット（たとえば、C R C 出力ポート 113A - 113N 上の C R C\_A ）であり、他方は、ユニット / 経路内で開始するまたは進行中のパケット（たとえば、C R C 出力ポート 112A - 112N 上の C R C\_B ）である。レジスタ 160 は、複数のワードに跨るパケットの積算 C R C 値（CRC\_accum\_new 170）を記憶する。

## 【0028】

30

並列 C R C 計算では、部分的 C R C を計算するためのデータにゼロが追加されてもよい。これらの追加されるゼロは「空ビット」と呼ばれる。このように、さまざまな実施形態は、パケットの終わりにある付加的に積算されるゼロを（たとえば、図 2 に示されるような C R C 回路を用いて）128 ビット境界に、または（たとえば、図 3 に示されるような C R C 回路を用いて）512 ビット境界にも、訂正する。これらの方策の各々は、終了調節が必要ない場合、たとえば、元のパケットが冒頭でゼロ詰めされれば、これを 128 ビットまたは 512 ビット境界に未揃えさせるようにも適用可能である。1 つの実施形態では、C R C ユニット 110A - 110N の各々における処理に従って空ビットおよび / またはゼロ詰めに対処するさらなる演算を実現することもできる。たとえば、「Fwd」ブロック、フォワーディングユニット 120B、120N、および 120X は、異なる数の空ビットだけ C R C 値をフォワードする。レーンアンロールユニット 130A - 130N および バイトアンロールユニット 150A - 150N は、異なる数の空バイトだけ C R C をアンロールする（戻す）。「フォワーディング」および「アンロール」機能は、図 2 および図 3 の例示的な C R C ユニット 200 および 300 の検討に従って以下により詳細に記載される。

40

50

## 【0029】

1つの実施形態では、Nビットデータバス上の入来データ（たとえば、本明細書中ではパケットとも称されることがあるイーサネット（登録商標）フレーム）は、(N/L)個のビットパケット開始(SoP)およびパケット終了(EoP)信号を含む。1つの実施形態では、SoPおよびEoP信号のサイズはN/Lビットである。CRC回路100全体内でN/L本のレーンが存在する。応じて、1つの実施形態では、SoP信号またはEoP信号は、パケット（またはフレーム、PDUなど）が対応のレーンにおいて開始するまたは終了するかどうか、およびレーン内のどこでフレームが終了するかを示す。SoP信号またはEoP信号がレーンについて検出されれば、レーンに対応するSoPまたはEoPフラグが設定される。たとえば、単一のビットは一「1」に設定されて、特定のレーンについてSoP信号が検出されたことを示し、かつSoP信号がレーン中のデータ上で検出されなければ、SoPフラグはゼロ「0」のままであり得る。1つの実施形態では、パケットの始めがレーンの始めに整列されなければならないと仮定する。1つの実施形態では、パケットの終わりはレーンの終わりに整列されないことがある。しかしながら、1つの実施形態では、パケットの終わりがバイトの終わりに整列されると仮定される。このように、レーンはL/8バイトを含有し、パケットは、終了レーン内の任意のバイトで終了し得る。1つの実施形態では、Mty（「空」）値が算出されて、レーン内の空バイトの数を示す。1つの実施形態では、Mty値は、特定のバイト内のEoP信号の検出と、EoP信号が検出されるバイトの位置よりも下のレーン内の付加的なバイトの数の判定に基づいて算出される。Mty値を記憶するのに必要なビットの数は、size\_Mty = (N/512)\*Log2(L/8)ビットによって与えられる。最小サイズのイーサネット（登録商標）パケットは512ビットであるので、(n = N / 512)個までのパケットが同じワード内に含有され得る。このように、n番目のMtyはn番目の完了パケットについてのものである。

## 【0030】

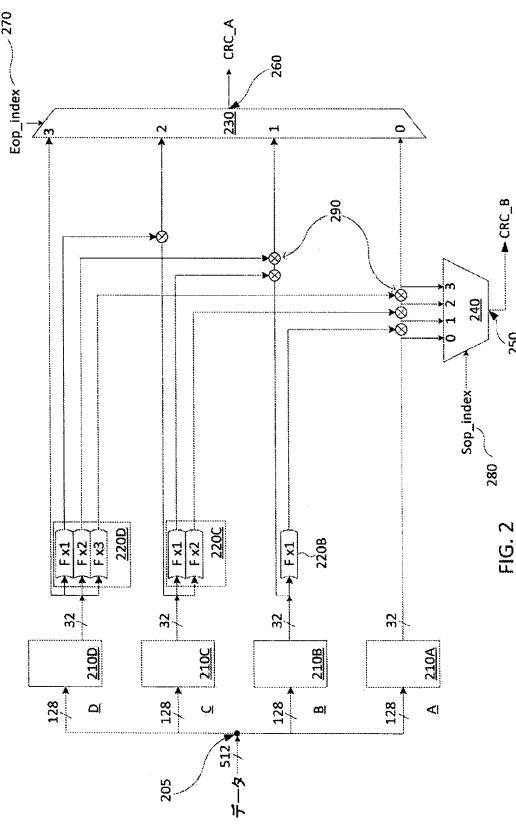

図2は、L = 128である（すなわち、レーンの幅が128ビットである）512ビットCRCユニット200の例示的な実施形態を示す。たとえば、CRCユニット200は、図1のCRCユニット110A - 110Nの各々として実現されてもよい。図2に示されるように、CRCユニット200は4つのCRCモジュール210A - 210Dを含む。モジュールの各々は、各々のLビットレーンA - D上のデータ上のCRC値を計算する。各々のLビットレーン上のCRC値は、本明細書中で部分的CRC値と称される。フォワーディングユニット220B、220C、および220Dは、「i」本のレーンだけ部分的CRC値をフォワーディングするための「Fxi」モジュールを含む。たとえば、図2に示されるように、フォワーディングユニット220CはF×2モジュールを含み、これは、レーンCの部分的CRC値を2レーンだけ、すなわちレーンAにフォワーディングする。図2に示されるように、フォワーディングされた部分的CRC値の各々は、宛先レーンの部分的CRC値に組合される。たとえば、図2にいくつかの結合器290が示されるが、その各々は、たとえば、これが入力として取る部分的CRC値に対して排他的or演算を行なうためのものである。

## 【0031】

部分的CRC値をフォワーディングすることに加えて、フォワーディングユニット220B - 220Dの各々は、部分的CRC値を特定の宛先レーンにフォワーディングする/送る前に、宛先レーンに対応する多数のビットに基づいて部分的CRC値を「フォワーディングする」。ビットフォワーディングの動作は、他のレーンならびに/または、たとえばマルチプレクサ230および240などの選択モジュールに、結果的に得られるCRC値を「フォワーディングする」（たとえば、送出するおよび/または出力する）こととは対照的なCRC値に対するデータ操作/演算である。たとえば、レーンD中のフォワーディングユニット220DのF×2モジュールは、256ビット（2つのレーンに対応するビットの数）に基づいて部分的CRC値をフォワーディングし、結果的に得られる部分的CRC値をレーンBに送出し、これは、排他的or演算を介して結合器290でレーンB

の部分的CRC値に組合される。1つの実施形態では、フォワーディングすることは、生成関数および宛先レーンへの距離（ビットの数）に基づく入力CRC値の行列変換を備える。特定のレーンの最後の結合器に従って出力されるCRC値は、マルチブレクサ230への入力の1つを備える。フォワーディングユニット220B-220Dのうち各々の中のフォワーディングモジュールの各々は、同様の様で動作する。さまざまなレーンからの部分的CRC値の組合せを備えるCRC値は、マルチブレクサ230および240へのそれぞれの入力を備える。

#### 【0032】

「EoP\_index」信号270は、パケットが終了しているレーン（たとえば、対応のEOPビット/フラグが、パケットがそのレーンで終了していることを示す「1」に設定されているレーン）の指標を特定する。EoP\_index信号270は、マルチブレクサ230への入力のうちどれが、CRC\_A（CRCモジュール200によって処理される512ビット内で終了するパケットのCRC値）として出力ポート260上に出力されるかを制御する。換言すると、マルチブレクサ230は、EoP\_indexの値に基づいて、CRC\_Aとしてどの入力CRC値を出力すべきかを選択する。同様に、「SoP\_index」信号280は、パケットが開始しているレーンの指標を特定する（すなわち、レーンについての対応のSOPビット/フラグが「1」に設定される）。EoP\_indexおよびSoP\_indexのデフォルト値は、それぞれ0および(512/L-1)である。SoP\_index信号280は、マルチブレクサ240への入力CRC値のうちどれがCRC\_B（CRCユニット200内で開始するまたは進行中のパケットのCRC値）として出力ポート250上に出力されるかを制御する。換言すると、マルチブレクサ240は、SoP\_indexの値に基づいて、CRC\_Bとしてどの入力CRC値を出力すべきかを選択する。10

20

#### 【0033】

図1の検討に戻って、CRC回路100のさらなる構成要素および特徴をここで説明する。以上で言及したように、パケットはレーンの始まりで始まるとき仮定される。しかしながら、1つの実施形態では、パケットは、経路内の任意のレーンで、および（バイトの終わりで終了と仮定される）レーン内の任意の位置で、終了してもよい。応じて、1つの実施形態では、バイトアンロールユニット150A-150NがCRC回路100に含まれて、レーンの終わりで終了しないパケットに対処する。以上で言及したように、1つの実施形態では、Mty（「空」）値が算出されて、レーン内の空バイトの数を示す。Mty値は、特定のバイト内のEOP信号の検出と、EOP信号が検出されるバイトの位置よりも下のレーン内の付加的なバイトの数の判定に基づいて算出されてもよい。Mty値を記憶するのに必要なビットの数は、size\_Mty = (N/512)\*Log2(L/8)ビットによって与えられる。最小サイズのイーサネット（登録商標）パケットは512ビットであるので、(n=N/512)個までのパケットが同じワード内に含有され得る。このように、n番目のMtyは、n番目の完了パケットについてのものである。図1に示されるように、Mty\_1<sup>st</sup>、Mty\_2<sup>nd</sup>...Mty\_(n/512)<sup>th</sup>はそれぞれ、バイトアンロールユニット150A-150Nへの入力である。一例として、Mty\_1<sup>st</sup>は値7を有し得る。これは、パケットがレーンのバイト9で終了し、レーンの最後の7バイトがゼロ/空バイトとして扱われるべきであることを示す。30

40

#### 【0034】

1つの実施形態では、Mty値に応じてCRCを「アンロールする（戻す）」または「解く」ために、生成関数に基づくおよびMtyの値（ビットの数）に基づく入力CRC値の行列変換が行なわれる。別の実施形態では、バイトアンロールユニット150A-150Nのうち任意の1つ以上においてパイプライン化アンロール演算を実現してもよい。1つの実施形態では、パイプラインは、i個の段を備え、i番目の段が2<sup>i</sup>バイトをアンロールするためのものである。このように、1つの実施形態では、16バイトまでをアンロールするのに4つのパイプライン段が必要である。別の実施形態では、反復関数が行なわれる。たとえば、1つの実施形態では、CRC値の最下位ビットが除去される。ビットが「1」であれば、結果的に生じるCRC値に除数（すなわち、生成多項式/生成関数）50

が加算される。しかしながら、除去されるビットがゼロ「0」であれば、結果的に生じるCRC値にゼロが加算される。この演算は、Mty\_1<sup>st</sup>の値が2であれば(2バイトまたは16ビット)、アンロール演算を16回行なって最終CRC値を計算する。また別の実施形態では、異なるアンロールアルゴリズムを利用してもよい。換言すると、本開示は、任意の1つの特定のアンロールアルゴリズムに限定されるものではない。

#### 【0035】

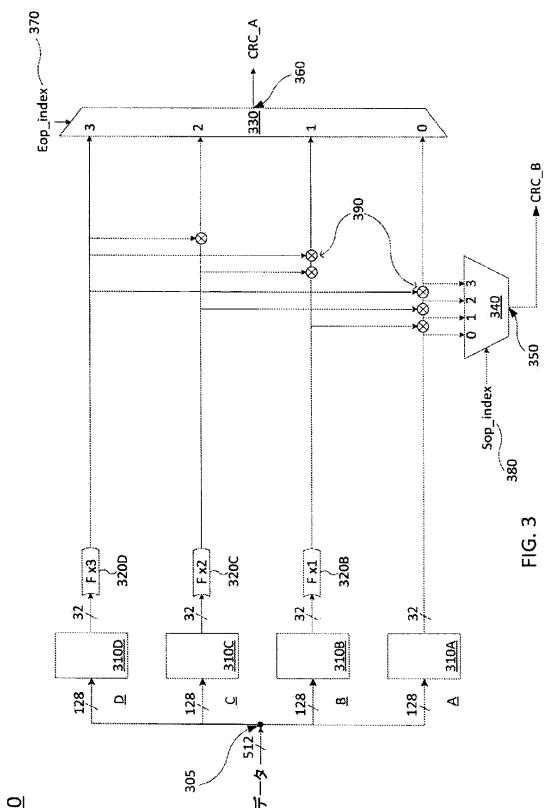

CRC回路100のCRCユニット110A-110Nの各々が図2のユニット200などのCRCユニットを備える場合、レーンアンロールユニット130A-130Nを回路100から省略してもよい。しかしながら、1つの実施形態では、これらのレーンアンロールユニットは、CRCユニットが512ビット経路の終わりへのパケット整列を維持する回路100中に含まれる。経路の終わりに整列する例示的なCRCユニットを図3に示す。

#### 【0036】

図3は、1つの実施形態に従うCRCユニット300を示す。たとえば、図1のCRCユニット110A-110Nのうち任意の1つ以上がCRCユニット300を備えてもよい。図3に示されるように、CRCユニット300は、図2のCRCユニット200との多数の類似点を共有する。たとえば、CRCユニット300は、512ビット入力ポート/バスと、512ビットを4本の128ビットレーンA-Dに分割するスプリッタ305とを有する。レーンA-Dの各々は、それぞれCRCモジュール310A-310Dを含む。しかしながら、図2に対して、図3のフォワーディングユニット320B-320Dは、CRC値を出力する/フォワーディングする前に単一のビットフォワーディング動作のみを行なう。たとえば、フォワーディングユニット320Dは、レーンAの宛先レーンを仮定する384ビット(3レーンフォワーディング)に基づいてCRC値中のビットを経路の最後のレーンにフォワーディングしてもよい。パケットは実際にレーンA上で終了し得るが、そうである必要がないことに留意されたい。たとえば、パケットは依然としてレーンB上で終了してもよい。同様に、フォワーディングユニット320Cは、経路の最後のレーンであるレーンAの宛先も仮定して、256ビットに基づいて、CRCユニット310Cによって出力される部分的CRCのビットを「フォワーディング」してもよい。この態様のビットフォワーディングは本質的に、パケットをCRCユニット300の経路/終わりに整列させる。しかしながら、この仮定は誤っているかもしれないで、図1のCRC回路100のレーンアンロールユニット130A-130Nで経路の終わりに対するパケットの整列を訂正してもよい。CRCユニット300の付加的な構成要素は、図2のCRCユニット200の構成要素と同様の態様で機能する。たとえば、選択モジュール/マルチブレクサ330は、パケット終了EoP\_index値370に基づいて出力ポート360上にCRC\_Aとして出力すべき、入力部分的CRC値を選択する。同様に、選択モジュール/マルチブレクサ340は、パケット開始SoP\_index値380に基づいて出力ポート350上にCRC\_Bとして出力すべき入力CRC値を選択する。さらに、結合器390の各々は図2の結合器290と同じ機能を有する。

#### 【0037】

図1のCRC回路100に戻って、512ビット経路の終わりに整列するCRCユニットを用いる場合には、レーンアンロールユニット130A-130Nを含んでもよい。たとえば、図1のCRCユニット110Bが図3のCRCユニット300を備えると仮定する。パケットがCRCユニット300のレーンC(第2のレーン)上で終了すれば、マルチブレクサ330は、出力CRC\_Aとして(レーンCからの)入力2を選択する。しかしながら、フォワーディングユニット320Dおよび320Cは、本質的に2つ(2)多過ぎるレーンだけ、それらのそれぞれのCRC値を「過剰フォワーディング」したであろう。このように、レーンアンロールユニット130Bは、入力としてそれが受ける中間CRC値を2つのレーン(256ビット)だけアンロールしてもよい。レーンアンロールユニットは、先に記載したバイトアンロールユニット150A-150Nと同じまたは同様

10

20

30

40

50

の設計に基づいていてもよい。たとえば、アンロール演算は、生成関数および空レーンの数に対応する空ビットの数に基づく入力CRC値のマトリックス操作を備えてもよい。1つの実施形態では、レーンアンロールユニットは、対応のレーンのEoP\_index値に基づいてアンロールすべきレーンの数を決める。たとえば、以上の同じ例に従うと、パケットがレーンB上で終了すれば、EoP\_index = 2である。このように、レーンアンロールユニットは、2本の(2)レーン(256ビット)に対応するビットの数に基づいてアンロールする。パケットは依然としてレーンBの真ん中内で終了したかもしれないで、CRC値は、依然としてバイトアンロールユニット150A - 150Nのうち1つの中の終了レーン内の空バイトの数だけアンロールされるべきである。

## 【0038】

10

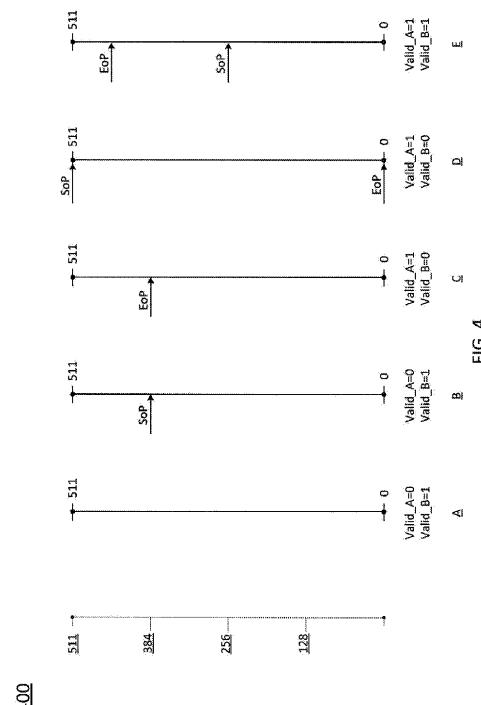

CRC回路100のさらなる機能、特にフォワーディングユニット120B, 120Nおよび選択ユニット140の機能を図4の例を用いて示し得る。特に、図4は、本開示の実施形態に従うCRCモジュールによって処理され得る512ビット入力のためのさまざまなシナリオのタイミング図400を示す。たとえば、5つの例A - Eの各々は、任意の1クロックサイクルで受信/処理され得る512ビットを表わす。これらの例では、ビット511は「より早い」ビットであり、ビット0がデータストリーム中の「後の」ビットであることに留意すべきである。たとえば、図1の回路100などのCRC回路は、ただ1つの構成要素であるトランシーバを備えてもよい。1つの実施形態では、トランシーバは、CRC回路およびトランシーバの他の構成要素によるより高速の処理のために並列データに変換されるシリアルデータを伝送するおよび/または受信する。このように、データがシリアルに受信されると、これをデータワードの順次の並列ビット位置に置いてもよい(これは次に、上述のようにいくつかの512ビットCRCユニットによる処理のために、CRC回路によっていくつかの経路に分割されてもよい)。例Aでは、経路中で(すなわち、512ビットCRCユニットによって処理される512ビット内で)受信されるSOPまたはEOP信号が存在しない。これは2つの理由によることがある。すなわち、経路上にパケット/データが存在しないか、またはパケットが経路を通って進行中である場合である(たとえば、パケットが512ビットよりも大きい場合、パケットは他の512ビットCRCユニットによって処理される異なる経路上で始まりかつ終了することがある)。いずれの場合も、経路内で終了するパケットが存在しないので、Valid\_Aはゼロ「0」に設定されて、経路内で終了するパケットのCRC\_A出力が有効な出力ではないことを示す。一方で、Valid\_Bは一「1」に設定されて、経路内で開始するまたは進行中のパケットについてのCRC\_B出力が有効な出力であることを示す。

20

## 【0039】

30

例Bでは、512ビット内にSOP信号が見出されるが、依然としてEOP信号は見出されない。このように、経路内で始まるパケットが存在するが、パケットは経路内で終了しない。このように、Valid\_Aはゼロ「0」に設定され、Valid\_Bは一「1」に設定される。例Cでは、512ビット内にEOP信号が見出されるが、SOP信号は存在しない。応じて、Valid\_Aが一「1」に設定されて、経路内で終了するパケットについてのCRC\_A出力が有効であることを示す(というのも、パケットは、EOP信号が示すように経路内で終了するからである)。しかしながら、Valid\_Bはゼロ「0」に設定されて、経路内で開始するまたは進行中のパケットについてCRC\_B出力が無効な出力であることを示す。

40

## 【0040】

例Dでは、SOPおよびEOP信号の両方が512ビット内に見出される。SOPおよびEOP信号の両者ともが512ビット内に見出されるが、Valid\_Aのみが一「1」に設定される。これは、EOPがSOPの後に見出されて、EOPがSOP信号で始まる同じパケット内で終了していることを明確に示すからである。このため、出力CRC\_Bは無効であり、したがってパケットは経路内で終了したので、いずれの他のCRCユニットからのいずれの他のCRC値とも組合せてはならない。例Eでは、ここでも、SOPおよびEOP信号が両者とも512ビット中に見出される。しかしながら、EOP信号はSOP

50

信号よりも早く、このことは、EoP信号が別のCRCユニット／経路から継続しているが現在の経路内で終了するパケットについてのものである一方で、Sop信号が新しいパケットの開始についてのものであることを示す。このように、Valid\_Aは一「1」に設定されて、経路内で終了するパケットのCRC値であるCRC\_Aが有効であることを示す。同様に、Valid\_Bは一「1」に設定されて、ユニットを通って開始するまたは連続的であるパケットのCRC値であるCRC\_Bも有効であることを示す。

#### 【0041】

図4と関連してここで図1を参照すると、回路100のデータバスは、3つの512ビット経路に分割される1536ビットワードを備えてもよい。一例として、最も早い経路(経路N)は、図4の例Bに示されるように、512ビットを備え、真ん中の経路(経路B)は、例Eの512ビットを備え、かつ最後の経路(経路A)は、例Cの512ビットを備える。このように、経路NのCRCユニット110Nは、データ経路上のビットを処理して、CRC\_AおよびCRC\_Bを生成する。さらに、Valid\_Aはゼロ「0」に設定され、Valid\_Bは「1」に設定される。応じて、CRCユニット110Nによって出力されるCRC\_Aを用いるべきではない。選択ユニット140の目的は、出力ポート180A - 180N上の1つ以上の最終CRC値として出力すべき有効なCRC値を選ぶことである。このように、経路NについてのValid\_A信号／フラグがゼロ「0」、すなわち無効であることに基づいて、選択ユニット140は、最終CRC値として出力すべきCRCユニットの110NのCRC\_Aとして出力されるCRC値を無視してもよい、または選択しないようにしてもよい。フォワーディングユニット120Bおよび120Nの目的は、パケットが終了する別の経路/CRCユニットからの中間のCRC値と組合せるべき、現在の経路内で終了しないパケットの中間CRC値をフォワーディングすることである。このように、Valid\_Bが「1」に設定されている、すなわち有効であるので、フォワーディングユニット120Nは、他のCRCユニットの出力と組合せるべきCRC\_Bを出力／送出してもよい。

#### 【0042】

フォワーディングユニット120Nならびにフォワーディングユニット120Bおよび120Xは、図2および図3に示されるフォワーディングユニットと同様の態様で機能することに留意すべきである。このように、たとえば、フォワーディングユニット120Nが、1レーンだけ(たとえば、レーンBに)CRC\_Bをフォワーディングしている場合、これは、512ビット(宛先レーンへのビットでの距離)に基づいてフォワーディングし、2レーン(たとえば、レーンAに)フォワーディングする場合は、これは1024ビットに基づいてフォワーディングする。

#### 【0043】

経路N上で処理が発生するのと同時に、経路B中のCRCユニット110Bは、図4の例E中に示されるように512ビットを処理する。CRCユニット110Bは、中間のCRC値CRC\_AおよびCRC\_Bとしての出力のためのCRC値を生成する。さらに、Sop信号の前にEoP信号が見出される。そのため、Valid\_AおよびValid\_Bは両者とも一「1」に設定される。注目すべきことに、フォワーディングユニット120Nは、経路Nから経路BにCRC\_Bを出力する／送る(上述のように、CRCユニット110N／経路NについてのValid\_B=1)。このように、CRCユニット110NからのCRC\_Bは、たとえば排他的or演算を実行する結合器190において、CRCユニット110BからのCRC\_Aと組合される。組合されたCRC値は次に、アンロールユニット130Bおよび選択ユニット140によって受信される。さらに、選択ユニット140は、最終CRC値として出力すべき、経路B上の組合されたCRC値を選ぶ。たとえば、選択ユニット140は、経路BについてのValid\_A信号を調べてもよく、これは「1」に設定されているので、パケットが現在のCRCユニット110B内でまたは経路Bに沿って終了したことを見出す。

#### 【0044】

さらに、新しいパケットが経路B上のデータ内で始まりもする。Valid\_Bも一「1」に

10

20

30

40

50

設定されるため、フォワーディングユニット 120B は、図 1 に示される接続に沿って CRC\_B をフォワーディングする。

#### 【0045】

CRC ユニット 110Aにおいて、図 4 の例 C の 512 ビットが処理され、CRC\_A および CRC\_B が出力される。EOP 信号は経路 A 上のデータ内に見出される。このように、Valid\_A = 1 である一方で、Valid\_B = 0 である。CRC ユニット 110A の CRC\_A の値は、たとえば排他的 or 演算を実行する結合器 190 において CRC ユニット 110B からの CRC\_B 値と組合される。組合された CRC 値は次に、アンロールユニット 130A および選択ユニット 140 によって受信される。Valid\_A = 1 であるので、選択ユニット 140 は、経路 A に沿う組合された CRC 値が最終的な CRC 値として出力されるのを許容する。注目すべきことに、この例では、単一の 1536 ビットワードについて、選択ユニット 140 によって 2 つの CRC 値が最終的な CRC 値として並列に出力される。10

#### 【0046】

以上の例は本実施形態のいくつかの特徴および利点を示すが、いくつかの事例ではパケットは複数のワードに跨ってもよいことにも留意すべきである。この状況も説明するため、CRC 回路中の最後の経路（たとえば、図 1 の CRC 回路 100 中の経路 A）の出力を、後のサイクルで処理すべき次のデータワードのシード CRC 値として用いる。図 1 に示されるように、値 CRC\_accum\_new 170 は、CRC\_accum レジスタ 160 への入力を備える。このように、たとえば、CRC 回路 100 の経路 B 中で開始し次のデータワード内で終了するパケットについては、フォワーディングユニット 120B は、CRC ユニット 110A の CRC\_A および CRC\_B の両者と組合せるべき CRC ユニット 110B からの CRC\_B 値をフォワーディングする。上の経路 B からの CRC\_B は、ユニット 110A の CRC\_A と組合される。しかしながら、パケットは経路 A 上で終了しないので、CRC ユニット 110A の CRC\_A は無効であり (Valid\_A = 0)、選択ユニット 140 は、単にこの組合された CRC 値を無視する。一方で、ユニット 110B からの CRC\_B は、（たとえば、排他的 or を介して）ユニット 110A からの CRC\_B と組合され、この組合された CRC 値は有効であり、次のデータワードのためのシード CRC 値、すなわち CRC\_accum\_new 170 である。20

#### 【0047】

特定の CRC ユニット / 経路について Valid\_B = 1 である場合、経路のフォワーディングユニットは、1つよりも多くの他の経路に CRC\_B 値をフォワーディングしてもよいことにも留意すべきである。たとえば、フォワーディングユニット 120N は、経路 B および A の両方に CRC ユニット 110N の CRC\_B 値をフォワーディングしてもよい。しかしながら、経路 N 上で開始するまたは進行中のパケットは、経路 A 上ではなく、経路 B 上で終了してもよい。その結果、経路 N の CRC\_B 値は、経路 B のユニット 110B の出力 CRC\_A 値とのみ組合されるべきであり、経路 A 上では無視されるべきである。この目的を達成するため、1つの実施形態では、CRC 回路 100 は連続した検査回路をさらに含んでもよい。30

#### 【0048】

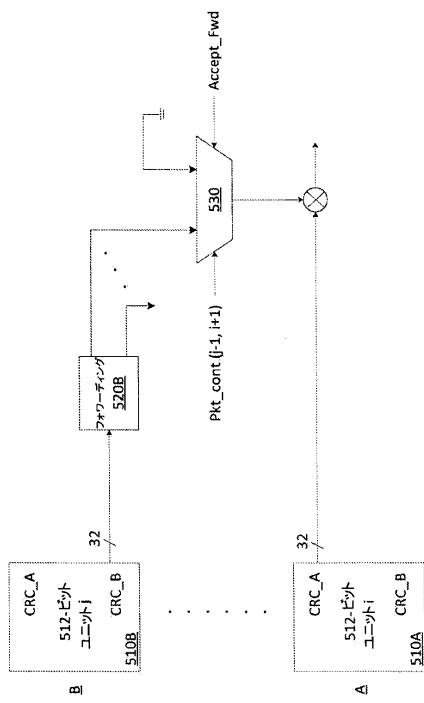

図 5 は、隣接する経路 / CRC ユニット間でパケットが連続しているか否かを検査するための検査回路 500 の例を示す。図 5 に示されるように、経路 A および B 中にそれぞれ 2 つの隣接する CRC ユニット 510A および 510B が存在する。検査ユニット 530 は、フォワーディングユニット 520B の出力と宛先レーン A との間に位置する。1 つの実施形態では、検査ユニットはマルチプレクサを備える。1 つの実施形態では、検査ユニット 530 への入力のうち 1 つはフォワーディングユニット 520B の出力を備え、他方の入力は接地（たとえば、ゼロ「0」）を備える。さらに、1 つの実施形態では、検査ユニット 530 は、「パケット連続」制御信号 Pkt\_cont(j-1, i+1) によって制御される。40

#### 【0049】

進められた CRC\_accum または CRC\_B は、パケットがユニット i よりも上で終了すれ

50

ば、ユニット*i*のCRC\_Aとは組合されないことがある。たとえば、ユニット*j*からの進められたCRC\_Bは、パケットがユニット(*j*-1)とユニット(*i*+1)との間で連続していれば、ユニット*i*のCRC\_Aと組合される。さらに、進められたCRC\_accumは、パケットがいちばん上のユニットとユニット(*i*+1)との間で連続していれば、ユニット*i*のCRC\_Aと組合される。同様に、進められたCRC\_accumまたはCRC\_Bは、パケットが現在のデータワード内で終了すれば、新しいCRC\_accumを生成するのには用いられないことがある。たとえば、ユニット*j*からの進められたCRC\_Bは、パケットがユニット(*j*-1)とユニット0との間で連続していれば、積算には用いられない。パケットがいちばん上のユニットとユニット0との間で連続していれば、(最後のデータワードからの)進められたCRC\_accumも積算に用いられる。1つの実施形態では、ユニット同士の間のSOPおよびEOPビットを見ることによって、パケットがユニット同士の間で連続しているか否かが判断される。応じて、図5に示されるように、検査ユニット530は、Pkt\_cont(*j*-1, *i*+1)がSOPおよびEOP信号に基づいて生成される信号であり、かつパケットがユニット(*j*-1)と(*i*+1)との間で(たとえば、それぞれユニット510Aとユニット510Bとの間で)連続しているか否かを示す場合に、進められたCRC(CRC\_B)を転送すべきかどうかを判断する。同様の態様で異なる連続性検査を行なうように、多数の同様の検査ユニットが異なる経路の間に位置してもよいことに留意すべきである。

10

#### 【0050】

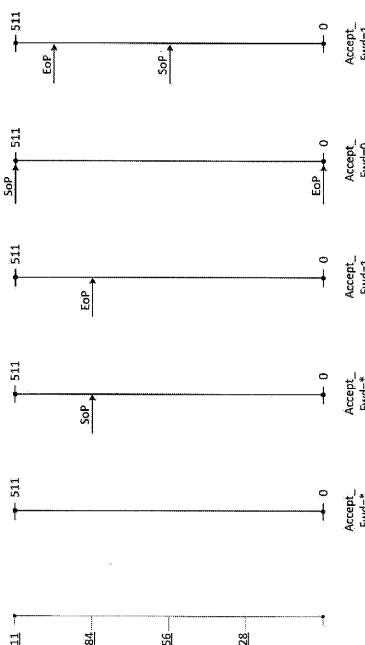

進められたCRCがユニットに転送されるべきか否かを決めるとともに、1つの実施形態では、ユニットが進められるCRCを受付けることを望むか否かを決める必要もある。パケットが同じユニット内で開始しかつ終了する場合、このユニットのCRC\_Aは、いずれの進められるCRCとも組合される必要がない。図6は、経路上および/またはCRCユニットを通して処理されるビットについてのいくつかの例示的なシナリオと、進められたCRC値を受付けるべきか否かについての判断とを有するタイミング図600を示す。1つの実施形態では、経路内に存在し得るSOPおよびEOP信号は、より高いユニットからおよびCRC\_accumレジスタから、進められたCRCをユニット/経路が受付けるべきか否かを判断することができる。ここで、「\*」は「無関係」を意味する。なぜなら、これらの場合、ユニットのCRC\_A出力は無効だからである。1つの実施形態では、「フォワーディング受付」Accept\_Fwd信号は単一のビットを備え、これを、図5中の検査ユニット530への附加的な制御信号として用いてもよい。別の実施形態では、別個の制御論理が同じ経路内に位置して、Accept\_Fwd信号に従うフォワーディングまたは阻止を達成してもよい。

20

30

#### 【0051】

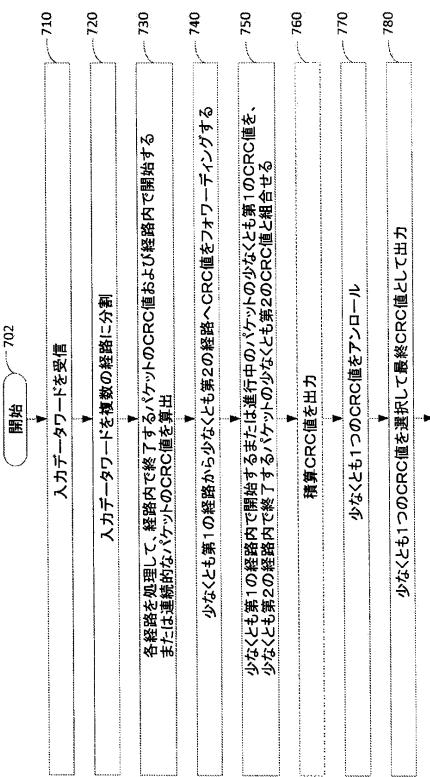

図7は、巡回冗長検査を行なうための方法700のブロック図を示す。たとえば、上述の実施形態のうち任意の1つ以上に従う回路/装置によって方法700を行なうことができる。1つの実施形態では、本開示に従うコンピュータ読み出可能媒体は、方法700のステップ、機能、または動作を行なうようにプログラマブル装置がプログラミングするようにする一連の命令を記憶する。方法はステップ702で開始し、ステップ710に進む。

40

#### 【0052】

ステップ710で、方法700は入力データワードを受信する。たとえば、方法は、1024ビット幅以上のデータバスを介して並列データを受信し得る。

#### 【0053】

ステップ720で、方法700は、入力データワードを複数の経路に分割する。たとえば、方法は、データワードを並列処理のためのいくつかの等しいサイズの経路に分割してもよい。1つの実施形態では、経路の各々は512ビット幅である。

#### 【0054】

ステップ730で、方法700は、経路の各々をたとえば並列に処理する。1つの実施形態では、経路の各々を処理することは、経路内で終了するパケットの巡回冗長検査(C

50

R C ) 値を算出することと、経路内で開始するまたは進行中のパケットの巡回冗長検査値を算出することとを含む。

#### 【 0 0 5 5 】

1つの実施形態では、各経路毎に、処理することは、経路を複数のレーンに分割することを備える。たとえば、レーンの各々は、経路からの等しい数の一連のバイトを備えてよい。1つの実施形態では、各レーン毎に、方法は部分的 C R C 値を計算し、部分的 C R C 値を「より下の」レーン（概して他のレーン）にフォワーディングする。1つの実施形態では、フォワーディングすることは、現在のレーンから宛先レーンへの距離に応じた部分的 C R C 値の行列変換を備える。1つの実施形態では、各レーン毎に、方法はさらに、たとえば排他的 o r 演算を用いて、そのレーンについて算出される C R C 値を、任意の「より上の」レーン（概して他のレーン）からレーンに進められる任意の C R C 値と組合せる。最終的に、方法は、レーンの1つから組合された C R C 値を選択して、特定のレーン中で検出され得るパケット信号の終了に基づいて経路内で終了するパケットの C R C 値として出力してもよい。同様に、方法は、デフォルト条件（たとえば、レーンのうちいずれにも、検出されるパケット信号の開始が存在しない場合、パケットが経路の中で始まつておらず、上方のいずれかの経路の中でまたは先のデータワードの中で開始したと仮定される場合）に基づいて、またはレーンのうち1つ内でのパケット信号の開始の検出に基づいて、経路を通して開始するまたは連続的なパケットの組合された C R C 値を選択して出力してもよい。10

#### 【 0 0 5 6 】

ステップ 740 で、方法は、少なくとも第1の経路から少なくとも第2の経路に C R C 値をフォワーディングする。たとえば、パケットは、第1の経路中で開始してもよく、または連続的であってもよい。このように、経路内で開始するまたは連続的であるパケットの部分的 C R C 値は、「より下の」1つ以上の経路（たとえば、パケットが終了する経路）の他の部分的 C R C 値と組合される。1つの実施形態では、フォワーディングすることは、宛先経路に従う部分的 C R C 値の行列変換を備える。たとえば、宛先経路が現在の経路より2つ前の経路であれば、行列変換は、経路当たりのビットの数の2倍に基づいてよい。1つの実施形態では、ステップ 740 は、複数の経路から複数の異なる宛先経路に C R C 値をフォワーディングすることを備えることに留意すべきである。さらに、1つの実施形態では、ステップ 740 で、以前のデータワードからの積算 C R C 値も経路のうち1つ以上に進められてもよい。30

#### 【 0 0 5 7 】

ステップ 750 で、方法 700 は、少なくとも第1の経路内で開始するまたは進行中のパケットの少なくとも第1の C R C 値を、少なくとも第2の経路内で終了するパケットの少なくとも第2の C R C 値と組合せる。1つの実施形態では、組合せることは、2つの C R C 値に対して排他的 o r 演算を行なうことを備える。1つの実施形態では、ステップ 750 は、2つの経路の間でパケットが連続的であるか否かをまず検査することを含む。たとえば、同じパケットは、第1の経路上で開始し、第2の経路上で終了してもよい。このように、2つの経路からの C R C 値が組合される。しかしながら、2つの経路にわたって同じパケットの連続性が存在しなければ、C R C 値を組合せるべきではない。これに代えてまたはこれに加えて、1つの実施形態では、ステップ 750 は、以前のデータワードからの積算 C R C 値を現在のデータワードの1つ以上の経路からの1つ以上の C R C 値と組合せることを備えてもよい。40

#### 【 0 0 5 8 】

オプションのステップ 760 で、方法 700 は積算 C R C 値を出力する。たとえば、パケットがデータワードの最後の経路中で進行中であるまたは連続的であり、かつパケットが現在のデータワード内で終了していないければ、積算 C R C 値を出力し、かつ（パケットデータが終了し得る）次のデータワードに対する方法 700 のその後の反復のために記憶すべきである。

#### 【 0 0 5 9 】

50

ステップ 770 で、方法 700 は少なくとも 1 つの C R C 値をアンロールする。たとえば、パケットはレーン内の任意の位置で終了してもよい。このように、C R C 値は、パケットの終わりとレーンの終わりおよび / または経路の終わりとの間の任意の空ビットに対処するように調節される必要があり得る。たとえば、1 つの実施形態では、アンロールすることは、生成関数 / 多項式および多数の空ビットに従う C R C 値の行列変換を備える。1 つの実施形態では、方法 700 は、2 つ以上の C R C 値をアンロールすることを備える。たとえば、2 つ以上のパケットは、本実施形態では、同じデータワード内で終了し得る。このように、ステップ 770 で、空ビットのそれぞれの数に基づいて、C R C 値の各々に対して別個のアンロール動作を行なってもよい。

## 【0060】

ステップ 780 で、方法は、1 つ以上の C R C 値を選択し、最終的な C R C 値として C R C 値を出力する。たとえば、1 つ、2 つ、またはいくつかのパケットは、すべて同じデータワード内で終了してもよい。たとえば、ワードサイズが N であれば、経路サイズは 512 であり、最小パケットサイズも 512 であり、同じワード内で潜在的に終了するパケットの数は  $n = N / 512$  である。 $N = 1536$  であれば、3 つの経路が存在し、ワード内で終了するパケットが潜在的に 3 つある。しかしながら、経路の各々は C R C 出力を有し得るが、出力のすべてが必ずしも有効な最終 C R C 値であるわけではない。たとえば、パケットは、真ん中の経路ではなく、第 1 の経路内および最後の経路内で終了することがある。このように、ステップ 780 で、方法 700 は、有効な C R C 値のみを選択して、最終的な C R C 値として出力してもよい。

## 【0061】

ステップ 780 の後に、方法 700 はステップ 795 に進み、ここで方法が終了する。具体的に特定されていないが、方法 700 の 1 つ以上のステップまたは動作は、特定の適用例にとって要件とされるように、記憶する、表示する、および / または出力するステップを含んでもよいことに留意すべきである。換言すると、方法において論じられる任意のデータ、記録、フィールド、表、および / または中間の結果を、特定の適用例の必要に応じて、別の装置に記憶する、表示する、および / または出力することができる。さらに、判断動作を記載するまたは決定に係る、図 7 中のステップ、動作、またはブロックは、必ずしも、判断動作の両方の分岐を実施することを要件とするとは限らない。換言すると、判断動作の分岐のうち 1 つをオプションのステップとみなすことができる。

## 【0062】

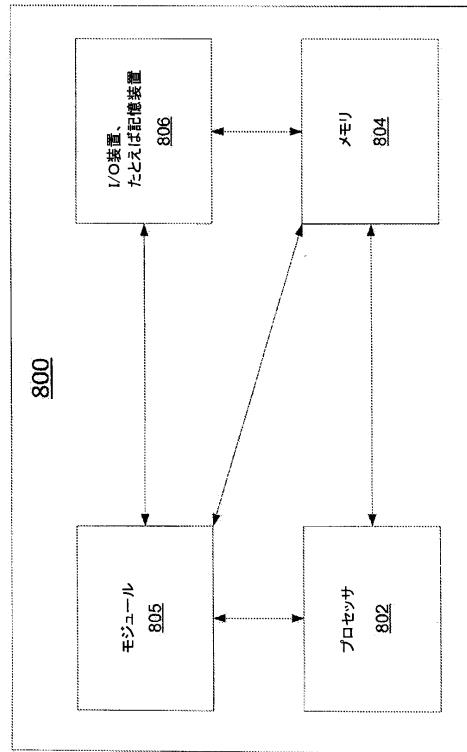

図 8 は、本明細書中に記載の機能のうちいくつかまたはすべてを行なうのに用いるのに好適な汎用コンピュータ、計算装置、または計算システム 800 の高レベルブロック図を描く。図 8 に描かれるように、システム 800 は、プロセッサ素子 802 (たとえば、CPU)、たとえばランダムアクセスメモリ (RAM) および / または読み専用メモリ (ROM) などのメモリ 804、冗長巡回検査を行なうためのモジュール 805、ならびにさまざまな入力 / 出力装置 806 (たとえば、メモリ装置、テープドライブ、フロッピー (登録商標) ドライブ、ハードディスクドライブもしくはコンパクトディスクドライブ、受信機、送信機、スピーカ、ディスプレイ、音声合成器、出力ポート、およびユーザ入力装置 (キーボード、キーパッド、マウスなど) を含むがこれらに限定されない記憶装置) を備える。

## 【0063】

たとえば、特定用途向け集積回路 (ASIC)、FPGA などの PLD、汎用コンピュータ、またはマイクロプロセッサなどの任意の他のハードウェア均等物を用いて、ソフトウェアとハードウェアとの組合せで本開示の実施形態を実現することができる。1 つの実施形態では、冗長巡回検査を行なうための本モジュールまたはプロセスをメモリ 804 にロードし、プロセッサ 802 によって実行して、以上で論じたような機能を実現することができる。このため、本開示の実施形態の (関連のデータ構造を含む) 冗長巡回検査を行なうための本モジュールまたはプロセス 805 を、たとえば、RAM メモリ、磁気もしくは光学ドライブ、またはディスクケットなどの非一時的コンピュータ読み出可能記憶媒体上に

10

20

30

40

50

記憶することができる。

#### 【0064】

本開示の実施形態は、たとえば、PLDおよび/またはFPGAなどの、同調可能ICによって全体がまたは部分的に実現されてもよい。より具体的には、プログラマブル論理装置(PLD)は、さまざまな選択された機能を実現するようにユーザがプログラミング可能な汎用装置である。1つの種類のPLDは、典型的には、コンフィギュラブル論理ブロック(CLB)のアレイおよび複数の入力/出力ブロック(IOB)を含むフィールドプログラマブルゲートアレイ(FPGA)である。CLBは個別にプログラミング可能であり、二、三の入力信号に対してさまざまな論理機能を行なうように構成可能である。IOBは、CLBからFPGAの外部ピンへ出力信号を駆動する、および/または外部のFPGAピンから入力信号を受信するように構成可能である。FPGAは、さまざまなCLBおよびIOBの間で選択的に信号を経路決めして多数の入力信号のより複雑な機能を生じるようにプログラミング可能なプログラマブル相互接続構造も含む。CLB、IOB、およびプログラマブル相互接続構造は、(たとえば、汎用コンピュータ800からの)コンフィギュレーションデータを、CLB、IOB内のさまざまなスイッチおよびマルチブレクサならびに相互接続構造を制御する関連のメモリセル中にロードすることによってプログラミングされて、コンフィギュレーションデータによって特定される論理および経路決め機能を実現してFPGAにおいてユーザ設計を実現する。FPGAは、他のプログラミング可能なおよびプログラミング不可能なリソースも含んでもよい。そのため、図1-図3と関連して以上で示される回路は、図1-図3の回路のうち任意の1つ以上の任意の1つ以上の構成要素の均等の論理演算を行なう複数のCLBにおいて実現されてもよい。たとえば、1536ビット幅のデータバス上で受信されるパケットに対してCRCを行なうための本開示の実施形態は、約15,000個のルックアップテーブル(LUT)、3,000個のレジスタ、および4,500個のスライスを用いてFPGA上で実現された。

#### 【0065】

以上は本開示の1つ以上の局面に従う例示的な実施形態を説明するが、以下の請求項およびその均等物によって定められるその範囲から逸脱することなく、本開示の1つ以上の局面に従う他のおよびさらなる実施形態を考案してもよい。ステップを列挙する請求項はステップの任意の順序を暗示するものではない。商標は、それらのそれぞれの所有者の財産である。

【図1】

【図2】

【図3】

【図4】

【図5】

FIG. 5

500

【図7】

FIG. 7

700

【図6】

FIG. 6

【図8】

FIG. 8

---

フロントページの続き

(72)発明者 ブレブナー , ゴードン・ジェイ

アメリカ合衆国、95124 カリフォルニア州、サン・ノゼ、ロジック・ドライブ、2100

(72)発明者 カーソン , マーク・ビィ

アメリカ合衆国、95124 カリフォルニア州、サン・ノゼ、ロジック・ドライブ、2100

審査官 岡 裕之

(56)参考文献 米国特許出願公開第2009/0282322(US, A1)

特開平10-209880(JP, A)

特開2002-359561(JP, A)

特許第3554715(JP, B2)

特開2011-211353(JP, A)

鳴原 正博 他, 100Gbps級MAC用並列CRC演算処理の検討, 2007年電子情報通信学会通信ソサイエティ大会講演論文集2, 2007年 8月29日, p.140, B-7-80

(58)調査した分野(Int.Cl., DB名)

H04L 1/00

G06F 13/00

H03M 13/09

I EEE X plore